ad9858中文资料

AD9850介绍AD9850中文资料

第13章DDS芯片AD9850/AD9851的设计13.1 硬件设计信号源作为现代电子产品设计和生产中的重要工具,必须满足高精度、高速度、高分辨率等要求。

本章基于DDS ( Direct Digital Synthesis ,直接数字频率合成)技术,采用AD9850 DDS芯片,采用F169单片机作为控制芯片,实现一种了简易信号发生器的设计,该信号发生器具有输出频率范围宽,可以输出正弦和方波两种波形,与键盘结合易于实现全数字化的设计。

13.1.1 AD9850 DDS芯片简介随着数字技术的飞速发展,用数字控制方法从一个参考频率源产生多种频率的技术,即直接数字频率合成(DDS)技术异军突起。

美国AD公司推出的高集成度频率合成器AD9850便是采用DDS技术的典型产品之一。

AD9850采用CMOS工艺,其功耗在3.3V左右。

供电时仅为155mW,扩展工业级温度范围为-40~80℃,采用28脚SSOP表面封装形式。

AD9850的引脚排列如图13-1所示:LSB D0FQ-UD CLKIN AGND AVDDRSET QOUT QOUTBD4D5D6D7 MSBDGNDDVDORESETIOUTIOUTBAGNDAVDODACBL(NC)VINPVINN图13-1 AD9850的引脚图图13-2中层虚线内是一个完整的可编程DDS系统,外层虚线内包含了AD9850的主要组成部分。

图13-3为其组成框图。

图13-2 AD9850组成原理AD9850内含可编程DDS 系统和高速比较器,能实现全数字编程控制的频率合成[22]。

可编程DDS 系统的核心是相位累加器,它由一个加法器和一个N 位相位寄存器组成,N 一般为24~32。

每来一个外部参考时钟,相位寄存器便以步长M 递加。

相位寄存器的输出与相位控制字相加后可输入到正弦查询表地址上。

正弦查询表包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0°~360°范围的一个相位点。

基于AD9858的雷达信号波形产生器设计

基于AD9858的雷达信号波形产生器设计1 引言近年来,随着雷达技术的高速发展对雷达信号源的要求也越来越高。

宽工作频段、高输出功率、复杂多变的信号调制形式和信号的稳定度已成为衡量雷达信号源性能的重要指标。

ad9858是业界首款具有1 gs/s直接数字合成器(dds),10位d/a转换器,快速频率跳跃和精细调谐分辨率功能的单片解决方案,ad9858优良的性能使其适用于军事以及航空雷达的信号源设计。

2 雷达信号波形产生器雷达信号波形产生器在有源雷达整体结构中占有重要地位,能在低功率电平上产生雷达信号的基本波形,因而易于得到脉冲压缩和相参系统等所要求的复杂波形。

基本波形经过功率放大器后即可送至天线作为雷达输出信号。

图1所示为采用功率放大发射机和超外差接收机雷达的简化框图。

雷达系统普遍采用的发射信号大敛分为:单频脉冲、线性调频信号及编码调制信号。

为了增大探测距离,优化距离分辨率、速度分辨率等技术指标,通常可将这些信号组合来形成波形。

采用高速dds器件ad9858形成的波形信号具有高精度、高扫描率、抗干扰性好、截获率低等特性,而且硬件电路结构简单,有助于设备的小型化和集成化。

3 dds工作原理3.1 dds基本原理直接数字频率合成(dds)采用全数字结构,具有精确的频率分辨率、快速的频率转换时间以及可灵活产生多种信号等特点。

因此,dds已逐渐取代模拟方式。

dds由相位累加器、波形存储器和数模转换器等组成。

其原理:向dds写入频率控制字,经过相位累加器转换成瞬时相位,在外部参考时钟作用下,每个时钟周期相位累加器累加相位步进一次,然后对应到波形存储器中所存储的正弦函数查询表,不同的瞬时相位码输出不同的幅值编码,再将该幅值编码输出给数模转换器(d/a),把数字量转换为模拟量输出给低通滤波器,最后输出所需的信号。

3.2 ad9858简介与其他高速dds器件相比,ad9858内部集成有10位数模转换器,其频率分辨率为32位,最高输出频率可达400 mhz。

AD9850中文资料

VC C4

2

U2

VCC CLK GND

16MHz

VCC

36 81

U21

DDS_D0 DDS_D1

4 3

D0

R

DDS_D2 DDS_D3

2 1

D A D1

D2

DA

DDS_D4 28 DDS_D5 27 DDS_D6 26 DDS_D7 25

W_CLK 7

FQ_UP

8

D3

IOUT

D4

D5

dds 芯片复位

A,@R1;

写入 5 个频率字

@DPTR,A

R1;

R0,PROC_9850;

A,#00H

DPTR,#FQ_UP ;装载频率字并启动转换

@DPTR,A ;

J1,J4 为总线插槽,具体管脚定义如下表:

符号

定义

引脚

功能说明

D0~D7

数据总线

4~11 D0~D7 /A0~A7 总线分时复用,非扩展

方式下可作为位控

A0~A7

低 8 位地址线 12~19

CS0~CS7

输 入 输 出 地 址 23~30 由处理器板中的 CPLD 对数据存储地址空间

段选择信号

中的高位地址线译码产生,占据最高的

图 0341-6 模块器件分布图

U2 为有源晶振;

J2 为电源,从上往下依次为:VCC,GND;

U21 为 AD9850;

J6 为电源插座;

J5 为 CPLD 下载编程接口;从左向右依次为:VCC,GND,TCK,TDO,TDI,TMS;

J3 信号输出端。从上到下依次为: SIN_OUT,GND,BUS_CLK,GND;

adc0808中文资料[整理版]

![adc0808中文资料[整理版]](https://img.taocdn.com/s3/m/c09ee7f85ff7ba0d4a7302768e9951e79b896975.png)

11.2.4 典型的集成ADC芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。

仅美国AD公司的ADC产品就有几十个系列、近百种型号之多。

从性能上讲,它们有的精度高、速度快,有的则价格低廉。

从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。

选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC芯片允许输出线与微机系统的数据总线直接相连,并在转换结束后利用读数信号RD选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。

对脉冲启动转换的ADC芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

一般能和MPU配套使用的芯片,MPU的I/O写脉冲都能满足ADC芯片对启动脉冲的要求。

对电平启动转换的ADC芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。

为此,必须用D 触发器或可编程并行I/O 接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

AD9852中文资料

AD9852的引脚说明:D7—D0: Pin1—8,并行编程模式下的8位并行数据I/O口。

A0—A5: Pin14—19,并行编程模式下的6位并行地址口。

其中,Pin 17与串行通信的复位端复用,Pin18与串行数据输出口复用(3线模式),Pin19与串行数据I/O口复用((2线模式)。

DVDD: Pin9,10,23,24,25,73,74,79,80,数字电路电源端,相对于数字地3.3V供电,3.135V—3.465V可保证设计指标。

DGND: Pinll,12,26,27,28,72,75,76,77,78,数字地。

AVDD: Pin31,32,37,38,44,50,54,60,65,模拟电路电源端,相对于模拟地3.3V供电,3.135V—3.465V可保证设计指标。

电路设计时,应加强DVDD和AVDD 之间的去藕,以防噪声相互串扰。

AGND: Pin33,34,39,40,41,45,46,47,53,59,62,66,67,模拟地。

NC: Pin13,35,57,58,63,内部无连接的引脚,布线时可以悬空。

I/O UD: Pin20,频率更新端口。

要向AD9852寄存器内写数据,先是写到端口的缓冲器里,等工作模式所需的数据写完后,再在此引脚上加一持续至少8个系统时钟周期的高电平,使DDS芯片按照所设置的方式运行。

频率更新也可以设置成内部更新模式,这时DDS按照UDC寄存器设置的值定时自动更新频率,同时输出持续8个系统时钟周期高电平的同步信号。

WRB/SCLK: Pin21,并行模式下的读控制端,与串行模式时钟信号输入端复用。

RDB/CSB: Pin22,并行模式下的写控制端,与串行模式片选端复用。

FSK/BPSK/HOLD: Pin29,多功能复用引脚。

FSK工作模式下,低电平选择频率F1,高电平选F2; BPSK模式时,低电平选相位1,高电平选相位2 ; Chirp模式时,高电平使DDS输出保持当前频率。

基于AD9858的雷达信号波形产生器设计

基于AD9858的雷达信号波形产生器设计

张新安;张毅锋;游志刚

【期刊名称】《国外电子元器件》

【年(卷),期】2008(000)005

【摘要】针对直接数字频率合成器(DDS)AD9858的特点及工作模式,提出了一种通过计算机并口控制AD9858的雷达信号波形产生器,可模拟产生高性能多波形复杂雷达发射源信号,该雷达信号波形发生器输出信号频率、相位、幅度可调,结构简单.

【总页数】3页(P5-7)

【作者】张新安;张毅锋;游志刚

【作者单位】解放军电子工程学院,安徽,合肥,230037;解放军电子工程学院,安徽,合肥,230037;解放军电子工程学院,安徽,合肥,230037

【正文语种】中文

【中图分类】TN95

【相关文献】

1.基于AD9858宽带雷达信号源的设计及应用 [J], 师鹏宇;杨洪丰;王磊

2.通过计算机并口控制AD9858的雷达信号波形产生器设计 [J], 张晋华

3.基于AD9858的雷达信号源设计与实现 [J], 吕艳;戚继明;奚玮

4.基于DDS芯片AD9858的复杂雷达信号模拟器设计 [J], 高旺;姚龙海

5.基于AD9858的宽带雷达信号源设计与实现 [J], 段龙辉

因版权原因,仅展示原文概要,查看原文内容请购买。

基于AD9858的线性调频信号源设计

基于AD9858的线性调频信号源设计吴斌【摘要】AD9858是一款高性能DDS芯片,它集成了10位高速D/A转换器,能够输出频率高达450MHz的正弦波信号。

本文详细介绍了AD9858的工作流程及时序关系、寄存器的配置方法,以及基于AD9858的调频信号源硬件设计实现。

% The AD9858 is a high performance DDS chip with the integration of 10-bit D/A converter at high speed, from which the sine wave signal with the frequency of up to 450MHz is output. The paper introduces the work flow and time sequence relationship of the AD9858, as well as how to configure registers in the AD9858 and how to design and implement the hardware for the AD9858-based frequency-modulated signal source.【期刊名称】《现代导航》【年(卷),期】2013(000)003【总页数】4页(P231-234)【关键词】直接数字频率合成;调相;调频;倍频【作者】吴斌【作者单位】海军装备部驻西安地区军事代表局【正文语种】中文【中图分类】TN911.231 AD9858性能与功能描述直接数字合成器(DDS,Direct Digital Synthesis)以精准时钟为参考,利用数字化的方法直接产生相位可调、频率可调的正弦波信号。

DDS器件的推出,以其精确性、可靠性和多功能性极大地推动了雷达技术的发展。

目前,世界上许多芯片制造厂商都陆续推出了采用先进CMOS工艺生产的高集成度、多功能的高性能 DDS芯片,应用最广泛的是 AD公司的AD985X系列,尤其是AD9858。

ad9852cn

AD9852中文应用资料包括了:基于AD9852的调制信号发生器的设计等几篇应用文章,方便网友朋友学习使用AD9852。

DDS原理与AD9852的结构基本的DDS是在高速存储器中放入正弦函数-相位数据表格,经过查表操作,将读出的数据送到高速DAC产生正弦波。

常用的可编程DDS系统如图1所示。

DDS系统由频率控制字、相位累加器、正弦查询表、D/A转换器和低通滤波器组成。

参考时钟一般为高稳定度的晶体振荡器,其输出用于同步DDS各组成部分的工作。

对于计数容量为2的相位累加器和具有M个相位取样点的正弦波波形存储器,若频率控制字为K,输出信号频率为fo,参考时钟频率为fc,则DDS系统输出信号的频率为:AD9852是由ADI公司生产的高性能DDS芯片,主要由DDS核心、寄存器、DAC、数字乘法器、反辛格函数滤波器、比较器、I/O接口等电路组成。

其系统功能框图如图2所示。

信号的产生AM信号的产生设需要产生一个载波频率为f0,调制频率为f 的幅度调制信号,则给AD9852输入一个4 8位的频率控制字,产生一个频率为f0的固定幅度的载波。

AD9852可以通过数字乘法器控制输出信号的幅度,要产生一个调制频率为f 的振幅调制信号,只需产生一系列随着调制信号幅度变化的幅度控制字,则可直接产生数字式的调幅波。

AM信号产生原理如图3所示。

FM信号的产生根据(1)式,通过改变频率控制字K,可以迅速改变输出信号的频率。

因此,FM信号的产生和前面的AM信号产生相似,按照调制信号幅度的变化,实时改变频率控制字使输出的频率随调制信号的幅度变化。

特别地,AD9852通过改变工作模式,可以产生线性调频信号(Chirp),通过改变时间步进量(斜率计数器)和频率步进量( 频率字)来产生不同斜率,从而实现非线性扫频。

FM信号产生原理如图4所示。

二进制PSK信号的产生两点(二元或两相位)相移键控是在预先设置好的两个14位相移量中快速切换。

其控制信号为芯片的一个管脚“BPSK”,“BPSK”端的逻辑状态选择相移量,当为低时,选择相位1;为高时,选择相位2。

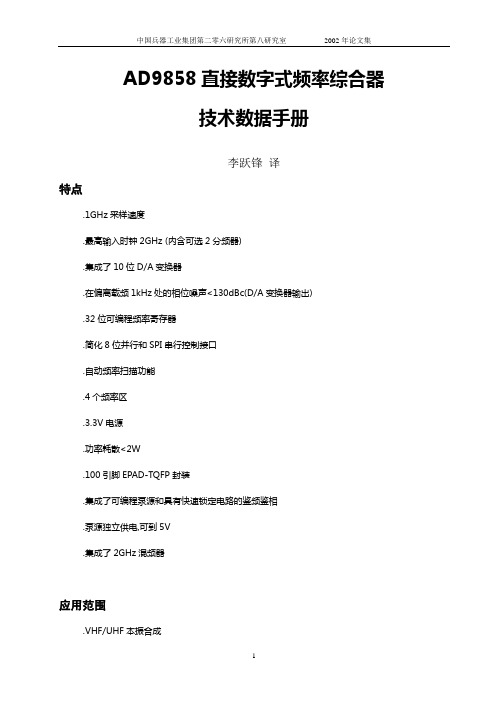

AD9858

AD9858直接数字式频率综合器技术数据手册李跃锋译特点.1GHz采样速度.最高输入时钟2GHz (内含可选2分频器).集成了10位D/A变换器.在偏离载频1kHz处的相位噪声<130dBc(D/A变换器输出).32位可编程频率寄存器.简化8位并行和SPI串行控制接口.自动频率扫描功能.4个频率区.3.3V电源.功率耗散<2W.100引脚EPAD-TQFP封装.集成了可编程泵源和具有快速锁定电路的鉴频鉴相.泵源独立供电,可到5V.集成了2GHz混频器应用范围.VHF/UHF本振合成.调谐器.仪器设备.多功能时钟合成.蜂窝基站跳频合成器.雷达.SONET/SDH时钟合成简要介绍AD9858直接数字式频率综合器(DDS)内部提供了一个每秒1G次采样率的10位数模变换器。

AD9858采用先进的DDS技术,又结合内部的高速、高性能D/A变换器,构成了一种频率高、数字可编程的完善的合成器,能够产生频率变化灵活、最高频率大于400MHz的模拟正弦波信号。

AD9858具有跳频速度快、频率分辨率高(32位频率调谐字)的特点。

频率调谐字和功能控制字通过并行(8位)或串行接口调入。

AD9858含有一个集成泵源(CP)和一个鉴频/鉴相器,用于需要把高速DDS和锁相环结合起来的场合;还提供了一个片内模拟混频器, 用于需要把高速DDS、锁相环和混频器结合起来的场合,例如频率平移锁相环、调谐器等。

AD9858的时钟输入端还提供了一个除2分频器,该分频器允许输入时钟的最高频率达2GHz。

AD9858的额定工作温度范围是-40~+85℃,属于扩展工业级产品。

引脚功能排列图功能方框图图1 AD9858的功能方框图工作原理一概述AD9858直接数字式频率综合器(DDS)是一种可塑性很强的器件,应用范围很广。

该器件由一个32位相位累加器的NCO、一个14位移相、一个高效的DDS核心、一个每秒1G次采样率的10位数模变换器组成。

基于AD9850多波形发生器的设计

为了给后端电路提供一个理想信号,一般用信号发生器所产生的的信号来替代前端电路的实际信号。为了可以方便的在各种不同条件下所需的不同特性信号,就需要一个特征参数可以被认为设定的信号源。这样的信号源对于产品的研发和日常学校的电路实验很有成效。我们可以通过测量出的信号进行比对,以此来确定电路的特性和功能是否达到了所需的标准和要求

DDS技术的波形发生器的特点有以下几个:输出频率稳定、准确、波形输出质量好、输出频率范围可观。以上几个特点都是波形发生器值得我们去研究的一个重要方向。DDS作为一种较为先进的频率合成技术,它相较其他波形发生器比较容易通过程序来控制,且其相位连续,输出频率稳定度高、分频率高。

1.3 DDS技术的发展历程和研究现状

自20世纪80年代以来各国都在研究DDS产品,并广泛的应用于各个领域。DDS技术具有集成度高、芯片体积小、稳定度好、分辨率高等优点,同时有着两个缺点:一个是带宽较小,二个是杂散大。杂散大的原因是因为D/A转换过程中的量化误差和非线性误差造成的以该技术为核心的生产的波形发生器不仅可以产生传统波形发生器的能产生的正弦波、方波、三角波、锯齿波等,还可以产生可变频的载频信号、部分调制信号。同时还可产生任意编辑的波形。

在日常的生产实践和科技领域中信号发生器具有着较为广泛应用。在通信中,需要高频发射,其中的射频波指的就是载波,将音频、视频信号或脉冲信号运载发送出去,需要能产生高频的振荡器。在不同的领域中例如工业的高频感应加热、熔炼、淬火,生物医学中的核磁共振成像等都需要功率不同的,频率不同的振荡器。对于计量和校准领域来说高精度的信号发生器也可以作为标准的信号源,把参考源做为标准将需要校准的仪器调校。这证明了,信号发生器的应用领域十分的广泛。

系统结构的简图如下所示,可从中看出波形发生器的大体运作流程。

最新-基于AD9858的线性调频源设计 精品

基于AD9858的线性调频源设计摘要简要介绍了线性调频信号产生技术的现状,给出了高性能芯片9858的主要特点和配置方法,同时以图形方式给出了基于9858芯片的倍频器的硬件结构及互连方法,详细描述了输出线性调频信号的控制流程。

关键词线性调频源;直接数字频率合成;98581引言随着雷达技术的发展,线性调频信号已经广泛应用于高分辨率雷达领域。

过去获得线性调频信号主要借助模拟方法,其中包括VCO方法和声表面波方法。

这两种脉冲电压信号的产生方法因其一些固有的缺陷如对环境温度比较敏感、信号波形比较单一、信号产生的重复性差、线性度及信号间的相关性不理想等而制约了雷达整机性能的提高。

目前,VCO方法和声表面波方法已渐渐被数字方法所取代。

直接数字频率合成方法具有传统方法所不具备的许多突出优点,如频率分辨率和切换速度高,频率切换时相位可保持连续,超宽的频率范围,能实现各种调制波和任意波形的产生以及易于实现全数字化设计等。

然而,其全数字化的工作原理也给它带来了两个缺点,一是输出杂散较大,二是输出带宽将受到限制。

但是,这一缺陷随着新工艺和新算法的出现正在逐渐得到改善。

AD9858是AD公司于2003年推出的一款高性能DDS芯片,其工作频率高达1GHz,杂散性能指标更高于以前的产品。

AD9858凭借优良的性能可广泛应用于甚高频/超高频本振合成器、雷达、蜂窝基站跳频合成器等许多领域。

2AD9858的主要特点AD9858的工作频率最高可达1GHz,由于该芯片在时钟输入端提供有二分频器,因而其外部时钟最高可达2GHz。

AD9858内部集成有10位数模转换器,其频率分辨率即频率累加器位数为32位,可输出高达400MHz的信号。

而其内部集成的可编程快锁充电泵chargepump和鉴频器phasefrequencydetector使其非常适合于高速DDS和锁相。

ad9850中文资料

海纳电子资讯网:www.fpga-arm.com目录摘要 —————————————————————————2 创新之处 ———————————————————————2 关键词 ————————————————————————2 引言 —————————————————————————2 系统工作原理 —————————————————————3 直接数字频率合成 ———————————————————4 DDS 基本原理及性能特点 —————————————————5 采用 DDS 的 AD9851 ———————————————————6 AD9851 的原理 —————————————————————7 AD9851 在信号源中的应用 ————————————————8 AD9851 在本系统的应用电路 ———————————————9 低通滤波器(LPF) ——————————————————10 锁相环频率合成 ———————————————————11 锁相环频率合成 MC145151 在本电路中的应用 ————————12 压控振荡器(VCO) ———————————————————12 缓冲放大器 ——————————————————————13 单片机控制的整体电路 —————————————————14 功率放大 ———————————————————————15 本系统的软件设计 ———————————————————15 总调试 ————————————————————————25 结束语 ————————————————————————25 DDS 短波信号发生器技术指标 ——————————————26 所采用的仪器设备 ———————————————————26 所用软件 ———————————————————————26 参考文献 ———————————————————————26 参考网站 ———————————————————————27www.fpga-ar m1.海纳电子资讯网:www.fpga-arm.comDDS 短波信号发生器摘要: 本文主要介绍的是采用直接数字频率合成的短波信号发生器, 它 主要以微电脑控制部分、直接数字频率合成(DDS)部分、数字锁相 环频率合成部分、背光液晶显示部分、功率放大部分等组成。

AD9850介绍AD9850中文资料

精心整理第13章DDS 芯片AD9850/AD9851的设计13.1硬件设计信号源作为现代电子产品设计和生产中的重要工具,必须满足高精度、高速度、高分辨率等要求。

本章基于DDS(DirectDigitalSynthesis,直接数字频率合成)技术,采用AD9850DDS 芯片,采用F169单片机作为控制芯片,实现一种了简易信号发生器的设计,该信号发生器具有输出频率范围宽,可以输出正弦和方波两种波形,与键盘结合易于实现全数字化的设计。

(DDS )80℃,采用28图13-3系统的10位后输入到DAC ,DAC 再输出两个互补的电流。

DAC 满量程输出电流通过一个外接电阻set R 调节,调节关系为set I =32(1.148V/RSET),set R 的典型值是3.9K Ω。

将DAC 的输出经低通滤波后接到AD9850内部的高速比较器上即可直接输出一个抖动很小的方波。

其系统功能如图3-3所示。

AD9850在接上精密时钟源和写入频率相位控制字之后就可产生一个频率和相位都可编程控制的模拟正弦波输出,此正弦波可直接用作频率信号源或经内部的高速比较器转换为方波输出[23]。

在125MHz 的时钟下,32位的频率控制字可使AD9850的输出频率分辨率达0.0291Hz ;并具有5位相位控制位,而且允许相位按增量180,45,90,22.5,11.25或这些值的组合进行调整。

精心整理图13-3AD9850的内部结构13.1.2AD9850的控制字与控制时序AD9850有40位控制字,32位用于频率控制,5位用于相位控制。

1位用于电源休眠(Powerdown )控制,2位用于选择工作方式。

这40位控制字可通过并行方式或串行方式输入到AD9850,在并行装入方式中,通过8位总线D0…D7将可数据输入到寄存器,在重复5次之后再在FQ_UD 上升沿把40位数据从输入寄存器装入到频率/相位数据寄存器(更新DDS 输出频率和相位),同时把地址指针复位到第一个输入寄存器。

最详细的AD9851中文资料

特征180 MHz时钟速率参考时钟具有6倍倍乘器。

芯片具有高性能10位DAC和高速滞后比较器无杂散动态范围SFDR为43分贝@ 70 MHz的模拟输出。

32位频率控制字简化控制接口:并行或串行异步加载格式5位相位调制和补偿能力比较器纹波抖动<80 ps p-p @ 20 MHz+2.7 V至+5.25 V单电源工作低功耗: 555毫瓦@ 180兆赫省电功能, 4毫瓦@ 2.7 V超小28引线SSOP封装频带宽正常输出工作频率范围为 0~72MHz ;应用频率/相敏正弦波合成为进行数字通信设定时钟恢复和锁定电路通信数字控制的ADC编码发生器敏捷L.O应用在正交振荡器连续波,调幅,调频, FSK信号,发射机的MSK模式。

概述该AD9851是一种高度集成的设备,采用先进的DDS技术,再加上内部高速度、高性能D / A转换器,和比较器,使一个数字可编程频率合成器和时钟发生器功能化。

当参照准确的时钟源,AD9851可以产生一个稳定的频率和相位且可数字化编程的模拟正弦波输出。

此正弦波可直接用作时钟源,在其内部转化为方波成为灵活的时钟发生器。

AD9851采用的最新的高速DDS内核可接受32位的频率控制字,180 MHz系统时钟,分辨率为0.04赫兹。

该AD9851包含一个特有的6 ×REFCLK倍乘器电路,因此无需高速外部晶振。

6 × REFCLK倍乘器使其有最小的无杂散动态范围SFDR和相位噪声特性。

AD9851提供了5位可编程相位调制,使移相输出的增量为11.25°。

功能方框图该AD9851包含一个内部的高速比较器。

可以输出一个低抖动输出脉冲。

可进行频率调整,控制能将相位调谐字异步加载到AD9851并通过并行或串行方式载入。

并行负载格式由五个迭代的8位控制字(字节)。

第一个8位字节控制输出相位, 6 × REFCLK倍乘器,电源关闭启用和装载模式;其余字节组成32位频率控制字。

AD9858 直接数字频率合成器的特点与应用简述

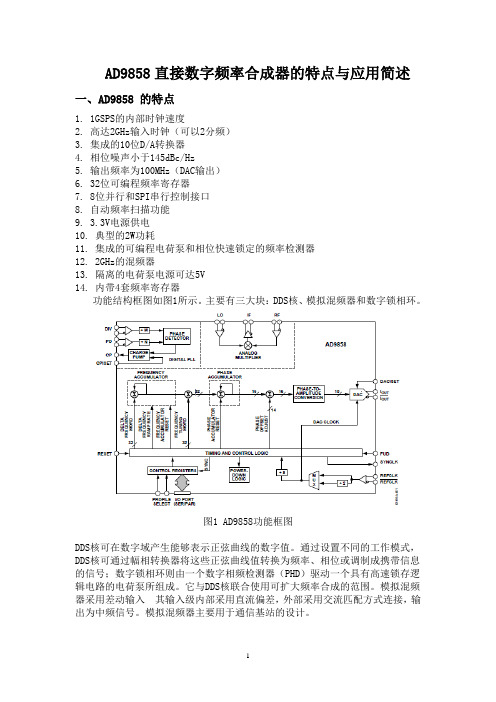

AD9858直接数字频率合成器的特点与应用简述一、AD9858 的特点1. 1GSPS的内部时钟速度2. 高达2GHz输入时钟(可以2分频)3. 集成的10位D/A转换器4. 相位噪声小于145dBc/Hz5. 输出频率为100MHz(DAC输出)6. 32位可编程频率寄存器7. 8位并行和SPI串行控制接口8. 自动频率扫描功能9. 3.3V电源供电10. 典型的2W功耗11. 集成的可编程电荷泵和相位快速锁定的频率检测器12. 2GHz的混频器13. 隔离的电荷泵电源可达5V14. 内带4套频率寄存器功能结构框图如图1所示。

主要有三大块:DDS核、模拟混频器和数字锁相环。

图1 AD9858功能框图DDS核可在数字域产生能够表示正弦曲线的数字值。

通过设置不同的工作模式,DDS核可通过幅相转换器将这些正弦曲线值转换为频率、相位或调制成携带信息的信号;数字锁相环则由一个数字相频检测器(PHD)驱动一个具有高速锁存逻辑电路的电荷泵所组成。

它与DDS核联合使用可扩大频率合成的范围。

模拟混频器采用差动输入 其输入级内部采用直流偏差,外部采用交流匹配方式连接,输出为中频信号。

模拟混频器主要用于通信基站的设计。

二、应用1. VHF/UHF LO频率合成2. 调谐器3. 仪器仪表4. 捷变时钟频率合成5. 蜂窝基站调频合成6. 雷达7. Sonet/SDH时钟频率合成AD9858在雷达信号源中的应用图2所示是一般雷达系统的工作原理示意图。

图中,雷达发射机产生电磁波后,会经收发天线辐射入大气层。

电磁波在大气中以光速传播,若目标在天线的波束内,则它要截取一定的电磁能并将其向各方向散射。

雷达接收到这些散射电磁波后会以此来判断目标的距离和速度等信息。

图2 雷达系统工作原理由AD9858产生的雷达信号源的原理框图如图3所示。

图3 雷达信源原理框图该系统在工作时,控制计算机发出控制信号以决定系统产生波形的种类及参数,并将频率码打入高速DSP芯片内部。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

特点1 GSPS的内部时钟速度高达2 GHz的输入时钟(可选除以2)集成的10位D/ A转换器<145 dBc / Hz的相位噪声@ 1 kHz偏移输出频率为100兆赫(DAC输出)32位可编程频率寄存器简化8位并行和SPI®串行控制接口自动扫频功能4频剖面3.3 V电源供电功耗2 W典型集成的可编程电荷泵和相快速锁定电路与频率探测器隔离电荷泵提供至5 V综合2 GHz的混频器应用甚高频/超高频劳合成调谐器仪器仪表敏捷时钟合成蜂窝基站跳频合成器雷达SONET / SDH时钟合成一般说明AD9858的是特色经营,以1GSPS的10位DAC的直接数字合成器(DDS)。

AD9858的使用先进的DDS技术,加上内部的高速,高性能D / A转换,形成数字可编程的,完整的高频率合成器能够产生高达400兆赫的频率灵活的模拟输出正弦波。

AD9858的设计提供快速跳频和微调分辨率(32位频率控制字)。

被装入了AD9858的频率调整和控制字通过并行(8位)或串行加载格式。

AD9858的包含一个集成的电荷泵(CP)的合成需要一个高速DDS锁相环(PLL)的功能相结合的应用和相位频率检测器(PFD)。

模拟调音台,还提供片上的应用需要一个DDS,PLL和混频器的组合,如频率转换回路,调谐器,等。

在AD9858的时钟输入还设有一个分2,允许外部时钟,以高达2 GHz的高。

AD9858的指定工作在扩展工业温度范围-40°C至85°C目录功能................................................. .. (1)应用................................................. . (1)一般说明................................................ (1)功能块图............................................... .. (1)AD9858的,电气规格.............................................. .. 3绝对最高评分............................................... . (6)防静电注意事项................................................ . (6)引脚配置................................................ .. (7)引脚功能描述............................................... (8)典型性能特性 (10)论操作............................................... .. (15)概述................................................. (15)构件块................................................ (15)操作模式............................................... .. (17)同步................................................. . (19)在AD9858的编程............................................... (21)AD9858的应用建议 (29)评估委员会................................................ . (30)外形尺寸................................................ .. (31)警告................................................. .. (31)订购指南................................................ .. (31)修订历史11/03-Data表改变从启。

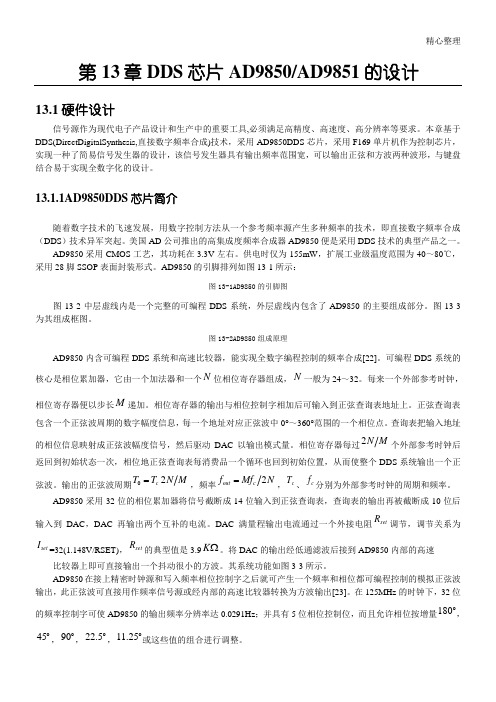

0到1 REV的。

一规格变化............................................... (5)移动静电谨慎.............................................. .. (6)移动引脚配置到.............................................. .. (7)移动引脚功能描述到............................................. .. 8到方程的变化............................................... . (19)三角洲频率爬升字的变化(DFRRW) (27)AD9858—ELECTRICAL SPECIFICA TIONSTable 1. Unless otherwise noted, VDD = 3.3 V ±5%, CPVDD = 5 V ±5%, RSET = 2 kΩ, CPISET = 2.4 kΩ, Reference Clock Frequency = 1 GHz.ParameterTempTest LevelMinTypMaxUnitREF CLOCK INPUT CHARACTERISTICS1, 2Reference Clock Frequency Range (Divider Off) Full VI 10 1000 MHz Reference Clock Frequency Range (Divider On) Full VI 20 2000 MHzDuty Cycle @ 1 GHz 25°C V 42 50 58 %Input Capacitance 25°C V 3 pFInput Impedance 25°C IV 1500 ΩInput Sensitivity Full VI –20 +5 dBmDAC OUTPUT CHARACTERISTICSResolution Full 10 BitsFull-Scale Output Current Full 5 20 40 mAGain Error Full VI –10 +10 % FSOutput Offset Full VI 15 μA Differential Nonlinearity Full VI 0.5 1 LSBIntegral Nonlinearity Full VI 1 1.5 LSBOutput Impedance Full VI 100 kΩV oltage Compliance Range Full VI A VDD – 1.5 A VDD + 0.5 V Wideband SFDR (DC to Nyquist)40 MHz FOUT Full V 60 dBc100 MHz FOUT Full V 54 dBc180 MHz FOUT Full V 53 dBc360 MHz FOUT Full V 50 dBc180 MHz FOUT (700 MHz REFCLK) Full IV 52 dBcNarrow-Band SFDR3340 MHz FOUT (±15 MHz) Full V82 dBc40 MHz FOUT (±1 MHz) Full V87 dBc40 MHz FOUT (±50 kHz) Full V 88 dBc100 MHz FOUT (±15 MHz) Full V81 dBc100 MHz FOUT (±1 MHz) Full V82 dBc100 MHz FOUT (±50 kHz) Full V 86 dBc180 MHz FOUT (±15 MHz) Full V74 dBc180 MHz FOUT (±1 MHz) Full V84 dBc180 MHz FOUT (±50 kHz) Full V 85 dBc360 MHz FOUT (±15 MHz) Full V75 dBc360 MHz FOUT (±1 MHz) Full V85 dBc360 MHz FOUT (±50 kHz) Full V 86 dBc180 MHz FOUT (±15 MHz) (700 MHz REFCLK) Full V 65 dBc180 MHz FOUT (±1 MHz) (700 MHz REFCLK) Full V 80 dBc180 MHz FOUT (±50 kHz) (700 MHz REFCLK) Full V 84 dBc OUTPUT PHASE NOISE CHARACTERISTICS (@ 103 MHz IOUT)@ 1 kHz Offset Full V –147 dBc/Hz@ 10 kHz Offset Full V –150 dBc/Hz@ 100 kHz Offset Full V –152 dBc/Hz OUTPUT PHASE NOISE CHARACTERISTICS (@ 403 MHz IOUT)@ 1 kHz Offset Full V –133 dBc/Hz@ 10 kHz Offset Full V –137 dBc/Hz@ 100 kHz Offset Full V –140 dBc/Hz OUTPUT PHASE NOISE CHARACTERISTICS (@ 100 MHz IOUT with 700 MHz REFCLK) @ 100 Hz Offset Full V –125 dBc/Hz@ 1 kHz Offset Full V –140 dBc/Hz@ 10 kHz Offset Full V –148 dBc/Hz@ 100 kHz Offset Full V –150 dBc/Hz@ 1 MHz Offset Full V–150 dBc/Hz@ 10 MHz Offset Full V–150 dBc/Hz PHASE DETECTOR AND CHARGE PUMPPhase Detector Frequency Full VI 150 MHzPhase Detector Frequency (Divide-by-4 Enabled)4 Full VI 400 MHz Charge Pump Sink and Source Current5 Full VI 4 mAFast Lock Current (Acquisition Only) Full VI 7 mAOpen-Loop Current (Acquisition Only) Full VI 30 mASink and Source Current Absolute Accuracy6 Full V 2.5 %Sink and Source Current Matching6 Full V 1 %Input Sensitivity PDIN and D IVIN (50 Ω)7Full IV –15 0 dBmInput Impedence PDIN and DIVIN (Single-Ended) Full V 1 kΩPhase Noise @ 100 MHz Input Frequency@ 10 kHz Offset Full V 110 dBc/Hz@ 100 kHz Offset Full V 140 dBc/Hz@ 1 MHz Offset Full V148 dBc/Hz Charge Pump Output Range8 Full V CPVDD V MIXERIFOUT9 Full V 400 MHz FRF Full VI 2 GHz FLO Full VI 2 GHz Conversion Gain Full VI 0.0 3.5 dBLO Level Full VI –10 +5 dBm RF Level Full VI –20 dBm AD9858的,电动的规格表1。