stm32f10x库函数的封装过程图解

STM32固件库文件结构及作用详解

STM32标准外设固件库文件结构及用途文件夹树图及文件作用详述stm32f10x_stdperiph_lib_V3.5.0--------------ST 公司针对STM32提供的函数接口├─Release_Notes.html -------------------------官方网页资源├─stm32f10x_stdperiph_lib_um.chm-------------库的帮助文档 ├─stm32f10x_stdperiph_lib_um.chw ├─htmresc -----------------------------------CMSIS 内核和ST 公司Logo │ ├─CMSIS_Logo_Final.jpg │ └─logo.bmp ├─Libraries ----------------------------------固件库 │ ├─CMSIS -Cortex Microcontroller Software Interface Standard(Cortex 内核软件接口标准) │ │ ├─CMSIS debug support.htm ------------官方网页资源 │ │ ├─CMSIS_changes.htm ------------------官方网页资源 │ │ ├─License.doc │ │ ├─CM3 固件库文件夹树形图│ │ │ ├─CoreSupport----为采用Cortex-M3核设计SOC的芯片商设计的芯片外设提供一个进入M3内核的接口│ │ │ │ ├─core_cm3.c│ │ │ │ └─core_cm3.h│ │ │ └─DeviceSupport│ │ │ └─ST│ │ │ └─STM32F10x│ │ │ ├─Release_Notes.html│ │ │ ├─stm32f10x.h --------------------定义寄存器的地址及使用的结构体封装│ │ │ ├─system_stm32f10x.c--------------设备外设访问层,主要配置时钟频率│ │ │ ├─system_stm32f10x.h--------------配置时钟频率相应的头文件│ │ │ └─startup--------由汇编编写的系统启动文件,不同的文件对应不同的芯片型号│ │ │ ├─arm-------ARM编译器启动文件│ │ │ │ ├─startup_stm32f10x_cl.s------cl:互联型产品,stm32f105/107系列│ │ │ │ ├─startup_stm32f10x_hd.s------hd:高密度产品,FLASH大于128│ │ │ │ ├─startup_stm32f10x_hd_vl.s---vl:超值型产品,stm32f100系列│ │ │ │ ├─startup_stm32f10x_ld.s------ld:低密度产品,FLASH小于64K│ │ │ │ ├─startup_stm32f10x_ld_vl.s│ │ │ │ ├─startup_stm32f10x_md.s------md:中等密度产品,FLASH=64 or 128 │ │ │ │ ├─startup_stm32f10x_md_vl.s│ │ │ │ └─startup_stm32f10x_xl.s----xl:超高密度(容量)产品,stm32f101/103系列│ │ │ ├─gcc_ride7………………GCC编译器启动文件│ │ │ ├─iar………………………………IAR编译器启动文件│ │ │ └─TrueSTUDIO……………TrueSTUDIO编译器启动文件│ │ └─Documentation│ │ └─CMSIS_Core.htm --------------CMSIS_Core网页资源│ └─STM32F10x_StdPeriph_Driver-----------CMSIS的设备外设函数,由stm32f10x_ppp.c或 stm32f10x_ppp.h ││文件组成,PPP表示外设名称。

浅谈STM32芯片行丝印含义,固件库命名规则及三大结构发展图示

浅谈 STM32 芯片行丝印含义,固件库命名规则及三

大结构发展图示

STM32 芯片上的 5 行丝印 1、ARM 代表 ARM 内核,ARM 后面跟着的是 X,代表芯片版本 内核是不变的 只是 ST 的版本 X 是最终版本,就是以后这个型号就不会再升级了,有数字的代理以后还 可以升级 2/3、第二行和第三行是型号

中,只允许有一条下划线,用来区分外围模块缩写和剩下的函数名。 5、使用 X_InitTypeDef 中指定的参数初始化 X 外围模块的函数,被命名 为 X_Init. 6、复位 X 外围模块的寄存器为默认值的函数,命名为 X_DeInit。 7、将 X_InitTypeDef 结构体每个成员设置为复位值的函数,命名为 x_StructInit. 8、用来使能或者禁止指定的 X 外围的函数,命名为 X_Cmd。 9、用来使能或禁止指定的 X 外围模块的某个中断资源的函数,命名为 X_ITConfig。 10、用来使能或禁止指定的 X 外围模块的 DMA 接口的函数,命名为 X_DMAConfig.

11、用来设置某个外围模块的函数,总是以字符串 Config 结尾。 12、用来检验指定 X 的标志是否被职位或清零的函数命名为 X_GetFlagStatus. 13、用来清除某个 X 的标志函数,命名为 X_ClearFlag 14、用来检验指定 X 的中断是否发生的函数,命名 X_GeTITstatus 15、用来清除某个 X 中断挂起位的函数,命名为 X_ClearITPendingBit stm32 三大结构发展图示

4、原厂出厂编号 5、MYS 是马来西亚封装产地,641 是代表 2016 年 41 周生产的 CHN 是国内封装产地 STM;rsquo;的形式表示。 2、在单一文件中使用的常量在该文件中定义。在多个文件中使用的常量 定义在头文件中。所有常量都以大写字母表示。 3、寄存器当做常量看待,同样以大写字母表示,多数情况下,在 STM3210X 参考手册中使用相同的缩写。 4、外围模块的功能函数的名字,需要有相应的外围模块缩写加下划线这 样的前缀,每个单词的首字符要大写。例如 SPI_SendData,在一个函数名

从零开始学习STM32(2)——STM32的芯片封装来自三千萝卜众

从零开始学习STM32(2)——STM32的芯片封装来自三千萝卜众STM32采用了三种封装分别是LQFP(代码为T)、BGA(代码为H)和QFN(代码为U)至于引脚数量,T代表36、C代表48、R代表64、V代表100、Z代表144比如我用的STM32F103VBT6,用的是LQFP封装,引脚数为100,这要是自己焊该怎么办啊这一刻,我愁了LQFP(好多金属脚,大型集成电路比较常见)LQFP也就是薄型QFP(Low-profile Quad Flat Package)指封装本体厚度为1.4mm的QFP,是日本电子机械工业会根据制定的新QFP外形规格所用的名称。

下面介绍下QFP封装:这种技术的中文含义叫方型扁平式封装技术(Plastic Quad Flat Package),该技术实现的CPU芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。

该技术封装CPU时操作方便,可靠性高;而且其封装外形尺寸较小,寄生参数减小,适合高频应用;该技术主要适合用SMT 表面安装技术在PCB上安装布线。

BGA(底部很多金属点,电脑cpu貌似都是这种)BGA封装(Ball Grid Array Package)的I/O端子以圆形或柱状焊点按阵列形式分布在封装下面,BGA技术的优点是I/O引脚数虽然增加了,但引脚间距并没有减小反而增加了,从而提高了组装成品率;虽然它的功耗增加,但BGA能用可控塌陷芯片法焊接,从而可以改善它的电热性能;厚度和重量都较以前的封装技术有所减少;寄生参数减小,信号传输延迟小,使用频率大大提高;组装可用共面焊接,可靠性高。

BGA封装技术可详分为五大类:1.PBGA(Plasric BGA)基板:一般为2-4层有机材料构成的多层板。

Intel系列CPU中,Pentium II、III、IV处理器均采用这种封装形式。

2.CBGA(CeramicBGA)基板:即陶瓷基板,芯片与基板间的电气连接通常采用倒装芯片(FlipChip,简称FC)的安装方式。

STM32F10x_Flash库函数介绍

/* Enable or disable the Prefetch Buffer */

FLASH->ACR &= ACR_PRFTBE_Mask;// Mask = 0xFFFFFFEF FLASH->ACR |= FLASH_PrefetchBuffer; }

No

函数名

描述

1 FLASH_SetLatency

设置代码延时值

2 FLASH_HalfCycleAccessCmd

使能或者失能FLASH半周期访问

3 FLASH_PrefetchBufferCmd

使能或者失能预取指缓存

4 FLASH_Unlock

解锁FLASH编写擦除控制器

5 FLASH_Lock

9.2.3 函数FLASH_PrefetchBufferCmd

Table 149. 函数FLASH_PrefetchBufferCmd

函数名

FLASH_PrefetchBufferCmd

函数原形 void FLASH_PrefetchBufferCmd(u32

FLASH_PrefetchBuffer)

功能描述

使能或者失能FLASH半周期访问

输入参数

FLASH_HalfCycleAccess:FLASH_HalfCycle访问模式

输出参数

无

返回值

无

先决条件

无

被调用函数 无

FLASH_HalfCycleAccess :用来选择FLASH半周期访问的模式。

STM32F10X的USB固件库说明

6)、usb_endp.c,本文件包含端点收、发送的处理函数,由用户根据不同的USB设备进行不同的定义。

USB的应用软件在这三层上,在不同的USB应用中,用户可能需要对USB固件库的上层部分文件配置进行修改(主要为usb_prop.c何usb_endp.c文件)。而中间层何底层封装的非常好,对

3)、usb_sil.c,本文件包含精简接口的初始化或向端点读写的操作函数。

上层

1)、usb_pwr.c,该文件中包含处理上电、掉电、挂起和恢复事件的函数。

2)、usb_istr.c,该文件中只有一个函数,即USB中断的USB_Istr函数,该函数对各类引起USB中断的事件做轮询处理。

3)、usb_desc.c,该文件包含一些与USB相关的设备描述符、配置描述符等,以数组形式存储,在USB主机请求的时候这些信息将发送给主机。

3)、usb_mem.c,本文件主要负责进行数据传输处理。它主要负责数据在用户区域(内存)或USB数据包缓冲c,本文件主要负责USB协议管理,如USB标准请求、各种端点0的控制信息处理。

2)、usb_init.c,本文件主要包含了USB初始化的函数。

这些文件用户是不需要进行改动的。

最底层

1)、usb_int.c,本文件包含两个中断服务函数CTR_LP()和CTR_HP(),在接收发送中断时使用这两个函数进行处理,这两个函数又调用各个USB端点处理函数,端点处理函数由用户自定义。

2)、usb_regs.c,本文件时硬件抽象层。它含有各种用于读取或设置USB寄存器的函数,相当于对寄存器操作方法的封装。

第6章 STM32F10x最小系统

精选课件ppt

Cortex-M3有32根 地址线,所以它 的寻址空间大小 为2^32 bit=4GB

程序存储器、数 据存储器、外设 寄存器、输入输 出端口被组织在 00至0x5FFF

FFFF(512MB )的

地址分配给片上

外设。

17

外设存储器映像 STM32F103外设寄存器组起始地址

精选课件ppt

2

6.1 STM32系列微控制器简介

STM32系列是基于ARM Cortex-M核的32位闪存微 控制器,集成度高、性能高、实时性、数字信号处理、 低功耗、低电压操作的易开发的芯片,适合不同用户的 需求。

精选课件ppt

3

例:STM32F10X系列

片上存储器容 量、集成外设 、功能模块、 封装形式等有 所区别。

精选课件ppt

4

S T M 3 2 F 1 0 x 系

列

产

品

编 号

精选课件ppt

5

精选课件ppt

6

ARM Lite Hi-Speed Bus Matrix / Arbiter (max 72MHz)

Flash I/F

CORTEXM3 CPU

72 MHz

32kB-512kB

STM32F10Fl3ash系Memo列ry 芯片

Power Supply Reg 1.8V

POR/PDR/PVD

JTAG/SW Debug Nested vect IT Ctrl

1x Systic Timer

6kB-64kB SRAM

20B Backup Regs External Memory

Interface**

XTAL oscillators 32KHz + 4~16MHz Int. RC oscillators

STM32F1与STM32F2之间的兼容性

QFP64 STM32F20x F10x

5 6 31 47

F20x

5 6 31 47

3

PH0 - OSC_IN PH1 - OSC_OUT VCAP1 VCAP2

LQFP100封装兼容板

对于STM32F1芯片,零欧 姆电阻连到VSS 对于STM32F2芯片,零欧 姆电阻连到VDD 直接接地即可 对于STM32F1芯片,这里放置零欧姆电 阻或者焊接桥接通; 对于STM32F2芯片,这里直接断开即可

2

12 31 31 47 47 63 63

20 49 73 74 99

LQFP64封装兼容板

对于STM32F1芯片,这里放置零欧姆电阻或 者焊接桥接通 对于STM32F2芯片,这里直接断开即可

引脚名称 STM32F10x

PD0 - OSC_IN PD1 - OSC_OUT VSS_1 VSS_2

STM32F10x系列

工作电压 2.0V ~ 3.6V

STM32F2xx系列

1.8V(1.65V) ~ 3.6V

CPU最高工作频率

片上SRAM容量 片上闪存容量 外部存储器接口(FSMC) 备份SRAM

72MHz

高达96K字节 高达1M字节 100引脚及以上封装有 无

120MHz

高达128K字节 高达1M字节 100引脚及以上封装有 有4K字节

引脚名称 STM32F10x

PD0 - OSC_IN

PD1 - OSC_OUT VSSA VSS_1 VSS_3

QFP100 STM32F20x F10x

12

13 19 49 99

F20x

12

13 19 49 99

4

PH0 - OSC_IN

stm32f10x参考手册

STM32F10x参考手册第一版STM32F10x参考手册1文档中的约定 (1)1.1寄存器描述中使用的缩写列表 (1)2存储器和总线构架 (2)2.1系统构架 (2)2.2存储器组织 (3)2.3存储器映像 (4)2.3.1外设存储器映像 (5)2.3.2嵌入式SRAM (6)2.3.3位段 (6)2.3.4嵌入式闪存 (6)2.4启动配置 (8)3电源控制(PWR) (9)3.1电源 (9)3.1.1独立的A/D转换器供电和参考电压 (9)3.1.2电池备份 (9)3.1.3电压调节器 (10)3.2电源管理器 (10)3.2.1上电复位(POR)和掉电复位(PDR) (10)3.2.2可编程电压监测器(PVD) (10)3.3低功耗模式 (11)3.3.1降低系统时钟 (12)3.3.2外部时钟的控制 (12)3.3.3睡眠模式 (12)3.3.4停止模式 (13)3.3.5待机模式 (14)3.3.6低功耗模式下的自动唤醒(AWU) (15)3.4电源控制寄存器 (16)3.4.1电源控制寄存器(PWR_CR) (16)3.4.2电源控制/状态寄存器 (17)3.5PWR寄存器映像 (18)4复位和时钟控制 (19)4.1复位 (19)4.1.1系统复位 (19)4.1.2电源复位 (19)4.2时钟 (20)4.2.1HSE时钟 (22)4.2.2HSI时钟 (22)4.2.3PLL (23)4.2.4LSE时钟 (23)4.2.5LSI时钟 (23)4.2.6系统时钟(SYSCLK)选择 (24)4.2.7时钟安全系统(CSS) (24)4.2.8RTC时钟 (24)4.2.9看门狗时钟 (24)4.2.10时钟输出 (25)4.3RCC寄存器描述 (26)4.3.1时钟控制寄存器(RCC_CR) (26)4.3.2时钟配置寄存器(RCC_CFGR) (27)4.3.3时钟中断寄存器 (RCC_CIR) (29)4.3.4APB2外设复位寄存器 (RCC_APB2RSTR) (32)4.3.5APB1外设复位寄存器 (RCC_APB1RSTR) (33)4.3.6AHB外设时钟使能寄存器 (RCC_AHBENR) (35)4.3.7APB2外设时钟使能寄存器(RCC_APB2ENR) (36)4.3.8APB1外设时钟使能寄存器(RCC_APB1ENR) (37)4.3.9备份域控制寄存器 (RCC_BDCR) (39)4.3.10控制/状态寄存器 (RCC_CSR) (40)4.4RCC寄存器映像 (43)5通用和复用功能I/O(GPIO和AFIO) (44)5.1GPIO功能描述 (44)5.1.1通用I/O(GPIO) (45)5.1.2单独的位设置或位清除 (45)5.1.3外部中断/唤醒线 (46)5.1.4复用功能(AF) (46)5.1.5软件重新映射I/O复用功能 (46)5.1.6GPIO锁定机制 (46)5.1.7输入配置 (46)5.1.8输出配置 (47)5.1.9复用功能配置 (48)5.2GPIO寄存器描述 (50)5.2.1端口配置低寄存器(GPIOx_CRL) (x=A..E) (50)5.2.2端口配置高寄存器(GPIOx_CRH) (x=A..E) (51)5.2.3端口输入数据寄存器(GPIOx_IDR) (x=A..E) (52)5.2.4端口输出数据寄存器(GPIOx_ODR) (x=A..E) (52)5.2.5端口位设置/复位寄存器(GPIOx_BSRR) (x=A..E) (53)5.2.6端口位复位寄存器(GPIOx_BRR) (x=A..E) (53)5.2.7端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) (54)5.3复用功能I/O和调试配置(AFIO) (55)5.3.1把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 (55)5.3.2BXCAN复用功能重映射 (55)5.3.3JTAG/SWD复用功能重映射 (55)5.3.4定时器复用功能重映射 (56)5.3.5USART复用功能重映射 (57)5.3.6I2C 1 复用功能重映射 (58)5.3.7SPI 1复用功能重映射 (58)5.4AFIO寄存器描述 (59)5.4.1复用重映射和调试I/O配置寄存器(AFIO_MAPR) (60)5.4.2外部中断配置寄存器1(AFIO_EXTICR1) (62)5.4.3外部中断配置寄存器2(AFIO_EXTICR2) (62)5.4.4外部中断配置寄存器3(AFIO_EXTICR3) (63)5.4.5外部中断配置寄存器4(AFIO_EXTICR4) (63)5.5GPIO 和AFIO寄存器地址映象 (64)5.5.1GPIO寄存器地址映象 (64)5.5.2AFIO寄存器地址映象 (65)6中断和事件 (66)6.1嵌套向量中断控制器(NVIC) (66)6.1.1系统嘀嗒(SysTick)校准值寄存器 (66)6.1.2中断和异常向量 (66)6.2外部中断/事件控制器(EXTI) (68)6.2.1主要特性 (68)6.2.2框图 (69)6.2.3唤醒事件管理 (69)6.2.4功能说明 (69)6.2.5外部中断/事件线路映像 (71)6.3EXTI 寄存器描述 (72)6.3.1外部中断/事件寄存器映像 (75)7DMA 控制器(DMA) (76)7.1简介 (76)7.2主要特性 (76)7.3功能描述 (77)7.3.1DMA处理 (77)7.3.2仲裁器 (77)7.3.3DMA 通道 (78)7.3.4错误管理 (79)7.3.5DMA请求映像 (79)7.4DMA寄存器 (82)7.4.1DMA中断状态寄存器(DMA_ISR) (82)7.4.2DMA中断标志清除寄存器(DMA_IFCR) (82)7.4.3DMA通道x配置寄存器(DMA_CCRx)(x = 1...7).. (83)7.4.4DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1...7) (85)7.4.5DMA通道x外设地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.4.6DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.5DMA寄存器映像 (86)8实时时钟(RTC) (88)8.1简介 (88)8.2主要特性 (88)8.3功能描述 (88)8.3.1概述 (88)8.3.2复位过程 (90)8.3.3读RTC寄存器 (90)8.3.4配置RTC寄存器 (90)8.3.5RTC标志的设置 (90)8.4RTC寄存器描述 (91)8.4.1RTC控制寄存器高位(RTC_CRH) (91)8.4.2RTC控制寄存器低位(RTC_CRL) (92)8.4.3RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) (93)8.4.4RTC预分频分频因子寄存器(RTC_DIVH / RTC_DIVL) (94)8.4.5RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) (95)8.4.6RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) (95)8.5RTC寄存器映像 (97)9备份寄存器(BKP) (98)9.1简介 (98)9.2特性 (98)9.3侵入检测 (98)9.4RTC校准 (98)9.5BKP寄存器描述 (99)9.5.1备份数据寄存器x(BKP_DRx) (x = 1 ... 10) (99)9.5.2RTC时钟校准寄存器(BKP_RTCCR) (99)9.5.3备份控制寄存器(BKP_CR) (99)9.5.4备份控制/状态寄存器(BKP_CSR) (100)9.6BKP寄存器映像 (101)10独立看门狗(IWDG) (103)10.1简介 (103)10.1.1硬件看门狗 (103)10.1.2寄存器访问保护 (103)10.1.3调试模式 (104)10.2IWDG寄存器描述 (104)10.2.1键寄存器(IWDG_KR) (104)10.2.2预分频寄存器(IWDG_PR) (105)10.2.3重装载寄存器(IWDG_RLR) (106)10.2.4状态寄存器(IWDG_SR) (106)10.3IWDG寄存器映像 (107)11窗口看门狗(WWDG) (108)11.1简介 (108)11.2主要特性 (108)11.3功能描述 (108)11.4如何编写看门狗超时程序 (109)11.5调试模式 (110)11.6寄存器描述 (111)11.6.1控制寄存器(WWDG_CR) (111)11.6.2配置寄存器(WWDG_CFR) (111)11.6.3状态寄存器(WWDG_SR) (112)11.7WWDG寄存器映像 (113)12高级控制定时器(TIM1) (114)12.1简介 (114)12.2主要特性 (114)12.3框图 (115)12.4功能描述 (116)12.4.1时基单元 (116)12.4.2计数器模式 (117)12.4.3重复向下计数器 (125)12.4.4时钟选择 (126)12.4.5捕获/比较通道 (129)12.4.6输入捕获模式 (131)12.4.7PWM输入模式 (132)12.4.8强置输出模式 (132)12.4.9输出比较模式 (133)12.4.10PWM 模式 (134)12.4.11互补输出和死区插入 (136)12.4.12使用刹车功能 (138)12.4.13在外部事件时清除OCxREF信号 (139)12.4.14六步PWM的产生 (140)12.4.15单脉冲模式 (141)12.4.16编码器接口模式 (143)12.4.17定时器输入异或功能 (144)12.4.18与霍尔元件的接口 (145)12.4.19定时器和外部触发的同步 (146)12.4.20定时器同步 (149)12.4.21调试模式 (149)12.5TIM1寄存器描述 (150)12.5.1控制寄存器1(TIM1_CR1) (150)12.5.2控制寄存器2(TIM1_CR2) (151)12.5.3从模式控制寄存器(TIM1_SMCR) (153)12.5.4DMA/中断使能寄存器(TIM1_DIER) (154)12.5.5状态寄存器(TIM1_SR) (156)12.5.6事件产生寄存器(TIM1_EGR) (157)12.5.7捕获/比较模式寄存器1(TIM1_CCMR1) (158)12.5.8捕获/比较模式寄存器2(TIM1_CCMR2) (161)12.5.10计数器(TIM1_CNT) (165)12.5.11预分频器(TIM1_PSC) (165)12.5.12自动重装载寄存器(TIM1_ARR) (165)12.5.13周期计数寄存器(TIM1_RCR) (166)12.5.14捕获/比较寄存器1(TIM1_CCR1) (166)12.5.15捕获/比较寄存器2(TIM1_CCR2) (167)12.5.16捕获/比较寄存器3(TIM1_CCR3) (167)12.5.17捕获/比较寄存器(TIM1_CCR4) (168)12.5.18刹车和死区寄存器(TIM1_BDTR) (168)12.5.19DMA控制寄存器(TIM1_DCR) (170)12.5.20连续模式的DMA地址(TIM1_DMAR) (170)12.6TIM1寄存器图 (171)13通用定时器(TIMx) (173)13.1概述 (173)13.2主要特性 (173)13.3框图 (174)13.4功能描述 (175)13.4.1时基单元 (175)13.4.2计数器模式 (176)13.4.3时钟选择 (183)13.4.4捕获/比较通道 (185)13.4.5输入捕获模式 (187)13.4.6PWM输入模式 (187)13.4.7强置输出模式 (188)13.4.8输出比较模式 (188)13.4.9PWM 模式 (189)13.4.10单脉冲模式 (191)13.4.11在外部事件时清除OCxREF信号 (193)13.4.12编码器接口模式 (193)13.4.13定时器输入异或功能 (195)13.4.14定时器和外部触发的同步 (195)13.4.15定时器同步 (198)13.4.16调试模式 (202)13.5TIMx寄存器描述 (203)13.5.2控制寄存器2(TIMx_CR2) (205)13.5.3从模式控制寄存器(TIMx_SMCR) (206)13.5.4DMA/中断使能寄存器(TIMx_DIER) (207)13.5.5状态寄存器(TIMx_SR) (209)13.5.6事件产生寄存器(TIMx_EGR) (211)13.5.7捕获/比较模式寄存器1(TIMx_CCMR1) (212)13.5.8捕获/比较模式寄存器2(TIMx_CCMR2) (215)13.5.9捕获/比较使能寄存器(TIMx_CCER) (216)13.5.10计数器(TIMx_CNT) (218)13.5.11预分频器(TIMx_PSC) (218)13.5.12自动重装载寄存器(TIMx_ARR) (218)13.5.13捕获/比较寄存器1(TIMx_CCR1) (219)13.5.14捕获/比较寄存器2(TIMx_CCR2) (220)13.5.15捕获/比较寄存器3(TIMx_CCR3) (220)13.5.16捕获/比较寄存器(TIMx_CCR4) (221)13.5.17DMA控制寄存器(TIMx_DCR) (221)13.5.18连续模式的DMA地址(TIMx_DMAR) (222)13.6TIMx寄存器图 (223)14控制器局域网(bxCAN) (225)14.1简介 (225)14.2主要特点 (225)14.3总体描述 (225)14.3.1CAN 2.0B内核 (226)14.3.2控制、状态和配置寄存器 (226)14.3.3发送邮箱 (226)14.3.4接收过滤器 (226)14.3.5接收FIFO (227)14.4工作模式 (228)14.4.1初始化模式 (228)14.4.2正常模式 (228)14.4.3睡眠模式(低功耗) (228)14.4.4测试模式 (229)14.4.5静默模式 (229)14.4.6环回模式 (229)14.4.7环回静默模式 (230)14.5功能描述 (230)14.5.1发送处理 (230)14.5.2时间触发通信模式 (232)14.5.3接收管理 (232)14.5.4标识符过滤 (234)14.5.5报文存储 (238)14.5.6出错管理 (239)14.5.7位时间特性 (239)14.6中断 (241)14.7寄存器访问保护 (243)14.8CAN 寄存器描述 (243)14.8.1控制和状态寄存器 (243)14.8.2邮箱寄存器 (255)14.8.3CAN过滤器寄存器 (260)14.9bxCAN寄存器列表 (264)15I2C接口 (267)15.1介绍 (267)15.2主要特点 (267)15.3概述 (268)15.4功能描述 (269)15.4.1I2C从模式 (269)15.4.2I2C主模式 (271)15.4.3错误条件 (274)15.4.4SDA/SCL线控制 (275)15.4.5SMBus (275)15.4.6DMA请求 (277)15.4.7包错误校验(PEC) (278)15.5中断请求 (279)15.6I2C寄存器描述 (281)15.6.1控制寄存器1(I2C_CR1) (281)15.6.2控制寄存器2(I2C_CR2) (283)15.6.3自身地址寄存器1 (I2C_OAR1) (284)15.6.4自身地址寄存器2(I2C_OAR2) (285)15.6.5数据寄存器(I2C_DR) (285)15.6.6状态寄存器1(I2C_SR1) (285)15.6.7状态寄存器2 (I2C_SR2) (288)15.6.8时钟控制寄存器(I2C_CCR) (289)15.6.9TRISE寄存器(I2C_TRISE) (290)15.7I2C寄存器地址映象 (291)16串行外设接口(SPI) (292)16.1简介 (292)16.2主要特征 (292)16.3功能描述 (292)16.3.1概述 (292)16.3.2SPI从模式 (295)16.3.3SPI主模式 (296)16.3.4单向通信 (297)16.3.5状态标志 (297)16.3.6CRC计算 (298)16.3.7利用DMA的SPI通信 (299)16.3.8错误标志 (299)16.3.9中断 (300)16.4SPI寄存器描述 (300)16.4.1SPI控制寄存器1(SPI_CR1) (300)16.4.2SPI控制寄存器2(SPI_CR2) (302)16.4.3SPI 状态寄存器(SPI_SR) (303)16.4.4SPI 数据寄存器(SPI_DR) (304)16.4.5SPI CRC多项式寄存器(SPI_CRCPR) (304)16.4.6SPI Rx CRC寄存器(SPI_RXCRCR) (305)16.4.7SPI Tx CRC寄存器(SPI_TXCRCR) (305)16.5SPI 寄存器地址映象 (306)17USART收发器(USART) (307)17.1介绍 (307)17.2概述 (308)17.2.1框图 (309)17.2.2USART 特征描述 (310)17.2.3发送器 (310)17.2.4接收器 (312)17.2.5分数波特率的产生 (315)17.2.617.2.6 多处理器通信 (316)17.2.7校验控制 (317)17.2.8LIN(局域互联网)模式 (318)17.2.9USART 同步模式 (320)17.2.10单线半双工通信 (322)17.2.11智能卡 (322)17.2.12IrDA SIR ENDEC 功能块 (324)17.2.13利用DMA连续通信 (325)17.2.14硬件流控制 (326)17.3中断请求 (327)17.4USART寄存器描述 (329)17.4.1状态寄存器(USART_SR) (329)17.4.2数据寄存器(USART_DR) (330)17.4.3波特比率寄存器(USART_BRR) (331)17.4.4控制寄存器1 (USART_CR1) (331)17.4.5控制寄存器2(USART_CR2) (333)17.4.6控制寄存器3(USART_CR3) (335)17.4.7保护时间和预分频寄存器(USART_GTPR) (336)17.5USART寄存器地址映象 (338)18USB全速设备接口(USB) (339)18.1导言 (339)18.2主要特征 (339)18.3方框图 (339)18.4功能描述 (340)18.4.1USB功能模块描述 (341)18.5编程中需要考虑的问题 (342)18.5.1通用USB设备编程 (342)18.5.2系统复位和上电复位 (342)18.5.3双缓冲端点 (346)18.5.4同步传输 (347)18.5.5挂起/恢复事件 (348)18.6USB寄存器描述 (350)18.6.1通用寄存器 (350)18.6.2端点寄存器 (355)18.6.3缓冲区描述表 (358)18.7USB寄存器映像 (361)19模拟/数字转换(ADC) (363)19.1介绍 (363)19.2主要特征 (363)19.3引脚描述 (365)19.4功能描述 (365)19.4.1ADC开关控制 (365)19.4.2ADC时钟 (365)19.4.3通道选择 (365)19.4.4单次转换模式 (366)19.4.5连续转换模式 (366)19.4.6时序图 (367)19.4.7模拟看门狗 (368)19.4.8扫描模式 (368)19.4.9注入通道管理 (369)19.4.10间断模式 (369)19.5校准 (370)19.6数据对齐 (371)19.7可编程的通道采样时间 (371)19.8外部触发转换 (371)19.9DMA请求 (372)19.10双ADC模式 (372)19.10.1同时注入模式 (374)19.10.2同时规则模式 (374)19.10.3快速交替模式 (375)19.10.4慢速交替模式 (375)19.10.5交替触发模式 (376)19.10.6独立模式 (377)19.10.7混合的规则/注入同步模式 (377)19.10.8混合的同步规则+交替触发模式 (377)19.10.9混合同步注入+交替模式 (378)19.11温度传感器 (378)19.12中断 (379)19.13ADC寄存器描述 (381)19.13.1ADC状态寄存器(ADC_SR) (381)19.13.2ADC控制寄存器1(ADC_CR1) (382)19.13.3ADC控制寄存器2(ADC_CR2) (384)19.13.4ADC采样时间寄存器1(ADC_SMPR1) (387)19.13.5ADC采样时间寄存器2(ADC_SMPR2) (387)19.13.6ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) (388)19.13.7ADC看门狗高阀值寄存器(ADC_HTR) (388)19.13.8ADC看门狗低阀值寄存器(ADC_LRT) (388)19.13.9ADC规则序列寄存器1(ADC_SQR1) (390)19.13.10ADC规则序列寄存器2(ADC_SQR2) (390)19.13.11ADC规则序列寄存器3(ADC_SQR3) (391)19.13.12ADC注入序列寄存器(ADC_JSQR) (391)19.13.13ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) (392)19.13.14ADC规则数据寄存器(ADC_DR) (392)19.14ADC寄存器地址映像 (394)20调试支持(DBG) (396)20.1概况 (396)20.2ARM参考文献 (397)20.3SWJ调试端口(serial wire and JTAG) (397)20.3.1JTAG-DP和SW-DP切换的机制 (397)20.4引脚分布和调试端口脚 (398)20.4.1SWJ调试端口脚 (398)20.4.2灵活的SWJ-DP脚分配 (398)20.4.3JTAG脚上的内部上拉和下拉 (399)20.4.4利用串行接口并释放不用的调试脚作为普通I/O口 (400)20.5STM32F10x JTAG TAP 连接 (400)20.6ID 代码和锁定机制 (401)20.6.1MCU DEVICE ID编码 (401)20.6.2TMC TAP (401)20.6.3Cortex-M3 TAP (401)20.6.4Cortex-M3 JEDEC-106 ID代码 (401)20.7JTAG调试端口 (402)20.8SW调试端口 (403)20.8.1SW协议介绍 (403)20.8.2SW协议序列 (403)20.8.3SW-DP状态机(Reset, idle states, ID code) (404)20.8.4DP和AP读/写访问 (404)20.8.5SW-DP寄存器 (405)20.8.6SW-AP寄存器 (405)20.9对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) (405)20.10内核调试 (406)20.11调试器主机在系统复位下的连接能力 (407)20.12FPB (Flash patch breakpoint) (407)20.13DWT(data watchpoint trigger) (407)20.14ITM (instrumentation trace macrocell) (408)20.14.1概述 (408)20.14.2时间戳包,同步和溢出包 (408)20.15MCU调试模块(MCUDBG) (409)20.15.1低功耗模式的调试支持 (409)20.15.2支持定时器和看门狗和bxCAN的调试 (409)20.15.3调试MCU配置寄存器 (410)20.16TPIU (trace port interface unit) (411)20.16.1导言 (411)20.16.2跟踪引脚分配 (412)20.16.3TPUI格式器 (414)20.16.4TPUI帧异步包 (414)20.16.5同步帧包的发送 (415)20.16.6同步模式 (415)20.16.7异步模式 (415)20.16.8TRACECLKIN在STM32F10x内部的连接 (415)20.16.9TPIU寄存器 (416)20.16.10配置的例子 (416)20.17DBG寄存器地址映象 (417)STM32F10x参考手册第一版文档中的约定1 文档中的约定1.1 寄存器描述中使用的缩写列表在对寄存器的描述中使用了下列缩写:read / write (rw) 软件能读写此位。

STM32F10x参考手册参考手册参考手册参考手册

关于如何进入停止模式,详见表 3-4。 在停止模式下,通过设置电源控制寄存器(PWR_CR)的 LPDS 位使内部调节器进入低功耗 模式,能够降低更多的功耗。

如果正在进行 Flash 编程,直到对内存访问完成,系统才进入停止模式。 如果正在进行对 APB 的访问,直到对 APB 访问完成,系统才进入停止模式。 可以通过对独立的控制位进行编程,可选择以下功能:

表3-4 停止模式

进入

退出 唤醒延时

在以下条件下执行WFI或WFE指令: – 设置Cortex-M3系统控制寄存器中的SLEEPDEEP位 – 清除电源控制寄存器(PWR_CR)中的PDDS位 – 通过设置PWR_CR中LPDS位选择电压调节器的模式 注:为了进入停止模式,所有的外部中断的请求位(挂起寄存器(EXTI_PR))和RTC的闹 钟标志都必须被清除,否则停止模式的进入流程将会被跳过,程序继续运行。

STM32F10x 参考手册

第一版

电源控制(PWR)

3 电源控制(PWR)

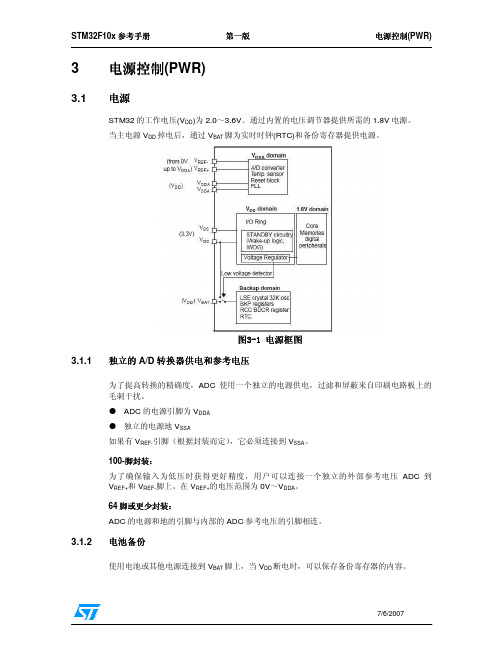

3.1 电源

STM32 的工作电压(VDD)为 2.0~3.6V。通过内置的电压调节器提供所需的 1.8V 电源。 当主电源 VDD 掉电后,通过 VBAT 脚为实时时钟(RTC)和备份寄存器提供电源。

3.1.1

图3-1 电源框图 独立的 A/D 转换器供电和参考电压

如果应用中没有使用外部电池,VBAT 必须连接到 VDD 引脚上。

注意:在 VDD 上升阶段(tRSTTEMPO),VBAT 和 VDD 之间的电源开关仍会保持连接在 VBAT。当 VDD 快速上升且达 到稳定状态,当 VBAT 低于 VDD−0.6V 时,电流通过 VDD 和 VBAT 之间的二极管流入到 VBAT。关于 tRSTTEMPO 可参考数据手册中的相关部分。

STM32单片机的知识点总结

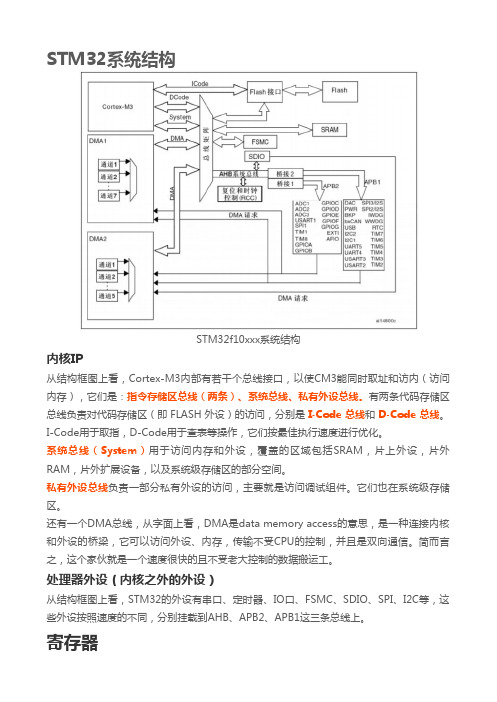

STM32系统结构STM32f10xxx系统结构内核IP从结构框图上看,Cortex-M3内部有若干个总线接口,以使CM3能同时取址和访内(访问内存),它们是:指令存储区总线(两条)、系统总线、私有外设总线。

有两条代码存储区总线负责对代码存储区(即 FLASH 外设)的访问,分别是 I-Code 总线和 D-Code 总线。

I-Code用于取指,D-Code用于查表等操作,它们按最佳执行速度进行优化。

系统总线(System)用于访问内存和外设,覆盖的区域包括SRAM,片上外设,片外RAM,片外扩展设备,以及系统级存储区的部分空间。

私有外设总线负责一部分私有外设的访问,主要就是访问调试组件。

它们也在系统级存储区。

还有一个DMA总线,从字面上看,DMA是data memory access的意思,是一种连接内核和外设的桥梁,它可以访问外设、内存,传输不受CPU的控制,并且是双向通信。

简而言之,这个家伙就是一个速度很快的且不受老大控制的数据搬运工。

处理器外设(内核之外的外设)从结构框图上看,STM32的外设有串口、定时器、IO口、FSMC、SDIO、SPI、I2C等,这些外设按照速度的不同,分别挂载到AHB、APB2、APB1这三条总线上。

寄存器什么是寄存器?寄存器是内置于各个IP外设中,是一种用于配置外设功能的存储器,并且有想对应的地址。

一切库的封装始于映射。

是不是看的眼都花了,如果进行寄存器开发,就需要怼地址以及对寄存器进行字节赋值,不仅效率低而且容易出错。

库的存在就是为了解决这类问题,将代码语义化。

语义化思想不仅仅是嵌入式有的,前端代码也在追求语义特性。

从点灯开始学习STM32内核库文件分析cor_cm3.h这个头文件实现了:1、内核结构体寄存器定义。

2、内核寄存器内存映射。

3、内存寄存器位定义。

跟处理器相关的头文件stm32f10x.h实现的功能一样,一个是针对内核的寄存器,一个是针对内核之外,即处理器的寄存器。

STM32库函数底层操作解析

至此对程序段一的①解析可以做一个总结:该行定义一个结构体类型的变 量 GPIO_InitStructure , 并 且 该 结 构 体 有 3 个 成 员 , 分 别 为 GPIO_Pin 、 GPIO_Speed 和 GPIO_Mode,并且 GPIO_Pin 表示 GPIO 设备引脚 GPIO_Speed 表示 GPIO 设备速率和 GPIO_Mode 表示 GPIO 设备工作模式。

STM32 库函数底层操作解析

意法半导体在推出 STM32 微控制器之初,也同时提供了一套完整细致的固件开发包,里面包含 了在 STM32 开发过程中所涉及到的所有底层操作。通过在程序开发中引入这样的固件开发包,可以 使开发人员从复杂冗余的底层寄存器操作中解放出来,将精力专注应用程序的开发上,这便是 ST 推出这样一个开发包的初衷。

/* 读出当前配置字 */ tmpreg = GPIOx->CRL; for (pinpos = 0x00; pinpos < 0x08; pinpos++) {

/* 获取将要配置的引脚号 */ pos = ((u32)0x01) << pinpos; currentpin = (GPIO_InitStruct->GPIO_Pin) & pos; if (currentpin == pos) {

assert_param(IS_GPIO_SPEED(GPIO_InitStruct->GPIO_Speed)); currentmode |= (u32)GPIO_InitStruct->GPIO_Speed; }

第1章 STM32F10X系统介绍

• • • • •

多达2个 同步串行接口(18兆位 多达 个SPI同步串行接口 兆位 秒) 同步串行接口 兆位/秒 CAN 接口 接口(2.0B 主动 主动) USB 2.0 全速接口 调试模式 串行线调试(SWD)和JTAG接口 串行线调试 和 接口

1.1.4 STM32F10X 的应用前景

销售终端机 安防设备

• 72MHz CortexTM-M3 CPU

512 K

384 K

– 6KB to 64KB SRAM – Two lines: Performance and Access – FULL compatibility across family

256 K

128 K

STM32F103CB STM32F101CB STM32F103T8 STM32F103C8 STM32F101C8 STM32F103C6 STM32F101C6 48 pins LQFP

银行卡读卡器 超市收银机 扫描仪 报警系统 控制面板

USB 设备

生物认证和安全设备 读卡器

医药卫生

监护仪 检测设备

其它 工业自动化

程序控制器 工业网络 电池管理 ……

消费电子

PC附属设备 数码相机、GPS导航仪 卫星电话

强大的工具支持

Compilers and IDE Device Programming

– 16位处理器 位处理器 – 最高40MHz 最高

• 存储器

– 从32K字节至 字节至128K字节闪存 字节闪存 字节至 程序存储器 – 从6K字节至 字节至20K字节 字节SRAM 字节至 字节 – 多重自举功能

• 存储器

– 32K字节 字节 – SRAM:2K : – 只能从FLASH启动 只能从 启动

STM32F10xxx闪存编程参考手册

STM32F10xxx闪存编程手册

页1/22

依据2008年9月英文第4版翻译。本译文仅供参考,如有翻译错误,请以英文原稿为准

目录

1 概述 ...................................................................................................................................................4 1.1 特性 ........................................................................................................................................4 1.2 闪存模块组织 ...............................................................................................4

z Cortex-M3内核集成了两个调试端口: − JTAG调试接口(JTAG-DP)提供基于JTAG(Joint Test Action Group 联合测试行动 小组)协议的5线标准接口。 − SWD调试接口(SWD-DP)提供基于SWD(Serial Wire Debug 串行线调试)协议的2 线标准接口。

z 中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx 和STM32F103xx微控制器。

z 大 容 量 产 品 是 指 闪 存 存 储 器 容 量 在 256K 至 512K 字 节 之 间 的 STM32F101xx 和 STM32F103xx微控制器。

STM32F10x闪存编程手册_V6

3 寄存器说明 ......................................................................................................................................15 3.1 闪存访问控制寄存器(FLASH_ACR)......................................................................................15 3.2 FPEC键寄存器(FLASH_KEYR) ............................................................................................16 3.3 闪存OPTKEY寄存器(FLASH_OPTKEYR) ............................................................................16 3.4 闪存状态寄存器(FLASH_SR)................................................................................................16 3.5 闪存控制寄存器(FLASH_CR) ...............................................................................................17 3.6 闪存地址寄存器(FLASH_AR)................................................................................................18 3.7 选项字节寄存器(FLASH_OBR).............................................................................................18 3.8 写保护寄存器(FLASH_WRPR) .............................................................................................19 3.9 闪存寄存器映像 ....................................................................................................................19

stm32入门说明

下载好的文件一般是个压缩包, 我们把它解压一下默认的文件名就可以了, 我现在使用的是 v3.1.2 的库,解压后的文件名 STM32F10x_StdPeriph_Lib_V3.1.2,打开解压后的文件可以看到 如下的内容

Libraries 是系统的库,不需要我们修改。project 是工程的一些东西,里面是些例程和模板。 Utilities 是 st 的开发板的一些东西。我们主要关注 project 里面的内容。Project 如下

GPIOSpeed_TypeDef GPIO_Speed;

GPIOMode_TypeDef GPIO_Mode;

}GPIO_InitTypeDef; 其中的 GPIOSpeed_TypeDef, GPIOMode_TypeDef 可以查看库中的 GPIO.h 文件中的详细定义 这里就不介绍。 看下 st 给出的库提供了哪些操作端口的函数吧: 这些函数的详细信息可以参考 st 的库说明,最好去看一下函数的原型代码,这样会有更好 的理解。当然了,我在具体使用的时候也会做一般的说明。 void GPIO_DeInit(GPIO_TypeDef* GPIOx); void GPIO_AFIODeInit(void); void GPIO_Init(GPIO_TypeDef* GPIOx, GPIO_InitTypeDef* GPIO_InitStruct); void GPIO_StructInit(GPIO_InitTypeDef* GPIO_InitStruct); uint8_t GPIO_ReadInputDataBit(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin); uint16_t GPIO_ReadInputData(GPIO_TypeDef* GPIOx); uint8_t GPIO_ReadOutputDataBit(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin); uint16_t GPIO_ReadOutputData(GPIO_TypeDef* GPIOx); void GPIO_SetBits(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin); void GPIO_ResetBits(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin); void GPIO_WriteBit(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin, BitAction BitVal); void GPIO_Write(GPIO_TypeDef* GPIOx, uint16_t PortVal); void GPIO_PinLockConfig(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin); void GPIO_EventOutputConfig(uint8_t GPIO_PortSource, uint8_t GPIO_PinSource); void GPIO_EventOutputCmd(FunctionalState NewState); void GPIO_PinRemapConfig(uint32_t GPIO_Remap, FunctionalState NewState); void GPIO_EXTILineConfig(uint8_t GPIO_PortSource, uint8_t GPIO_PinSource); void GPIO_ETH_MediaInterfaceConfig(uint32_t GPIO_ETH_MediaInterface); 介绍到这里, 对通用的 I/O 端口有个大概的了解了吧, 下面我们通过例子来详细的说明一下。 说到这里,是该介绍一下如何使用 MDK4.0 开始一个新的工程,这里我们使用最新的库进行 配置操作。 去下载新的库,如何下载大家 google 吧,一般 st 的网站上都有的,这里就略过了。

STM32F10x参考手册参考手册参考手册参考手册

STM32F10x参考手册

第一版

通用和复用功能I/O(GPIO和AFIO)

5.3

5.3.1 5.3.2

5.3.3

复用功能I/O和调试配置(AFIO)

为了优化64脚或100脚封装的外设数目,可以把一些复用功能重新映射到其他引脚上。设置 复用重映射和调试I/O配置寄存器(AFIO_MAPR)(参见5.4.1节)实现引脚的重新映射。这时, 复用功能不再映射到它们的原始分配上。

调试接口信号被映射到GPIO端口上,如表5-4所示。 表5-4 调试接口信号

复用功能 JTMS/SWDIO JTCK/SWCLK

JTDI JTDO/TRACESWO

JNTRST TRACECK TRACED0 TRACED1 TRACED2 TRACED3

GPIO端口 PA13 PA14 PA15 PB3 PB4 PE2 PE3 PE4 PE5 PE6

其它

禁用

1. I/O口只可在不使用异步跟踪时使用。

定时器复用功能重映射

定时器4的通道1到通道4可以从端口B重映射到端口D。其他定时器的重映射可能性列在表 5-6到表5-9里。

表5-6 定时器4复用功能重映像

复用功能

TIM4_REMAP = 0

TIM4_REMAP = 1

TIM4_CH1

PB6

PD12

3 STM32F10x简介

STM32系列微控制器 STM32系列微控制器 STM32F10x内部结构 STM32F10x内部结构 时钟结构 存储结构 启动模式

3.2 STM32F10x内部结构 STM32F10x内部结构

3.2 STM32F10x内部结构 STM32F10x内部结构

基本型与增强型配置的差异

ARM Cortex-M3模块结构 Cortex-M3模块结构

3.4 存储结构

存储组织: 存储组织:

Cortex-M3的存储系统采用统一编址方式, Cortex-M3的存储系统采用统一编址方式,小端方式 的存储系统采用统一编址方式 的线性地址空间内, 4GB 的线性地址空间内,寻址空间被分成 8 个主块

block0block0-block7 每块512MB 每块512MB

3.3 时钟结构

3.3 时钟结构

系统复位后,所有外设全部关闭, 系统复位后,所有外设全部关闭,

但 SRAM 和 FLASH接口(FLITF)除外 FLASH接口 FLITF) 接口(

使用外设之前需打开该外设时钟

设置 RCC——AHBENR 寄存器 RCC—— ——AHBENR

参见PDF 参见PDF资料 PDF资料

3.2 STM32F10x内部结构 STM32F10x内部结构

FLASH接口 接口

总 线 矩 阵

3.2 STM32F10x内部结构 STM32F10x内部结构

四个主动单元

M3内核的ICode总线(I-bus)、DCode总线(D-bus)、 M3内核的ICode总线(I-bus)、DCode总线(D-bus)、 内核的ICode总线(I 总线(D 系统总线(S bus)、DMA(DMA1、DMA2、以太网DMA) (S系统总线(S-bus)、DMA(DMA1、DMA2、以太网DMA)

STM32F10x固件库下载与安装说明(第20步固件库的安装)

1/9

【创建新工程文件】

先选择一个硬盘目录作为工程建立的地方(文件夹名支持中文)。在这个目录下手动新建如下 4 个文件夹。

把此目录下的 2 个文件: E:\ STM32F10x_StdPeriph_Lib_V3.5.0\Libraries\CMSIS\CM3\CoreSupport

编写时间: 201 年月日

硬件支持: STM32F103C8 外部晶振 8M

修Байду номын сангаас日志:

1-

*/

#include "stm32f10x.h" //STM 头文件

int main (void){//主程序 while(1){

//无限循环程序

} }

9/9

YoungTalk 洋桃电子

STM32F10x 固件库下载与安装说明

V1.0 2017-11-30 STM32 固件库 STM32 Standard Peripheral Libraries,适用于 STM32F1 系列。 STM32 的固件库是芯片官方给出的用于新建 STM32 工程与相关的库文件、示例程序的资料包。 【固件库下载】 最新版本是 3.5.0 (STM32F10x_StdPeriph_Lib_V3.5.0) 官网下载链接: /en/embedded-software/stm32-standard-peripheral-libraries.html?querycriteria=produ ctId=LN1939

配置完成后,点击下方 OK 按钮退出。在 KEIL 主界面左边工程目录中就会有如下的文件目录。

5/9

3,初始化设置

点击下图中的图标。 在 Target 中设置晶振频率为 8.0(洋桃 1 号核心板上的晶振频率)。

深入浅出stm32

STM32学前班教程之一:为什么是它经过几天的学习,基本掌握了STM32的调试环境和一些基本知识。

想拿出来与大家共享,笨教程本着最大限度简化删减STM32入门的过程的思想,会把我的整个入门前的工作推荐给大家。

就算是给网上的众多教程、笔记的一种补充吧,所以叫学前班教程。

其中涉及产品一律隐去来源和品牌,以防广告之嫌。

全部汉字内容为个人笔记。

所有相关参考资料也全部列出。

:lol教程会分几篇,因为太长啦。

今天先来说说为什么是它——我选择STM32的原因。

我对未来的规划是以功能性为主的,在功能和面积之间做以平衡是我的首要选择,而把运算放在第二位,这根我的专业有关系。

里面的运算其实并不复杂,在入门阶段想尽量减少所接触的东西。

不过说实话,对DSP的外设并和开发环境不满意,这是为什么STM32一出就转向的原因。

下面是我自己做过的两块DSP28的全功能最小系统板,在做这两块板子的过程中发现要想尽力缩小DSP的面积实在不容易(目前只能达到50mm×45mm,这还是没有其他器件的情况下),尤其是双电源的供电方式和1.9V的电源让人很头疼。

后来因为一个项目,接触了LPC2148并做了一块板子,发现小型的AR M7在外设够用的情况下其实很不错,于是开始搜集相关芯片资料,也同时对小面积的AVR和51都进行了大致的比较,这个时候发现了C ortexM3的S TM32,比2148拥有更丰富和灵活的外设,性能几乎是2148两倍(按照MIPS值计算)。

正好2148我还没上手,就直接转了这款STM32F103。

与2811相比较(核心1.8V供电情况下),135MHz×1MIPS。

现在用S TM32F103,72MHz×1.25MIPS,性能是DSP的66%,STM32F103R型(64管脚)芯片面积只有2811的51%,STM32F103C型(48管脚)面积是2811的25%,最大功耗是DSP的20%,单片价格是DSP的30%。