BUL45G;BUL45;中文规格书,Datasheet资料

BUL45D2G;BUL45D2;中文规格书,Datasheet资料

BUL45D2GHigh Speed, High Gain Bipolar NPN Power Transistorwith Integrated Collector−Emitter Diode and Built−in Efficient Antisaturation NetworkThe BUL45D2G is state−of−art High Speed High gain BiPolar transistor (H2BIP). High dynamic characteristics and lot−to−lot minimum spread (±150 ns on storage time) make it ideally suitable for light ballast applications. Therefore, there is no need to guarantee an h FE window. It’s characteristics make it also suitable for PFC application. Features•Low Base Drive Requirement•High Peak DC Current Gain (55 Typical) @ I C = 100 mA •Extremely Low Storage Time Min/Max Guarantees Due tothe H2BIP Structure which Minimizes the Spread •Integrated Collector−Emitter Free Wheeling Diode•Fully Characterized and Guaranteed Dynamic V CE(sat)•“6 Sigma” Process Providing Tight and Reproductible Parameter Spreads•These Devices are Pb−Free and are RoHS Compliant* MAXIMUM RATINGSRating Symbol Value Unit Collector−Emitter Sustaining Voltage V CEO400Vdc Collector−Base Breakdown Voltage V CBO700Vdc Collector−Emitter Breakdown Voltage V CES700Vdc Emitter−Base Voltage V EBO12VdcCollector Current− Continuous− Peak (Note 1)I CI CM510AdcBase Current− Continuous− Peak (Note 1)I BI BM24AdcTotal Device Dissipation @ T C = 25_C Derate above 25°C P D750.6WW/_COperating and Storage Temperature T J, T stg−65 to 150_CTHERMAL CHARACTERISTICSCharacteristics Symbol Max Unit Thermal Resistance, Junction−to−Case R q JC 1.65_C/W Thermal Resistance, Junction−to−Ambient R q JA62.5_C/W Maximum Lead Temperature for SolderingPurposes 1/8″ from Case for 5 SecondsT L260_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Pulse Test: Pulse Width = 5 ms, Duty Cycle ≤ 10%.*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.POWER TRANSISTOR5.0 AMPERES,700 VOLTS, 75 WATTSTO−220ABCASE 221A−09STYLE 1MARKING DIAGRAMA= Assembly LocationY= YearWW= Work WeekG= Pb−Free Package Device Package Shipping ORDERING INFORMATIONBUL45D2G TO−220(Pb−Free)50 Units / RailOFF CHARACTERISTICSCollector−Emitter Sustaining Voltage(I C = 100 mA, L = 25 mH)V CEO(sus)400450VdcCollector−Base Breakdown Voltage(I CBO = 1 mA)V CBO700910VdcEmitter−Base Breakdown Voltage(I EBO = 1 mA)V EBO1214.1VdcCollector Cutoff Current(V CE = Rated V CEO, I B = 0)I CEO100m AdcCollector Cutoff Current(V CE = Rated V CES, V EB = 0)(V CE = 500 V, V EB = 0)@ T C = 25°C@ T C = 125°C@ T C = 125°CI CES100500100m AdcEmitter−Cutoff Current(V EB = 10 Vdc, I C = 0)I EBO100m Adc ON CHARACTERISTICSBase−Emitter Saturation Voltage(I C = 0.8 Adc, I B = 80 mAdc)@ T C = 25°C@ T C = 125°C V BE(sat)0.80.710.9Vdc(I C = 2 Adc, I B = 0.4 Adc)@ T C = 25°C@ T C = 125°C 0.890.7910.9Collector−Emitter Saturation Voltage(I C = 0.8 Adc, I B = 80 mAdc)@ T C = 25°C@ T C = 125°C V CE(sat)0.280.320.40.5Vdc(I C = 2 Adc, I B = 0.4 Adc)@ T C = 25°C@ T C = 125°C 0.320.380.50.6(I C = 0.8 Adc, I B = 40 mAdc)@ T C = 25°C@ T C = 125°C 0.460.620.751DC Current Gain(I C = 0.8 Adc, V CE = 1 Vdc)@ T C = 25°C@ T C = 125°C h FE22203429—(I C = 2 Adc, V CE = 1 Vdc)@ T C = 25°C@ T C = 125°C 107149.5DIODE CHARACTERISTICSForward Diode Voltage(I EC = 1 Adc)@ T C = 25°C@ T C = 125°C V EC1.040.71.5V(I EC = 2 Adc)@ T C = 25°C@ T C = 125°C1.2 1.6(I EC = 0.4 Adc)@ T C = 25°C@ T C = 125°C 0.850.621.2Forward Recovery Time (see Figure 27)(I F = 1 Adc, di/dt = 10 A/m s)@ T C = 25°CT fr330ns (I F = 2 Adc, di/dt = 10 A/m s)@ T C = 25°C360(I F = 0.4 Adc, di/dt = 10 A/m s)@ T C = 25°C320DYNAMIC CHARACTERISTICSCurrent Gain Bandwidth(I C = 0.5 Adc, V CE = 10 Vdc, f = 1 MHz)f T13MHzOutput Capacitance(V CB = 10 Vdc, I E = 0, f = 1 MHz)C ob5075pFInput Capacitance(V EB = 8 Vdc)C ib340500pF DYNAMIC SATURATION VOLTAGEDynamic Saturation Voltage:Determined 1 m s and 3 m s respectively after rising I B1 reaches 90% of final I B1I C = 1 AI B1 = 100 mAV CC = 300 V@ 1 m s@ T C = 25°C@ T C = 125°CV CE(dsat) 3.79.4V@ 3 m s@ T C = 25°C@ T C = 125°C0.352.7VI C = 2 AI B1 = 0.8 AV CC = 300 V@ 1 m s@ T C = 25°C@ T C = 125°C3.912V@ 3 m s@ T C = 25°C@ T C = 125°C0.41.5VSWITCHING CHARACTERISTICS: Resistive Load (D.C. ≤ 10%, Pulse Width = 20 m s)Turn−on TimeI C = 2 Adc, I B1 = 0.4 AdcI B2 = 1 AdcV CC = 300 Vdc @ T C = 25°C@ T C = 125°Ct on90105150nsTurn−off Time@ T C = 25°C@ T C = 125°C t off 1.151.51.3m sTurn−on TimeI C = 2 Adc, I B1 = 0.4 AdcI B2 = 0.4 AdcV CC = 300 Vdc @ T C = 25°C@ T C = 125°Ct on90110150nsTurn−off Time@ T C = 25°C@ T C = 125°C t off 2.13.12.4m sSWITCHING CHARACTERISTICS: Inductive Load (V clamp = 300 V, V CC = 15 V, L = 200 m H)Fall TimeI C = 1 AdcI B1 = 100 mAdcI B2 = 500 mAdc @ T C = 25°C@ T C = 125°Ct f9093150nsStorage Time@ T C = 25°C@ T C = 125°C t s0.721.050.9m sCrossover Time@ T C = 25°C@ T C = 125°C t c9595150nsFall TimeI C = 2 AdcI B1 = 0.4 AdcI B2 = 0.4 Adc @ T C = 25°C@ T C = 125°Ct f80105150nsStorage Time@ T C = 25°C@ T C = 125°C t s 1.952.92.25m sCrossover Time@ T C = 25°C@ T C = 125°C t c225450300nsFigure 1. DC Current Gain @ 1 Volt 100806040200I C , COLLECTOR CURRENT (AMPS)h F E, D C C U R R E NT GA I NFigure 2. DC Current Gain @ 5 Volt100806040200I C , COLLECTOR CURRENT (AMPS)h F E , D C C U R R E N T G A I NFigure 3. Collector Saturation Region 420I B , BASE CURRENT (AMPS)Figure 4. Collector −Emitter Saturation Voltage1010.1I C , COLLECTOR CURRENT (AMPS)V C E , V O L T A G E (V O L T S )V C E , V O L T A G E (V O L T S )31Figure 5. Collector −Emitter Saturation Voltage 1010.1I C , COLLECTOR CURRENT (AMPS)Figure 6. Collector −Emitter Saturation Voltage1010.1I C , COLLECTOR CURRENT (AMPS)V C E , V O L T A G E (V O L T S )V C E , V O L T A G E (V O L T S )Figure 7. Base −Emitter Saturation Region 1010.1I C, COLLECTOR CURRENT (AMPS)Figure 8. Base −Emitter Saturation Region1010.1I C , COLLECTOR CURRENT (AMPS)V B E , V O L T A G E (V O L T S )V B E , V O L T A G E (V O L T S )Figure 9. Base −Emitter Saturation Region 1010.1I C , COLLECTOR CURRENT (AMPS)Figure 10. Forward Diode Voltage1010.1REVERSE EMITTER-COLLECTOR CURRENT (AMPS)V B E , V O L T A G E (V O L T S )F O R W A R D D I O D E V O L T AG E (V O L T S )Figure 11. Capacitance 1000101V R , REVERSE VOLTAGE (VOLTS)100Figure 12. BVCER = f(ICER)1000700400R BE (W )B VC E R (V O L T S )900800600500Figure 13. Resistive Switch Time, t on1000400I C , COLLECTOR CURRENT (AMPS)t , T IM E (n s )800600200Figure 14. Resistive Switch Time, t offI C , COLLECTOR CURRENT (AMPS)t , T I M E ( s )μFigure 15. Inductive Storage Time,t si @ I C /I B = 542I C , COLLECTOR CURRENT (AMPS)31t , T I M E ( s )μFigure 16. Inductive Storage Time,t si @ I C /I B = 10I C , COLLECTOR CURRENT (AMPS)t , T I M E ( s )μt , T I M E (n s )Figure 17. Inductive Switching,t c & t fi @ I C /I B = 5600200I C , COLLECTOR CURRENT (AMPS)400300100500Figure 18. Inductive Switching,t fi @ I C /I B = 10t , T I M E (n s )4002004I C , COLLECTOR CURRENT (AMPS)3001001500I C , COLLECTOR CURRENT (AMPS)Figure 19. Inductive Switching,t c @ I C /I B = 1052h FE , FORCED GAIN431000t, T I M E (n s )500, S T O R A G E T I M E(t s i μs )Figure 20. Inductive Storage TimeFigure 21. Inductive Fall Time 45050h FE , FORCED GAINFigure 22. Inductive Crossover Time14004000h FE , FORCED GAIN1000600200350t f i , F A L L T I M E (n s )t c , C R O S S O V E R T I M E (n s )250150800Figure 23. Inductive Storage Time, t si30000I C , COLLECTOR CURRENT (AMPS)2000t , T I M E (n s )1000Figure 24. Forward Recovery Time t fr360300I F , FORWARD CURRENT (AMP)t f r , F O R W A R D R E C O V E R Y T I M E (n s )3403201200Figure 25. Dynamic SaturationVoltage MeasurementsTIMEFigure 26. Inductive Switching Measurements104TIME86297531Figure 27. t fr MeasurementsV ITable 1. Inductive Load Switching Drive CircuitV (BR)CEO(sus)L = 10 mH R B2 = ∞V CC = 20 Volts I C(pk) = 100 mAInductive Switching L = 200 m H R B2 = 0V CC = 15 Volts R B1 selected for desired I B1RBSOA L = 500 m H R B2 = 0V CC = 15 Volts R B1 selected for desired IB1m FI C PEAKV CEI BFigure 28. Forward Bias Safe Operating Area 1000.01V CE , COLLECTOR-EMITTER VOLTAGE (VOLTS)Figure 29. Reverse Bias Safe Operating Area630V CE , COLLECTOR-EMITTER VOLTAGE (VOLTS)10.1I C , C O L L E C T O R C U R R E N T (A M P S )I C , C O L L E C T O R C U R R E N T (A M P S )254TYPICAL CHARACTERISTICS101TYPICAL CHARACTERISTICSFigure 30. Forward Bias Power Derating10T C , CASE TEMPERATURE (°C)0.8P O W E R D E R A T I N G F A C T O R0.60.40.2There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate I C −V CE limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate. The data of Figure 28 is based on T C = 25°C; T J(pk) is variable depending on power level. Second breakdown pulse limits are valid for duty cycles to 10% but must be derated when T C > 25°C. Second breakdown limitations do not derate the same as thermal limitations. Allowable current at the voltages shown on Figure 28 may be found at any case temperature by using the appropriate curve on Figure 30.T J(pk) may be calculated from the data in Figure 31. At any case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown. For inductive loads, high voltage and current must be sustained simultaneously during turn −off with the base to emitter junction reverse biased. The safe level is specified as a reverse biased safe operating area (Figure 29). This rating is verified under clamped conditions so that the device is never subjected to an avalanche mode.TYPICAL THERMAL RESPONSEFigure 31. Typical Thermal Response (Z q JC (t)) for BUL45D210.01t, TIME (ms)0.1r (t ), T R A N S I E N T T H E R M A L R E S I S T A N C E (N O R M A L I Z E D )分销商库存信息:ONSEMIBUL45D2G BUL45D2。

BXCB4545Datasheet7-14-09

BRIDGELUX BLUE POWER DIEBXCB 45 x 45 milPRODUCT DATA SHEET DS-C7The Bridgelux family of blue power die enables high performance and cost effective solutions to serve solid state lighting market. This next generation chip technology delivers improved efficiency and performance to enable increased light output for a variety of lighting, signaling and display applications.Features•High lumen output and efficiency•Long operating life•Increased current spreading traces for highly efficient and uniformillumination•100% Tested and sorted bywavelength, power and forwardvoltage•Lambertian emission pattern•Compatible with Solder paste,solder preform or silver epoxy dieattach•Delivered on medium tack blue tape (20cm±10mm ×20 cm±10mm) Applications•General Illumination•Street Lights•Portable Lighting•Architectural Lighting•Directional Lighting•Wide Area Lighting•Display Backlighting•Digital Camera Flash•Automotive Lighting•White LEDsLED Chip DiagramBXCB 45 x 45 milPart Numbering and Bin DefinitionsBridgelux LED chips are sorted into the brightness and dominant wavelength bins shown below at I f = 350 mA. Each blue tape contains die from only one brightness bin and one wavelength bin.Each blue tape contains chips with 0.2 V forward voltage bins: 3.0 - 3.2 V, 3.2 - 3.4 V and 3.4 - 3.6 V. The typical forward voltage is 3.4 V and the maximum forward voltage (V f max) = 3.6 V.Product NomenclatureB XC B 4 5 4 5 X X X – Y Y – ZWhere: BXCB: Designates product family4545: Designates die size (45 mil x 45 mil) XXX: Designates dominant wavelength bin YY: Designates radiometric power binZ:Designates forward voltage binDominant WavelengthPower Bin D1 (255 – 275 mW)Power Bin D2 (275 – 295 mW)Power Bin E1 (295 – 320 mW)445 to 447.5nm BXCB4545445-D1-z BXCB4545445-D2-z BXCB4545445-E1-z 447.5 to 450nm BXCB4545447-D1-z BXCB4545447-D2-z BXCB4545447-E1-z 450 to 452.5nm BXCB4545450-D1-z BXCB4545450-D2-z BXCB4545450-E1-z 452.5 to 455nm BXCB4545452-D1-z BXCB4545452-D2-z BXCB4545452-E1-z455 to 457.5nm BXCB4545455-D1-z BXCB4545455-D2-z BXCB4545455-E1-z 457.5 to 460nm BXCB4545457-D1-z BXCB4545457-D2-z BXCB4545457-E1-z 460 to 462.5nm BXCB4545460-D1-z BXCB4545460-D2-z BXCB4545460-E1-z 462.5 to 465nm BXCB4545462-D1-z BXCB4545462-D2-z BXCB4545462-E1-zBXCB 45 X 45 MILMechanical DimensionsAbsolute Maximum RatingsParameterSymbolMaximum RatingCondition DC Forward Current I f 700 mA 1T j = 125°CJunction Temperature T j 150°C Reverse Voltage V r -5 V T a = 25°C Reverse CurrentI r< 10 µAV r = -5 VAssembly Process Temperature 325°C for < 5 secondsStorage Conditions (chip on tape)60°C to +40°C ambient, RH < 65%Notes:1. Maximum drive current depends on junction temperature, die attach methods/materials, and lifetimerequirements of the application.2. Bridgelux LED chips are Class 1 ESD sensitive.3. The typical spectra half-width of the BXCB4545 blue power die is < 25 nm.4. Please consult the Bridgelux technical support team for information on how to optimize the light outputof our chips in your package.5. Brightness values are measured in an integrating sphere using gold plated TO39 headers withoutencapsulation.6. Tapes should be stored in a vertical orientation, not horizontally stacked. Stacking of tapes can placeexcessive pressure on the bond pads of the LED, resulting in reduced wire bonding strength.Environmental ComplianceBridgelux is committed to providing environmentally friendly products to the solid state lightingmarket. Bridgelux BXCB4545 blue power die are compliant to the European Union directives on the restriction of hazardous substances in electronic equipment, namely the RoHS directive. Bridgelux will not intentionally add the following restricted materials to BXCB4545 die products: lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) or polybrominated diphenyl ethers (PBDE).Chip Size 1143 +30/-10 µm × 1143 +30/-10 µm (45 mil x 45 mil)Chip Thickness 150 ± 10 µm (5.9 mil)Au Pad Thickness2.4 ± 0.2 µm Au Pad Diameter P Pad (2X): 100 µm N Pad (2X): 105 µmBRIDGELUX BLUE POWER DIEBXCB 45 x 45 milPerformance vs. CurrentThe following curves represent typical performance of the BXCB4545 blue power die. Actual performance will vary slightly for different power and dominant wavelength bins.Figure 1: Relative Luminous Intensity vs. Forward Current (device tested on a probe station)Figure 2: Forward Current vs. Forward Voltage (T j = 25°C)Performance vs. Junction TemperatureFigure 3: Forward Voltage vs. Junction TemperatureFigure 4: Relative Light Output vs. Junction TemperatureFigure 5: Wavelength Shift vs. Junction Temperature Typical Radiation PatternFigure 6: Typical Radiation Pattern (350 mA Operation)BXCB 45 x 45 milCurrent Derating CurvesFigure 7: Current Derating Curve vs. Ambient Temperature (derating based on T j max 150°C)About BridgeluxBridgelux is a leading developer and manufacturer of technologies and solutions transforming the $40 billion global lighting industry into a $100 billion market opportunity. Based in Livermore, California, Bridgelux is a pioneer in solid-state lighting (SSL), expanding the market for light-emitting diode (LED) technologies by driving down the cost of LED lighting systems. Bridgelux’s patented light source technology replaces traditional technologies (such as incandescent, halogen, fluorescent and high intensity discharge lighting) with integrated, solid-state lighting solutions that enable lamp and luminaire manufacturers to provide high performance and energy-efficient white light for the rapidly growing interior and exterior lighting markets, including street lights, commercial lighting and consumer applications. With more than 500 patent applications filed or granted worldwide, Bridgelux is the only vertically integrated LED manufacturer and developer of solid-state light sources that designs its solutions specifically for the lighting industry.© 2011 Bridgelux, Inc. All rights reserved. Product specifications are subject to change without notice.。

MJF44H11G;MJF45H11G;MJF44H11;MJF45H11;中文规格书,Datasheet资料

20 30 50 70 100

VCE, COLLECTOR-EMITTER VOLTAGE (VOLTS)

Figure 2. Maximum Rated Forward Bias Safe Operating Area

There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate IC − VCE limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

−

−

500

−

−

500

−

−

140

−

−

100

−

Unit Vdc mA mA Vdc Vdc

−

pF MHz

ns ns ns

r(t), TRANSIENT THERMAL RESISTANCE (NORMALIZED)

1.0 0.7 D = 0.5 0.5

0.3 0.2

0.2

0.1 0.1

0.07

0.05

0.05 0.02

MJF44H11 MJF45H11

Symbol VCEO(sus)

ICES IEBO VCE(sat) VBE(sat) hFE

W25Q128BVEIG;中文规格书,Datasheet资料

Publication Release Date: April 18, 20123V 128M-BITSERIAL FLASH MEMORY WITH DUAL AND QUAD SPITable of Contents1.GENERAL DESCRIPTION (5)2.FEATURES (5)3.PACKAGE TYPES AND PIN CONFIGURATIONS (6)3.1Pad Configuration WSON 8x6-mm (6)3.2Pad Description WSON 8x6-mm (6)3.3Pin Configuration SOIC 300-mil (7)3.4Pin Description SOIC 300-mil (7)3.5Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array) (8)3.6Ball Description TFBGA 8x6-mm (8)4.PIN DESCRIPTIONS (9)4.1Chip Select (/CS) (9)4.2Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3) (9)4.3Write Protect (/WP) (9)4.4HOLD (/HOLD) (9)4.5Serial Clock (CLK) (9)5.BLOCK DIAGRAM (10)6.FUNCTIONAL DESCRIPTIONS (11)6.1SPI OPERATIONS (11)6.1.1Standard SPI Instructions (11)6.1.2Dual SPI Instructions (11)6.1.3Quad SPI Instructions (11)6.1.4Hold Function (11)6.2WRITE PROTECTION (12)6.2.1Write Protect Features (12)7.STATUS REGISTERS AND INSTRUCTIONS (13)7.1STATUS REGISTERS (13)7.1.1BUSY Status (BUSY) (13)7.1.2Write Enable Latch Status (WEL) (13)7.1.3Block Protect Bits (BP2, BP1, BP0) (13)7.1.4Top/Bottom Block Protect Bit (TB) (13)7.1.5Sector/Block Protect Bit (SEC) (13)7.1.6Complement Protect Bit (CMP) (14)7.1.7Status Register Protect Bits (SRP1, SRP0) (14)7.1.8Erase/Program Suspend Status (SUS) (14)7.1.9Security Register Lock Bits (LB3, LB2, LB1) (14)7.1.10Quad Enable Bit (QE) (15)7.1.11Status Register Memory Protection (CMP = 0) (16)7.1.12 Status Register Memory Protection (CMP = 1) (17)Publication Release Date: April 18, 20127.2 INSTRUCTIONS (18)7.2.1 Manufacturer and Device Identification ................................................................................ 18 7.2.2 Instruction Set Table 1 (Erase, Program Instructions) .......................................................... 19 7.2.3 Instruction Set Table 2 (Read Instructions) .......................................................................... 20 7.2.4 Instruction Set Table 3 (ID, Security Instructions) ................................................................ 21 7.2.5 Write Enable (06h) ............................................................................................................... 22 7.2.6 Write Enable for Volatile Status Register (50h) .................................................................... 22 7.2.7 Write Disable (04h) ............................................................................................................... 23 7.2.8 Read Status Register-1 (05h) and Read Status Register-2 (35h) ........................................ 24 7.2.9 Write Status Register (01h) .................................................................................................. 24 7.2.10 Read Data (03h) ................................................................................................................. 26 7.2.11 Fast Read (0Bh) ................................................................................................................. 27 7.2.12 Fast Read Dual Output (3Bh) ............................................................................................. 28 7.2.13 Fast Read Quad Output (6Bh) ............................................................................................ 29 7.2.14 Fast Read Dual I/O (BBh) ................................................................................................... 30 7.2.15 Fast Read Quad I/O (EBh) ................................................................................................. 32 7.2.16 Word Read Quad I/O (E7h) ................................................................................................ 34 7.2.17 Octal Word Read Quad I/O (E3h) ....................................................................................... 36 7.2.18 Set Burst with Wrap (77h) .................................................................................................. 38 7.2.19 Continuous Read Mode Bits (M7-0) ................................................................................... 39 7.2.20 Continuous Read Mode Reset (FFh or FFFFh) .................................................................. 39 7.2.21 Page Program (02h) ........................................................................................................... 40 7.2.22 Quad Input Page Program (32h) ........................................................................................ 41 7.2.23 Sector Erase (20h) ............................................................................................................. 42 7.2.24 32KB Block Erase (52h) ..................................................................................................... 43 7.2.25 64KB Block Erase (D8h) ..................................................................................................... 44 7.2.26 Chip Erase (C7h / 60h) ....................................................................................................... 45 7.2.27 Erase / Program Suspend (75h) ......................................................................................... 46 7.2.28 Erase / Program Resume (7Ah) ......................................................................................... 47 7.2.29 Power-down (B9h) .............................................................................................................. 48 7.2.30 Release Power-down / Device ID (ABh) ............................................................................. 49 7.2.31 Read Manufacturer / Device ID (90h) ................................................................................. 51 7.2.32 Read Manufacturer / Device ID Dual I/O (92h) ................................................................... 52 7.2.33 Read Manufacturer / Device ID Quad I/O (94h) ................................................................. 53 7.2.34 Read Unique ID Number (4Bh)........................................................................................... 54 7.2.35 Read JEDEC ID (9Fh) ........................................................................................................ 55 7.2.36 Read SFDP Register (5Ah) ................................................................................................ 56 7.2.37 Erase Security Registers (44h) ........................................................................................... 57 7.2.38 Program Security Registers (42h) ...................................................................................... 58 7.2.39 Read Security Registers (48h) . (59)8.ELECTRICAL CHARACTERISTICS (60)8.1Absolute Maximum Ratings (60)8.2Operating Ranges (60)8.3Power-up Timing and Write Inhibit Threshold (61)8.4DC Electrical Characteristics (62)8.5AC Measurement Conditions (63)8.6AC Electrical Characteristics (64)8.7AC Electrical Characteristics (cont’d) (65)8.8Serial Output Timing (66)8.9Serial Input Timing (66)8.10HOLD Timing (66)8.11WP Timing (66)9.PACKAGE SPECIFICATION (67)9.18-Pad WSON 8x6-mm (Package Code E) (67)9.216-Pin SOIC 300-mil (Package Code F) (68)9.324-Ball TFBGA 8x6-mm (Package Code B, 5x5-1 Ball Array) (69)9.424-Ball TFBGA 8x6-mm (Package Code C, 6x4 Ball Array) (70)10.ORDERING INFORMATION (71)10.1Valid Part Numbers and Top Side Marking (72)11.REVISION HISTORY (73)Publication Release Date: April 18, 20121. GENERAL DESCRIPTIONThe W25Q128BV (128M-bit) Serial Flash memory provides a storage solution for systems with limited space, pins and power. The 25Q series offers flexibility and performance well beyond ordinary Serial Flash devices. They are ideal for code shadowing to RAM, executing code directly from Dual/Quad SPI (XIP) and storing voice, text and data. The device operates on a single 2.7V to 3.6V power supply with current consumption as low as 4mA active and 1µA for power-down.The W25Q128BV array is organized into 65,536 programmable pages of 256-bytes each. Up to 256 bytes can be programmed at a time. Pages can be erased in groups of 16 (4KB sector erase), groups of 128 (32KB block erase), groups of 256 (64KB block erase) or the entire chip (chip erase). The W25Q128BV has 4,096 erasable sectors and 256 erasable blocks respectively. The small 4KB sectors allow for greater flexibility in applications that require data and parameter storage. (See Figure 2.)The W25Q128BV supports the standard Serial Peripheral Interface (SPI), and a high performance Dual/Quad output as well as Dual/Quad I/O SPI: Serial Clock, Chip Select, Serial Data I/O0 (DI), I/O1 (DO), I/O2 (/WP), and I/O3 (/HOLD). SPI clock frequencies of up to 104MHz are supported allowing equivalent clock rates of 208MHz (104MHz x 2) for Dual Output and 280MHz (70MHz x 4) for Quad SPI when using the Fast Read Quad SPI instructions. These transfer rates can outperform standard Asynchronous 8 and 16-bit Parallel Flash memories. The Continuous Read Mode allows for efficient memory access with as few as 8-clocks of instruction-overhead to read a 24-bit address, allowing true XIP (execute in place) operation.A Hold pin, Write Protect pin and programmable write protection, with top, bottom or complement array control, provide further control flexibility. Additionally, the device supports JEDEC standard manufacturer and device identification with a 64-bit Unique Serial Number.2. FEATURES• Family of SpiFlash Memories – W25Q128BV: 128M-bit/16M-byte – 256-byte per programmable page– Standard SPI: CLK, /CS, DI, DO, /WP, /Hold– Dual SPI: CLK, /CS, IO 0, IO 1, /WP, /Hold– Quad SPI: CLK, /CS, IO 0, IO 1, IO 2, IO 3• Highest Performance Serial Flash– 104/70MHz Dual Output/Quad SPI clocks– 208/280MHz equivalent Dual /Quad SPI– 35MB/S continuous data transfer rate– Up to 5X that of ordinary Serial Flash– More than 100,000 erase/program cycles (1)– More than 20-year data retention• Efficient “Continuous Read Mode” – Low Instruction overhead– Continuous Read with 8/16/32/64-Byte Wrap – As few as 8 clocks to address memory – Allows true XIP (execute in place) operation – Outperforms X16 Parallel Flash • Low Power, Wide Temperature Range– Single 2.7 to 3.6V supply– 4mA active current, <1µA Power-down current – -40°C to +85/105°C operating range • Flexible Architecture with 4KB sectors– Uniform Sector/Block Erase (4K/32K/64K-Byte)– Program one to 256 bytes– Erase/Program Suspend & Resume• Advanced Security Features – Software and Hardware Write-Protect – Top/Bottom, 4KB complement array protection – Lock-Down and OTP array protection – 64-Bit Unique Serial Number for each device – Discoverable Parameters (SFDP) Register – 3X256-Byte Security Registers with OTP locks– Volatile & Non-volatile Status Register Bits• Space Efficient Packaging – 8-pad WSON 8x6-mm – 16-pin SOIC 300-mil – 24-ball TFBGA 8x6-mm– Contact Winbond for KGD and other options Note 1. More than 100k Block Erase/Program cycles for Industrial and Automotive temperature; more than 10k fullchip Erase/Program cycles tested in compliance with AEC-Q100.3.PACKAGE TYPES AND PIN CONFIGURATIONSW25Q128BV is offered in an 8-pad WSON 8x6-mm (package code E), a 16-pin SOIC 300-mil (package code F) and two 24-ball 8x6-mm TFBGAs (package code B, C) as shown in Figure 1a-c respectively. Package diagrams and dimensions are illustrated at the end of this datasheet.3.1Pad Configuration WSON 8x6-mmFigure 1a. W25Q128BV Pad Assignments, 8-pad WSON 8x6-mm (Package Code E)3.2Pad Description WSON 8x6-mmPAD NO. PAD NAME I/O FUNCTION1 /CS I Chip Select Input2 DO (IO1) I/O Data Output (Data Input Output 1)*1(IO2)I/O Write Protect Input ( Data Input Output 2)*23 /WP4 GND Ground5 DI (IO0) I/O Data Input (Data Input Output 0)*16 CLK I Serial Clock Input(IO3)I/O Hold Input (Data Input Output 3)*27 /HOLD8 VCC PowerSupply*1: IO0 and IO1 are used for Standard and Dual SPI instructions*2: IO0 – IO3 are used for Quad SPI instructionsPublication Release Date: April 18, 20123.3 Pin Configuration SOIC 300-milFigure 1b. W25Q128BV Pin Assignments, 16-pin SOIC 300-mil (Package Code F)3.4 Pin Description SOIC 300-milPIN NO.PIN NAMEI/OFUNCTION1 /HOLD (IO3)I/OHold Input (Data Input Output 3)*22 VCC Power Supply3 N/C No Connect4 N/C No Connect5 N/C No Connect6 N/C No Connect7 /CS I Chip Select Input8DO (IO1)I/O Data Output (Data Input Output 1)*19 /WP (IO2)I/OWrite Protect Input (Data Input Output 2)*210 GND Ground 11 N/C No Connect 12 N/C No Connect 13 N/C No Connect 14 N/C No Connect 15 DI (IO0) I/O Data Input (Data Input Output 0)*116CLKISerial Clock Input*1: IO0 and IO1 are used for Standard and Dual SPI instructions.*2: IO0 – IO3 are used for Quad SPI instructions, /WP or /HOLD functions are only available for Standard/Dual SPI.3.5Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array)Figure 1c. W25Q128BV Ball Assignments, 24-ball TFBGA 8x6-mm (Package Code B, C)3.6Ball Description TFBGA 8x6-mmBALL NO. PIN NAME I/O FUNCTIONB2 CLK I Serial Clock InputB3 GND GroundSupplyB4 VCC PowerC2 /CS I Chip Select Input(IO2)I/O Write Protect Input (Data Input Output 2)*2C4 /WPD2 DO (IO1) I/O Data Output (Data Input Output 1)*1D3 DI (IO0) I/O Data Input (Data Input Output 0)*1(IO3)I/O Hold Input (Data Input Output 3)*2D4 /HOLDMultiple NC NoConnect*1: IO0 and IO1 are used for Standard and Dual SPI instructions.*2: IO0 – IO3 are used for Quad SPI instructions, /WP or /HOLD functions are only available for Standard/Dual SPI.Publication Release Date: April 18, 20124. PIN DESCRIPTIONS4.1 Chip Select (/CS)The SPI Chip Select (/CS) pin enables and disables device operation. When /CS is high the device is deselected and the Serial Data Output (DO, or IO0, IO1, IO2, IO3) pins are at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal erase, program or write status register cycle is in progress. When /CS is brought low the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up, /CS must transition from high to low before a new instruction will be accepted. The /CS input must track the VCC supply level at power-up (see “Write Protection” and Figure 38). If needed a pull-up resister on /CS can be used to accomplish this.4.2 Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3)The W25Q128BV supports standard SPI, Dual SPI and Quad SPI operation. Standard SPI instructions use the unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the rising edge of the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to read data or status from the device on the falling edge of CLK.Dual and Quad SPI instructions use the bidirectional IO pins to serially write instructions, addresses or data to the device on the rising edge of CLK and read data or status from the device on the falling edge of CLK. Quad SPI instructions require the non-volatile Quad Enable bit (QE) in Status Register-2 to be set. When QE=1, the /WP pin becomes IO2 and /HOLD pin becomes IO3.4.3 Write Protect (/WP)The Write Protect (/WP) pin can be used to prevent the Status Register from being written. Used in conjunction with the Status Register’s Block Protect (CMP, SEC, TB, BP2, BP1 and BP0) bits and Status Register Protect (SRP) bits, a portion as small as a 4KB sector or the entire memory array can be hardware protected. The /WP pin is active low. When the QE bit of Status Register-2 is set for Quad I/O, the /WP pin function is not available since this pin is used for IO2. See Figure 1a-c for the pin configuration of Quad I/O operation.4.4 HOLD (/HOLD)The /HOLD pin allows the device to be paused while it is actively selected. When /HOLD is brought low, while /CS is low, the DO pin will be at high impedance and signals on the DI and CLK pins will be ignored (don’t care). When /HOLD is brought high, device operation can resume. The /HOLD function can be useful when multiple devices are sharing the same SPI signals. The /HOLD pin is active low. When the QE bit of Status Register-2 is set for Quad I/O, the /HOLD pin function is not available since this pin is used for IO3. See Figure 1a-c for the pin configuration of Quad I/O operation.4.5 Serial Clock (CLK)The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations. ("See SPI Operations")5.BLOCK DIAGRAM ArrayFigure 2. W25Q128BV Serial Flash Memory Block Diagram分销商库存信息: WINBONDW25Q128BVEIG。

BUL44;BUL44G;中文规格书,Datasheet资料

VCE, VOLTAGE (VOLTS)

1.0

0.01

0.1

1.0

10

IC, COLLECTOR CURRENT (AMPS)

Characteristic

Symbol

Min

OFF CHARACTERISTICS

Collector−Emitter Sustaining Voltage (IC = 100 mA, L = 25 mH)

Collector Cutoff Current (VCE = Rated VCEO, IB = 0)

400

ICEO

−

ICES

−

−

−

IEBO

−

ON CHARACTERISTICS

Base−Emitter Saturation Voltage (IC = 0.4 Adc, IB = 40 mAdc) (IC = 1.0 Adc, IB = 0.2 Adc)

Collector−Emitter Saturation Voltage (IC = 0.4 Adc, IB = 40 mAdc)

BUL44G

SWITCHMODEt NPN Bipolar Power Transistor

For Switching Power Supply Applications

The BUL44G have an applications specific state−of−the−art die designed for use in 220 V line operated Switchmode Power supplies and electronic light ballasts.

Features

D45H11;中文规格书,Datasheet资料

D45H11 — PNP Power Amplifier© 2012 Fairchild Semiconductor Corporation D45H11 Rev. A11June 2012D45H11PNP Power Amplifier•This device is designed for power amplifier, regulator and switching circuits where speed is important.•Sourced from process 5Q.Absolute Maximum RatingsElectrical Characteristics T a = 25°C unless otherwise notedThermal Characteristics T a = 25°C unless otherwise noted* Note) Device mounted on FR-$ PCB 36mm*18mm*1.5mm: Mounting pad for the collector lead min. 6cm2.SymbolParameterValueUnitsV CEO Collector-Emitter Voltage-80V I C Collector Current - Continuous-10A T J , T STGOperating and Storage Junction Temperature Range-55 to +150°CSymbolParameter Test Condition Min.Max.UnitsOff Characteristics V (BR)CEO Collector-Emitter Breakdown Voltage I C = -100mA, I B = 0-80V I CBO Collector-Cutoff Current V CB = -80V, I E = 0-10μA I EBO Emitter-Cutoff Current V EB = -5V, I C = 0-100μAOn Characteristics *h FE DC Current GainV CE = -1V, I C = -2A V CE = -1V, I C = -4A 6040V CE (sat)Collector-Emitter Saturation Voltage I C = -8A,I B = -0.4A -1.0V V BE (sat)Base-Emitter Saturation Voltage I C = -8A,I B = -0.8A -1.5V V BE (on)Base-Emitter On Voltage V CE = -2V, I C = -10mA -0.54-0.65V Small Signal Characteristicsf TCurrent Gain Bandwidth ProductI C = -500mA, V CE = -10V40MHZSymbolParameterMax.UnitsP D Total Device DissipationDerate above 25°C60480W mW/°C R θJC Thermal Resistance, Junction to Case 2.1°C/W R θJAThermal Resistance, Junction to Ambient62.5°C/W1TO-2201. Base2. Collector3. EmitterMark: D45H11The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is notAX-CAP¥*BitSiC¥Build it Now¥CorePLUS¥CorePOWER¥CROSSVOLT¥CTL¥Current Transfer Logic¥DEUXPEED®Dual Cool™ EcoSPARK®EfficientMax¥ESBC¥®Fairchild®Fairchild Semiconductor®FACT Quiet Series¥FACT®FAST®FastvCore¥FETBench¥FlashWriter®*FPS¥Global Power ResourceGreenBridge¥Green FPS¥Green FPS¥ e-Series¥G max¥GTO¥IntelliMAX¥ISOPLANAR¥Making Small Speakers Sound Louderand Better™MegaBuck¥MICROCOUPLER¥MicroFET¥MicroPak¥MicroPak2¥MillerDrive¥MotionMax¥Motion-SPM¥mWSaver¥OptoHiT¥OPTOLOGIC®OPTOPLANAR®®Programmable Active Droop¥QFET®QS¥Quiet Series¥RapidConfigure¥¥Saving our world, 1mW/W/kW at a time™SignalWise¥SmartMax¥SMART START¥Solutions for Your Success¥SPM®STEALTH¥SuperFET®SuperSOT¥-3SuperSOT¥-6SuperSOT¥-8SupreMOS®SyncFET¥Sync-Lock™®*The Power Franchise®TinyBoost¥TinyBuck¥TinyCalc¥TinyLogic®TINYOPTO¥TinyPower¥TinyPWM¥TinyWire¥TranSiC¥TriFault Detect¥TRUECURRENT®*P SerDes¥UHC®Ultra FRFET¥UniFET¥VCX¥VisualMax¥VoltagePlus¥XS™* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a)are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, , under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet Identification Product Status DefinitionAdvance Information Formative / In DesignDatasheet contains the design specifications for product development. Specifications may change分销商库存信息: FAIRCHILDD45H11。

EMC45DRYI中文资料(List Unclassifed)中文数据手册「EasyDatasheet - 矽搜」

106.68 109.22 121.92 124.46 129.54 149.86

B

+_ 0.20

12.70 15.24 17.78 20.32 22.86

27.94 33.02 35.56 40.64 45.72 48.26

50.80 53.34 58.42 60.96 66.04 68.58

.275 [6.98]

.225 [5.72]

字母b SIDE

0.016 [0.41]厚, 总体PLATED ONLY

.007 [0.18] THICK

EYELET (TE)

EYELET (RE)

FITS .043 [1.09]

直角

(RA)

.125 [3.18]

.185 [4.70]

.050 [1.27]

C = PPS /铍镍(咨询工厂) N = PEEK /铍铜(咨询工厂) W = PEEK /铍镍(咨询工厂)

F = PPS / Pfinodal ***(咨询工厂)

咨询工厂其他材料

触点表面涂层

接触面

Z = 0.000010"金 X = 0.000030"金 G = 0.000010"金奖 Y = 0.000030"金奖

5.275 5.575

5.475 5.775

6.275 6.575

ቤተ መጻሕፍቲ ባይዱ

E

+_.020

1.275 1.375 1.475 1.575 1.675

1.875 2.075 2.175 2.375 2.575 2.675

2.775 2.875 3.075 3.175 3.375 3.475

新世纪LED芯片45mil规格书

V.990105BCONTROLLEDDOCUMENTAPPROVAL SHEETProduct Type:Blue InGaN/ GaN LED DP5 (45X45) ChipsPart No: B4545ECD0Doc ID: MK-QA-010 Rev: E.Date : January 05, 2010Created By: Approved By:Heaven HsuO scar Chan Heaven HsuV.990105B 1.Scope:This specification applies to Blue InGaN/GaN LED chips,DP5(45X45) of Genesis Photonics Inc.。

And Includes the inspection of electro-optical characteristics。

2.Materials:2.1 P-contact:ITO。

2.2 P-pad:Au。

2.3 N-pad:Au。

3.Mechanical specifications :3.1 Chip size:1143×1143µm ( ± 10µm )。

3.2 P-pad:φ 110µm ( ± 10µm )。

3.3 N-pad:φ 110µm ( ± 10µm )。

3.4 Chip thickness:150µm ( ± 10µm )。

3.5 Chip diagramTop view Cross section4.Electro-optical characteristics and specification:4.1 Test condition:Parameter Symbol Condition UnitDominant wavelength Wd If = 350 mA nmLuminous intensity Iv If = 350 mA mWForward voltage Vf If = 350 mA VReverse current Ir Vr = - 5 V µAV.990105B4.2 Characteristics:Maximum Ratings at T a=25℃Symbol Conditions RatingsDC Forward Current I F T j=125℃700mAJunction Temperature T j150℃Reverse Voltage V r T a=25℃-5VReverse Current I r V r=-5V<2µAAssembly Process Temp. 325℃(<5sec)Notes:Maximum ratings were measured in an integrating sphere using Au plated TO-39 headers without an encapsulate, and may differ with different package types..4.3 Model No:Part No : A B C D E F G H IBin : 1 2 3 4 5 6 7 – 8 9Exp:Part No: B4545ECD0Bin : V33 P45A-294.3.1 Code A B C D E F G H I :Product code: A B C D E F G H IProduct code4.3.2 Code 1 2 3 :Vf range(V): 1 2 3V31 3.1~3.2 V32 3.2~3.3 V33 3.3~3.4 V34 3.4~3.54.3.3 Code 4 :Electrical spec: 4P Vf<3.5 ; Ir<2µAV.990105B4.3.4 Code 5 6 7 :Wd range(nm): 5 6 744B 442.5~445.0 45A 450.0~452.5 45D 457.5~460.044C 445.0~447.5 45B 452.5~455.0 46A 460.0~462.544D 447.5~450.0 45C 455.0~457.5 46B 462.5~465.04.3.5 Code 8 9 :Iv range (mW): 8 926 180~20027 200~22028 220~24029 240~26030 260~28031 280~300Lot No:L/N: A B C D E – F G H I J – K L MExp:L/N:61621-18183-0015.Bin description:Below is a table which defines the specific part numbers or “bins” which are within the B4545ECD0 kit. Each tape will contain chips from only one bin, and a customer order for kit B4545ECD0 will befulfilled with a shipment of production devices which may contain any combination of tapesconsisting of any or all bins in the table.Wd Grade Iv Grade45A -29 -30 -3145B -29 -30 -3145C -29 -30 -3145D -28 -29 -30 -3146A -28 -29 -30 -3146B -28 -2946C -27 -28 -2946D -27 -28V.990105B6. Packing specification :6.1 LED chips are placed on the blue adhesive tape with the bonding pads facing up (i.e. sapphireis adhered to the tape) and covered with a glossy paper (See Figure 6-1)6.2 Chip array must be placed within the center of the blue adhesive tape and the bar code label islocated on the back of the blue tape at the left lower corner (See Figure. 6-2).6.3 Label specification :MIN AVG MAX STD Vf (V) -- actual spec actual Iv (mW) spec actual spec actual Wd (nm) spec actual spec actual6.4 Packaging dimensions (See table 6-1)ItemDimensionBlue adhesive tape 200 mm × 200 mm (±10mm) Mesh curtain 70 mm × 70 mm (±10mm) Backing glossy paper 200 mm × 210 mm (±10mm) Label location on blue tapeLower left corner; 10 ± 2 mmFig 6-1 Chip on tapeFig 6-2 Location of labelTable 6-1 Package dimensionsV.990105B6.5 Packaging for shipment6.5.1 The sheet (blue adhesion tape +mesh curtain+ glossy paper) must be packed in ananti-electrostatic bag and paper box for shipment(See Fig 6-3)6.5.2 The max numbers of blue tapes in a bag is 20 pieces 6.5.3 The ESD attention label is stamped on bag6.5.4 Each box and each sheet should be labeled with information describing its content.BagShipping AddressPacking ListESD labelV.990105BCriteria of Defective Chip1. Inspection Equipment and Method Inspecting Chip by Microscope Magnification: 30X2. Figure of ExampleItemDefective itemCriteria of Defect ChipExample1 Active Area Broken Rejected2 Active Area Dirty (1)Dirty Area≥ 10% of Active Area3Active Layer Breakage and Scratched1. Breakage and scratch must not cross active layer2. Breakage and Scratch ≥ 10% of Active Layer4Pad DirtyDirty Area≥ 10% of Pad AreaV.990105BItem Defective item Criteria of Defect Chip Example5 Pad Scratched1.Scratched Area ≥ 20% of Pad Area2.Scratched Length ≥ 1/3 of Pad Diameter3.Exposed Sub-tract6 Remnant Metal1. Remnant Area≥ 10% of Active Area2. Remnant metal ≥ 3 Spots and Spot Length ≥ 20 μm3. Remnant metal over active area7 Defective Scribe1. Double Chips2. Scribed on active area or N-pad3. Racked or Chipped Area ≥ 10% of the Original Area4. Un-scribed Area≥ 110% of the Original Area9Wrong LabelRejected --10 Inverse Protective Paper Rejected-- 11 The Amount of ChipsAmount per Blue Tape ≥ 50 pcs--V.990105BDominant wavelength shift vs Forward currentRelative luminous intensity vs Forward currentV.990105B Led Chip View angle Measurement1.Package typeChip on TO-39 Without Cap2.Measurement ConditionMeasurement Distance: 100mmOperating Angle From -900 to 9003.ResultRelative Intensity vs. Off Axis Angle ( View Angle)50% Power Angle:122.5 degreeNotes:The above diagram is measured with the current at 200mA using Au plated To39 headers without an encapsulate.。

AT45DB321D-SU;AT45DB321D-SU-2.5;AT45DB321D-MU;AT45DB321D-TU;AT45DB321D-MWU;中文规格书,Datasheet资料

Figure 1-1. Pin configurations and pinouts.

MLF(1) (VDFN) Top View

SI 1 SCK 2 RESET 3

CS 4

8 SO 7 GND 6 VCC 5 WP

To allow for simple, in-system reprogrammability, the AT45DB321D does not require high input voltages for programming. The device operates from a single power supply, 2.7V to 3.6V, for both the program and read operations. The AT45DB321D is enabled through the chip select pin (CS) and accessed via a three-wire interface consisting of the serial input (SI), serial output (SO), and serial clock (SCK) lines.

Note:

TSOP package is not recommended for new designs. Future die shrinks will support 8-pin packages only.

/

Atmel AT45DB321D

2

3597Q–DFLASH–6/11

A NC NC NC NC

B NC SCK GND VCC NC

19665;中文规格书,Datasheet资料

Dual-Wire Dual-Operator Programmable Monitor DescriptionThe patented* Desco Dual-Wire Dual-OperatorProgrammable Monitor monitors two operators and two ESD work worksurfaces eliminating the need for periodic Figure 1. Desco 19665 Dual-Wire Dual-Operator Programmable MonitorFeatures and ComponentsTECHNICAL BULLETIN TB-3019Made in theUnited States of AmericaFigure 2. Dual-Wire Dual-Operator Programmable CBDE FG H I J K LFRONT VIEWBACK VIEWOperation1. Monitoring of the operators will remain in the STANDBY condition until a wrist cord is plugged into the operator remote. STANDBY mode is indicated by a blinking yellow operator LED.10mm snap needs to pierce and clinch bottom side of mat. Snap needs to be at least 12" apart or 72" max. 10mm snap needs to pierce and clinch bottom side of mat. Snap needs to be at least 12" apart or 72" max.OPERATOR 1WORKSURFACEOPERATOR 2WORKSURFACE10mm PUSH & CLINCH SNAP10mm PUSH & CLINCH SNAPBENCH GROUNDMAT 1 WIRING WHITE CABLEMAT 2 WIRING BLACK CABLEWRIST STRAP MONITORWRIST STRAP MONITORELECTRIC GROUNDOPERATOR 2REMOTE JACK BLACK CABLEOPERATOR 2REMOTE JACK WHITE CABLE Screw allows ground cord to be bolted to mat; keeps cord from disconnecting.Figure 3. Installing the Dual-Wire Dual-Operator Programmable MonitorororFigure 4. Connecting a dual-wire wrist strap to the operator remoteSETTING THE OPERATOR TEST VOLTAGE AND TEST LIMITThe Dual-Wire Dual-Operator Monitor’s operator test voltage and high test limit can be set to different values. The operator test voltage can be set to either +5V or +8V, and the operator high test limit can be set to either 10 megohms or 35 megohms. The default voltage is +8V, and the default operator high test limit is 10 megohms. These settings are controlled by a set of 3 switches located inside the monitor’s enclosure.NOTE: Desco recommends re-calibration of the monitor should either setting be changed. See the “Calibration” section for more information.To gain access to these switches, remove the monitor’s cover and position the monitor so the PCB matches the orientation shown in Figure 5. Switches SW1 and SW2 control the operator test voltage. Switch SW3 controls the operator high test limit.Operator Test Voltage+5VSW1 Position: RIGHTSW2 Position: LEFT+8VSW1 Position: LEFTSW2 Position: RIGHTOperator High Test Limit10 megohmsSW3 Position: RIGHT35 megohmsSW3 Position: LEFTCalibrationFrequency of recalibration should be based on the critical nature of those ESD sensitive items handled and the risk of failure for the ESD protective equipment and materials. In general, Desco recommends that calibration be performed annually.Use the EMIT 50524 Limit Comparator for Dual-Wire Monitors to perform periodic testing (once every 6-12 months) of the Dual-Wire Dual-Operator Programmable Monitor. The Limit Comparator can be used on the shop floor within a few minutes virtually eliminating downtime, verifying that the monitor is operating within tolerances. See TB-6542 for more information.Figure 5. Switches SW1, SW2 and SW3 inside the monitor’s enclosure Figure 6. EMIT 50524 Limit Comparator for Dual-Wire MonitorsNIST CalibrationDesco provides a basic, National Institute of Standardsand Technology (NIST) traceable calibration for theproducts that we manufacture. This is sometimesreferred to as a Level 1 calibration.For more on National Institute of Standards andTechnology see:/index.htmlFor more information on the calibration that Desco’sprovides for products that we manufacture see:/Calibration.aspxSpecificationsOperating Voltage 12 VDCOperating Temperature 32°F - 104°F (0 - 40°C)Monitor Dimensions 4.4" x 4.7" x 2.1"(11.2cm x 11.9cm x 5.3cm)Monitor Weight 1.1 lbs (0.5 kg)TEST VOLTAGESOperator +8 V** or +5 VWorksurface 200 mVTEST LIMITSOperator Low Fail: < 1.72 megohmsPass: 2 - 9 megohms**High Fail: > 11.5 megohms**orPass: 2 - 30 megohmsHigh Fail: > 40 megohmsWorksurface Pass: < 3.5 megohmsFail: > 3.8 megohms**DefaultFigure 7. Operator Remote dimensionsReplacement remotes are available as EMIT itemnumbers 50525 and 50526.分销商库存信息: DESCO19665。

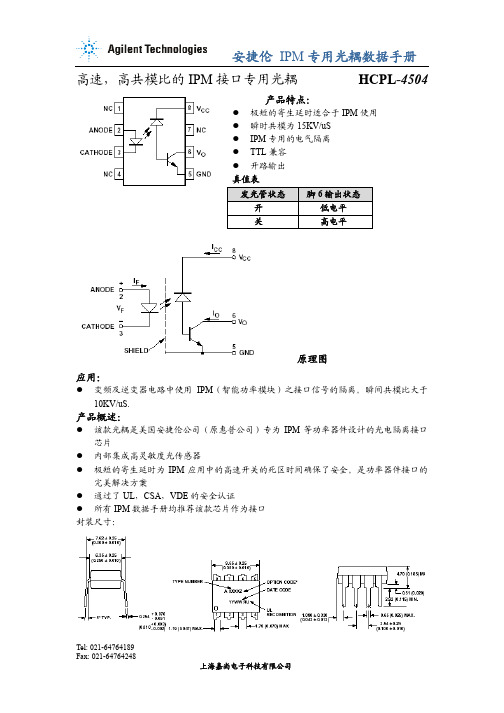

HCPL4504中文资料

高速,高共模比的IPM 接口专用光耦 HCPL-4504产品特点:极短的寄生延时适合于IPM 使用 瞬时共模为15KV/uS IPM 专用的电气隔离 TTL 兼容 开路输出 真值表原理图应用:变频及逆变器电路中使用IPM (智能功率模块)之接口信号的隔离。

瞬间共模比大于10KV/uS.产品概述:该款光耦是美国安捷伦公司(原惠普公司)专为IPM 等功率器件设计的光电隔离接口芯片内部集成高灵敏度光传感器极短的寄生延时为IPM 应用中的高速开关的死区时间确保了安全。

是功率器件接口的完美解决方案通过了UL ,CSA ,VDE 的安全认证所有IPM 数据手册均推荐该款芯片作为接口 封装尺寸:发光管状态脚6输出状态 开 低电平 关高电平最大额定值:参数符号最小值最大值单位储存温度 TS -55 125 ℃ 工作温度 TA -55 100 ℃ 正向输入电流 IF 25 mA 输入电流峰值@1mS IF1 50 mA 输入电流峰值<1uS IF2 1 A 输入信号电压(脚3-2) VR5V输入功率 PIN 45 mA 输出电流 IO 8 mA 输出峰值电流 IOF 16 mA 控制电压(脚8-5) Vcc0.530V输出电压(脚6-5) V o 0.5 20 V 输出功率 PO 100 mW电气特性:参数符号最小值 典型值最大值单位 测试条件电流传输比 CTR 25 32 60 % IF =16mA, Vcc = 4.5V 输出低电平时 VOL 0.2 0.4 V IF =16mA, Vcc = 4.5V , IO =4mA 输出高电平时 IOH 0.01 1 μA IF=0mA, Vcc=15V , IO=4mA低电平时电源 ICCL50 200 μAIF=16mA, Vcc=15V 高电平时电源 ICCH 0.02 1 μA IF=0mA, Vcc=15V 输入正向压降 VF 1.5 1.7 V IF =16mA 输入反向电压 BVR 5VIR =10uA输入电容 Cin 60 PF F =1MHZ, VF =0V 下降沿延时 TPHL 0.2 0.3 μS F=20K,If=16mA 上升沿延时 TPLH 0.3 0.5 μS F=20K,IF=16mA 隔离耐压 VISO 2500 V 1分钟@25C隔离电阻RIO 1012Ω评估电路:1. IF :输入电流信号,假设为16mA;2. V o:输出电压信号;3. tPHL, tPLH :输入输出之间的延时;4. RL 的选择建议在10K-20K之间;5. CL的选择建议在10pF-100pF之间;6. 建议在5与8脚之间加0.1uF去偶电容;7. 7脚和8脚需要短路连接;变频设计中的死区时间和寄生延时的说明:该款产品提供了一些规格来帮助工程师“最小化死区时间”,这就是“寄生延时”误差规格。

DSI45-12A;中文规格书,Datasheet资料

Tube

30

471895

Similar Part DSI45-16A DSI45-16AR DSI45-08A

Package TO-247AD (2) ISOPLUS247 (2) TO-247AD (2)

Voltage class 1600 1600 800

IXYS reserves the right to change limits, conditions and dimensions.

TVJ = 25°C TVJ = 25°C TVJ = 150°C TVJ = 25°C

TVJ = 150°C

TC = 130°C TVJ = 175°C

TC = 25°C TVJ = 45°C VR = 0 V TVJ = 150°C VR = 0 V TVJ = 45°C VR = 0 V TVJ = 150°C VR = 0 V TVJ = 25°C

Package:

● Housing: TO-247

●rIndustry standard outline ●rEpoxy meets UL 94V-0 ●rRoHS compliant

Symbol VRRM IR VF

IFAV VF0 rF RthJC TVJ Ptot IFSM

I 2t

CJ

Definition

20090529a

DSI45-12A

Ratings

Symbol IRMS RthCH Tstg Weight

Definition

RMS current thermal resistance case to heatsink storage temperature

Conditions per pin 1)

BD45465中文资料

ApplicationsVOLTAGE DETECTOR IC with counter timerBD45XXXG BD46XXXGBD45XXXG and BD46XXXG are series of high-accuracy detection voltage and low current consumption VOLTAGE DETECTOR ICs adopting CMOS process. New lineup of 156 types with delay time circuit have developed. Delay time is fixed in the IC due to the built-in counter timer to require no external capacitor. Total 156 types of VOLTAGE DETECTOR ICs including BD45XXXG series (Nch open drain output) and BD46XXXG series (CMOS output), each of which has 26 kinds in every 0.1V step (2.3~4.8V) and three kinds of delay time (50msec, 100msec, 200msec) have developed.Every kind of appliances with microcontroller and logic circuitFeatures1) Built-in delay time circuit(Fixed delay time by the built-in ±10% of high-accuracy counter timer)2) No external capacitor for setting delay time required 3) 3 kinds of delay time: 50msec (Typ.)(BD45XX5G,BD46XX5G) 100msec (Typ.)(BD45XX1G,BD46XX1G) 200msec (Typ.)(BD45XX2G,BD46XX2G)4) Detection voltage: 2.3V ~ 4.8V 0.1V step 5) High-accuracy detection voltage: ±1.0% 6) Ultra low current consumption: 0.85µA typ.7) Output circuit: Nch open drain (BD45XXXG) 8) Package: SSOP5(SMP5C2)9) Operating temperature range: -40°C ~ +105°C BD45XXXGBD46XXXGPin No.SSOP5ERSubGNDV OUTV DD12345 Application CircuitCMOS (BD46XXXG)Absolute Maximum Ratings (Ta=25˚C)Electrical characteristics (1 ˚C ˚C∗1 This value is guranteed at Ta=25˚C.Note) R L is not necessary for CMOS output type.Note) Please refer to the detection voltage of Line-up table.Characteristic diagram and Measurement circuitV DET ±0.5VΩV DET ±0.5VΩTa (°C)t P L H (m s e c )-Ta (°C)t P L H [µs e c ]-Output delay time "L → H"Output delay time "H → L"V DD (V)IDD(µA)V DD (V)VOUT(V)(mA)V DS (V)IOLTiming waveformV DDTa (˚C)VDET(V)VΩVΩVV DS (V)IDS(mA)V DDV DDV OUTERV DET0VVVVV DET+∆VI/O characteristic Detection voltagePart number and Marking of samplesBD45485BD45475BD45465BD45455BD45445BD45435BD45425BD45415BD45405BD45395BD45385BD45375BD45365BD45355BD45345BD45335BD45325BD45315BD45305BD45295BD45285BD45275BD45265BD45255BD45245T0T1T2T3T4T5T6T7T8T9TA TB TC TD TE TF TG TH TJ TK TL TM TN TP TQ TRTS TT TU TV TW TX TY TZ U0U1U2U3U4U5U6U7U8U9UA UB UC UD UE UF UG UHUJ UK UL UM UN UP UQ UR US UT UU UV UW UX UY UZ V0V1V2V3V4V5V6V7V8V94.8V 4.7V 4.6V 4.5V 4.4V 4.3V 4.2V 4.1V 4.0V 3.9V 3.8V 3.7V 3.6V 3.5V 3.4V 3.3V 3.2V 3.1V 3.0V 2.9V 2.8V 2.7V 2.6V 2.5V 2.4V 2.3VBD45235BD45481BD45471BD45461BD45451BD45441BD45431BD45421BD45411BD45401BD45391BD45381BD45371BD45361BD45351BD45341BD45331BD45321BD45311BD45301BD45291BD45281BD45271BD45261BD45251BD45241BD45231BD45482BD45472BD45462BD45452BD45442BD45432BD45422BD45412BD45402BD45392BD45382BD45372BD45362BD45352BD45342BD45332BD45322BD45312BD45302BD45292BD45282BD45272BD45262BD45252BD45242BD45232BD46485BD46475BD46465BD46455BD46445BD46435BD46425BD46415BD46405BD46395BD46385BD46375BD46365BD46355BD46345BD46335BD46325BD46315BD46305BD46295BD46285BD46275BD46265BD46255BD46245VA VB VC VD VE VF VG VH VJ VK VL VM VN VP VQ VR VS VT VU VV VW VX VY VZ W0W1W2W3W4W5W6W7W8W9WA WB WC WD WE WF WG WH WJ WK WL WM WN WP WQ WR WS WTWU WV WW WX WY WZ X0X1X2X3X4X5X6X7X8X9XA XB XC XD XE XF XG XH XJ XKBD46235BD46481BD46471BD46461BD46451BD46441BD46431BD46421BD46411BD46401BD46391BD46381BD46371BD46361BD46351BD46341BD46331BD46321BD46311BD46301BD46291BD46281BD46271BD46261BD46251BD46241BD46231BD46482BD46472BD46462BD46452BD46442BD46432BD46422BD46412BD46402BD46392BD46382BD46372BD46362BD46352BD46342BD46332BD46322BD46312BD46302BD46292BD46282BD46272BD46262BD46252BD46242BD46232(SMP5C2)Marking Voltage Part No.Marking Part No.Marking Part No.Marking Part No.Marking Part No.Marking Part No.Line-up。

SBR10U45SP5-13;中文规格书,Datasheet资料

Test Condition

IR = 0.3mA IF = 8A, TJ = 25ºC IF = 10A, TJ = 25ºC IF = 10A, TJ = 125ºC VR = 45V, TJ = 25ºC VR = 45V, TJ = 100ºC VR = 45V, TJ = 150ºC

SBR and PowerDI are registered trademarks of Diodes Incorporated.

3 of 5

10

100

1,000 10,000

TP, PULSE DURATION (µS)

Fig. 6 Maximum Avalanche Power

December 2010

© Diodes Incorporated

Package Outline Dimensions

SBR10U45SP5

10A SBR® SUPER BARRIER RECTIFIER

PowerDI®5

Mechanical Data

• Case: PowerDI®5 • Case Material: Molded Plastic, “Green” Molding Compound.

UL Flammability Classification Rating 94V-0 • Moisture Sensitivity: Level 1 per J-STD-020 • Terminals: Finish – Matte Tin annealed over Copper leadframe.

Unit ºC/W

ºC ºC

Electrical Characteristics @TA = 25°C unless otherwise specified

APT45GP120BG;中文规格书,Datasheet资料

050-7429 R e v C 6-2003APT45GP120B1200VThe POWER MOS 7® IGBT is a new generation of high voltage power ing Punch Through Technology this IGBT is ideal for many high frequency,high voltage switching applications and has been optimized for high frequency switchmode power supplies.•Low Conduction Loss •100 kHz operation @ 800V, 16A •Low Gate Charge•50 kHz operation @ 800V, 28A •Ultrafast Tail Current shutoff•RBSOA ratedPOWER MOS 7®IGBTAPT Website - /050-7429 R e v C 6-2003APT45GP120BDYNAMIC CHARACTERISTICSSymbol C ies C oes C res V GEP Q g Q ge Q gc RBSOA t d(on)t r t d(off)t f E on1E on2E off t d(on)t r t d(off)t f E on1E on2E off Test Conditions Capacitance V GE = 0V, V CE = 25Vf = 1 MHz Gate Charge V GE = 15V V CE = 600V I C = 45AT J = 150°C, R G = 5Ω, V GE =15V, L = 100µH,V CE = 960V Inductive Switching (25°C)V CC = 600VV GE = 15V I C = 45A R G = 5ΩT J = +25°CInductive Switching (125°C)V CC = 600VV GE = 15V I C = 45A R G = 5ΩT J = +125°C Characteristic Input Capacitance Output CapacitanceReverse Transfer Capacitance Gate-to-Emitter Plateau Voltage Total Gate Charge 3Gate-Emitter ChargeGate-Collector ("Miller") Charge Safe Operating Area Turn-on Delay Time Current Rise Time Turn-off Delay Time Current Fall TimeTurn-on Switching Energy 4Turn-on Switching Energy (Diode) 5Turn-off Switching Energy 6Turn-on Delay Time Current Rise Time Turn-off Delay Time Current Fall TimeTurn-on Switching Energy 4 4Turn-on Switching Energy (Diode) 55Turn-off Switching Energy 66MINTYPMAX3935300557.51852580170182910238900186990418291517990030782254UNITpFV nC A ns µJns µJUNIT °C/W gm MINTYPMAX.20N/A 5.9CharacteristicJunction to Case (IGBT)Junction to Case (DIODE)Package WeightSymbol R ΘJC R ΘJC W TTHERMAL AND MECHANICAL CHARACTERISTICS1Repetitive Rating: Pulse width limited by maximum junction temperature.2For Combi devices, I ces includes both IGBT and FRED leakages 3See MIL-STD-750 Method 3471.4E on1 is the clamped inductive turn-on-energy of the IGBT only, without the effect of a commutating diode reverse recovery currentadding to the IGBT turn-on loss. (See Figure 24.)5E on2 is the clamped inductive turn-on energy that includes a commutating diode reverse recovery current in the IGBT turn-on switching loss. (See Figures 21, 22.)6E off is the clamped inductive turn-off energy measured in accordance wtih JEDEC standard JESD24-1. (See Figures 21, 23.)7Continuous current limited by package lead temperature.APT Reserves the right to change, without notice, the specifications and information contained herein./050-7429 R e v C 6-2003APT45GP120BV CE , COLLECTER-TO-EMITTER VOLTAGE (V)V CE , COLLECTER-TO-EMITTER VOLTAGE (V)FIGURE 1, Output Characteristics(V = 15V)FIGURE 2, Output Characteristics (V= 10V)V GE , GATE-TO-EMITTER VOLTAGE (V) GATE CHARGE (nC)FIGURE 3, Transfer Characteristics FIGURE 4, Gate ChargeV GE , GATE-TO-EMITTER VOLTAGE (V)T J , Junction Temperature (°C)FIGURE 5, On State Voltage vs Gate-to- Emitter Voltage FIGURE 6, On State Voltage vs Junction Temperature T J , JUNCTION TEMPERATURE (°C)T C , CASE TEMPERATURE (°C)FIGURE 7, Breakdown Voltage vs. Junction TemperatureFIGURE 8, DC Collector Current vs Case Temperature B V C E S , C O L L E C T O R -T O -E M I T T E R B R E A K D O W N V C E , C O L L E C T O R -T O -E M I T T E R V O L T A G E (V )I C , C O L L E C T O R C U R R E N T (A )I C , C O L L E C T O R C U R R E N T (A )V O L T A G E (N O R M A L I Z E D )I C , D C C O L L E C T O R C U R R E N T (A )V C E , C O L L E C T O R -T O -E M I T T E R V O L T A G E (V )V G E , G A T E -T O -E M I T T E R V O L T A G E (V )I C , C O L L E C T O R C U R R E N T (A )-50-250255075100125-50-2502550751001251501.21.151.101.051.00.950.90.850.8160140120100806040200/050-7429 R e v C 6-2003I CE , COLLECTOR TO EMITTER CURRENT (A)I CE , COLLECTOR TO EMITTER CURRENT (A)FIGURE 9, Turn-On Delay Time vs Collector Current FIGURE 10, Turn-Off Delay Time vs Collector Current CE I CE , COLLECTOR TO EMITTER CURRENT (A)FIGURE 11, Current Rise Time vs Collector Current FIGURE 12, Current Fall Time vs Collector Current I CE , COLLECTOR TO EMITTER CURRENT (A)FIGURE 13, Turn-On Energy Loss vs Collector Current R G , GATE RESISTANCE (OHMS)T J , JUNCTION TEMPERATURE (°C)FIGURE 15, Switching Energy Losses vs. Gate Resistance FIGURE 16, Switching Energy Losses vs Junction TemperatureS W I T C H I N G E N E R G Y L O S S E S (µJ )E O N 2, T U R N O N E N E R G Y L O S S (µJ )t r , R I S E T I M E (n s )t d (O N ), T U R N -O N D E L A Y T I M E (n s )S W I T C H I N G E N E R G Y L O S S E S (µJ )E OF F , T U R N O F F E N E RG Y L O S S (µJ )t f , F A L L T I M E (n s )t d (O F F ), T U R N -O F F D E L A Y T I M E (n s )1200100016014012010080604020060005000400030002000100080007000600050004000300020001000/050-7429 R e v C 6-20030.250.200.150.100.050Z θJ C , T H E R M A L I M P E D A NC E (°C /W )RECTANGULAR PULSE DURATION (SECONDS)Figure 19A, Maximum Effective Transient Thermal Impedance, Junction-To-Case vs Pulse Duration5,0001,000500100501016014012010080604020C , C A P A C I T A N C E (PF )I C , C O L L E C T O R C U R R E N T (A )F M A X , O P E R A T I NG F R E Q U E N C Y (kH z )V CE , COLLECTOR-TO-EMITTER VOLTAGE (VOLTS)V CE , COLLECTOR TO EMITTER VOLTAGEFigure 17, Capacitance vs Collector-To-Emitter VoltageFigure 18, Minimim Switching Safe Operating Area01002003004005006007008009001000 I C , COLLECTOR CURRENT (A)Figure 20, Operating Frequency vs Collector Currentmax max1max 2max1d(on)r d(off )fdiss cond max 2on2offJ C diss JCF min(f ,f )0.05f t t t t P P f E E T T P R θ==+++−=+−=FIGURE 19B, TRANSIENT THERMAL IMPEDANCE MODEL0.007820.01500.185temp. (RC MODEL/050-7429 R e v C 6-2003APT45GP120BT0-247 Package OutlineDimensions in Millimeters and (Inches)Figure 22, Turn-on Switching Waveforms and DefinitionsFigure 23, Turn-off Switching Waveforms and DefinitionsFigure 24, E ON1Test CircuitGate VoltageCollector VoltageCollector Current90%Switching EnergyT J = 125 C90%t d(off)t f10%10%t d(on)5%10%90%t r5 %Collector CurrentCollector VoltageGate VoltageSwitching EnergyT = 125 CAPT’s products are covered by one or more of U.S.patents 4,895,810 5,045,903 5,089,434 5,182,234 5,019,5225,262,336 6,503,786 5,256,583 4,748,103 5,283,202 5,231,474 5,434,095 5,528,058 and foreign patents. US and Foreign patents pending. All Rights Reserved.V /分销商库存信息: MICROSEMIAPT45GP120BG。

OP705A;OP705B;OP705C;OP705D;中文规格书,Datasheet资料

Fea t ures •Narrow receiving angle •Variety of sensitivity ranges •T-1 package style•Small package size for space limited applications•Base-emitter resistor provides ambient light protectionDe s crip t ionThe OP705 series devices consist of NPN silicon phototransistors molded in blue tinted epoxy packages. The narrow receiving angle provides excellent on-axis coupling. These devices are 100%production tested using infrared light for close correlation with Optek’s GaAs and GaAlAs emitters.The phototransistor has an internal base-emitter resistor which provides protection from low level ambient lightingconditions. This feature is also useful when the media being detected is semi-transparent to infrared light in interruptive applications.Ab so lute Maxi mum Rat ings (T A = 25o C un less oth er wise noted)Collector- E mitter V olt a ge............................................ 30 V Emit ter Re verse Current........................................... 10 mA Col lec tor DC Cur rent ............................................. 30 mA Stor age and Op er at ing Tem pera ture Range.................. -40o C to +100o C Lead Sol der ing Tem pera ture [1/16 inch (1.6 mm) from case for 5 sec. with sol der ing iron]........................................................ 260o C (1)Power D is s i p a t ion ............................................ 100 mW (2)NOTES:(1) RMA flux is recommended. Duration can be extended to 10 sec. max. when flow soldering.Max. 20 grams force may be applied to leads when soldering.(2) Derate linearly 1.33 mW/o C above 25o C.(3) Light source is an unfiltered GaAs LED with a peak emission wavelength of 935 nm and aradiometric intensity level which varies less than 10% over the entire lens surface of the phototransistor being tested.(4) The knee point irradiance is defined as the irradiance required to increase I C(ON) to 50 µA.Typi cal Per form ance CurvesProd uct Bul le tin OP705A March 1999NPN Pho t o t ran s is tor with Base-Emit t er Resistor Types OP705A, OP705B, OP705C, OP705DOp tek Tech nol ogy, Inc. 1215 W. Crosby Road Car roll ton, Texas 75006 (972)323- 2200 Fax (972)323-2396Typi cal Spec tral Re sponseWave length - nmSche maticTypes OP705A, OP705B, OP705C, OP705DOp tek re serves the right to make changes at any time in or der to im prove de sign and to sup ply the best prod uct pos si ble.Op tek Tech nol ogy, Inc. 1215 W. Crosby Road Car roll ton, Texas 75006 (972)323- 2200 Fax (972)323-2396Elec t ri c al C har a c t er i s t ics (T A = 25o C un less oth er wise noted)Typi cal Per form ance CurvesOn-State Collector Currentvs. IrradianceNormalized Collector Currentθ - Angular Displacement - Deg.Normalized Light and Dark Current vs. Ambient TemperatureT A - Ambient Temperature - ° C Dark CurrentNor mal ized Out putvs. Fre quencyFrequency - KHzTypical Rise and Fall Timevs. Load ResistanceR L - Load Resistance - K ΩSwitching Time Test CircuitTest Conditions:Light source is pulsed LED with, t r and t f ≤ 500 ns.I F is adjusted for V OUT = 1 Volt.Light Currente分销商库存信息:OPTEK-TECHNOLOGYOP705A OP705B OP705C OP705D。

PHTX-45 产品说明书

Figure 1-1 PHTX-45 ConfigurationsFigure 1-2 Specifications - ViewsFigure 2-1 Multi-Purpose Bracket Figure 2-2 PHTX-45 Mounting ConfigurationsFigure 2-3 2-Wire Integral Mount Detail Figure 2-4 2-Wire Panel Mount and Cut-outFigure 2-5 115/230 VAC Panel Mount and Cut-outVoltage between Terminals 9 and 10 MUST be between 16 and 35 VDC.Earth ground into Terminal 12 is HIGHLY recommended. This connection can greatly improve stability in electrically noisy environments.Figure 3-1 Loop Power Connection, Omega PHE-45P Sensor and PHTX-45 TransmitterFigure 3-2 Line Power ConnectionThe power strip, TB1, allows up to 14 AWG wire. A wire gauge of 16 AWG is recommended to allow for an easy pass-through into the PG-9 ports when wiring.Figure 3-3 Line Power w/ Relays ConnectionAlso in the line-power w/ relays configuration, a special cable is connected under the power supply that runs to the AUX connector on the main part of the instrument. The cable is retained by a clip mounted under the AUX connector on the shield. Under the power supply, the black wire in the cable should be facing PIN 2. On the AUX connector, the white wire should be in the upper left corner (see Figure 3-4 for further details).Figure 3-4 Relay Cable ConnectionFigure 3-5 Relay ContactsIn the battery-powered version, the instrument is converted toa display-only portable unit. The battery option card cannot be used with any other option cards. All of thenormal software functions are active in the portable unit. In addition, there are several unique hardware featureswhich are described in detail here.3.5 Battery-Powered (Portable)Configuration Note: Do not attempt to connect external DC or ACpower supplies to the portable unit or severePHTX-45 TRANSMITTER DC BATTERY BOARD Figure 3-6 DC Battery Board ConnectionFigure 4-1 Bulkhead ConnectionIf the instrument is ordered with the Relay Option Board installed, the enclosure includes three PG-11 cord grips to allow for the additional wiring going into the enclosure.Figure 4-2 Sensor Cable Connections, Omega PHE-45PNote: Only the custom 6-wire shielded interconnect cable attached to the sensor must be usedwhen connecting the Model PHE-45P sensor tothe instrument. This high-performance, doubleshielded, polyethylene jacketed cable is speciallydesigned to provide the proper signal shieldingfor the sensor used in this system. No substitu-Figure 4-3 Sensor Connections, Combination ElectrodesFigure 4-4 External Temperature Compensators*When utilizing the 3-wire RTD connection, a wire jumpermust be made between the yellow and blue wires in thejunction box as shown. The blue wire on the connectingsensor cable must be attached to Terminal 6 in thePHTX-45 Transmitter as shown. In addition, a jumperon the scaling board must also be removed. Refer toPage 36 for further details.Connecting sensor cable lengths can be up to 400 feetwith a 2-wire RTD connection, and up to 3,000 feet with a3-wire RTD connection.When utilizing the junction box connection, the blue wireon the connecting sensor cable must be attached toTerminal 6 on the PHTX-45 Transmitter, as above. How-ever, the blue wire on the PHE-45P Sensor cable is notused.Use ONLY the provided sensor interconnect cable betweenthe transmitter and the junction box.Figure 4-5 Junction Box Connection and Three-Wire RTD Connection(Display shown with all segments ON) Figure 5-1 User InterfaceThe icon area contains display icons that assist the user in set-up and indicate important states of system functions. The CAL, CONFIG, and DIAG icons are used to tell the user what branch of the software tree the user is in while scrolling through the menu items. This improves software map navigation dramatically. Upon entry into a menu, the title is displayed (such as CAL), and then the title disappears to make way for the actual menu item. However, the icon The HOLD icon indicates that the current output of the in-strument has been put into output hold. In this case, the output is locked to the last input value measured when the HOLD function was entered. HOLD values are retained even if the unit power is cycled.The FAIL icon indicates that the system diagnostic function has detected a problem that requires immediateThe software of the PHTX-45 is organized in an easy to follow menu-based system. All user settings are organ-ized under four menu sections: Measure, Calibration ], Configuration [CONFIG], and Diagnostics [The default Measure Menu is display-only and has no。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VCE(sat) VCE(sat) hFE

Vdc Vdc --

Dynamic Saturation Voltage: Determined 1.0 ms and 3.0 ms respectively after rising IB1 reaches 90% of final IB1 (see Figure 18)

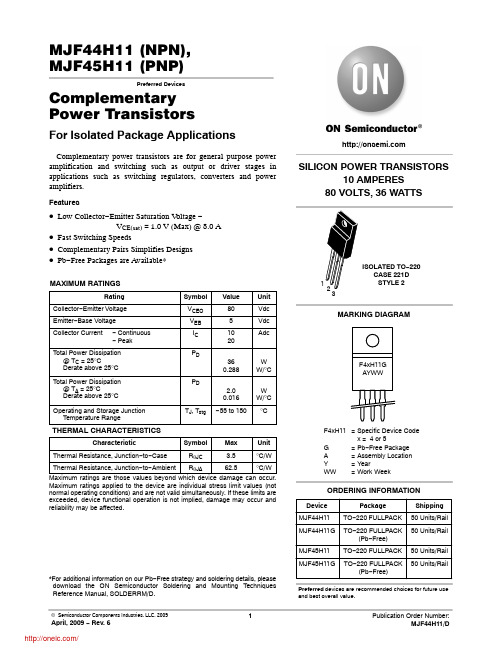

Characteristic OFF CHARACTERISTICS Collector--Emitter Sustaining Voltage (IC = 100 mA, L = 25 mH) Collector Cutoff Current (VCE = Rated VCEO, IB = 0) Collector Cutoff Current (VCE = Rated VCES, VEB = 0) (TC = 125C) Emitter Cutoff Current (VEB = 9.0 Vdc, IC = 0) ON CHARACTERISTICS Base--Emitter Saturation Voltage (IC = 1.0 Adc, IB = 0.2 Adc) (IC = 2.0 Adc, IB = 0.4 Adc) Collector--Emitter Saturation Voltage (IC = 1.0 Adc, IB = 0.2 Adc) (TC = 125C) Collector--Emitter Saturation Voltage (IC = 2.0 Adc, IB = 0.4 Adc) (TC = 125C) DC Current Gain (IC = 0.3 Adc, VCE = 5.0 Vdc) (IC = 2.0 Adc, VCE = 1.0 Vdc) (IC = 10 mAdc, VCE = 5.0 Vdc) DYNAMIC CHARACTERISTICS Current Gain Bandwidth (IC = 0.5 Adc, VCE = 10 Vdc, f = 1.0 MHz) Output Capacitance (VCB = 10 Vdc, IE = 0, f = 1.0 MHz) Input Capacitance (VEB = 8.0 Vdc) (IC = 1.0 Adc IB1 = 100 mAdc VCC = 300 V) (IC = 2.0 Adc IB1 = 400 mAdc VCC = 300 V) 1.0 ms 3.0 ms 1.0 ms 3.0 ms (TC = 125C) (TC = 125C) (TC = 125C) (TC = 125C) ton toff VCE (Dyn sat) fT Cob Cib ---------------70 -2.6 ------------12 50 920 1.75 4.4 0.5 1.0 1.85 6.0 0.5 1.0 75 120 2.8 3.5 -200 -4.2 230 400 110 100 1.1 1.5 170 170 80 0.6 175 — 75 1200 --------110 -3.5 -170 -3.8 -350 -150 -1.7 -250 -120 0.9 300 ns ms MHz pF pF (TC = 125C) (TC = 125C) VBE(sat) ------14 -7.0 5.0 10 0.84 0.89 0.175 0.150 0.25 0.275 -32 14 12 22 1.2 1.25 0.25 -0.4 -34 ----Vdc VCEO(sus) ICEO ICES IEBO 400 ----------100 10 100 100 Vdc mAdc mAdc mAdc Symbol Min Typ Max Unit

TJ = 25C VCE , VOLTAGE (VOLTS)

VCE , VOLTAGE (VOLTS)

1.5 1 A 1.5 2 A A 3A 4A 5A 6A

1.0

1.0

0.1

IC/IB = 10 IC/IB = 5 TJ = 25C TJ = 125C 0.10 1.00 10.00

0.5 IC = 0.5 A 0 0.01

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. 1. Pulse Test: Pulse Width = 5 ms, Duty Cycle 10%.

1 0.01

0.10

1.00

10.00

1 0.01

0.10

1.00

10.00

IC, COLLECTOR CURRENT (AMPS)

IC, COLLECTOR CURRENT (AMPS)

Figure 1. DC Current Gain @ 1 Volt

2.0 10

Figure 2. DC Current Gain at @ 5 Volts

Features

Improved Efficiency Due to:

Low Base Drive Requirements (High and Flat DC Current Gain hFE) Low Power Losses (On-State and Switching Operations) Fast Switching: tfi = 100 ns (typ) and tsi = 3.2 ms (typ) @ IC = 2.0 A, IB1 = IB2 = 0.4 A Full Characterization at 125C Tight Parametric Distributions Consistent Lot--to--Lot These Devices are Pb--Free and are RoHS Compliant*

BUL45G NPN Silicon Power Transistor

High Voltage SWITCHMODE Series

Designed for use in electronic ballast (light ballast) and in SWITCHMODE Power supplies up to 50 W.

MAXIMUM RATINGS

Rating Collector--Emitter Sustaining Voltage Collector--Base Breakdown Voltage Emitter--Base Voltage Collector Current Base Current Total Device Dissipation @ TC = 25_C Derate above 25C Operating and Storage Temperature -- Continuous -- Peak (Note 1) Symbol VCEO VCES VEBO IC ICM IB PD TJ, Tstg Value 400 700 9.0 5.0 10 2.0 75 0.6 --65 to 150 Unit Vdc Vdc Vdc Adc Adc W W/_C _C

ORDERING INFORMATION

Device BUL45G Package TO--220 (Pb--Free) Shipping 50 Units / Rail

*For additional information on our Pb--Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Vdc

SWITCHING CHARACTERISTICS: Resistive Load Turn--On Time Turn--Off Time (IC = 2.0 Adc, IB1 = IB2 = 0.4 Adc Pulse Width = 20 ms, (TC = 125C) Duty Cycle < 20% VCC = 300 V (TC = 125C) (IC = 2.0 Adc, IB1 = 0.4 Adc IB2 = 0.4 Adc)

SWITCHING CHARACTERISTICS: Inductive Load (VCC = 15 Vdc, LC = 200 mH, Vclamp = 300 Vdc) Fall Time Storage Time Crossover Time Fall Time Storage Time Crossover Time Fall Time Storage Time Crossover Time (TC = 125C) (TC = 125C) (TC = 125C) (IC = 1.0 Adc, IB1 = 100 mAdc (TC = 125C) IB2 = 0.5 Adc) (TC = 125C) (TC = 125C) (IC = 2.0 Adc, IB1 = 250 mAdc (TC = 125C) IB2 = 2.0 Adc) (TC = 125C) (TC = 125C) tfi tsi tc tfi tsi tc tfi tsi tc ns ms ns ns ms ns ns ms ns

2

/

BUL45G