4214RM中文资料

UNR4214资料

104

IO VIN

VO = 5 V Ta = 25°C

VIN IO

100 VO = 0.2 V Ta = 25°C

5

Output current IO (µA)

4

3

102

Input voltage VIN (V)

103

10

1

2

10

0.1

Characteristics charts of UNR4210 IC VCE

Ta = 25°C

VCE(sat) IC

Collector-emitter saturation voltage VCE(sat) (V)

100 IC / IB = 10 400

hFE IC

VCE = 10 V

1

0 0.1

1

10

100

1 0.4

0.6

0.8

1.0

1.2

1.4

0.01 0.1

1

10

100

Collector-base voltage VCB (V)

Input voltage VIN (V)

Output current IO (mA)

元器件交易网

Transistors with built-in Resistor

UNR421x Series (UN421x Series)

Silicon NPN epitaxial planar type

Unit: mm

For digital circuits ■ Fea9 mA 0.8 mA

Forward current transfer ratio hFE

fluke中文使用手册421

MAX4211AETE中文资料

4V TO 28V

+ -

+ -

25:1

IOUT POUT

1.21V REFERENCE INHIBIT

REF

CIN1+

COUT1 CIN1LE CIN2+ COUT2

µMAX is a registered trademark of Maxim Integrated Products, Inc. Pin Configurations and Selector Guide appear at end of data sheet.

MAX4211A MAX4211B MAX4211C GND

CIN2-

Functional Diagrams continued at end of data sheet. ________________________________________________________________ Maxim Integrated Products 1

Functional Diagrams

+

VSENSE RSENSE LOAD RS+ VCC 2.7V TO 5.5V RS-

-

Applications

Overpower Circuit Breakers Smart Battery Packs/Chargers Smart Peripheral Control Short-Circuit Protection Power-Supply Displays Measurement Instrumentation Baseband Analog Multipliers VGA Circuits Power-Level Detectors

油气非金属管道检验批表格SY4214-2017

非金属管道工程施工质量控制资料

管道下料与加工检验批质量验收记录

(SY4214-2017)

热塑性塑料管道安装检验批质量验收记录

(SY4214-2017)

高压玻璃纤维管道安装检验批质量验收记录

(SY4214-2017)

塑料合金防腐蚀复合管道安装检验批质量验收记录

(SY4214-2017)

钢骨架聚乙烯塑料复合管道安装检验批质量验收记录

(SY4214-2017)

钢骨架增强塑料复合连续管道和柔性复合高压输送管道安装检验批质量验收记录

(SY4214-2017)

站内工艺管道安装检验批质量验收记录

(SY4214-2017)

管道支吊架及附件安装检验批质量验收记录

(SY4214-2017)

(SY4214-2017)

(SY4214-2017)

管道保温补口检验批质量验收记录

(SY4214-2017)

管沟开挖检验批质量验收记录

(SY4214-2017)

(SY4214-2017)

(SY4214-2017)。

rm中文简介

概观所述PmodTMP2是温度传感器和围绕建成恒温控制板ADI公司ADT7420。

其特点包括:•高达16-bit分辨率•典型精度优于0.25°C•有4种可选I2C接口地址•240毫秒连续转换时间•支持3.3V和5V接口•无需校准•可编程过温/欠温控制引脚。

功能说明该PmodTMP2使用8针连接器允许通过I2C通信,并提供了引脚以菊花链的PmodTMP2其他I2C设备。

该PmodTMP2还提供了两个2-排针用于选择的I2C地址芯片和两个2针接头,用于控制基于温度的外部设备通过在软件的用户定义的阈值。

I2C接口该PmodTMP2的板载芯片ADT7420行为由于采用了业界标准的从设备I2C通信方案。

沟通与PmodTMP2设备的I2C 主机设备必须指定一个从地址(0x48-0x4B)和一个标志,表示该通信是读(1)或写(0)。

此后面是实际的数据传输。

为了ADT7420,数据传送应当包括所需的设备寄存器的地址接着要写入的数据指定寄存器。

从寄存器读取的主机必须写入所需的寄存器地址到ADT7420,然后发送一个I2C启动条件,并发送一个新的读请求ADT7420。

如果主人不产生启动条件试图读之前,然后将值写入到地址寄存器将被复位到00H。

正如一些寄存器存储16位值作为8位注册对,ADT7420将自动递增的设备的地址寄存器访问特定的寄存器,如当温度寄存器和阈值寄存器。

这允许主机使用单个的读或写的请求同时访问低字节和高字节,这些寄存器。

一个寄存器和他们的行为的完整列表可以在ADT7420数据手册中找到可在ADI公司网站。

正如一些寄存器存储16位值作为8位注册对,ADT7420将自动递增的设备的地址寄存器访问特定的寄存器,如当温度寄存器和阈值寄存器。

这允许主机使用单个的或写的请求同时访问低字节和高字节,这些寄存器。

一个寄存器和他们的行为的完整列表可以在ADT7420数据手册中找到可在ADI公司网站。

I2C接口标准使用两个信号线。

Leica RM 2245-中文版

是我们在该领域中进行的调查研究所理解和掌

徕卡保留在没有事先通知的情况下改变技

ห้องสมุดไป่ตู้

握的。

术规范和生产流程的权力。只有这样才能不断

我们没有义务根据当前的最新的技术发展 地改进我们产品中所采用的技术和制造工艺。

状况来定期更新该手册,并且为客户提供本手

该文档受版权法的保护。该文档的所有版

册的额外副本或更新材料等。

是,不对因遵守本手册中的叙述或其他信息所 中的文字和图表进行复制的行为都必须事先获

MAX4214中文资料

MAX4214/MAX4215/MAX4217/MAX4219/MAX4222

_______________Ordering Information

PART TEMP. RANGE PINPACKAGE 5 SOT23-5 8 SO 8 µMAX 8 SO 8 µMAX 14 SO 16 QSOP 14 SO 16 QSOP SOT TOP MARK ABAH — — — — — — — —

Supply Voltage (VCC to VEE) ..................................................12V IN_-, IN_+, OUT_, EN_ ....................(VEE - 0.3V) to (VCC + 0.3V) Output Short-Circuit Duration to VCC or VEE ..............Continuous Continuous Power Dissipation (TA = +70°C) 5-pin SOT23 (derate 7.1mW/°C above +70°C).............571mW 8-pin SO (derate 5.9mW/°C above +70°C)...................471mW 8-pin µMAX (derate 4.1mW/°C above +70°C) .............330mW 14-pin SO (derate 8.3mW/°C above +70°C)................667mW 16-pin QSOP (derate 8.3mW/°C above +70°C)...........667mW Operating Temperature Range ...........................-40°C to +85°C Storage Temperature Range .............................-65°C to +150°C Lead Temperature (soldering, 10sec) .............................+300°C

MC-4R512FKE6D-840资料

GND LDQA8 GND LDQA6 GND LDQA4 GND LDQA2 GND LDQA0 GND LCTMN GND LCTM GND NC GND LROW1 GND LCOL4 GND LCOL2 GND LCOL0 GND LDQB1 GND LDQB3 GND LDQB5 GND LDQB7 GND LSCK VCMOS SOUT VCMOS NC GND NC VDD VDD NC NC NC NC

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 A32 A33 A34 A35 A36 A37 A38 A39 A40 A41 A42 A43 A44 A45 A46

NC NC NC NC VREF GND SA0 VDD SA1 SVDD SA2 VDD RCMD GND RDQB8 GND RDQB6 GND RDQB4 GND RDQB2 GND RDQB0 GND RCOL1 GND RCOL3 GND RROW0 GND RROW2 GND NC GND RCFMN GND RCFM GND RDQA1 GND RDQA3 GND RDQA5 GND RDQA7 GND

NC NC NC NC VREF GND SCL VDD SDA SVDD SWP VDD RSCK GND RDQB7 GND RDQB5 GND RDQB3 GND RDQB1 GND RCOL0 GND RCOL2 GND RCOL4 GND RROW1 GND NC GND RCTM GND RCTMN GND RDQA0 GND RDQA2 GND RDQA4 GND RDQA6 GND RDQA8 GND

CS44210资料

The CS44210 architecture uses a direct-to-digital approach that maintains digital signal integrity to the final output filter. This minimizes analog interference effects that can negatively affect system performance.

RM6204中文规格书资料

英寸 典型值

0.130 0.060 0.018 0.365 0.300 0.250 0.100 0.130 0.355

7°

最大值

0.210

0.135

0.400

0.255

0.150 0.375 15°

2012-6-4

7

note2 JA

………………………………70℃/W

注: 1.测试点选择靠近7、8脚, 2. 7、8脚处不能少于200 mm2 的铜皮;

2012-6-4

3

电气特性

测试条件: T=25℃,,VCC=5.5-7.5V, RS=1Ω;

参数

符号

条件

输出

开关管最大耐压

Ioc=10mA

饱和压降 输出上升时间 输出下降时间 输出限制电流

当功率管截止时,内部电路将功率管反向 偏置,利用双极性晶体管 CB 的耐高压特性来提 高 OC 脚的耐压能力,从而确保功率管的安全 性。

RM6204 内部设计了多款保护功能,如:过 载保护、输出短路保护、过温保护、VCC 脚过 压保护等。

RM6204 采用标准的 DIP-8 封装形式。

■内置800V高压三极管;; ■应用电路设计简单,元器件少; ■内置锁存脉宽调制和逐脉冲电流检测技术; ■低电压降频且待机功耗小于0.3W; ■内置斜坡补偿、反馈补偿功能; ■内置独立上限电流检测电路,实时处理过流

9.017

6.223

2.921 8.509

0°

毫米 典型值

3.302 1.524 0.457 9.271 7.620 6.350 2.540 3.302 9.017

7°

最大值

5.334

3.429

10.160

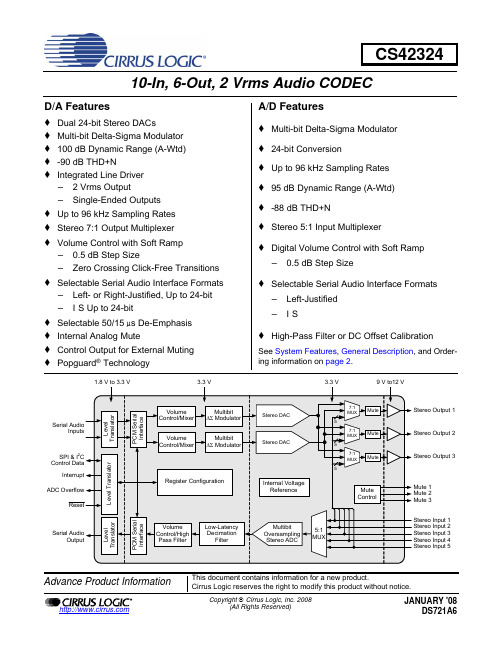

CS42324中文资料

10-In, 6-Out, 2Vrms Audio CODECD/A FeaturesDual 24-bit Stereo DACs Multi-bit Delta-Sigma Modulator 100dB Dynamic Range (A-Wtd) -90dB THD+N Integrated Line Driver– 2 Vrms Output–Single-Ended OutputsUp to 96kHz Sampling Rates Stereo 7:1 Output Multiplexer Volume Control with Soft Ramp–0.5dB Step Size–Zero Crossing Click-Free Transitions Selectable Serial Audio Interface Formats –Left- or Right-Justified, Up to 24-bit –I²S Up to 24-bitSelectable 50/15 μs De-Emphasis Internal Analog MuteControl Output for External Muting Popguard ® TechnologyA/D FeaturesMulti-bit Delta-Sigma Modulator 24-bit ConversionUp to 96kHz Sampling Rates 95dB Dynamic Range (A-Wtd) -88dB THD+NStereo 5:1 Input MultiplexerDigital Volume Control with Soft Ramp–0.5dB Step SizeSelectable Serial Audio Interface Formats–Left-Justified –I²SHigh-Pass Filter or DC Offset Calibration See System Features , General Description , and Order-ing information on page 2.CS42324System FeaturesDirect Interface with 1.8 V to 3.3 V Logic LevelsSupports Asynchronous Serial Port Operation –Two Independent Clock Domains–ADC, DAC1, and DAC2 can beIndependently Assigned to the Two ClockDomains–Each Serial Port Supports Master or Slave OperationInternal Digital Loopback+3.3V Analog Power Supply+3.3V Digital Power Supply+9 V to +12 V High-Voltage Power SupplyHardware or Software Mode Configuration –Supports I²C® and SPI™ Software Interface General DescriptionThe CS42324 is a highly integrated stereo audio CODEC. The CS42324 performs stereo analog-to-digital (A/D) and up to four channels of digital-to-analog (D/A) conversion of up to 24-bit serial values at sample rates up to 96kHz.A 5:1 stereo input multiplexer is included for selecting between line-level inputs. The output of the input multi-plexer is followed by an advanced 3rd-order, multi-bit delta-sigma modulator and digital filtering/decimation. Sampled data is transmitted by the serial audio inter-face at rates from 4kHz to 96kHz, in either Slave or Master Mode.The D/A converter is based on a 5th-order multi-bit del-ta-sigma modulator with an ultra-linear low-pass filter and offers a volume control that operates with a 0.5dB step size. It incorporates selectable soft ramp and zero crossing transition functions to eliminate clicks and pops.An integrated 7:1 stereo output multiplexer on each of the three stereo 2 Vrms line-level outputs is used to se-lect any of the 5 stereo analog inputs, for analog bypass support, or the outputs of the 2 internal DACs. Each 2Vrms output can be muted with the selectable analog mute function.Standard 50/15μs de-emphasis is available for a 44.1kHz sample rate for compatibility with digital audio programs mastered using the 50/15μs pre-emphasis technique.Integrated digital level translators allow easy interfacing between the CS42324 and other devices operating over a wide range of logic levels.The CS42324 is available in a 48-pin LQFP package in Commercial (-40°C to +85°C) and Automotive (-40°C to +105°C) grades. The CDB42324 Customer Demonstra-tion board is also available for device evaluation and implementation suggestions. Please refer to “Ordering information” on page71 for complete details.TABLE OF CONTENTS1. PIN DESCRIPTIONS (8)1.1 Software Mode (8)1.2 Hardware Mode (10)1.3 Digital I/O Pin Characteristics (12)2. CHARACTERISTICS AND SPECIFICATIONS (13)RECOMMENDED OPERATING CONDITIONS (13)ABSOLUTE MAXIMUM RATINGS (13)DAC ANALOG CHARACTERISTICS - COMMERCIAL (-CQZ) (14)DAC ANALOG CHARACTERISTICS - AUTOMOTIVE (-DQZ) (15)DAC COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (16)ADC ANALOG CHARACTERISTICS - COMMERCIAL (-CQZ) (17)ADC ANALOG CHARACTERISTICS - AUTOMOTIVE (-DQZ) (18)ADC DIGITAL FILTER CHARACTERISTICS (19)ANALOG PASS-THRU CHARACTERISTICS (20)DC ELECTRICAL CHARACTERISTICS (21)DIGITAL INTERFACE CHARACTERISTICS (21)SWITCHING CHARACTERISTICS - SERIAL AUDIO (22)SWITCHING CHARACTERISTICS - SERIAL AUDIO (CONT.) (23)SWITCHING CHARACTERISTICS - SOFTWARE MODE - I²C FORMAT (24)SWITCHING CHARACTERISTICS - SOFTWARE MODE - SPI FORMAT (25)3. TYPICAL CONNECTION DIAGRAMS (26)4. APPLICATIONS (28)4.1 System Clocking (28)4.1.1 Master Clock (28)4.1.2 Synchronous / Asynchronous Mode (29)4.2 Serial Port Operation (29)4.2.1 Master Mode (30)4.2.2 Slave Mode (30)4.2.3 ADC, DAC1, and DAC2 clock selection (31)4.2.4 High-Impedance Digital Output (31)4.2.5 Digital Interface Formats (32)4.2.6 Synchronization of Multiple Devices (32)4.3 Analog-to-Digital Data Path (33)4.3.1 ADC Analog Input Multiplexer (33)4.3.2 ADC Description (33)4.3.3 High-Pass Filter and DC Offset Calibration (34)4.3.4 Digital Attenuation Control (34)4.4 Digital-to-Analog Data Path (34)4.4.1 Digital Volume Control (34)4.4.2 Mono Channel Mixer (34)4.4.3 De-Emphasis Filter (35)4.4.4 Internal Digital Loopback (35)4.4.5 DAC Description (35)4.4.6 Analog Output Multiplexer (36)4.4.7 Output Transient Control (36)4.4.8 Mute Control (37)4.5 Initialization (37)4.5.1 Determining Hardware or Software Mode (37)4.5.2 Hardware Mode Start-Up (37)4.5.3 Software Mode Start-Up (38)4.5.4 Initialization Flow Chart (39)4.6 Device Control (40)4.6.2 Software Mode - I²C Control Port (41)4.6.3 Software Mode - SPI Control Port (42)4.6.4 Memory Address Pointer (MAP) (43)4.7 Interrupts and Overflow (43)5. REGISTER QUICK REFERENCE (44)6. REGISTER DESCRIPTION (46)6.1 Device I.D. and Revision Register (Address 00h) (Read Only) (46)6.1.1 Device I.D. (Read Only) (46)6.1.2 Chip Revision (Read Only) (46)6.2 Mute Control (Address 01h) (46)6.2.1 System MCLK Source (46)6.2.2 Mute DAC2 Left-Channel (46)6.2.3 Mute DAC2 Right-Channel (47)6.2.4 Mute DAC1 Left-Channel (47)6.2.5 Mute DAC1 Right-Channel (47)6.2.6 Mute ADC Left-Channel (47)6.2.7 Mute ADC Right-Channel (47)6.3 Operational Control (Address 02h) (47)6.3.1 Global Power-Down (47)6.3.2 INT Pin High/Low Active (INT_H/L) (48)6.3.3 Freeze (48)6.3.4 Tri-State SDOUT (48)6.3.5 Tri-State Serial Port 1 (48)6.3.6 Tri-State Serial Port 2 (49)6.4 Serial Port 1 Control (Address 03h) (49)6.4.1 Serial Port 1 Master/Slave Select (49)6.4.2 Serial Port 1 Speed Mode (49)6.4.3 MCLK1 Divider (49)6.4.4 Serial Port 1 MCLK source (49)6.5 Serial Port 2 Control (Address 04h) (50)6.5.1 Serial Port 2 Master/Slave Select (50)6.5.2 Serial Port 2 Speed Mode (50)6.5.3 MCLK2 Divider (50)6.5.4 Serial Port 2 MCLK Source (50)6.6 ADC Clocking (Address 06h) (50)6.6.1 ADC MCLK Source (50)6.6.2 ADC Serial Port Source (51)6.6.3 ADC Digital Interface Format (ADC_DIF) (51)6.7 DAC1 Clocking (Address 07h) (51)6.7.1 DAC1 MCLK Source (51)6.7.2 DAC1 Serial Port Source (51)6.7.3 DAC1 Digital Interface Format (DAC1_DIF) (51)6.8 DAC2 Clocking (Address 08h) (52)6.8.1 DAC2 MCLK Source (52)6.8.2 DAC2 Serial Port Source (52)6.8.3 DAC2 Digital Interface Format (DAC2_DIF) (52)6.9 ADC Control (Address 0Ah) (52)6.9.1 ADC High-Pass Filter Freeze (52)6.9.2 ADC Soft Ramp Control (52)6.9.3 Analog Input Selection (53)6.10 DAC1 Control (Address 0Bh) (53)6.10.1 DAC1 De-Emphasis Control (53)6.10.2 DAC1 Single Volume Control (53)6.10.4 DAC1 Zero Cross Control (54)6.10.5 DAC1 Loop-Back (54)6.10.6 DAC1 Invert Signal Polarity (54)6.10.7 DAC1 Channel Mixer (54)6.11 DAC2 Control (Address 0Ch) (55)6.11.1 DAC2 De-Emphasis Control (55)6.11.2 DAC2 Single Volume Control (55)6.11.3 DAC2 Soft Ramp Control (55)6.11.4 DAC2 Zero Cross Control (55)6.11.5 DAC2 Loop-Back (56)6.11.6 DAC2 Invert Signal Polarity (56)6.11.7 DAC2 Channel Mixer (56)6.12 AOUT1 Control (Address 0Dh) (56)6.12.1 External Mute Control Pin (56)6.12.2 AOUT1 Select (56)6.13 AOUT2 Control (Address 0Eh) (57)6.13.1 External Mute Control Pin (57)6.13.2 AOUT2 Select (57)6.14 AOUT3 Control (Address 0Fh) (57)6.14.1 External Mute Control Pin (57)6.14.2 AOUT3 Select (58)6.15 ADCx Volume Control: ADCA (Address 10h) & ADCB (Address 11h) (58)6.16 DAC1x Volume Control: DAC1A (Address 12h) & DAC1B (Address 13h) (58)6.17 DAC2x Volume Control: DAC1A (Address 14h) & DAC1B (Address 15h) (59)6.18 Interrupt Mode (Address 16h) (59)6.19 Interrupt Mask (Address 17h) (59)6.19.1 DAC2 Auto Mute Left Mask (DAC2_AMUTELM) (60)6.19.2 DAC2 Auto Mute Right Mask (DAC2_AMUTERM) (60)6.19.3 DAC1 Auto Mute Left Mask (DAC1_AMUTELM) (60)6.19.4 DAC1 Auto Mute Right Mask (DAC1_AMUTELM) (60)6.19.5 Serial Port 2 Clock Error Mask (SP2_CLKERRM) (60)6.19.6 Serial Port 1 Clock Error Mask (SP1_CLKERRM) (60)6.19.7 ADC Positive Overflow Mask (ADC_OVFLPM) (61)6.19.8 ADC Negative Overflow Mask (ADC_OVFLNM) (61)6.20 Interrupt Status (Address 18h) (Read Only) (61)6.20.1 DAC2 Auto Mute Left Interrupt Status (DAC2_AMUTEL) (61)6.20.2 DAC2 Auto Mute Right Interrupt Status (DAC2_AMUTER) (61)6.20.3 DAC1 Auto Mute Left Interrupt Status (DAC1_AMUTEL) (62)6.20.4 DAC1 Auto Mute Right Interrupt Status (DAC1_AMUTEL) (62)6.20.5 Serial Port 2 Clock Error Interrupt Status (SP2_CLKERR) (62)6.20.6 Serial Port 1 Clock Error Interrupt Status (SP1_CLKERR) (62)6.20.7 ADC Positive Overflow Interrupt Bit (ADC_OVFLP) (62)6.20.8 ADC Negative Overflow Interrupt Bit (ADC_OVFLN) (63)7. GROUNDING AND POWER SUPPLY DECOUPLING (64)8. ADC FILTER PLOTS (65)9. DAC DIGITAL FILTER RESPONSE PLOTS (67)10. PARAMETER DEFINITIONS (69)11. PACKAGE DIMENSIONS (70)THERMAL CHARACTERISTICS AND SPECIFICATIONS (70)12. ORDERING INFORMATION (71)13. REVISION HISTORY (71)LIST OF FIGURESFigure 1.Equivalent Analog Output Load (16)Figure 2.Maximum Analog Output Loading (16)Figure 3.Serial Input Timing (22)Figure 4.Serial Output Timing (23)Figure 5.Software Mode Timing - I²C Format (24)Figure 6.Software Mode Timing - SPI Mode (25)Figure 7.Typical Connection Diagram - Software Mode (26)Figure 8.Typical Connection Diagram - Hardware Mode (27)Figure 9.Serial Port Topology (29)Figure 10.Master Mode Clock Generation (30)Figure 11.Converter Clocking (31)Figure 12.Tri-State Serial Port (31)Figure 13.Left-Justified up to 24-Bit Data (32)Figure 14.I²S up to 24-Bit Data (32)Figure 15.Right-Justified 16-Bit Data, Right-Justified 24-Bit Data (32)Figure 16.Analog Input Architecture (33)Figure 17.De-Emphasis Curve (35)Figure 18.Analog Output Architecture (36)Figure 19.Initialization Flow Chart (39)Figure 20.Software Mode Timing, I²C Write (41)Figure 21.Software Mode Timing, I²C Read (41)Figure 22.Software Mode Timing, SPI Mode (43)Figure 23.Single-Speed Mode Stopband Rejection (65)Figure 24.Single-Speed Mode Transition Band (65)Figure 25.Single-Speed Mode Transition Band (Detail) (65)Figure 26.Single-Speed Mode Passband Ripple (65)Figure 27.Double-Speed Mode Stopband Rejection (65)Figure 28.Double-Speed Mode Transition Band (65)Figure 29.Double-Speed Mode Transition Band (Detail) (66)Figure 30.Double-Speed Mode Passband Ripple (66)Figure 31.Single-Speed Stopband Rejection (67)Figure 32.Single-Speed Transition Band (67)Figure 33.Single-Speed Transition Band (detail) (67)Figure 34.Single-Speed Passband Ripple (67)Figure 35.Double-Speed Stopband Rejection (67)Figure 36.Double-Speed Transition Band (67)Figure 37.Double-Speed Transition Band (detail) (68)Figure 38.Double-Speed Passband Ripple (68)Figure 39.Quad-Speed Stopband Rejection (68)Figure 40.Quad-Speed Transition Band (68)Figure 41.Quad-Speed Transition Band (detail) (68)Figure 42.Quad-Speed Passband Ripple (68)LIST OF TABLESTable 1. I/O Power Rails (12)Table 2. Speed Modes (28)Table 3. Single-Speed Mode Common Clock Frequencies (28)Table 4. Double-Speed Mode Common Clock Frequencies (28)Table 5. M1 and M0 Mode Pins in Hardware Mode (29)Table 6. Slave Mode SCLK/LRCK Ratios (30)Table 7. MCLKx to LRCKx Ratios (30)Table 8. Hardware Mode Interface Format Control (32)Table 9. Hardware Mode Feature Summary (40)Table 10. Freeze-able Bits (48)1.PIN DESCRIPTIONS1.1Software ModePin Name #Pin DescriptionSDA/CDOUT1I²C Format SDA (Input/Output ) - Acts as an input/output data pin. An external pull-up resistor is required for I²C control port operation.SPI Format CDOUT (Output ) - Acts as an output only data pin.SCL/CCLK 2I²C Format, SCL (Input ) – Serial clock for the serial control port. An external pull-up resistor is required for I²C control port operation.SPI Format, CCLK (Input ) – Serial clock for the serial control port.AD0/CS 3I²C Format, AD0 (Input ) - Forms the device address input AD[0].SPI Format, CS (Input ) - Acts as the active low chip select input.AD1/CDIN 4I²C Format, AD1 (Input ) - Forms the device address input AD[1].SPI Format, CDIN (Input ) - Becomes the input data pin.INT 5Interrupt (Output ) - Indicates an interrupt condition has occurred.FILT+6FILT+ (Output ) - Full-scale reference voltage for ADC.VCMADC 7ADC Common-Mode Voltage (Output ) - Filter connections for the ADC internal quiescent refer-ence voltage.GND 8Analog Ground (Input ) - Analog ground reference.VA 9Analog Power (Input) - Positive power for the internal analog section.VBIAS 10Bias Voltage (Output ) - Positive reference voltage for the internal DAC.MUTEC111Mute Control 1 (Output ) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.SCL/CCLK G N D HS C L K 1AD0/CS AD1/CDININT SDA/CDOUT FILT+VCMADCGND VA VBIAS MUTEC1MUTEC2V A _HA O U T 1BA O U T 2AA O U T 2BA O U T 3AA O U T 3BM U T E C 3V C M B U FV C M D A CV A _HA O U T 1AS D I N 2M C L K 1L R C K 1V DG N DV LS D O U TC L K 2L R C K 2M C L K 2D I N 1MUTEC212Mute Control 2 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.MUTEC313Mute Control 3 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.VCMBUF14VCMBUF (Output) -Internally buffered VCMDACVCMDAC15DAC Common-Mode Voltage (Output)-Filter connections for the DAC internal quiescent refer-ence voltage.VA_H 1618Analog High Voltage Power (Input)-Positive power for the internal output buffer section.GNDH17Analog Ground (Input) - Ground reference for high-voltage section.AOUT1A, AOUT1B AOUT2A, AOUT2B AOUT3A, AOUT3B 19, 2021, 2223, 24DAC Analog Audio Outputs (Output) - The full-scale output level is specified in the DAC Analog Characteristics specification table.AIN5B, AIN5A AIN4B, AIN4A AIN3B, AIN3A AIN2B, AIN2A AIN1B, AIN1A 25, 2627, 2829, 3031, 3233, 34Stereo Analog Inputs 1-5 (Input)-The full-scale input level is specified in the ADC Analog Char-acteristics specification table.RST35Reset (Input) - The device enters a low-power mode when this pin is driven low. OVFL36ADC Overflow (Output) -Indicates an ADC overflow condition is present.SDIN2 SDIN13738Serial Audio Data Input (Input) - Input for two’s complement serial audio data.MCLK239Master Clock 2 (Input) - Optional asynchronous clock source for the DAC’s delta-sigma modula-tors.LRCK240Serial Port 2 Left/Right Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio input data line.SCLK241Serial Port 2 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 2. VD42Digital Power (Input) -Positive power for the internal digital section.GND43Digital Ground (Input) - Ground reference for the internal digital section.VL44Digital Interface Power (Input) -Determines the required signal level for the control and serial port interfaces as shown in “I/O Power Rails” on page12. Refer to the“Recommended Operating Conditions” on page13 for appropriate voltages.SDOUT45Serial Audio Data Output (Output) -Output for two’s complement serial audio data. SCLK146Serial Port 1 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 1.LRCK147Serial Port 1 Left/Right Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio output data line.MCLK148Master Clock 1 (Input) - Clock source for the ADC’s delta-sigma modulators. By default, this sig-nal also clocks the DAC’s delta-sigma modulators.1.2Hardware ModePin Name#Pin DescriptionM0, M11, 2Mode Selection (Input) - Determines the operational mode of the device.MDIV3MCLK Divider (Input) - Setting this pin high places a divide-by-2 circuit in the MCLK path to the core device circuitry.MUTE4MUTE (Input) -Engages the internal digital mute and activates the MUTECx pinsDIF5DIF (Input) -Sets the serial audio interface format. Setting DIF high selects I²S audio format and low selects LJ audio format.FILT+6FILT+ (Output) -Full-scale reference voltage for ADC.VCMADC7ADC Common-Mode Voltage (Output)-Filter connections for the ADC internal quiescent refer-ence voltage.GND8Analog Ground (Input)-Analog ground reference.VA9Analog Power (Input)-Positive power for the internal analog section. VBIAS10Bias Voltage (Output)-Positive reference voltage for the internal DAC.MUTEC111Mute Control 1 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.MUTEC212Mute Control 2 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.OVFLRSTAIN1AAIN1BAIN2AAIN2BAIN3AAIN3BAIN4AAIN4BAIN5AAIN5BM1MDIVMUTEDIFM0FILT+VCMADCGNDVAVBIAS MUTEC1 MUTEC2SCLK1SDIN2 MCLK1LRCK1VDGNDVLSDOUTSCLK2LRCK2MCLK2SDIN1GNDHVA_HAOUT1BAOUT2AAOUT2BAOUT3AAOUT3B MUTEC3VCMBUFVCMDACVA_HAOUT1AMUTEC313Mute Control 3 (Output) - Active-low mute output can drive external circuitry to eliminate the clicks and pops associated with any single-rail output. This pin will become a high-impedance out-put during power-down mode or when an invalid MCLK to LRCK ratio is detected.VCMBUF14VCMBUF (Output) -Internally buffered VCMDACVCMDAC15DAC Common-Mode Voltage (Output)- Filter connections for the DAC internal quiescent refer-ence voltage.VA_H16, 18Analog High Voltage Power (Input)-Positive power for the internal output buffer section. GNDH17Analog Ground (Input) - Ground reference for high-voltage section.AOUT1A, AOUT1B AOUT2A, AOUT2B AOUT3A, AOUT3B 19, 2021, 2223, 24DAC Analog Audio Outputs (Output) - The full-scale output level is specified in the DAC Analog Characteristics specification table.AIN5B, AIN5A AIN4B, AIN4A AIN3B, AIN3A AIN2B, AIN2A AIN1B, AIN1A 25, 2627, 2829, 3031, 3233, 34Stereo Analog Inputs 1-5 (Input)-The full-scale input level is specified in the ADC Analog Char-acteristics specification table.RST35Reset (Input) - The device enters a low-power mode when this pin is driven low. OVFL36ADC Overflow (Output) -Indicates an ADC overflow condition is present.SDIN2 SDIN13738Serial Audio Data Input (Input) - Input for two’s complement serial audio data.MCLK239Master Clock 2 (Input) - Optional asynchronous clock source for the DAC’s delta-sigma modula-tors.LRCK240Serial Port 2 Left/Right Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio input data line.SCLK241Serial Port 2 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 2. VD42Digital Power (Input) -Positive power for the internal digital section.GND43Digital Ground (Input) - Ground reference for the internal digital section.VL44Digital Interface Power (Input) -Determines the required signal level for the control and serial port interfaces as shown in “I/O Power Rails” on page12. Refer to the“Recommended Operating Conditions” on page13 for appropriate voltagesSDOUT45Serial Audio Data Output (Output) -Output for two’s complement serial audio data. SCLK146Serial Port 1 Serial Bit Clock (Input/Output)-Serial bit clock for serial audio interface 1.LRCK147Serial Port 1 Left Right/Clock(Input/Output) - Determines which channel, Left or Right, is cur-rently active on the serial audio output data line.MCLK148Master Clock 1 (Input) - Clock source for the ADC’s delta-sigma modulators. By default, this sig-nal also clocks the DAC’s delta-sigma modulators.1.3Digital I/O Pin CharacteristicsThe logic level for each input should adhere to the corresponding power rail and should not exceed the max-imum ratings.Power SupplyPinNumberPin Name I/O Driver ReceiverSoftware ModeVL 1SDACDOUTInput/OutputHi-Z/Output1.8 V - 3.3 V, Open Drain1.8 V - 3.3 V, CMOS1.8 V - 3.3 V, with Hysteresis 2SCLCCLKInput- 1.8 V - 3.3 V, with Hysteresis 3AD0CSInput- 1.8 V - 3.3 V, with Hysteresis 4AD1CDINInput- 1.8 V - 3.3 V, with Hysteresis 5INT Output 1.8 V - 3.3 V, Open Drain 1.8 V - 3.3 V, with HysteresisHardware ModeVL 1M0Input- 1.8 V - 3.3 V, with Hysteresis 2M1Input- 1.8 V - 3.3 V, with Hysteresis 3MDIV Input- 1.8 V - 3.3 V, with Hysteresis 4MUTE Input- 1.8 V - 3.3 V, with Hysteresis 5DIF Input- 1.8 V - 3.3 V, with HysteresisAll ModesVL 35RST Input- 1.8 V - 3.3 V 4740LRCK1LRCK2Input/Output 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V 4641SCLK1SCLK2Input/Output 1.8 V - 3.3 V, CMOS 1.8 V - 3.3 V 4839MCLK1MCLK2Input- 1.8 V - 3.3 V 3837SDIN1SDIN2Input- 1.8 V - 3.3 V 45SDOUT Output 1.8 V - 3.3 V, CMOS-36OVFL Output 1.8 V - 3.3 V, Open Drain-VA_H 111213MUTEC1MUTEC2MUTEC3Output9.0 V - 12.0 V-Table 1. I/O Power Rails2.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONSGND =GNDH =0V; All voltages with respect to ground.ABSOLUTE MAXIMUM RATINGSGND =GNDH =0 V; All voltages with respect to ground. (Note 1)Notes:1.Operation beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.2.Any pin except supplies. Transient currents of up to ±100mA on the analog input pins will not causeSCR latch-up.ParametersSymbol Min Nom Max Units DC Power Supplies:Analog Digital LogicHigh Voltage AnalogVA VD VL VA_H 3.133.131.718.55 3.33.33.39.0 3.473.473.4712.60V V V V Ambient Operating Temperature (Power Applied)Commercial(-CQZ)Automotive(-DQZ)T A-40-40--+85+105°C °CParameterSymbol Min Max Units DC Power Supplies:Analog Digital LogicHigh Voltage AnalogVA VD VL VA_H -0.3-0.3-0.3-0.3+4.50+4.50+4.50+17.0V V V V Input Current (Note 2)I in -10+10mA Analog Input Voltage V INA GND - 0.3VA_H + 0.3V Digital Input VoltageLogicV IND -0.3VL + 0.4V Ambient Operating Temperature (Power Applied)T A -55+125°C Storage TemperatureT stg-65+150°CTest Conditions (unless otherwise specified): VA = VD = VL = 3.3V, VA_H = 9V, GND =GNDH =0V; T A = 25°C; 997Hz Full-Scale Output Sine Wave. Decoupling capacitors, Filter capacitors, and Recommended output filter as shown in Figure 7 on page 26 and Figure 8 on page 27; Fs =48 kHz or 96kHz; Synchronous Mode; Measurement Bandwidth 10 Hz to 20kHz,Notes:3.One-half LSB of triangular PDF dither added to data.4.See Figures 1 and 2 on page 16. R L and C L reflect the minimum resistance and maximum capacitanceallowed in order to maintain stability in the internal op-amp. C L affects the dominant pole of the internal output amp; increasing C L beyond 100pF can cause the internal op-amp to become unstable.ParameterSymbolMin Typ Max Unit Dynamic Range(Note 3)18 to 24-Bit A-weighted unweighted 16-BitA-weighted unweighted94918885100979390----dB dB dB dB Total Harmonic Distortion + Noise(Note 3)18 to 24-Bit0 dB -20 dB-60 dB 16-Bit0 dB -20 dB -60 dB THD+N -------90-77-37-87-77-37-84-73-33-82-62-22dB dB dB dB dB dB Interchannel Isolation (1kHz)--100-dB DC AccuracyInterchannel Gain Mismatch -0.10.25dB Gain Drift -100-ppm/°C Analog OutputFull-Scale Output Voltage1.92.0 2.1V rms Max current draw from an AOUT pin I OUT-575-μA AC-Load Resistance (Note 4)R L 5--k ΩLoad Capacitance (Note 4)C L --100pF Output ImpedanceZ OUT-50-ΩTest Conditions (unless otherwise specified): VA =3.13V to 3.47V, VD =3.13V to 3.47V, VL =1.71V to 3.47V, VA_H = 8.55V to 12.60V, GND=GNDH=0V; T A = -40° C to +85° C; 997Hz Full-Scale Output Sine Wave. Decoupling capacitors, filter capacitors, and recommended output filter as shown in Figure 7 on page 26 and Fig-ure 8 on page 27; Fs=48 kHz or 96kHz; Synchronous Mode; Measurement Bandwidth 10 Hz to 20kHz,Parameter Symbol Min Typ Max Unit Dynamic Range(Note 3)18 to 24-Bit A-weightedunweighted 16-Bit A-weightedunweighted 90878380100979390----dBdBdBdBTotal Harmonic Distortion + Noise(Note 3)18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB THD+N-------90-77-37-87-77-37-80-67-27-77-67-27dBdBdBdBdBdBInterchannel Isolation(1kHz)--100-dB DC AccuracyInterchannel Gain Mismatch-0.10.25dB Gain Drift-100-ppm/°C Analog OutputFull-Scale Output Voltage 1.9 2.0 2.1V rms Max current draw from an AOUT pin I OUT-575-μA AC-Load Resistance(Note 4)R L5--kΩLoad Capacitance(Note 4)C L--100pF Output Impedance Z OUT-50-ΩDAC COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSENotes:5.Response is clock-dependent and will scale with Fs. Note that the amplitude vs. frequency plots of thisdata (Figures 31 to 42) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.6.For Single-Speed Mode, the measurement bandwidth is from StopBand to 3 Fs.For Double-Speed Mode, the measurement bandwidth is from StopBand to 3 Fs.7.De-emphasis is available only in Single-Speed Mode.Parameter (Note 5)SymbolMinTypMaxUnitSingle-Speed Mode Passband (Note 6)to -0.01dB corner to -3dB corner00--.454.499Fs FsFrequency Response (10Hz to 20kHz)-0.01-+0.01dB StopBand0.547--Fs StopBand Attenuation (Note 6)102--dB Group Delaytgd-9.4/Fs -s De-emphasis Error (Note 7) Fs = 44.1 kHz--+/-0.14dBDouble-Speed Mode Passband (Note 6)to -0.01dB corner to -3dB corner00--.43.499Fs Fs Frequency Response (10Hz to 20kHz)-0.01-+0.01dB StopBand.583--Fs StopBand Attenuation (Note 6)80--dB Group Delaytgd- 4.6/Fs-sFigure 1. Equivalent Analog Output Load Figure 2. Maximum Analog Output Loading。

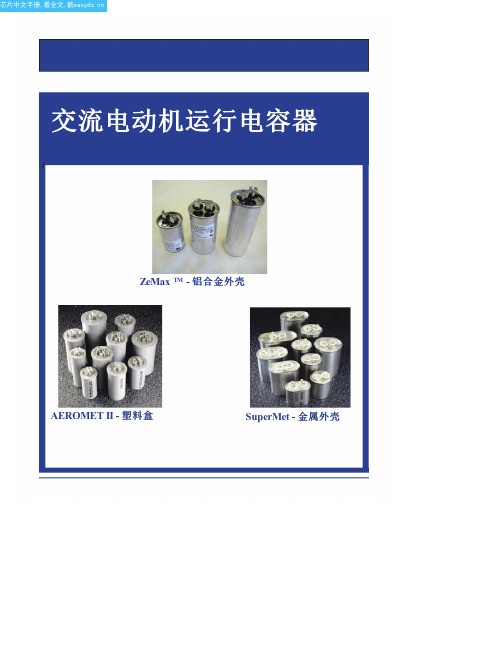

Z64S4440M中文资料(Aerovox)中文数据手册「EasyDatasheet - 矽搜」

交流电动机运行电容器

ZeMax TM - 铝合金外壳

AEROMET II - 塑料盒

SuperMet - 金属外壳

芯片中文手册,看全文,戳

目录

AEROMET II规格(系列M型).......................................... .................................... 3 SuperMet & ZeMax TM 规格(系列Z型)............................................ .................. 4 部分编号系统.............................................................................................................五 AEROMET II评分表(单台容量)系列M型....................................... ........... 6 AEROMET II评分表(双功能)系列型号M ....................................... ............. 8 SuperMet评分表(单台容量)系列Z型........................................ ............... 9 SuperMet评分表(双容量)系列Z型........................................ .............. 11 ZeMax TM 评分表(单台容量)系列Z型......................................... ........... 13 AEROMET II机械尺寸.............................................. .......................................... 15 SuperMet机械尺寸............................................... ........................................... 16 ZeMax TM 机械Dimensions............................................................................................17 附件 - 安装硬件.............................................. ............................................ 18

EPM240GT100C4N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

由MAX II系列支持.

表1-5 显示外部电源电压

表 1-5. MAX II外接电源电压

设备

多电压内核外部电源电压(V 多电压I / O接口电压电平(V 须知 表 1-5: (1)MAX IIG和MAX IIZ器件只接受1.8 V他们 (2)MAX II器件在1.8 V内部操作

) (2) )

EPM 240 EPM 570 EPM 1270 EPM 2210

3.3 V / 2.5 V或1.8 V ■ 多电压I / O接口,支持3.3 V,2.5 V,1.8 V和1.5 V逻辑电平 ■ 总线型架构,包括可编程摆率,驱动能力,

总线防护持,和可编程上拉电阻

■ 施密特触发器能够容忍噪声输入(每个引脚可编程)

■ I / O是完全符合外围组件互连特别 兴趣小组(PCI SIG)PCI本地总线规范,修订2.2 3.3 V 工作在66兆赫

100-Pin FineLine

BGA

100-Pin TQFP

0.5

0.5

1

0.5

25

36

121

256

5×5

6×6

11 × 11 16 × 16

144-Pin TQFP

0.5 484 22 × 22

144-Pin Micro FineLine BGA

256-Pin Micro FineLine BGA

256-Pin FineLine

BGA

324-Pin FineLine

BGA

0.5

0.5

1

1

49

121

289

361

7×7

11 × 11 17 × 17 19 × 19

芯片中文手册,看全文,戳

TLE4214G资料

ApplicationApplications in automotive electronics require intelligent power switches activated by logic signals, which are shorted-load protected and provide error feedback.This IC contains two of these power switches (low-side switches). In case of inductive loads the integrated clamp diodes clamp the discharging voltage. If a “high” signal is applied to the enable input both switches can be activated independently of one another with TTL signals at the control inputs (active high). The high impedance inputs should always be connected to a fixed potential (noise immunity).The status output (open collector) signals the following malfunctions with high potential:q Overload,q Open load,q Shorted load to ground,q Overvoltage,qOvertemperature.Type Ordering Code PackageTLE 4214 G Q67000-A9094P-DSO-20-7 (SMD)Intelligent Double Low-Side Switch 2 x 0.5 A Bipolar ICTLE 4214GP-DSO-20-7Featuresq Double low-side switch, 2 x 0.5 Aq Power limitationq Overtemperature shutdown q Overvoltage shutdown q Status monitoringq Shorted-load protection q Integrated clamp diodesqTemperature range – 40 to 125°CPin Configuration(top view)TLE 4214 GPin Definitions and FunctionsPin No.Symbol Function6, 16GND Ground Design wiring for the max.short-circuit current (2 x 1 A)10IN2Control input 2(TTL compatible) activates the outputtransistor 2 in case of high potential2V S Supply voltage In case of overvoltage at this pin largesections of the circuit are deactivated. The statusoutput indicates this malfunction without delay time. 7Q2Output 2Shorted load protected, open collectoroutput for currents up to 0.5 A, with clamping diodes tosupply voltage.5Q1Output 1Shorted load protected, open collectoroutput for currents up to 0.5 A, with clamping diodes tosupply voltage.9ENA Enable input, active high1IN1Control input 1(TTL-compatible) activates outputtransistor 1 in case of high potential15STA Status output(open collector) for both outputs;indicates overtemperature, overload, open load andshorted load to ground as well as overvoltage at pin3.It is switched to high after a defined delay time in caseof malfunction (except: overvoltage)3, 4, 8, 11…14,N. C.Not connected17 (20)Block DiagramCircuit DescriptionInput CircuitsThe control inputs and the enable input consist of TTL-compatible Schmitt triggers with hysteresis. Controlled by these stages the buffer amplifiers drive the NPN power transistors.Switching StagesThe output stages consist of NPN power transistors with open collectors. Since the protective circuit allocated to each stage limits the power dissipation, the outputs are shorted-load protected to the supply voltage throughout the entire operating range. Positive voltage peaks, which occur during the switching of inductive loads, are limited by the integrated clamp diodes.Monitoring and Protective FunctionsDuring the activated status the outputs are monitored for open load, overload, and shorted load to ground (see table below). In addition, large sections of the circuit are shut down in case of excessive supply voltages V S. Linked via OR gate the information regarding these malfunctions effects the status output (open collector, active high). An internally determined delay time applied to all malfunctions but overvoltage prevents the output of messages in case of short-term malfunctions. Furthermore, a temperature protection circuit prevents thermal overload. If overload occurs, the outputs are protected according to the safe operating area (SOA) mode (see diagram). If voltage and current are outside the SOA, the outputs oscillate to reduce the power dissipation. The switching frequency depends on the internal delay time and the external load (inductances and capacitances). If the frequency is low, the status output may follow the oscillation. An integrated reverse diode protects the supply voltage V S against reverse polarities. Similarly the load circuit is protected against reverse polarities within the limits established by the maximum ratings (no shorted load at the same time!). At supply voltages below the operating range an undervoltage detector ensures that neither the status nor the outputs are activated. At supply voltages below the operating range the output stages are de-activated.Status Output (H = Error)Undervoltage > 3.5 VOperating Range Overvoltage VI= L(passive)VI= H(active)Normal function L L L H Overload L L H H Open load L L H H Shorted output to ground L H H H Overtemperature L H H HCircuit DiagramAbsolute Maximum RatingsTj= – 40 to 150 °CParameter Symbol Limit Values Unitmin.max.VoltagesSupply voltage,t<0.2 sSupply voltageInput voltageOutput voltage (status output) Output voltage (switching stages)VSVSVIVOVQ––1.3–13–0.3–0.370404040+V SVVVVVCurrentsOutput current (switching stages) Current with reverse polarity,t< 0.1 s Output current positive clamp Ground currentOutput current (status output)IQIQIQIGNDIOinternallylimited–0.7––1.4–––0.72.010–AAAmAJunction temperature Storage temperature TjTstg–– 50150150°C°COperating RangeSupply voltage V S6 1)25V Supply voltage slew rate d V S/d t– 11V/µsOutput current (switching stages) Input voltageOutput current (status output)IQVI,V FIO– 0.5– 50.5325AVmAAmbient temperature T A– 40125°C1)Lower limit = 5 V, if previously VSgreater than 6 V (turn-on hysteresis)Supply voltage while shorted load V S–15V Thermal resistance junction to ambient R th JA–77K/WCharacteristicsVS= 6 to 16 V (typ.V S = 12 V);T j = – 40 to 150°C (typ.T j = 25 °C)Parameter Symbol Limit Values Unit Test Conditionmin.typ.max.General CharacteristicsQuiescent current Supply voltage ISIS––235450mAmAVF<V FLVI=V I >V IH,V F >V FHSupply overvoltage shutdown threshold VSO303742V V L =5 V;V O > 4.5 VHysteresis of supplyovervoltage shutdownthreshold∆V SO469V V L =5 V;V O > 4.5 VOpen load error threshold voltage VQ52050mV V L =5 V;V O > 4.5 VOpen load error threshold current IQU1–40mA V Q =V QUOpen load error threshold currentfor both channels active IQU––80mA V Q1 =V Q2 =V QUAbsolute Maximum Ratings (cont’d)Tj= – 40 to 150 °CParameter Symbol Limit Values Unitmin.max.LogicControl inputsH-input voltage threshold L-input voltage threshold V IH V IL 1.30.9 1.81.2 2.11.5V V ––Hysteresis of control input voltage∆V I0.20.61.0V–Enable inputH-input voltage threshold L-input voltage threshold V FH V FL 1.61.4 2.11.8 2.72.3V V ––Hysteresis of enable input voltage ∆V F0.10.30.7V –H-input current L-input currentI IH – I IL 00––1010µA µAV I =5 V V I = 0.5 VStatus Output (open collector)L-saturation voltage V osat 0.10.20.4V I O =5 mAStatus delay timet dS82032µs1)1)Period from the beginning of the disturbance at one channel (exception: overvoltage) until the 50 % value of the status switching edge is reached.Characteristics (cont’d)V S = 6 to 16 V (typ.V S = 12 V);T j = – 40 to 150°C (typ.T j = 25 °C)ParameterSymbolLimit Values Unit Test Conditionmin.typ.max.Switching StagesSaturation voltage Saturation voltage VQSatVQSat––0.6450.8100VmVIQ=0.5 A;V I >V IH;VF>V FHIQ=50 mA;V I >V IH;VF>V FHOutput current Leakage current IQIQ0.5– 5––50AµAVQSat= 0.8 V; V I >V IHVQ= 6 V; V I <V ILSwitch-ON time Switch-OFF time tD ONtD OFF0.20.20.5255µsµsIQ=0.5 A see TimingIQ=0.5 A DiagramForward voltage of substrate diode Forward voltage of clamp diode VQSVQF––1.31.31.71.7VVIQ= – 0.5 At< 0.1 sIQ=0.5 At< 0.1 sLeakage current of clamp diode –I QF––5µA V Q= 0 V; V I <V ILCharacteristics (cont’d)VS= 6 to 16 V (typ.V S = 12 V);T j = – 40 to 150°C (typ.T j = 25 °C)Parameter Symbol Limit Values Unit Test Conditionmin.typ.max.Test CircuitTiming DiagramApplication CircuitQuiescent Current I S versus Ambient Temperature T A in the OFF-Status V S = 12 V;V F <V FLOutput Voltage V Q versusOutput Current V S = 12 V; V I >VIHShorted Load Current I Q0versus Output Voltage VQEqual current at both channelsOnly one channel in operationFirst channel 50 mA, second channel IQPackage OutlinesP-DSO-20-7(Plastic Dual Small Outline Package)G P S O 5094Sorts of PackingPackage outlines for tubes, trays etc. are contained in our Data Book “Package Information”.Dimensions in mmSMD = Surface Mounted Device。

巨鹰Giant204 四通道称重模块 用户手册说明书

Giant204四通道称重模块用户手册 V1.0目录1 技术支持 (3)2 产品介绍 (4)3 技术参数 (5)4 外形尺寸,电气连接以及选型 (6)4.1 外形尺寸 (6)4.2 电气连接与说明 (6)4.2.1 称重传感器连接 (7)4.2.2 指示灯 (8)4.2.3 通信接口RS232/RS485 (8)4.3 选型 (8)5 显示与按键 (9)6 功能与设置 (10)6.1 主界面显示与功能 (11)6.1.1 相关指令 (12)6.2功能菜单 (15)6.2.1 相关指令 (16)6.3校准菜单 (21)6.3.1 校准方式选择菜单 (21)6.3.2 实物校准菜单 (22)6.3.3 数字校准菜单 (24)6.3.4 相关指令 (25)6.4 参数保存菜单 (27)6.4.1相关指令 (27)6.5 显示设置菜单 (28)6.5.1相关指令 (28)6.6 通信设置菜单 (29)6.6.1 相关指令 (30)7 MODBUS通讯协议 (33)8用户设置软件 (40)8.1 软件安装与启动 (40)9 附件 (41)9.1 仪表显示的错误代码 (41)9.2 基本术语 (41)9.3 标准ASCII码 (42)1 技术支持感谢您选择并使用大连哲勤科技有限公司产品,此用户手册协助您了解并正确使用设备。

如需订购产品、技术支持、以及产品信息反馈,请通过以下方式联系我们。

请在联系时附注设备的购买时间,购买方式,联系人信息,地址以及电话等相关信息,便于我们为您服务。

网址E-Mail**************电话+86-411-66831953, 4000-511-521传真+86-411-82388125版本控制2 产品介绍Giant204四通道称重变送器是面向工业控制领域的重量变送器,集四个高速称重通道,RS485和RS232通信接口于一体(Modbus-RTU通信协议),同时进行四个重量的独立并行高速检测。

中科曙光TC4600刀片服务器用户手册V1.0

商标和版权

“SUGON”及图标是曙先信息产业股份有限公司的商标或注册商标。 “中科曙先”及图标是曙先信息产业股份有限公司的商标或注册商标,文中“曙先信息产业股份有限公司”简称“曙

先公司”。

“AMD”,“Opteron”及图标是 Advanced Micro Devices 公司的注册商标。 “Microsoft”.“Windows”.“Windows Server”及“Windows Server System”是微软公司的商标或注册商标。

如您不正确地或未按本手册的指示和要求安装.使用或保管本产品,或让非曙先公司授权的技术人员修理.变更本产品, 曙先公司将不对由此导致的损害承担任何责任。

本手册中所提供照片.图形.图表和揑图,仅用于解释和说明目的,可能与实际产品有些差别,另外,产品实际觃栺和 配置可能会根据需要不时变更,因此与本手册内容有所不同。请以实际产品为准。

目录

1 2

3

产品简介............................................................................................................. 1

1.1

产品概述 ...................................................................................................................... 1

电气接地要求 服务器必须正确接地,以使其正常运行幵确保安全。必须遵照以下要求安装本设备:任何区域性或国家/地区的电气 连线觃程,如国际电工委员会 (IEC) 觃程 364 第 1 至7 部分。此外,您必须确保安装过程中使用的所有配电设备 (如分支连线和揑座)均为已列出的或经过认证的接地型设备。 由于连在同一电源上的多台服务器需要将大量电流导入地下,因此曙先公司建议所用的 PDU 要么固定地连到建筑 物的分支电路上,要么配装一根连接工业揑头的不可拆卸的电线。那些符合IEC 60309 标准的揑头均视为适用揑头。 建议不要使用普通的电源接线板来连接本服务器。

AD421中文资料

功能框图LOCALOSCILLATORSWITCHEDCURRENTSOURCESANDFILTERINGBANDGA PREFERENCEREF IN2.5VREF OUT11.25VREFOUT22.5VLVVCCDRIVECOMPBOOSTLOOPRTNC1C2C3COMLATCHCLOCKDA TA4016-BITSIGMA-DELTA DAC75k112.5k134k121k80kAD421INPUT SHIFTREGISTERDAC LATCHPOWER-ONRESET环路供电型4 mA-20 mA DACAD421特性电流输出4 mA至20 mAHART??兼容型16位分辨率和单调性±0.01积分非线性稳压器输出5 V或3 V2.5 V和1.25 V精密基准电压源静态电流750 ??A最大值可编程报警电流能力灵活的高速串行接口16引脚SOIC和PDIP封装概述AD421是一款完整的环路供电型4 mA-20 mA数字转换器专为满足工业控制领域智能发射器制造商的需求而设计。

作为一种完全集成的高精度、低成本解决方案该器件采用紧凑型16引脚封装是以极低成本提高4 mA-20 mA智能发射器分辨率的理想之选。

AD421内置一个可选稳压器用于为自身及发射器中的其它器件供电。

此稳压器可提供5 V、3.3 V或3 V调节输出电压。

该器件还内置有1.25 V和2.5 V精密基准电压源。

因此AD421不需要外接独立的稳压器和基准电压源。

外部元件只需若干无源元件和一个调整管用于扩充大环路电压范围。

AD421可以结合标准HART FSK协议通信电路使用而且额定性能不会受到影响。

高速串行接口能够以10 Mbps速率工作并允许通过一个标准三线式串行接口与常用的微处理器和微控制器简单相连。

这款DAC采用∑-架构可保证16位单调性且积分非线性为±0.01。

该器件提供4 mA零电平输出电流失调误差为±0.1以及20 mA满量程输出电流增益误差为±0.2。

中泰RM411模块说明书

2.2 RM411详细介绍2.2.1 概述RM411是远端热电阻采集模块,适用于各类工业现场,可采集9路PT100、CU500型热电阻,并转换成相应的温度值,通过RS485接口,与上位机实时通讯。

RM411采用MAX132CNGA/D 转换芯片进行18位双积分模数转换,可直接对0~512mV 的信号进行处理,分辨率达2uV/bit 。

RM411是远端热电阻模块,同时采用了光电隔离技术,使模块的抗干扰能力进一步加强。

2.2.2 主要技术指标● 输入通道数:9路● 信号输入范围: 0~500Ω● A/D 转换分辨率:18bit ,2uV/bit ● A/D 转换时间:16次/秒 ● 处理芯片:AT89C51● 通讯方式:RS485接口,2线制 ● 驱动距离:1200米 ● 通迅格式:9600-8N1 ● 通讯协议:被动查询● 通讯输出数值方式: 电阻值或温度值 ● 通讯输出稳定度:温度0.5℃ ● 隔离电压:≥500V● 供电电压:DC24V ,500mA ●使用环境要求:工作温度:0℃ ~ 60℃ 相对湿度:40% ~ 80% RH 存贮温度:-55℃ ~ +85℃2.2.3 工作原理RM411远端热电阻模块由CPU 、光电隔离、A/D 转换、通道转换、三端电流激励、RS485接口、站址开关和DC/DC 组成,工作原理框图。

RM411工作原理图CH 1 CH 92.2.3.1 CPUR M411模块上的CPU 选用AT89C51,其速度快、内含2K ROM 、128byte RAM ,端口驱动能力达20mA ,能较好地适用于热电阻的采集和热电阻温度值的转换。

2.2.3.2 RS485接口RM411选用MAX485CPA 接口芯片完成RS485数据通讯。

MAX485驱动达1200米,传输速率250Kb/S ,可连接32个站点,并有±15KV 的抗静电冲击。

2.2.3.3 A/D 转换RM411选用MAX132完成A/D 转换,MAX132是CMOS 、18位加符号位、串行模数转换器(ADC),采用多斜度积分技术构成,具有在短时间内提供高转换精度的优点,MAX132工作于每秒钟转换16次的状态,低转换噪声保证了满刻度输入范围为±512mV(2uV/LSB),工作电流为60mA ,24P 窄DIP 封装。

P4404EDG中文资料

Forward Transconductance1

gfs

VDS = -10V, ID = -10A DYNAMIC

Input Capacitance Output Capacitance Reverse Transfer Capacitance Total Gate Charge

2

Ciss Coss Crss Qg Qgs Qgd

JAN-17-2005 2

元器件交易网

NIKO-SEM

P-Channel Logic Level Enhancement

Mode Field Effect Transistor ( Preliminary )

P4404EDG

TO-252(DPAK) Lead-Free

TYPICAL PERFORMANCE CHARACTERISTICS

G S

1. GATE 2. DRAIN 3. SOURCE

ABSOLUTE MAXIMUM RATINGS (TC = 25 °C Unless Otherwise Noted) PARAMETERS/TEST CONDITIONS Drain-Source Voltage Gate-Source Voltage Continuous Drain Current Pulsed Drain Current Power Dissipation

Max.

9.35 2.2 0.48 0.89 0.45 0.03

6

6.4 5.2 0.6 0.64 4.4

6.6 5.4 1 0.9 4.6

A

B

C

F

H

G L

XXXXXXXXX

NIKOS

K

M

J

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SBOS176

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated。