芯片8251A介绍

关于8251串行芯片的论文

《关于8251串行芯片的论文》摘要:随着计算机通信和计算机网络的飞速发展,串行通信技术得到了广泛的应用,所谓串行通信就是数据一位一位的依次传输,每位数据占用一个固定的时间长度。

8251具有独立的发送器和接收器,他能以单工,半双工,全双工方式进行通信。

关键字:8251一.8251的性能指标①可用于串行通讯的同步和异步传送。

②同步传送:5~8位/字符,内部或外部同步,可自动插入同步字符。

③异步传送:5~8位/字符,时钟速率为通信波特率的1、16或64倍。

④可产生终止字符(Break Character);可产生1、1.5或2个位的停止位。

自动检测和处理终止字符。

⑤可检查假的启动位。

⑥波特率:异步传送的最大波特率为19.2K;同步传送的最大波特率64K。

⑦完全双工,发送和接收双缓冲器。

⑧出错检测-具有奇偶、溢出、帧错误等检测电路。

二.8251A的功能结构D7D0BRKDE8251A的功能结构分成5个部分:接收器、发生器、调制控制、读/写控制和I/O缓冲器组成。

其中I/O缓冲器由状态缓冲器、发送数据/命令缓冲器和接收数据缓冲器3部分组成。

8251A的内部由内部数据总线实现相互之间的通信。

(1)接收器:接收器包括接收移位寄存器和数据输入寄存器。

串行输入的数据通过8251A芯片的RXD管脚逐位进入接收移位寄存器,然后变成并行格式进入数据输入寄存器,等待CPU取走。

接收控制电路是用来控制数据接收工作(2)异步串行通信:在异步方式下,如果允许接收和准备好接收数据,8251控制线路监视RXD线。

在无字符传送时RXD线上为高电平(即线路空闲);当发现RXD线上出现低电平时,则认为是起始位,随即启动内部计数器,当计数到一个数据位宽度的一半(若时钟脉冲频率为波特率的16倍时,则为计数到第8个脉冲)时,重新采样RXD 线,若仍为低电平,则确认为起始位,而不是噪声信号。

此后,每隔16个脉冲采样一次RXD线作为输入信号,送至移位寄存器,经过移位,又经过奇偶校验和去掉停止位后,就得到了变换为并行的数据,经过内部数据总线传送至接收数据缓冲器,同时发出RxRDY信号,表示字符可用。

8255A、8251A的原理及应用

8255A的内部结构,由三部分电路组成:与CPU的接口电路、内部控制逻辑电路和与外设连接的输入/输出接口电路。

D7~D0(data bus):三态、双向数据线,与CPU数据总线连接,用来传送数据。

(chip select):片选信号线,低电平有效时,芯片被选中。

A1, A0(port address):地址线,用来选择内部端口。

(read):读出信号线,低电平有效时,允许数据读出。

(write):写入信号线,低电平有效时,允许数据写入。

RESET(reset):复位信号线,高电平有效时,将所有内部寄存器(包括控制寄存器)清0。

PA7~PA0(port A):A口输入/输出信号线。

PB7~PB0(port B):B口输入/输出信号线。

PC7~PC0(port C):C口输入/输出信号线。

VCC:+5V电源。

GND:电源地线。

8255A的工作方式方式0:基本输入输出方式适用于无条件传送和查询方式的接口电路方式1:选通输入输出方式适用于查询和中断方式的接口电路方式2:双向选通传送方式适用于与双向传送数据的外设适用于查询和中断方式的接口电路8255A初始化编程8255A的A,B,C三个端口的工作方式是在初始化编程时,通过向8255A的控制端口写入控制字来设定的。

8255A由编程写入的控制字有两个:方式控制字和置位/复位控制字。

方式控制字用于设置端口A, B, C的工作方式和数据传送方向;置位/复位控制字用于设置C口的PC7~PC0中某一条口线PC i(i=0~7)的电平。

两个控制字公用一个端口地址,由控制字的最高位作为区分这两个控制字的标志位。

(1)方式控制字的格式8255A工作方式控制字的格式如图7.11所示。

D0:设置PC3~PC0的数据传送方向。

D0=1为输入;D0=0为输出。

D1:设置B口的数据传送方向。

D1=1为输入;D1=0为输出.D2:设置B口的工作方式。

D2=1为方式1;D2=0为方式0。

可编程串行通信接口芯片8251A

可编程串行通信接口芯片8251A可编程串行通信接口芯片8251A2010-05-25 15:058251 A是一个通用串行输入/输出接口,可用来将86系列CPU以同步或异步方式与外部设备进行串行通信。

它能将主机以并行方式输入的8位数据变换成逐位输出的串行信号;也能将串行输入数据变换成并行数据传送给处理机。

由于由接口芯片硬件完成串行通信的基本过程,从而大大减轻了CPU的负担,被广泛应用于长距离通信系统及计算机网络。

8251A是一个功能很强的全双工可编程串行通信接口,具有独立的双缓冲结构的接收和发送器,通过编程可以选择同步方式或者异步方式。

在同步方式下,既可以设定为内同步方式也可以设定为外同步方式,并可以在内同步方式时自动插入一个到两个同步字符。

传送字符的数据位可以定义为5~8位,波特率0~64K可选择。

在异步方式下,可以自动产生起始和停止位,并可以编程选择传送字符为5~8位之间的数据位以及1、1/2位之中的停止位,波特率0~19.2K可选择。

同步和异步方式都具有对奇偶错、覆盖错以及帧错误的检测能力。

一、8251A内部结构及功能图8.5.1为8251A结构框图。

作为常用的通信接口,和8255A类似,8251A 的结构也可以归纳为以下三个部分:第一部分是和CPU或者总线的接口部分,其中包括数据总线缓冲器、读/写控制逻辑。

数据总线缓冲器用来把8251A和系统数据总线相连,在CPU执行输入/输出指令期间,由数据总线缓冲器发送和接收数据,此外,控制字,命令字和状态信息也通过数据总线缓冲器传输,读/写控制逻辑电路用来配合数据总线缓冲器工作。

CPU通过数据总线缓冲器和读写控制逻辑向8251A写入工作方式和控制命令字,对芯片初始化;向8251A写入要发送字符的数据代码,送到发送缓冲器进行并行到串行的转换,并且将接收的、已转换成并行代码的接收缓冲器中的字符数据读入CPU。

第二部分是数据格式转换部分,包括发送缓冲器、并行数据到串行数据转换的发送移位器,接收缓冲器和串行数据到并行数据转换的接收移位器,以及发送控制电路和接收控制电路。

8251a有何特点-在串行通信中作用_8251a的工作方式

8251a有何特点-在串行通信中作用_8251a的工作方式8251a有何特点?在串行通信中作用_8251a的工作方式8251A的内部结构(1)接收器接收器包括接收缓冲器和接收控制逻辑两部分。

接收器的功能是接收在RXD引脚上的串行数据,并按规定的格式把它转换成并行数据,存放在数据总线缓冲器中。

①接收缓冲器接收缓冲器主要由移位寄存器和数码寄存器组成。

接收器接收传送到RXD(接收数据输入端)引脚上的串行数据,并对串行数据流的特殊位(奇偶位,停止位等)和字符(同步字符)进行检查、处理,按规定的格式将串行数据转换为并行数据存放在缓冲器中。

接收移位寄存器和接收数据缓冲器组成了双缓冲器结构。

②接收控制逻辑这一部分控制串行数据的接收,包括三条控制线:RXRDY(Receiver Ready)接收器准备好,输出,高电平有效。

RXC(Receiver Clock)接收时钟,输入。

SYNDET/BRKDET(SYNchronous DETect/BreaK DETect)同步检测/断点检测,输出/输入,高电平有效。

(2)发送器发送器包括发送缓冲器和发送控制逻辑两部分。

①发送缓冲器和发送过程发送数据缓冲器接收由CPU送来的并行数据,按初始化编程指定的数据格式转换成串行数据流送至发送移位寄存器,在TXC的下降沿从TXD引脚发送出去。

发送数据缓冲器和发送移位寄存器组成了发送的双缓冲器结构。

②发送控制逻辑该部分控制串行数据的发送操作,包括3条控制线:TXRDY(Transmitter ReaDy)发送器准备好,输出,高电平有效。

TXE(Transmitter Empty)发送器空,输出,高电平有效。

第4讲可编程串行通信接口芯片8251A

第4讲 可编程串行通信接口芯片8251A

例2:编写通过8251A采用查询方式接收数据 的初始化程序

将8251定义为:异步传送方式,波特率系数为 64偶校验,1位停止位,7位数据位.设8251A数 据口地址为06A0H,控制口地址为06A2H.

第4讲 可编程串行通信接口芯片8251A

MOV DX,06A2H MOV AL,7BH ;写工作方式控制字 OUT DX,AL MOV AL,14H ;写操作命令控制字 OUT DX,AL WAIT: IN AL,DX ;读入状态控制字 AND AL,02H JZ WAIT ;检查RxRDY是否为1 MOV DX,06A0H IN AL,DX ;输入数据

5.全双工,双缓冲的发送器和接收器.

6.具有三种错误检测功能:奇/偶,溢出和帧错误.

第4讲 可编程串行通信接口芯片8251A

8251A的内部工作原理图:

第4讲 可编程串行通信接口芯片8251A

第4讲 可编程串行通信接口芯片8251A

8251A芯片的初始化

为使8251配合cpu进行通信,通信之前: 1.约定双方的通信方式〔同步/异步〕,数据格式

3.单片机:把cpu、内存储器、输入输出 接口集成在一个芯片上所构成的微型计 算机.

INC DI

IN AL,0F1H

TEST AL,38H

;检测错误标志

JNZ ERROR

;出错,至错误处理

LOOP WAIT

第4讲 可编程串行通信接口芯片8251A

相关术语

1.微型计算机:把cpu、内存储器、输入 输出接口电路集成在若干芯片上,加上 控制电极和电源等所组成的计算机.

2.单板机:把cpu、内存储器、输入输出 接口电路装在一块印制电路板上所构成 的微型计算机.

可编程串行接口芯片8251A

停止位位数

图9.13 方式指令字各位含义

校验类型:1 偶校验;0 奇校验 S2 S1 00 0 1 1b 1 0 1.5b 1 1 2b

Hale Waihona Puke 1.3 8251A的编程接口技术

B2、B1位表示收发时钟与波特率的关系。

如当B2、B1置为10时,假设收发时钟频率为 19.2KHz,则表示8251A为异步方式,且波特 率为1200。

1.3 8251A的编程

接口技术

对8251A的编程是指由CPU写入控制字(包 括方式指令字和命令指令字)和读/写收发数 据,实现对8251A的各种工作方式以及工作进 程的控制。

8251A的编程包括初始化编程和收发数据过程 的编程两部分。

1.方式指令字

8251A方式指令字各位的定义如图9.13所示。

L2、L1指定串行异步通信中每个字符数据的 位数,可以在5~8位之间选择。

PEN位用来选择是否需要奇偶校验位。

EP位用来选择奇校验或偶校验,若EP=1, 则进行偶校验;若EP=0,则进行奇校验。

1.3 8251A的编程

接口技术

S2、S1用来指定异步方式下的停止位的位数, 可以选择1、1.5或2位。 在 同 步 方 式 ( B2、B1=00), 则 S1=1 为 外 同步,

1.3 8251A的编程

接口技术

1.方式指令字

8251A方式指令字各位的定义如图9.13所示。

D7 D6 D5 D4 D3 D2 D1 D0 S2 S1 EP PEN L2 L1 B2 B1

波特率因子

字符长度

B2 B1 00同步 011 1 016 1 164

L2 L1 005b 016b 107b 1 18b

8251芯片

可编程通信接口8251A(USART)1.8251A的基本结构8251A的基本结构包括5个功能模块(1)数据总线缓冲器——用于暂存接收,发送数据,CPU发来的命令及8251的工作状态。

(2)读/写控制逻辑——接收来自CPU控制总线的控制信号,控制数据的传送方向。

(3)接收器——从接收数据线RXD上接收串行数据,按指定方式将其转换成并行数据。

(4)发送器——接收CPU送来的并行数据,按指定方式将其转换成串行数据通过发送数据线TXD发送出去。

(5)调制解调器控制电路——提供4个通用的控制信号,即(数据终端准备好),(数据设备准备好),(请求发送)和(准许发送),以备8251A与外设联络。

2.8251A的工作过程(1)8251A发送数据的过程①当发送缓冲器为空时,信号TXRDY有效(或状态字的D0=1),以示发送器准备好,等待CPU送入数据。

②CPU将要发送的数据写入8251A的发送缓冲器;③发送的数据进行“并→串”转换;④插入起始位、奇/偶位和停止位或同步字符等,数据一位一位从TXD端串行输出。

(2)8251A接收数据的过程①在RXD端检测到起始位或同步字符;②开始在RXD线上采集数据;③将接收到的数据“串→并”转换,并进行奇偶校验和检查错误;④将采样到的、经过变换的8位数据由接收缓冲器送入数据总线缓冲器;⑤信号RXRDY有效(或状态字的D1=1),以示8251A已接收到一个数据,待CPU读取。

3.8251A的初始化在如前面已经强调过的,在使用可编程接口之前必须进行初始化,即在使用8251A进行数据传输前,对其进行编程,将相关方式指令字、命令指令字写入8251A。

8251A初始化的具体步骤如图7-3所示。

图7-3 8251A 初始化流程图4. CPU 对8251A 的操作和控制8251A 有两个端口地址,偶地址为输入/输出数据端口地址,奇地址为控制/状态端口地址。

引脚线C/与A 0连接:A 0=0,访问输入/输出数据端口A 0=1,访问控制/状态端口控制信号:、、C/、合成对8251A 的操作如表7-1所示。

可编程串行通信接口芯片8251A

逻辑低电平为+3V~+15V

逻辑高电平为-3V~-15V 实际常用±12V或±15V

相互转换

标准TTL电平 低电平:0V~0.8V 高电平:+2V~+5V

Page 16

RS-232C的引脚定义

RS-232C是一种标准接口,D型插座,采用25芯引 脚或9芯引脚的连接器,如图所示。

Page 5

1.串行数据传送方式

串行通信数据传送方式分为:单工通信方式、半双工通信 方式和全双工通信方式。 ⑴单工通信方式 传输的线路用一根线,通信的数据只允许按照一个固定的 方向传送。如图:只能从A站点传送到B站点。 A T B R

例: 单工通信类似无线电广播,电台发送信号,收音机 接收信号,收音机永远不能发送信号。

…

1

起始位——每个字符开始传送的标志,起始位 数据位——数据位紧跟着起始位传送。由5~8 校验位——用于校验是否传送正确;可选择奇 停止位——表示该字符传送结束。停止位采用 空闲位——传送字符之间的逻辑1电平,表示 采用逻辑0电平 个二进制位组成,低位先传送 检验、偶校验或不传送校验位 逻辑1电平,可选择1、1.5或2位 没有进行传送

收、发双方取得同步的方法是采用在字符格式中设置起始 位和停止位。

在一个有效字符正式发送前,发送器先发送一个起始位, 然后发送有效字符位,在字符结束时再发送一个停止位, 起始位至停止位构成一帧。

Page 9

异步通信数据格式

字符 数据位

起始位

校验位停止位 空闲位 0/1 0/1 1 1 高位

1

0

0/1 0/1 低位

Page 6

⑵半双工通信方式

传输的过程中依然用一根线连接,在某个时刻,只能迚行

串行通信和可编程串行接口芯片8251A

控制线的连接

控制线用于控制8251a芯片的工作方式和状态,如起始位、 停止位、波特率等。

控制线通常由微处理器通过编程设置,以实现串行通信的参 数配置和控制。

地址线的连接

地址线用于标识8251a芯片在系统中的地址,以便微处理 器能够正确寻址和访问。

02

movwf CR ; 将值写入CR寄存器

03 movlw 0x01 ; 设置IER寄存器,允许接收中断

初始化编程

movwf IER ; 将值写入IER寄存器

```ቤተ መጻሕፍቲ ባይዱ

数据发送编程

01 发送步骤

02

将数据写入发送缓冲寄存器(THR)。

03

通过设置控制寄存器(CR)的发送使能位启动发送过

程。

数据发送编程

编程控制

通过编程控制8251A的工作模式、 波特率、数据位、停止位等参数, 实现灵活的串行通信功能。

感谢您的观看

THANKS

05 串行通信协议及8251a的 应用

RS-232C协议

定义

RS-232C是一种标准的串行通信协议,用于 连接计算机和其他设备。

特点

采用单端信号传输方式,具有高电平、低电 平两种逻辑状态,传输距离较近。

应用

常用于连接计算机和调制解调器、打印机等 低速设备。

RS-485协议

定义

RS-485是一种改进的串行通信协议,克服了RS-232C传输距离较 近的限制。

• 数据发送代码示例

数据发送编程

01

```

02

movlw 0x12 ; 要发送的数据是0x12

03

8251A知识点总结

8251A 知识点总结1、 基本性能 (1)工作方式:⎩⎨⎧--k2.190640异步:波特率同步:波特率k(2)同步:5~8bit/字符,可以使用内部、外部同步检测,可自动插入同步字符,实现收发同步,允许增加1位奇偶校验位。

(3)异步:5~8bit/字符,时钟频率是波特率的1、16 、64倍。

(4)可产生终止符,产生1、1.5、2位停止位。

(5)可以单、半双、全双工通信。

(6)提供一些简单的控制信号,方便与modern 连接。

(7)具有奇偶、溢出和帧错误检测功能。

(1)I/O缓冲器(8位)⎪⎩⎪⎨⎧的数据或命令放入命令缓冲器:存放发送数据备送给已经装配好的字符,准接收数据缓冲器:存放查询内部状态信息供状态缓冲器:寄存A CPU CPU CPU A 8251/8251 (2)读/写控制电路:接收来自CPU 的控制信号,并对内部总线上的数据传送方向进行控制,实际上是8251A 的内部控制器。

(3)接收器:从RxD 引脚接收串行数据,并按格式转换为并行数据,存放在I/O 缓冲器的接收数据缓冲器中。

(4)发送器:从CPU 接受并行数据,加上适当的字符格式信号,把数据由并行变串行,从TxD 引脚串行发送出去。

3、工作方式8251A的工作方式由CPU执行的程序设定的,发送与接受数据之前必须友CPU送出一组控制命令字来预置8251A,分为:方式控制指令和命令指令。

方式选择字必须跟在复位命令之后,之后才可以写入同步字符和命令字指令。

8251A的方式选择字示意图之后必须加入命令字状态字示意图CPU通过读取状态字获取接口与外设等的状态。

(1)FE=1时,帧格式错,在异步方式下,当下一个字符终了而没有检测到规定的停止位时的差错。

(2)OE=1时,超越错误,CPU未读完这个字符,而下一个字符已经到来,OE=1,出现这个错误时,上一个字符将丢失。

3、8251A的初始化编程初始化流程:(1)控制字,以决定通信方式,数据位数,校验方式等。

8251a有几个端口地址_对8251a进行初始化及流程

8251a有几个端口地址_对8251a进行初始化及流程

8251a内部结构框图8251A是一种可编程的通用同步/异步接收发送器,通常作为串行通信接口使用,被广泛应用Intel80X86为CPU的微型计算机中。

8251a有几个端口地址8251a有两个连续的端口地址,数据输入端口和数据输出端口合用同一个偶地址,而状态端口和控制端口合用同一个奇地址。

8251A初始化编程流程及程序例:8251A工作于异步方式,方式选择控制字为11111011B,工作命令控制字为00010001B。

其初始化程序为:

…

MOV AL,0FBH ;8251A方式选择字

OUT CONTR,AL

MOV AL,11H ;8251A操作命令字

OUT CONTR,AL

…

8251A的应用举例例:微机系统中两台微机之间进行双机串行通信的硬件连接和软件编程。

(1)要求

在甲乙两台微机之间进行串行通信,甲机发送,乙机接收。

要求把甲机上开发的应用程序(其长度为2DH)传送到乙机中去。

双方采用起止式异步方式,通信的数据格式为,字符长度为8位,2位停止位,波特率因子为64,无校验,波特率为4800。

CPU与8251A之间用查询方式交换数据,8251A的端口地址分配是:309H为命令/状态口,308H为数据口。

(2)分析

由于是近距离传输,因此可以不设MODEM,两台微机之间直接通过RS-232标准接口连接即可。

同时是采用查询I/O方式,故收/发程序中只需检查发/收准备好的状态是否置位,即可收发l个字节。

第七章终结篇——8251A的总结

第七章终结篇——8251A的总结总算把这个第七章复习完了,我把剩下⼀点关于8251A的发上来吧本来在讲解8251A书本上还有关于RS232和串⼝通信的讲解,但是太浅了,就不放了,有兴趣的朋友可以⾃⾏参考其他⽂章串⾏通信芯⽚8251A有以下特点1. 可以⽤于同步或者异步传输,同步0-64kbps,异步0-19.2kpbs2. 同步传送的时候,5-8位/字符,可以⽤于内同步或者外同步,可⾃动插⼊同步字符3. 异步传送的时候,5-8位/字符,有1,2,1.5个停⽌位4. 完全双⼯,双缓冲发送和接受数据5. 具有出错检查,奇偶校验、溢出、和帧错误等检测电路好吧,为啥要这个8251A因为计算机内部都是并⾏传输数据的,但是长距离通信都是⽤的串⾏通信的(这些概念不太明⽩的不懂的朋友可以⾃⾏百度⼀下概念或者看看书)必须要个东西来转化⼀下82518251的内部结构内部结构包括接收器,发送器,读/写控制逻辑,数据总线缓冲器和调制解调控制电路五⼤部分接收器包括接收缓冲器,并⾏转换逻辑和接受控制电路三个部分接收缓冲器对外引脚为RxD,功能是从此引脚上接收串⾏数据,然后转换成并⾏数据,是由接受移位寄存器和接收数据缓冲器组成双缓冲结构接受控制电路是配合缓冲器⼯作的,作⽤如下1 .在异步⽅式下,芯⽚复位后,先检测输⼊信号中的有效1,⼀旦检测到到,就接着寻找有效的低电平来确定启动位2 消除假启动⼲扰3 对接收到的信息进⾏奇偶校验,并根据校验结果建⽴相应的状态位4 检测停⽌位,并按检测结构建⽴状态位发送器和接收器差不多,也是有发送缓冲器,发送控制电路和并串转换逻辑3个部分发送缓冲器上⾯接的是TxD脚,发送数据缓冲器和发送移位寄存器组成了发送的双缓冲结构,发送控制电路也是辅助发送缓冲器的,但是和接受的功能不⼀样发送控制电路作⽤如下1. 在异步⽅式下插⼊起始位,校验位和停⽌位2. 在同步⽅式下,插⼊同步字符,在数据中插⼊校验位数据总线缓冲器提供与8251A和CPU系统总线相连,在CPU执⾏输⼊输出操作的时候,进⾏数据交换或者读写命令读/写控制逻辑电路⽤来配合总线缓冲器⼯作1. 写信号WR#,把数据总线的信号(数据/控制字)写⼊8251A2. 读信号RD#,将状态/数据字发送到CPU(发到数据总线)3. 接收控制/数据信号C/D#,与读。

8-3串行接口芯片8251A

串行接口芯片8251A8251A基本功能⏹可用于同步和异步通信方式(通信方式通过对方式字编程实现):☐同步方式:波特率0-64Kbps,每个字符可为5~8位,可使用内部同步检测和外部同步检测,能自动插入同步字符。

☐异步方式:波特率0-19.2Kbps,每个字符可为5~8位,自动增加起始位、停止位和校验位。

时钟TxC,RxC的时钟频率为传输波特率的1,16和64倍。

⏹全双工,具有双缓冲器接收器和发送器;⏹出错检测,具有奇偶、溢出和帧错等检测电路。

8251A的内部结构8251A的内部结构主要包括:数据总线缓冲器、接收缓冲器、接收控制电路、发送缓冲器、发送控制电路、调制/解调控制电路、读/写控制逻辑电路等数据总线缓冲器发送缓冲器发送控制电路接收缓冲器接收控制电路D0~D7SYNDETRxDRxRDY读写控制电路C / DCLKRESETRDWRCSDSRCTSDTRRTSRxCTxCTxETxRDYTxD调制解调控制电路内部总线8251A的内部结构⏹发送器:包括发送缓冲器和发送控制电路☐采用异步方式时,则由发送控制电路自动在其首尾加上起始位、奇偶校验位和停止位,然后从起始位开始,经移位寄存器从数据输出线TxD逐位串行输出。

发送速率取决于TxC接收的发送时钟频率,可以编程定义是发送速率的1、16、64倍。

8251A的内部结构☐采用同步方式,则在发送数据之前,发送器将自动送出1个或2个同步字符,然后才逐位串行输出数据。

◆如果CPU与8251A之间采用中断方式交换信息,那么TxRDY可作为向CPU发出的中断请求信号,表示发送缓冲器已空,可以接收CPU下一个数据。

◆当发送器中的8位数据串行发送完毕时,由发送控制电路向CPU发出TxE有效信号,表示发送器中移位寄存器已空。

8251A的内部结构⏹接收器:包括接收缓冲器和接收控制电路从RxD引脚上接收串行数据转换成并行数据后存入接收缓冲器。

☐异步方式:在RxD线上检测低电平,将检测到的低电平作为起始位,8251A开始进行采样,完成字符装配,并进行奇偶校验和去掉停止位,变成了并行数据后,送到数据输入寄存器,同时发出RxRDY信号送CPU,表示已经收到一个可用的数据。

可编程串行通信接口芯片8251A

• 2)在同步发送方式中,发送缓冲器在准备发送的数据前面先插入由初始化程序设 定的一个或两个同步字符,在数据中插入奇偶校验位。然后在发送时钟TXC的作用 下,将数据逐位地由TXD引脚发送出去。

能根据编程为每个字符设置1个、1.5个或2个停止位。 • (4)所有的输入输出电路都与TTL电平兼容。 • (5)全双工双缓冲的接收/发送器。

2

1.1 8251A内部逻辑与工作原理

• 8251A的结构框图如图1.1所示,可分五个主要部分:写控制逻辑电路和调制解调控制电路。

6

(3)接收缓冲器

• 1)在异步接收方式,当“允许接收”和“准备好接收数据”有效时,接收缓冲器 监视RXD线。在无字符传送时,RXD线上为高电平,当RXD线上出现低电平时,即 认为它是起始位,就启动接收控制电路中的一个内部计数器,计数脉冲就是8251A 的接收时钟脉冲RXC,当计数器计到一个数据位宽度的一半(若时钟脉冲频率为波 特率的16倍,则计数到第8个脉冲)时,又重新采样RXD线,若其仍为低电平,则 确认它为起始位,而不是噪声信号。

17

• 1.方式选择控制字:根据题意,方式选择控制字为00111000B(即38H),写入控 制端口,端口地址为91H。

• 2.命令控制字:设置为10010111B(即97H),使8251A进入同步字符检测,出错 标志复位,允许发送和接收,置引脚有效,写入控制端口,端口地址为91H。

• 3.同步字符:2个同步字符,均为3AH。 • 4.初始化程序:

9

1.3 8251A的控制字

串行通信和可编程接口芯片8251A

ABCD

发送数据

通过将数据写入到8251A的数据寄存器中,然 后启动发送过程。

错误检测与处理

在数据传输过程中,应进行错误检测,如奇偶校 验、帧错误等,并采取相应的处理措施。

使用8251A芯片进行数据传输的示例

设置参数

首先,配置8251A的寄存器以设置数据传输 参数,如数据格式、波特率等。

发送数据

将要发送的数据写入到8251A的数据寄存器 中,然后启动发送过程。

03 8251A芯片与串行通信的 结合

8251A芯片在串行通信中的作用

数据传输

8251A芯片作为串行通信接口, 能够实现数据在串行通道上的传 输,包括发送和接收。

协议转换

8251A芯片可以将并行数据转换 为串行数据,或者将串行数据转 换为并行数据,实现不同协议之 间的转换。

信号调制与解调

8251A芯片可以对信号进行调制 和解调,以适应不同的传输介质 和距离要求。

工业控制

02

03

智能仪表

在工业控制系统中,传感器和执 行器之间的通信通常使用串行通 信。

பைடு நூலகம்

智能仪表之间的通信通常使用串 行通信,例如通过RS-485总线进 行数据传输。

02 8251A芯片介绍

8251A芯片的特点

高度集成

01

8251A是一款高度集成的串行通信芯片,内部包含波特率生成

器、数据接收器和发送器等模块。

异常处理

在协议转换过程中,应处理可能出现的异常情况,如协议不匹配、 数据格式错误等。

05 8251A芯片的常见问题与 解决方案

8251A芯片无法正常工作的问题及解决方案

总结词

无法正常工作

详细描述

8251A芯片无法正常工作可能是由于电源问题、接口连接不良、芯 片损坏等原因。

8251芯片

接收端初始化程序和接收控制程序

2、发送器DB 数据发送来自冲器工作过程 CPU执行输出指令, 并行数据→发送缓冲器。

发送缓冲器→发送移位寄 存器,向CPU提出中断

异 或 门 0

内部 CLK ÷

申请(TxRDY=1)。

波 特 率

TXD SOUT

内部产生起始、奇偶 检验、停止位,按约定 的波特率从TxD输出。 当数据全部输出结束, 在TXD发出连续低电平 (TxE=1)。

2.两台微型计算机通过8251A相 互通信的举例

分析:初始化程序由两部分组成: ⑴是将一方定义为发送器。发送 端CPU每查询到TXRDY有效,则 向8251A并行输出一个字节数据; ⑵是将对方定义为接收器。接收 端CPU每查询到RXRDY有效,则 从8251A输入一个字节数据,一直 进行到全部数据传送完毕为止。

M O D E M 波特率 发生器

电 话 线 接 口

RTS(Request to Send)数据终端向 MODEM发出请求表 示数据已准备好需 要发送

8251A

RxC TxC 数据终端设备DTE

电 CTS(Clear to Send) 话 MODEM回应终端, 线 若TxEN有效8251可

以发送数据,发送 结束CTS=“1”。

输出第一个同步字符 双同步 输出第二个同步字符

N

输出命令字 复位 传送数据

Y

N

输入状态字

N

传送完

Y

1. 8251复位 电源上电,8251自动进入复位状态,为了确保在送方式字 和命令字之前8251正确复位,可向8251的控制口连续写 入3个“0”,然后再写入一个复位控制字(40H),用软 件使8251可靠复位。 注:对8251的控制口进行一次写入操作,需有写恢复时间。 (写恢复时间一般为16个时钟周期) DELAY1: MOV CX,02H

8251芯片介绍

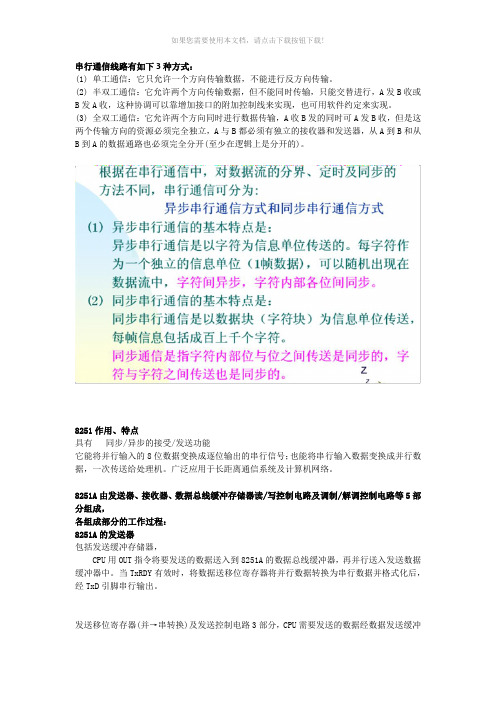

串行通信线路有如下3种方式:(1) 单工通信:它只允许一个方向传输数据,不能进行反方向传输。

(2) 半双工通信:它允许两个方向传输数据,但不能同时传输,只能交替进行,A发B收或B发A收,这种协调可以靠增加接口的附加控制线来实现,也可用软件约定来实现。

(3) 全双工通信:它允许两个方向同时进行数据传输,A收B发的同时可A发B收,但是这两个传输方向的资源必须完全独立,A与B都必须有独立的接收器和发送器,从A到B和从B到A的数据通路也必须完全分开(至少在逻辑上是分开的)。

8251作用、特点具有同步/异步的接受/发送功能它能将并行输入的8位数据变换成逐位输出的串行信号;也能将串行输入数据变换成并行数据,一次传送给处理机。

广泛应用于长距离通信系统及计算机网络。

8251A由发送器、接收器、数据总线缓冲存储器读/写控制电路及调制/解调控制电路等5部分组成,各组成部分的工作过程:8251A的发送器包括发送缓冲存储器,CPU用OUT指令将要发送的数据送入到8251A的数据总线缓冲器,再并行送入发送数据缓冲器中。

当TxRDY有效时,将数据送移位寄存器将并行数据转换为串行数据并格式化后,经TxD引脚串行输出。

发送移位寄存器(并→串转换)及发送控制电路3部分,CPU需要发送的数据经数据发送缓冲存储器并行输入,并锁存到发送缓冲存储器中。

如果是采用同步方式,则在发送数据之前,发送器将自动送出一个(单同步)或两个(双同步)同步字符(Sync)。

然后,逐位串行输出数据。

如果采用异步方式,则由发送控制电路在其首尾加上起始位及停止位,然后从起始位开始,经移位寄存器从数据输出线T X D逐位串行输出,其发送速率由T X C端上收到的发送时钟频率决定。

当发送器作好接收数据准备时,由发送控制电路向CPU发出T X RDY有效信号,CPU立即向8251A 并行输出数据。

如果8251A与CPU之间采用中断方式交换信息,那时T X RDY作为向CPU发出的发送中断请求信号。

串行接口芯片8251A课件

THANKS

感谢观看

06

8251A芯片应用案例

应用场景一:串行通讯系统

总结词

8251A芯片在串行通讯系统中发挥着关键作用,能够实现数据的高速传输和可靠通讯。

详细描述

在串行通讯系统中,8251A芯片作为主控制器与多个从设备进行数据交换。通过设置不同的波特率和数据位,可 以灵活地适应不同的通讯协议和传输速率。同时,8251A芯片还支持奇偶校验和流控制功能,提高了数据传输的 可靠性和稳定性。

串行接口芯片8251a课件

contents

目录

• 8251A芯片概述 • 8251A芯片工作原理 • 8251A芯片编程与控制 • 8251A芯片接口技术 • 8251A芯片调试与测试 • 8251A芯片应用案例

01

8251A芯片概述

芯片简介

8251A是Intel公司生产的一款可编程的串行接口芯片,用于实现计算机与外部设备 之间的串行通讯。

编程实例与演示

01

02

03

04

设置波特率

演示如何设置8251A的波特 率,以便控制数据传输速率。

数据发送与接收

演示如何通过8251A发送和 接收数据。

中断处理

演示如何处理8251A产生中 断的情况。

多机通讯

演示如何使用8251A实现多 机通讯。

04

8251A芯片接口技术

接口类型与规范

接口类型

8251A芯片支持同步和异步串行通讯 接口,包括RS-232、RS-422和RS485等类型。

在工业自动化领域,8251A芯片可以 用于实现计算机与机器人、传感器等 设备之间的通讯和控制。

数据采集与控制系统

在数据采集与控制系统中,8251A芯 片可以用于实现计算机与各种外表和 控制设备之间的通讯。

8251A可编程串行接口芯片

• CTS # :允许传送,是输入信号,低电平有效。 允许传送,是输入信号,低电平有效。 通常是MODEM对8251A的信号的响应,当 的信号的响应, 通常是 对 的信号的响应 CTS#有效且工作命令字中的 有效且 位为1时 有效 工作命令字中的TxE位为 时 位为 8251A方可发送数据。 方可发送数据。 方可发送数据 • 如果在发送器工作过程中,TxE位变为 或 如果在发送器工作过程中, 位变为0或 位变为 CTS #变为无效,则发送器关闭之前要将已经 变为无效, 变为无效 写入的所有数据发送出去后才关闭。 写入的所有数据发送出去后才关闭。如果在最 后一个字符出现在串行数据流之前出现这种状 则最后一个字符将在CTS #变为有效和 况,则最后一个字符将在 变为有效和 TxE变为 时再发送一次。 变为1时再发送一次 变为 时再发送一次。

• CLK:工作时钟,由外部时钟源提供。为芯片 :工作时钟, 外部时钟源提供。 提供 内部电路提供定时, 内部电路提供定时,并非发送或接收数据的时 在同步方式下, 的频率要大于接收器 钟。在同步方式下,CLK的频率要大于接收器 或发送器输入时钟(RxC或TxC)频率的 倍。 频率的30倍 或发送器输入时钟 或 频率的 在异步方式下, 在异步方式下,CLK的频率要大于接收器或发 的频率要大于接收器或发 送器输入时钟频率的4.5倍 另外, 送器输入时钟频率的 倍。另外,CLK的周 的周 期要在0.4µs到1.35µs范围内。 范围内。 期要在 到 范围内

• TxRDY(Transmitter Ready):发送器准备好,输出, :发送器准备好,输出, 高电平有效。当它有效时, 高电平有效。当它有效时,表示发送器已准备好接收 CPU送来的数据字符,通知 送来的数据字符, 可以向8251A发送数 送来的数据字符 通知CPU可以向 可以向 发送数 据。CPU向8251A写入了一个字符以后,TxRDY自 向 写入了一个字符以后, 自 写入了一个字符以后 动复位。在用查询方式时,此信号作为一个状态位, 动复位。在用查询方式时,此信号作为一个状态位, CPU可从状态寄存器的 位检测这个信号;在用中 可从状态寄存器的D0位检测这个信号 可从状态寄存器的 位检测这个信号; 断方式时,此信号作为中断请求信号。 断方式时,此信号作为中断请求信号。 • TxEMPTY(Transmitter Empty):发送器空,输出, :发送器空,输出, 高电平有效。当它有效时, 高电平有效。当它有效时,指示发送器中的数据已发 送出去,已经没有要发送的字符了。当8251A从CPU 送出去,已经没有要发送的字符了。 从 接收待发的字符后,自动复位。 接收待发的字符后,自动复位。TxEMPTY既然表示 既然表示 发送已经结束,这样在半双工方式中, 半双工方式中 发送已经结束,这样在半双工方式中,CPU就从它知 就从它知 道何时切换数据的传输方向,由发送转为接收。 道何时切换数据的传输方向,由发送转为接收。此信 号可从状态寄存器的D2位检测到 位检测到。 号可从状态寄存器的 位检测到。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

⑸ 8251A与外设间的联络线和信号线

DTR——数据终端准备好信号输出端,当DTR=0时, 表示8251A已接收CPU发来的字符,准备向外设发送;

DSR——数据设备准备好信号输入,当DSR=0时,表示 外设已准备好,CPU可以经8251A向外设传送1个字符;

RTS——请求发送信号输出,当RTS=0时,表示 8251A已准备好发送字符;

TXE——发送器空信号,为1时表示串行输出信号发送 完毕,在同步方式下,若CPU未来及时送出字符,则 8251A自动填入空字符来补充间隙;

RXRDY——接收器准备好信号,为1时表示8251A从外 设或调制解调器中接收到1个字符,通知CPU来取走, CPU取走后 RXRDY=0;

SYNDET——同步检测信号(仅用于同步方式),为1 时,表示8251A检测到同步字符。

操作命令控制字格式

EH IR RTS ER SBRK RXE DTR TXEN

外部搜索方式 1:启动搜索同

步字符

错误标志复位 1:全部错误标

志复位

接收允许 0:屏蔽 1:允许

发送允许 0:屏蔽 1:允许

请求发送 1:迫使RTS输出低

数据终端准备好 1:迫使DTR输出低

内部复位

送中止字符

1:返回方式指令格式 1:迫使TXD输出低 0:正常工作

1 0 1 CPU读8251A的状态 1 1 0 CPU向8251A写控制命令

在IBM-PC机中,串行通信口的地址(保留) 口1:3F8H~3FFH 口2:2F8H~2FFH

偶地址 奇地址

⑷ CPU的收发联络信号

TXRDY——发送准备好信号,为1时表示8251A作好 发送准备,CPU可以向其发送1个字符,发送结束后, TXRDY=0;

例:每秒钟传送120个字符,而每个字符由10位数据位 组成,则传送的波特率为:

fd= 10×120=1200 bit/s=1200波特 或称为1200 bps。

标准:110/300/600/1200/1800/2400/4800/9600/19200

有时也用位周期(Td)来表示传输速度,表示每一位的 传送时间,是波特率的倒数。

‘A’:41H=1000001B 100000111

字符‘C’的数据格式为:

‘C’:43H=1000011B 110000101

练习:设异步通信数据格式为7位数据、1位奇校验 和1位停止位,则字符‘9’的数据格式为:

‘ 9 ’: 39H=0111001B 1 0 01 1 1 0 1 1

②数据传送速率 ——每秒钟传输数据的位数(波特率)

③发送时钟与接收时钟

异步通信中,发送端和接收端各用一个时钟来确定发送 和接收的速率,分别称为发送时钟和接收时钟。

这两个时钟的频率fc和数据传输速率fd的关系为: fc = Kfd

其中K称为波特率系数,取值可为16、32或64

④校验方式

发送时在传送的字符后自动在奇偶校验位置上添加1或 0,使得字符1的个数(包括校验位)为偶数(偶校验) 或奇数(奇校验);

计

计

算 机

算

或

机

外

设

微机系统在串行通信时必须进行串行与并行的转换

2. 同步方式和异步方式 •异步串行方式

发送和接收两地不用同一时钟同步的数据传输方式; 一般以若干位表示一个字符,收发以字符为独立的 通信单位,每个字符出现的时间是任意的。 为了保证异步通信的正确,必须在收发双方通信前 约定字符格式、传送速率、时钟和校验方式等。

3. 8251A的引脚功能 ⑴ 数据线D7~D0——双向、三态,用于与CPU传 送数据、命令、状态等信息;

⑵ 片选CS——用于芯片寻址; ⑶ 读写控制RD,WR; (4) C D 控制/数据选择信号(输入)

C/D(A0)RD WR功能 0 0 1 CPU从8251A输入数据 0 1 0 CPU向8251A输出数据

OUT DX,AL

MOV DI,RBUFF ;接收数据缓冲区首地址送DI

MOV CX,80

;计数器赋初值

COMT:MOV DX,RCONT ;读取状态字

IN AL,DX

TEST AL,02H

;RxRDY有效否?

JZ COMT

;无效,继续等待

AND AL,38H

;有效,查询接收过程有无错误?

5.串行总线接口标准 一个完整的串行通信系统除对通信规程、定时控制有 规定外,在电气连接上也有接口标准。 常用的有以下串行接口标准:

①RS-232C接口标准; ②电流环接口标准; ③RS-422、RS-423和RS-485接口标准。

看教材P292~296

8.3.2 串行接口芯片8251A

1. 8251A的基本性能

RXC——接收器时钟

同步方式:RXC为接收时钟的波特率; 异步方式:RXC可以为波特率的1、16或64倍——波 特因子。

注:实际使用时,RXC与TXC并接

4. 8251A的编程

8251A使用前必须进行初始化,以确定工作方式、传 送速率、字符格式以及停止位长度等;

改变8251A的工作方式时必须再次进行初始化编程;

状态字格式

DSR SYNDET FE OE PE TXE RXRDY TXRDY

奇偶错误 溢出错误 帧错误(仅异步) 与8251的同名引脚同定义

与引脚

TXRDY

有差别

•编程方法

8251A初始化编程 及数据传送流程图

5 应用举例 例8.5 利用8251A实现两台微型计算机的远距离通信

设采用半双工查询方式,异步传送,一方定义为发 送器,另一方为接收器。当发送端CPU查询到 TxRDY有效时,向825lA并行输出一字节数据;接 收端CPU每查询到RxRDY有效,则从8251A并行输 入一个字节数据,一直进行到全部数据传送完为止。

0.3V

+3V——+V

2. 8251A的内部结构

I/O缓冲器——将8251A与系统数据总线相连,包含3 个8位缓冲寄存器: ➢发送数据/命令缓冲器接受CPU输出的数据或命令; ➢接收数据缓冲器暂存接收器送来的数据; ➢状态缓冲器寄存8251A的各种状态信息。

读/写控制电路——接收来自CPU的控制信号和控制 字,译码后向8251A各功能部件发出有关的控制信号, 因此它实际上是8251A的内部控制器。

8251A有两个控制字和一个状态字: ➢方式选择控制字:用于规定8251A的工作方式 ; ➢操作命令控制字:使8251A处于规定的工作状态,

以准备接收或发送数据 ➢状态字:寄存8251A的工作状态

方式选择控制字格式

D7 D6 D5 D4 D3 D2 D1 D0

奇偶校验

X0:无校验 01:奇校验 11:偶校验

8.3 串行接口芯片8251A

8.3.1 关于串行通信的基本概念

1. 并行通信和串行通信 ❖并行通信——指数据的各位同时进行传送的方式。 其特点是传输速度快;但当传输距离远,位数多时 导致通信线路复杂、成本高。

D0

D1

D2

计

D3

计 算 机

算

D4

或

机

D5

外

D6

设

D7

❖串行通信——指只需一条数据线便可进行数据传送, 数据的各位是按规定的顺序一位一位传送的通信方 式。其特点传输线简单,可利用多种介质,适用于 远距离通信,成本较低;但速度较慢。

①字符格式——字符的编码形式及规定 每个串行字符由以下4部分组成:

起始位(1位,低电平); 数据位(5~8位); 奇偶校验位(1位); 停止位(1、1.5或2位,高电平)。

1 到 0 的跳变作为字符的开始

LSB 起始位

MSB 字符间隔(均为 1)

1、1.5 或 2 个停止位(均为 1) 1 位可选的奇偶校验位 5 到 8 位的数据位,低位在前,高位在后

Modem控制电路——用以控制825lA与调制解调器之间 的信息传送。

接收器——接收来自RxD引脚上的串行数据,并按设 定的格式将其转换为并行数据,存放在I/O缓冲器的接 收数据缓冲器中。

异步、同步不同,详见P297

发送器——锁存CPU输出的数据,把数据由并行变串 行,从TxD引脚串行发送出去。 异步、同步不同,详见P297

常见的几种格式如教材P290图8.29

同步传送速度高于异步传送,传送效率高;但同步传 送要求发送端和接收端使用同一时钟,故硬件电路比 较复杂。

3. 单工、半双工和全双工 ➢单工方式——只收不发或只发不收

➢半双工方式——接收和发送使用一条通信线,收/发 分时进行

➢全双工方式——接收(输入)和发送(输出)可以 同时进行(收/发各使用1条通信线)

Y

SYN?

N

同步控制

X0:内同步 X1: 外同步 0X: 两同步字符 1X: 单同步字符

帧控制

00:不确定 01: 1停止位 10: 1.5停止位 11: 2停止位

字符长度

00:5位 01: 6位 10: 7位 11: 8位

波特率系数

00:同步方式 01:异步 X 1 10:异步 X16 11:异步 X64

OUT DX,AL

MOV DI,TBUFF ;发送数据块首地址送DI

MOV CX,80

;计数器赋初值

NEXT:MOV DX,TCONT ;读取状态字

IN AL,DX

AND AL,0lH

;TxRDY有效否?

JZ NEXT

;无效,继续等待

MOV DX,TDATA ;有效,向8251A输出一字节数据

MOV AL,[DI]

而接收时,要检查所接收的字符及其校验位是否符合 规定,若不符合规定就置出错标志,供CPU查询处理。 CCITT的建议,在异步通信中使用偶校验,而在同步 通信中使用奇校验。

•同步串行方式 以一组字符组成一个数据块(或称信息帧),在每