NT78C5DC9V0.8中文资料

uPD780055GCA-xxx-8BT资料

Detaileபைடு நூலகம் function descriptions are provided in the following user’s manuals. Be sure to read them before

64-pin 42/44-pin

Control

µPD78075B µPD78078 µPD78070A

µ PD780058 µPD78058F µPD78054 µPD780065 µPD780078 µPD780034A µPD780024A µPD78014H µPD78018F µPD78083

µPD78005xY(A)) are products of the µPD780058Y Subseries in the 78K/0 Series. These microcontrollers show a reduction in the EMI (Electro Magnetic Interference) noise generated internally

DATA SHEET MOS INTEGRATED CIRCUIT

µPD780053(A), 780054(A), 780055(A), 780056(A), 780058B(A), 780053Y(A), 780054Y(A), 780055Y(A), 780056Y(A), 780058BY(A)

78K/0 Series

Products in mass production

NTE78中文资料

Note 1. Pulse test: e = 5%.

元器件交易网

.420 (10.67) Max .110 (2.79)

.147 (3.75) Dia Max

.500 (12.7) Max

.250 (6.35) Max .500 (12.7) Min .070 (1.78) Max Base .100 (2.54)

Emitter Collector/Tab

元器件交易网

NTE78 Silicon NPN Transistor RF Power Output

NT78US5DC9V0.8中文资料

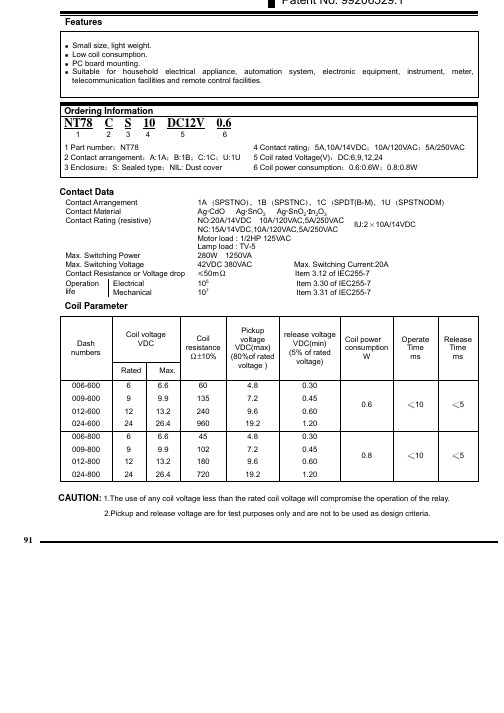

Dash numbers

Coil resistance ±10%

Coil power consumption W

Operate Time ms

R9-600 012-600 024-600 006-800 009-800 012-800 024-800 6 9 12 24 6 9 12 24

Max. 6.6 9.9 13.2 26.4 6.6 9.9 13.2 26.4 60 135 240 960 45 102 180 720

CAUTION: 1.The use of any coil voltage less than the rated coil voltage will compromise the operation of the relay.

1 Part number:NT78 2 Contact arrangement:A:1A;B:1B;C:1C;U:1U 3 Enclosure:S: Sealed type;NIL: Dust cover

Contact Data

Contact Arrangement Contact Material Contact Rating (resistive) 1A SPSTNO f1B SPSTNC f1C SPDT(B-M)f1U SPSTNODM Ag CdO Ag SnO2 Ag SnO2 In2O3 NO:20A/14VDC 10A/120VAC,5A/250VAC IU:2y10A/14VDC NC:15A/14VDC,10A/120VAC,5A/250VAC Motor load : 1/2HP 125VAC Lamp load : TV-5 280W 1250VA 42VDC 380VAC Max. Switching Current:20A 50m Item 3.12 of IEC255-7 105 Item 3.30 of IEC255-7 107 Item 3.31 of IEC255-7

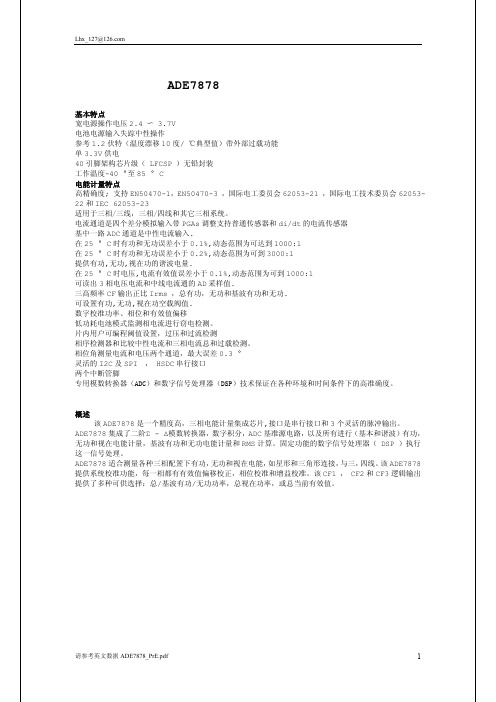

ADE7878中文数据资料

SCLK 上升沿之后的数据保持时间 数据输出下降沿时间

tDHD tDF

数据输出上升沿时间

tDR

SCLK 上升沿时间

tSR

SCLK 下降沿时间

tSF

标准模式

快速模式机 单位

50

ns

400

ns

175

ns

175

ns

5

40

ns

20

ns

5

ns

20

ns

20

ns

20

ns

20

ns

请参考英文数据 ADE7878_PrE.pdf

超出所列的极限参数可能引起器件的永久性损坏。以上给出的仅仅是极限范围,在这样的极 限条件或超出这些条件工作,器件的技术指标将得不到保证。长期将在这种极限条件下工作 还会影响器件的可靠性。 静电警告 ESD(静电放电)敏感的器件,带电的设备和电路板在没有觉察的情况下放 电。尽管这种产品具有独特的静电放电保护电路,但高能量的静电放电仍可能造成 器件的永久性损坏。因此,建议采取适当的静电放电预防措施避免器件性能下降或 功能丧失。

请参考英文数据 ADE7878_PrE.pdf

输入高电平 VINH

2.4

输入低电平 VIHL

0.8

输入电流,Iin

+-3

输入电容 Cin

10

逻辑输出-IRQ0,IRQ1,MISO/HSDA

请参考英文数据 ADE7878_PrE.pdf

mV peak,Max K欧姆 mV max % typ

dB typ dB typ KHz

V max

pF max

mV max K欧姆 ppm/℃ typ ppm/℃ max

V max mV typ

SM78L08中文资料

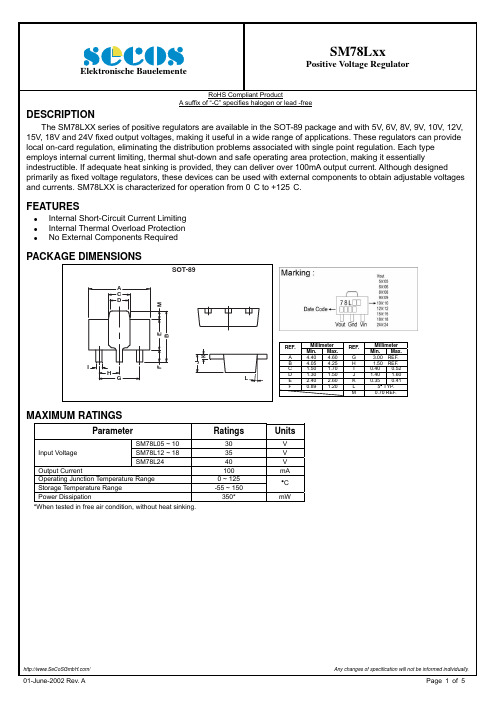

DESCRIPTION

The SM78LXX series of positive regulators are available in the SOT-89 package and with 5V, 6V, 8V, 9V, 10V, 12V, 15V, 18V and 24V fixed output voltages, making it useful in a wide range of applications. These regulators can provide local on-card regulation, eliminating the distribution problems associated with single point regulation. Each type employs internal current limiting, thermal shut-down and safe operating area protection, making it essentially indestructible. If adequate heat sinking is provided, they can deliver over 100mA output current. Although designed primarily as fixed voltage regulators, these devices can be used with external components to obtain adjustable voltages and currents. SM78LXX is characterized for operation from 0°C to +125°C.

LN78资料

R0.6

Symbol PD IF IFP

*

Ratings 180 100 1 3 –25 to+85 –30 to +100

Unit mW mA A V ˚C ˚C

1: Cathode 2: Anode

VR Topr Tstg

f = 100 Hz, Duty cycle = 0.1 %

Electro-Optical Characteristics (Ta = 25˚C)

Parameter Radiant power Peak emission wavelength Spectral half band width Forward voltage (DC) Reverse current (DC) Capacitance between pins Half-power angle Cutoff frequency

10 –1

0

1

2

3

4

5

Ambient temperature Ta (˚C )

Duty cycle (%)

Forward voltage VF (V)

∆PO — IFP

10 2 (1) tw = 10µs f = 100Hz (2) DC Ta = 25˚C (1) 2.2

VF — Ta

10

∆PO — Ta

*

Symbol PO λP ∆λ VF IR Ct θ fC*

Conditions IF = 50mA IF = 50mA IF = 50mA IF = 100mA VR = 3V VR = 0V, f = 1MHz

The angle in which radiant intencity is 50%

78D09中文资料

MIN

7.7 7.6

TYP

8.0

MAX

8.3 8.4 80 40 80 80 8.0 1.0 0.5

UNIT

V V mV mV mV mV mA mA mA uV mV/ C dB A mA V

Vo

56

58 -0.9 72 1.2 250 2.0

Contek78D09 ELECTRICAL CHARACTERISTICS

35 40 0.5 Limited +150 -65 to+150

UNIT

V V A W C C

Power Dissipation Operating Junction Temperature Range Storage Temperature Range

Contek78D05 ELECTRICAL CHARACTERISTICS

Vo

Iq DIq DIq VN DVo/DT RR IPK ISC Vd

56

58 -1.1 72 1.2 250 2.0

Contek Microelectronics Co.,Ltd.

V78XX-1000中文资料

rev. page date 1 of 4

04/2008

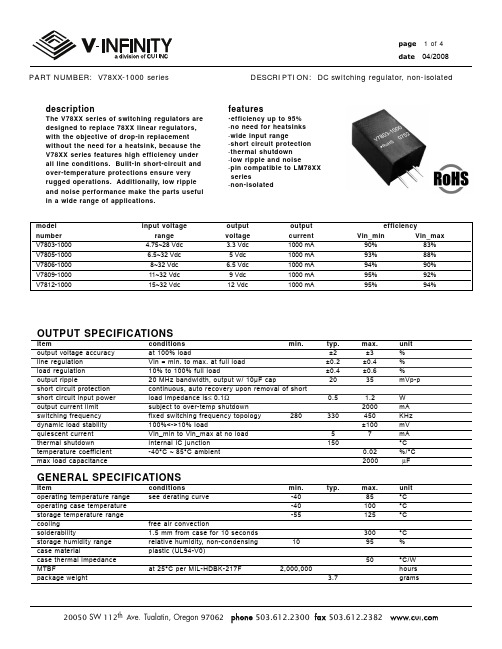

PART NUMBER: V78XX-1000 series

DESCRIPTION: DC switching regulator, non-isolated

description

The V78XX series of switching regulators are designed to replace 78XX linear regulators, with the objective of drop-in replacement without the need for a heatsink, because the V78XX series features high efficiency under all line conditions. Built-in short-circuit and over-temperature protections ensure very rugged operations. Additionally, low ripple and noise performance make the parts useful in a wide range of applications.

model number V7803-1000 V7805-1000 V7806-1000 V7809-1000 V7812-1000

input voltage range 4.75~28 Vdc 6.5~32 Vdc 8~32 Vdc 11~32 Vdc 15~32 Vdc

output voltage 3.3 Vdc 5 Vdc 6.5 Vdc 9 Vdc 12 Vdc

Vout

78,79系列三端稳压器器件资料

7805 790578XX系列集成稳压器的典型应用电路如下图所示,这是一个输出正5V直流电压的稳压电源电路。

IC采用集成稳压器7805,C1、C2分别为输入端和输出端滤波电容,RL为负载电阻。

当输出电较大时,7805应配上散热板。

下图为提高输出电压的应用电路。

稳压二极管VD1串接在78XX稳压器2脚与地之间,可使输出电压Uo得到一定的提高,输出电压Uo为78XX稳压器输出电压与稳压二极管VC1稳压值之和。

VD2是输出保护二极管,一旦输出电压低于VD1稳压值时,VD2导通,将输出电流旁路,保护7800稳压器输出级不被损坏。

下图为输出电压可在一定范围内调节的应用电路。

由于R1、RP电阻网络的作用,使得输出电压被提高,提高的幅度取决于R P与R1的比值。

调节电位器RP,即可一定范围内调节输出电压。

当RP=0时,输出电压Uo等于78XX稳压器输出电压;当RP逐步增大时,Uo也随之逐步提高。

下图为扩大输出电流的应用电路。

VT2为外接扩流率管,VT1为推动管,二者为达林顿连接。

R1为偏置电阻。

该电路最大输出电流取决于VT2的参数。

下图为提高输入电压的应用电路。

78XX稳压器的最大输入电压为35V(7824为40V),当输入电压高于此值时,可采用下图所示的电路。

VT、R1和VD组成一个预稳压电路,使得加在7800稳压器输入端的电压恒定在VD的稳压值上(忽略VT的b-e结压降)。

Ui端的最大输入电压仅取决于VT的耐压。

集成稳压器还可以用作恒流源。

下图为78XX稳压器构成的恒流源电路,其恒定电流Io等于78XX稳压器输出电压与R1的比值。

79XX系列集成压器是常用的固定负输出电压的三端集成稳压器,除输入电压和输出电压均为负值外,其他参数和特点与78XX系列集成稳压器相同。

79XX系列集成稳压的三个引脚为:1脚为接地端,2脚为输入端,3脚为输出端。

79XX系列集成稳压器的应用电路也很简单。

下图所示为输出-5V直流电压的稳压电源电路,IC采用集成稳压器7905,输出电流较大时应配上散热板。

RS Pro K78xx-500R3 DC-DC转换器数据手册说明书

ENDatasheetRS Pro K78xx-500R3 DC-DC ConverterWide input voltage non-isolated and regulated single output.CB RoHSFEATURES⚫ High efficiency up to 95%⚫ No-load input current as low as 0.2mA ⚫ Operating ambient temperature range -40℃ ~+85℃⚫ Output short-circuit protection⚫ Pin-out compatible with LM78XX linearregulators⚫ IEC60950, UL60950, EN60950 approved ⚫ 3 Year WarrantyK78xx-500R3 series are high efficiency switching regulators and ideal substitutes for LM78xx series three-terminal linear regulators. The converters feature high efficiency, low loss, short circuit protection, positive output voltage and there is no need for a heat sink. These products are widely used in applications such as industrial control, instrumentation and IoT.Selection GuideCertificationRS Stock no.(Standard Pack) RS Stock no. (Tube Pack 43)Part No.Input Voltage(VDC)* OutputFull Load Efficiency (%)Vin Min. / VinMax. Max. Capacitive Load (µF) Nominal (Range)Voltage (VDC) Output Current (mA) UL/CE/CB 1933974 1933972 K7803-500R3 24 (4.75-36)3.3 500 86/80 680 19339761933975 K7805-500R3 24 (6.5-36) 5.0 500 90/84 680 1933978 1933977 K7809-500R3 24 (12-36) 9 500 93/90 680 1933980 1933979 K7812-500R3 24 (15-36) 12 500 94/91 680 19339821933981K7815-500R324 (19-36)1550095/93680* Note: For input voltages exceeding 30 VDC, an input capacitor of 22µF/50V is required.Input SpecificationsItemOperating Conditions Min. Typ. Max. Unit No-load Input Current Positive output --0.21.5mAReverse Polarity at Input Avoid / Not protected Input FilterCapacitance filterOutput SpecificationsItemOperating Conditions Min. Typ. Max. UnitVoltage Accuracy Full load, input voltage rangeK7803-500R3 -- ±2 ±4 % Others-- ±2 ±3 Linear Regulation Full load, input voltage range -- ±0.2 ±0.4 Load RegulationNominal input voltage, 10% -100% load3.3/5 VDC output -- ±0.6 -- Others -- ±0.3 -- Ripple & Noise* 20MHz bandwidth, nominal input voltage, 10% -100% load-- 20 75 mVp-p Temperature Coefficient Operating ambient temperature -40℃ ~ +85℃ -- -- ±0.03 %/℃ Transient Response Deviation Nominal input voltage, 25% load step change -- 50 250 mV Transient Recovery Time --0.21ms Short-circuit ProtectionNominal input voltageContinuous, self-recovery*Note:① The “parallel cable” method is used for ripple and noise test, please refer to DC -DC Converter Application Notes for specific information;② With light loads at or below 10%, Ripple & Noise for 3.3V/5V output parts increases to 150mVp-p max, and for 9V/12V/15V output parts to 2%Vo max.General SpecificationsItemOperating Conditions Min.Typ.Max.UnitOperating Temperature See Fig. 1 -40 -- +85 ℃Storage Temperature-55 -- +125 Pin Soldering Resistance Temperature Soldering spot is 1.5mm away from case for 10 seconds----+260Storage Humidity Non-condensing5 -- 95 %RH Switching Frequency Full load, nominal input voltage 550 -- 850 KHz MTBF MIL-HDBK-217F@25℃2000----K hoursMechanical SpecificationsCase Material Black plastic; flame-retardant and heat-resistant (UL94 V-0) Dimensions 11.60 x 7.55 x 10.16 mm Weight1.8g (Typ.)Cooling Method Free air convectionElectromagnetic Compatibility (EMC)Emissions CE CISPR32/EN55032 CLASS B (see Fig. 5-② for recommended circuit) RE CISPR32/EN55032 CLASS B (see Fig. 5-② for recommended circuit)Immunity ESD IEC/EN 61000-4-2 Contact ±4KV perf. Criteria B RS IEC/EN 61000-4-3 10V/m perf. Criteria A EFT IEC/EN 61000-4-4 ±1KV (see Fig. 5-① for recommended circuit) perf. Criteria B Surge IEC/EN 61000-4-5 line to line ±1KV (see Fig. 5-① for recommended circuit) perf. Criteria B CS IEC/EN 61000-4-6 3Vr.m.sperf. Criteria A Typical Characteristic CurvesOutputPowerPercentage(%)20406080100120-4004085120S a fe Opera ti ng AreaOperating T emperatur e (℃)71T empera ture Dera ting CurveFig. 1K7805-500R3K7815-500R376788082848688909294966.51219202224262830323436Efficiency(%)Input voltage(V)Pos itive output efficiency Vs input voltage(full load)K7805-500R3K7815-500R3102030405060708090100102030405060708090100Efficiency(%)Output cur r ent per centage(%)Pos itive output efficiency Vs outputload(Vin=Vin-nominal)Design Reference1. Typical application+VinGNDGND DC/DC123+VoutC 1C 2Positive output application circuittable 1Part No. C1(ceramic capacitor)C2(ceramic capacitor)K7803-500R310μF/50V 22μF/10V K7805-500R3 22μF/10VK7809-500R3 22μF/16V K7812-500R3 22μF/25V K7815-500R3 22μF/25VFig. 2 Typical application circuitNote:1. The required capacitors C1 and C2 (C3 and C4) must be connected as close as possible to the terminals of the module;2. Refer to Table 1 for C1 and C2 (C3 and C4) capacitor values. For certain applications, increased values and/or tantalum or low ESR electrolytic capacitors may also be used instead;3. When using configurations as shown in figure 3, we recommended to add an inductor (LDM) with a value of up to 10μH which helps reducing mutual interference;4. Converter cannot be used for hot swap and with output in parallel;5. To further reduce the output ripple and noise, we suggested the use of a “LC ” filter at the output terminals, with an inductor value (L) o f 10µH -47µH.Positive outputNegative outputFig. 4 Using the “LC ” output filter application2. EMC compliance circuitDC /DCVinLDM 2②C 0LDM 1M OVFUS E①C 5V inGN D++VoGN DLOADC 2C 1Fig. 5 EMC compliance circuitNote: Part ①in Fig. 5 shows EMS compliance filter and part ② filter for EMI compliance; depending on requirement both filters ① and ② can be used in seriesas shown.FUSEMOV LDM1 C0 C1/C2 C5 LDM2 Select fuse value according toactual input currentS20K3082µH680µF /50VRefer to table 14.7µF /50V12µHDimensions and Recommended LayoutNotes:1.The specified maximum capacitive load is tested under full load condition and over the input voltage range;2.Unless otherwise specified, parameters in this datasheet were measured under the conditions of T a=25℃, humidity<75% withnominal input voltage and rated output load;3.All index testing methods in this datasheet are based on company corporate standards;4.We can provide product customization service, please contact our technicians directly for specific information; Products are related tolaws and regulations: see "Features" and "EMC";5.Our products shall be classified according to ISO14001 and related environmental laws and regulations and shall be handled byqualified units.。

IC-78中文说明书

8)可变频模式/存储模式指示 常规操作期间出现"MEMO"字样. 只有某些版本出现该指示. 可变频模式期间出现"VFO"字样.

9)信道号读数 显示已选择的信道号.

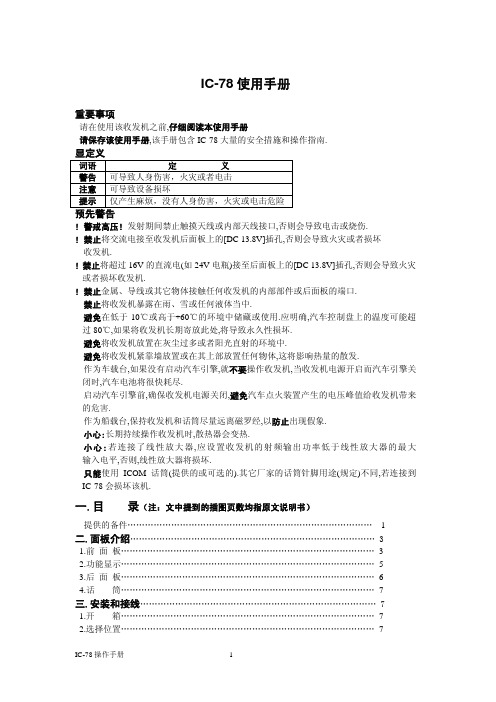

IC-78 使用手册

重要事项

请在使用该收发机之前,仔细阅读本使用手册

请保存该使用手册,该手册包含 IC-78 大量的安全措施和操作指南.

显定义

词语

定

义

警告 可导致人身伤害,火灾或者电击

注意 可导致设备损坏

提示 仅产生麻烦,没有人身伤害,火灾或电击危险

预先警告

! 警戒高压! 发射期间禁止触摸天线或内部天线接口,否则会导致电击或烧伤.

! 禁止将交流电接至收发机后面板上的[DC 13.8V]插孔,否则会导致火灾或者损坏

收发机.

! 禁止将超过 16V 的直流电(如 24V 电瓶)接至后面板上的[DC 13.8V]插孔,否则会导致火灾

或者损坏收发机.

! 禁止金属、导线或其它物体接触任何收发机的内部部件或后面板的端口.

禁止将收发机暴露在雨、雪或任何液体当中.

10)空闲指示 选择没有编程频率的信道时出现.

11)异频(双工)指示 选择双工信道(编程的发射和接收频率不同)时出现.

12)接收频率微调指示 使用接收频率微调功能时出现.

九.遥控插孔信息…………………………………………………………………… 23

1.通讯接口-V(CI-V)遥控………………………………………… ………………… 23 2.收发机之间的克隆………………………………………… ……………………… 23

AN78N05中文资料

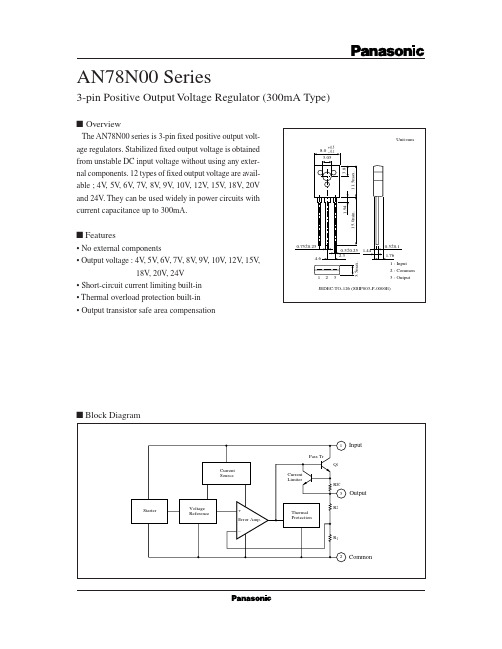

AN78N00 Series

3-pin Positive Output Voltage Regulator (300mA Type)

s Overview

The AN78N00 series is 3-pin fixed positive output voltage regulators. Stabilized fixed output voltage is obtained from unstable DC input voltage without using any external components. 12 types of fixed output voltage are available ; 4V, 5V, 6V, 7V, 8V, 9V, 10V, 12V, 15V, 18V, 20V and 24V. They can be used widely in power circuits with current capacitance up to 300mA.

Note 1) The specified condition Tj=25˚C means that the test should be carried out with the test time so short (within 10ms) that the drift in characteristic value due to the rise in chip junction temperature can be ignored. Note 2) When not specified, VI=10V, IO=100mA, CI=0.33µF, CO=0.1µF, Tj=0 to 125˚C

· AN78N04 (4V Type)

AN7805中文资料

Input

Output

Starter

Voltage Reference

+ Error Amp. −

R2 Thermal Protection

R1 2

Common

8.70±0.30

4.20±0.25 3.80±0.25

12.5±0.2 17.0±0.2 26.1±0.2 29.0±0.3

8.7±0.2

(13.6)

2.54 2.54

0.45 +0.2 –0.0 (2.0) (2.5)

10.5±0.3

HSIP003-P-0000

AN78xxF series

10.50±0.30 φ5.30 (4.30) (1.73) φ3.10±0.10

Unit: mm

2.77±0.30

16.70±0.30

17.00±0.25

元器件交易网

Voltage Regulators

AN78xx/AN78xxF Series

3-pin positive output voltage regulator (1 A type)

I Overview

The AN78xx series and the AN78xxF series are 3pin, fixed positive output type monolithic voltage regulators. Stabilized fixed output voltage is obtained from unstable DC input voltage without using any external components. 11 types of fixed output voltage are available; 5V, 6V, 7V, 8V, 9V, 10V, 12V, 15V, 18V, 20V, and 24V. They can be used widely in power circuits with current capacity of up to 1A. AN78xx series

78DxxA-TN3-R中文资料

UNISONIC TECHNOLOGIES CO.,78DxxA Linear Integrated Circuit3-TERMINALS 1A POSITIVE VOLTAGE REGULATORDESCRIPTIONThe UTC 78DXXA family is monolithic fixed voltage regulator integrated circuit. They are suitable for applications that required supply current up to 1 A.FEATURES* Peak output current up to 1A.* Fixed output voltage of 3.3V, 4.7V, 5V, 6V, 7V, 8V, 9V, 10V,12V, 15V, 18V and 24V available.* Thermal overload shutdown protection.* Short circuit current limiting.* Output transistor SOA protection.*Pb-free plating product number: 78DxxAL PIN CONFIGURATIONPIN NO.PIN NAME1 Input2 Ground3 OutputORDERING INFORMATIONOrdering NumberNormal Lead Free PlatingPackage Packing 78DxxA-TM3-T 78DxxAL-TM3-T TO-251 Tube 78DxxA-TN3-R 78DxxAL-TN3-R TO-252 TapeReel 78DxxA-TN3-T 78DxxAL-TN3-T TO-252 Tube Note: xx: Output Voltage, refer to below table.OUTPUT VOLTAGE INFORMATIONOutput Voltage Code3.3V 334.7V 475V 056V 067V 078V 089V 0910V 1012V 1215V 1518V 1824V 24BLOCK DIAGRAMINPUTZ1APPLICATION CIRCUITNote:Bypass capacitors are recommended for optimum stability and transient response and should be locatedas close as possible to the regulators.ABSOLUATE MAXIUM RATINGS (Ta = 25℃,unless otherwise specified)PARAMETER SYMBOL RATINGS UNITV OUT =3.3~18V 35Input Voltage V OUT =20~24V V IN40V Output Current I OUT 1 A Power Dissipation P D Internally Limited W Operating Temperature Range T OPR -40 ~ +85 °C Operating Junction Temperature T J 0~+125 °C Storage Temperature Range T STG -40 ~ +150 °CNote:1. Absolute maximum ratings are stress ratings only and functional device operation is not implied. The devicecould be damaged beyond Absolute maximum ratings.2. The device is guaranteed to meet performance specifications within 0℃~70℃ operating temperature range and assured by design from –40℃~85℃.3.The maximum steady state usable output current are dependent on input voltage, heat sinking, lead length of the package and copper pattern of PCB. The data are showed as electrical characteristics table represents pulse test conditions with junction temperatures specified at the initiation of test.ELECTRICAL CHARACTERISTICS (T J =25℃, P D ≦15W, unless otherwise specified) For 78D33A (V IN =5.8V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNIT I OUT =5mA ~ 1.0A 3.168 3.30 3.432 VOutput Voltage V OUTV IN =5.8~18.3V, I OUT =5mA~1.0A 3.135 3.465 V I OUT =5mA~1.0A 33 mVLoad Regulation ∆V OUTI OUT =0.25A~0.75A 17 mV V IN =5.8~18.3V 33 mVLine Regulation ∆V OUTV IN =5.8~18.3V, I OUT =1.0A 33 mV Quiescent Current I QI OUT ≦1.0A 8.0 mA V IN =5.8~18.3V 1.0 mAQuiescent Current Change ∆I QI OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz 55 µVTemperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -0.4 mV/°C Ripple Rejection RR V IN =6.3~16.3V,f=120Hz 57 dB Peak Output Current I PEAK 1.8 A Short-Circuit Current I SC V IN =35V 250 mA Dropout VoltageV D 2.0 VFor 78D47A (V IN =9.7V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNITI OUT =5mA~1.0A4.512 4.70 4.888 V Output Voltage V OUT V IN =5.8~18.3V, I OUT =5mA~1.0A 4.465 4.935 VI OUT =5mA~1.0A 47 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 24 mV V IN =5.8~18.3V 47 mV Line Regulation ∆V OUT V IN =5.8~18.3V, I OUT =1.0A 47 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =5.8~18.3V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz40 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -0.6 mV/°C Ripple Rejection RR V IN =6.3~16.3V,f=120Hz62 80 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 VFor 78D05A (V IN =10V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNITI OUT =5mA~1.0A4.805.0 5.20 V Output Voltage V OUT V IN =7.5~20V, I OUT =5mA~1.0A 4.75 5.25 VI OUT =5mA~1.0A 50 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 25 mV V IN =7~25V 50 mV Line Regulation ∆V OUT V IN =7.5~20V, I OUT =1.0A 50 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =7.5~20V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz40 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -0.6 mV/°C Ripple Rejection RR V IN =8~18V,f=120Hz62 80 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 V For 78D06A (V IN =11V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNIT I OUT =5mA~1.0A5.766.0 6.24 V Output Voltage V OUT V IN =8.5~21V, I OUT =5mA~1.0A 5.7 6.3 VI OUT =5mA~1.0A 60 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 30 mV V IN =8~25V 60 mV Line Regulation ∆V OUT V IN =8.5~21V, I OUT =1.0A 60 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =8.5~21V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz45 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -0.7 mV/°C Ripple Rejection RR V IN =9~19V,f=120Hz59 75 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 V For 78D07A (V IN =13V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNIT I OUT =5mA~1.0A6.727.0 7.28 V Output Voltage V OUT V IN =9.5~22V, I OUT =5mA~1.0A 6.65 7.35 VI OUT =5mA~1.0A 70 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 35 mV V IN =9~25V 70 mV Line Regulation ∆V OUT V IN =9.5~22V, I OUT =1.0A 70 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =9.5~22V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz50 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -0.8 mV/°C Ripple Rejection RR V IN =10~20V,f=120Hz59 75 dB Peak Output Current I PEAK1.7 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 VFor 78D08A (V IN =14V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNITI OUT =5mA~1.0A7.68 8.0 8.32 V Output Voltage V OUT V IN =10.5~23V, I OUT =5mA~1.0A 7.6 8.4 VI OUT =5mA~1.0A 80 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 40 mV V IN =10.5~25V 80 mV Line Regulation ∆V OUT V IN =10.5~23V, I OUT =1.0A 80 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =10.5~23V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz58 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -0.9 mV/°C Ripple Rejection RR V IN =11.5~21.5V,f=120Hz56 72 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 V For 78D09A (V IN =15V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNIT I OUT =5mA~1.0A7.68 8.0 8.32 V Output Voltage V OUT V IN =11.5~24V, I OUT =5mA~1.0A 7.6 8.4 VI OUT =5mA~1.0A 80 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 40 mV V IN =11.5~25V 80 mV Line Regulation ∆V OUT V IN =11.5~24V, I OUT =1.0A 80 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =11.5~24V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz58 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -0.9 mV/°C Ripple Rejection RR V IN =12.5~22.5V,f=120Hz56 72 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 V For 78D10A (V IN =16V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNIT I OUT =5mA~1.0A9.60 10.0 10.40 V Output Voltage V OUT V IN =12.5~25V, I OUT =5mA~1.0A 9.5 10.5 VI OUT =5mA~1.0A 100 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 50 mV V IN =13~25V 100 mV Line Regulation ∆V OUT V IN =13~25V, I OUT =1.0A 100 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =12.6V~25V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz58 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -1.1 mV/°C Ripple Rejection RR V IN =13~23V,f=120Hz56 72 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 VFor 78D12A (V IN =19V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNITI OUT =5mA~1.0A11.52 12.0 12.48 V Output Voltage V OUT V IN =14.5~27V, I OUT =5mA~1.0A11.4 12.6 V I OUT =5mA~1.0A 120 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 60 mV V IN =14.5~30V 120 mV Line Regulation ∆V OUT V IN =14.6~27V, I OUT =1.0A 120 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =12.6~25V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz75 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -1.5 mV/°C Ripple Rejection RR V IN =15~25V,f=120Hz55 72 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 V For 78D15A (V IN =23V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNIT I OUT =5mA~1.0A11.52 12.0 12.48 V Output Voltage V OUT V IN =17.5~30V, I OUT =5mA~1.0A11.4 12.6 V I OUT =5mA~1.0A 120 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 60 mV V IN =18.5~30V 120 mV Line Regulation ∆V OUT V IN =17.7~30V, I OUT =1.0A 120 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =17.5~30V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz75 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -1.5 mV/°C Ripple Rejection RR V IN =18.5~28.5V,f=120Hz55 72 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 V For 78D18A (V IN =27V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNIT I OUT =5mA~1.0A17.28 18.0 18.72 V Output Voltage V OUT V IN =21~33V, I OUT =5mA~1.0A 17.1 18.9 VI OUT =5mA~1.0A 180 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 90 mV V IN =21~33V 180 mV Line Regulation ∆V OUT V IN =21~33V, I OUT =1.0A 180 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =21.5~33V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz110 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -2.2 mV/°C Ripple Rejection RR V IN =22~32V,f=120Hz53 69 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 VFor 78D24A (V IN =33V, I OUT =0.5A, C1=0.33uF, C0=0.1uF)PARAMETER SYMBOLTEST CONDITIONS MIN TYP MAX UNITI OUT =5mA~1.0A23.04 24.0 24.96 V Output Voltage V OUT V IN =27~38V, I OUT =5mA~1.0A 22.8 25.2 VI OUT =5mA~1.0A 240 mV Load Regulation ∆V OUT I OUT =0.25A~0.75A 120 mV V IN =27~38V 240 mV Line Regulation ∆V OUT V IN =27~38V, I OUT =1.0A 240 mV Quiescent Current I Q I OUT ≦1.0A 8.0 mA V IN =28~38V 1.0 mA Quiescent Current Change ∆I Q I OUT =5mA~1.0A0.5 mA Output Noise VoltageeN 10Hz ≦f ≦100kHz170 µV Temperature coefficient of V OUT ∆V OUT /∆T I OUT =5mA -2.8 mV/°C Ripple Rejection RR V IN =28~38V,f=120Hz50 66 dB Peak Output Current I PEAK1.8 A Short-Circuit Current I SC V IN =35V250 mA Dropout VoltageV D2.0 V。

友台半导体有限公司 UMW 78DXX 三极管电源说明书

FeaturesOutput Current up to 0.5AOutput Voltages of 5,6,8,9,12,15,18,24VThermal Overload Protection Short Circuit Protection Output Transistor Safe Operating area (SOA)ProtectionDescriptionThe 78DXX three-terminal positive regulators are available in the TO-252 package with several fixed output voltages making it useful in a wide range of applications.Internal Block DigramAbsolute Maximum RatingsElectrical Characteristics(78D05)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=10V, unless otherwise specified,, VT j = 25°Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.Electrical Characteristics(78D06)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=11V, unless otherwise specified,, VT j =25°Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.Electrical Characteristics(78D08)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=14V, unless otherwise specified,, VT j =Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.Electrical Characteristics(78D09)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=15V, unless otherwise specified,, VT j =Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.Electrical Characteristics(78D12)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=19V, unless otherwise specified,, VT j =Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.Electrical Characteristics(78D15)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=23V, unless otherwise specified,, VT j =Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.Electrical Characteristics(78D18)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=26V, unless otherwise specified,, VT j =Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.UMW R UMW 78DXX ArrayElectrical Characteristics(78D24)(Refer to the test circuits, 0 < T J < +125°C, I O=350mA, V I=33V, unless otherwise specified,, VT j =Notes:Load and line regulation are specified at constant junction temperature. Change in Vo due to heating effects must be taken into account separately. Pulse testing with low duty is used.。

LM78CCVF-J资料

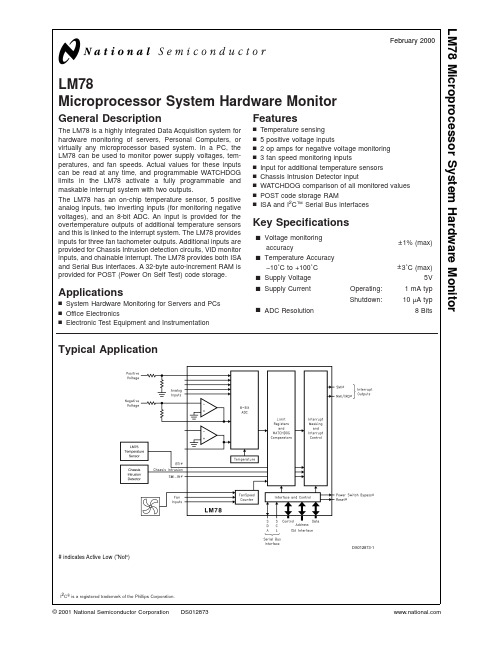

LM78Microprocessor System Hardware MonitorGeneral DescriptionThe LM78is a highly integrated Data Acquisition system for hardware monitoring of servers,Personal Computers,or virtually any microprocessor based system.In a PC,the LM78can be used to monitor power supply voltages,tem-peratures,and fan speeds.Actual values for these inputs can be read at any time,and programmable WATCHDOG limits in the LM78activate a fully programmable and maskable interrupt system with two outputs.The LM78has an on-chip temperature sensor,5positive analog inputs,two inverting inputs (for monitoring negative voltages),and an 8-bit ADC.An input is provided for the overtemperature outputs of additional temperature sensors and this is linked to the interrupt system.The LM78provides inputs for three fan tachometer outputs.Additional inputs are provided for Chassis Intrusion detection circuits,VID monitor inputs,and chainable interrupt.The LM78provides both ISA and Serial Bus interfaces.A 32-byte auto-increment RAM is provided for POST (Power On Self Test)code storage.Applicationsn System Hardware Monitoring for Servers and PCs n Office Electronicsn Electronic Test Equipment and InstrumentationFeaturesn Temperature sensing n 5positive voltage inputsn 2op amps for negative voltage monitoring n 3fan speed monitoring inputsn Input for additional temperature sensors n Chassis Intrusion Detector inputn WATCHDOG comparison of all monitored values n POST code storage RAMnISA and I 2C ™Serial Bus interfacesKey Specificationsj Voltage monitoringaccuracy±1%(max)j Temperature Accuracy−10˚C to +100˚C±3˚C (max)j Supply Voltage 5Vj Supply Current Operating:1mA typ Shutdown:10µA typj ADC Resolution8BitsTypical ApplicationI 2C ®is a registered trademark of the Phillips Corporation.DS012873-1#indicates Active Low (”Not“)February 2000LM78Microprocessor System Hardware Monitor©2001National Semiconductor Corporation Ordering InformationTemperature Range Package−10˚C ≤T A ≤+100˚COrder Number Device Marking LM78CCVFLM78CCVF-JVGZ44A Connection DiagramBlock DiagramDS012873-2DS012873-3L M 78 2Pin DescriptionsPin Name(s)PinNumberNumberof PinsType DescriptionIORD11Digital Input An active low standard ISA bus I/O Read Control.IOWR21Digital Input An active low standard ISA bus I/O Write Control.SYSCLK31Digital Input The reference clock for the ISA bus.Typically ranges from4.167MHz to8.33MHz.The minimum clock frequency this input can handle is1Hz. D7–D04–118Digital I/O Bi-directional ISA bus Data lines.D0corresponds to the low order bit,with D7the high order bit.V CC(+5V)121POWER+5V V CC power.Bypass with the parallel combination of10µF(electolytic or tantalum)and0.1µF(ceramic)bypass capacitors.GNDD131GROUND Internally connected to all digital circuitry.SMI__IN141Digital Input Chainable SMI(System Management Interrupt)Input.This is an activelow input that propagates the SMI signal to the SMI output of the LM78via SMI Mask Register Bit6and SMI enable Bit1of the ConfigurationRegister.Chassis Intrusion 151Digital I/O An active high input from an external circuit which latches a ChassisIntrusion event.This line can go high without any clamping actionregardless of the powered state of the LM78.The LM78provides aninternal open drain on this line,controlled by Bit7of NMI Mask Register2,to provide a minimum20ms reset of this line.Power Switch Bypass 161Digital Output An active low push-pull output intended to drive an external P-channelpower MOSFET for software power control.FAN3–FAN117–193Digital Input0V to+5V amplitude fan tachometer input.SCL201Digital Input Serial Bus Clock.SDA211Digital I/O Serial Bus bidirectional Data.RESET221Digital Output Master Reset,5mA driver(open drain),active low output with a20msminimum pulse width.Available when enabeld via Bit7in SMI MaskRegister2.NTEST231Test Output NAND Tree totem-pole output that provides board-level connectivitytesting.Refer to Section11.0on NAND Tree testing.GNDA241GROUND Internally connected to all analog circuitry.The ground reference for allanalog inputs.−IN6251Analog Input Ground-referred inverting op amp input.Refer to Section4.0,“ANALOGINPUTS”.FB6261Analog Output Output of inverting op amp for Input6.Refer to section4.0,“ANALOGINPUTS”.FB5271Analog Output Output of inverting op amp for Input5.Refer to section4.0,“ANALOGINPUTS”.−IN5281Analog Input Ground-referred inverting op amp input.Refer to Section4.0,“ANALOGINPUTS”.IN4–IN029–335Analog Input0V to4.096V FSR Analog Inputs.VID3–VID034–374Digital Input Voltage Supply readouts from P6.This value is read in the VID/FanDivisor Register.BTI381Digital Input Board Temperature Interrupt driven by O.S.outputs of additionaltemperature sensors such as LM75.Provides internal pull-up of10kΩ.NMI/IRQ391Digital Output Non-Maskable Interrupt(open source)/Interrupt Request(open drain).The mode is selected with Bit5of the Configuration Register and theoutput is enabled when Bit2of the Configuration Register is set to1.The default state is disabled and IRQ mode.SMI401Digital Output System Management Interrupt(open drain).This output is enabled whenBit1in the Configuration Register is set to1.The default state isdisabled.LM783Pin Descriptions(Continued)Pin Name(s)Pin Number Number of PinsType DescriptionA2–A041–433Digital Input The three lowest order bits of the 16-bit ISA Address Bus.A0corresponds to the lowest order bit.CS441Digital InputChip Select input from an external decoder which decodes high order address bits on the ISA Address Bus.This is an active low input.TOTAL PINS44L M 78 4Absolute Maximum Ratings(Notes1,2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Positive Supply Voltage(V CC) 6.5V Voltage on Any Input or Output Pin−0.3V to(V CC+0.3V) Ground Difference(GNDD–GNDA)±300mV Input Current at any Pin(Note3)±5mA Package Input Current(Note3)±20mA Maximum Junction Temperature(T J max)150˚C ESD Susceptibility(Note5)Human Body Model2000V Machine Model175V Soldering InformationPQFP Package(Note6):Vapor Phase(60seconds)215˚C Infrared(15seconds)220˚C Storage Temperature−65˚C to+150˚COperating Ratings(Notes1,2)Operating Temperature Range T MIN≤T A≤T MAX LM78−55˚C≤T A≤+125˚C Specified Temperature Range T MIN≤T A≤T MAX LM78−10˚C≤T A≤+100˚C Junction to Ambient Thermal Resistance(θJA(Note4))NS Package ID:VGZ44A62˚C/W Supply Voltage(V CC)+4.25V to+5.75V Ground Difference(IGNDD–GNDAI)≤100mV V IN Voltage Range−0.05V to V CC+0.05VDC Electrical Characteristics(Note7)The following specifications apply for+4.25V DC≤V CC≤+5.75V DC,f SYSCLK=8.33MHz,R S=25Ω,unless otherwise speci-fied.Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.Symbol Parameter Conditions Typical Limits Units(Note8)(Note9)(Limits) POWER SUPPLY CHARACTERISTICSI CC Supply Current Interface Inactive 1.02mA(max)Shutdown Mode10µA TEMPERATURE-TO-DIGITAL CONVERTER CHARACTERISTICSAccuracy−10˚C≤T A≤+100˚C±3˚C(max)Resolution1˚C(min) ANALOG-TO-DIGITAL CONVERTER CHARACTERISTICSResolution(8bits with full-scale at4.096V)16mVTUE Total Unadjusted Error(Note10)±1%(max)DNL Differential Non-Linearity±1LSBPSS Power Supply Sensitivity±1%/Vt C Total Monitoring Cycle Time(Note11) 1.0 1.5sec(max)OP AMP CHARACTERISTICSOutput Current(Sourcing)50µAInput Offset Voltage I OUT=50µA±1mVInput Bias Current±0.1nAPSRR60dBDC Open Loop Gain70dBGain Bandwidth Product500kHz MULTIPLEXER/ADC INPUT CHARACTERISTICSOn Resistance4002000Ω(max)Off Channel Leakage Current±0.1nAInput Current(On Channel Leakage Current)±0.1nAFAN RPM-TO-DIGITAL CONVERTERAccuracy+25˚C≤T A≤+75˚C±10%(max)−10˚C≤T A≤+100˚C±15%(max) Full-scale Count255(max)LM785DC Electrical Characteristics (Note 7)(Continued)The following specifications apply for +4.25V DC ≤V CC ≤+5.75V DC ,f SYSCLK =8.33MHz,R S =25Ω,unless otherwise speci-fied.Boldface limits apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =25˚C.SymbolParameterConditionsTypical Limits Units (Note 8)(Note 9)(Limits)FAN RPM-TO-DIGITAL CONVERTERFAN1and FAN2Nominal Input RPM (See Section 6.0)Divisor =1,Fan Count =153(Note 12)8800RPM Divisor =2,Fan Count =153(Note 12)4400RPM Divisor =3,Fan Count =153(Note 12)2200RPM Divisor =4,Fan Count =153(Note 12)1100RPM FAN3Design Nominal Input RPM Fan Count =153(Note 12)4400RPM Internal Clock Frequency+25˚C ≤T A ≤+75˚C 22.520.2kHz (min)24.8kHz (max)−10˚C ≤T A ≤+100˚C22.519.1kHz (min)25.9kHz (max)DIGITAL OUTPUTS (Power Switch Bypass,NTEST,NMI/IRQ)V OUT(1)Logical “1”Output Voltage I OUT =±5.0mA 2.4V (min)V OUT(0)Logical “0”Output Voltage I OUT =±5.0mA 0.4V (max)ISA D0–D7DIGITAL OUTPUTSV OUT(1)Logical “1”Output Voltage I OUT =±12.0mA 2.4V (min)V OUT(0)Logical “0”Output Voltage I OUT =±12.0mA 0.4V (max)I OUTTRI-STATE ®Output CurrentV OUT =0V DC 0.0051µA (max)V OUT =V CC−0.005−1µA (min)OPEN DRAIN DIGITAL OUTPUTS (SDA,RESET,SMI,Chassis Intrusion)V OUT(0)Logical “0”Output Voltage I OUT =−5.0mA 0.4V (min)I OHHigh Level Output Current V OUT =V CC0.1100µA (max)RESET and Chassis Intrusion 4520ms (min)Pulse WidthDIGITAL INPUTS:SMI__IN,VID0–VID3,BTI,CS,A0,A1,A2,Mode Control and Interface Inputs (IORD,IOWR,SYSCLK),Data Lines (D0–D7),Chassis Intrusion,and Tach Pulse Logic Inputs (FAN1,FAN2,FAN3)V IN(1)Logical “1”Input Voltage 2.0V (min)V IN(0)Logical “0”Input Voltage 0.8V (max)SERIAL BUS DIGITAL INPUTS (SCL,SDA)V IN(1)Logical “1”Input Voltage 0.7x V CC V (min)V IN(0)Logical “0”Input Voltage 0.3x V CCV (max)ALL DIGITAL INPUTS EXCEPT FOR BTII IN(1)Logical “1”Input Current V IN =V CC −0.005−1µA (min)I IN(0)Logical “0”Input Current V IN =0V DC0.0051µA (max)C IN Digital Input Capacitance 20pF BIT DIGITAL INPUTI IN(1)Logical “1”Input Current V IN =V CC 110µA (max)I IN(0)Logical “0”Input Current V IN =0V DC −500−2000µA (max)C INDigital Input Capacitance20pFL M 78 6LM78AC Electrical Characteristics(Note13)The following specifications apply for+4.25V≤V CC≤DC +5.75V DC unless otherwise specified.Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.Symbol Parameter Conditions Typical Limits Units(Note8)(Note9)(Limits)ISA TIMING CHARACTERISTICSf SYSCLK System Clock(SYSCLK)Input Frequency8.33MHzt CS(setup)CS Active to IORD/IOWR Active10ns(min)t CS(hold)IORD/IOWR Inactive to CS Inactive10ns(min)t SA(setup)Address Valid to IORD/IOWR Active30ns(min)t SA(hold)IORD/IOWR Inactive to Address Invalid10ns(min)ISA WRITE TIMINGt SDWR(setup)Data Valid to IOWR Active5ns(min)t SDWR(hold)IOWR Inactive to Data Invalid5ns(min)t WR(setup)IOWR Active to Rising Edge of SYSCLK20ns(min) ArrayDS012873-4The delay between consecutive IORD and IOWR pulses should be greater than50ns to ensure that an Power-on reset does notoccur unintentionally.(See Section3.2‘Resets’)FIGURE1.ISA Bus Write Timing Diagram7AC Electrical Characteristics (Note 13)The following specifications apply for +4.25V DC ≤V CC ≤+5.75V DCunless otherwise specified.Boldface limits apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =25˚C.(Continued)Symbol ParameterConditionsTypical Limits Units (Note 8)(Note 9)(Limits)ISA READ TIMING t SDRD (setup)Data Valid to IORD Inactive 120ns (min)t SDRD (hold)IORD Inactive to Data Invalid5ns (min)t RD (setup)IORD Active to Rising Edge of SYSCLK 20ns (min)t RS (delay)Rising Edge of SYSCLK number 1to Data ValidWith 8.33MHz SYSCLK360ns (max)DS012873-5The delay between consecutive IORD and IOWR pulses should be greater than 50ns to ensure that an Power-on reset does not occur unintentionally.(See Section 3.2‘Resets’)FIGURE 2.ISA Bus Read Timing DiagramL M 78 8LM78AC Electrical Characteristics(Note13)The following specifications apply for+4.25V≤V CC≤+5.75V DCDCunless otherwise specified.Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.(Continued) Symbol Parameter Conditions Typical Limits Units(Note8)(Note9)(Limits) SERIAL BUS TIMING CHARACTERISTICSt1SCL(Clock)Period 2.5µs(min)t2Data In Setup Time to SCL High100ns(min)t3Data Out Stable After SCL Low0ns(min)t4SDA Low Setup Time to SCL Low(start)100ns(min)t5SDA High Hold Time After SCL High(stop)100ns(min) ArrayDS012873-6FIGURE3.Serial Bus Timing Diagram9Electrical Characteristics (Continued)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed.Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:All voltages are measured with respect to GND,unless otherwise specifiedNote 3:When the input voltage (V IN )at any pin exceeds the power supplies (V IN <(GNDD or GNDA)or V IN >V CC ),the current at that pin should be limited to 5mA.The 20mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5mA to four.Note 4:The maximum power dissipation must be derated at elevated temperatures and is dictated by T J max,θJA and the ambient temperature,T A .The maximum allowable power dissipation at any temperature is P D =(T J max−T A )/θJA .Note 5:The human body model is a 100pF capacitor discharged through a 1.5k Ωresistor into each pin.The machine model is a 200pF capacitor discharged directly into each pin.Note 6:See the section titled “Surface Mount”found in any post 1986National Semiconductor Linear Data Book for other methods of soldering surface mount devices.Note 7:Each input and output is protected by a nominal 6.5V breakdown voltage zener diode to GND;as shown below,input voltage magnitude up to 0.3V above V CC or 0.3V below GND will not damage the LM78.There are parasitic diodes that exist between the inputs and the power supply rails.Errors in the ADC conversion can occur if these diodes are forward biased by more than 50mV.As an example,if V CC is 4.50V DC ,input voltage must be ≤4.55V DC ,to ensure accurate conversions.Note 8:Typicals are at T J =T A =25˚C and represent most likely parametric norm.Note 9:Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).Note 10:TUE (Total Unadjusted Error)includes Offset,Gain and Linearity errors of the ADC and any error introduced by the amplifiers as shown in the circuit of Figure 13.Note 11:Total Monitoring Cycle Time includes temperature conversion,7analog input voltage conversions and 3tachometer readings.Each temperature and input voltage conversion takes 100ms typical and 112ms maximum.Fan tachometer readings take 20ms typical,at 4400rpm,and 200ms max.Note 12:The total fan count is based on 2pulses per revolution of the fan tachometer output.Note 13:Timing specifications are tested at the TTL logic levels,V IL =0.4V for a falling edge and V IH =2.4V for a rising edge.TRI-STATE output voltage is forced to 1.4V.DS012873-7An x indicates that the diode exists.Pin Name D1D2D3IORD x IOWR x SYSCLK xD0–D7x x x SMI__IN x Chassis Intrusion xx Power Switch Bypassx xxPin Name D1D2D3FAN1–FAN3x SCLxSDA x x RESET x x NTESTxxxPin Name D1D2D3−IN6x x FB6x x x FB5x x x −IN5x x IN4–IN0x x x VID3–VID0xxxPin Name D1D2D3BTI x x NMI/IRQ xx x SMI xx A0–A2x CSxFIGURE 4.ESD Protection Input StructureL M 78 10Test CircuitFunctional Description1.0GENERAL DESCRIPTIONThe LM78provides7analog inputs,a temperature sensor,a Delta-Sigma ADC(Analog-to-Digital Converter),3fan speed counters,WATCHDOG registers,and a variety of inputs and outputs on a single chip.Interfaces are provided for both the ISA parallel bus or Serial Bus.The LM78performs power supply,temperature,and fan monitoring for personal com-puters.The LM78continuously converts analog inputs to8-bit digital words with a16mV LSB(Least Significant Bit)weighting, yielding input ranges of from0V to4.096V.The two negative analog inputs provide inverting op amps,with their non-inverting input referred to ground.With additional exter-nal feedback components,these inputs provide measure-ments of negative voltages(such as-5V and-12V power supplies).The analog inputs are useful for monitoring sev-eral power supplies present in a typical computer.Tempera-ture is converted to an8-bit two’s-complement digital word with a1˚C LSB.Fan inputs measure the period of tachometer pulses from the fans,providing a higher count for lower fan speeds.The fan inputs are digital inputs with an acceptable range of0V to 5V and a transition level of approximately1.4V.Full scale fan counts are255(8-bit counter)and this represents a stopped or very slow fan.Nominal speeds,based on a count of153, are programmable from1100to8800RPM on FAN1and FAN2,with FAN3fixed at4400RPM.Signal conditioning circuitry is included to accommodate slow rise and fall times. The LM78provides a number of internal registers,as de-tailed in Figure6.These include:•Configuration Register:Provides control and con-figuration.•Interrupt Status Registers:Two registers to provide status of each WATCHDOG limit or Interrupt event.•Interrupt Mask Registers:Allows masking of indi-vidual Interrupt sources,as well as separate masking for each of both hardware Interrupt outputs.•VID/Fan Divisor Registers:A register to read the sta-tus of the VID input lines.The high bits of this register contain the divisor bits for FAN1and FAN2inputs.•Serial Bus Address Register:Contains the Serial Bus address.At power on it assumes the default value of 0101101binary,and can be altered via the ISA or Serial Bus interface.•Chip Reset/ID Register:Allows reseting of all the reg-isters to the default power-on reset value.Provides a bit for identification between the current version of this de-vice and an older version which does not have this reset capability.•POST RAM:FIFO RAM to store up to32bytes of8-bit POST codes.Overflow of the POST RAM will set an Interrupt.The POST RAM,located at base address x0h and x4h,allows for easy decoding to address80h and 84h,the normal addresses for outputting of POST codes.Interrupt will only be set when writing to port x0h or x4h.The POST RAM can be read via ports85h and86h.•Value RAM:The monitoring results:temperature,volt-ages,fan counts,and WATCHDOG limits are all con-tained in the Value RAM.The Value RAM consists of a total of64bytes.The first11bytes are all of the results, the next19bytes are the WATCHDOG limits,and are located at20h-3Fh,including two unused bytes in the upper locations.The next32bytes,located at60h-7Fh, mirror the first32bytes with identical contents.The only difference in the upper bytes are that they auto-increment the LM78Internal Address Register when read from or written to via the ISA bus(auto-increment is not available for Serial Bus communications).When the LM78is started,it cycles through each measure-ment in sequence,and it continuously loops through the sequence approximately once every second.Each mea-sured value is compared to values stored in WATCHDOG,or Limit registers.When the measured value violates the pro-grammed limit the LM78will set a corresponding Interrupt in the Interrupt Status Registers.Two hardware Interrupt lines, SMI and NMI/IRQ,are fully programmable with separate masking of each Interrupt source,and masking of each output.In addition,the Configuration Register has control bits to enable or disable the hardware Interrupts. Additional digital inputs are provided for chaining of SMI (System Management Interrupt),outputs of multiple external LM75temperature sensors via the BTI(Board Temperature Interrupt)input,and a Chassis Intrusion input.The Chassis Intrusion input is designed to accept an active high signal from an external circuit that latches when the case is re-moved from the computer.DS012873-8FIGURE5.Digital Output Load Circuitry LM78Functional Description(Continued)2.0INTERFACEThe LM78only decodes the three lowest address bits on the ISA bus.Referring to the ISA bus timing diagrams in Figure 1and Figure 2,the Chip Select Input,CS,should be taken low by external address decoder circuitry to access the LM78.The LM78decodes the following base addresses:-Port x0h:Power On Self Test codes from ISA bus.-Port x4h:Power On Self Test codes from ISA bus.-Port x5h:The LM78s Internal Address Register -Port x6h:Data RegisterIORD is the standard ISA bus signal that indicates to the LM78that it may drive data on to the ISA data bus.IOWR is the standard ISA command to the LM78that it may latch data from the ISA bus.SYSCLK is the standard ISA SYSCLK,typically 8.33MHz.This clock is used only for timing of the ISA interface of the LM78.All other clock functions within LM78such as the ADC and fan counters are done with a separate asynchronous internal clock.A typical application designed to utilize the POST RAM would decode the LM78to the address space starting at 80h,which is where POST codes are output to.Otherwise,the LM78can be decoded into a different desired address space.To communicate with an LM78Register,first write the ad-dress of that Register to Port x5h.Read or write data from or to that register via Port x6h.A write will take IOWR low,while a read will take IORD low.If the Serial Bus Interface and ISA bus interface are used simultaneously there is the possibility of collision.To prevent this from occurring in applications where both interfaces are used,read port x5h and if the Most Significant Bit,D7,is high,ISA communication is limited to reading port x5h only until this bit is low.A Serial Bus communication occurring while ISA is active will not be a problem,since even a single bit of Serial Bus communication requires 10microseconds,in comparison to less than a microsecond for an entire ISA communication.L M 78Functional Description(Continued)DS012873-9FIGURE6.LM78Register Structure LM78Functional Description(Continued)2.1Internal Registers of the LM78TABLE 1.The internal registers and their corresponding internal LM78address is as follows:RegisterLM78Internal HexAddress Power on ValueNotes(This is the data to be written to Port x5h)Configuration Register 40h 00001000Interrupt Status Register 141h 00000000Auto-increment to the address of Interrupt Status Register 2after a read or write to Port x6h.Interrupt Status Register 242h 00000000SMI Mask Register 143h 00000000Auto-increment to the address of SMI Mask Register 2after a read or write to Port x6h.SMI Mask Register 244h 00000000NMI Mask Register 145h 00000000Auto-increment to the address of NMI Mask Register 2after a read or write to Port x6h.NMI Mask Register 246h 01000000VID/Fan Divisor Register47h0101XXXXThe first four bits set the divisor for FanCounters 1and 2.The lower four bits reflect the state of the VID inputs.Serial Bus Address Register 48h 00101101Chip Reset/ID Register 49h 01000000POST RAM00h-1FhAuto-increment when written to from Port x0h or x4h.Auto-increment after a read or write to Port x6h,with a separate pointer.Auto-incrementing stops when address 1Fh is reached.Value RAM 20h-3Fh Value RAM60h-7FhAuto-increment after a read or write to Port x6h.Auto-incrementing stops when address 7Fh is reached.A typical communication with the LM78would consist of:1.Write to Port x5h the LM78Internal Address (from col-umn 2above)of the desired register.Alternatively,when both ISA and Serial Bus interfaces are used,the first step in a communication may be to read Port x5h to ascertain the state of the Busy bit to avoid contention with an Serial Bus communication.2.Read or write the corresponding registers data with reads/writes from Port x6h.The LM78Internal Address latches,and does not have to be written if it is already pointing at the desired register.The LM78Internal Address Register is read/write (Bit 7is read only).L M 78Functional Description(Continued) 2.2Serial Bus InterfaceWhen using the Serial Bus Interface a write will always consist of the LM78Serial Bus Interface Address byte,fol-lowed by the Internal Address Register byte,then the data byte.There are two cases for a read:1.If the Internal Address Register is known to be at thedesired Address,simply read the LM78with the Serial Bus Interface Address byte,followed by the data byte read from the LM78.2.If the Internal Address Register value is unknown,writeto the LM78with the Serial Bus Interface Address byte, followed by the Internal Address Register byte.Then restart the Serial Communication with a Read consisting of the Serial Bus Interface Address byte,followed by the data byte read from the LM78.In all other respects the LM78functions identically for Serial Bus communications as it does for ISA communications.Auto-Increment does not operate.When writing to or reading from a Register which Auto-Increments with ISA communi-cations,the Register must be manually incremented for Serial Bus communications.The default power on Serial Bus address for the LM78is: 0101101binary.This address can be changed by writing any desired value to the Serial Bus address register,which can be done either via the ISA or Serial Bus.During and Serial Bus communication on the BUSY bit(bit7)in the address register at x5h will be high,and any ISA activity in that situation should be limited to reading port x5h only.All of these communications are depicted in the Serial Bus Interface Timing Diagrams as shown in Figure7.DS012873-10(a)Serial Bus Write to the Internal Address Register followed by the Data ByteDS012873-11(b)Serial Bus Write to the Internal Address Register OnlyDS012873-12 (c)Serial Bus Read from a Register with the Internal Address Register Preset to Desired LocationFIGURE7.Serial Bus Timing LM78Functional Description(Continued)3.0USING THE LM783.1Power OnWhen power is first applied,the LM78performs a “power on reset”on several of its registers.The power on condition of registers in shown in Table I.Registers whose power on values are not shown have power on conditions that are indeterminate (this includes the value RAM and WATCH-DOG limits).The ADC is inactive.In most applications,usu-ally the first action after power on would be to write WATCH-DOG limits into the Value RAM.3.2ResetsConfiguration Register INITIALIZATION accomplishes the same function as power on reset on most registers.The POST RAM,Value RAM conversion results,and Value RAM WATCHDOG limits are not Reset and will be indeterminate immediately after power on.If the Value RAM contains valid conversion results and/or Value RAM WATCHDOG limits have been previously set,they will not be affected by a Configuration Register INITIALIZATION.Power on reset,or Configuration Register INITIALIZATION,clear or initialize the following registers (the initialized values are shown on Table I):•Configuration Register •Interrupt Status Register 1•Interrupt Status Register 2•SMI Mask Register 1•SMI Mask Register 2•NMI Mask Register 1•NMI Mask Register 2•VID/Fan Divisor Register•Serial Bus Address Register (Power on reset only,not reset by Configuration Register INITIALIZATION)Configuration Register INITIALIZATION is accomplished by setting Bit 7of the Configuration Register high.This bit automatically clears after being set.The LM78-J allows the user to perform an unconditional complete Power-on reset by writing a one to Bit 5of the Chip Reset/ID Register.The LM78-J can be differentiated from the LM78without the J suffix by reading Chip Reset/ID Register Bit 6.A high would indicate that the LM78-J is being used.The LM78-J allows an unconditional complete Power-on reset to be initiated by taking the IOWR and IORD signal lines low simultaneously,for at least 50ns,while CS is high.The delay between consecutive IORD and IOWR pulses should be greater than 50ns to ensure that an Power-on reset does not occur unintentionally.In systems where the serial bus is only being used it may be advantageous to take both IOWR and IORD to the system reset pulse.In this way whenever the system is reset the LM78-J will also be reset to a known state.3.3Using the Configuration RegisterThe Configuration Register provides all control over the LM78.At power on,the ADC is stopped and INT__Clear is asserted,clearing the SMI and NMI/IRQ hardwire outputs.The Configuration Register starts and stops the LM78,en-ables and disables interrupt outputs and modes,and pro-vides the Reset function described in Section 3.2.Bit 0of the Configuration Register controls the monitoring loop of the LM78.Setting Bit 0low stops the LM78monitor-ing loop and puts the LM78in shutdown mode,reducing power consumption.ISA and Serial Bus communication is possible with any register in the LM78although activity on these lines will increase shutdown current,up to as much as maximum rated supply current,while the activity takes place.Taking Bit 0high starts the monitoring loop,described in more detail subsequently.Bit 1of the Configuration Register enables the SMI Interrupt hardwire output when this bit is taken high.Similarly,Bit 2of the Configuration Register enables the NMI/IRQ Interrupt hardwire output when taken high.The NMI/IRQ mode is determined by Bit 5in the Configuration Register.When Bit 5is low the output is an active low IRQ output.Taking Bit 5high inverts this output to provide an active high NMI output.The Power Switch Bypass provides an active low at the Power Switch Bypass output when set high.This is intended for use in software power control by activating an external power control MOSFET.3.4Starting ConversionThe monitoring function (Analog inputs,temperature,and fan speeds)in the LM78is started by writing to the Configu-ration Register and setting INT__Clear (Bit 3),low,and Start (bit 0),high.The LM78then performs a “round-robin”moni-toring of all analog inputs,temperature,and fan speed inputs approximately once a second.The sequence of items being monitored corresponds to locations in the Value RAM and is:1.Temperature 2.IN03.IN14.IN25.IN36.IN47.-IN58.-IN69.Fan 110.Fan 211.Fan 33.5Reading Conversion ResultsThe conversion results are available in the Value RAM.Conversions can be read at any time and will provide the result of the last conversion.Because the ADC stops,and starts a new conversion whenever it is read,reads of any single value should not be done more often then once every 120ms.When reading all values,allow at least 1.5seconds between reading groups of values.Reading more frequently than once every 1.5seconds can also prevent complete updates of Interrupt Status Registers and Interrupt Output’s.A typical sequence of events upon power on of the LM78would consist of:1.Set WATCHDOG Limits2.Set Interrupt Masks3.Start the LM78monitoring process4.0ANALOG INPUTSThe 8-bit ADC has a 16mV LSB,yielding a 0V to 4.08V (4.096–1LSB)input range.This is true for all analog inputs.In PC monitoring applications these inputs would most often be connected to power supplies.The 2.5V and 3.3V supplies can be directly connected to the inputs.The 5V and 12V inputs should be attenuated with external resistors to any desired value within the input range.L M 78。

UPD78P078GC-8EU资料