FPGA可编程逻辑器件芯片XC2S200E-6FG456C中文规格书

FPGA可编程逻辑器件芯片XC2S30-5FG456C中文规格书

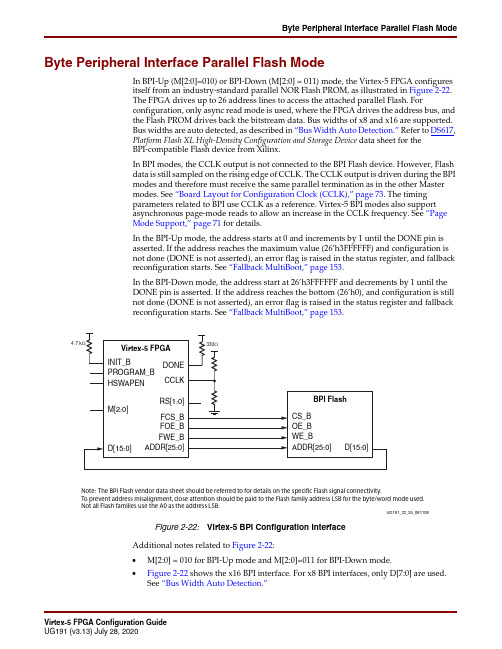

width. Table 1-5 shows an example bitstream with an inserted bus width detection pattern.When observing the pattern on the FPGA data pin, the bits are bit swapped, as describedin “Parallel Bus Bit Order.”The bitstream data in Table 1-5 shows the 32-bit configuration word for an unswappedbitstream. For a swapped bitstream format, the LSB and MSB order for the individual bytesare swapped. For example, the Sync word at the FPGA pins in the D[31:00] bit order wouldbe: 0x5599AA66. For swapped and unswapped formats see “Configuration Data FileFormats.”.Bus width auto detection is transparent to most users, because all configuration bitstreams(BIT or RBT files) generated by the Xilinx ISE® Bitstream Generator (BitGen) softwareinclude the Bus Width Auto Detection pattern. These patterns are ignored by theconfiguration logic if the Mode pins are set to Master Serial, Slave Serial, JTAG, or SPImode.For the x8 bus, the configuration bus width detection logic first finds 0xBB on the D[0:7]pins, followed by 0x11. For the x16 bus, the configuration bus width detection logic firstfinds 0xBB on D[0:7] followed by 0x22. For the x32 bus, the configuration bus widthdetection logic first finds 0xBB , on D[0:7], followed by 0x44.If the immediate byte after 0xBB is not 0x11, 0x22, or 0x44, the bus width state machine isreset to search for the next 0xBB until a valid sequence is found. Then it switches to theappropriate external bus width and starts looking for the Sync word.Sync WordA special Sync word is used to allow configuration logic to align at a 32-bit word boundary.No packet processed by the FPGA until the Sync word is found. The bus width must bedetected successfully for parallel configuration modes before the Sync word can bedetected. Table 1-6 shows the Sync word in an unswapped bitstream format.Table 1-5:Bus Width Detection Pattern D[24:31]D[16:23]D[8:15]D[0:7]Comments0xFF0xFF 0xFF 0xFF 0x000x000x000xBB Bus Width Pattern 0x110x220x000x44Bus Width Pattern0xFF 0xFF 0xFF 0xFF 0xFF0xFF 0xFF 0xFF 0xAA0x990x550x66Sync Word ……………Table 1-6:Sync Word31:2423:1615:87:00xAA 0x990x550x66Generating PROM FilesChapter 2:Configuration Interfaces∙Sending a bitstream to the data pin follows the same bit-swapping rule as in SelectMAP mode. See “Parallel Bus Bit Order.”∙If Flash programming is not required, FCS_B, FOE_B, and FWE_B can be tied off; that is, DONE is connected to FCS_B, FOE_B is tied Low, and FWE_B is tied High.∙The CCLK outputs are not used to connect to Flash but are used to sample Flash readdata during configuration. All timings are referenced to CCLK. The CCLK pin mustnot be driven or tied High or Low.∙The RS[1:0] pins are not connected as shown in Figure 2-22. These output pins areonly required for MultiBoot configuration. See Chapter 8, “Reconfiguration andMultiBoot.”∙HSWAPEN must be connected to either disable or enable the pull-up resistors.∙If HSWAPEN is left unconnected or tied High, a pull-up resistor is required forFCS_B.∙If HSWAPEN is tied Low, the FCB_B, FOE_B, FWE_B, and the address pins haveinternal weak pull-up resistors during configuration. After configuration, FCS_B canbe either controlled by I/O in user mode or by enabling a weak pull-up resistorthrough constraints.∙To enable the active driver on DONE, the DriveDONE option in BitGen must beenabled.∙“MultiBoot Bitstream Spacing,” page 155 provides information on when DCI or DCMlock wait is turned on.∙For daisy chaining FPGAs in BPI mode, see Figure 2-12, page 52.∙The BPI Flash vendor data sheet should be referred to for details on the specific Flashsignal connectivity. To prevent address misalignment, close attention should be paidto the Flash family address LSB for the byte/word mode used. Not all Flash familiesuse the A0 as the address LSB.Table 2-9 defines the BPI configuration interface pins.If the FPGA is subject to reprogramming or fallback during configuration from the BPIflash, then the INIT pin can be connected to the BPI reset to set the BPI into a known state.Table 2-9:Virtex-5 Device BPI Configuration Interface Pins Pin Name TypeDedicated or Dual-PurposeDescription M[2:0] Input Dedicated The Mode pins determine the BPI mode:010 = BPI-Up mode011 = BPI-Down modeHSWAPEN Input Dedicated Controls I/O (except Bank 0 dedicated I/Os) pull-up resistors duringconfiguration. This pin has a built-in weak pull-up resistor.0 = Pull-up during configuration1 = 3-state during configurationDONE Bidirectional, Open-Drain, or Active Dedicated Active-High signal indicating configuration is complete:0 = FPGA not configured 1 = FPGA configuredByte Peripheral Interface Parallel Flash Mode INIT_B Input or Output, Open-Drain Dedicated Before the Mode pins are sampled, INIT_B is an input that can be heldLow to delay configuration. After the Mode pins are sampled, INIT_Bis an open-drain, active-Low output indicating whether a CRC erroroccurred during configuration:0 = CRC error1 = No CRC errorWhen the SEU detection function is enabled, INIT_B is optionallydriven Low when a read back CRC error is detected.PROGRAM_B Input Dedicated Active-Low asynchronous full-chip resetCCLK Output Dedicated Configuration clock output. CCLK does not directly connect to BPIFlash but is used internally to generate the address and sample readdata.FCS_B Output Dual Active-Low Flash chip select output. This output is actively driven Lowduring configuration and 3-stated after configuration. It has a weakpull-up resistor during configuration. By default, this signal has a weakpull-down resistor after configuration.FOE_B Output Dual Active-Low Flash output enable. This output is actively driven Lowduring configuration and 3-stated after configuration. It has a weakpull-up resistor during configuration. By default, this signal has a weakpull-down resistor after configuration.FWE_B Output Dual Active-Low Flash write enable. This output is actively driven Highduring configuration and 3-stated after configuration. It has a weakpull-up resistor during configuration. By default, this signal has a weakpull-down resistor after configuration.ADDR[25:0]Output DualAddress output. For I/O bank locations, see Table 1-2, page 17.D[15:0]Input Dual Data input, sampled by the rising edge of the FPGA CCLK. For I/Obank location, see Table 1-2, page 17.Table 2-9:Virtex-5 Device BPI Configuration Interface Pins (Continued)Pin NameType Dedicated or Dual-Purpose DescriptionChapter 2:Configuration Interfaces。

FPGA可编程逻辑器件芯片XC2S100E-7FGG456C中文规格书

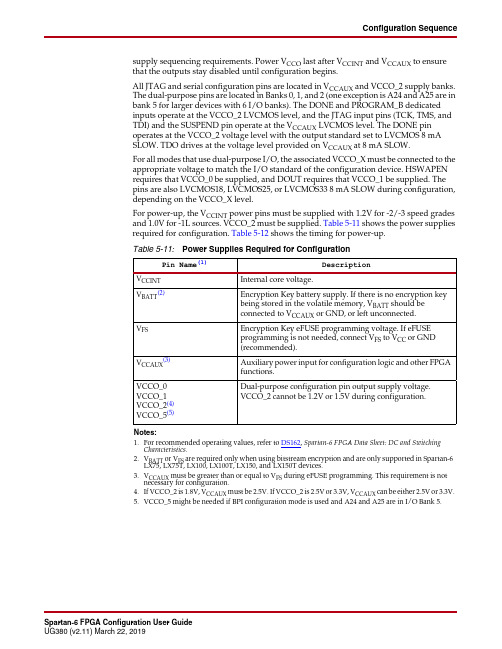

Configuration Sequence supply sequencing requirements. Power V CCO last after V CCINT and V CCAUX to ensurethat the outputs stay disabled until configuration begins.All JTAG and serial configuration pins are located in V CCAUX and VCCO_2 supply banks. The dual-purpose pins are located in Banks 0, 1, and 2 (one exception is A24 and A25 are in bank5 for larger devices with 6 I/O banks). The DONE and PROGRAM_B dedicated inputs operate at the VCCO_2 LVCMOS level, and the JTAG input pins (TCK, TMS, and TDI) and the SUSPEND pin operate at the V CCAUX LVCMOS level. The DONE pin operates at the VCCO_2 voltage level with the output standard set to LVCMOS 8mA SLOW. TDO drives at the voltage level provided on V CCAUX at 8 mA SLOW.For all modes that use dual-purpose I/O, the associated VCCO_X must be connected to the appropriate voltage to match the I/O standard of the configuration device. HSWAPEN requires that VCCO_0 be supplied, and DOUT requires that VCCO_1 be supplied. The pins are also LVCMOS18, LVCMOS25, or LVCMOS33 8mA SLOW during configuration, depending on the VCCO_X level.For power-up, the V CCINT power pins must be supplied with 1.2V for -2/-3 speed grades and 1.0V for -1L sources. VCCO_2 must be supplied. Table5-11 shows the power supplies required for configuration. Table5-12 shows the timing for power-up.Table 5-11:Power Supplies Required for ConfigurationPin Name(1)DescriptionV CCINT Internal core voltage.V BATT(2)Encryption Key battery supply. If there is no encryption keybeing stored in the volatile memory, V BATT should beconnected to V CCAUX or GND, or left unconnected.V FS Encryption Key eFUSE programming voltage. If eFUSEprogramming is not needed, connect V FS to V CC or GND(recommended).V CCAUX(3)Auxiliary power input for configuration logic and other FPGAfunctions.VCCO_0 VCCO_1 VCCO_2(4) VCCO_5(5)Dual-purpose configuration pin output supply voltage. VCCO_2 cannot be 1.2V or 1.5V during configuration.Notes:1.For recommended operating values, refer to DS162, Spartan-6 FPGA Data Sheet: DC and SwitchingCharacteristics.2.V BATT or V FS are required only when using bitstream encryption and are only supported in Spartan-6LX75, LX75T, LX100, LX100T, LX150, and LX150T devices.3.V CCAUX must be greater than or equal to V FS during eFUSE programming. This requirement is notnecessary for configuration.4.If VCCO_2 is 1.8V, V CCAUX must be 2.5V. If VCCO_2 is 2.5V or 3.3V, V CCAUX can be either 2.5V or 3.3V.5.VCCO_5 might be needed if BPI configuration mode is used and A24 and A25 are in I/O Bank 5.Chapter 5:Configuration DetailsConfiguration PacketsSuspend Register (PWRDN_REG)Frame Length RegisterFrame Length Register (FLR) is written with the length of a frame, as measured in 16-bit words, near the beginning of the configuration bitstream. FLR must be written before any FDR operation will work. It is not necessary to set the FLR more than once.The actual value written to FLR = Actual Frame Length.Based on the segmentation scheme in Spartan-6 devices, the frame length for type0 (CLB, IOI, and special blocks) and type1 (block RAM) are fixed. The only block that needs a specified frame length is IOB.Multi-Frame Write RegisterThe Spartan-6 FPGA supports Multi-Frame Write (MFWR) for first-time configuration but does not support it during reconfiguration. The FPGA has to go through one power cycle or use PROGRAM_B to reset the chip before MFWR can be used.Table 5-37:Power-Down Register Description Field Bit IndexDescriptionBitGen DefaultRESERVED 15Reserved.EN_EYES14Enable Multi-Pin Wake-Up.0: Disable Multi-Pin Wake-Up.1: Enable Multi-Pin Wake-Up.0RESERVED 13:6Reserved.0010_0010FILTER_B 50: Suspend filter (300ns) on.1: Filter off.0EN_PGSR40: No GSR pulse during return from Suspend.1: Generate GSR pulse during return from Suspend.0RESERVED 3Reserved.EN_PWRDN 20: Suspend is disabled.1: Suspend is enabled.0KEEP_SCLK0: Use MCCLK for startup sequence initiated by power-up.1: Use SSCLKSRC for startup sequence initiated by power-up.1Table 5-38:Frame Length RegisterBits FLR[15:0]xxxxxxxxxxxxxxxxChapter 5:Configuration DetailsConfiguration Watchdog Timer RegisterThe configuration watchdog timer (CWDT) register stores the value of the number of clock cycles that the FPGA will wait before the watchdog time-out (in which SYNCWORD is not received). The default is 64k clock cycles. The minimum value is 16h'0201.HC_OPT_REG RegisterThe HC_OPT_REG register can only be reset to default by por_b.GENERAL Registers 1, 2, 3, 4, and 5GENERAL1 and GENERAL2 registers are used to store loadable multiple configuration addresses for SPI and BPI.GENERAL3 and GENERAL4 registers have a similar function as GENERAL1 andGENERAL2, except that GENERAL3 and GENERAL4 store the golden bitstream address instead of the MultiBoot address.The GENERAL5 register is a 16-bit register that allows users to store and access any extra information desired for the fail-safe scheme. These register contents are untouched during a soft reboot.These registers are set by the bitstream. BitGen can be instructed not to write to these registers using the -g next_config_register_write:Disable command. This allows the ability to store user data in the FPGA between re-configuration attempts.If the second configuration needs a previously unknown SPI vendor command, the new vendor command has already been loaded in GENERAL2 from the bitstream by this point.Table 5-39:CWDT RegisterBits Value [15:0]16h'ffffTable 5-40:HC_OPT_REG DescriptionName Bits DescriptionDefault INIT_SKIP 60: Do not skip initialization.1: Skip initialization.0RESERVED5:0Reserved.011111Table 5-41:General RegistersName Bits DescriptionGENERAL1[15:0]The lower half of the multiple boot address.GENERAL2[15:0]15:8 – SPI opcode.7:0 – Higher half of the boot address.GENERAL3[15:0]The lower half of the golden bitstream address.GENERAL4[15:0]15:8 – SPI opcode.7:0 – Higher half of the golden boot address.GENERAL5[15:0]The user-defined scratchpad register.Configuration Packets。

FPGA可编程逻辑器件芯片XC2V2000-6FG456C中文规格书

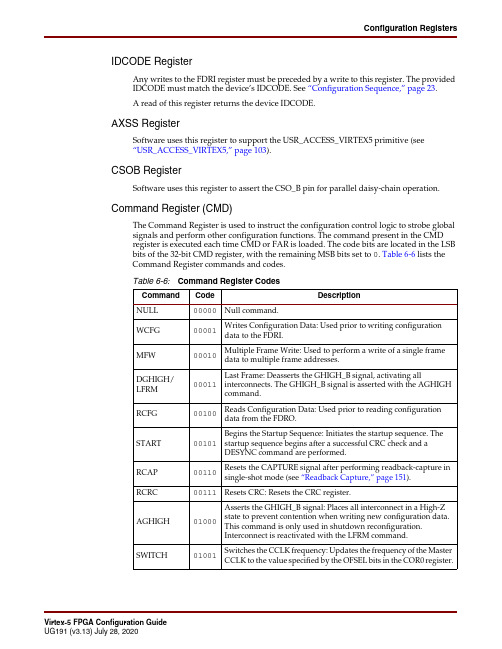

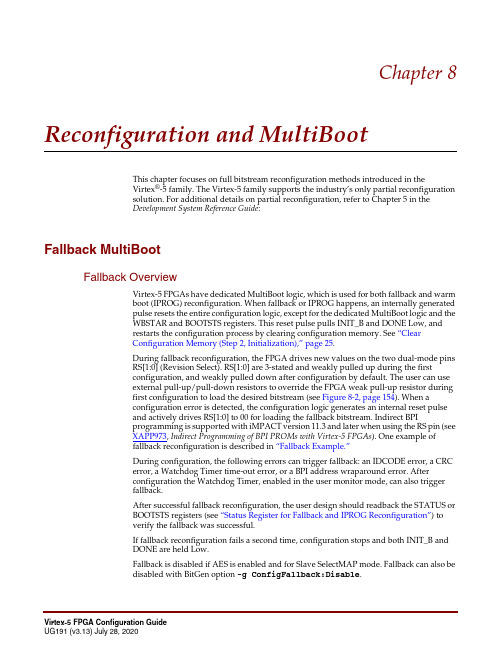

IDCODE RegisterAny writes to the FDRI register must be preceded by a write to this register. The provided IDCODE must match the device’s IDCODE. See “Configuration Sequence,” page23.A read of this register returns the device IDCODE.AXSS RegisterSoftware uses this register to support the USR_ACCESS_VIRTEX5 primitive (see“USR_ACCESS_VIRTEX5,” page103).CSOB RegisterSoftware uses this register to assert the CSO_B pin for parallel daisy-chain operation. Command Register (CMD)The Command Register is used to instruct the configuration control logic to strobe global signals and perform other configuration functions. The command present in the CMD register is executed each time CMD or FAR is loaded. The code bits are located in the LSB bits of the 32-bit CMD register, with the remaining MSB bits set to 0. Table6-6 lists the Command Register commands and codes.Table 6-6:Command Register CodesCommand Code DescriptionNULL00000Null command.WCFG00001Writes Configuration Data: Used prior to writing configuration data to the FDRI.MFW00010Multiple Frame Write: Used to perform a write of a single frame data to multiple frame addresses.DGHIGH/ LFRM 00011Last Frame: Deasserts the GHIGH_B signal, activating allinterconnects. The GHIGH_B signal is asserted with the AGHIGHcommand.RCFG00100Reads Configuration Data: Used prior to reading configuration data from the FDRO.START00101Begins the Startup Sequence: Initiates the startup sequence. The startup sequence begins after a successful CRC check and a DESYNC command are performed.RCAP00110Resets the CAPTURE signal after performing readback-capture in single-shot mode (see “Readback Capture,” page151).RCRC00111Resets CRC: Resets the CRC register.AGHIGH01000Asserts the GHIGH_B signal: Places all interconnect in a High-Z state to prevent contention when writing new configuration data. This command is only used in shutdown reconfiguration. Interconnect is reactivated with the LFRM command.SWITCH01001Switches the CCLK frequency: Updates the frequency of the Master CCLK to the value specified by the OFSEL bits in the COR0 register.Warm Boot Start Address Register (WBSTAR)The name of each bit position in the WBSTAR is given in Figure 6-6 and described in Table 6-12.DescriptionReservedPERSIST_DEASSERT_AT_DESYNCHReserved ReservedRBCRC_NO_PINRBCRC_EN ReservedBPI_1ST_READ_CYCLESBPI_PAGE_SIZEBit Index 313029282726252423222120191817161514131211109876543210ValueFigure 6-5:Configuration Options Register 1Table 6-11:Configuration Options Register 1 Description NameBit IndexDescriptionPERSIST_DEASSERT_AT_DESYNCH 17Enables deassertion of PERSIST with the DESYNCH commandRBCRC_NO_PIN 9Disables INIT_B as read back CRC error status output pinRBCRC_EN8Continuous readback CRC enable BPI_1ST_READ_CYCLES[3:2]First byte read timing:00: 1 C C LK 01: 2 C C LKs 10: 3 C C LKs 11: 4 C C LKs BPI_PAGE_SIZE [1:0]Flash memory page size:00: 1byte/word 01: 4 bytes/words 10: 8 bytes/words 11: ReservedChapter 6:Configuration DetailsWatchdogFPGA End of StartupTo use the Watchdog to monitor the bitstream configuration, set TIMER_CFG_MON to 1 and the desired TIMER_VALUE in a write to the TIMER register in the bitstream. The TIMER_VALUE should be adequate to cover the entire FPGA configuration time until startup is complete. Any wait time in startup for DCI match, DCM lock, or DONE should also be included.Once enabled, the watchdog timer starts to count down. If the timer reaches 0 and the FPGA has not reached the final state of startup, a watchdog time-out error occurs and triggers a fallback configuration.User OperationTo use the Watchdog to monitor the user logic, set TIMER_USR_MON to 1 and the desired TIMER_VALUE in a write to the TIMER register in the bitstream. The user must constantly reset the watchdog counter before it times out, either by the LTIMER command or by directly accessing the TIMER register. The watchdog is automatically disabled when the device is shut down or on power down (including shutdown).Table 8-6 shows an example bitstream for reloading the Watchdog using the LTIMER command.Table 8-7 shows an example bitstream for directly accessing the TIMER register:Table 8-6:Example Bitstream for Reloading the Watchdog with LTIMERConfiguration Data(hex)Explanation FFFFFFFF Dummy Word AA995566 Sync Word 20000000 Type 1 NO OP30008001 Type 1 Write 1 Words to CMD00000000 NULL 20000000 Type 1 NO OP30008001 Type 1 Write 1 Words to CMD00000011 LTIMER Command 20000000 Type 1 NO OP30008001 Type 1 Write 1 Words to CMD0000000D DESYNCH 20000000Type 1 NO OPTable 8-7:Example Bitstream for Accessing the TIMER RegisterConfiguration Data(hex)Explanation FFFFFFFF Dummy Word AA995566Sync WordChapter 9:Readback CRC。

FPGA可编程逻辑器件芯片XC2S200-5FGG256C中文规格书

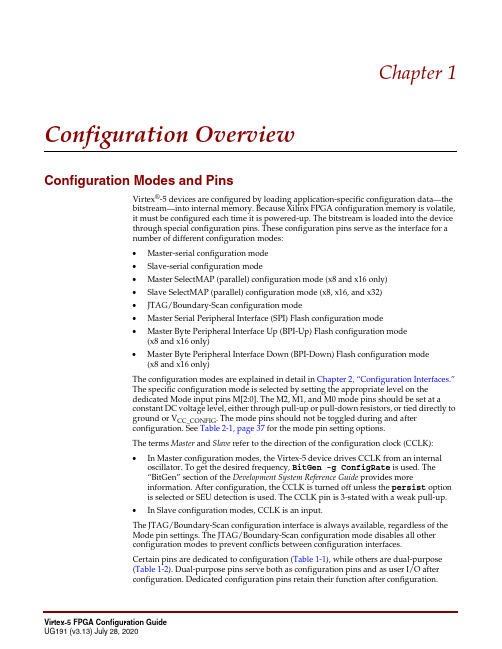

Chapter1 Configuration OverviewConfiguration Modes and PinsVirtex®-5 devices are configured by loading application-specific configuration data—thebitstream—into internal memory. Because Xilinx FPGA configuration memory is volatile,it must be configured each time it is powered-up. The bitstream is loaded into the devicethrough special configuration pins. These configuration pins serve as the interface for anumber of different configuration modes:∙Master-serial configuration mode∙Slave-serial configuration mode∙Master SelectMAP (parallel) configuration mode (x8 and x16 only)∙Slave SelectMAP (parallel) configuration mode (x8, x16, and x32)∙JTAG/Boundary-Scan configuration mode∙Master Serial Peripheral Interface (SPI) Flash configuration mode∙Master Byte Peripheral Interface Up (BPI-Up) Flash configuration mode(x8 and x16 only)∙Master Byte Peripheral Interface Down (BPI-Down) Flash configuration mode(x8 and x16 only)The configuration modes are explained in detail in Chapter2, “Configuration Interfaces.”The specific configuration mode is selected by setting the appropriate level on thededicated Mode input pins M[2:0]. The M2, M1, and M0 mode pins should be set at aconstant DC voltage level, either through pull-up or pull-down resistors, or tied directly toground or V CC_CONFIG. The mode pins should not be toggled during and afterconfiguration. See Table2-1, page37 for the mode pin setting options.The terms Master and Slave refer to the direction of the configuration clock (CCLK):∙In Master configuration modes, the Virtex-5 device drives CCLK from an internaloscillator. To get the desired frequency, BitGen -g ConfigRate is used. The“BitGen” section of the Development System Reference Guide provides moreinformation. After configuration, the CCLK is turned off unless the persist optionis selected or SEU detection is used. The CCLK pin is 3-stated with a weak pull-up.∙In Slave configuration modes, CCLK is an input.The JTAG/Boundary-Scan configuration interface is always available, regardless of theMode pin settings. The JTAG/Boundary-Scan configuration mode disables all otherconfiguration modes to prevent conflicts between configuration interfaces.Certain pins are dedicated to configuration (Table1-1), while others are dual-purpose(Table1-2). Dual-purpose pins serve both as configuration pins and as user I/O afterconfiguration. Dedicated configuration pins retain their function after configuration.Chapter 1:Configuration OverviewConfiguration constraints can be selected when generating the Virtex-5 bitstream. Certainconfiguration operations can be affected by these constraints. For a description of theavailable constraints, see the software constraints guide.Table 1-1:Virtex-5 FPGA Dedicated Configuration PinsPin Name Type(1)DescriptionM[2:0]Input Mode pins that determine configuration mode. Sampled on the rising edge of INIT_B.CCLK Input orOutput Configuration clock source for all configuration modes except JTAG. Refer to the "Board Layout for Configuration Clock (CCLK)" section for details.D_IN Input Serial data input for serial configuration modes.DOUT_BUSY Output In Serial configuration mode, pin acts as serial data output for daisy-chainconfiguration. In SelectMAP mode, pin acts as BUSY output.DONE Bidirectional,Open-Drain,or Active Active High signal indicating configuration is complete.0 = FPGA not configured1 = FPGA configuredRefer to the “BitGen” section of the Development System Reference Guide for software settings.INIT_B Bidirectional,Input orOutput,Open-Drain Before the Mode pins are sampled, INIT_B is an input that can be held Low to delay configuration. INIT_B is bidirectional during configuration.After the Mode pins are sampled, INIT_B is an open-drain, active-Low output, indicating whether a CRC error occurred during configuration or a readback CRC error occurred after configuration (when enabled):0 = CRC or IDCODE Error (DONE Low) or Readback CRC Error (DONE High andReadback CRC enabled)1 = No CRC error, housecleaning complete.PROGRAM_B(2)Input Active-Low, asynchronous full-chip reset.HSWAPEN Input Active-High input used to disable weak preconfiguration I/O pull-up resistors:0 = Weak preconfiguration I/O pull-up resistors enabled1 = Weak preconfiguration I/O pull-up resistors disabledHSWAPEN has a weak pull-up prior to and during configuration. HSWAPEN must beconnected to either disable or enable the pull-up resistors. The weak pull-up does notalways provide a reliable 1.TDI Input Test Data In. This pin is the serial input to all JTAG instruction and data registers. The stateof the TAP controller and the current instruction determine the register that is fed by theTDI pin for a specific operation. TDI has an internal resistive pull-up to provide a logicHigh to the system if the pin is not driven. TDI is applied into the JTAG registers on therising edge of TCK.TDO Output Test Data Out. This pin is the serial output for all JTAG instruction and data registers. Thestate of the TAP controller and the current instruction determine the register (instruction ordata) that feeds TDO for a specific operation. TDO changes state on the falling edge of TCKand is only active during the shifting of instructions or data through the device. TDO is anactive driver output.TMS Input Test Mode Select. This pin determines the sequence of states through the TAP controller onthe rising edge of TCK. TMS has an internal resistive pull-up to provide a logic High if thepin is not driven.TCK Input Test Clock. This pin is the JTAG Test Clock. TCK sequences the TAP controller and the JTAGregisters in Virtex-5 devices.Configuration SequenceConfiguration SequenceWhile each of the configuration interfaces is different, the basic steps for configuring a Virtex-5 device are the same for all modes. Figure 1-2 shows the Virtex-5 configuration process. The following subsections describe each step in detail, where the current step is highlighted in gray at the beginning of each subsection.The Virtex-5 device is initialized and the configuration mode is determined by sampling the mode pins in three setup steps.Setup (Steps 1-3)The setup process is similar for all configuration modes (see Figure 1-3).The setup steps are critical for proper device configuration. The steps include Device Power-Up, Clear Configuration Memory, and Sample Mode Pins.Table 1-7:Sync Word Bit Swap ExampleSync Word[31:24](1)[23:16][15:8][7:0]Bitstream Format 0xAA 0x990x550x66Bit Swapped0x550x990xAA0x66Notes:1.[31:24] changes from 0xAA to 0x55 after bit swapping.Table 1-8:Sync Word Data Sequence Example for x8, x16, and x32 ModesCCLK Cycle 1234D[7:0] pins for x8 0x550x990xAA0x66D[15:0] pins for x160x55990xAA66D[31:0] pins for x320x5599AA66Figure 1-2:Virtex-5 Device Configuration ProcessUG191_c1_01_050406Steps。

FPGA可编程逻辑器件芯片XC2S400-4FG456C中文规格书

550

550

MHz

FX100T devices

PLL Maximum Output Frequency for FX130T devices

500

450

N/A

MHz

FOUTMIN TEXTFDVAR RSTMINPULSE FPFDMAX FPFDMIN TFBDELAY

PLL Maximum Output Frequency for LX220T, LX330T, SX95T, SX240T, and FX200T devices PLL Minimum Output Frequency(5) External Clock Feedback Variation Minimum Reset Pulse Width Maximum Frequency at the Phase Frequency Detector Minimum Frequency at the Phase Frequency Detector Maximum Delay in the Feedback Path

Outputs Clocks (High Frequency Mode)

32.00 135.00 64.00 270.00

2.0 90.00 32.00 160.00

32.00 120.00 64.00 240.00

2.0 80.00 32.00 140.00

32.00 120.00 64.00 240.00

0.36

TAXD

AX inputs to DMUX output

0.62

TBXB

BX inputs to BMUX output

0.41

Speed Grade

-2I

FPGA可编程逻辑器件芯片XC2S200E-6FGG456C中文规格书

Byte Peripheral Interface Parallel Flash ModeByte Peripheral Interface Parallel Flash ModeIn BPI-Up (M[2:0]=010) or BPI-Down (M[2:0]=011) mode, the Virtex-5 FPGA configures itself from an industry-standard parallel NOR Flash PROM, as illustrated in Figure 2-22. The FPGA drives up to 26 address lines to access the attached parallel Flash. Forconfiguration, only async read mode is used, where the FPGA drives the address bus, and the Flash PROM drives back the bitstream data. Bus widths of x8 and x16 are supported. Bus widths are auto detected, as described in “Bus Width Auto Detection.” Refer to DS617, Platform Flash XL High-Density Configuration and Storage Device data sheet for the BPI-compatible Flash device from Xilinx.In BPI modes, the CCLK output is not connected to the BPI Flash device. However, Flash data is still sampled on the rising edge of CCLK. The CCLK output is driven during the BPI modes and therefore must receive the same parallel termination as in the other Master modes. See “Board Layout for Configuration Clock (CCLK),” page 73. The timing parameters related to BPI use CCLK as a reference. Virtex-5 BPI modes also support asynchronous page-mode reads to allow an increase in the CCLK frequency. See “Page Mode Support,” page 71 for details.In the BPI-Up mode, the address starts at 0 and increments by 1 until the DONE pin is asserted. If the address reaches the maximum value (26’h3FFFFFF) and configuration is not done (DONE is not asserted), an error flag is raised in the status register, and fallback reconfiguration starts. See “Fallback MultiBoot,” page 153.In the BPI-Down mode, the address start at 26’h3FFFFFF and decrements by 1 until the DONE pin is asserted. If the address reaches the bottom (26’h0), and configuration is still not done (DONE is not asserted), an error flag is raised in the status register and fallback reconfiguration starts. See “Fallback MultiBoot,” page 153.Additional notes related to Figure 2-22:∙M[2:0]=010 for BPI-Up mode and M[2:0]=011 for BPI-Down mode.∙Figure 2-22 shows the x16 BPI interface. For x8 BPI interfaces, only D[7:0] are used.See “Bus Width Auto Detection.”Figure 2-22:Virtex-5 BPI Configuration InterfaceUG191_c2_25_0611084.7 k Note: The BPI Flash vendor data sheet should be referred to for details on the specific Flash signal connectivity.To prevent address misalignment, close attention should be paid to the Flash family address LSB for the byte/word mode used. Not all Flash families use the A0 as the address LSB.Board Layout for Configuration Clock (CCLK)Chapter 2:Configuration InterfacesBoundary-Scan for Virtex-5 Devices Using IEEE Standard 1149.1Single Device ConfigurationTable3-4 describes the TAP controller commands required to configure a Virtex-5 device.Refer to Figure3-2 for TAP controller states. These TAP controller commands are issuedautomatically if configuring the part with the iMPACT software.Table 3-4: Single Device Configuration SequenceTAP Controller Step and Description Set and Hold# of Clocks TDI TMS TCK1.On power-up, place a logic 1 on the TMS, and clockthe TCK five times. This ensures starting in the TLR(Test-Logic-Reset) state.X152.Move into the RTI state.X013.Move into the SELECT-IR state.X124.Enter the SHIFT-IR state.X025.Start loading the CFG_IN instruction, LSB first:111000101096.Load the MSB of CFG_IN instruction when exitingSHIFT-IR, as defined in the IEEE standard.1117.Enter the SELECT-DR state.X128.Enter the SHIFT-DR state.X029.Shift in the Virtex-5 bitstream. Bitn (MSB) is the firstbit in the bitstream(1).bit1...bit n0(bits in bitstream)-110.Shift in the last bit of the bitstream. Bit0 (LSB) shiftson the transition to EXIT1-DR.bit01111.Enter UPDATE-DR state.X1112.Reset TAP by clocking five 1s on TMS X1513.Move into RTI state.X0114.Enter the SELECT-IR state.X1215.Move to the SHIFT-IR state.X0216.Start loading the JSTART instruction. The JSTARTinstruction initializes the startup sequence.1110011000917.Load the last bit of the JSTART instruction.11118.Move to the UPDATE-IR state.X1119.Move to the RTI state and clock the startupsequence by applying a minimum of 12 clock cyclesto the TCK.X01220.Move to the TLR state. The device is now functional.X13Notes:1.In the Configuration Register, data is shifted in from the right (TDI) to the left (TDO), MSB first. (Shifts into the Configuration Register aredifferent from shifts into the other registers in that they are MSB first.)Chapter 4:User PrimitivesCAPTURE_VIRTEX5The CAPTURE_VIRTEX5 primitive is used to capture I/O, CLB, and block RAM outputflip-flop status, and then read back through the configuration interface. The CAP input issampled by CLK to generate an internal gcap signal. The I/O and CLB flip-flop status arecaptured into an FPGA configuration memory cell when the gcap signal is High. There areoperation modes, a one-shot mode, or a continuous mode.In one-shot mode, after the first CAP falling edge, gcap is held to 0 to avoid furthercapturing. An explicit RCAP command is required to re-arm the capture circuit.In continuous mode, the CAP input is simply sampled by CLK, and becomes the gcapsignal, allowing the user to control when to capture.CAPTURE_VIRTEX5 should not operate simultaneously with the FRAME_ECC_VIRTEX5primitive or the Readback CRC function (see Chapter9, “Readback CRC”) becausecapturing a value into configuration memory might cause a false error.Table 4-2:CAPTURE_VIRTEX5 Pin TablePin Name Type DescriptionCLK Input Clock for sampling the CAP input.CAP Input Active-High capture enable. The CAP input is sampled bythe rising edge of CLK.ICAP_VIRTEX5The ICAP_VIRTEX5 primitive works the same way as the SelectMAP configurationinterface except it is on the fabric side, and ICAP has a separate read/write bus, as opposedto the bidirectional bus in SelectMAP. The general SelectMAP timing diagrams and theSelectMAP bitstream ordering information as described in the “SelectMAP ConfigurationInterface” section of this user guide are also applicable to ICAP. It allows the user to accessconfiguration registers, readback configuration data, or partially reconfigure the FPGAafter configuration is done.ICAP has three data width selections through the ICAP WIDTH parameter: x8, x16, andx32.The two ICAP ports cannot be operated simultaneously. The design must start from the topICAP, then switch back and forth between the two.Table 4-3:ICAP_VIRTEX5 Pin TablePin Name Type DescriptionCLK Input ICAP interface clockCE Input Active-Low ICAP interface select. Equivalent to CS_B inthe SelectMAP interface.WRITE Input0=WRITE, 1=READ. Equivalent to the RDWR_B signal inthe SelectMAP interface.I[31:0]Input ICAP write data bus. The bus width depends onICAP_WIDTH parameter. The bit ordering is identical tothe SelectMAP interface. See SelectMap Data Ordering inFigure2-19.。

FPGA可编程逻辑器件芯片XC2S200E-5FG456I中文规格书

Chapter1 Configuration OverviewOverviewSpartan®-6 FPGAs are configured by loading application-specific configuration data—abitstream—into internal memory. Spartan-6 FPGAs can load themselves from an externalnonvolatile memory device or they can be configured by an external smart source, such asa microprocessor, DSP processor, microcontroller, PC, or board tester. In any case, there aretwo general configuration datapaths. The first is the serial datapath that is used tominimize the device pin requirements. The second datapath is the 8- or 16-bit datapathused for higher performance or access (or link) to industry-standard interfaces,ideal forexternal data sources like processors, or x8- or x16-parallel flash memory.Like processors and processor peripherals, Xilinx® FPGAs can be reprogrammed, insystem, on demand, an unlimited number of times.Because Xilinx FPGA configuration data is stored in CMOS configuration latches (CCLs), itmust be reconfigured after it is powered down. The bitstream is loaded each time into thedevice through special configuration pins. These configuration pins serve as the interfacefor a number of different configuration modes:•JTAG configuration mode•Master Serial/SPI configuration mode (x1, x2, and x4)•Slave Serial configuration mode•Master SelectMAP/BPI configuration mode (x8 and x16)•Slave SelectMAP configuration mode (x8 and x16)The configuration modes are explained in detail in Chapter2, Configuration InterfaceBasics.The specific configuration mode is selected by setting the appropriate level on the modeinput pins M[1:0]. The M1 and M0 mode pins should be set at a constant DC voltage leveland tied directly to ground or VCCO_2. The mode pins should not be toggled during orbefore configuration but can be toggled after. See Chapter2, Configuration InterfaceBasics, for the mode pin setting options.The terms Master and Slave refer to the direction of the configuration clock (CCLK):•In Master configuration modes, the Spartan-6 device drives CCLK from an internaloscillator by default or optional external master clock source GCLK0/USERCCLK. Toselect the desired frequency, the BitGen -g ConfigRate option is used for theinternal oscillator. The default is 2MHz. The CCLK output frequency varies withprocess, voltage, and temperature. The data sheet F MCCKTOL specification defines thefrequency tolerance. A frequency tolerance of ±50% means that a ConfigRate settingof 10 could generate a CCLK rate of between 5MHz and 15MHz.The BitGen sectionChapter 6:Readback and Configuration VerificationChapter 5:Configuration DetailsFDRO RegisterThe FDRO is for reading configuration data or captured data from the device. Loading thecommand register with the RCFG command, and then addressing the FDRO with a readcommand perform a readback.MASK RegisterMASK register performs writes to the CTL register. A 1 in bit N of the mask allows that bitposition to be written in the CTL register. The default value of the mask is 0.EYE_MASK RegisterThe EYE_MASK register stores the mask for the SCP pins for the Multi-Pin Wake-Upfeature. It is 16bits, with the lower 8 representing the mask. The upper 8 bits are reserved.The lower 8 bits are set from the -g wakeup_mask BitGen option.LOUT RegisterThe Legacy Output Register (LOUT) is used for daisy-chaining the configuration bitstream to other Xilinx devices. Data written to the LOUT is serialized and appears on theDOUT pin.CBC_REG RegisterThis register is used by the bitstream compression option to hold the Initial Vector (IV) forAES decryption.IDCODE RegisterAny writes to the FDRI register must be preceded by a write to this register. The providedIDCODE must match the device’s IDCODE. See Configuration Sequence, page82.A read of this register returns the device IDCODE.CSBO RegisterThe CSBO register is designed to assert the CSB_O signal and then ignore any incomingdata for a specified word count. It works much the same way as the LOUT register exceptthat it only outputs a Low on CSB_O and no data is passed through. Like the LOUTregister, multiple calls can be nested for different devices in support of daisy-chaining.Command Register (CMD)The Command Register is used to instruct the configuration control logic to strobe globalsignals and perform other configuration functions. The command present in the CMDregister is executed each time the FAR is loaded with a new value. Table5-33 lists theCommand Register commands and codes.Table 5-33:Command Register CodesCommand Code DescriptionNULL00000Null CommandWCFG00001Writes Configuration Data: Used prior to writing configurationdata to the FDRI.Configuration PacketsTable 5-33:Command Register Codes (Cont’d)Command Code DescriptionMFW00010Multiple Frame Write: Used to perform a write of a single framedata to multiple frame addresses.LFRM00011Last Frame: Deasserts the GHIGH_B signal, activating allinterconnects. The GHIGH_B signal is asserted with the AGHIGHcommand.RCFG00100Reads Configuration Data: Used prior to reading configurationdata from the FDRO.START00101Begins the Startup Sequence: Initiates the startup sequence. Thestartup sequence begins after a successful CRC check and aDESYNC command are performed.RCRC00111Resets CRC: Resets the CRC register.AGHIGH01000Asserts the GHIGH_B signal: Places all interconnect in a high-Zstate to prevent contention when writing new configuration data.This command is only used in shutdown reconfiguration.Interconnect is reactivated with the LFRM command. GRESTORE01010Pulses the GRESTORE signal: Sets/resets (depending on userconfiguration) IOB and CLB flip-flops.SHUTDOWN01011Begins the shutdown sequence: Initiates the shutdown sequence,disabling the device when finished. Shutdown activates on the nextsuccessful CRC check or RCRC instruction (typically, an RCRCinstruction).DESYNC01101Resets the DALIGN Signal: Used at the end of configuration todesynchronize the device. After desynchronization, all values onthe configuration data pins are ignored.IPROG01110Generates reboot_rst to reconfigure from the address specified inthe general register.Chapter 7:Reconfiguration and MultiBoot。

FPGA可编程逻辑器件芯片XC2S400E-6FTG256I中文规格书

Readback and Configuration VerificationSpartan®-6 devices allow users to read configuration memory through the SelectMAP,ICAP, and JTAG interfaces. During readback, the user reads all configuration memorycells, including the current values on all user memory elements (LUT RAM, SRL16, andblock RAM).To read configuration memory, users must send a sequence of commands to the device toinitiate the readback procedure. Once initiated, the device dumps the contents of itsconfiguration memory to the SelectMAP or JTAG interface. The Accessing ConfigurationRegisters through the SelectMAP Interface section and IEEE Std 1149.1 JTAG describe thesteps for reading configuration memory.Users can send the readback command sequence from a custom microprocessor, CPLD, orFPGA-based system, or use iMPACT to perform JTAG-based readback verify. iMPACT, thedevice programming software provided with the ISE® software by Xilinx, can perform allreadback and comparison functions for Spartan-6 devices and report to the user whetherthere were any configuration errors.Once configuration memory is read from the device, the next step is to determine if thereare any errors by comparing the readback bitstream to the configuration bitstream. TheVerifying Readback Data section explains how this is done.Preparing a Design for ReadbackThere are two mandatory bitstream settings for readback using JTAG or SelectMAP: theBitGen security setting must not prohibit readback (-g Security:none), and bitstreamencryption must not be used. Additionally, if readback is to be performed through theSelectMAP interface, the port must be set to retain its function after configuration bysetting the persist option in BitGen (-g Persist:Yes), otherwise the SelectMAP data pinsrevert to user I/O, precluding further configuration operations. Beyond these security andencryption requirements, no special considerations are necessary to enable readbackthrough the boundary-scan port. Also, these requirements are not necessary when usingreadback via the ICAP. Limitations for readback are:•Performing a readback while the design is in operation (without providing ashutdown command) results in reading back invalid block RAM data. The actualcontents of the block RAM are unaffected.•Performing a readback (with or without a shutdown command) corrupts the contentsof block RAMs configured in 9K mode.Chapter 8:Readback CRC•In addition, the JTAG instruction register (IR) must not contain any configurationinstructions (CFG_IN, CFG_OUT, or ISC_ENABLE). When these instructions arepresent, at any time, the readback CRC logic can not access the configuration logicand cannot run. Any configuration operation performed via the JTAG interfaceshould finish by loading the IR with a value other than these three configurationinstructions.These dynamically changeable memory locations are masked during backgroundreadback:•Look-up tables (LUTs) configured as distributed RAM or shift registers are notchecked. In Spartan-6 FPGAs, only SLICEMs can be configured as these memoryelements. Due to the granularity of the LUT masking, any LUTs in the same verticalalignment as a LUTRAM or SRL16 in a given frame are not checked. To ensuremaximum coverage of the readback CRC, these LUTs used as memories must be keptin separate frames from the LUTs used for logic.•Block RAM content is dynamic, so it is not expected to be the same as the initialconfiguration; therefore, these elements are not checked.•Use of the PLL DRP is not masked; therefore, any change to the PLL results in a CRCerror.•The I/O interface DRP at the top and bottom can be masked; however, LUTs for CLBsin the same frame are also masked. Similarly, masking LUTs in the top or bottomframe will also mask the I/O interface.CRC MaskingConfiguration data is organized into frames. Each frame of data configures portions ofmultiple configurable logic blocks (CLBs), and multiple frames are needed to configure asingle CLB. The granularity of masking for the Spartan-6FPGA is at a single frame thatspans several CLBs. To understand the coverage of the CRC, it is necessary to understandthe masking details. Three masking scenarios are presented:•CLBs containing LUTs configured as distributed RAM•CLBs near top or bottom IOI DRP•CLBs near top or bottom IOI DRP with LUT configured as distributed RAMNote:Distributed RAM is a LUT configured as a distributed RAM or a shift register.Chapter 10:Advanced JTAG ConfigurationsJTAG Configuration/Readback3.Overwrite the FPGA configuration with a design that does not use inversion at the inputs.4.Modify the original design to avoid the IOB invert path.JSTART and JSHUTDOWN are instructions specific to the Spartan-6 architecture and configuration flow. In Spartan-6 devices, the TAP controller is not reset by thePROGRAM_B pin and can only be reset by bringing the controller to the TLR state. The TAP controller is reset on power up.For details on the standard boundary-scan instructions EXTEST, INTEST, and BYPASS, refer to IEEE Std 1149.1.Boundary-Scan ArchitectureSpartan-6 device registers include all registers required by IEEE Std 1149.1. In addition to the standard registers, the family contains optional registers for simplified testing and verification (Table 10-1).Boundary-Scan RegisterThe test primary data register is the boundary-scan register. Boundary-scan operation is independent of individual IOB configuration. Each IOB, bonded or unbonded, starts as bidirectional with 3-state control. Later, it can be configured to be an input, output, or 3-state only. Therefore, three data register bits are provided per IOB (Figure 10-1).When conducting a data register (DR) operation, the DR captures data in a parallel fashion during the CAPTURE-DR state. The data is then shifted out and replaced by new data during the SHIFT-DR state. For each bit of the DR, an update latch is used to hold the input data stable during the next SHIFT-DR state. The data is then latched during the UPDATE-DR state when TCK is Low.The update latch is opened each time the TAP controller enters the UPDATE-DR state. Care is necessary when exercising an INTEST or EXTEST to ensure that the proper data has been latched before exercising the command. This is typically accomplished by using the SAMPLE instruction.Table 10-1:Spartan-6 FPGA JTAG Registers Register Name Register LengthDescription Boundary-Scan Register 3bits per I/OControls and observes input, output, and output enable Instruction Register 6bitsHolds current instruction opcode and captures internal device status BYPASS Register 1bitBypasses the device Identification Register 32bitsCaptures the Device ID JTAG Configuration Register 16bitsAllows access to the configuration bus when using the CFG_IN or CFG_OUT instructions USERCODE Register 32bitsCaptures the user-programmable code User-Defined Registers (USER1,USER2, USER3, and USER4)Design specific Design specificChapter 10:Advanced JTAG Configurations。

FPGA可编程逻辑器件芯片XC2S600E-6FGG456C中文规格书

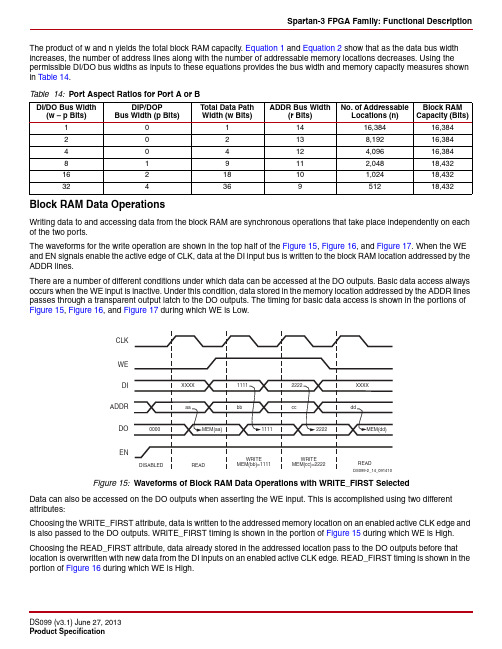

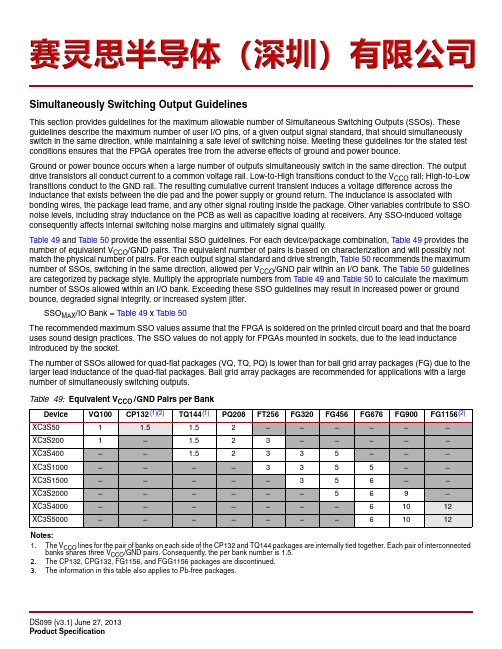

Spartan-3 FPGA Design DocumentationThe functionality of the Spartan®-3 FPGA family is described in the following documents. The topics covered in each guide are listed.•UG331: Spartan-3 Generation FPGA User Guide •Clocking Resources•Digital Clock Managers (DCMs)•Block RAM•Configurable Logic Blocks (CLBs)-Distributed RAM -SRL16 Shift Registers -Carry and Arithmetic Logic•I/O Resources•Embedded Multiplier Blocks •Programmable Interconnect •ISE® Software Design Tools •IP C ores•Embedded Processing and Control Solutions •Pin Types and Package Overview •Package Drawings •Powering FPGAs•UG332: Spartan-3 Generation Configuration User Guide •Configuration Overview -Configuration Pins and Behavior -Bitstream Sizes•Detailed Descriptions by Mode-Master Serial Mode using Xilinx Platform Flash PROM-Slave Parallel (SelectMAP) using a Processor -Slave Serial using a Processor -JTAG Mode•ISE iMPACT Programming ExamplesCreate a Xilinx user account and sign up to receiveautomatic e-mail notification whenever this data sheet or the associated user guides are updated.For specific hardware examples, see the Spartan-3 FPGA Starter Kit board web page, which has links to various design examples and the user guide.DS099 (v3.1) June 27, 2013Product SpecificationThe output frequency (f CLKFX) can be expressed as a function of the incoming clock frequency (f CLKIN) as follows:f CLKFX = f CLKIN(CLKFX_MULTIPL Y/CLKFX_DIVIDE)Equation3 Regarding the two attributes, it is possible to assign any combination of integer values, provided that two conditions are met:•The two values fall within their corresponding ranges, as specified in Table18.•The f CLKFX frequency calculated from the above expression accords with the DCM’s operating frequency specifications.For example, if CLKFX_MULTIPL Y = 5 and CLKFX_DIVIDE = 3, then the frequency of the output clock signal would be 5/3 that of the input clock signal.DFS Frequency ModesThe DFS supports two operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DFS_FREQUENCY_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits the two DFS outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows both these outputs to operate at the highest possible frequencies. DFS With or Without the DLLThe DFS component can be used with or without the DLL component:Without the DLL, the DFS component multiplies or divides the CLKIN signal frequency according to the respective CLKFX_MULTIPL Y and CLKFX_DIVIDE values, generating a clock with the new target frequency on the CLKFX and CLKFX180 outputs. Though classified as belonging to the DLL component, the CLKIN input is shared with the DFS component. This case does not employ feedback loop; therefore, it cannot correct for clock distribution delay.With the DLL, the DFS operates as described in the preceding case, only with the additional benefit of eliminating the clock distribution delay. In this case, a feedback loop from the CLK0 output to the CLKFB input must be present.The DLL and DFS components work together to achieve this phase correction as follows: Given values for theCLKFX_MULTIPL Y and CLKFX_DIVIDE attributes, the DLL selects the delay element for which the output clock edge coincides with the input clock edge whenever mathematically possible. For example, when CLKFX_MULTIPL Y = 5 and CLKFX_DIVIDE = 3, the input and output clock edges will coincide every three input periods, which is equivalent in time to five output periods.Smaller CLKFX_MULTIPL Y and CLKFX_DIVIDE values achieve faster lock times. With no factors common to the two attributes, alignment will occur once with every number of cycles equal to the CLKFX_DIVIDE value. Therefore, it is recommended that the user reduce these values by factoring wherever possible. For example, given CLKFX_MULTIPL Y = 9 and CLKFX_DIVIDE = 6, removing a factor of three yields CLKFX_MULTIPL Y = 3 and CLKFX_DIVIDE = 2. While both value-pairs will result in the multiplication of clock frequency by 3/2, the latter value-pair will enable the DLL to lock more quickly.Table 18:DFS AttributesAttribute Description ValuesDFS_FREQUENCY_MODE Chooses between High Frequency and Low Frequency modes Low, HighCLKFX_MULTIPL Y Frequency multiplier constant Integer from 2 to 32 CLKFX_DIVIDE Frequency divisor constant Integer from 1 to 32Table 19:DFS SignalsSignal Direction DescriptionCLKFX Output Multiplies the CLKIN frequency by the attribute-value ratio (CLKFX_MULTIPL Y/CLKFX_DIVIDE) to generate a clock signal with a new target frequency.CLKFX180Output Generates a clock signal with same frequency as CLKFX, only shifted 180° out-of-phase.Both the Fixed Phase and Variable Phase operating modes employ this calculation. If the PHASE_SHIFT value is zero, then CLKFB and CLKIN will be in phase, the same as when the PS component is disabled. When the PHASE_SHIFT value is positive, the CLKFB signal will be shifted later in time with respect to CLKIN. If the attribute value is negative, the CLKFB signal will be shifted earlier in time with respect to CLKIN.The Fixed Phase ModeThis mode fixes the desired fine phase shift to a fraction of the T CLKIN, as determined by Equation4 and its user-selected PHASE_SHIFT value P. The set of waveforms insection [b] of Figure22 illustrates the relationship between CLKFB and CLKIN in the Fixed Phase mode. In the Fixed Phase mode, the PSEN, PSCLK and PSINCDEC inputs are not used andmust be tied to GND. Fixed phase shift requires ISE software version 10.1.03 or later.ConfigurationSpartan-3 devices are configured by loading application specific configuration data into the internal configuration memory. Configuration is carried out using a subset of the device pins, some of which are "Dedicated" to one function only, while others, indicated by the term "Dual-Purpose", can be re-used as general-purpose User I/Os once configuration is complete.Depending on the system design, several configuration modes are supported, selectable via mode pins. The mode pins M0, M1, and M2 are Dedicated pins. The mode pin settings are shown in Table 26.The HSWAP_EN input pin defines whether the I/O pins that are not actively used during configuration have pull-up resistorsduring configuration. By default, HSWAP_EN is tied High (via an internal pull-up resistor if left floating) which shuts off the pull-up resistors on the user I/O pins during configuration. When HSWAP_EN is tied Low, user I/Os have pull-ups during configuration. The Dedicated configuration pins (CCLK, DONE, PROG_B, M2, M1, M0, HSWAP_EN) and the JTAG pins (TDI, TMS, TCK, and TDO) always have a pull-up resistor to VCCAUX during configuration, regardless of the value on the HSWAP_EN pin. Similarly, the dual-purpose INIT_B pin has an internal pull-up resistor to VCCO_4 or VCCO_BOTTOM, depending on the package style.Depending on the chosen configuration mode, the FPGA either generates a CCLK output, or CCLK is an input accepting an externally generated clock.A persist option is available which can be used to force the configuration pins to retain their configuration function even after device configuration is complete. If the persist option is not selected then the configuration pins with the exception of CCLK, PROG_B, and DONE can be used as user I/O in normal operation. The persist option does not apply to the boundary-scan related pins. The persist feature is valuable in applications that readback configuration data after entering the User mode.Table 27 lists the total number of bits required to configure each FPGA as well as the PROMs suitable for storing those bits. See DS123: Platform Flash In-System Programmable Configuration PROMs data sheet for more information.The maximum bitstream length that Spartan-3 FPGAs support in serial daisy-chains is 4,294,967,264 bits (4Gbits), roughly equivalent to a daisy-chain with 323 XC3S5000 FPGAs. This is a limit only for serial daisy-chains where configuration data is passed via the FPGA’s DOUT pin. There is no such limit for JTAG chains.Table 26:Spartan-3 FPGAs Configuration Mode Pin SettingsConfiguration Mode (1)M0M1M2Synchronizing ClockData WidthSerial DOUT (2)Master Serial 000CCLK Output 1Y es Slave Serial 111CCLK Input 1Y es Master Parallel 110CCLK Output 8No Slave Parallel 011CCLK Input 8No JTAG 11TC K Input1NoNotes:1.The voltage levels on the M0, M1, and M2 pins select the configuration mode.2.The daisy chain is possible only in the Serial modes when DOUT is used.Table 27:Spartan-3 FPGA Configuration DataDevice File Sizes Xilinx Platform Flash PROMSerial ConfigurationParallel ConfigurationXC3S50439,264XCF01S XCF08P XC3S2001,047,616XCF01S XCF08P XC3S4001,699,136XCF02S XCF08P XC3S10003,223,488XCF04S XCF08P XC3S15005,214,784XCF08P XCF08P XC3S20007,673,024XCF08P XCF08P XC3S400011,316,864XCF16P XCF16P XC3S500013,271,936XCF16PXCF16P。

FPGA可编程逻辑器件芯片XC2S200-6FG456C中文规格书

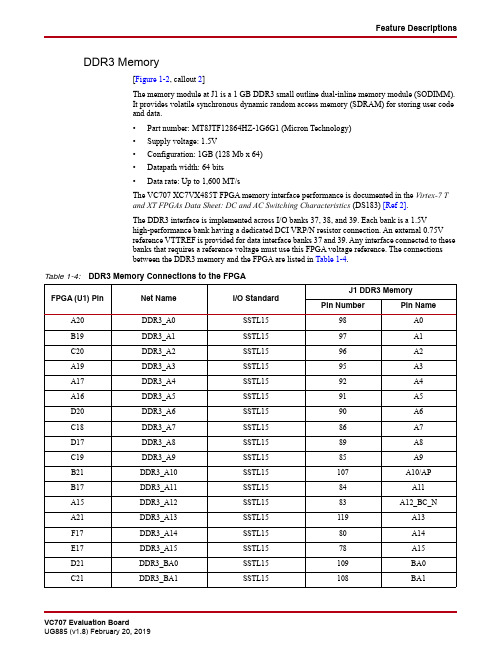

VITA 57.1 FMC1 HPC Connector (Partially Populated)[Figure1-2, callout 30]The VC707 board implements two instances of the FMC HPC VITA 57.1 specification connector.This section discusses the FMC1 HPC J35 connector.Note:The FMC1 HPC J35 connector is a keyed connector oriented so that a plug-on card facesaway from the VC707 board.The VITA 57.1 FMC standard calls for two connector densities: a high pin count (HPC) and a lowpin count (LPC) implementation. A 400 pin 10x40 position connector form factor is used for bothversions. The HPC version is fully populated with all 400 pins present. The LPC version is partiallypopulated with 160 pins.The 10x40 rows of an FMC HPC connector provides pins for up to:•160 single-ended or 80 differential user-defined signals•10 GTX transceivers• 2 GTX clocks• 4 differential clocks•159 ground and 15 power connectionsThe VC707 board FMC1 HPC connector J35 implements a subset of the maximum signal and clockconnectivity capabilities:•80 differential user-defined pairs•34 LA pairs (LA00-LA33)•24 HA pairs (HA00-HA23)•22 HB pairs (HB00-HB21)•8 GTX transceivers• 2 GTX clocks• 2 differential clocksThe FMC1 HPC signals are distributed across GTX Quads 118 and 119. Each Quad has the VCCOvoltage connected to V ADJ.Note:The VC707 board VADJ voltage for the FMC1 HPC (J35) connector is determined by theFMC VADJ power sequencing logic described in FMC_VADJ Voltage Control.VITA 57.1 FMC2 HPC Connector (Partially Populated)[Figure1-2, callout 31]The VC707 board implements two instances of the FMC HPC VITA 57.1 specification connector.This section discusses the FMC2 HPC J37 connector.Note:The FMC2 HPC J37 connector is a keyed connector oriented so that a plug-on card facesaway from the VC707 board.The FMC standard calls for two connector densities: a High Pin Count (HPC) and a Low Pin Count(LPC) implementation. A 400pin 10x40 position connector form factor is used for both versions.The HPC version is fully populated with all 400 pins present. The LPC version is partially populatedwith 160 pins.C2FMC2_HPC_DP0_C2M_P (1)N2D1PWRCTL1_VCC4B_PG AL32C3FMC2_HPC_DP0_C2M_N (1)N1D4FMC2_HPC_GBTCLK0_M2C_P (1)K8C6FMC2_HPC_DP0_M2C_P (1)P8D5FMC2_HPC_GBTCLK0_M2C_N (1)K7C7FMC2_HPC_DP0_M2C_N (1)P7D8FMC2_HPC_LA01_CC_P LVCMOS18AF41C10FMC2_HPC_LA06_P LVCMOS18AD38D9FMC2_HPC_LA01_CC_N LVCMOS18AG41C11FMC2_HPC_LA06_N LVCMOS18AE38D11FMC2_HPC_LA05_P LVCMOS18AF42C14FMC2_HPC_LA10_P LVCMOS18AB41D12FMC2_HPC_LA05_N LVCMOS18AG42C15FMC2_HPC_LA10_N LVCMOS18AB42D14FMC2_HPC_LA09_P LVCMOS18AJ38C18FMC2_HPC_LA14_P LVCMOS18AB38D15FMC2_HPC_LA09_N LVCMOS18AK38C19FMC2_HPC_LA14_N LVCMOS18AB39D17FMC2_HPC_LA13_P LVCMOS18W40C22FMC2_HPC_LA18_CC_P LVCMOS18U36D18FMC2_HPC_LA13_N LVCMOS18Y40C23FMC2_HPC_LA18_CC_N LVCMOS18T37D20FMC2_HPC_LA17_CC_P LVCMOS18U37C26FMC2_HPC_LA27_P LVCMOS18P32D21FMC2_HPC_LA17_CC_N LVCMOS18U38C27FMC2_HPC_LA27_N LVCMOS18P33D23FMC2_HPC_LA23_P LVCMOS18R38C30FMC2_HPC_IIC_SCL U52.6D24FMC2_HPC_LA23_N LVCMOS18R39C31FMC2_HPC_IIC_SDA U52.5D26FMC2_HPC_LA26_P LVCMOS18N33C34GA0=0=GND D27FMC2_HPC_LA26_N LVCMOS18N34C35VCC12_P D29FMC2_HPC_TCK_BUF U19.13C37VCC12_P D30FMC1_TDO_FMC2_TDI U27.2C39VCC3V3D31FMC2_TDO_FPGA_TDI U46.3D32VCC3V3D33FMC2_HPC_TMS_BUF U19.16D34NCD35GA1=0=GND D36VCC3V3D38VCC3V3D40VCC3V3Table 1-28:J37 VITA 57.1 FMC 2 HPC Connections (Cont’d)J37FMC 2HPC PinSchematic Net NameI/O Standard U1 FPGA PinJ37 FMC 2 HPC PinSchematic Net NameI/O Standard U1 FPGA PinE2FMC2_HPC_HA01_CC_P LVCMOS18AD32F1FMC2_HPC_PG_M2C LVCMOS18AF29E3FMC2_HPC_HA01_CC_N LVCMOS18AD33F4FMC2_HPC_HA00_CC_P LVCMOS18AB33E6FMC2_HPC_HA05_P LVCMOS18Y32F5FMC2_HPC_HA00_CC_N LVCMOS18AC33E7FMC2_HPC_HA05_N LVCMOS18Y33F7FMC2_HPC_HA04_P LVCMOS18AB29E9FMC2_HPC_HA09_P LVCMOS18AE29F8FMC2_HPC_HA04_N LVCMOS18AC29E10FMC2_HPC_HA09_N LVCMOS18AE30F10FMC2_HPC_HA08_P LVCMOS18AA31E12FMC2_HPC_HA13_P LVCMOS18AE32F11FMC2_HPC_HA08_N LVCMOS18AA32E13FMC2_HPC_HA13_N LVCMOS18AE33F13FMC2_HPC_HA12_P LVCMOS18AF34E15FMC2_HPC_HA16_P LVCMOS18AG36F14FMC2_HPC_HA12_N LVCMOS18AG34E16FMC2_HPC_HA16_N LVCMOS18AH36F16FMC2_HPC_HA15_P LVCMOS18AE37E18FMC2_HPC_HA20_P LVCMOS18AD36F17FMC2_HPC_HA15_N LVCMOS18AF37E19FMC2_HPC_HA20_N LVCMOS18AD37F19FMC2_HPC_HA19_P LVCMOS18AC35E21FMC2_HPC_HB03_P LVCMOS18AT16F20FMC2_HPC_HA19_N LVCMOS18AC36E22FMC2_HPC_HB03_N LVCMOS18AU16F22FMC2_HPC_HB02_P LVCMOS18A V16E24FMC2_HPC_HB05_P LVCMOS18BA17F23FMC2_HPC_HB02_N LVCMOS18AW16E25FMC2_HPC_HB05_N LVCMOS18BB17F25FMC2_HPC_HB04_P LVCMOS18AU18E27FMC2_HPC_HB09_P LVCMOS18A V20F26FMC2_HPC_HB04_N LVCMOS18A V18E28FMC2_HPC_HB09_N LVCMOS18AW20F28FMC2_HPC_HB08_P LVCMOS18AY20E30FMC2_HPC_HB13_P LVCMOS18AT20F29FMC2_HPC_HB08_N LVCMOS18BA20E31FMC2_HPC_HB13_N LVCMOS18AT19F31FMC2_HPC_HB12_P LVCMOS18AU19E33FMC2_HPC_HB19_P LVCMOS18AP18F32FMC2_HPC_HB12_N LVCMOS18A V19E34FMC2_HPC_HB19_N LVCMOS18AP17F34FMC2_HPC_HB16_P LVCMOS18AR18E36FMC2_HPC_HB21_P LVCMOS18AN19F35FMC2_HPC_HB16_N LVCMOS18AR17E37FMC2_HPC_HB21_N LVCMOS18AN18F37FMC2_HPC_HB20_P LVCMOS18AK17E39V ADJF38FMC2_HPC_HB20_N LVCMOS18AL17F40V ADJTable 1-28:J37 VITA 57.1 FMC 2 HPC Connections (Cont’d)J37FMC 2HPC PinSchematic Net NameI/O Standard U1 FPGA PinJ37 FMC 2 HPC PinSchematic Net NameI/O Standard U1 FPGA PinAppendix B:VITA 57.1 FMC Connector Pinouts。

FPGA可编程逻辑器件芯片XC2VP4-5FG456C-ES中文规格书

Feature DescriptionsSGMII GTX Transceiver Clock Generation[Figure1-2, callout 16]An Integrated Circuit Systems ICS844021I chip (U2) generates a high-quality, low-jitter, 125MHzLVDS clock from a 25MHz crystal (X3). This clock is sent to FPGA U1, Bank 113 GTXtransceiver (clock pins AH8 (P) and AH7 (N)) driving the SGMII interface. Series AC couplingcapacitors are present to allow the clock input of the FPGA to set the common mode voltage.Figure1-17 shows the Ethernet SGMII clock source.Figure 1-17:Ethernet 125 MHz SGMII GTX ClockReferencesDetails about the tri-mode Ethernet MAC core are provided in LogiCORE IP Tri-Mode EthernetMAC Product Guide for Vivado Design Suite (PG051) [Ref9] and in the LogiCORE IP Tri-ModeEthernet MAC v4.5 User Guide (UG138) [Ref13].The product brief for the Marvell 88E1111 Alaska Gigabit Ethernet Transceiver can be found at theMarvell website [Ref21].The data sheet can be obtained under NDA with Marvell. Contact information is at the Marvellwebsite [Ref21].For more information about the ICS844021 device, go to the Integrated Device Technology website[Ref22] and search for part number ICS844021.USB-to-UART Bridge[Figure1-2, callout 17]The VC707 board contains a Silicon Labs CP2103GM USB-to-UART bridge device (U44) whichallows a connection to a host computer with a USB port. The USB cable is supplied in the VC707Evaluation Kit (Type-A end to host computer, Type mini-B end to VC707 board connector J17). TheCP2103GM is powered by the USB 5V provided by the host PC when the USB cable is plugged intothe USB port on the VC707 board.Xilinx UART IP is expected to be implemented in the FPGA logic. The FPGA supports theUSB-to-UART bridge using four signal pins: Transmit (TX), Receive (RX), Request to Send (RTS),and Clear to Send (CTS).Silicon Labs provides royalty-free Virtual COM Port (VCP) drivers for the host computer. Thesedrivers permit the CP2103GM USB-to-UART bridge to appear as a COM port to communicationsapplication software (for example, TeraTerm) that runs on the host computer. The VCP deviceChapter 1:VC707 Evaluation Board FeaturesTable 1-26:GPIO Connections to FPGA U1 (Cont’d)FPGA (U1) Pin Schematic Net Name I/O Standard GPIO PinAW40GPIO_SW_W LVCMOS18SW7.3A V39GPIO_SW_C LVCMOS18SW6.38-Pole DIP SwitchA V30GPIO_DIP_SW0LVCMOS18SW2.16AY33GPIO_DIP_SW1LVCMOS18SW2.15BA31GPIO_DIP_SW2LVCMOS18SW2.14BA32GPIO_DIP_SW3LVCMOS18SW2.13AW30GPIO_DIP_SW4LVCMOS18SW2.12AY30GPIO_DIP_SW5LVCMOS18SW2.11BA30GPIO_DIP_SW6LVCMOS18SW2.10BB31GPIO_DIP_SW7LVCMOS18SW2.9User Rotary SwitchAT31ROTARY_INCB LVCMOS18SW10.6AW31ROTARY_PUSH LVCMOS18SW10.5AR33ROTARY_INCA LVCMOS18SW10.1User SMAAN31USER_SMA_GPIO_P LVCMOS18J33.1AP31USER_SMA_GPIO_N LVCMOS18J34.1Switches[Figure1-2, callout 27 - 28]The VC707 board Evaluation Board includes a power and a configuration switch:•Power On/Off Slide Switch SW12 (callout 27)•FPGA_PROG_B SW9, active-Low (callout 28)Power On/Off Slide Switch SW12[Figure1-2, callout 27]The VC707 board power switch is SW12. Sliding the switch actuator from the Off to On positionapplies 12V power from J18, a 6-pin mini-fit connector. Green LED DS16 illuminates when theVC707 board power is on. See Power Management for details on the onboard power system.Caution!Do NOT plug a PC ATX power supply 6-pin connector into J18 on the VC707 board.The ATX 6-pin connector has a different pinout than J18. Connecting an ATX 6-pin connectorinto J18 will damage the VC707 board and void the board warranty.Feature DescriptionsThe VC707 Evaluation Kit provides the adapter cable shown in Figure 1-29 for powering the VC707 board from the ATX power supply 4-pin peripheral connector. The Xilinx part number for this cable is 2600304, and is equivalent to Sourcegate Technologies part number AZCBL-WH-1109-RA4. For information on ordering this cable, see [Ref 27].Figure 1-30 shows the power connector J18, power switch SW12 and indicator LED DS16.FPGA_PROG_B Pushbutton SW9 (Active-Low)[Figure 1-2, callout 28]Switch SW9 grounds the FPGA's PROG_B pin when pressed. This action initiates an FPGA reconfiguration. The FPGA_PROG_B signal is connected to FPGA U1 pin AJ11.See 7Series FPGAs Configuration User Guide (UG470) [Ref 3] for further details on configuring the 7series FPGAs.Figure 1-31 shows SW9.Figure 1-29:ATX Power Supply Adapter CableFigure 1-30:Power On/Off Switch SW15UG885_c1_26_030512To A TX 4-Pin Peripheral Power ConnectorTo J18 on VC707 BoardUG885_c1_27_030512VCC12_P_INVCC12_PR2791k Ω1%INPUT_GND1234SW12GND C320330μF 25V C4711μF 25VGNDDS1656J1812345612V N/C COM 12V N/C COMINPUT_GNDPowerPCIeU73138765Appendix B:VITA 57.1 FMC Connector PinoutsAppendix C:Xilinx Constraints File。

FPGA可编程逻辑器件芯片XC2S200E-6FT256C中文规格书

Chapter1 Introduction to the RocketIO GTX TransceiverOverviewThe RocketIO™ GTX transceiver is a power-efficient transceiver for Virtex®-5 FPGAs. TheGTX transceiver is highly configurable and tightly integrated with the programmable logicresources of the FPGA. It provides the following features to support a wide variety ofapplications:•Current Mode Logic (CML) serial drivers/buffers with configurable termination,voltage swing, and coupling.•Programmable TX pre-emphasis, RX equalization, and linear and decision feedbackequalization (DFE) for optimized signal integrity.•Line rates from 750Mb/s to 6.5Gb/s, with optional 5x digital oversampling requiredfor rates between 150Mb/s and 750Mb/s. The nominal operation range of the sharedPMA PLL is from 1.5GHz to 3.25GHz. These are nominal values, see DS202: Virtex-5FPGA Data Sheet for specifications.•Optional built-in PCS features, such as 8B/10B encoding, comma alignment, channelbonding, and clock correction.•Fixed latency modes for minimized, deterministic datapath latency.•Beacon signaling for PCI Express® designs and Out-of-Band signaling includingCOM signal support for SATA designs.•RX/TX Gearbox provides header insertion and extraction support for 64B/66B and64B/67B (Interlaken) protocols.•Receiver eye scan:♦Vertical eye scan in the voltage domain for testing purposes♦Horizontal eye scan in the time domain for testing purposesThe first-time user is recommended to read High-Speed Serial I/O Made Simple[Ref1], whichdiscusses high-speed serial transceiver technology and its applications.Table1-1 lists some of the standard protocols designers can implement using the GTXtransceiver. The Xilinx® CORE Generator™ tool includes a Wizard to automaticallyconfigure GTX transceivers to support one of these protocols or perform customconfiguration (see Chapter2, “RocketIO GTX Transceiver Wizard”).The GTX_DUAL tile offers a data rate range and features that allow physical layer supportfor various protocols as illustrated in Table1-1.Ports and AttributesTable 1-4 lists alphabetically the signal names, clock domains, directions, and descriptions for the CRC ports, and provides links to their detailed descriptions.TXPOWERDOWN0[1:0]TXPOWERDOWN1[1:0]InTXUSRCLK2(1)Powers down the TX lanes.Power Control (page 111), Receive Detect Support for PCI Express Operation (page 154), TX Out-of-Band/Beacon Signaling (page 157)TXPREEMPHASIS0[3:0]TXPREEMPHASIS1[3:0]In Async Controls the pre-emphasis.Configurable TX Driver (page 151)TXRESET0TXRESET1In AsyncResets the PCS of the GTXtransmitter, including the phase adjust FIFO, the 8B/10B encoder, and the FPGA TX interface.Reset (page 102), FPGA TX Interface (page 122)TXRUNDISP0[3:0] TXRUNDISP1[3:0]Out TXUSRCLK2Indicates the current running disparity of the 8B/10B encoder.Configurable 8B/10B Encoder (page 131)TXSEQUENCE0[6:0]TXSEQUENCE1[6:0]In TXUSRCLK2Input to the TX Gearbox from a sequence counter implemented in the FPGA logic.TX Gearbox (page 134)TXSTARTSEQ0TXSTARTSEQ1In TXUSRCLK2Input to the TX Gearbox from theFPGA logic indicating the start of a TX sequence.TX Gearbox (page 134)TXUSRCLK0TXUSRCLK1In N/AProvides a clock for the internal TX PCS datapath.FPGA TX Interface(page 122), TX Buffering, Phase Alignment, and TX Skew Reduction (page 143)TXUSRCLK20TXUSRCLK21In N/ASynchronizes the FPGA logic with the TX interface.FPGA TX Interface (page 122)Notes:1.TXPOWERDOWN0[1:0] and TXPOWERDOWN1[1:0] of the GTX_DUAL tile belong to the TXUSRCLK2 clock domain. This isdifferent from the GTP_DUAL tile implementation where TXPOWERDOWN0[1:0] and TXPOWERDOWN1[1:0] are asynchronous.Table 1-3:GTX_DUAL Port Summary (Cont’d)PortDirDomainDescriptionSection (Page)Table 1-4:CRC Port Summary PortDir Domain DescriptionSection (Page)CRCCLK In N/A CRC clock.Cyclic Redundancy Check (page 242)CRCDATAVALID In CRCCLK Indicates valid data on 32-bit CRCIN inputs.Cyclic Redundancy Check (page 243)CRCDATAVALIDA In CRCCLK Indicates valid data on 64-bit CRCIN inputs.Cyclic Redundancy Check (page 242)CRCDATAWIDTH[2:0]InCRCCLKIndicates how many input data bytes are valid.Cyclic Redundancy Check (page 242)Table 1-5 lists alphabetically the attribute names, default values, and directions of the GTX_DUAL attributes, and provides links to their detailed descriptions.CRCIN[63:0]InCRCCLKCRC input data. The maximum datapath width is eight bytes.Cyclic Redundancy Check (page 242)CRCOUT[31:0]Out CRCCLK32-bit CRC output. CRCOUT is the byte-reversed, bit-inverted CRC value corresponding to theCRC calculation on valid bytes from the previous clock cycle and the previous CRC value.CRCDATAVALIDA must be driven High.Cyclic Redundancy Check (page 242)CRCRESET In CRCCLKSynchronous reset of CRC registers. Cyclic Redundancy Check (page 242)Table 1-4:CRC Port Summary (Cont’d)PortDir Domain DescriptionSection (Page)Table 1-5:GTX_DUAL Attribute Summary AttributeType DescriptionSection (Page)AC_CAP_DIS_0AC_CAP_DIS_1BooleanDisables built-in AC couplingcapacitors on receiver inputs when setto TRUE.RX Termination andEqualization (page 163)ALIGN_COMMA_WORD_0ALIGN_COMMA_WORD_1IntegerControls alignment of detectedcommas within a multi-byte datapath.Configurable Comma Alignment and Detection (page 193)CB2_INH_CC_PERIOD_0CB2_INH_CC_PERIOD_1IntegerSpecific for PCI Express designs,allows removal or retaining of control characters during channel bonding and clock correction.Configurable Channel Bonding (Lane Deskew) (page 219)CDR_PH_ADJ_TIME5-bit Binary Defines the waiting time afterdeassertion of the CDR phase reset before the optional reset sequence for PCI Express designs is complete during electrical idle.Reset (page 103), RX Clock Data Recovery (page 179)CHAN_BOND_1_MAX_SKEW_0CHAN_BOND_1_MAX_SKEW_1CHAN_BOND_2_MAX_SKEW_0CHAN_BOND_2_MAX_SKEW_1IntegerSets the maximum amount of lane skew allowed when using channel bonding. Must be set less than one-half the minimum distance between channel bonding sequences.Configurable Channel Bonding (Lane Deskew) (page 219)CHAN_BOND_KEEP_ALIGN_0CHAN_BOND_KEEP_ALIGN_1Boolean Specific for PCI Express designs, allows lanes to remember the previous skew during periods of electrical idle.Configurable Channel Bonding (Lane Deskew) (page 219)CHAN_BOND_LEVEL_0CHAN_BOND_LEVEL_1IntegerIndicates the amount of internal pipelining used for the elastic buffer control signals.Configurable Channel Bonding (Lane Deskew) (page 220)Chapter 2:RocketIO GTX Transceiver Wizard。

FPGA可编程逻辑器件芯片XC2V2000-6FG456I中文规格书

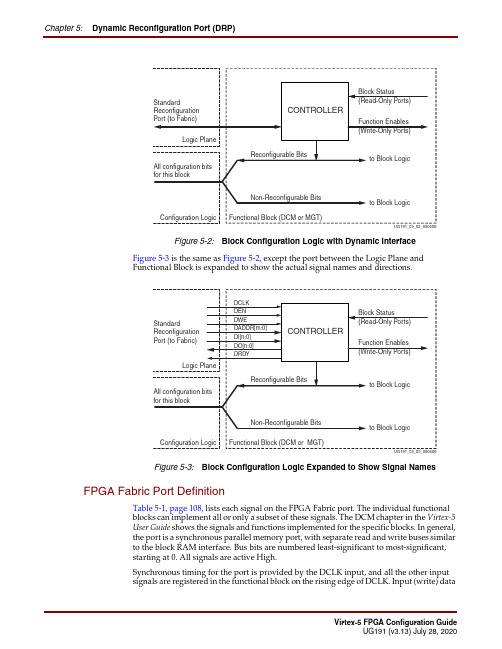

Figure 5-2:Block Configuration Logic with Dynamic Interface Figure5-3 is the same as Figure5-2, except the port between the Logic Plane andFunctional Block is expanded to show the actual signal names and directions.UG191_c5_03_050406 Figure 5-3:Block Configuration Logic Expanded to Show Signal Names FPGA Fabric Port DefinitionTable5-1, page108, lists each signal on the FPGA Fabric port. The individual functionalblocks can implement all or only a subset of these signals. The DCM chapter in the Virtex-5User Guide shows the signals and functions implemented for the specific blocks. In general,the port is a synchronous parallel memory port, with separate read and write buses similarto the block RAM interface. Bus bits are numbered least-significant to most-significant,starting at 0. All signals are active High.Synchronous timing for the port is provided by the DCLK input, and all the other inputsignals are registered in the functional block on the rising edge of DCLK. Input (write) dataMinor AddressEach column contains a certain number of frames, which are accessed using the minor address. The number of frames inside a column depends on the block type and on the column, as explained in “Block Type.”Block TypeThe block type divides the configuration address space into eight sections, but only four are used in Virtex-5 devices. This is done to separate configuration frames depending on their function or on how they are accessed.The four block types used in Virtex-5 devices are:∙Interconnect and Block Configuration ∙Block RAM contents∙Interconnect and block special frames ∙Block RAM non-configuration frameInterconnect and Block ConfigurationThis section of the configuration address space contains all the normal interconnect and block configuration frames (CLB, DSP, IOB, etc.). It also includes the frames that configure the parameters of the block RAM (such as port widths and FIFO operation). However, it does not include the contents of the block RAM.Table 6-16 lists the number of frames (minor addresses) per column when using this block type.Figure 6-12:Assignment of Major Addresses in a RowSecond Sequence:Major Address For Each BRAM ColumnUG191_c6_12_050406Notes:1.The sequence of normal major addresses is in light gray, and the sequence of block RAM major addresses is in dark gray.Chapter 7:Readback and Configuration VerificationTable7-9 shows a snippet from a logic allocation file for the ISE jc2_top example design.The line from the header comments explaining the line format has been moved to the startof the bit offset data for clarity. The Offset field gives the absolute bit offset from thebeginning of the readback frame data. The Frame Address field gives the frame addressthat the capture bit is located in, and the Frame Offset field gives the bit offset from the startof the frame. The Information field gives the mapping between the bit and the userdesign—for example, the DIR register (Table7-9) that is located in Slice X8Y15 is located atbit offset 100790. Captured DFF values are stored in their inverted sense.Table 7-9:Logic Allocation File FormatOffsetFrameAddressFrameOffsetInformation1007140x000e040042Block=B7, Latch=I, Net=RIGHT_IBUF 1007340x000e040062Block=A8, Latch=I, Net=RIGHT_IBUF 1007540x000e040082Block=B8, Latch=I, Net=RIGHT_IBUF 1007900x000e0400118Block=SLICE_X8Y15, Latch=YQ, Net=DIR 1190380x0010040062Block=C8, Latch=I, Net=STOP_IBUF 1191320x00100400156Block=SLICE_X11Y14, Latch=YQ, Net=RUN 1365660x00120200118Block=SLICE_X12Y15, Latch=XQ, Net=Q_3 1366060x00120200158Block=SLICE_X12Y14, Latch=XQ, Net=Q_1 1373000x0012040020Block=C9, Latch=O2, Net=Q_3 1373200x0012040040Block=D9, Latch=O2, Net=Q_1 1373980x00120400118Block=SLICE_X12Y15, Latch=YQ, Net=Q_2 1374380x00120400158Block=SLICE_X12Y14, Latch=YQ, Net=Q_0 1556620x0014040078Block=D10, Latch=O2, Net=Q_1 1740460x00160400158Block=D13, Latch=O2, Net=Q_2。

FPGA可编程逻辑器件芯片XC2S200-5FG456C中文规格书

0

SHIFT-IR

0

1 EXIT1-IR 1

0

PAUSE-IR

0

1 0 EXIT2-IR

1

UPDATE-IR

1

0

NOTE: The value shown adjacent to each state transition in this figure represents the signal present at TMS at the time of a rising edge at TCK.

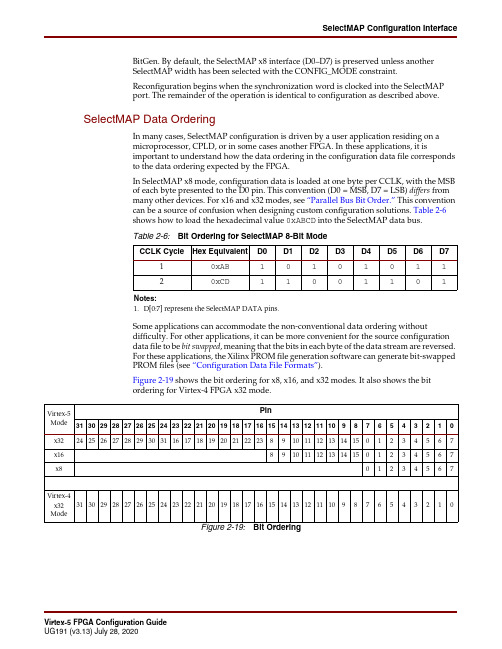

Table 2-6: Bit Ordering for SelectMAP 8-Bit Mode

CCLK Cycle Hex Equivalent D0 D1 D2 D3 D4 D5 D6 D7

1

0xAB

1

0

1

0

1

0

1

1

2

0xCD

1

1

0

0

1

1

0

1

Notes: 1. D[0:7] represent the SelectMAP DATA pins.

For details on the standard Boundary-Scan instructions EXTEST, INTEST, and BYPASS, refer to the IEEE Standard.

Virtex-5 FPGA Configuration Guide UG191 (v3.13) July 28, 2020

UG191_c3_02_050406

Figure 3-2: Boundary-Scan TAP Controller

Virtex-5 devices support the mandatory IEEE 1149.1 commands, as well as several Xilinx vendor-specific commands. The EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, USERCODE, and HIGHZ instructions are all included. The TAP also supports internal user-defined registers (USER1, USER2, USER3, and USER4) and configuration/readback of the device.

FPGA可编程逻辑器件芯片XC2S200E-6FT256AFS中文规格书

DCM dynamic reconfiguration 105

DRP defined 105

E

encryption 33 loading 34 using iMPACT 34

F

fallback 28, 30, 31, 34, 67, 153 BPI 154

frame address

configuration 130 register 118 FRAME_ECC_VIRTEX5 101

Chapter 9: Readback CRC

Virtex-5 FPGA Configuration Guide UG191 (v3.13) July 28, 2020

Index

A

AES defined 33

B

BitGen 18, 34, 60 settings 40, 41, 43, 49, 50, 51, 52, 53, 60, 117, 123, 135, 153, 162 readback 135

C

CAPTURE_VIRTEX5 100, 135, 151 CCLK 73 configuration 15

AES 33 basic steps 23 BitGen 34, 40, 41, 43, 49, 50, 51, 52,

53 bitstream encryption 33 Boundary-Scan 89 clearing memory 25 CRC 30 cyclic redundancy check 30 delaying 26 file formats 18 ICAP 35 IDCODE 28 initialization 25 in-system 77 interfaces 37 load data frames 30 loading bitstreams 27, 34

FPGA可编程逻辑器件芯片XC2S200-5FGG456I中文规格书