PWR_AMP_final

笔记本电脑主板新图纸(全)

29 38 PMH-7G/A Serial ATA I/F USB 2.0 Port1 Mocha-1 Block Diagram 34 Media Slice VCC1R8B S-BAT-PWR CRT UltraSlimBay RJ45 USB2514 USB Hub SMSC MAX6694 Thermal Sensor SMBus SATA Port 1 I/F 20,21,22,23 34 CRT Port Media Slice 195 40 Processor 15 Serial ATA 150MB/s PCI Express CRT I/F G-Sensor 42 CH10 Bluetooth 31 CH8 DDR3 1067/800 Channel A UNBUFFERED DDR3 SODIMM Reverse Socket 204-PIN DDR3 SODIMM 13 14 Channel B DDR3 1067/800 VCC1R05AMT/VCC1R5A VCC5V_OUT VCC3M VCC1R05AMT VCC1R5A VCC1R8B BD3550 VT351A 50 52,53 I2C Bus / SM Bus Thermal Sensor LM26 5

Trace should be less than 0.5 inch 2 2 2 2 2 TPAD302 22 2 22 2 2

E 2 2 22 MAX6694TE9A-2-GP 2 E 22 SC2200P50V2KX-2GP E 22 2 2 2 22 2 2 22

18 Display Port 3029 Azalia bus IOSUB Card Conn. 32 USB 2.0CH5 Media Card Reader 3-in-1 Slot USB 3 USB2.0 CH6VCC1R5A VCC0R75AMT BD3550 MAX1510 Display Port RJ 11Conn Audio Codec IOSUB Card (LCD Conn)HP OUT MIC IN 16

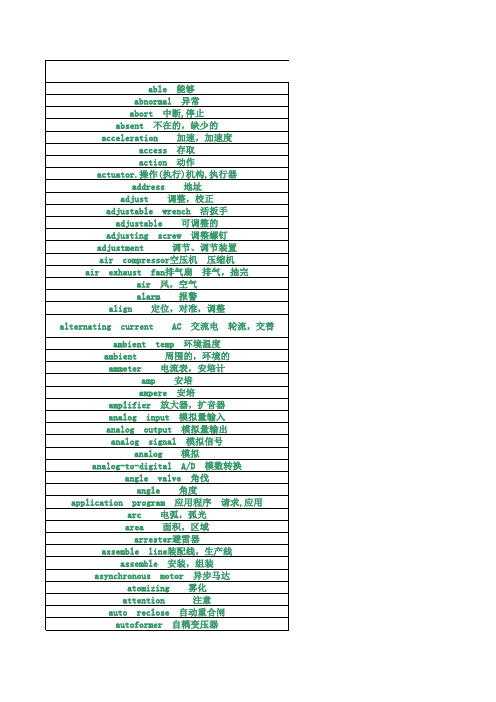

ATE 中英文对照

附录2:ATE TEST ITEM 的中文解释WDCT系列一、H/S Motherboard ATE测试项目3 UUT Type Check 测试H/S MCU版本4 Idle Current 测试H/S在关机状态下的静态电流5 TX Current 测试H/S TX 部分电路工作时的电流6 RX Current 测试H/S RX 部分电路工作时的电流7 Total Current Draw 测试H/S 各部分电路工作时的总电流11 Software Build 测试H/S OTP 软件(产品软件)版本27 Backup Registration 备份H/S ID 记录35 Read Freq Tuning Data 检查H/S频率参数41 HS Mic Bias (V) 测试MIC两端电压43 HS Mic Audio (dB) 测试MIC 音频信号47 HS Mod Audio Setup 令HS 进入TX(发射)状态50 WDCT Acoustic Approx 调整MIC并写入MIC参数,(-46,3,5)表示MIC的可调范围是-46+/-3DB,最大可设置为+/-5DB51 HS Mod Aud (1kHz) 测试在MIC处给定1kHz信号时调制输出音频信号大小52 HS Mod Distortion 测试调制输出音频信号失真度======53 HS Mod SINAD 测试调制输出音频信号信噪比54 Mute TXAudio 测试MUTE时有无发送信号57 HS Mod Aud (300Hz) 测试在MIC处给定300Hz信号时调制输出音频信号大小61 HS Dmod Audio Setup 令HS 进入RX(接收)状态66 HS Dmod Audio 测试在RECEIVER处给定1kHz信号时解调输出音频信号大小67 HS Dmod Distortion 测试解调输出音频信号失真度68 HS Dmod SINAD 测试解调输出音频信号信噪比二、B/S Motherboard ATE 测试项目2 UUT Type Check 测试B/S MCU版本3 Idle Current 测试B/S在关机状态下的静态电流4 TX Current 测试B/S TX 部分电路工作时的电流5 RX Current 测试B/S RX 部分电路工作时的电流6 Total Current Draw 测试B/S 各部分电路工作时的总电流7 Software Build 测试B/S OTP 软件(产品软件)版本12 RF Power (V) 测试 RF部分供电电压13 MCU Power (V) 测试 MCU供电电压17 Regulator Power (V) 火牛供电电压50 Line to SPK Audio 开B/S SPK51 Line to SPK(1KHZ) 测试电话线输入1KHZ信号时B/S SPK输出信号大小52 Line to SPK Distort 测试电话线输入1KHZ信号时B/S SPK输出信号失真度53 Line to SPK SINAD 测试电话线输入1KHZ信号时B/S SPK输出信号信噪比57 Line to SPK (300HZ) 测试电话线输入300HZ信号时B/S SPK输出信号大小62 Off-Hook Loop Current 测试SPK开通时的环路电流65 SPK MIC to line Aud 令B/S处于MIC开通状态66 MIC to line (1KHZ) 测试在MIC处给定1kHz信号时电话线输出音频信号大小66 MIC to line Distort 测试在MIC处给定1kHz信号时电话线输出音频信号失真度66 MIC to line SINAD 测试在MIC处给定1kHz信号时电话线输出音频信号信噪比66 MUTE MIC to line AUDIO 测试在MUTE MIC时电话线有无输出音频信号80 Caller ID - Type II 测试开机CID83DTMF 1 测试音频拨号”1”101Line Drop 掉线测试102No Line 无电话线条检测110 Caller ID - Type I 试关机CID114Parallel Set 并线测试120 Cradle Detect 测试充电检测信号121 Cradle Charge (mA) 测试充电电流122 Spare Battery Charge 测试备用电池充电电流``150 PotsMode 测试 PotsMode是否正常151 PotsMode-RF Pwr(V) 测试 PotsMode 时RF 供电电压152 PotsMode-CDT Pwr(V) 测试备用电池充电电压三、Final RF ATE 测试项目Ch0, Hi Pwr 测试H/S 0频道HI POWER41 42 Ch47, Lo Pwr 测试H/S 0频道LOW POWER43 Ch47, Hi Pwr 测试H/S 47频道HI POWER44 Ch94, Hi Pwr 测试H/S 94频道HI POWER51Ch2 Deviation Tuning 调整2频道频偏52 Ch2 Tx Freq Offset 2频道频率衰减53 Ch2 Drift+Noise(DC-D 2频道频率漂移及杂波55Ch90 Deviation Tuning 调整90频道频偏56 Ch90 Tx Freq Offset 90频道频率衰减57 Ch90 Drift+Noise(DC- 90频道频率漂移及杂波59 Approx Tx Amp Vals 检查频偏调整结果是否可要求N.S系列一、B/S Audio ATE 测试项目Test item Lower Upper Unit1. 5V supply (检查5V/TP17的电压) 4.75 5.25 V2. 3V supply (检查3V/TP6的电压) 2.853.15 V3. Software version (检查软件版本)4. Base parameters (下载 eeprom参数)5. Freq (检查振荡器的振荡频率) 10367790 10368210 HZ6. Ring on det (振铃检测)7. Ring off det (停止振铃检测)8. Off DC (关机时电话线两端电压) 29 30.2 V9. On DC (开机时电话线两端电压) 4.25 7.25 V10. Line Rms (电话线信号电压/拨号&吹咪) 27000 33000 Dec11. Tp14 AC volt (TP14 的交流电压) 400 700 mV12. Pulse volt (脉冲拨号电压) -5.5 -3.6 V13. Line sense voltage (电话线感觉到的电压) 60 90 Dec14. Clip Rms (修剪线路检测/R声&CID) 27000 33000 Dec15. Charge Adc (充电和登记检测) 65 125 Dec16. Tp19 high (TP19高电压) 1.2 1.6 V17. Tp19 low (TP19低电压) 0 0.1 V18. Tp20 (TP20的电压) 1.4 1.8 V19. Tp21 high (TP21高电压) 1.2 1.6 V20. Tp21 low (TP19低电压) 0 0.1 V21. Tp22 to 5V (在TP22和5V之间连一个220欧的电阻) 20 20 Hex22. Tp22 to GND(在TP22和5V之间连一个220欧的电阻0 0 Hex二、B/S RF ATE 测试项目test item Lower Upper Unit1. Quad tune voltage (正交解调电压) 1.4 1.6 V2. Quad tune value (正交解调值) 20 200 Dec3. Tester lock (测试设备的锁定)4. Connect 94 BS (连接 BS)5. Chan 94 NTP (94频道的发射功率) 20 27 dBm6. Chan 94 deviation (94 频道的频偏) 210000 240000 HZ7. Chan 94 offset (94频道的频率漂移量) -80000 80000 HZ8. Chan 94 drift (94频道的频率漂移) -20000 20000 HZ/ms9. Tester lock (测试设备的锁定)10.connect 0 BS (连接BS)11.Chan 0 NTP (0频道的发射功率) 20 27 dBm12.Chan 0 deviation (0 频道的频偏) 210000 240000 HZ13.Chan 0 offset (0频道的频率漂移量) -80000 80000 HZ14.Chan 0 (0频道的频率漂移) -20000 20000 HZ/ms15.Tester lock (测试设备的锁定)16.Connect BS (连接BS)17.BER@ hope mode (误码率) 0 0.001 %三、H/S Audio ATE测试项目test item Lower Upper Unit1. Current2.5V( off ) (关机状态的电流) 5000 UA2. Supply volt (TP101的供电电压) 2.4 2.8 V3. Software version (检查软件版本)4. Sleep current (静态电流) 1 8 mA5. Eeprom size (检查EEPROM的容量) 1.66. Default program (送默认的内容到EEPROM)7. Handset parameter (HS EPROM的参数)8. 2.5V Adjust (调节BMC电压=2.5V ) 2.48 2.52 V9. Adjust value (当调节BMC电压=2.5V时要设置的数值) 0 15 Dec10.Check D101(检查D101/TP100&TP101的电压) 2.45 2.55 V11.Cradle detect (充电检测)12.Registration (检查登记电压/在TP100) 2.5 3 V13.Batt ADC (测试电池电压) 50 90 Dec14.Max Freq (调节振荡器的最高频率) 10366000 10367400 HZ15.Min Freq (调节振荡器的最低频率) 10368600 10370000 HZ16.Audio Path 1(音频1->for HS/TP104&105 的电压) 0.45 1.1 V17.Audio Path 2(音频2->for HJ/TP107&GND的电压) 0.18 0.35 V四、H/S RF ATE测试项目HS RF test item (for DG ATE)test item Lower Upper Unit1. Quadtune voltage (正交解调电压) 1.2 1.8 V2. Quadtune value (正交解调值) 20 230 Dec3. Connect HS (连接 HS)4. Chan 0 NTP (0频道的发射功率) 20 27 dBm5. Chan 0 clock freq (0频道的时钟频率) 20 235 Dec6. Chan 0 deviation (0 频道的频偏) 210000 240000 HZ7. Chan 0 offset (0 频道频率漂移量) -80000 80000 HZ8. Chan 0 drift (0 频道频率漂移) -20000 20000 HZ/ms9. Connect HS (连接 HS)10.Chan94 NTP (94频道的发射功率) 20 27 dBm11.Chan94 deviation (94 频道的频偏) 210000 240000 HZ12.Chan94 offset (94频道频率漂移量) -80000 80000 HZ13.Chan94 drift (0 频道频率漂移) -20000 20000 HZ/ms14.Connect HS (连接 HS)20 27 dBm 15.Chan94 ant1 NTP (94频道天线1的发射功率)16.Connect HS (连接 HS)17.BER@ hope model (误码率) 0 0.01 % DECT系列一、HS RF ATE测试项目TEST Item 测试项目1. Check Current 检查电流1.1 H/S Version H/S 版本2. Battery A to D 电池信号的仿真量转换或数字量2.1 Batt A/D Batt的A/D转换3. RF Test RF板的测试3.0 Connect to UUT 连接测试信道3.1 Current RF RF板的电流3.2 Freq Acc 频率的精确度3.3 RF Dev(+Ve) Max RF最大的频偏 (+Ve)3.4 RF Dev(-Ve) Max RF最大的频偏 (-Ve)3.5 RF Dev(+Ve) Min RF最小的频偏 (+Ve)3.6 RF Dev(-Ve) Min RF最小的频偏 (-Ve)3.7 Freq Drift 频率漂移3.8 Jitter Meas 信号稳定性测量3.9 NTP 天线发射功率3.10 Power VS Time P/T功率与时间的关系3.11 Ref Ber at –73dBm 在-73dBm二进制编码误差率的基准点3.12 Rec Sens at –91dBm 在-91dBm的接收灵敏度4. RSSI Measure 接收信号强度测量4.1 RSSI at -73dBm 在-73dBm的接收信号强度4.2 RSSI at –90dBm 在-90dBm的接收信号强度二、 HS FINAL ATE 测试项目Item Test 测试项目1. Check Current 检查电流1.1 H/S Version 检查版本2. Battery A to D 电池信号的仿真转换或数字量2.1 BATT A/D BATT A/D (AD转换)3. RF Test RF测试3.1 Connect ACC 连接信号的灵敏度3.2 Freq ACC 频率的灵敏度3.3 RF Dev(+Ve) at CH5 RF在CH 5(第5频道) 的频偏(+Ve) 3.4 RF Dev(+Ve) at CH5 RF在CH 5(第5频道) 的频偏(-Ve) 3.5 Freq Drift 频率漂移3.6 Jitter meas 信号稳定性的测量3.7 NTP 天线发射功率3.8 Power VS Time 功率与时间的联系3.9 Ref Ber at –73dBm 在-73dBm二进制编码误差率的基准点3.10 Rec Sens at –91dBm 在-91dBm的接收灵敏度4. RSSI Measure 接收信号强度的测量4.1 RSSI at –73dBm 在-73dBm的接收信号强度4.2 RSSI at –91dBm 在-91dBm的接收信号强度三、BS Audio ATE测试项目Test Item 测试项目1. ATE Initialisation ATE初始化2. PCB Initialisation PCB初始化3. Current Check 电流检查3.1 Current RF OFF RF关断电流3.2 Current RF ON RF开通电流4. SW Version 软件版本4.1 Version 版本5. Reference Clock 参考时钟5.1 REF CLR 参考时钟6. +3.6V +3.6V7. +2.65V +2.65V7.1 +2.65 VDC +2.65 VDC8. Battery Charger 电池充电8.1 BAT CHRG 电池充电9. ON Hook 挂机10. Off Hook 摘机10.1 OFF Hook Norm 正常摘机10.2 OFF Hook Rev 反向电流摘机11. Ring Dector 振铃检测11.1 25Hz RingDET 25Hz下的铃声检测12. Receve Audio 接收音频12.1 REC 3K LEV 接收3KHz的音频信号电平12.2 REC 1K LEV 接收1KHz的音频信号的电平 12.3 REC 1K DIST 接收1KHz的音频信号的失真12.4 REC 0.3K LEV 接收0.3KHz的音频信号的电平13. Meter pule Filter 测量脉冲滤波13.1 MET Pulse 测量脉冲14. DTMF 双音频拔号14.1 DTMF LO 低频双音频拔号14.2 DTMF HI 高频双音频拔号。

ET200S接线

DATE:

A 2 OF 3

SAVE DATE: 2007-11-22

REVAFSFHEECETTED

CHANGE DESCRIPTION

DATE

CHANGE CHANGED CODE BY

REVAFSFHEECETTED

CHANGE DESCRIPTION

DATE CHANGECHANGED CODE BY

STATUS:

PACKAGE SGMW青岛整车产能扩建项目总装车间 QD PROJECT GA SHOP

SYSTEM/TOOL NO:

DESCRIPTION:质检站-底盘A线、最终A线-1 QC STATION-CHASISS-A&FINAL-A-1

QD08GA-TCFA03-QC01

SHEET

连锁图

2 目录 TABLE OF CONTENTS

3 更改纪录 MASTER CHANGE SHEET

C INTERCONNECT

1 连锁图 INTERCONNECT

E MAGNETICS

1 电气原理图 MAGNETICS

F I/O

1 输入输出 I/O

2 输入输出 I/O

3 输入输出 I/O

X ENCLOSURES

STATUS:

PACKAGE SGMW青岛整车产能扩建项目总装车间 QD PROJECT GA SHOP

SYSTEM/TOOL NO:

DESCRIPTION:质检站-底盘A线、最终A线-1 QC STATION-CHASISS-A&FINAL-A-1

QD08GA-TCFA03-QC01

SHEET

更改纪录

170

0VDC

CTL9

YP-350-A资料

AC input range selected by switch With +5VSB:0 ~ 2.0A max.Power good signal output Power fail signal output Power ON-OFF switch High efficiencyForced air cooling by built-in DC fan 100% full load burn-in testApprovals: TUV / CSA / CB / FCC / CE 1 year warrantySPECIFICATIONYP-350A-AA ORDER NO.DC VOLTAGE CHANNEL SAFETY MODEL NO.MINIMUM CURRENT MAXIMUM CURRENTCOMBINE LOAD RATED POWER (max.)RIPPLE & NOISE (max.)Note.2OUTPUTLINE REGULATION LOAD REGULATION Note.3HOLD UP TIME VOLTAGE RANGE FREQUENCY RANGEEFFICIENCY (Typ.)INPUTENVIRONMENT INRUSH CURRENT (max.)LEAKAGE CURRENT(max.)POWER GOOD SIGNAL POWER FAIL SIGNAL PS-ON INPUT SIGNALSAFETY STANDARDS SAFETY &EMC(Note 4)WORKING TEMP.WORKING HUMIDITYSTORAGE TEMP., HUMIDITYTEMP. COEFFICIENT VIBRATIONOTHERSNOTEPROTECTION AC CURRENT3.3V CH1YP-350-A 5V CH212V 1CH312V 2-5V CH4CH5-12V CH65VSB STANDBY 2A 17A2A 18A1A 8A1A 0.1A 14A0.3A0.1A 0.8A0A 2.0A250W+5V, +3.3V, +12V 230W max.+5V, +3.3V 115W max.50mVp-p50mVp-p 120mVp-p 120mVp-p 50mVp-p 120mVp-p 50mVp-p 1.0% 1.0% 1.0% 1.0% 2.0% 2.0% 1.0%5.0%5.0%5.0%5.0%10%10%5.0%8ms min. at full load103 ~ 132VAC / 206 ~ 264VAC selected by switch 47 ~ 63Hz 70%3.5mA / 240VACCSA(C22.2 60950, UL60950),TUV EN60950 approved Compliance to EN55022 (CISPR22) class B, FCC part 15 class B HARMONIC CURRENT Compliance to EN61000-3-2,-3EMS IMMUNITY Compliance to EN61000-4-2,3,4, 5,6,8,11, light industry level, criteria A MTBF100K hrs min. MIL-HDBK-217F (25)COOLING Forced air ventilation by 8cm DC fan WITHSTAND VOLTAGEI/P-O/P, I/P-FG:1.5KVACISOLATION RESISTANCEI/P-O/P,:50M Ohms / 500VDC I/P-FG / 25/ 70% RH-10 ~ +3520 ~ 90% RH non-condensing The TTL compatible signal out with 100ms to 500ms delay after power set up The TTL compatible signal will go down at least 1ms before +5V below 4.75V Power on: PS-ON = "Low" or "<0.8V" ; Power off: PS-ON = "Hi" or ">2V"-20 ~ +85, 10 ~ 95% RH 0.05% /(0 ~ 50)10 ~ 200Hz, 2G 10min./1cycle, 60min. each along X,Y, Z axes CONNECTORATX main power connector * 1ea; +12V power connector * 1ea; Serial ATA connector * 1ea Peripheral power connector * 5 ea; Floppy drive power connector * 2 ea DIMENSION 150*140*86mm (L*W*H)PACKING1.1kg ; 12pcs / 16kg / CARTON1. All parameters NOT specially mentioned are measured at 230VAC input, rated load and 25of ambient temperature.2. Ripple & noise are measured at 20MHz of bandwidth by using a 12" twisted pair-wire terminated with a 0.1uf & 47uf parallel capacitor.3. Load regulation is measured from 20% to 100% max.Load.4. The power supply is considered a component which will be installed into a final equipment. The final equipment must be re-confirmed that it still meets EMC directives.File Name:YP-350A-AA-SPEC 2007-05-14FUNCTIONFeatures :OVERLOADSHORT CIRCUITOVER VOLTAGE105 ~ 150%rated output powerProtection type : Shut down o/p voltage, re-power on to recover +3.3V, +5V, +12V +12V : 110%~130% of rated voltage 1,2Protection type : Shut down o/p voltage, re-power on to recover All output equipped with short circuitProtection type : Shut down o/p voltage,re-power on to recover EMI CONDUCTION & RADIATION 6.0A / 115VAC 3.0A / 230VAC 40A / 115VAC 80A / 230VAC SUDR250W ATX 12V PC Power SupplyYP-350A-AARATED CURRENT 12A 12A 5A 9A 0.3A 0.8A 2.0AMechanical SpecificationFile Name:YP-350A-AA-SPEC 2007-05-14Unit: mm54321W I R E O U T P U T O F C A S E(A)24 Pin ATX main power connector(or 20+4pin)Type: MOLEX 39-01-2240 or equivalent (C)Serial ATA connectorType: MOLEX 88751 or equivalent (E)Floppy drive connectorType:AMP 171822-4 or equivalent(B)+12V power connector Type: MOLEX 39-01-2040 or equivalent (D)Peripheral connectorType: MOLEX 8981-04P or equivalent+12V 1+12V 1+5V S B P W R -O K G N D +5V D C G N D +5V D C G N D +3.3V D C +3.3V D C+3.3V D C+5V D C +5V D C+5V D C -5V D C G N D C O MG N D G N D P S -O N G N D -12V D C +3.3V D C(A )P I N 13P I N 1L =150m mL =300m m 20m m432112344321+5V D C C O M C O M +12V 1+5V D C C O M C O M +12V 1( D )( D )( E )2143+5V D C C O M C O M +12V 1C O M+12V 2C O M +12V 2L =300m m 20m m( B )( C )L =600m m 20m m+12V C O M +5V D C C O M +3.3V D C1L =300m m 20m mL =150m mL =300m m 20m m43214321+5V D C C O M C O M +12V 1+5V D C C O M C O M +12V 1( D )( D )( E )L =150m m1234+5V D C C O M C O M +12V 1L =150m mL =150m m4321+5V D C C O M C O M +12V 1( D )W I R E O U T P U T H O L E2306#-32UND(4X)6.0MM MAX DEEPAC INPUTCONNECTOR118.552.413811425.943.5562.0574166443.45250W ATX 12V PC Power SupplyYP-350A-AA。

ATE软件包使用说明

ATE 软件包使用说明V1.0聚锋公司提供的ATE软件包是集校准(Calibration)、板测(BoardTest)和终测(FinalTest)于一体的自动测试软件(有关校准和测试的规范详见“生产测试规范”文档)。

1.建立测试站图1是一个典型的测试站连接图,其中需要用到的硬件:测试柜(推荐)一个计算机(装有Windows 2000中文版操作系统) 一套综测仪(Agilent 8960或CMU200)一台电源(Agilent 663xx,模拟主电池)一台电源(模拟充电器)一台NI-PCI GPIB卡一块GPIB Cable通信电缆一根射频电缆一根Dongle一个夹具(含射频头,SIM卡)一个屏蔽盒一个。

图1 测试连接框图需要注意的是,电源的V+/V-,S+/S-分两路输出,在尽可能接近负载(手机)的地方将V+和S+,V-和S-连在一起,以减少电压损耗。

另一点,射频电缆应尽可能的短,转接次数越少越好。

2.安装AutoTest 软件包请先阅读安装目录下的Readme.txt 。

运行安装程序setup.exe ,根据提示将ATE 软件包放在一个特定的文件夹,如D:\ATE 。

3.界面介绍运行ATE.exe ,该软件启动后的界面如下:图2⑴ 菜单 运行(R)菜单有四个选项,开始(F1),停止(F2),暂停(F3)和退出。

设置(S)菜单有三个选项,选择测试文件(F4),参数设置(F5)和校准模式(F6)。

帮助(H)菜单显示版本信息。

⑵ 程序的信息(5) (6)显示该程序是板测(BoardTest)还是终测(FinalTest)。

⑶并显示工位号工位号由配置文件Configure.dat文件来设置的。

⑷显示测试内容及测试值在此对话框中,显示测试内容,上下限及测试值,并判断测试结果。

若测试值超出了给定的上下限,则测试结果为FAILED,并显示为红色。

如图4所示。

⑸显示测试信息显示测试过程中的测试信息,如Connecting to phone...,AFC phasing等。

Silego SLG5NT1487V 7.8mΩ 5A 单通道负载开关说明书

Ultra-small 7.8 m Ω5 A Load Switch with DischargeSLG5NT1487VBlock DiagramGeneral DescriptionThe SLG5NT1487V is a 7.8 m Ω 5 A single-channel load switch that is able to switch 1 to 5 V power rails. The product is pack-aged in an ultra-small 1.5 x 2.0 mm package.Features• 1.5 x 2.0 mm FC-TDFN 8L package (2 fused pins for drain and 2 fused pins for source)•Logic level ON pin capable of supporting 0.85 V CMOS Logic•User selectable ramp rate with external capacitor •7.8 m Ω RDS ON while supporting 5 A •Discharges load when off•Two Over Current Protection Modes •Short Circuit Current Limit •Active Current Limit•Over Temperature Protection•Pb-Free / Halogen-Free / RoHS compliant •Operating Temperature: -20 °C to 70°C •Operating Voltage: 2.5 V to 5.5 VPin ConfigurationApplications•Notebook Power Rail Switching •Tablet Power Rail Switching•Smartphone Power Rail Switching8-pin FC-TDFN (Top View)VDD1CAP GND D ON 2378SLG5NT1487VD4SS 56DSLinear Ramp ControlCMOS InputONCharge Pump+2.5 to 5.5 VCAP*******ΩOver Current and Over TemperatureProtectionPin DescriptionOrdering InformationPin #Pin Name Type Pin Description1VDD PWR VDD power for load switch control (2.5 V to 5.5 V)2ON Input Turns MOSFET ON (4 M Ω pull down resistor)CMOS input with VIL < 0.3 V, VIH > 0.85 V 3D MOSFET Drain of Power MOSFET (fused with pin 4)4D MOSFET Drain of Power MOSFET (fused with pin 3)5S MOSFET Source of Power MOSFET (fused with pin 6)6S MOSFET Source of Power MOSFET (fused with pin 5)7CAP Input Capacitor for controlling power rail ramp rate 8GNDGNDGroundPart Number Type Production Flow SLG5NT1487V FC-TDFN 8LCommercial, -20 °C to 70 °C SLG5NT1487VTRFC-TDFN 8L (Tape and Reel)Commercial, -20 °C to 70 °CAbsolute Maximum RatingsElectrical CharacteristicsParameterDescription ConditionsMin.Typ.Max.Unit V DD Power Supply ----7V T S Storage Temperature -65--150°C ESD HBM ESD ProtectionHuman Body Model 2000----V W DISPackage Power Dissipation----1W MOSFET IDS PK Peak Current from Drain to Source For no more than 1 ms with 1% duty cycle----7ANote: Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress ratingonly and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.T A = -20 to 70 °C (unless otherwise stated)ParameterDescriptionConditions Min.Typ.Max.Unit V DD Power Supply Voltage -20 to 70°C 2.5-- 5.5V I DD Power Supply Current (PIN 1)when OFF ----1μA when ON, No load --70100μA RDS ON Static Drain to Source ON Resistance T A 25°C @ 100 mA --7.88.5m ΩT A 70°C @ 100 mA --8.59.6m ΩIDS Operating Current V D = 1.0 V to 5.5 V----5A V D Drain Voltage 1.0--V DD V T ON_Delay ON pin Delay Time50% ON to Ramp Begin300500μs T Total_ONTotal Turn On Time50% ON to 90% V SConfigurable 1ms Example: CAP (PIN 7) = 4 nF, V DD = V D = 5 V, Source_Cap = 10 μF, IDS = 100 mA -- 1.96--ms T SLEWRATESlew Rate10% V S to 90% V SConfigurable 1V/ms Example: CAP (PIN 7) = 4 nF, V DD = V D = 5 V, Source_Cap = 10 μF, IDS = 100 mA -- 3.0--V/ms CAP SOURCE Source CapSource to GND----500μF R DIS Discharge Resistance 100150300ΩON_V IH High Input Voltage on ON pin 0.85--V DD V ON_V IL Low Input Voltage on ON pin -0.300.3V I LIMITActive Current LimitMOSFET will automatically limit cur-rent when V S > 250 mV--7.0--A Short Circuit Current LimitMOSFET will automatically limit cur-rent when V S < 250 mV--0.5--A THERM ONThermal shutoff turn-on temperature --125--°C THERM OFF Thermal shutoff turn-off temperature --100--°C THERM TIME Thermal shutoff time ----1ms T OFF_DelayOFF Delay Time50% ON to V S Fall, V DD = V D = 5 V----15μsNotes:1.Refer to table for configuration details.SLG5NT1487V Turn ONThe normal power on sequence is first VDD, with VD only being applied after VDD is > 1 V, and then ON after VD is at least 90% of final value. The normal power off sequence is the power on sequence in reverse.If VDD and VD are turned on at the same time then it is possible that a voltage glitch will appear on VS before VDD achieves 1V which is the VT of the main MOSFET. The size of the glitch is dependent on source and drain capacitance loading and the ramp rate of VDD & VD.SLG5NT1487V Turn ONThe VS ramp follows a linear path, not an RC limitation provided the ramp is slow enough to not be current limited by load capacitance.SLG5NT1487V Current LimitingThe SLG5NT1487V has two forms of current limiting.6 A Standard Current Limiting ModeCurrent is measured by mirroring the current through the main MOSFET. The mirrored current is then sent through a resistor creating a voltage V(i) proportional to the MOSFET current. The V(i) is then compared with a Band Gap voltage V(BG). If V(i) exceeds the Band Gap voltage then the voltage V(g) on the gate of the main MOSFET is reduced. The V(g) continues to drop until V(i) < V(BG). This response is a closed loop response and is therefore very fast and current limits in less than a few micro-seconds. There is no difference between peak or constant current limit.Temperature CutoffHowever, as the V(g) drops the Rds(ON) of the main MOSFET will increase, thus limiting the current, but also increasing the power dissipation of the IC. The IC is very small and cannot dissipate much power. Therefore, if a current limit condition is sustained the IC will heat up. If the temperature exceeds approximately 120°C, then V(g) will be brought low completely shutting off the main MOSFET. As the die cools the MOSFET will be turned back on at 100°C.If the current limiting condition has not been mitigated then the die will again heat up to 120°C and the process will repeat. Short Circuit Current Limiting ModeWhen V(S) < 250 mV, which is the case if there is a solder bridge during the manufacturing process or a hard short on the power rail, then the current is limited to approximately 500 mA. This current limit is accomplished in the same manner as the Standard Current Limiting Mode with the exception that the current mirror is 15x greater. Because the current mirror is so much larger, a 15x smaller main MOSFET current is required to generate the same V(i). If V(S) rises above approximately 250 mV, then this mode is automatically switched out.T Total_ON vs. CAP @ V DD = 3.3 VT Total_ON vs. CAP @ V DD = 5.0 VSLG5NT1487V T Total_ON : ON (50%) - V S (90%)V DD = 3.3 V, T A = 25 °C. C L = 10 μF, IDS = 100 mASLG5NT1487V T Total_ON : ON (50%) - V S (90%)V DD = 5.0 V, T A = 25 °C. C L = 10 μF, IDS = 100 mA23456T t o t a l _o n (m s )VD = 1.5VVD = 2.5V VD = 3.3V01200040006000800010000120001400016000Cap (pf)23456T t o t a l _o n (m s )VD = 1.50VVD = 2.50V VD = 3.30V VD = 5.00V01200040006000800010000120001400016000Cap (pf)T SLEW vs. CAP @ V DD = 3.3 VT SLEW vs. CAP @ V DD = 5.0 VSLG5NT1487V T Total_ON : ON (50%) - V S (90%)V DD = 3.3 V, T A = 25 °C. C L = 10 μF, IDS = 100 mASLG5NT1487V T Total_ON : ON (50%) - V S (90%)V DD = 5.0 V, T A = 25 °C. C L = 10 μF, IDS = 100 mA56789101112131415V /m sVD = 1.50V VD = 2.50V VD = 3.30V1234010002000300040005000600070008000900010000110001200013000140001500016000Cap (pf)56789101112131415V /m sVD = 1.50VVD = 2.50V VD = 3.30V VD = 5.00V1234010002000300040005000600070008000900010000110001200013000140001500016000Cap (pf)T Total_ON , T ON_Delay and Slew Rate Measurement90% V S50% ON T ON_DELAYSlew Rate (V/ms)ONV ST Total_ON10% V S50% ON10% V S T OFF_DELAYT FALL90% V SPackage Top Marking System DefinitionXXA DDR LLDate Code + RevisionPart Code + Assembly SiteLot TraceabilityPin 1 IdentifierTape and Reel SpecificationsCarrier Tape Drawing and DimensionsRecommended Reflow Soldering ProfilePlease see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 2.25 mm 3 (nominal). Moreinformation can be found at .Package Type # ofPins Nominal Package Size [mm]Max Units Reel &Hub Size [mm]Leader (min)Trailer (min)Tape Width [mm]Part Pitch [mm]per Reel per Box Pockets Length [mm]Pockets Length [mm]TDFN 8LFC Green81.5 x2.0 x 0.7530003000178 / 6010040010040084Package TypePocket B TM Length Pocket B TMWidth Pocket Depth Index Hole PitchPocket Pitch Index Hole DiameterIndex Hole to Tape Edge Index Holeto Pocket CenterTape Width A0B0K0P0P1D0E F W TDFN 8L FC Green1.682.180.9441.51.753.58。

常用机电英语词汇(上下)

cooling water pump 冷却水泵 cooling 冷却 copy 拷贝 core 铁心、核心、磁心 correct 正确的,改正 correction 修正、改正 corrosion 腐蚀 cost of fuel 燃料费用 counting 计数器 couple CPL 联轴器 crane 起重机 curdle 凝固 currency 流动、流通 current n. 电流,水流、当前、气流 current transformer CT 电流互感器 cursor 光标 curve 曲线 cutter 切削工具 ccycle 循环、周期、周波 cylinder CYL 汽缸,圆柱体 cymometer 频率表,频率计 damage 损坏、破坏 danger zone 危险区 danger 危险、危险物 dangerous 危险的 dank 潮湿 data base 数据库 data pool 数据库 data 数据 deactivate 使无效 dead band 死区 debugging .调试 deceleration n. 减速,减速度 decrease DEC 减少 deep 深度、深的、深 default 默认(值),缺省(值) degree 度、等级 delay time 延时 delay 延迟 delete 删除 defective 有缺陷的 description 说明、描述 detect 发现、检定 detector 检测器,探测器 deviate 偏离、偏差

clockwise 顺时针、右旋的 clogged 障碍,塞满,粘注 close 关闭 closed-loop 闭环 coarse 粗的、不精确的 code 代号、密码 coder 编码器 coil 线圈 cold 冷 collect 收集 colour 颜色 command 命令、指挥 communication 通信、通讯 compensation 补偿,矫正 component 元件 compress air 压缩空气 compress 压缩 compressor 压缩机 computer 计算机 condensate 冷凝、使凝结 condition 条件、状况、环境 conduct 传导 conductivity 导电率 conductor 导体,导线 configure 组态 congealer 冷却器、冷冻器 connect 连接 connection 联接 connector 联接器、接线盒 console 控制台 constant 恒定的 contact 接触,触点,vt.接触,联系 contact to earth 接地、触地、碰地 contact 触点 contactor (电流)接触器、触头 continuous 连续的 control CNTR/CNTPL 控制 control panel 控制盘 control valve 调节阀 controller 控制器 convert 转换 vt.使转变,转换…. conveyor 传送带,输送机 cooktop 炉灶 cool 冷的 cooler 冷却器 cooling fan 冷却风机 cooling tower 冷却塔

高速智能载体电压负荷细胞接口卡说明书

High Speed, Intelligent Load Cell Interface Card with USB and RS232/485 InterfacesThe LCIC-WIM is a high speed, intelligent load cell interface card with USB/RS-232/RS-485 interfaces. Besides its basic mode, the board includes an integral Fill Mode supplyingan independent filling control. The board is intelligent and powerful enough for OEM customers—it is ready to accept piggy-back modules and/or embedded applications for OEM special requirements. The LCIC-WIM-BEN is useful in applications such as analyzing noise and vibration in a belt conveyor or any dynamic weighing system, for example the time it takes for stabilization after a load was applied. Other potential applications include checking scale behavior for slow/high speed WIM (weighing in motion) applications, measuring maximum (peak) and minimum forces on a scale/testing machine (helps to select the suitable load cell for optimum performance), and running tests and getting immediate final weight results on WIM and check weighers.LCIC-WIM Software Three software utilities are supplied with the board: LCIC-WIM-CALIBRATION, LCIC-WIM-SETTINGSand LCIC-WIM-MONITOR. LCIC-WIM-BENU High Speed; Up to 52,000 Samples per SecondU 24-Bit A/D with ±8 Million Counts for Tension and Compression ApplicationsU Powerful 32-Bit /135 MIPS DSP for High Speed On-Board Processing— OEM Applications Can Be Embedded On The BoardU 4 Opto-Isolated Outputs Configurable as Setpoints, Latching Alarms or User OutputsU 4 Opto-Isolated Inputs; Input #1 Has Counter OptionU Analog Output— 0 to 2.5V , 16-BitU 8-Digit LED DisplayU On Board Temperature SensorU USB 2.0 Interface— Full Speed CompatibleU RS-232/RS485 Communications Ideal for PLC Based ApplicationsU Multiple Boards May Be Connected Via USB or RS485These software utilities enable easy selection and setup of the required board. The calibration utility (LCIC-WIM-CALIBRATION) enables you to calibrate the LCIC-WIM-BEN board by adjusting it to your own system. The utility is straight forward and is in the form of a Windows ® wizard. The LCIC-WIM-SETTINGS utility gives control to card’s filters, analog output, fill mode parameters and more. The LCIC-WIM-MONITOR utility is a vital tool for analyzing dynamic load/force systems.It takes full advantage of the board’s speed and samples the load cell signal at maximum speed (15,000 samples per second), sending the data to the PC via the USB port and displaying it as a curve—load cell signal/versus time. Y ou can then zoom in/out on the data, view max (peak) and min readings, save the data in standard ASCII file format for later use and even perform some calculations like averaging on a required part of the curve.LCIC-WIM-BEN load cell interface card.Ordering Example: LCIC-WIM-BEN , high speed load cell interface card with enclosure and OCW-1 OMEGACARE SM year extended warranty (adds 1 year to standard 1-year warranty).Windows software showing vibration on a scale.Windows software showing weight of truck passing a scale.LCIC-101 load cell sold separately and shown slightly smaller than actual sizeSpecifications LOAD CELL INPUT Bridge Input: 1 input, 4-wire or 6-wire Excitation: 5 Vdc excitation for up to 10 load cells (350 Ω ) in parallel Compatibility: Compatible with 1, 2 & 3 mV/V load cellsA/D Speed: Low noise wide bandwith amplifier, very high speed, up to 52,000 samples per second Resolution: 24-bit A/D with ±8 million counts for tension and compression applicationsCOMMUNICATIONS Standard Interfaces: USB 2.0 full speed compatible; combined RS-232/RS-485INPUTS Digital Inputs: 4 opto-isolated inputs with 10 to 30 Vdc range, each with status LED; input #1 configurable as high speed counter; input #2 configurable as sample triggerOUTPUTS Relays: 4 opto-isolated solid state relays rated at 50 V, 300 mA; configurable as setpoints, latching alarms or user outputs, each with status LED Analog Output: 0 to 2.5 Vdc with 16-bit resolution GENERAL Power: From included 110/220 Vac adaptor DSP: Powerful 32-bit/135 MIPS DSP for high speed onboard processing Display: 8-digit LED display RS-232/485 Port:DB9F connector I/O Port: DB15M connector (digital inputs, relay outputs, analog output)Temperature Sensor: On-board Dimensions: Standard (Eurocard); 160 L x 100 mm W (6.3 x 3.94”) Weight: 251 g (9 oz)Case: ABS Laptop not included LCIC-DTERM screw terminal adaptor facilitates cell connections with screw terminal connections (sold separately).Extended Warranty OMEGACARE SM extended warranty program is available for models shown on this page. Ask your sales respresentative for full details when placing an order. OMEGACARE SM covers parts, labor and equivalent loaners.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1C-BAND POWER AMPLIFIER 525.787 Microwave Monolithic Integrated Circuits (MMIC) Design

Gary S. Hoffman Fall 2001

ABSTRACT – MMIC Class-F, cascade C-Band power amplifier designed for final class project using TriQuint parts. Frequency band of 5.15 to 5.875 GHz, or a bandwidth of 725.0 MHz, with a center frequency of 5.5125 GHz. Amplifier small signal gain >12.0 dB across the band with an output power > +24.0 dBm at center frequency, 1.0 dB compression point. On-chip resonant circuits in series and parallel, tuned to center frequency and its 3rd harmonic respectively, shape the output waveform and improve Power Added Efficiency (PAE). On-chip input and output matching networks into 50.0 Ohms, minimize VSWR to <1.5:1 across the band.

1. INTRODUCTION CIRCUIT DESCRIPTION – With reference to a simplified final layout shown in Schematic #1 on page 6A, this C-Band power amplifier is a cascade Class-F power amplifier, which has a Class-A biased pre-amplifier (Q2) with a Class-AB biased post-amplifier (Q1). This design allowed for an overall small signal gain >12.0 dB to be divided between two amplifier stages. Center frequency of amplifier is 5.5125 GHz with a 725.0 MHz bandwidth (5.15-5.875 GHz). On-chip input matching (L12, L16), output matching (L4) with resonant circuits in series (L8, C8) and parallel (L7, C7), plus DC blocking and by-pass capacitors (C2, C4, C5, C9, C11, C12, C13). 1.0 mH inductors (L18 - L21) shown in DC bias paths are bond wire models, while input and output tqtrx_ports (P1, P2) are models of G-S-G signal-probe pads [5, 6].

For individual TriQuint GFET amplifiers; Class-A biased pre-amplifier, as given by marker #1 in IV Curves of Plot #1 on page 5A, has a DC bias point of –0.5 V for VGS, +7.0 V for VDS and 63.0 mA for IDS. Schematic #2 on page 6B gives the number of gates and gate widths for this 330.0 um GFET as 6 and 55.0 um respectively. Class-AB biased post-amplifier, as given by marker #1 in the IV Curves of Plot #2 on page 5B, has a DC bias point (25.0% of the IDSS value shown at marker #2) of –1.5 V for VGS, +7.0 V for VDS, and 49.0 mA for IDS. Schematic #3 on page 6C for this 720.0 um GFET gives number of gates and gate widths as 6 and 120.0 um respectively [5, 6].

Returning to Schematic #1 on page 6A, Input Matching Network (IMN) formed by L12 and L16 match pre-amplifier (Q2) to a 50.0 Ohm source impedance. L17, C2 and L15 form an inductive pi-network between pre-amplifier Q2 and post-amplifier Q1. L4 on output of post-amplifier Q1 has an RCripp load value of 50.0 Ohms and matches Q1 to an output load impedance of 50.0 Ohms through an output resonant network of series circuit L8 and C8, plus parallel circuit of L7 and C7 [5, 6].

This output resonant network shapes the output waveform and improves overall Power Added Efficiency (PAE). It is composed of resonant circuit L8 and C8 tuned to 16.54 GHz (3rd harmonic of 5.5125 GHz), and resonant circuit L7 and C7 tuned to center frequency (i.e. 5.5125 GHz). With these two resonant circuits, this network provides an OPEN to the 3rd harmonic (16.54 GHz) and a SHORT to the 2nd harmonic (11.03 GHz) but prevents their appearance at the load. For center frequency of 5.5125 GHz, this resonant network provides a MATCH to a 50.0 Ohm load. C4 is a DC blocking capacitor, but is also part of this resonant network and tunes-out any added inductance between the Q1 drain and load presented by this output resonant network [1, 2, 3, 4]. 2

Plot #3 on page 5C along with Schematic #4 on page 6D, show the full final layout for this C-Band, cascade Class-F amplifier. Stated design specifications for this C-Band cascade Class-F power amplifier.

FREQUENCY BAND: 5.15 to 5.875 GHz [center frequency of 5.5125 GHz], BANDWIDTH: > 725.0 MHz, GAIN, small signal: > 12.0 dB Min [15.0 dB goal], GAIN RIPPLE (flatness): ± 0.5 dB Max, OUTPUT POWER: > +24.0 dBm @ 1.0 dB compression point, EFFICIENCY: > 20.0% @ 1.0 dB compression point [25.0 % goal], VSWR into 50.0 Ohms: < 1.5:1 [ Γ < 0.2, Return Loss < -14.0 dB ] for input and output, SUPPLY VOLTAGES: +7.0 and – 5.0 VDC, SIZE: 60.0 x 60.0 mil ANACHIP.

DESIGN PHILOSOPHY – Class-F amplifiers are also termed harmonic control amplifiers. This, from use of a frequency selective network on the amplifier output which is resonant at odd and even harmonics of the fundamental, but blocks these selected harmonics from appearing on the output load. By appearing as an open or a short to these odd/even harmonics, drain voltages and currents are optimized to reduce overall power dissipation in the GFET which results in a higher Power Added Efficiency (PAE). For this design, an open appears for the 3rd harmonic and a short appears for the 2nd harmonic. An open presented to the 3rd harmonic causes flattening of the drain voltage, which if more harmonics were involved, would eventually produce a square wave. A short for the 2nd harmonic causes a flattened sinusoid from added output current flow with a lowered output drain voltage and results in the higher PAE mentioned [1, 2, 3, 4, 5, 6].