P64M6416YBC-8A中文资料

MEMORY存储芯片TMS32C6414TBGLZWA8中文规格书

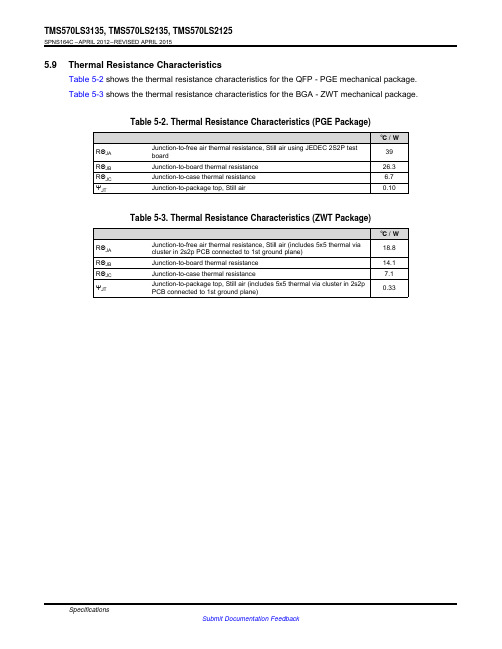

TMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL20155.9Thermal Resistance CharacteristicsTable5-2shows the thermal resistance characteristics for the QFP-PGE mechanical package.Table5-3shows the thermal resistance characteristics for the BGA-ZWT mechanical package.Table5-2.Thermal Resistance Characteristics(PGE Package)°C/WJunction-to-free air thermal resistance,Still air using JEDEC2S2P testRΘJA39boardRΘJB Junction-to-board thermal resistance26.3RΘJC Junction-to-case thermal resistance 6.7ΨJT Junction-to-package top,Still air0.10Table5-3.Thermal Resistance Characteristics(ZWT Package)°C/WJunction-to-free air thermal resistance,Still air(includes5x5thermal viaRΘJA18.8cluster in2s2p PCB connected to1st ground plane)RΘJB Junction-to-board thermal resistance14.1RΘJC Junction-to-case thermal resistance7.1Junction-to-package top,Still air(includes5x5thermal via cluster in2s2pΨJT0.33PCB connected to1st ground plane)SpecificationsTMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL2015 5.10Output Buffer Drive StrengthsTable5-4.Output Buffer Drive StrengthsLOW-LEVEL OUTPUT CURRENT,I OL for V I=V OLmaxor SIGNALSHIGH-LEVEL OUTPUT CURRENT,I OH for V I=V OHminFRAYTX2,FRAYTX1,FRAYTXEN1,FRAYTXEN2,MIBSPI5CLK,MIBSPI5SOMI[0],MIBSPI5SOMI[1],MIBSPI5SOMI[2],MIBSPI5SOMI[3],MIBSPI5SIMO[0],MIBSPI5SIMO[1],MIBSPI5SIMO[2],MIBSPI5SIMO[3],8mA TMS,TDI,TDO,RTCK,SPI4CLK,SPI4SIMO,SPI4SOMI,nERROR,N2HET2[1],N2HET2[3],All EMIF Outputs and I/Os,All ETM OutputsMIBSPI3SOMI,MIBSPI3SIMO,MIBSPI3CLK,MIBSPI1SIMO,MIBSPI1SOMI,MIBSPI1CLK, 4mAnRSTAD1EVT,CAN1RX,CAN1TX,CAN2RX,CAN2TX,CAN3RX,CAN3TX,DMM_CLK,DMM_DATA[0],DMM_DATA[1],DMM_nENA,DMM_SYNC,GIOA[0-7],GIOB[0-7],LINRX,LINTX,2mA zero-dominantMIBSPI1NCS[0],MIBSPI1NCS[1-3],MIBSPI1NENA,MIBSPI3NCS[0-3],MIBSPI3NENA,MIBSPI5NCS[0-3],MIBSPI5NENA,N2HET1[0-31],N2HET2[0],N2HET2[2],N2HET2[4],N2HET2[5],N2HET2[6],N2HET2[7],N2HET2[8],N2HET2[9],N2HET2[10],N2HET2[11],N2HET2[12],N2HET2[13],N2HET2[14],N2HET2[15],N2HET2[16],N2HET2[18],SPI2NCS[0],SPI2NENA,SPI4NCS[0],SPI4NENAECLK,selectable8mA/2mA SPI2CLK,SPI2SIMO,SPI2SOMIThe default output buffer drive strength is8mA for these signals.Table5-5.Selectable8mA/2mA ControlSIGNAL CONTROL BIT ADDRESS8mA2mAECLK SYSPC10[0]0xFFFF FF7801SPI2CLK SPI2PC9[9](1)0xFFF7F66801SPI2SIMO SPI2PC9[10](1)0xFFF7F66801SPI2SOMI SPI2PC9[11](1)0xFFF7F66801(1)Either SPI2PC9[11]or SPI2PC9[24]can change the output strength of the SPI2SOMI pin.In case of a32-bit write where these two bitsdiffer,SPI2PC9[11]determines the drive strength.SpecificationsTMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL20155.11Input TimingsFigure5-2.TTL-Level InputsTable5-6.Timing Requirements for Inputs(1)MIN MAX UNIT t pw Input minimum pulse width t c(VCLK)+10(2)ns(1)t c(VCLK)=peripheral VBUS clock cycle time=1/f(VCLK)(2)The timing shown in Figure5-2is only valid for pins used in GPIO mode.5.12Output TimingsTable5-7.Switching Characteristics for Output Timings versus Load Capacitance(C L)PARAMETER MIN MAX UNITCL=15pF 2.5CL=50pF4Rise time,t r nsCL=100pF7.2CL=150pF12.5 8mA low EMI pins(see Table5-4)CL=15pF 2.5CL=50pF4Fall time,t f nsCL=100pF7.2CL=150pF12.5CL=15pF 5.6CL=50pF10.4Rise time,t r nsCL=100pF16.8CL=150pF23.2 4mA low EMI pins(see Table5-4)CL=15pF 5.6CL=50pF10.4Fall time,t f nsCL=100pF16.8CL=150pF23.2 2mA-z low EMI pins CL=15pF8(see Table5-4)CL=50pF15Rise time,t r nsCL=100pF23CL=150pF33CL=15pF8CL=50pF15Fall time,t f nsCL=100pF23CL=150pF33 Specifications。

嵌入式主板说明书

ARM8060嵌入式主板说明书北京阿尔泰科技发展有限公司Beijing Art Technology Development Co.,Ltd.!安全须知电气方面安全性➢为避免可能的电击造成严重损害,在移动主板之前,请先将主板的电源切断。

➢当您要加入硬件设备到系统中或者要移除系统中的硬件设备时,请务必先连接该设备的信号线,然后再连接电源线。

➢请确定电源的电压设置已调整到所规定的电压标准值。

操作方面的安全性➢在您安装主板以及加入硬件设备之前,请务必详细阅读本手册所提供的相关信息。

➢在使用本产品之前,请确定所有的排线、电源线都正确地连接好。

若您发现有任何重大的瑕疵,请尽快联系我们或您的经销商。

➢为避免发生电气短路情形,请务必将所有没用到的螺丝、回形针及其它零件收好,不要遗留在主板上。

➢灰尘、湿气以及剧烈的温度变化都会影响主板的使用寿命,因此请尽量避免放置在这些地方。

➢当操作系统启动过程中,请勿断电,为避免损坏主板芯片➢系统运行过程中,防止静电,最好不要用手接触主板➢若在本产品使用上有任何的技术性问题,请和我们的技术支持人员联系。

目录目录11.产品简介11.1产品概述11.2 产品特点错误!未定义书签。

2产品特性72.1跳线说明72.2 外围设备接口连接82.3 软件特性错误!未定义书签。

3.电气参数及机械特性14附录A 订购信息15附录B 应用程序开发环境151.产品简介1.1产品概述ARM8060是北京阿尔泰科技发展有限公司基于Atmel公司ARM926EJ-S内核的AT91SAM9261处理器,结合PC104总线规范设计的一款具有极高性价比、结构和尺寸极其紧凑并且功耗极低的工业级嵌入式主板,其上运行嵌入式Linux 或WinCE操作系统,可以处理多种计算任务。

主板采用超低功耗嵌入式处理器,无风扇设计,超宽工作温度-20°C ~+70°C,低温工作性能优良,高温工作彻底解决了由于风扇可靠性而引起的故障。

P64M6416HHB-75A中文资料

SDRAM DDR MODULE 64M X 64 DIMM Features:• 184 pin dual in-line memory modules (DIMM)• Fast data transfer rates PC2100 fully compatible• Utilizes 266 DDR SDRAM 66p TSOP components.• 512MB (64MX64) built w/64MX4 components• Vdd = 2.5v +0.2v, VddQ = 2.5v +0.2v• 2.5v I/O (SSTL_2 compatible)• Internal pipelined double data rate (DDR)Architecture, two data accesses per clock cycle• Bidirectional data strobe (DQS) transmitted/Received with data• Differential clock inputs (CK0 and CK0#)• 7.8125us maximum average periodic refresh interval• Programmable burst lengths: 2, 4 or 8Options: Part Number:16 - 64Mx4 DDR SDRAM TSOP P64M6416HHB-XXKEY DIMM MODULE TIMING PARAMETERSModule Marking ComponentMarkingClockFrequencyCASLatency-75A -75A 133MHz 2.5GENERAL DESCRIPTIONThe P64M6416HHB is high performance dynamic random-access 512MB modules respectively. These modules are organized in a x64 configuration, and utilize quad bank architecture with a synchronous DDR interface. These DDR SDRAM modules use double data rate architecture to achieve high speed operation._______________________________________________ _ABSOLUTE MAXIMUM RATINGS:Voltage on Vdd Supply relative to Vss............-1 to +4.6V Voltage on VddQ Supply relative to Vss……..-1V to +3.6V Voltage on Vref and Inputs relative to Vss…..-1V to +3.6V Voltage on I/O pins relative to Vss… -0.5V to VddQ +0.5V Operating Temperature T A (Ambient) .......25 ° to +70 °C Storage Temperature...................................-55 to +150 ° Power Dissipation………………………………………18 W Short Circuit Output Current…………………………..50 mAPIN ASSIGNMENT184-Pin DIMMPIN SYMBOL PIN SYMBOL PIN SYMBOL PIN SYMBOL1 Vref 47 NC 93 Vss 139 Vss2 DQ0 48 A0 94 DQ4 140 NC3 Vss 49 NC 95 DQ5 141 A104 DQ1 50 Vss 96 VddQ 142 NC5 DQS0 51 NC 97 DQS9 143 VddQ6 DQ2 52 BA1 98 DQ6 144 NC7 Vdd 53 DQ32 99 DQ7 145 Vss8 DQ3 54 VddQ 100 Vss 146 DQ369 NC 55 DQ33 101 NC 147 DQ3710 NC 56 DQS4 102 NC 148 Vdd11 Vss 57 DQ34 103 NC (A13) 149 DQS1312 DQ8 58 Vss 104 VddQ 150 DQ3813 DQ9 59 BA0 105 DQ12 151 DQ3914 DQS1 60 DQ35 106 DQ13 152 Vss15 VddQ 61 DQ40 107 DQS10 153 DQ4416 CK1 62 VddQ 108 Vdd 154 RAS#17 CK1# 63 WE# 109 DQ14 155 DQ4518 Vss 64 DQ41 110 DQ15 156 VddQ19 DQ10 65 CAS# 111 CKE1 157 SO#20 DQ11 66 Vss 112 VddQ 158 S1#21 CKE0 67 DQS5 113 NC(BA2)159 DQS1422 VddQ 68 DQ42 114 DQ20 160 Vss23 DQ16 69 DQ43 115 NC (A12) 161 DQ4624 DQ17 70 Vdd 116 Vss 162 DQ4725 DQS2 71 NC(S2#)117 DQ21 163 NC(S3#)26 Vss 72 DQ48 118 A11 164 VddQ27 A9 73 DQ49 119 DQS11 165 DQ5228 DQ18 74 Vss 120 Vdd 166 DQ5329 A7 75 CK2# 121 DQ22 167 NC30 VddQ 76 CK2 122 A8 168 Vdd31 DQ19 77 VddQ 123 DQ23 169 DQS1532 A5 78 DQS6 124 Vss 170 DQ5433 DQ24 79 DQ50 125 A6 171 DQ5534 Vss 80 DQ51 126 DQ28 172 VddQ35 DQ25 81 Vss 127 DQ29 173 NC36 DQS3 82 Vddid 128 VddQ 174 DQ6037 A4 83 DQ56 129 DQS12 175 DQ6138 Vdd 84 DQ57 130 A3 176 Vss39 DQ26 85 Vdd 131 DQ30 177 DQS1640 DQ27 86 DQS7 132 Vss 178 DQ6241 A2 87 DQ58 133 DQ31 179 DQ6342 Vss 88 DQ59 134 NC 180 VddQ43 A1 89 Vss 135 NC 181 SA044 NC 90 WP 136 VddQ 182 SA145 NC 91 SDA 137 CK0 183 SA246 Vdd 92 SCL 138 CKO# 184 VDDSPDStresses beyond these may cause permanent damage tothe device. This is a stress rating only and functional operation of the device at or beyond these conditions isnot implied. Exposure to these conditions for extended periods may affect reliability.CAPACITANCE: (This parameter is sampled. Vdd = +2.5V ± 0.2V)Parameter Symbol Max Units512MBInput/Output Capacitance: DQ’s, DQS’s C l0 10.0 pFInput Capacitance: A0-A12, BA0, BA1, RAS#, CAS#, WE#, S0#(256MB)C l1 N/A pFInput Capacitance: A0-A12, BA0, BA1, RAS#, CAS#, WE# (512MB) C l1 48.0 pFInput Capacitance: S0#, S1# (512MB) C l2 24.0 pFInput Capacitance: CK0, CK0# C l3 12.0 pFInput Capacitance: CK1, CK1#, CK2, CK2# C l3 18.0 pFInput Capacitance: CKE0 , (CKE1: 512MB only) C l4 24.0 pFDC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS:Parameter Symbol Min Max Units Supply Voltage Vdd 2.3 2.7 V I/O Supply Voltage VddQ 2.3 2.7 V I/O Reference Voltage Vref 0.49 x VddQ 0.51 X VddQ V I/O Termination Voltage (system) Vtt Vref – 0.04 Vref + 0.04 V Input High (Logic 1) Voltage V IH(DC) Vref + 0.15 Vdd + 0.3 V Input Low (Logic 0) Voltage V IL(DC) -0.3 Vref – 0.15 VWE#, RAS#, CAS#, BA0, BA1 I I-3232uAS0#, S1#, CKE0, CKE1 I I -16 16 uACK0, CK0# I I-88uAInput Leakage CurrentAny input = 0V < VIN < VddAll other pins not under test =0VCK1/CK1#, CK2/CK2# I I -12 12 uA Output Leakage Current DQs are disabled; 0V < VOUT < VddQ I OZ -10 10 uA Output High Current (V OUT = 1.95V, maximum Vtt) I OH -16.8 - mA Output Low Current ( V OUT = .35V, minimum Vtt) I OL 16.8 - mAAC OPERATING CONDITIONS: (This parameter is sampled. Vdd = +2.5V ± 0.2V, VddQ = +2.5V +0.2V)AC CHARACTERISTICS Symbol -75A Units PARAMETER MIN MAXData valid output window NA tQH - tDQSQ ns REFRESH to REFRESH command interval (256MB) tREFC 70.3 us Average periodic refresh interval (256MB) tREFI 7.8 us Terminating voltage delay to Vdd tVTD 0 nsAC INPUT OPERATING CONDITIONS: (This parameter is sampled. Vdd = +2.5V ± 0.2V, VddQ = +2.5V +0.2V)Parameter Symbol MIN MAX Units Input High (Logic 1) Voltage VIH (AC) Vref +0.310 V Input Low (Logic 0) Voltage VIL (AC) Vref +0.310 V I/O Reference Voltage Vref (AC) 0.49 X VddQ 0.51 x VddQ VIDD OPERATING CONDITIONS AND MAXIMUM LIMITS: Vdd = 2.5V ± .2V, Temp. = 25° to 70 °CAC ELECTRICAL CHARACTERISTICS: Vdd = 2.5V ± .2V, Temp. = 25° to 70°C (CL = CAS Latency)AC CHARACTERISTICS -75A PARAMETER SYM MIN MAX UNITS Access window of DQ’s from ck/ck# tAC -0.75 +0.75 ns CK high-level width tCH 0.45 0.55 tCK CK low-level width tCL 0.45 0.55 tCK Clock cycle time CL=2.5 tCK 7.5 113 ns DQ and DM input hold time tDH 0.5 ns DQ and DM input setup time tDS 0.5 ns DQ and DM input pulse width (for each input) tDIPW 1.75 ns Access window of DQS from CK/CK# tDQSCK -0.75 +0.75 ns DQS input high pulse width tDQSH 0.35 tCK DQS input low pulse width tDQSL 0.35 tCK DQS-DQ-DQ skew (first to last transition per access) tDQSQ 0.5 ns Write command to first DQS latching transition tDQSS 0.75 1.25 tCK DQS falling edge to CK rising – setup time tDSS 0.2 tCK DQS falling edge from CK rising – hold time tDSH 0.2 tCK Half clock period tHP tCH, tCL tCK Data-out high-impedance window from CK/CK# tHZ +0.75 ns Data-out low-impedance window from CK/CK# tLZ -0.75 ns Address and control input hold time tIH 0.90 ns Address and control input setup time tIS 0.90 ns LOAD MODE REGISTER command cycle time tMRD 15 ns Data hold skew factor tQHS 0.75 ns ACTIVE to PRECHARGE command tRAS 40 120,000 ns ACTIVE to READ with auto precharge command tRAP 20 ns ACTIVE to ACTIVE/AUTO REFRESH command period tRC 65 ns AUTO REFRESH command interval tRFC 75 us ACTIVE to READ or WRITE delay tRCD 20 ns PRECHARGE command period tRP 20 ns DQS read preamble tRPRE 0.9 1.1 tCK DQS read postamble tRPST 0.4 0.6 tCK ACTIVE bank a to ACTIVE bank b command tRRD 15 ns DQS Write preamble tWPRE 0.25 tCK DQS Write preamble setup time tWPRES 0 ns DQS Write postamble tWPST 0.4 0.6 tCK DQS Write recovery time tWR 15 ns Internal WRITE to READ command delay tWTR 1 tCK NOTES:SERIAL PRESENCE-DETECT OPERATION - This module incorporates Serial Presence-Detect (SPD). The SPD function is implemented using a 2,048 bit EEPROM, containing 256 bytes of nonvolatile storage. The first 128 bytes can be programmed by SpecTek to identify the module type and various DRAM organization and timing parameters. The remaining 128 bytes of storage are available for use by the customer. System READ/WRITE operations between the master (system logic) and the slave EEPROM device (DIMM) occur via a standard IIC bus using the DIMM’s SCL (clock) and SDA (data) signals, together with SA (2:0), which provide 8 unique DIMM/EEPROM addresses.SPD CLOCK AND DATA CONVENTIONS - Data states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are reserved for indicating start and stop conditions (Figures 1 and 2).SPD START CONDITION - All commands are preceded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH. The serial PD device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.SPD STOP CONDITION - All communications are terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition also places the serial PD device into standby power mode.SPD ACKNOWLEDGE - Acknowledge is a software convention used to indicate successful data transfers. The transmitting device, either master or slave, will release the bus after transmitting eight bits of data (Figure 3). The PD device will always respond with an acknowledge after recognition of a start condition and its slave address. If both the device and a write operation have been selected, the PD device will respond with an acknowledge after the receipt of each subsequent eight bit word. In the read mode the PD device will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is not detected, the slave will terminate further data transmissions and await the stop condition to return to standby power mode.SERIAL PRESENCE-DETECT EEPROM DC OPERATING CONDITIONS (VCC = +3.3V ± 0.3V)PARAMETER/CONDITION Symbol MIN MAX Units Supply Voltage V CC 3.0 3.6 V Input High (Logic 1) Voltage, all inputs V IH Vcc x .7 Vcc x .5 V Input Low (Logic 0) Voltage, all inputs V IL -1.0 Vcc x .3 V OUTPUT LOW VOLTAGE, I OUT =3mA V OL 0.4 V INPUT LEAKAGE CURRENT, V IN = GND to Vcc I LI 10 µA OUTPUT LEAKAGE CURRENT, V OUT = GND to Vcc I LO 10 µA STANDBY CURRENT SCL=SDA=Vcc -0.3V, All other inputs = GND or 3.3V +10% I SB 30 µA POWER SUPPLY CURRENT SCL clock frequency = 100 KHz I CC 2 µA SERIAL PRESENCE-DETECT EEPROM AC OPERATING CONDITIONS (VCC = +3.3V ± 0.3V)AC CHARACTERISTICSPARAMETER/CONDITION Symbol MIN MAX Units Notes SCL LOW to SDA data-out valid t AA 0.3 3.5 µsIdle bus time before a transition can start t BUF 4.7 µs Data-out hold time t DH 300 ns SDA and SCL fall time t F 300 ns Data-in hold time T HD:DAT 0 µs Start condition hold time T HD:STA 4 µs Clock HIGH period t HIGH 4 µs Noise suppression time constant at SCL, SDA inputs t l 100 ns Clock LOW period t LOW 4.7 µs SDA and SCL rise time t R 1 µs SCL clock frequency t SCL 100 KHz Data-in setup time T SU:DAT 250 ns Start condition setup time T SU:STA 4.7 µs Stop condition setup time T SU:STO 4.7 µs WRITE cycle time t WR 10 ms1 NOTES: 1. The SPD EEPROM WRITE cycle time (t WR) is the time from a valid stop condition of a WRITE sequence to the end of the EEPROM internal erase/program cycle. During the WRITE cycle the EEPROM bus interface circuit is disabled, SDA remains HIGH due to pull-up resistor, and the EEPROM does not respond to its slave address.SCLSDADATA STABLEDATA CHANGEDATA STABLEFigure 1DATA VALIDITYSTART BITSTOP BITSCLSDAFigure 2DEFINITION OF STARTAND STOP98SCL from Master Data Output from Transmitter AcknowledgeFigure 3ACKNOWLEDGE RESPONSEFROM RECEIVERData Output from Receiver。

PST 641U变压器差动保护装置技术说明书V1.22

5 定值整定说明 ........................................................................................................................................................ 9 5.1 保护定值清单及说明 ...................................................................................................................................... 9 5.2 运行参数清单及说明 .....................................................................................................................................10 5.3 软压板清单及说明.........................................................................................................................................11 6 装置信息代码表....................................................................................................................................................12 6.1 6.2 6.3 6.4 事件信息表 ....................................................................................................................................................12 告警信息表 ....................................................................................................................................................12 软压板信息表 ................................................................................................................................................12 遥信量信息表 ................................................................................................................................................13

MB85RC64中文

铁电存储器MB85RC64(8K×8)1.概述MB85RC64了FRAM(铁电随机存取记忆体)独立芯片配置了8192×8位,形成铁电工艺和硅栅CMOS工艺技术非易失性内存中的细胞。

MB85RC64采用两线串行接口(与世界标准的I2C总线兼容)。

与SRAM不同的MB85RC64是无需使用数据备份电池,能够保留数据。

MB85RC64的读写次数10亿次,与EPROM和FLASH相比,有显著的改善。

而且不在向写完存储器后,不需要查询序列。

2.特性●位操作:8192×8位●工作电压:2.7V—3.3V●工作频率:400KHz●两串行总线:I2C总线2.1标准版,支持标准模式和快速模式,由SCL和SDA控制。

●工作温度范围:-40℃—85℃●数据保持:10年(55℃)●读写寿命:至少每位10亿次●封装:Plastic / SOP, 8-pin (FPT-8P-M02)●低电压消耗:工作电流0.15mA,待机电流5uA3.管脚分配3.管脚功能描述管教编号管脚名功能描述1—3 A0/A1/A2 器件地址一个I2C总线可以连接8个和MB85RC64类似的器件。

通过将A0/A1/A2与VDD和VSS连接,确定每个器件的地址。

如果A0/A1/A2未连接,默认为0。

CPU通过SDA线输出一个地址与器件进行匹配。

4 VSS 数字地5 SDA 数据IO串口这是双向通信的数据IO口,用来读写铁电存储器的阵列数据,这是开漏极输出,可能是与其它漏极开路(或者集电极开路信号总线)进行线或运算,因此需要一个上拉电阻连接到外部电路。

6 SCL 时钟串口这是时钟输入口,时钟上升沿进行数据采样,下降沿进行数据输出。

7 WP 写保护WP是H电平,禁止写入。

WP是L电平,可进行写数据,如果WP没有置位,默认为L电平。

而读数据操作,不受WP 管脚的限制。

8 VDD 电源电压4.模块框图5.I2C电路MB85RC64有两线串行接口,支持I2C总线,并作为从器件工作。

MEMORY存储芯片MT46V256M4P-75 A中文规格书

Architecture33.2.7.1USB Controller Peripheral Mode Operation•Soft connect-After a reset,the SOFTCONN bit of POWER register(bit6)is cleared to0.The controller will therefore appear disconnected until the software has set the SOFTCONN bit to1.Theapplication software can then choose when to set the PHY into its normal mode.Systems with alengthy initialization procedure may use this to ensure that initialization is complete and the system isready to perform enumeration before connecting to the USB.Once the SOFTCONN bit has been set,the software can also simulate a disconnect by clearing this bit to0.•Entry into suspend mode-When operating as a peripheral device,the controller monitors activity on the bus and when no activity has occurred for3ms,it goes into Suspend mode.If the Suspendinterrupt has been enabled,an interrupt will be generated at this time.At this point,the controller can then be left active(and hence able to detect when Resume signalingoccurs on the USB),or the application may arrange to disable the controller by stopping its clock.However,the controller will not then be able to detect Resume signaling on the USB.As a result,some external hardware will be needed to detect Resume signaling(by monitoring the DM and DP signals),so that the clock to the controller can be restarted.•Resume Signaling-When resume signaling occurs on the bus,first the clock to the controller must be restarted if necessary.Then the controller will automatically exit Suspend mode.If the Resumeinterrupt is enabled,an interrupt will be generated.•Initiating a remote wakeup-If the software wants to initiate a remote wakeup while the controller is in Suspend mode,it should write to the Power register to set the RESUME bit to1.The software shouldleave then this bit set for approximately10ms(minimum of2ms,a maximum of15ms)beforeresetting it to0.NOTE:No resume interrupt will be generated when the software initiates a remote wakeup.•Reset Signaling-When reset signaling occurs on the bus,the controller performs the following actions:–Clears FADDR register to0–Clears INDEX register to0–Flushes all endpoint FIFOs–Clears all control/status registers–Generates a reset interrupt.If the HSENA bit in the POWER register(bit5)was set,the controller also tries to negotiate for high-speed operation.Whether high-speed operation is selected is indicated by HSMODE bit of POWER register(bit4).When the application software receives a reset interrupt,it should close any open pipes and wait forbus enumeration to begin.SetupStatus phase(OUT)Int Sequence #1Idle TX state Idleset TxPktRdyand set DataEndand setTxPktRdyreq. and clearRxPktRdyand setTxPktRdyCPU actionsSequence #2Sequence #3No data phaseSequence #1Sequence #2ArchitectureFigure33-4.CPU Actions at Transfer PhasesFigure33-5.Sequence of Transfer。

PSP641技术说明书V1.0

PSP 641数字式备用电源自投装置技术说明书使用说明书国电南京自动化股份有限公司PSP 641数字式备用电源自投装置技术说明书使用说明书编写承文新姚卫兵审核马文龙批准郭效军2000年10月* 本公司保留对此说明书修改的权利,请注意最新版本资料。

第一部分技术说明书(2000.10)目次声明 (1)安全标准 (1)1装置简介 (1)2技术参数 (4)2.1 额定参数 (4)2.2 主要技术性能 (4)2.3 绝缘性能 (5)2.4 抗电磁干扰性能 (6)2.5 机械性能 (6)2.6 环境条件 (6)3装置硬件 (7)3.1 机箱结构 (7)3.2 交流插件 (7)3.3 CPU插件 (8)3.4 电源插件 (10)3.5 逻辑及跳闸插件 (10)4功能说明 (13)4.1 逻辑可编程备投原理 (13)4.2 典型备用电源自投方式 (15)4.3 数据记录 (26)5与变电站自动化系统配合 (27)6定值及整定说明 (28)PSP641 数字式备用电源自投装置的整定值清单及说明 (28)·声明· 1声明恭喜您购买了国电南京自动化股份有限公司的数字式保护及自动化产品—数字保护及自动化技术的国内领先者。

所有国电南京自动化股份有限公司的PS系列数字式保护及自动化产品符合严格的技术规范和ISO9001产品质量标准,经得起恶劣的现场工作环境的考验。

拥有丰富的数字式保护及自动化设备的开发经验、对用户常年24小时的技术支持,您尽可以信赖国电南京自动化股份有限公司的产品。

PS系列产品采用完全汉化的显示技术,人机界面友好,使您免除查找说明书操作的烦恼。

每款产品均配置了基于PC机调试界面的接口,结合本公司提供的Psview调试软件包,大大改善了现场调试手段。

PS640系列产品采用防水、防尘、抗振动设计,适合安装于开关柜等环境条件较为恶劣的现场运行。

机箱面板采用先进的工业美学设计,使用方便,倍感亲切。

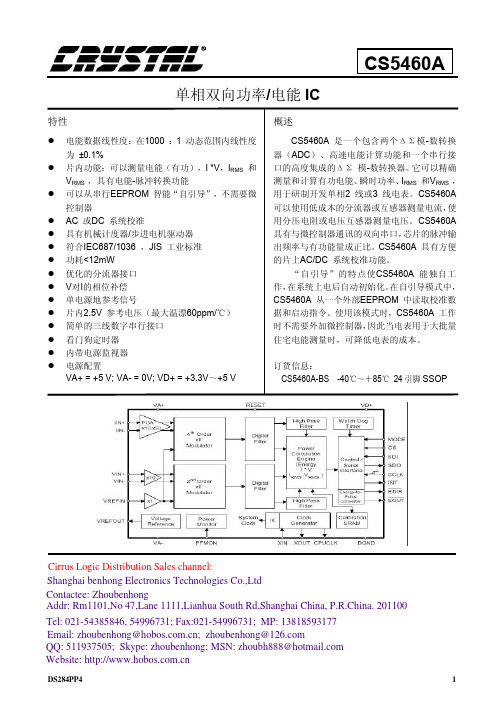

CS5460A中文数据手册

l 片内功能:可以测量电能(有功),I *V,IRMS 和 VRMS ,具有电能-脉冲转换功能

l 可以从串行EEPROM 智能“自引导”,不需要微 控制器

l AC 或DC 系统校准 l 具有机械计度器/步进电机驱动器 l 符合IEC687/1036 ,JIS 工业标准 l 功耗<12mW l 优化的分流器接口 l V对I的相位补偿 l 单电源地参考信号 l 片内2.5V 参考电压(最大温漂60ppm/℃) l 简单的三线数字串行接口 l 看门狗定时器 l 内带电源监视器 l 电源配置

VA+ = +5 V; VA- = 0V; VD+ = +3.3V~+5 V

概述

CS5460A 是一个包含两个ΔΣ模-数转换 器(ADC)、高速电能计算功能和一个串行接 口的高度集成的ΔΣ 模-数转换器。它可以精确 测量和计算有功电能、瞬时功率、IRMS 和VRMS , 用于研制开发单相2 线或3 线电表。CS5460A 可以使用低成本的分流器或互感器测量电流,使 用分压电阻或电压互感器测量电压。CS5460A 具有与微控制器通讯的双向串口,芯片的脉冲输 出频率与有功能量成正比。CS5460A 具有方便 的片上AC/DC 系统校准功能。

cs5460a单相双向功率电能ic特性rms具有电能脉冲转换功能可以从串行eeprom智能自引导不需要微控制器ac或dc系统校准符合iec6871036jis工业标准片内25v参考电压最大温漂60ppm电源配置va0v

台达A641数控系统说明书

STANDARD FEATURESAxis ControlDigital Servo Function1 Controlled Path StandardSimultaneously controlled axes: Up to maximum of 4; 3 if Contouring Spindle ConfiguredSerial Encoder InterfaceAxis Name Selected from X,Z and Y,A,B,CSpindle Up to two SpindlesLeast input increment0.001mm, 0.001deg, 0.0001inchIncrement system 1/100.0001mm, 0.0001deg, 0.00001inchFlexible feed gear Optional DMRFine Acc & Dec controlInch/metric conversionInterlock All axes/each axis/each direction/block start/cutting block startMachine lock All axes/each axisEmergency stopOvertravelStored stroke check 1Stored stroke check 2, 3Chuck and tail stock barrierMirror image Each axisFollow-upServo offChamfering on/offBacklash compensationBacklash compensation for each rapid traverse and cutting feedStored pitch error compensationPosition switchOperationAutomatic Data Backup (R641)Automatic operation (memory)DNC operation Reader/puncher interface is required.MDI operationSchedule functionProgram number searchSequence number searchSequence number comparison and stopProgram restartBuffer registerDry runSingle blockJOG feedManual reference position returnReference position setting without DOGReference position setting with mechanical stopperManual handle feed Max. 2 units (requires MPG - order from IOetc Sheet)Manual handle feed ratex1, x10, xm, xn m: 0~127, n: 0~1000Manual handle interruptionIncremental feedx1, x10, x100, x1000Jog and handle simultaneous modeInterpolationPositioning G00 (Linear interpolation type positioning is possible)Linear interpolationCircular interpolation Multi-quadrant is possibleDwell Dwell in secondsDwell per revolution (synchronous cutting function is required.) Polar coordinate interpolationCylindrical interpolationThreading, synchronous cuttingMultiple threadingThreading retractContinuous threadingVariable lead threadingSkip G31Torque limit skipReference position return G28Reference position return check G272nd reference position return3rd/4th reference position returnFeed FunctionRapid traverse rate Max. 240m/min (1μm)Max. 100m/min (0.1μm)Rapid Traverse Feedrate Override preset value, 25%, 50%, 100% settingsFeed per minuteFeed per revolutionTangential speed constant controlCutting feedrate clampAutomatic acceleration/deceleration Rapid traverse: linear; Cutting feed: exponentialRapid traverse bell-shaped acceleration/decelerationLinear acceleration/deceleration after cutting feed interpolationFeedrate override0~254%Jog override0~655.34%Override cancelManual per revolution feedError detectionRapid traverse block overlapExternal decelerationProgrammingTape code EIA RS244/ISO840Label skipParity check Horizontal and vertical parityControl in/outOptional block skip 9 LevelsMax. programmable dimension±8-digitProgram number O4-digitExternal memory and sub program calling functionSequence number N5-digitAbsolute/incremental programming Combined use in the same block Decimal point programming/ pocket calculator type decimal point programmingInput unit 10 time multiplyDiameter/radius programming (X axis)Plane selection G17, G18, G19Rotary axis designationRotary axis roll-overCoordinate system settingAutomatic coordinate system settingCoordinate system shiftDirect input of coordinate system shiftWorkpiece coordinate system G52~G59Workpiece coordinate system presetDirect input of workpiece origin offset value measuredManual absolute on and offDirect drawing dimension programmingG code system A/B/CProgrammable data input G10Sub program call 4 folds nestedCustom macroAddition of custom macro common variables#100~#199, #500~#999Canned cyclesMultiple repetitive cycleCanned cycles for drillingCircular interpolation by R programmingTape format for FANUC Series 10/11Auxiliary and Spindle FunctionsAuxiliary function M8-digitAuxiliary function lockHigh-speed M/S/T/B interfaceMultiple command of auxiliary function3Spindle speed function S5-digit, binary output Spindle serial output S5-digit, serial output Constant surface speed controlSpindle override0~254%Spindle speed fluctuation detection1st spindle orientationSpindle positioningRigid tappingTool Functions and Tool CompensationTool Function T7 + 1/T6 + 2 digitsTool offset pairs±6 digits 64Tool offsetTool nose radius compensationTool geometry/wear compensationTool life managementTool offset value counter inputDirect input of tool offset value measuredPart Program Storage & EditingPart Program Storage512KBNumber of registerable programs400Part program editingProgram protectBackground editingExtended part program editingPassword functionDisplayStatus displayClock functionCurrent position displayProgram comment display Program name 31 charactersParameter setting and displaySelf-diagnosis functionAlarm displayAlarm history displayOperator message history displayOperation history displayHelp functionRun hour and parts count displayActual cutting feedrate displayDisplay of spindle speed and T code on all screensDirectory display of floppy cassetteDirectory display and punch for each groupServo setting screenDisplay of hardware and software configurationPeriodic maintenance screenMaintenance information screenTrouble diagnosisSoftware operator's panelEnglish Language Display, Multiple Languages Selectable Sp,Chi,Por,Rus,Tur,HindiData protection key 4 typesErase CRT screen displayData Input/Output and CommunicationsI/O Link InterfacePunch Panel with 2m Cable A02B-0236-C192 in LCD MountReader/Punch Interface 1 (RS-232)External data input:External tool offset External message External machine zero point shift External key inputExternal program inputExternal workpiece number search9999Expanded external workpiece number searchExternal program number search1~9999Memory card input/output for maintenanceEmbedded EthernetOtherCD-ROM containing Product Manuals included in the BOM of the Root CNC.24V Power Cable44C741911-001CBL +24V M3 TERM-AMP 5M USA Spare Fuses A02B-0236-K100FUSE, CONTROL UNITCable Clamps A02B-0124-K001CABLE CLAMPSGrounding Bar44B295864-001GROUNDING BAR 11 SLOTMiscellaneous Solder Connectors A02B-0120-K324CONNECTOR AND PINSPackage ABasic Func Pkg 5This Form assumes the use of HRV2. If HRV3 servo control is required, please complete 2 Axes, upto 4 supportedthis form as close as possible to your desired configuration, then e-mail the form and A02B-0321-B530yourrequestedchangesto:****************************LCD Mount with 0 SlotsA02B-0319-H174#T200x400mmCNC Express will modify the form per your request and return the form to you.8.4" Color LCD/MDI USB Port Embedded EthernetAutomatic Data Back-up, 3 Sets of Back-up Data, SRAM + PPS R641 Auto Data BackupPMC/L for 0ί-D 5K StepsApprox 1280m PPSUSB Memory Input/Output is available on LCD Mount Controls.HRV3 servo controlPMC/L for 0ί-D 8K StepsPMC/L for 0ί-D 24K StepShading indicates restrictions, see Package Options for detailsSERIES 0ί-TD Mate PACKAGE CHOICES0ί-TDMaterequires at leastVersion 5.7 of FANUC Ladder III PACKAGE DEPENDENT OPTIONSORDER FORMSeries 0ί-TD Mate CNC Express Package A 8.4" Color LCD Mount Pick One PMC Options-PMC/L for 0ί-D 8K Steps (R002#8K)PMC/L for 0ί-D 24K Steps (R002#24K)Options3rd Servo Axis Interface (R419#3)4th Servo Axis Interface (R419#4), Controllable Axes Expand(R689), increase controllable axes to 5.Simultaneous Controllable Axis Expansion - Allows 4 axes to be controlled simultaneously. (J803)5th Servo Axis Interface (R419#5)Spindle Axes Expansion (R604) - Allows up to 2 Spindles, 2 Serial or 1 Serial & 1 Analog.Analog Spindle Interface required for Analog Spindle. Axis Count + Spindles must be <= 6.Analog Spindle Interface. (Serial Spindle Interface Standard). See Drives Tab for Spindle Encoder.Axis Control by PMC (J804)Extended PMC ladder instruction function (R851)Function Block function (R852)Multi Language PMC Message 128K (S977#128K)Dynamic Graphic Display (J973)(enhanced tool path plotting, preview cutting path)Grinding Function A (S682)(includes multi-step skip and canned cycles for grinding)Grinding Function B (S683) incl's Angular Axis Control and Grinding Function A features.Multi-step skip (J849)Manual Guide 0ίManual Guide 0ί(S772)Macro Executor Related Options - require Development Tools. (See Tools Page)Macro Executor (J888) Requires Custom SW size. System SW reserves 96KB.Macro Executor & C-lang Executor (J734) Req's >= 2MB Custom SW. System SW reserves 700KB.FANUC PICTURE Executor (R644) Requires >=3MB Custom SW size. System SW reserves 2MB.Custom SW size 512KB. (J738#512K) (J888)Custom SW size 4MB. (J738#4M)Flash CardCompact Flash Card Kit 128MB0I/O unit for 0iI/O unit for 0i-D This is compatible with the DI/DO I/F of I/O card of Series 0i-B. DI/DO : 96/64 pts.See the IOetc page for the available I/O Link signal cables.Analog Servo InterfaceAnalog Servo Inf for 2 axes Incl's Analog Inf Module, Conn's & Fuse - Req F/O cbl on 230V DrivesAnalog Servo Interface for 3rd axis Includes Analog Interface Module, Ribbon Cable & Connector'sAnalog Servo Interface for 4th axis Includes ConnectorsAnalog Servo Inf for 5th axis Incl's Analog Inf Module, Conn's & Fuse - Req F/O cbl on 230V DrivesRequired Fiber Optic Command Cable is ordered on the 230V Drives tab.Enter Analog Quote Number:See Sales Engineer for Quote Number.Product Manuals The Operator's, Parameter and Maintenance manuals, (marked with an "*")Series 0ί-D, 0ί-D Mate Description Manual, B-64302EN0Series 0ί-D, 0ί-D Mate Conn H/W Manual, B-64303EN0Series 0ί-D, 0ί-D Mate Conn Func Manual, B-64303EN-10Series 0ί-D, 0ί-D Mate Maintenance Manual *, B-64305EN0Series 0ί-D, 0ί-D Mate Parameter Manual * B-64310EN0Series 0ί-MD Mate Operator's Manuals *, Common and Lathe specific, B-64304EN & -10This Manual is NOT included on any CD. A complimentary copy is shipped with the CNC.Extra hard-copy manuals, if required, may be ordered here.Series 0i-D Operation & Maintenance Handbook, B-64307EN 0Check here if no I/O is needed.Check here if I/O has already been purchased。

W78E58中文

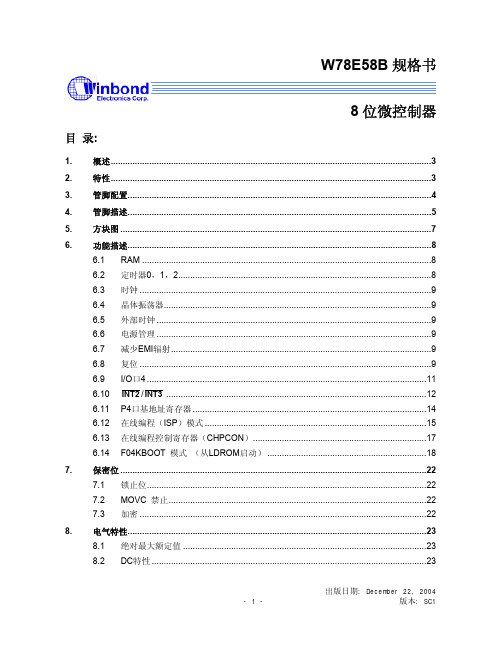

W78E58B规格书8位微控制器目录:1.概述 (3)2.特性 (3)3.管脚配置 (4)4.管脚描述 (5)5.方块图 (7)6.功能描述 (8)6.1 RAM (8)6.2 定时器0,1,2 (8)6.3 时钟 (9)6.4 晶体振荡器 (9)6.5 外部时钟 (9)6.6 电源管理 (9)6.7 减少EMI辐射 (9)6.8 复位 (9)6.9 I/O口4 (11)6.10 INT2/INT3 (12)6.11 P4口基地址寄存器 (14)6.12 在线编程(ISP)模式 (15)6.13 在线编程控制寄存器(CHPCON) (17)6.14 F04KBOOT 模式(从LDROM启动) (18)7.保密位 (22)7.1 锁止位 (22)禁止 (22)7.2 MOVC7.3 加密 (22)8.电气特性 (23)8.1 绝对最大额定值 (23)8.2 DC特性 (23)出版日期: December 22, 20048.3 AC特性 (25)8.3.1时钟输入波形 (25)8.3.2程序读取周期 (26)8.3.3数据读取周期 (26)8.3.4数据写周期 (27)8.3.5端口访问周期 (27)9.时序波形图 (28)9.1 程序读取周期 (28)9.2 数据读周期 (28)9.3 数据写周期 (29)9.4 端口访问周期 (29)10.典型应用电路 (30)10.1 扩展的外部程序存储器和石英晶体 (30)10.2 扩展的外部程序存储器和振荡器 (31)11.封装尺寸 (32)11.1 DIP40 (32)11.2 44 管脚PLCC (33)11.3 44 管脚PQFP (34)12.应用指南 (35)12.1 ISP 软件编程示例: (35)13.文件版本描述 (42)1. 概述W78E58B是具有带ISP功能的Flash EPROM的低功耗8位微控制器;ISP功能的Flash EPROM可用于固件升级。

常用三极管参数大全

玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理。

SAMSUNG SDRAM 64Mb H-die (x4, x8, x16) 数据手册

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAM64Mb H-die SDRAM Specification54 TSOP-II with Pb-Free(RoHS compliant)Revision 1.3August 2004* Samsung Electronics reserves the right to change products or specification without notice.Rev. 1.3 August 2004SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAM Revision HistoryRevision 1.0 (September, 2003)• FinalizedRevision 1.1 (October, 2003)Deleted speed -7C and AC parameter notes 5.Revision 1.2 (May, 2004)• Added Note 5. sentense of tRDL parameterRevision 1.3 (August, 2004)• Corrected typo.Rev. 1.3 August 2004SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004Part No.Orgainization Max Freq.InterfacePackageK4S640432H-UC(L)7516Mb x 4 133MHz(CL=3)LVTTL54pin TSOP(II)K4S640832H-UC(L)758Mb x 8133MHz(CL=3) K4S641632H-UC(L)604Mb x 16166MHz(CL=3) K4S641632H-UC(L)70143MHz(CL=3) K4S641632H-UC(L)75133MHz(CL=3)The K4S640432H / K4S640832H / K4S641632H is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 4,194,304 words by 4 bits, / 4 x 2,097,152 words by 8 bits, / 4 x 1,048,576 words by 16 bits, fabricated with SAMSUNG ′s high perfor-mance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.• JEDEC standard 3.3V power supply• LVTTL compatible with multiplexed address • Four banks operation• MRS cycle with address key programs -. CAS latency (2 & 3)-. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave)• All inputs are sampled at the positive going edge of the system clock• Burst read single-bit write operation• DQM (x4,x8) & L(U)DQM (x16) for masking • Auto & self refresh• 64ms refresh period (4K cycle)• Pb-free Package• RoHS compliantGENERAL DESCRIPTIONFEATURESOrdering Information4M x 4Bit x 4 / 2M x 8Bit x 4 / 1M x 16Bit x 4 Banks Synchronous DRAMRow & Column address configurationOrganizationRow Address Column Address16Mx4A0~A11A0-A98Mx8A0~A11A0-A84Mx16A0~A11A0-A7SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAM Package Physical Dimension54Pin TSOP(II) Package DimensionRev. 1.3 August 2004SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004LWE LDQMDQiSamsung Electronics reserves the right to change products or specification without notice.*SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004123456789101112131415161718192021222324252627545352515049484746454443424140393837363534333231302928PIN CONFIGURATION (Top view)54Pin TSOP (II)(400mil x 875mil)(0.8 mm Pin pitch)PIN FUNCTION DESCRIPTIONPin NameInput FunctionCLK System clock Active on the positive going edge to sample all inputs.CSChip selectDisables or enables device operation by masking or enabling all inputs except CLK, CKE and DQMCKE Clock enableMasks system clock to freeze operation from the next clock cycle.CKE should be enabled at least one cycle prior to new command.Disable input buffers for power down in standby.A 0 ~ A 11AddressRow/column addresses are multiplexed on the same pins.Row address : RA 0 ~ RA 11,Column address : (x4 : CA 0 ~ CA 9, x8 : CA 0 ~ CA 8 , x16 : CA 0 ~ CA 7)BA 0 ~ BA 1Bank select address Selects bank to be activated during row address latch time.Selects bank for read/write during column address latch time.RAS Row address strobe Latches row addresses on the positive going edge of the CLK with RAS low.Enables row access & precharge.CAS Column address strobe Latches column addresses on the positive going edge of the CLK with CAS low.Enables column access.WE Write enableEnables write operation and row tches data in starting from CAS, WE active.DQM Data input/output mask Makes data output Hi-Z, t SHZ after the clock and masks the output.Blocks data input when DQM active.DQ 0 ~ X15Data input/output Data inputs/outputs are multiplexed on the same pins.V DD /V SS Power supply/ground Power and ground for the input buffers and the core logic.V DDQ /V SSQ Data output power/ground Isolated power supply and ground for the output buffers to provide improved noise immunity.N.C/RFUNo connection/reserved for future useThis pin is recommended to be left No Connection on the device.x16x8x4x16x8x4V DD DQ0V DDQ DQ1DQ2V SSQ DQ3DQ4V DDQ DQ5DQ6V SSQ DQ7V DD LDQM WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ15V SSQ DQ14DQ13V DDQ DQ12DQ11V SSQ DQ10DQ9V DDQ DQ8V SSN.C/RFU UDQM CLK CKE N.C A11A9A8A7A6A5A4V SSV DDN.C V DDQ N.C DQ0V SSQ N.C N.C V DDQ N.C DQ1V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/APA0A1A2A3V DDV SS N.C V SSQ N.C DQ3V DDQ N.C N.C V SSQ N.C DQ2V DDQ N.C V SSN.C/RFU DQM CLK CKE N.C A11A9A8A7A6A5A4V SSV DD DQ0V DDQ N.C DQ1V SSQ N.C DQ2V DDQ N.C DQ3V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ7V SSQ N.C DQ6V DDQ N.C DQ5V SSQ N.C DQ4V DDQ N.C V SSN.C/RFU DQM CLK CKE N.C A11A9A8A7A6A5A4V SSSDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004ABSOLUTE MAXIMUM RATINGSParameter Symbol Value Unit Voltage on any pin relative to V SS V IN , V OUT -1.0 ~ 4.6V Voltage on V DD supply relative to V SS V DD , V DDQ-1.0 ~ 4.6V Storage temperature T STG -55 ~ +150°C Power dissipation P D 1W Short circuit currentI OS50mAPermanent device damage may occur if "ASOLUTE MAXIMUM RATINGS" are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.Note :DC OPERATING CONDITIONSRecommended operating conditions (Voltage referenced to V SS = 0V, T A = 0 to 70°C)Parameter Symbol Min Typ Max Unit NoteSupply voltage V DD , V DDQ3.0 3.3 3.6V Input logic high voltage V IH 2.0 3.0V DD +0.3V 1Input logic low voltage V IL -0.300.8V 2Output logic high voltage V OH 2.4--V I OH = -2mA Output logic low voltage V OL --0.4V I OL = 2mAInput leakage currentI LI-10-10uA31. V IH (max) = 5.6V AC.The overshoot voltage duration is ≤ 3ns.2. V IL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.3. Any input 0V ≤ V IN ≤ V DDQ .Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.Notes :CAPACITANCE (V DD = 3.3V, T A = 23°C, f = 1MHz, V REF =1.4V ± 200 mV)PinSymbol Min Max Unit Note ClockC CLK 2.5 4.0pF 1RAS, CAS, WE, CS, CKE, DQM C IN 2.5 5.0pF 2Address C ADD 2.5 5.0pF 2DQ 0 ~ DQ 3C OUT4.06.5pF31. -75 only specify a maximum value of 3.5pF2. -75 only specify a maximum value of3.8pF 3. -75 only specify a maximum value of 6.0pFNotes :SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 20041. Measured with outputs open.2. Refresh period is 64ms.3. K4S6404(08)32H-TC**4. K4S6404(08)32H-TL**5. Unless otherwise noted, input swing IeveI is CMOS(V IH /V IL =V DDQ /V SSQ)Notes :(Recommended operating condition unless otherwise noted, T A = 0 to 70°C for x4, x8)ParameterSymbolTest ConditionVersion Unit Note75Operating current (One bank active)I CC1 Burst length = 1 t RC ≥ t RC (min) I O = 0 mA75mA 1Precharge standby current in power-down modeI CC2P CKE ≤ V IL (max), t CC = 10ns 1mAI CC2PS CKE & CLK ≤ V IL (max), t CC = ∞1Precharge standby current in non power-down mode I CC2NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns15mAI CC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 6Active standby current in power-down mode I CC3P CKE ≤ V IL (max), t CC = 10ns 3mAI CC3PS CKE & CLK ≤ V IL (max), t CC = ∞3Active standby current in non power-down mode (One bank active)I CC3NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns30mAI CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25Operating current (Burst mode)I CC4 I O = 0 mA Page burst4Banks Activated t CCD = 2CLKs 115mA 1Refresh current I CC5t RC ≥ t RC (min)135mA 2Self refresh currentI CC6CKE ≤ 0.2VC 1mA 3L400uA4DC CHARACTERISTICSSDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 20041. Measured with outputs open.2. Refresh period is 64ms.3. K4S641632H-TC**4. K4S641632H-TL**5. Unless otherwise noted, input swing IeveI is CMOS(V IH /V IL =V DDQ /V SSQ)Notes :DC CHARACTERISTICS(Recommended operating condition unless otherwise noted, T A = 0 to 70°C for x16 only)ParameterSymbolTest ConditionVersionUnit Note607075Operating current (One bank active)I CC1 Burst length = 1 t RC ≥ t RC (min) I O = 0 mA140115110mA 1Precharge standby current in power-down modeI CC2P CKE ≤ V IL (max), t CC = 10ns 1mAI CC2PS CKE & CLK ≤ V IL (max), t CC = ∞1Precharge standby current in non power-down mode I CC2NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns15mAI CC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 6Active standby current in power-down mode I CC3P CKE ≤ V IL (max), t CC = 10ns 3mAI CC3PS CKE & CLK ≤ V IL (max), t CC = ∞3Active standby current in non power-down mode (One bank active)I CC3NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns30mAI CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25Operating current (Burst mode)I CC4 I O = 0 mA Page burst4Banks Activated t CCD = 2CLKs 160140135mA 1Refresh current I CC5t RC ≥ t RC (min)160140135mA 2Self refresh currentI CC6CKE ≤ 0.2VC 1mA 3L400uA4SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004AC OPERATING TEST CONDITIONS (V DD = 3.3V ± 0.3V, T A = 0 to 70°C)Parameter Value Unit AC input levels (Vih/Vil)2.4/0.4V Input timing measurement reference level 1.4V Input rise and fall timetr/tf = 1/1ns Output timing measurement reference level 1.4VOutput load conditionSee Fig. 23.3V1200Ω870ΩOutput30pFV OH (DC) = 2.4V, I OH = -2mA V OL (DC) = 0.4V, I OL = 2mAVtt = 1.4V50ΩOutput30pFZ0 = 50Ω(Fig. 2) AC output load circuit(Fig. 1) DC output load circuit Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle timeand then rounding off to the next higher integer.2. Minimum delay is required to complete write.3. All parts allow every cycle column address change.4. In case of row precharge interrupt, auto precharge and read burst stop.5. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported. SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP .OPERATING AC PARAMETER(AC operating conditions unless otherwise noted)ParameterSymbol VersionUnit Note 607075Row active to row active delay t RRD (min)121415ns 1RAS to CAS delay t RCD (min)182020ns 1Row precharge time t RP (min)182020ns 1Row active time t RAS (min)424945ns 1t RAS (max)100us Row cycle timet RC (min)606865ns 1Last data in to row precharge t RDL (min)2CLK 2,5Last data in to Active delayt DAL (min) 2 CLK + tRP-5Last data in to new col. address delay t CDL (min)1CLK 2Last data in to burst stopt BDL (min)1CLK 2Col. address to col. address delay t CCD (min)1CLK 3Number of valid output dataCAS latency = 32ea4CAS latency = 21SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 20041. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf) = 1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.Notes :DQ BUFFER OUTPUT DRIVE CHARACTERISTICSParameterSymbol Condition Min TypMax Unit Notes Output rise time trh Measure in linear region : 1.2V ~ 1.8V 1.37 4.37Volts/ns 3 Output fall time tfh Measure in linear region : 1.2V ~ 1.8V 1.30 3.8Volts/ns 3 Output rise time trh Measure in linear region : 1.2V ~ 1.8V 2.8 3.9 5.6Volts/ns 1,2 Output fall timetfhMeasure in linear region : 1.2V ~ 1.8V2.02.9 5.0Volts/ns1,21. Rise time specification based on 0pF + 50 Ω to V SS , use these values to design to.2. Fall time specification based on 0pF + 50 Ω to V DD , use these values to design to.3. Measured into 50pF only, use these values to characterize to.4. All measurements done with respect to V SS .Notes :AC CHARACTERISTICS (AC operating conditions unless otherwise noted)ParameterSymbol607075Unit NoteMin Max Min Max Min Max CLK cycle time CAS latency=3t CC 61000710007.51000ns 1CAS latency=2--10CLK to valid output delay CAS latency=3t SAC 56 5.4ns 1,2CAS latency=2--6Output data hold timeCAS latency=3t OH 2.533ns 2CAS latency=2--3CLK high pulse width t CH 2.53 2.5ns 3CLK low pulse width t CL 2.53 2.5ns 3Input setup time t SS 1.52 1.5ns 3Input hold time t SH 110.8ns 3CLK to output in Low-Z t SLZ111ns2CLK to output in Hi-ZCAS latency=3t SHZ56 5.4nsCAS latency=2--6SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004I OH Characteristics (Pull-up)Voltage 133MHz Min 133MHz Max (V)I (mA)I (mA)3.45- -1.683.30- -19.113.00-0.35 -51.872.70-3.75-90.442.50-6.65-107.311.95-13.75-137.91.80-17.75-158.341.65-20.55-173.61.50-23.55-188.791.40-26.2-199.011.00-36.25-241.150.20-46.5-351.68IBIS SPECIFICATIONI OL Characteristics (Pull-down)Voltage 133MHz Min 133MHz Max (V)I (mA)I (mA)3.4543.92155.823.30--3.0043.36153.721.9541.20148.401.8040.56146.021.6539.60141.751.5038.40136.081.4037.28131.391.0030.08105.840.8526.6493.660.6521.5275.250.4014.1649.140-100-200-300-400-500-600030.511.522.53.5Voltagem A250200150100500030.511.522.53.5Voltagem A133MHz Pull-up133MHz Pull-downI OH Min (133MHz)I OH Max (133MHz)I OL Min (133MHz)I OL Max (133MHz)SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004V DD Clamp @ CLK, CKE, CS, DQM & DQV DD (V)I (mA)0.00.00.20.00.40.00.60.00.70.00.80.00.90.01.0 0.231.2 1.341.4 3.021.6 5.061.8 7.352.0 9.832.212.482.415.302.618.31V SS Clamp @ CLK, CKE, CS, DQM & DQV SS (V)I (mA)-2.6-57.23-2.4-45.77-2.2-38.26-2.0-31.22-1.8-24.58-1.6-18.37-1.4-12.56-1.2 -7.57-1.0 -3.37-0.9 -1.75-0.8 -0.58-0.7 -0.05-0.6 0.0-0.4 0.0-0.2 0.0 0.00.0201510500312Voltagem AI (mA)Voltagem AI (mA)Minimum V DD clamp current(Referenced to V DD )Minimum V SS clamp current0-10-20-30-40-30-2-1-50-60SDRAM 64Mb H-die (x4, x8, x16)CMOS SDRAMRev. 1.3 August 2004SIMPLIFIED TRUTH TABLE (V=Valid, X=Don ′t care, H=Logic high, L=Logic low)CommandCKEn-1CKEnCSRASCASWEDQMBA 0,1A 10/APA 11,A 9 ~ A 0NoteRegisterMode register set H X L L L L X OP code1,2RefreshAuto refreshH H L L L H X X 3Self refreshEntry L 3ExitL H L H H H X X3H X X X 3Bank active & row addr.H X L L H H X V Row address Read &column address Auto precharge disable H X L H L H X V L Column address 4Auto precharge enable H 4,5Write &column address Auto precharge disable H X L H L L X VL Column address4Auto precharge enableH 4,5Burst stop HX L H H L X X 6Precharge Bank selection H X L L H L X V L XAll banksX H Clock suspend or active power downEntry H L H X X X X XL V V V Exit L H X X X X X Precharge power down modeEntryH L H X X X XXL H H H ExitL HH X X X X L V V V DQMH X V X 7No operation commandHXH X X X XXLHHH1. OP Code : Operand codeA 0 ~ A 11 & BA 0 ~ BA 1 : Program keys. (@ MRS)2. MRS can be issued only at all banks precharge state.A new command can be issued after 2 CLK cycles of MRS.3. Auto refresh functions are as same as CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto". Auto/self refresh can be issued only at all banks precharge state.4. BA 0 ~ BA 1 : Bank select addresses.If both BA 0 and BA 1 are "Low" at read, write, row active and precharge, bank A is selected.If both BA 0 is "Low" and BA 1 is "High" at read, write, row active and precharge, bank B is selected. If both BA 0 is "High" and BA 1 is "Low" at read, write, row active and precharge, bank C is selected. If both BA 0 and BA 1 are "High" at read, write, row active and precharge, bank D is selected. If A 10/AP is "High" at row precharge, BA 0 and BA 1 is ignored and all banks are selected.5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst.New row active of the associated bank can be issued at t RP after the end of burst.6. Burst stop command is valid at every burst length.7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0), but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)Notes :。

EDL6416CABH-10-E资料

64M bits Mobile RAM

EDL6416CABH (4M words × 16 bits)

Description

The EDL6416CABH is a 64M bits Mobile RAM organized as 1,048,576 words × 16 bits × 4 banks. The Mobile RAM achieved low power consumption and high-speed data transfer using the pipeline architecture. All inputs and outputs are synchronized with the positive edge of the clock. This product is packaged in 54-ball FBGA.

Document No. E0422E30 (Ver. 3.0) Date Published April 2004 (K) Japan URL: Elpida Memory, Inc. 2003-2004

EDL6416CABH

Ordering Information

(Top view)

A0 to A11 BA0, BA1 DQ0 to DQ15 CLK CKE /CS /RAS /CAS /WE UDQM LDQM VDD VSS VDDQ VSSQ NC

Address inputs Bank select Data inputs/ outputs Clock input Clock enable Chip select Row address strobe Column address strobe Write enable Upper DQ mask enable Lower DQ mask enable Power supply Ground Power supply for DQ Ground for DQ No connection

MEMORY存储芯片TMS320C6416TGLZA8中文规格书

TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005DEVICE CONFIGURATIONSThe C6414, C6415, and C6416 peripheral selections and other device configurations are determined by external pullup/pulldown resistors on the following pins (all of which are latched during device reset):D peripherals selection (C6415 and C6416 devices)−BEA11 (UTOPIA_EN)−PCI_EN (for C6415 or C6416, see Table 27 footnotes)−MCBSP2_EN (for C6415 or C6416, see Table 27 footnotes)The C6414 device does not support the PCI and UTOPIA peripherals; for proper operation of the C6414 device, do not oppose the internal pulldowns (IPDs) on the BEA11, PCI_EN, and MCBSP2_EN pins. (For IPUs/IPDs on pins, see the Terminal Functions table of this data sheet.)D other device configurations (C64x)−BEA[20:13, 7]−HD5peripherals selectionSome C6415/C6416 peripherals share the same pins (internally muxed) and are mutually exclusive (i.e., HPI, general-purpose input/output pins GP[15:9], PCI and its internal EEPROM, McBSP1, McBSP2, and UTOPIA).The VCP/TCP coprocessors (C6416 only) and other C64x peripherals (i.e., the Timers, McBSP0, and the GP[8:0] pins), are always available.D UTOPIA and McBSP1 peripheralsThe UTOPIA_EN pin (BEA11) is latched at reset. For C6415 and C6416 devices, this pin selects whether the UTOPIA peripheral or McBSP1 peripheral is functionally enabled (see Table 26).The C6414 device does not support the UTOPIA peripheral; for proper device operation, do not oppose the internal pulldown (IPD) on the BEA11 pin.Table 26. UTOPIA_EN Peripheral Selection (McBSP1 and UTOPIA) (C6415/C6416 Only) PERIPHERAL SELECTION PERIPHERALS SELECTEDUTOPIA_EN(BEA11) Pin [D16]UTOPIA McBSP1DESCRIPTION0√McBSP1 is enabled and UTOPIA is disabled [default].This means all multiplexed McBSP1/UTOPIA pins function as McBSP1 and all other standalone UTOPIA pins are tied-off (Hi-Z).1√UTOPIA is enabled and McBSP1 is disabled.This means all multiplexed McBSP1/UTOPIA pins now function as UTOPIA and all other standalone McBSP1 pins are tied-off (Hi-Z).D HPI, GP[15:9], PCI, EEPROM (internal to PCI), and McBSP2 peripheralsThe PCI_EN and MCBSP2_EN pins are latched at reset. They determine specific peripheral selection for the C6415 and C6416 devices, summarized in Table 27.The C6414 device does not support the PCI peripheral; for proper device operation, do not oppose the internal pulldowns (IPDs) on the PCI_EN and MCBSP2_EN pins.TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005DEVICE CONFIGURATIONS (CONTINUED)Table 28. Device Configuration Pins (BEA[20:13, 9:7], HD5, and BEA11)CONFIGURATIONPIN NO.FUNCTIONAL DESCRIPTIONBEA20E16Device Endian mode (LEND)0–System operates in Big Endian mode1−System operates in Little Endian mode (default)BEA[19:18][D18,C18]Bootmode [1:0]00–No boot01−HPI boot10−EMIFB 8-bit ROM boot with default timings (default mode)11−ReservedBEA[17:16][B18,A18]EMIFA input clock selectClock mode select for EMIFA (AECLKIN_SEL[1:0])00–AECLKIN (default mode)01−CPU/4 Clock Rate10−CPU/6 Clock Rate11−ReservedBEA[15:14][D17,C17]EMIFB input clock selectClock mode select for EMIFB (BECLKIN_SEL[1:0])00–BECLKIN (default mode)01−CPU/4 Clock Rate10−CPU/6 Clock Rate11−ReservedBEA13B17PCI EEPROM Auto-Initialization (EEAI) [C6415 and C6416 devices only][The C6414 device does not support the PCI peripheral; for proper device operation, do not oppose the internal pulldown (IPD) on the BEA13 pin.]PCI auto-initialization via external EEPROM0−PCI auto-initialization through EEPROM is disabled; the PCI peripheral uses the specified PCI default values (default).1−PCI auto-initialization through EEPROM is enabled; the PCI peripheral is configured through EEPROM provided the PCI peripheral pin is enabled (PCI_EN = 1) and theMcBSP2 peripheral pin is disabled (MCBSP2_EN = 0).Note: If the PCI peripheral is disabled (PCI_EN pin = 0), this pin must not be pulled up.For more information on the PCI EEPROM default values, see the TMS320C6000 DSP Peripheral Component Interconnect (PCI) Reference Guide (literature number SPRU581).BEA11D16UTOPIA Enable (UTOPIA_EN) [C6415 and C6416 devices only][The C6414 device does not support the UTOPIA peripheral; for proper device operation, do not oppose the internal pulldown (IPD) on the BEA11 pin.]UTOPIA peripheral enable (functional)0−UTOPIA peripheral disabled (McBSP1 functions are enabled). [default]This means all multiplexed McBSP1/UTOPIA pins function as McBSP1 and all otherstandalone UTOPIA pins are tied-off (Hi-Z).1−UTOPIA peripheral enabled (McBSP1 functions are disabled).This means all multiplexed McBSP1/UTOPIA pins now function as UTOPIA and all otherstandalone McBSP1 pins are tied-off (Hi-Z).。

DAM6416P说明书

DAM6416P图像处理平台用户使用手册V1.0闻亭科技发展有限责任公司2003年9月目录1 简介 (8)1.1 可支持的视频格式 (8)1.2 可支持音频格式 (8)1.3 工作方式 (8)1.4 通信接口 (8)1.5 DAM6416P外形图 (9)1.6 DAM6416P机械安装图 (9)2 DAM6416P图像处理平台硬件指标 (10)2.1 总体性能指标 (10)2.2 各模块性能指标 (10)3DAM6416P图像处理平台硬件结构 (12)3.1 综述 (12)3.1.1 DAM6416P功能模块构成 (12)3.1.2DAM6416P接口结构框图 (13)3.2 DSP处理器模块 (13)3.2.1DSP处理器简介 (13)23.2.2DSP处理器模块框图 (14)3.2.3DSP多通道串口使用 (14)3.2.4DSP外部寄存器扩展 (14)3.2.5DAM6416P的复位和引导 (16)3.2.6Flash的使用 (16)3.3 A/V接口模块 (17)3.3.1视频模块功能 (17)3.3.2视频模块框图 (18)3.3.3视频捕捉 (18)3.3.4视频产生 (18)3.3.5SVGA输出 (19)3.3.6音频信号的输入和输出 (19)3.3.7音视频接口盒 (20)3.4 通信接口模块 (20)3.4.1RS232(UART) (20)3.4.2RS422 (21)3.5 扩展接口模块 (21)3.5.1高速接口 (21)3.5.2交叉平台子板接口 (22)3.5.3UTOPIA接口 (22)3.6 主机接口 (23)3.7 电源模块 (23)3.8 LED模块 (23)4 软件支持开发环境 (23)4.1 开发板支持库 (23)4.1.1IEKSDK库和驱动 (23)34.1.2IEKLIB库 (24)4.1.3IEKC64.cdb (24)4.2 应用示例 (25)4.2.1应用IEKSDK库和驱动的开发例程 (25)4.2.2应用IEKLIB库的开发例程 (25)5DAM6416P硬件设置 (25)5.1 DSP引导模式设置 (25)5.2 EMIF时钟设置 (26)5.3 PCI模式设置 (26)设置 (26)5.4 UTOPIA/MCBSP#15.5 E NDIANESS 模式设置 (27)6DAM6416P接口 (27)6.1 DAM6416P接口位置图示 (27)6.2 RS422接口(J6)(选项) (27)6.2.1插件标号和类型 (27)6.2.2FTSH-110-04-F-D-RA插件图 (28)6.2.3422接口定义表 (28)6.3 RS232接口 (29)6.3.1RS232接口图 (29)6.3.2RS232接口定义表 (29)6.4 C ROSS P LATFORM I NTERFACE(J10/J11) (29)6.4.1扩展子板接口标准 (29)46.4.2交叉平台扩展子板安装图 (30)6.4.3插件标号和类型 (30)6.4.4SFM-140-L3-S-D-A插件图 (30)6.4.5J10接口定义表 (31)6.4.6J11接口定义表 (32)6.4.7TFM-140-32-S-D-A插件图 (33)6.5 UTOPIA接口(J12)(选项) (34)6.5.1UTOPIA接口标号和类型 (34)6.5.2SFM-115-L3-S-D-A插件图 (34)6.5.3J12接口定义表 (35)6.5.4TFM-115-32-S-D-A接口图 (35)6.6 FAST-PORT A 子板接口(J2)(选项) (35)6.6.1FAST-PORT A 子板接口标号和插件类型 (35)6.6.2SFM-140-L3-S-D-A插件图 (36)6.6.3J2接口定义表 (36)6.7 FAST-PORT A LINK接口(J1)(选项) (37)6.7.1FAST-PORT A LINK接口标号和类型 (37)6.7.2FTSH-130-04-G-D-RA插件图 (38)6.7.3J1接口定义表 (38)6.7.4CLP-130-02-F-D插件图 (39)6.8 FAST-PORT B 子板接口(J4)(选项) (40)6.8.1FAST-PORT B 子板接口标号和插件类型 (40)6.8.2SFM-140-L3-S-D-A插件图 (40)6.8.3J4接口定义表 (40)6.9FAST-PORT B LINK接口(J3)(选项)..416.9.1FAST-PORT B LINK接口标号和类型 (41)6.9.2FTSH-130-04-G-D-RA插件图 (42)6.9.3J3接口定义表 (42)6.9.4CLP-130-02-F-D插件图 (43)6.10 JTAG 接口(J7) (43)56.10.1JTAG接口图示 (43)6.10.2J7接口定义表 (43)6.11 AV接口(J5) (44)6.11.1AV接口图示 (44)6.11.2J5接口定义表 (44)6.12 SVGA接口(J9) (45)6.12.1SVGA接口图示 (45)6.12.2J9接口定义表 (45)6敬告用户欢迎您成为闻亭公司的用户,在未阅读此敬告前请勿使用我公司产品。

GU641B

28 自定义开关量输入 4

29 自定义开关量输入 5

30 磁力传感器信号{+}

开关输入信号公共端

31

与磁力传感器信号{-}

32 工作电源正极{+B} 33 工作电源负极{-B} 34 接地保护

0-346Vac 0-346Vac 0-346Vac

信号类

0-346Vac 0-346Vac 0-346Vac

LCD 能同时显示三行的数据信息,LCD 的背光功能,令操作者在白天或黑夜等任何时候都能清楚看 到信息,按任意键后一定时间会自动关闭背光。

液晶(LCD)显示及其控制键为操作者提供一个友好操作界面,方便操作者读取信息和设定运行参 数。

操作按键和 LED

功能描述

翻页键 翻页信息显示/连续按此键 2 秒进入/退出参数设置菜单。

手动模式键/指示灯/参数设置减少“-”键 此键用于手动操作模式设置,控制器运行于手动模式时,键上侧 LED 指示灯 亮。控制器通过“START”和“STOP”键来控制发电机启动运行与停止。 当进入参数设置操作,此键用于减少数值/向上移动选择。

测试模式键/指示灯/参数设置确认“√”键 此键用于测试操作模式设置,控制器运行于测试模式时,键上侧 LED 指示灯 亮。此时控制器模拟市电故障且“遥开信号”有效,来控制发电机启动运 行。 当进入参数设置操作,此键用于进入下一层子菜单/确认修改。

注意: z 以上控制程序的实现,是将其中一个可定义输入口定义为市电开关闭合,并将开

关的常开辅助触点连接到该端口。 z 实际应用中,可能没有一个可定义输入口定义为市电开关闭合,此时,市电供电

指示灯亮只表示控制器的市电合闸继电器闭合输出。在这种情况下,市电合闸失 败功能失效,并由此而启动运行发电机组的功能无效。

戴尔 Presario 系列电脑系统板组装备件配置代码和跳变器设置说明书

SystemBoards Assembly Spare Part SystemCnfig Code486SX/25003431-001003431-002160018-001Presario 625Presario CDSHGSHGT486SX/33003434-001003434-002160420-001Presario 633,Presario CDSHGU, HJDHHY, HJD486SX2/66003876-001164912-001Presario 660HJE486SX2/50003858-001164857-001Presario 650HKNJumper Settings (System Board 003431, 003434, 003858, 003876)Jumper Function Pins FunctionP5, P6On-board Video Select1,2 *EnabledNo jumpers DisabledP7Processor Select1,2Nonsocketed Enabled2,3Nonsocketed DisabledNo header SocketedP8Processor Speed1,233-MHz Processor Bus Select2,325-MHz Processor Bus P9 1, 2Processor Configuration1,2486DX/DX2, 486SX(nonsocketed),487SX/OD, 486SX22,3486SX (socketed)P10 1, 2Processor Configuration1,2486SX (nonsocketed)and 486SX(socketed)2,3486DX/DX2,487SX/OD, and486SX2P11 2Processor Configuration1,2486DX/DX2,486SX22,3487SX/OD3,4486SX (nonsocketed)and 486SX(socketed)P13ConfigurationResistors of Super I/O Chip 1,2 *No jumper26Eh/26Fh398h/399hP14Clear CMOS1,2Remove jumper for 10seconds to clear setup * Default.1 Headers not installed on 486/33 models.2 Headers not installed on 486/50 and 486/66 models. Configuration set by0-ohm resistors.Microprocessors Spare Part System486DX2/50163661-001Option486DX2/66194395-001OptionMemory Boards Assembly Spare Part System1 MB Memory Module118666-004141752-001Option2 MB Memory Module118667-004141753-001Option4 MB Memory Module137854-002141754-001Option8 MB Memory Module137853-002141755-001Option16 MB Memory Module137143-003149947-001Option Miscellaneous Internal Assembly Spare Part SystemBackplane (4-slot)002927143342-001AllController Boards Assembly Spare Part SystemFax/Data Modem **141605-001141607-001All except Presario650, 660, 633 CDS Serial/Parallel Interface *000990106886-001OptionEthernet 16 TP Controller003086147220-001OptionToken Ring Controller160782-001142836-001Option6260 SCSI-2 Controller *004004146993-001OptionQVision 1024/i Controller *002948148866-001OptionQVision 1280/i Controller *002951139182-001OptionData/Fax/Voice Modem003697164423-001Presario 650, 660,633 CDSSound Board, PAS-16 *160921-001160919-001Presario 625, CDS Sound Board, SB-16 *197492-001197493-001Presario 633, CDS * See Volume 2 Appendix, Multiproduct Boards, for settings.** See Volume 2 Appendix, Modem Configuration Information.Hard DrivesSize Type Inter-leaveInte-grated Spare Part System120 MB, IDE501:1Y143316-001Model 120200 MB, IDE511:1Y160702-001Model 200240 MB, IDE11:1Y143332-001Model 240270 MB, IDE65/661:1Y197441-001Option340 MB, IDE651:1Y171923-001Model 340525 MB, IDE421:1Y197014-001Option550 GBSCSI-2N/A142038-001Option1.05 GBSCSI-2N/A192799-001OptionCD-ROM Drives Spare Part SystemCD-ROM - LMSI160917-001Presario 625 CDS CD-ROM - Tray LoadInternal142223-001Presario 633 CDS CD-ROM - Tray LoadExternal199430-001OptionDiskette Drives Spare Part System1.44 MB (Light Grey)160788-201All1.2 MB141367-201OptionCables Used With Spare Part Diskette Drive Cable Diskette Drive141186-001CD-ROM Data CD-ROM Drive - Tray Load197842-001CD-ROM Audio CD-ROM Drive - Tray Load199493-001 LED Cable System141346-001 Hard Drive Cable Hard Drive141187-001CD-ROM Cable CD-ROM Drive LMSI160929-001 Telephone Fax/Modem127949-001ROM Information Spare Part 486 C2 06/13/94160192-001 Power Supply/Battery Spare PartPower SupplyDate Code < 401Date Code 401141337-001 (145 Watt/230 VAC) 137633-001 (145 Watt/115 VAC) 194352-001 (145 Watt Energy Star)Real-Time Clock Battery (4.5 v Alkaline)160274-001MEMORY UPGRADE CHART。

TMS320C6416TBGLZA8中文规格书

− Byte-Addressable (8-/16-/32-/64-Bit Data) − 8-Bit Overflow Protection − Bit-Field Extract, Set, Clear − Normalization, Saturation, Bit-Counting − VelociTI.2 Increased Orthogonality

Compatible (Motorola)

D Three 32-Bit General-Purpose Timers D UTOPIA [C6415T/C6416T]

− UTOPIA Level 2 Slave ATM Controller − 8-Bit Transmit and Receive Operations

D Three Multichannel Buffered Serial Ports

− Direct Interface to T1/E1, MVIP, SCSA Framers

− Up to 256 Channels Each − ST-Bus-Switching-, AC97-Conterface (SPI)

GHz)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

KEY DIMM MODULE TIMING PARAMETERS

Module

Component Clock

CAS

Marking Marking

Frequency Latency

-8A

-8A

100MHz

3

-75A

-75A

133MHz

3

GENERAL DESCRIPTION The P32M648YAC, P32M648YBC, P64M6416YAC, and

P32M648YAC, P64M6416YAC

1 SpecTek reserves the right to change products

P32M648YBC, P64M6416YBC

or specifications without notice. ©2002 SpecTek

Rev: 2/26/02

PIN

SYMBOL

85

Vss

86

DQ32

87

DQ33

88

DQ34

89

DQ35

90

Vcc

91

DQ36

92

DQ37

93

DQ38

94

DQ39

95

DQ40

96

Vss

97

DQ41

98

DQ42

99

DQ43

100 DQ44

101 DQ45

102 Vcc

103 DQ46

104 DQ47

105 NC

106 NC

107 Vss

38

A10

80

39

BA1

81

40

Vcc

82

41

Vcc

83

42

CK0

84

*128Mb version only

SYMBOL Vss DU S2# DQMB2 DQMB3 DU Vcc NC NC NC NC Vss DQ16 DQ17 DQ18 DQ19 Vcc DQ20 NC NC CKE1* Vss DQ21 DQ22 DQ23 Vss DQ24 DQ25 DQ26 DQ27 Vcc DQ28 DQ29 DQ30 DQ31 Vss CK2 NC NC SDA SCL Vcc

________________________________________________ ABSOLUTE MAXIMUM RATINGS: Voltage on VDD Supply relative to Vss............ -1 to +4.6V Operating Temperature TA (Ambient) .........25 ° to +70 °C Storage Temperature.................................... -55 to +125 ° Power Dissipation…………………………………………8 W Short Circuit Output Current…………………………..50 mA

• Quad internal banks for hiding row access/precharge. • 64ms 8192 cycle refresh. (7.81us/row) • All inputs, outputs, clocks LVTTL compatible.

Options:

0.4

Units V V V uA uA uA uA V V

Idd OPERATING CONDITIONS AND MAXIMUM LIMITS: VDD = 3.3V ± 10%V, Temp. = 25° to 70 °C

Supply Current OPERATING CURRENT: ACTIVE mode, burst = 2, READ or WRITE, tRC > tRC (MIN), one bank active, STANDBY CURRENT: POWER-DOWN mode, All device banks idle; CKE = LOW

(DIMM)

• TSOP components. • Single 3.3v +.3v power supply. • Nonbuffered fully synchronous; all signals measured on

positive edge of system clock.

• Internal pipelined operation; column address can be changed every clock cycle.

8 - 32Mx8 SDRAM TSOP 16 - 32Mx8 SDRAM TSOP

Older Versions 8 - 32Mx8 SDRAM TSOP 16 - 32Mx8 SDRAM TSOP

Part Number:

P32M648YAC-XX P64M6416YAC-XX

P32M648YBC-XX P64M6416YBC-XX

DQ12

58

17

DQ13

59

18

Vcc

60

19

DQ14

61

20

DQ15

62

21

NC

63

22

NC

64

23

Vss

65

24

NC

66

25

NC

67

26

Vcc

68

27

WE#

69

28

DQMB0

70

29

DQMB1

71

30

S0#

72

31

DU

73

32

Vss

74

33

A0

75

34

A2

76

35

A4

77

36

A6

78

37

A8

79

PIN ASSIGNMENT (Front View)

168-Pin DIMM

PIN

SYMBOL

PIN

1

Vss

43

2

DQ0

44

3

DQ1

45

4

DQ2

46

5

DQ3

47

6

Vcc

48

7

DQ4Biblioteka 498DQ5

50

9

DQ6

51

10

DQ7

52

11

DQ8

53

12

Vss

54

13

DQ9

55

14

DQ10

56

15

DQ11

57

16

CL=3

Symbol Idd1

Idd2

Density 256MB 512MB

256MB 512MB

-75A 1320 1392

72 144

-8A 1280 1344

64 128

Units mA

mA

Notes 1, 2, 3

STANDBY CURRENT: Active Mode;

CS# = HIGH, CKE = HIGH, All device banks active after

P64M6416YBC are high performance dynamic randomaccess 256MB and 512MB modules respectively. These modules are organized in a x64 configuration, and utilize quad bank architecture with a synchronous interface. All signals are registered on the positive edge of the clock signals CK0 through CK3. Read and write accesses to the SDRAM are burst oriented; accesses start at a location and continue for a programmed number of locations in a sequence. Accesses begin with an ACTIVE command, which is followed by a READ or WRITE command.

元器件交易网

P32M648YAC, P64M6416YAC

P32M648YBC, P64M6416YBC

Parameter

Input Capacitance: A0 - A12, BAO, BA1, RAS#, CAS#, WE#, Input Capacitance: CK0-CK3 Input Capacitance: S0#-S3# Input Capacitance: CKE0, CKE1, Input Capacitance: DQMB0#, DQMB7 Input Capacitance: SCL, SA0-SA2, SDA Input/Output Capacitance: DQ0-DQ63

元器件交易网

P32M648YAC, P64M6416YAC

P32M648YBC, P64M6416YBC

SDRAM MODULE

32M, 64M x 64 DIMM

Features:

• Intel PC-100/PC-133 Compatible • JEDEC-standard 168-pin, dual in-line memory module