GS8322V18GB-200I中文资料

832B中文资料

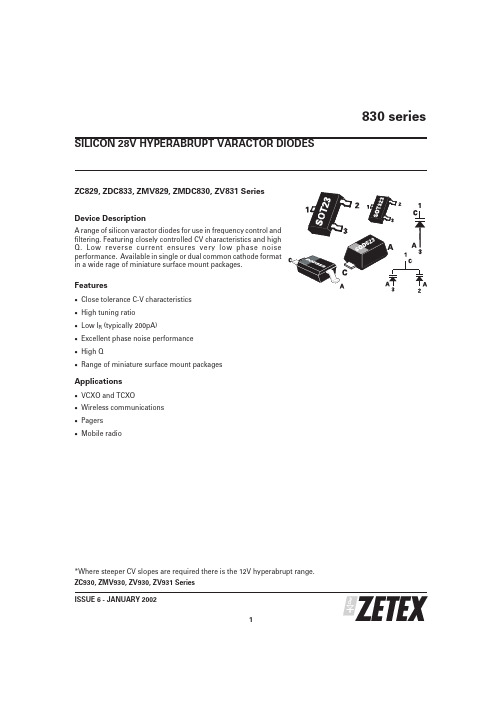

ZC829, ZDC833, ZMV829, ZMDC830, ZV831 Series Device DescriptionA range of silicon varactor diodes for use in frequency control and filtering.Featuring closely controlled CV characteristics and high Q.Low reverse current ensures very low phase noise performance.Available in single or dual common cathode format in a wide rage of miniature surface mount packages.Features·Close tolerance C-V characteristics ·High tuning ratio ·Low I R (typically 200pA)·Excellent phase noise performance ·High Q·Range of miniature surface mount packagesApplications·VCXO and TCXO·Wireless communications ·Pagers ·Mobile radio*Where steeper CV slopes are required there is the 12V hyperabrupt range.ZC930, ZMV930, ZV930, ZV931 Series 830 seriesISSUE 6 - JANUARY 20021SILICON 28V HYPERABRUPT VARACTOR DIODES830 seriesISSUE 6 - JANUARY 20022PARTCapacitance (pF)V R =2V,f=1MHzMin Q V R =3V f=50MHzCapacitance RatioC 2/C 20at f=1MHzMIN.NOM.MAX.MIN.MAX.829A 7.388.29.02250 4.3 5.8829B 7.798.28.61250 4.3 5.8830A 9.010.011.0300 4.5 6.0830B 9.510.010.5300 4.5 6.0831A 13.515.016.5300 4.5 6.0831B 14.2515.015.75300 4.5 6.0832A 19.822.024.2200 5.0 6.5832B 20.922.023.1200 5.0 6.5833A 29.733.036.3200 5.0 6.5833B 31.3533.034.65200 5.0 6.5834A 42.347.051.7200 5.0 6.5834B 44.6547.049.35200 5.0 6.5835A 61.268.074.8100 5.0 6.5835B 64.668.071.4100 5.0 6.5836A 90.0100.0110.0100 5.0 6.5836B95.0100.0105.0100 5.06.5TUNING CHARACTERISTICS at Tamb = 25°CPARAMETER SYMBOLMAX UNIT Forward currentI F 200mA Power dissipation at T amb =25ЊC SOT23P tot 330mW Power dissipation at T amb =25ЊC SOD323P tot 330mW Power dissipation at T amb =25ЊC SOD523P tot250mW Operating and storage temperature range-55to +150ЊCABSOLUTE MAXIMUM RATINGSPARAMETERCONDITIONS MIN.TYP.MAX.UNIT Reverse breakdown voltage I R =10uA 25V Reverse voltage leakageV R =20V 0.220nA Temperature coefficient of capacitanceV R =3V,f =1MHz300400ppCm/ЊCELECTRICAL CHARACTERISTICS at Tamb = 25°C830 seriesTYPICAL CHARACTERISTICSISSUE 6 - JANUARY 20023830 seriesISSUE 6 - JANUARY 20024O R D E R C O D E S A N D P A R T M A R K I N GR E E L C O D ER E E L S I Z ET A P E W I D T HQ U A N T I T Y P E R R E E LT A7i n c h (180m m )8m m3000T C13i n c h (330m m )8m m 10000T A P E A N D R E E L I N F O R M A T I O NT h e o r d e r c o d e s a r e s h o w n a s T A w h i c h i s f o r 7i n c h r e e l s .F o r 13i n c h r e e l s s u b s t i t u t e T C i n p l a c e o f T A i n t h e o r d e r c o d e .ISSUE 6 - JANUARY 20025830 seriesSOT23 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONSZetex plcFields New Road ChaddertonOldham, OL9 8NP United KingdomTelephone (44) 161 622 4422Fax: (44) 161 622 4420Zetex GmbHStreitfeldstraße 19D-81673 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49Zetex Inc700 Veterans Memorial Hwy Hauppauge, NY11788USATelephone: (631) 360 2222Fax: (631) 360 8222Zetex (Asia) Ltd3701-04Metroplaza, Tower 1Hing Fong Road Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494These offices are supported by agents and distributors in major countries world-wide.This publication is issued to provide outline information only which (unless agreed by the Company in writing)may not be used,applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned.The Company reserves the right to alter without notice the specification,design,price or conditions of supply of any product or service.For the latest product information,log on to©Zetex plc 2001830 series6ISSUE 6 - JANUARY 2002DIM MILLIMETRES MIN.MAX A ᎏ0.800A10.0000.100A20.6000.800b10.1600.300c 0.0800.220D 0.7000.900E 1.500 1.700E1 1.100 1.300L 0.2000.400L10.1700.230⍜1Њ4Њ10ЊSOD523 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONS。

低压三相电能计量箱技术规范

低压三相电能计量箱技术规范华北电网有限公司目录1范围....................................................... 错误!未定义书签。

2规范性引用文件 ............................................. 错误!未定义书签。

3术语和定义 ................................................. 错误!未定义书签。

4分类....................................................... 错误!未定义书签。

5技术要求................................................... 错误!未定义书签。

6试验....................................................... 错误!未定义书签。

7标志、包装、贮存和运输、文件资料............................ 错误!未定义书签。

8采购要求................................................... 错误!未定义书签。

9验收....................................................... 错误!未定义书签。

附表低压三相电能计量箱采购要求................................ 错误!未定义书签。

附件A 三相智能电能表外形尺寸 .................................. 错误!未定义书签。

附件B 集中器外形尺寸.......................................... 错误!未定义书签。

附件C 专变采集终端外形尺寸 .................................... 错误!未定义书签。

广柴8320船用柴油机供货技术条件

1In General1.1 This delivery conditions specify the main specifications, technical conditions, delivery scope,packing, factory warranty, spare parts, etc. for the 8320ZCd-8 diesel engine.1.2 When ex-factory, the engines shall be in accordance with the technical requirements stipulated inthis delivery conditions.1.3 For the details of the fitting data and the ex-factory test records, see the Technical Certificate. 1.4 For the particular requirements from users, such as to take out the output power from the frontend of the engine, to modify the dimensions of connecting the flywheel with the coupling, to use Geislinger flexible coupling, to install the remote control device, etc, they must be stipulated in the delivery contract.1.5 The torsional calculation must be carried out when projecting the propulsion plant in order tosatisfy the requirement of safety and operation. If the front end output shaft is applied, the equivalent system for the torsional calculation shall add relative mass points to ensure the accuracy of calculation.1.6 When the engine is used as the main propulsion plant with ahead & astern clutch gearbox, it isnot permitted to engage the clutch gearbox with the engine at minimum idling speed to avoid the engine stops automatically due to the sharp reduction of the speed. The speed for pre-engagement shall be decided according to the requirements for equipments of the shaft system. The recommended speed for pre-engagement is 55~60% of the rated speed of the engine.1.7 The supplier of the remote system must set suitable pre-engagement speed function fullyconsidering the requirement for control system from the engine and ahead & astern clutch gearbox to ensure the engine can operate normally during the operation of engagement and direction change.1.8 In case that the equipment item and its quantity supplied by the factory differ from the sameshown in this technical conditions document, the delivery contract will prevail.1.9 Guangzhou Diesel Engine Factory holds the right to replace the parts or components listed inthis Scope of Delivery with the ones of the same performance or the better when it is necessary.3.2 The SFOC of the engine is based on the fuel oil low caloric value of 42700kJ/kg.3.3 The reference conditions for the unrestricted navigation area engine according to 2001(CCS) areas follows:Absolute atmospheric pressure:P X=0.1MPa;Ambient temperature:T X=318K (45℃);Relative humidity:ΦX=60%;Cooling water temperature before charging air cooler:Tcx=305K(32℃)Under the reference conditions said above, the power of the engine is 2206kW with the engine speed of 525 r/min and the exhaust temperature at the outlet of each cylinder≤450℃.3.4 The overload rating (1hour) is referred as 110% of rated output providing that the engine isoperated for one hour every 12 hours.3.5 When the engine is operated at the continuous output power, the difference between thefollowing operating parameters in cylinders shall not be more than the following stipulated value:The compressed air pressure:2.5%Max. combustion pressure:4.0%Exhaust temperature at the outlet of cylinder:5.0%3.6 The engine under the cool status with the ambient temperature not less than 5℃shall be started upwithin 10 seconds.3.7 The air bottle with its air pressure of 2.94MPa can be used for starting the engine for more than 6times without filling up the air bottle with air.3.8 The engine is allowed to be operated at the load of less than 20% of rated output for a short timewhen the turbocharger fails to operate due to its default. But at that time, the cover of the air inlet chamber should be removed.3.9 It shall be allowed that the engine is to be operated at the load of not more than 50% of ratedoutput for a short time when one of the cylinders is out of firing.3.10 Users shall take the torsional calculation for the shafting with torsional calculation data of theengine from GDF and the calculating result shall agree to the requirement of CCS. GDF can do that for the user with extra charge.3.11 The cost for packing and CCS inspection will be extra charged.and store the engine according to the Operation and Maintenance Manual for Model 8320 Diesel Engine. Guangzhou Diesel Engine Factory will be responsible for repairing and replace the rust-eaten parts due to the incorrect oil seal in the guarantee period of oil seal.6.3 The damaged parts and / or components due to the poor manufacturing and assembly qualityshall be replaced by the factory free of charge under the following conditions that the user obeys the stipulations in the Operation and Maintenance Manual for Model 8320 Diesel Engine and the stipulations in the Points for Attention to Heavy Fuel Oil Operation for Series 320 Engines within 18 months from the date of ex-factory of the engine and the operating time is not exceeded 2000hours, and that the operating data must be recorded.6.4 The factory shall not be responsible for the parts and / or components damaged due to thefollowing causes:(a) Natural wear(b) Poor storage and maintenance(c) Operating not according to the operating manual(d) Use the lube oil, cooling water and fuel oil not according to the requirements in theoperating and maintenance manual(e) Chemical reactions and corrosion(f) Indirect losses incurred by the default of the engine(g) The user’s fault。

专变采集终端使用说明书模板

国网专变采集终端技术与使用说明书目录1、概述 (3)2、执行标准 (3)3、GK200技术参数 (4)3.1 型号命名 (4)3.2 供电方式 (4)3.3电源要求 (4)3.4性能指标 (4)3.5输入回路 (5)3.6输出回路 (5)3.7通道接口 (5)3.8停电运行 (6)3.9外壳与结构 (6)3.10使用环境 (6)3.11端钮盒 (6)4、GK200主要功能 (7)4.1、数据采集功能 (9)4.2数据处理功能 (9)4.3 参数设置和查询 (13)5、GK200人机交互功能 (17)5.1显示界面风格...............................................................5.2液晶使用附加说明...........................................................6、安装及接线 (18)6.1 安装准备 (18)6.2 终端安装一般要求 (18)6.3 终端接线和铺设一般要求 (18)6.4 终端安装方法 (18)1、概述GK200专变采集终端采用高性能32位的ARM微处理器、实时操作系统,具有功能强大,处理速度快,运行稳定可靠等优点。

广泛应用于大用电户、配变对用电量进行采集计算,控制和管理。

该终端设备设计制造符合了《电力用户用电信息采集系统技术规范》、《电力用户用电信息采集系统型式规范》和国家电力、电子、通讯的相关标准。

具有电度量采集、远程抄表、电量计算、功率计算、需量计算、历史数据查询、远程或本地定值设置、功控、电控,购电控、遥测、遥信、负荷越限报警、通讯等功能,可以通过GPRS 网络等方式进行远程数据传输。

2、执行标准终端产品的设计符合下列国家相关标准规定:GB/T 4208-2008 外壳防护等级(IP 代码)GB/T 13384-2008 机电产品包装通用技术条件GB/T 17215.211-2006 交流电测量设备通用要求试验和试验条件第11部分:测量设备GB/T 2829-2002 周期检验计数抽样程序及表(适用于对过程稳定性的检验) DL/T 533-2007 电力负荷管理终端DL/T 645 多功能电能表通信规约DL/T 698.1-2009 电能信息采集与管理系统第1部分:总则DL/T 721-2000 配电网自动化系统远方终端Q/GDW 129-2005 电力负荷管理系统通用技术条件Q/GDW 130-2005 电力负荷管理系统数据传输规约Q/GDW 373-2009 电力用户用电信息采集系统功能规范Q/GDW 374.3-2009 电力用户用电信息采集系统技术规范第三部分:通信单元技术规范Q/GDW 375.1-2009 电力用户用电信息采集系统型式规范第一部分:专变采集终端型式规范Q/GDW 376.1-2009 电力用户用电信息采集系统通信协议第一部分:主站与采集终端通信协议Q/GDW 379.2-2009 电力用户用电信息采集系统检验技术规范第二部分:专变采集终端检验技术规范GB/T 5169.11-2006 电工电子产品着火危险实验第11部分:灼热丝/热丝基本实验方法成品的灼热丝可燃性试验方法GB/T 16935.1-2008 低压系统内设备的绝缘配合第1部分:原理、要求和试验GB/T 17441-1998 交流电度表符号GB/Z21192-2007 电能表外形和安装尺寸Q/GDW 205-2008 电能计量器具条码JB/T 6214-1992 仪器仪表可靠性验证试验及测定试验(指数分布)导则DL/T 597-1996 低压无功补偿控制器订货技术条件DL/T 790.31-2001 采用配电线载波的配电自动化第3 部分:配电线载波信号传输要求第1 篇:频带和输出电平DL/T645-1997 多功能电能表通信规约国家电力公司(2005 年) 电力负荷管理系统通用技术条件国家电力公司(2005 年) 电力负荷管理系统数据传输规约YD/T 1214-2002 900/1800MHz TDMA 数字蜂窝移动通信网通用分组无线业务(GPRS)设备技术规范:移动台IEC 6100-6-1(1997) 居住、商业和轻工业环境通用抗扰性标准3、GK200技术参数3.1 型号命名3.2 供电方式使用三相供电,在系统故障(三相三线供电断一相电压,三相四线供电断二相电压)的条件下,终端能正常工作。

南方电网公司低压费控计量表箱技术规范

低压费控计量表箱技术规范南方电网公司市场营销部2015年11月目录1.范围 .............................................................. 错误!未定义书签。

2.规范性引用文件.................................................... 错误!未定义书签。

3.术语和定义 ........................................................ 错误!未定义书签。

. 低压费控计量表箱 ............................................... 错误!未定义书签。

. 进线室.......................................................... 错误!未定义书签。

. 计量室.......................................................... 错误!未定义书签。

. 互感器室........................................................ 错误!未定义书签。

. 出线室.......................................................... 错误!未定义书签。

4.计量表箱分类...................................................... 错误!未定义书签。

5.计量表箱型号与命名................................................ 错误!未定义书签。

6.要求 .............................................................. 错误!未定义书签。

指纹锁测试模板讲解

指纹锁1 范围:本标准规定了指纹产品的型号、术语和定义、要求、试验方法、检验规则和标志、包装运输和储存。

本标准适用予以指纹作为输入信,识别、处理其相关信息,以电动方式控制机械锁定结构启、闭的具有规定防破坏能力的锁。

本标准不适用于具有防盗功能的指纹防盗锁。

2 规范性引用文件下列文件中的条款通过本际准的引用而本标准的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本标准,然而,鼓励根据本标准达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本标准。

GB/T 191-2000包装储运图示标志GB/T 2828.1-2003计数抽样检验程序第1部分:按接收质量限(AQL)检索的逐批检验抽样计划GB/T 2829-2002周期检验计数抽洋程序及表(适用于对过程稳定性的检验)CB/T 6461-2002金属基体上金属和其他无机覆盖层经腐蚀试验后的试样和试件的评级GB/T 10125-1997 人造气氛腐蚀试验、盐雾试验GB/T 15211-l994报警系统环境试验GB/T 17626. 2-1998 电磁兼容试验和测量技术静电放电抗干扰度试验GB/T 17626. 3-1998 电磁兼容试验和测量技术射频电磁辐射抗干扰度试验GB/T 17626. 4-1998 电磁兼容试验和测量技术电快速瞬态脉冲群抗干扰度试验GB/T 17626. 11-1999 电磁兼容试验和测量技术电压暂降、短时中断和电压变化的抗干扰度试验GA/T 394-2002 出入口控制系统技术要求GA 374-2001 电子防盗锁QB/T 2474-2000弹子插芯门锁QB/T 3836-1999 锁具测试方法3 产品型号2-4阿拉伯数字表示:规格及颜色等信信息4位阿拉伯数字表示:分类及款式代号系列代示例:J1011表示系列代号为J的1011款指纹锁4术语和定义下列术语和定义适用于本标准4.1 指纹传惑嚣是指纹采集的一种设备,其能使指纹特征转换成数字化指纹图像。

ad832中文资料

在AD823,n沟道jfet是用来提供一个低偏移、低噪音、高阻抗输入级。最低输入共模电压范围从0.2 V低于−1 V < + VS VS。驾驶输入电压接近积极铁路造成损失的放大器带宽和增加共模电压误差。 这个AD823并不表现出反相输入电压和包括+ VS。图38显示响应的一个AD823电压跟随器到0 V到5 V(+ VS)方波输入。 输入和输出的叠加。输出极性跟踪输入极性高达+大战,没有反相。降低了带宽高于4 V输入使舍入的输出波形。输入 电压大于+大战,一个电阻串联在一起,AD823的同相输入防止反相,以牺牲更大的输入电压噪声。此过程如图39。

类型的架构允许更多的开环增益和输出驱动可以取得

比标准的2段架构将允许。

输出阻抗 开环输出阻抗低频率的共发射极输出级用于这个设计是 kΩ大约 30。虽然这是明显高于典型的射极跟随器输出阶段, 当它与反馈、输出阻抗是减少了运算放大器的开环增益。用 109 分贝的开环增益、输出阻抗降低到< 0.2Ω。在更高 的频率,输出阻抗上升为运算放大器的开环增益下降;但是,输出也变得电容由于积分器电容 C1 和 C2。这可以防止输 出阻抗从曾经变得过高(参见图 18),这可能会导致开车时容性负载稳定性问题。事实上 ,AD823 具有优良的帽负载驱 动能力的高频率运算放大器。如图 34 所示的连接是一个跟随者 AD823 开车 470 pF 直接电容性负载。在这些条件下, 阶段保证金约为 20°。如果大阶段保证金,是理想的,可以使用一个小电阻串联在一起,输出解耦效果的负载电容从 运算放大器(参见图 26)。此外,运行在更高的收益的一部分也提高了电容性负载驱动能力的运算放大器。

图 40 展示了一个示意性的一个 AD823 被 用来驱动两个输入和一个 AD1672 参考输 入,一个 12 位,3 m / s 的,单电源 ADC。 一个放大器被配置为一个单位增益从动 件驱动模拟输入的 AD1672,它被配置为接 受一个输入电压,范围从 0 V 2.5 诉其他 放大器配置为一个增益 2 驱动参考输入从 1.25 V 的参考。尽管 AD1672 有自己的内 部参考,有系统,需要更大的精度比内部 参考提供的。另一方面,如果 AD1672 内部 参考使用,第二 AD823 放大器可以用于缓 冲的参考电压,驱动其他电路虽然最小加 载引用源。

LC821中文资料

5.0 A

RF CHARACTERISTICS (

SYMBOL Gps PARAMETER Common Source Power Gain Drain Efficiency Load Mismatch Tolerance MIN 10 55 TYP

8.0 WATTS OUTPUT )

MAX UNITS dB % 20:1 TEST CONDITIONS Idq = 0.40 A, Vds = 12.5 V, F = Idq = 0.40 A, Vds = 12.5 V, F =

0.1 0 2 4 1 10 100

ID & GM VS VGS

L2C 1 DIE ID, GM vs VG

ID

GM

Vgs in Volts6ຫໍສະໝຸດ 81012

14

Zin Zout

PACKAGE DIMENSIONS IN INCHES

Tolerance .XX +/-0.01

.XXX +/-.005 inches

TM

SILICON GATE ENHANCEMENT MODE RF POWER LDMOS TRANSISTOR 8.0 Watts Single Ended Package Style AC HIGH EFFICIENCY, LINEAR HIGH GAIN, LOW NOISE

o

ABSOLUTE MAXIMUM RATINGS ( T = 25 C )

500 MHz 500 MHz

η

VSWR

Relative Idq = 0.40 A, Vds = 12.5 V, F = 500 MHz

ELECTRICAL CHARACTERISTICS ( EACH SIDE )

中文版3582i说明书

W8152 / IL

图 2. 3582i 型电 - 气阀门定位器

3582 型

技术规格

可供配置 参考型号说明一节

输入信号 对 3582 系列: ■ 3 至 15psig(0.2 至 1.0bar),■ 6 至 30psig

● 精确、有效、抗震性能好—— 3582 系列和 3582i 型定位器提供一种经过现场证明的定位器结构。它精 度高、响应快、能够承受大多数工厂环境里的振动。低 的稳态空气消耗量使得其工作更为有效。

● 可调范围宽—— 3582 系列和 3582i 型定位器具有 分程能力。零点和量程的或调范围允许使用所有的标 准输入信号,包括分程输入信号。

● 抗腐蚀——壳体、部件和垫片材料可承受苛刻的 环境。定位器在排放空气的同时也清洁了内部零部件,

5120 / IL

图 5. 582i 型电气转换器

从而提供了额外的保护。

● 现场可更换作用方向——只需要进行单位的调整 就可以在正作用和反作用之间进行互换。

● 控制阀诊断测试能力——为了使用 FlowScanner 阀门诊断系统对阀门 / 执行机构 / 定位器组件进行诊断 测试,连接件、接管和其它硬件可以很容易地安装在 3582 系列和 3582i 型与执行机构之间。

气源压力(1) 建议值: 比执行机构所需气源压力高5 psig(0.3 bar) 最大值: 50 psig(0.3 bar)或执行机构的额定值,以 低者为准。

产品样本 62.1:3582 2001 年 2 月

35 psig(2.4 bar)气源: 285.5 scth(8.1 标准 m3/hr)

性能 对 3582 系列: 独立线性度(1): 输出信号量程的± 1% 回差(1): 量程的 0.5% 对 3582i 型: 独立线性度(1): 输出信号量程的± 2% 回差(1): 量程的 0.6% 电磁干扰(EMI)(1): 当按 IEC801-3(1984)标准条件 进行测试时,在频率为 20-1000MHz 磁场强度为 30V/m 时,稳态偏差小于±1%。定位器被测试时 用一个罩子盖上,且其外部接线通过硬金属导管。 3582i 系列和 3582i 型: 开环增益(输出信号)(1): ■ 3 至 15 psig(0.2 至 1.0 bar)范围时为 100 ■ 6 至 30 psig(0.4 至 2.0 bar)范围时为 55

GB 200 标准型扩展模块用户手册说明书

1.产品选型 (2)2.数字量模块 (2)2.1数字量模块技术参数 (2)2.2数字量模块接线图 (5)3.模拟量输入模块 (7)3.1EM231产品外形 (7)3.2EM231产品参数 (7)3.3EM231接线示意图 (8)3.4EM231输入校准方法 (8)3.5EM231组态方法和配置 (8)3.6EM231模拟量输入数据格式 (9)3.7EM231-4AI输入示意图 (10)3.8EM231-8AI(电流型)输入示意图 (10)3.924VDC电源指示灯 (11)4.模拟量输出模块 (11)4.1EM232产品参数 (11)4.2EM232接线示意图 (12)4.4EM232模拟量输出数据字格式 (12)4.5EM232模拟量输出方框图 (13)5.模拟量混合模块 (14)5.1EM235产品外形 (14)5.2EM235产品参数 (14)5.3EM235接线示意图 (16)5.4EM235模拟量输入校准方法 (16)5.5EM235组态开关 (16)5.6EM235模拟量模块输入示意图 (17)6.温度模块 (18)6.1EM231-RTD4产品参数 (18)6.2EM231-RTD4接线示意图 (18)6.3EM231-RTD4组态方法 (19)6.4EM231-RTD4状态指示灯 (20)6.5EM231-TC热电偶产品参数 (20)6.6EM231-TC4/TC8接线示意图 (21)6.7EM231-TC4/TC8组态 (21)6.8EM231-TC状态指示灯 (22)7.扩展模块地址分配 (22)1.产品选型数字量输入模块描述24V供电尺寸(mm)功耗订货号EM221-I8数字量输入8×24VDC不需要46×80×622W6ES7221-1BF22-0XA8 EM221-I16数字量输入16×24VDC不需要71.2×80×623W6ES7221-1BH22-0XA8 EM221-32数字量输入32×24VDC不需要137.3×80×623W6ES7221-1BH22-0XA8数字量输出模块描述24V供电尺寸(mm)功耗订货号EM222-TQ88x24VDC晶体管不需要46×80×622W6ES7222-1BF22-0XA8 EM222-RQ88x继电器需要46×80×622W6ES7222-1HF22-0XA8 EM222-TQ1616x24VDC晶体管不需要71.2×80×623W6ES7222-1BH22-0XA8 EM222-RQ1616x继电器需要71.2×80×623W6ES7222-1HH22-0XA8 EM222-TQ3232x24VDC晶体管不需要137.3×80×626W6ES7222-1BL22-0XA8 EM222-RQ3232x继电器需要137.3×80×626W6ES7222-1HL22-0XA8数字量混合模块描述24V供电尺寸(mm)功耗订货号EM223-I4TQ44输入4晶体管输出不需要46×80×622W6ES7223-1BF22-0XA8 EM223-I4RQ44输入4继电器输出需要46×80×622W6ES7223-1HF22-0XA8 EM223-I8TQ88输入8晶体管输出不需要71.2×80×623W6ES7223-1BH22-0XA8 EM223-I8RQ88输入8继电器输出需要71.2×80×623W6ES7223-1PH22-0XA8 EM223-I16TQ1616输入16晶体管输出不需要137.3×80×626W6ES7223-1BL22-0XA8 EM223-I16RQ1616输入16继电器输出需要137.3×80×626W6ES7223-1PL22-0XA8模拟量输入模块描述24V供电尺寸(mm)功耗订货号EM231-AI44输入需要71.2×80×622W6ES7231-0HC22-0XA8 EM231-AI88输入(电流型)需要71.2×80×622W6ES7231-0HF22-0XA8模拟量输出模块描述24V供电尺寸(mm)功耗订货号EM232-AQ22输出需要46×80×622W6ES7232-0HB22-0XA8 EM232-AQ44输出需要71.2×80×622W6ES7232-0HD22-0XA8模拟量混合模块描述24V供电尺寸(mm)功耗订货号EM235-AI4AQ14输入1输出需要71.2×80×622W6ES7235-0KD22-0XA8温度模块描述24V供电尺寸(mm)功耗订货号EM231-RTD4热电阻PT1004输入需要71.2×80×62 1.8W6ES7231-7PC22-0XA8 EM231-TC4热电偶4输入需要71.2×80×62 1.8W6ES7231-7PD22-0XA8 EM231-TC8热电偶8输入需要71.2×80×62 1.8W6ES7231-7PF22-0XA82.数字量模块2.1数字量模块技术参数数字量输入规范24VDC输入输入类型漏型/源型输入额定电压24VDC,4mA最大持续电压30VDC 浪涌电压35VDC ,0.5s 逻辑115至30VDC 逻辑00至5VDC 输入延时(最大)4.5ms 连接两线接近开关传感器允许的最大漏电流1mA隔离(光电隔离)现场到逻辑500VAC ,1分钟数字量扩展模块输入内部结构图提示:内部使用双向光耦,可实现漏型或源型接法。

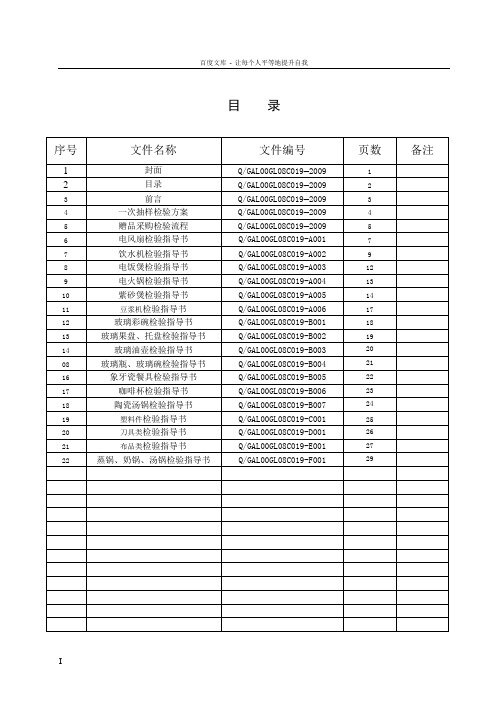

小家电————成品检验标准

目录

前言

Q/GAL00GL08C019—2009《赠品检验标准要求》是广东格兰仕集团有限公司质量管理标准之一。

本标准在修订时根据体系运行的实际情况并征求了各相关部门的意见,在符合性及可操作性等方面进一步完善。

本标准由广东格兰仕集团有限公司标准化委员会提出。

本标准由广东格兰仕集团有限公司全质办归口。

本标准起草单位:集团全质办。

本标准所述赠品暂分为七大类(后续可再增补):

●A类:电器类,主要包括电风扇、电饭煲、豆浆机等;

●B类:玻璃陶瓷类,主要包括烹调玻璃碗等;

●C类:塑料件类,主要包括保鲜盒、饭勺、汤勺等;

●D类:刀具类,主要包括厨具六件套、刀具组合等;

●E类:布料类,主要包括床上用品、沙滩椅等;

●F类:金属类,主要包括蒸锅、奶锅、汤锅等。

本标准主要起草人:宋振威、陈永柱、翟谦章、林波、陈天柱、任秋云、曾卫欢、苏永诚等。

本标准是在本公司现行的管理基础上进行编制,自2009年11月25日首次按标准化要求发布。

一次抽样检验方案:。

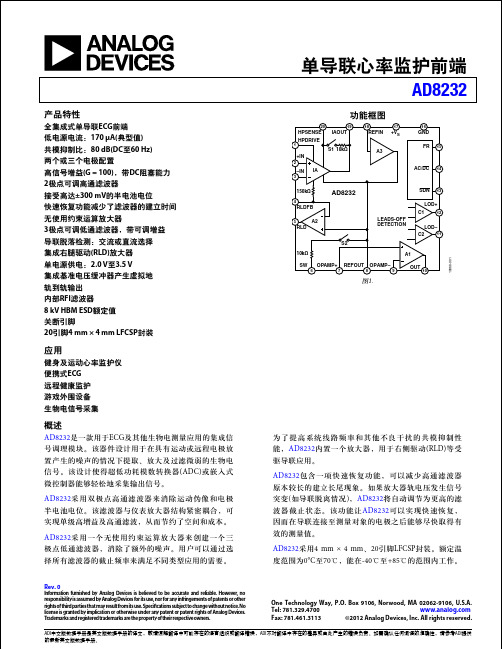

AD8232 中文产品数据手册

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

10866-001

AD8232 目录

特性................................................................................................... 1 应用................................................................................................... 1 功能框图 .......................................................................................... 1 概述................................................................................................... 1 修订历史 .......................................................................................... 2 技术规格 .......................................................................................... 3 绝对最大额定值............................................................................. 6 ESD警告...................................................................................... 6 引脚配置和功能描述 .................................................................... 7 典型工作特性 ................................................................................. 8 仪表放大器性能曲线............................................................... 8 运算放大器性能曲线............................................................. 11 右腿驱动(RLD)放大器性能曲线......................................... 14 基准电压缓冲器性能曲线 .................................................... 15 系统性能曲线 .......................................................................... 16 工作原理 ........................................................................................ 17 架构概览................................................................................... 17 仪表放大器 .............................................................................. 17 运算放大器 .............................................................................. 17 右腿驱动放大器...................................................................... 17 基准电压缓冲器...................................................................... 18 快速恢复电路 .......................................................................... 18 导联脱落检测 .......................................................................... 19 待机操作................................................................................... 19 输入保护................................................................................... 20 射频干扰(RFI) ......................................................................... 20 电源调整与旁路...................................................................... 20 折合到输入端的失调............................................................. 20 布局建议................................................................................... 20 应用信息 ........................................................................................ 21 消除电极失调 .......................................................................... 21 高通滤波................................................................................... 21 低通滤波和增益...................................................................... 23 驱动电极................................................................................... 23 应用电路 ........................................................................................ 24 心脏附近心率测量 ................................................................. 24 应用练习:在双手处测量心率 ........................................... 24 心脏监护仪配置...................................................................... 25 带运动伪像消除功能的便携式心脏监护仪 ..................... 25 封装和订购信息........................................................................... 27 外形尺寸................................................................................... 27 订购指南................................................................................... 27

AD8232_cn数据手册

Document Feedback

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2012–2013 Analog Devices, Inc. All rights reserved. Technical Support

参数符号测试条件注释最小值典型值最大值单位仪表放大器共模抑制比dc至60hz共模抑制比cmrr035v至2858086db035v至28580db电源抑制比电源抑制比psrr20v至357690db失调电压rtivos仪表放大器输入mv隔直输入平均失调漂移仪表放大器输入10输入偏置电流ib50200pana输入失调电流ios25100pana输入阻抗1075g?pf515g?pf输入电压噪声rti频谱噪声密度khz100nvhz峰峰值电压噪声01hz至10hz1205hz至40hz14pp输入电压范围0c至70c02vs直流差分输入范围vdiff300300mv输出输出摆幅rl01vs短路电流iout63ma增益av100增益误差vdiff300mv至300mv0c至70c12ppmc带宽bwkhzrfi滤波器截止频率每个输入端mhz运算放大器a1失调电压vosmv平均温度系数tc输入偏置电流ib100pana输入失调电流ios100pana输入电压范围01vs共模抑制比共模抑制比cmrr05v至25100db电源抑制比电源抑制比psrr100db大信号电压增益avo110db输出电压范围01vs短路电流限值iout12ma增益带宽积gbp100khzsr002电压噪声密度rtienkhz60nvhz峰峰值电压噪声rtienpp01hz至10hz05hz至40hzppad8232技术规格除非另有说明v25cfr低电平sdn高电平acdc低电平

E18系列产品规格书说明书

E18系列产品规格书CC25302.4GHz ZigBee3.0无线模块目录第一章产品概述 (3)1.1产品简介 (3)1.2特点功能 (4)1.3应用场景 (5)第二章规格参数 (6)2.1射频参数 (6)2.2电气参数 (6)2.3硬件参数 (6)2.4网络系统参数 (7)第三章机械尺寸与引脚定义 (8)第四章硬件设计 (11)第五章软件设计 (11)第六章常见问题 (13)6.1传输距离不理想 (13)6.2模块易损坏 (13)6.3误码率太高 (13)第七章焊接作业指导 (7)7.1回流焊温度 (7)7.2回流焊曲线图 (7)第八章相关型号 (8)第九章天线指南 (8)第十章产品包装图 (8)修订历史 (9)关于我们 (9)第一章产品概述1.1产品简介E18系列是亿佰特设计生产的2.4GHz频段的ZigBee通信协议转串口无线模块,贴片型,PCB板载天线或IPEX-1接口,引脚间距1.27mm,出厂自带自组网固件,到手即用,适用于多种应用场景(尤其智能家居)。

E18系列模块采用美国德州仪器公司原装进口CC2530射频芯片,芯片内部集成了8051单片机及无线收发器,部分模块型号内置PA功率放大器增加通信距离。

出厂自带固件基于ZigBee3.0协议实现的串口数据透传,支持ZigBee3.0协议下各种指令命令。

经实测,对市面上大多数ZigBee3.0产品有着非常良好的兼容性。

1.2ZigBee 3.0优势E18系列模块固件基于Z-Stack3.0.2协议栈(ZigBee 3.0),该版本为CC2530/CC2538系列芯片最优协议栈,因此我司也此基础上做了许多优化,确保系统长期稳定运行。

ZigBee3.0与早前版本的应用方式区别:1.组网方式发生变化:ZigBee 3.0取缔了一上电就组网的方式,而是根据实际需要进行组网。

任何设备在出厂状态下是无网络状态,协调器需要运行“formation”(调用bdb_StartCommissioning(BDB_COMMISSIONING_MODE_NWK_FORMATION))来新建网络,然后再运行"Steering"(调用bdb_StartCommissioning(BDB_COMMISSIONING_MODE_NWK_STEERING))打开网络,打开网络默认时间180秒,可通过广播"ZDP_MgmtPermitJoinReq"的方式将打开网络提前关闭。

20-直播卫星电视广播地面接收设备

编号:XK09-005卫星电视广播地面接收设备产品生产许可证实施细则(二)(直播卫星专用设备产品部分)2016年9月30日公布 2016年10月30日实施国家质量监督检验检疫总局目录第一章总则 (1)第二章发证产品及标准 (1)第三章企业申请生产许可证的基本条件和资料 (5)第四章企业实地核查 (16)第五章产品检验 (17)第六章证书许可范围 (33)第七章附则 (34)附件1 企业核查时准备书面材料清单 (35)附件1-1 企业生产卫星电视广播地面接收设备直播卫星专用产品主要工艺流程图.. 36附件1-2 企业生产卫星电视广播地面接收设备直播卫星专用产品生产设施和检验设施表 (37)附件1-3 企业生产卫星电视广播地面接收设备直播卫星专用产品生产场所示意图.. 38附件1-4 企业生产卫星电视广播地面接收设备直播卫星专用产品生产设备表 (39)附件1-5 企业生产卫星电视广播地面接收设备直播卫星专用产品检验设备表 (40)附件1-6 关键岗位专业技术人员表 (41)附件1-7 产品技术文件和工艺文件清单 (42)附件2 卫星电视广播地面接收设备直播卫星专用产品生产许可证企业实地核查办法43附件3 企业实地核查不符合和建议改进条款汇总表 (51)附件4 生产许可证企业实地核查报告 (52)附件5 检验报告格式 (53)附件6 本实施细则与旧版细则主要内容对比表 (57)卫星电视广播地面接收设备产品生产许可证实施细则(二)(直播卫星专用设备产品部分)第一章总则第一条为了做好卫星电视广播地面接收设备直播卫星专用产品生产许可证审查工作,依据《中华人民共和国工业产品生产许可证管理条例》、《中华人民共和国工业产品生产许可证管理条例实施办法》、《工业产品生产许可证实施通则》(以下简称通则)等规定,制定本工业产品生产许可证实施细则(以下简称细则)。

第二条本细则适用于卫星电视广播地面接收设备直播卫星专用产品生产许可的实地核查、产品检验等工作,应与通则一并使用。

GS8322Z18GE-200V资料

GS8322Z18/36/72(B/E/C)-xxxV36Mb Pipelined and Flow ThroughSynchronous NBT SRAM250 MHz –133 MHz 1.8 V or 2.5 V V DD 1.8 V or 2.5 V I/O119, 165 & 209 BGA Commercial Temp Industrial Temp Features• NBT (No Bus Turn Around) functionality allows zero wait Read-Write-Read bus utilization; fully pin-compatible with both pipelined and flow through NtRAM™, NoBL™ and ZBT™ SRAMs• 1.8 V or 2.5 V core power supply • 1.8 V or 2.5 V I/O supply• User-configurable Pipeline and Flow Through mode • ZQ mode pin for user-selectable high/low output drive • IEEE 1149.1 JTAG-compatible Boundary Scan • LBO pin for Linear or Interleave Burst mode• Pin-compatible with 2Mb, 4Mb, 8Mb, and 16Mb devices • Byte write operation (9-bit Bytes)• 3 chip enable signals for easy depth expansion • ZZ Pin for automatic power-down• JEDEC-standard 119-, 165- or 209-Bump BGA package • RoHS-compliant packages availableFunctional DescriptionThe GS8322Z18/36/72-xxxV is a 36Mbit Synchronous Static SRAM. GSI's NBT SRAMs, like ZBT, NtRAM, NoBL or other pipelined read/double late write or flow through read/single late write SRAMs, allow utilization of all available bus bandwidth by eliminating the need to insert deselect cycles when the device is switched from read to write cycles.Because it is a synchronous device, address, data inputs, and read/write control inputs are captured on the rising edge of the input clock. Burst order control (LBO) must be tied to a power rail for proper operation. Asynchronous inputs include the Sleep mode enable (ZZ) and Output Enable. Output Enable can be used to override the synchronous control of the output drivers and turn the RAM's output drivers off at any time. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates complex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing.The GS8322Z18/36/72-xxxV may be configured by the user to operate in Pipeline or Flow Through mode. Operating as a pipelined synchronous device, in addition to the rising-edge-triggered registers that capture input signals, the device incorporates a rising edge triggered output register. For read cycles, pipelined SRAM output data is temporarily stored by the edge-triggered output register during the access cycle and then released to the output drivers at the next rising edge of clock.The GS8322Z18/36/72-xxxV is implemented with GSI's high performance CMOS technology and is available in a JEDEC-standard 119-bump, 165-bump or 209-bump BGA package.Parameter Synopsis-250-225-200-166-150-133Unit Pipeline 3-1-1-1KQ tCycle 4.0 4.4 5.0 6.0 6.77.5ns Curr (x18)Curr (x36)Curr (x72)275330415255300385240280340215245305205230285180205255mA mA mA Flow Through 2-1-1-1t KQ tCycle 6.57.07.58.08.58.5ns Curr (x18)Curr (x36)Curr (x72)200225300190215280180205255170195245160185230150170225mA mA mAGS8322Z18/36/72(B/E/C)-xxxVGS8322Z72C-xxxV Pad Out—209-Bump BGA—Top View (Package C)1234567891011A DQ G DQ G A E2A ADV A E3A DQB DQ B AB DQ G DQ G BC BG NC W A BB BF DQ B DQ B BC DQ G DQ G BH BD NC E1NC BE BA DQ B DQ B CD DQ G DQ G V SS NC NC G NC NC V SS DQ B DQ B DE DQP G DQP C V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQPF DQP B EF DQ C DQ C V SS V SS V SS ZQ V SS V SS V SS DQ F DQ F FG DQ C DQ C V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ F DQ F GH DQ C DQ C V SS V SS V SS MCL V SS V SS V SS DQ F DQ F H J DQ C DQ C V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ F DQ F J K NC NC CK NC V SS CKE V SS NC NC NC NC K L DQ H DQ H V DDQ V DDQ V DD FT V DD V DDQ V DDQ DQ A DQ A L M DQ H DQ H V SS V SS V SS MCL V SS V SS V SS DQ A DQ A M N DQ H DQ H V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ A DQ A N P DQ H DQ H V SS V SS V SS ZZ V SS V SS V SS DQ A DQ A P R DQP D DQP H V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQP A DQP E R T DQ D DQ D V SS NC NC LBO NC NC V SS DQ E DQ E T U DQ D DQ D NC A NC A A A NC DQ E DQ E U V DQ D DQ D A A A A1A A A DQ E DQ E V W DQ D DQ D TMS TDI A A0A TDO TCK DQ E DQ E W11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump PitchGS8322Z18/36/72(B/E/C)-xxxVGS8322Z72C-xxxV 209-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn IAddress InputsDQ A DQ B DQ C DQ D DQ E DQ F DQ G DQ H I/O Data Input and Output pinsB A , B B I Byte Write Enable for DQ A , DQ B I/Os; active low BC ,BD I Byte Write Enable for DQ C , DQ D I/Os; active low BE , BF , BG ,B HI Byte Write Enable for DQ E , DQ F , DQ G , DQ H I/Os; active lowNC —No ConnectCK I Clock Input Signal; active high E 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active low ADV I Burst address counter advance enable ZZ I Sleep Mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowMCH I Must Connect High MCH IMust Connect High MCL Must Connect Low W I Write Enable; active low ZQ I FLXDrive Output Impedance Control Low = Low Impedance [High Drive], High = High Impedance [Low Drive]CKEIClock Enable; active lowGS8322Z18/36/72(B/E/C)-xxxVTMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322Z72C-xxxV 209-Bump BGA Pin DescriptionSymbolTypeDescriptionGS8322Z18/36/72(B/E/C)-xxxVGS8322Z36B-xxxV Pad Out—119-Bump BGA—Top View 1234567A V DDQ A A A A A V DDQ A B NC E2A ADV A E3NC B C NC A A V DD A A NC C D DQC DQPC V SS ZQ V SS DQPB DQB D E DQC DQC V SS E1V SS DQB DQB E F V DDQ DQC V SS G V SS DQB V DDQ F G DQC DQC BC A BB DQB DQB G H DQC DQC V SS W V SS DQB DQB H J V DDQ V DD NC V DD NC V DD V DDQ J K DQD DQD V SS CK V SS DQA DQA K L DQD DQD BD NC BA DQA DQA L M V DDQ DQD V SS CKE V SS DQA V DDQ M N DQD DQD V SS A1V SS DQA DQA N P DQD DQPD V SS A0V SS DQPA DQA P R NC A LBO V DD FT A NC R T NC NC A A A A ZZ T UV DDQTMSTDITCKTDONCV DDQU7 x 17 Bump BGA—14 x 22 mm 2 Body—1.27 mm Bump Pitch(Package B)GS8322Z18/36/72(B/E/C)-xxxVGS8322Z18B-xxxV Pad Out—119-Bump BGA—Top View 1234567A V DDQ A A A A A V DDQ A B NC E2A ADV A E3NC B C NC A A V DD A A NC C D DQB NC V SS ZQ V SS DQPA NC D E NC DQB V SS E1V SS NC DQA E F V DDQ NC V SS G V SS DQA V DDQ F G NC DQB BB A NC NC DQA G H DQB NC V SS W V SS DQA NC H J V DDQ V DD NC V DD NC V DD V DDQ J K NC DQB V SS CK V SS NC DQA K L DQB NC NC NC BA DQA NC L M V DDQ DQB V SS CKE V SS NC V DDQ M N DQB NC V SS A1V SS DQA NC N P NC DQPB V SS A0V SS NC DQA P R NC A LBO V DD FT A NC R T NC A A A A A ZZ T UV DDQTMSTDITCKTDONCV DDQU7 x 17 Bump BGA—14 x 22 mm 2 Body—1.27 mm Bump Pitch(Package B)GS8322Z18/36/72(B/E/C)-xxxVGS8322Z18/36B-xxxV 119-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn I Address Inputs DQ A DQ B DQ C DQ D I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active lowNC —No ConnectCK I Clock Input Signal; active high CKE I Clock Enable; active low W I Write Enable; active low E 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active low ADV I Burst address counter advance enable ZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance ControlLow = Low Impedance [High Drive], High = High Impedance [Low Drive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyBPR1999.05.18GS8322Z18/36/72(B/E/C)-xxxV165 Bump BGA—x18 Common I/O—Top View 1234567891011A NC A E1BB NC E3CKE ADV A A A A B NC A E2NC BA CK W G A A NC B C NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPA C D NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA D E NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA E F NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA F G NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA G H FT MCH NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC J K DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC K L DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC L M DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC M N DQPB NC V DDQ V SS NC NC NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A NC P RLBOAAATMSA0TCKAAAAR11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump Pitch(Package E)GS8322Z18/36/72(B/E/C)-xxxV165 Bump BGA—x36 Common I/O—Top View 1234567891011A NC A E1BC BB E3CKE ADV A A NC A B NC A E2BD BA CK W G A A NC B C DQPC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPB C D DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB D E DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB E F DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB F G DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB G H FT MCH NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQPD NC V DDQ V SS NC NC NC V SS V DDQ NC DQPA N P NC NC A A TDI A1TDO A A A NC P RLBOAAATMSA0TCKAAAAR11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump Pitch(Package E)GS8322Z18/36/72(B/E/C)-xxxVGS8322Z18/36E-xxxV 165-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn I Address Inputs A 18I Address Input DQ A DQ B DQ C DQ D I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active lowNC —No ConnectCK I Clock Input Signal; active high CKE I Clock Enable; active low W I Write Enable; active low E 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high FT I Flow Through / Pipeline Mode ControlG I Output Enable; active lowADV I Burst address counter advance enable; active highZQ I FLXDrive Output Impedance ControlLow = Low Impedance [High Drive], High = High Impedance [Low Drive])ZZ I Sleep mode control; active high LBO I Linear Burst Order mode; active lowTMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock MCH —Must Connect High V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322Z18/36/72(B/E/C)-xxxVFunctional DetailsClockingDeassertion of the Clock Enable (CKE) input blocks the Clock input from reaching the RAM's internal circuits. It may be used to suspend RAM operations. Failure to observe Clock Enable set-up or hold requirements will result in erratic operation.Pipeline Mode Read and Write OperationsAll inputs (with the exception of Output Enable, Linear Burst Order and Sleep) are synchronized to rising clock edges. Single cycle read and write operations must be initiated with the Advance/Load pin (ADV) held low, in order to load the new address. Device activation is accomplished by asserting all three of the Chip Enable inputs (E 1, E 2, and E 3). Deassertion of any one of the Enable inputs will deactivate the device. Function W B A B B B C B D Read H X X X X Write Byte “a”L L H H H Write Byte “b”L H L H H Write Byte “c”L H H L H Write Byte “d”L H H H L Write all Bytes L L L L L Write Abort/NOPLHHHHRead operation is initiated when the following conditions are satisfied at the rising edge of clock: CKE is asserted low, all three chip enables (E 1, E 2, and E 3) are active, the write enable input signals W is deasserted high, and ADV is asserted low. The address presented to the address inputs is latched into the address register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the next rising edge of clock the read data is allowed to propagate through the output register and onto the output pins.Write operation occurs when the RAM is selected, CKE is active, and the Write input is sampled low at the rising edge of clock. The Byte Write Enable inputs (B A , B B , B C, and B D ) determine which bytes will be written. All or none may be activated. A write cycle with no Byte Write inputs active is a no-op cycle. The pipelined NBT SRAM provides double late write functionality,matching the write command versus data pipeline length (2 cycles) to the read command versus data pipeline length (2 cycles). At the first rising edge of clock, Enable, Write, Byte Write(s), and Address are registered. The Data In associated with that address is required at the third rising edge of clock.Flow Through Mode Read and Write OperationsOperation of the RAM in Flow Through mode is very similar to operations in Pipeline mode. Activation of a Read Cycle and the use of the Burst Address Counter is identical. In Flow Through mode the device may begin driving out new data immediately after new address are clocked into the RAM, rather than holding new data until the following (second) clock edge. Therefore, in Flow Through mode the read pipeline is one cycle shorter than in Pipeline mode.Write operations are initiated in the same way, but differ in that the write pipeline is one cycle shorter as well, preserving the ability to turn the bus from reads to writes without inserting any dead cycles. While the pipelined NBT RAMs implement a double late write protocol in Flow Through mode a single late write protocol mode is observed. Therefore, in Flow Through mode, address and control are registered on the first rising edge of clock and data in is required at the data input pins at the second rising edge of clock.Synchronous Truth TableOperationType Address CK CKE ADV W Bx E 1E 2E 3G ZZDQNotesRead Cycle, Begin Burst R External L-H L L H X L H L L L Q Read Cycle, Continue Burst B Next L-H L H X X X X X L L Q 1,10NOP/Read, Begin Burst R External L-H L L H X L H L H L High-Z 2Dummy Read, Continue Burst B Next L-H L H X X X X X H L High-Z 1,2,10Write Cycle, Begin Burst W External L-H L L L L L H L X L D 3Write Cycle, Continue Burst B Next L-H L H X L X X X X L D1,3,10Write Abort, Continue Burst B Next L-H L H X H X X X X L High-Z 1,2,3,10Deselect Cycle, Power Down D None L-H L L X X H X X X L High-Z Deselect Cycle, Power Down D None L-H L L X X X X H X L High-Z Deselect Cycle, Power Down D None L-H L L X X X L X X L High-Z Deselect Cycle D None L-H L L L H L H L X L High-Z 1Deselect Cycle, Continue DNone L-H L H X X X X X X L High-Z 1Sleep ModeNone X X X X X X X X X H High-Z Clock Edge Ignore, StallCurrentL-HHXXXXXXXL-4Notes:1.Continue Burst cycles, whether read or write, use the same control inputs. A Deselect continue cycle can only be entered into if a Dese-lect cycle is executed first.2.Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the Wpin is sampled low but no Byte Write pins are active so no write operation is performed.3.G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off duringwrite cycles.4.If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the buswill remain in High Z.5. X = Don’t Care; H = Logic High; L = Logic Low; Bx = High = All Byte Write signals are high; Bx = Low = One or more Byte/Writesignals are Low6.All inputs, except G and ZZ must meet setup and hold times of rising clock edge.7.Wait states can be inserted by setting CKE high.8.This device contains circuitry that ensures all outputs are in High Z during power-up.9. A 2-bit burst counter is incorporated.10.The address counter is incriminated for all Burst continue cycles.GS8322Z18/36/72(B/E/C)-xxxVGS8322Z18/36/72(B/E/C)-xxxVDeselectNew ReadNew WriteBurst ReadBurst WriteWRBRBWDDBBWRD BWRDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input commandcodes as indicated in the Synchronous Truth Table.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipelined and Flow through Read/Write Control State DiagramWRPipelined and Flow Through Read Write Control State DiagramGS8322Z18/36/72(B/E/C)-xxxVPipeline Mode Data I/O State Diagram IntermediateIntermediateIntermediateIntermediateIntermediateIntermediateHigh Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)TransitionƒInput Command CodeKeyTransitionIntermediate State (N+1)Notes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateIntermediate ƒn n+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipeline Mode Data I/O State DiagramNext StateStateGS8322Z18/36/72(B/E/C)-xxxVFlow Through Mode Data I/O State Diagram High Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for: Pipeline and Flow Through Read Write Control State DiagramGS8322Z18/36/72(B/E/C)-xxxVBurst CyclesAlthough NBT RAMs are designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from read to write, multiple back-to-back reads or writes may also be performed. NBT SRAMs provide an on-chip burst address generator that can be utilized, if desired, to further simplify burst read or write implementations. The ADV control pin, when driven high, commands the SRAM to advance the internal address counter and use the counter generated address to read or write the SRAM. The starting address for the first cycle in a burst cycle series is loaded into the SRAM by driving the ADV pin low, into Load mode.Burst OrderThe burst address counter wraps around to its initial state after four addresses (the loaded address and three more) have beenaccessed. The burst sequence is determined by the state of the Linear Burst Order pin (LBO). When this pin is Low, a linear burst sequence is selected. When the RAM is installed with the LBO pin tied high, Interleaved burst sequence is selected. See the tables below for details.FLXDrive™The ZQ pin allows selection between NBT RAM nominal drive strength (ZQ low) for multi-drop bus applications and low drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Mode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down Control ZZ L or NC Active H Standby, I DD = I SB FLXDrive Output Impedance ControlZQL High Drive (Low Impedance)H or NCLow Drive (High Impedance)Note:There are pull-up devices on the ZQ and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.Note:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100GS8322Z18/36/72(B/E/C)-xxxVBurst Counter SequencesBPR 1999.05.18Sleep ModeDuring normal operation, ZZ must be pulled low, either by the user or by its internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after 2 cycles of wake up time.Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I SB 2. The duration of Sleep mode is dictated by the length of time the ZZ is in a High state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high, I SB 2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands may be applied while the SRAM is recovering from Sleep mode.Sleep Mode Timing DiagramtZZRtZZHtZZStKLtKHtKCCKZZDesigning for CompatibilityThe GSI NBT SRAMs offer users a configurable selection between Flow Through mode and Pipeline mode via the FT signal. Not all vendors offer this option, however most mark the pin V DD or V DDQ on pipelined parts and V SS on flow through parts. GSI NBT SRAMs are fully compatible with these sockets. Other vendors mark the pin as a No Connect (NC). GSI RAMs have an internal pull-up device on the FT pin so a floating FT pin will result in pipelined operation. If the part being replaced is a pipelined mode part, the GSI RAM is fully compatible with these sockets. In the unlikely event the part being replaced is a Flow Through device, the pin will need to be pulled low for correct operation.Absolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 4.6V V DDQ Voltage on V DDQ Pins –0.5 to V DDV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 4.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 4.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125oCT BIASTemperature Under Bias–55 to 125o CGS8322Z18/36/72(B/E/C)-xxxVNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component. Power Supply Voltage Ranges (1.8 V/2.5 V Version)ParameterSymbolMin.Typ.Max.UnitNotes1.8 V Supply Voltage V DD1 1.7 1.82.0V 2.5 V Supply Voltage V DD2 2.3 2.5 2.7V 1.8 V V DDQ I/O Supply Voltage V DDQ1 1.7 1.8V DD V 2.5 V V DDQ I/O Supply VoltageV DDQ22.32.5V DDVNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS8322Z18/36/72(B/E/C)-xxxVV DDQ2 & V DDQ1 Range Logic LevelsParameterSymbolMin.Typ.Max.UnitNotesV DD Input High Voltage V IH 0.6*V DD —V DD + 0.3V 1V DD Input Low VoltageV IL–0.3—0.3*V DDV1Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Recommended Operating TemperaturesParameterSymbolMin.Typ.Max.UnitNotesAmbient Temperature (Commercial Range Versions)T A 02570°C 2Ambient Temperature (Industrial Range Versions)T A–402585°C2Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DD ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFNote:These parameters are sample tested.(T A = 25= 2.5 V)AC Test ConditionsParameterConditionsDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceFigure 1Input high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 1Notes:1.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. GS8322Z18/36/72(B/E/C)-xxxVDC Electrical CharacteristicsParameterSymbolTest ConditionsMinMaxInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –1 uA 1 uA FT, ZQ, ZZ Input Current I IN V DD ≥ V IN ≥ 0 V –100 uA 100 uA Output Leakage CurrentI OLOutput Disable, V OUT = 0 to V DD–1 uA1 uADC Output Characteristics (1.8 V/2.5 V Version)ParameterSymbolTest ConditionsMinMax1.8 V Output High Voltage V OH1I OH = –4 mA, V DDQ = 1.6 V V DDQ – 0.4 V —2.5 V Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V1.7 V —1.8 V Output Low Voltage V OL1I OL = 4 mA —0.4 V2.5 V Output Low VoltageV OL2I OL = 8 mA—0.4 VGS8322Z18/36/72(B/E/C)-xxxVO p e r a t i n g C u r r e n t sP a r a m e t e r T e s t C o n d i t i o n s M o d eS y m b o l -250-225-200-166-150-133U n i t0t o 70°C –40 t o 85°C0t o 70°C–40 t o 85°C 0t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C O p e r a t i n g C u r r e n tD e v i c e S e l e c t e d ; A l l o t h e r i n p u t s ≥V I H o r ≤ V I LO u t p u t o p e n(x 72)P i p e l i n eI D DI D D Q380354003535035370353203034030280253002526025280252352025520m AF l o w T h r o u g hI D DI D D Q275252852525525265252352024520225202352021020220202101522015m A(x 36)P i p e l i n eI D DI D D Q300303203027525295252552527525225202452021020230201901521015m AF l o w T h r o u g hI D DI D D Q210152201520015210151901520015180151901517015180151601017010m A(x 18)P i p e l i n eI D DI D D Q260152801524015260152251524515200152201519015210151701019010m AF l o w T h r o u g hI D DI D D Q190102001018010190101701018010160101701015010160101401015010m AS t a n d b y C u r r e n tZ Z ≥ V D D – 0.2 V—P i p e l i n eI S B 608060806080608060806080m AF l o w T h r o u g hI S B608060806080608060806080m AD e s e l e c t C u r r e n tD e v i c e D e s e l e c t e d ; A l l o t h e r i n p u t s ≥ V I H o r ≤ V I L—P i p e l i n eI D D100115951109010585100851008095m AF l o w T h r o u g hI D D85100851008095809575907085m AN o t e s : 1.I D D a n d I D D Q a p p l y t o a n y c o m b i n a t i o n o f V D D 3, V D D 2, V D D Q 3, a n d V D D Q 2 o p e r a t i o n .2.A l l p a r a m e t e r s l i s t e d a r e w o r s t c a s e s c e n a r i o .。

负荷开关检验标准

Q/WJBZ负荷开关试验标准宁波伟吉电力科技有限公司发布前言本试验标准由宁波伟吉电力科技有限公司质量部提出本试验标准由宁波伟吉电力科技有限公司质量部归口本试验标准起草部门:质量部、研发部、办公室本试验标准主要起草人:负荷开关试验标准1目的及范围本试验标准规定了宁波伟吉电力科技有限公司对负荷开关(内置)的使用条件、电气性能、机械性能及环境性能等方面的技术要求和试验项目,规定了负荷开关的验收标准。

本试验标准适用于本公司用负荷开关的验收、定期确认、全性能检验。

2 规范性引用文件下列文件对于本文件的引用是必不可少的。

凡是注日期的引用文件,仅注日期的版本适用于本文件,凡是不注日期的引用文件,其最新版本(包括所有的修改单)适用于本文件。

GB/T 2423.1-2008 电工电子产品环境试验第2部分:试验方法试验A:低温GB/T 2423.2-2008 电工电子产品环境试验第2部分:试验方法试验B:高温GB/T2423.3-2006 电工电子产品环境试验第2部分:试验方法试验Cab:恒定湿热方法GB/T 2423.18 电工电子产品环境试验第2部分:试验试验Kb:盐雾,交变(氯化钠溶液)GB/T 2423.28-2005电工电子产品环境试验第2部分:试验方法试验T:锡焊GB/T 2423.32-2008 电工电子产品环境试验第2部分:试验方法试验Ta 润湿称量法可焊性GB/T 2423.60-2008 电工电子产品环境试验第2部分:试验方法引出端及整体安装件强度JB/T 10923 电子式电能表用磁保持继电器IEC 62055.31-2005 Electricity metering – Payment systems –Part 31: Particular requirements –Static payment meters for active energy (classes 1 and 2)GB/T 17215.211-2006 交流电测量设备通用要求、试验和试验条件第11部分:测量设备GB/T2828.1 计数抽样检验程序第1部分按接收质量限(AQL)检索的逐批检验抽样计划3 检验工具高低温交变湿热试验箱盐雾试验箱灼热丝试验仪红外测温仪推拉力计游标卡尺振动试验装置冲击试验装置继电器综合参数测试仪耐压测试仪钕铁硼强磁磁铁万用表4 技术要求4.1 包装要求包装设计应符合产品的性质、特点和储运条件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PreliminaryGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)2M x 18, 1M x 36, 512K x 7236Mb S/DCD Sync Burst SRAMs250 MHz –133 MHz1.8 V V DD 1.8 V I/O119-, 165-, & 209-Pin BGA Commercial Temp Industrial Temp Features• FT pin for user-configurable flow through or pipeline operation • Single/Dual Cycle Deselect selectable• IEEE 1149.1 JTAG-compatible Boundary Scan• ZQ mode pin for user-selectable high/low output drive • 1.8 V +10%/–10% core power supply • 1.8 V +10%/–10% core power supply • 1.8 V I/O supply• LBO pin for Linear or Interleaved Burst mode• Internal input resistors on mode pins allow floating mode pins • Default to SCD x18/x36 Interleaved Pipeline mode • Byte Write (BW) and/or Global Write (GW) operation • Internal self-timed write cycle• Automatic power-down for portable applications• JEDEC-standard 119-, 165-, and 209-bump BGA package • Pb-Free packages availableFunctional DescriptionApplicationsThe GS8322V18/36/72 is a 37,748,736-bit high performance synchronous SRAM with a 2-bit burst address counter. Although of a type originally developed for Level 2 Cache applications supporting high performance CPUs, the device now finds application in synchronous SRAM applications, ranging from DSP main store to networking chip set support.ControlsAddresses, data I/Os, chip enable (E1), address burst control inputs (ADSP, ADSC, ADV), and write control inputs (Bx, BW, GW) are synchronous and are controlled by a positive-edge-triggered clock input (CK). Output enable (G) and power down control (ZZ) are asynchronous inputs. Burst cycles can be initiated with either ADSP or ADSC inputs. In Burst mode, subsequent burst addresses are generated internally and are controlled by ADV. The burst address counter may be configured to count ineither linear or interleave order with the Linear Burst Order (LBO) input. The Burst function need not be used. New addresses can be loaded on every cycle with no degradation of chip performance.Flow Through/Pipeline ReadsThe function of the Data Output register can be controlled by the user via the FT mode . Holding the FT mode pin low places the RAM in Flow Through mode, causing output data to bypass the Data Output Register. Holding FT high places the RAM inPipeline mode, activating the rising-edge-triggered Data Output Register.SCD and DCD Pipelined ReadsThe GS8322V18/36/72 is a SCD (Single Cycle Deselect) and DCD (Dual Cycle Deselect) pipelined synchronous SRAM. DCD SRAMs pipeline disable commands to the same degree as read commands. SCD SRAMs pipeline deselect commands one stage less than read commands. SCD RAMs begin turning off their outputs immediately after the deselect command has been captured in the input registers. DCD RAMs hold the deselect command for one full cycle and then begin turning off their outputs just after the second rising edge of clock. The user may configure this SRAM for either mode of operation using the SCD mode input.Byte Write and Global WriteByte write operation is performed by using Byte Write enable (BW) input combined with one or more individual byte write signals (Bx). In addition, Global Write (GW) is available for writing all bytes at one time, regardless of the Byte Write control inputs.FLXDrive™The ZQ pin allows selection between high drive strength (ZQ low) for multi-drop bus applications and normal drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Parameter Synopsis-250-225-200-166-150-133UnitPipeline 3-1-1-1KQ t KQ (x72)tCycle 3.04.0 3.04.4 3.05.0 3.56.0 3.86.7 4.07.5ns ns Curr (x18)Curr (x36)Curr (x72)285350440265320410245295370220260320210240300185215265mA mA mA Flow Through 2-1-1-1t KQ tCycle 6.56.57.07.07.57.58.08.08.58.58.58.5ns ns Curr (x18)Curr (x36)Curr (x72)205235315195225295185210265175200255165190240155175230mA mA mAGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)209-Bump BGA—x72 Common I/O—Top View (Package C)1234567891011A DQ G DQ G A E2ADSP ADSC ADV E3A DQB DQ B AB DQ G DQ G BC BG NC BW A BB BF DQ B DQ B BC DQ G DQ G BH BD NC E1NC BE BA DQ B DQ B CD DQ G DQ G V SS NC NC G GW NC V SS DQ B DQ B DE DQP G DQP C V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQPF DQP B EF DQ C DQ C V SS V SS V SS ZQ V SS V SS V SS DQ F DQ F FG DQ C DQ C V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ F DQ F GH DQ C DQ C V SS V SS V SS MCL V SS V SS V SS DQ F DQ F H J DQ C DQ C V DDQ V DDQ V DD MCL V DD V DDQ V DDQ DQ F DQ F J K NC NC CK NC V SS MCL V SS NC NC NC NC K L DQ H DQ H V DDQ V DDQ V DD FT V DD V DDQ V DDQ DQ A DQ A L M DQ H DQ H V SS V SS V SS MCL V SS V SS V SS DQ A DQ A M N DQ H DQ H V DDQ V DDQ V DD SCD V DD V DDQ V DDQ DQ A DQ A N P DQ H DQ H V SS V SS V SS ZZ V SS V SS V SS DQ A DQ A P R DQP D DQP H V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQP A DQP E R T DQ D DQ D V SS NC NC LBO NC NC V SS DQ E DQ E T U DQ D DQ D NC A A A A A A DQ E DQ E U V DQ D DQ D A A A A1A A A DQ E DQ E V W DQ D DQ D TMS TDI A A0A TDO TCK DQ E DQ E W11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump PitchGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)GS8322V72 209-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset Inputs.An IAddress InputsDQ A DQ B DQ C DQ D DQ E DQ F DQ G DQ H I/O Data Input and Output pinsB A , B B I Byte Write Enable for DQ A , DQ B I/Os; active low BC ,BD I Byte Write Enable for DQ C , DQ D I/Os; active low BE , BF , BG ,B HI Byte Write Enable for DQ E , DQ F , DQ G , DQ H I/Os; active lowNC —No ConnectCK I Clock Input Signal; active highGW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSCI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep Mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowSCD I Single Cycle Deselect/Dual Cycle Deselect Mode ControlMCH IMust Connect High MCL Must Connect Low BW I Byte Enable; active lowZQ I FLXDrive Output Impedance Control(Low = Low Impedance [High Drive], High = High Impedance [Low Drive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCKIScan Test ClockGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322V72 209-Bump BGA Pin Description (Continued)SymbolTypeDescriptionGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)165-Bump BGA—x18 Commom I/O—Top View (Package E)1234567891011A NC A E1BB NC E3BW ADSC ADV A A AB NC A E2NC BA CK GW G ADSP A NC BC NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPA CD NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA DE NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA EF NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA FG NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA GH FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ HJ DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC JK DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC KL DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC LM DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC MN DQPB SCD V DDQ V SS NC A NC V SS V DDQ NC NC NP NC NC A A TDI A1TDO A A A A PR LBO A A A TMS A0TCK A A A A R11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump PitchGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)165-Bump BGA—x36 Common I/O—Top View 1234567891011A NC A E1BC BB E3BW ADSC ADV A NC A B NC A E2BD BA CK GW G ADSP A NC B C DQPC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPB C D DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB D E DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB E F DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB F G DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB G H FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQPD SCD V DDQ V SS NC A NC V SS V DDQ NC DQPA N P NC NC A A TDI A1TDO A A A A P RLBOAAATMSA0TCKAAAAR11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump Pitch(Package E)GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)GS8322V18/36 165-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn I Address Inputs DQ A DQ B DQ C DQ D I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active low (x36 Version)NC —No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active low GW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active l0w ADSC, ADSPI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock MCL —Must Connect LowSCD —Single Cycle Deselect/Dual Cyle Deselect Mode ControlV DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)119-Bump BGA—x36 Common I/O—Top View1234567A V DDQ A A ADSP A A V DDQ A B NC A A ADSC A A NC B C NC A A V DD A A NC C D DQ DQP V SS ZQ V SS DQP B DQ B D E DQ DQ V SS E1V SS DQ B DQ B E F V DDQ DQ V SS G V SS DQ B V DDQ F G DQ DQ BC ADV BB DQ B DQ B G H DQ DQ V SS GW V SS DQ B DQ B H J V DDQ V DD NC V DD NC V DD V DDQ J K DQ D DQ D V SS CK V SS DQ A DQ A K L DQ D DQ D BD SCD BA DQ A DQ A L M V DDQ DQ D V SS BW V SS DQ A V DDQ M N DQ D DQ D V SS A1V SS DQ A DQ A N P DQ D DQP D V SS A0V SS DQP A DQ A P R NC A LBO V DD FT A NC R T NC NC A A A A ZZ T UV DDQTMSTDITCKTDONCV DDQU7 x 17 Bump BGA—14 x 22 mm 2 Body—1.27 mm Bump PitchC C C C C C2C C CGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)119-Bump BGA—x18 Common I/O—Top View1234567A V DDQ A A ADSP A A V DDQ AB NC A A ADSC A A NC BC NC A A V DD A A NC CD DQ B NC V SS ZQ V SS DQP A NC DE NC DQ B V SS E1V SS NC DQ A EF V DDQ NC V SSG V SS DQ A V DDQ FG NC DQ B BB ADV NC NC DQ A GH DQ B NC V SS GW V SS DQ A NC HJ V DDQ V DD NC V DD NC V DD V DDQ JK NC DQ B V SS CK V SS NC DQ A KL DQ B NC NC SCD BA DQ A NC LM V DDQ DQ B V SS BW V SS NC V DDQ MN DQ B NC V SS A1V SS DQ A NC NP NC DQP B V SS A0V SS NC DQ A PR NC A LBO V DD FT A NC RT NC A A A A A ZZ TU V DDQ TMS TDI TCK TDO NC V DDQ U7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump PitchGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)GS8322V18/36 119-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn I Address Inputs DQ A DQ B DQ C DQ D I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active lowNC —No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active low GW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low G I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSCI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])SCD I Single Cycle Deselect/Dual Cyle Deselect Mode ControlTMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock V DD I Core power supply V SS I I/O and Core Ground V SS I I/O and Core Ground V DDQIOutput driver power supplyGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)A1A0A0A1D0D1Q1Q0Counter LoadD QDQRegisterRegisterDQRegisterDQRegisterDQRegisterD QRegisterD QRegisterD QRegisterDQR e g i s t e rDQRegisterA0–An LBO ADV CK ADSC ADSP GW BW E 1FT GZZPower Down ControlMemory Array36364AQD DQx1–DQx93636Note: Only x36 version shown for simplicity.SCD3636B AB BB CB DGS8322V18/36 Block DiagramMode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down Control ZZ L or NC Active H Standby, I DD = I SB Single/Dual Cycle Deselect Control SCD L Dual Cycle Deselect H or NC Single Cycle Deselect FLXDrive Output Impedance ControlZQL High Drive (Low Impedance)H or NCLow Drive (High Impedance)GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Note:There are pull-up devices on the ZQ, SCD, and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.The burst counter wraps to initial state on the 5th clock.The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110I nterleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Burst Counter SequencesBPR 1999.05.18GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Byte Write Truth TableFunctionGWBWB AB BB CB DNotesRead H H X X X X 1Read H L H H H H 1Write byte a H L L H H H 2, 3Write byte b H L H L H H 2, 3Write byte c H L H H L H 2, 3, 4Write byte d H L H H H L 2, 3, 4Write all bytes H L L L L L 2, 3, 4Write all bytesLXXXXX1.All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.2.Byte Write Enable inputs B A , B B , B C , and/or B D may be used in any combination with BW to write single or multiple bytes.3.All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.4.Bytes “C ” and “D ” are only available on the x36 version.Synchronous Truth TableOperationAddress UsedState Diagram Key 5E 1ADSPADSCADVW 3DQ 4Deselect Cycle, Power Down None X H X L X X High-Z Read Cycle, Begin Burst External R L L X X X Q Read Cycle, Begin Burst External R L H L X F Q Write Cycle, Begin Burst External W L H L X T D Read Cycle, Continue Burst Next CR X H H L F Q Read Cycle, Continue Burst Next CR H X H L F Q Write Cycle, Continue Burst Next CW X H H L T D Write Cycle, Continue Burst Next CWH X H L T D Read Cycle, Suspend Burst Current X H H H F Q Read Cycle, Suspend Burst Current H X H H F Q Write Cycle, Suspend Burst Current X H H H T D Write Cycle, Suspend BurstCurrentHXHHTDNotes:1.X = Don’t Care, H = High, L = Low2.W = T (True) and F (False) is defined in the Byte Write Truth Table preceding3.G is an asynchronous input. G can be driven high at any time to disable active output drivers. G low can only enable active drivers (shownas “Q” in the Truth Table above).4.All input combinations shown above are tested and supported. Input combinations shown in gray boxes need not be used to accomplishbasic synchronous or synchronous burst operations and may be avoided for simplicity.5.Tying ADSP high and ADSC low allows simple non-burst synchronous operations. See BOLD items above.6.Tying ADSP high and ADV low while using ADSC to load new addresses allows simple burst operations. See ITALIC items above.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)First WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWXXWRRWRXXX S i m p l e S y n c h r o n o u s O p e r a t i o nS i m p l e B u r s t S y n c h r o n o u s O p e r a t i o nCR RCWCRCRNotes:1.The diagram shows only supported (tested) synchronous state transitions. The diagram presumes G is tied low.2.The upper portion of the diagram assumes active use of only the Enable (E1) and Write (B A , B B , B C , B D , BW, and GW) control inputs, andthat ADSP is tied high and ADSC is tied low.3.The upper and lower portions of the diagram together assume active use of only the Enable, Write, and ADSC control inputs andassumes ADSP is tied high and ADV is tied low.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Simplified State DiagramFirst WriteFirst ReadBurst WriteBurst ReadDeselectR WCRCWXXWRRWRXXX CRR CW CRCRW CWW CWNotes:1.The diagram shows supported (tested) synchronous state transitions plus supported transitions that depend upon the use of G.e of “Dummy Reads” (Read Cycles with G High) may be used to make the transition from read cycles to write cycles without passingthrough a Deselect cycle. Dummy Read cycles increment the address counter just like normal read cycles.3.Transitions shown in grey tone assume G has been pulsed high long enough to turn the RAM’s drivers off and for incoming data to meetData Input Set Up Time.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Simplified State Diagram with GAbsolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 3.6V V DDQ Voltage in V DDQ Pins –0.5 to 3.6V V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 3.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 3.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125o C T BIASTemperature Under Bias–55 to 125oCGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Note:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component. Power Supply Voltage RangesParameterSymbolMin.Typ.Max.UnitNotes1.8 V Supply Voltage V DD 1.6 1.82.0V 1.8 V V DDQ I/O Supply VoltageV DDQ1.61.82.0VNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed3.6 V maximum, with a pulse width not to exceed 20% tKC.Recommended Operating TemperaturesParameterSymbolMin.Typ.Max.UnitNotesAmbient Temperature (Commercial Range Versions)T A 02570°C 2Ambient Temperature (Industrial Range Versions)T A–402585°C2Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Logic LevelsParameterSymbolMin.Typ.Max.UnitNotesV DD Input High Voltage V IH 0.6*V DD —V DD + 0.3V 1V DD Input Low Voltage V IL –0.3—0.3*V DD V 1V DDQ I/O Input High Voltage V IHQ 0.6*V DD —V DDQ + 0.3V 1,3V DDQ I/O Input Low VoltageV ILQ–0.3—0.3*V DDV1,3Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed3.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DD ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFNote:These parameters are sample tested.(T A = 25= 2.5 V)AC Test ConditionsParameterConditionsInput high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 11.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)DQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceDC Electrical CharacteristicsParameterSymbolTest ConditionsMinMaxInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –1 uA 1 uA ZZ Input Current I IN1V DD ≥ V IN ≥ V IH 0 V ≤ V IN ≤ V IH –1 uA –1 uA 1 uA 100 uA FT, SCD, and ZQ Input Current I IN2V DD ≥ V IN ≥ V IL 0 V ≤ V IN ≤ V IL–100 uA –1 uA 1 uA 1 uA Output Leakage Current I OL Output Disable, V OUT = 0 to V DD –1 uA 1 uA Output High Voltage V OH1I OH = –4 mA, V DDQ = 1.6 V V DDQ – 0.4 V—Output Low VoltageV OL1I OL = 4 mA, V DD = 1.6 V—0.4 VGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)O p e r a t i n g C u r r e n t sP a r a m e t e r T e s t C o n d i t i o n s M o d eS y m b o l -250-225-200-166-150-133U n i t0t o 70°C –40 t o 85°C0t o 70°C–40 t o 85°C 0t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C O p e r a t i n g C u r r e n tD e v i c e S e l e c t e d ; A l l o t h e r i n p u t s ≥V I H o r ≤ V I LO u t p u t o p e n(x 72)P i p e l i n eI D DI D D Q380604006035060370603205034050280403004026040280402353025530m AF l o w T h r o u g hI D DI D D Q275402854025540265402353024530225302353021030220302102022020m A(x 36)P i p e l i n eI D DI D D Q300503205027545295452554027540225352453521030230301902521025m AF l o w T h r o u g hI D DI D D Q210252202520025210251902020020180201902017020180201601517015m A(x 18)P i p e l i n eI D DI D D Q260252802524025260252252024520200202202019020210201701519015m AF l o w T h r o u g hI D DI D D Q190152001518015190151701518015160151701515015160151401515015m AS t a n d b y C u r r e n tZ Z ≥ V D D – 0.2 V—P i p e l i n eI S B 608060806080608060806080m AF l o w T h r o u g hI S B608060806080608060806080m AD e s e l e c t C u r r e n tD e v i c e D e s e l e c t e d ; A l l o t h e r i n p u t s ≥ V I H o r ≤ V I L—P i p e l i n eI D D100115951109010585100851008095m AF l o w T h r o u g hI D D85100851008095809575907085m AN o t e s : 1.I D D a n d I D D Q a p p l y t o a n y c o m b i n a t i o n o f V D D 3, V D D 2, V D D Q 3, a n d V D D Q 2 o p e r a t i o n .2.A l l p a r a m e t e r s l i s t e d a r e w o r s t c a s e s c e n a r i o .AC Electrical CharacteristicsParameterSymbol-250-225-200-166-150-133UnitMinMaxMinMaxMinMaxMinMaxMinMaxMinMaxPipelineClock Cycle Time tKC 4.0— 4.4— 5.0— 6.0— 6.7—7.5—ns Clock to Output Valid (x18/x36)tKQ — 2.5— 2.7— 3.0— 3.5— 3.8— 4.0ns Clock to Output Valid (x72)tKQ — 3.0— 3.0— 3.0— 3.5— 3.8— 4.0ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Setup time tS 1.2— 1.3— 1.4— 1.5— 1.5— 1.5—ns Hold time tH 0.2—0.3—0.4—0.5—0.5—0.5—ns Flow ThroughClock Cycle Time tKC 6.5—7.0—7.5—8.0—8.5—8.5—ns Clock to Output ValidtKQ — 6.5—7.0—7.5—8.0—8.5—8.5ns Clock to Output Invalid tKQX 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Clock to Output in Low-ZtLZ 1 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Setup time tS 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Hold time tH 0.5—0.5—0.5—0.5—0.5—0.5—ns Clock HIGH Time tKH 1.3— 1.3— 1.3— 1.3— 1.5— 1.7—ns Clock LOW Time tKL 1.5— 1.5— 1.5— 1.5— 1.7—2—ns Clock to Output in High-Z (x18/x36)tHZ 1 1.5 2.5 1.5 2.7 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns Clock to Output in High-Z (x72)tHZ 1 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns G to Output Valid (x18/x36)tOE — 2.5— 2.7— 3.0— 3.5— 3.8— 4.0ns G to Output Valid(x72)tOE — 3.0— 3.0— 3.0— 3.5— 3.8— 4.0ns G to output in Low-Z tOLZ 10—0—0—0—0—0—ns G to output in High-Z (x18/x36)tOHZ 1— 2.5— 2.7— 3.0— 3.0— 3.0— 3.0ns G to output in High-Z (x72)tOHZ 1— 3.0— 3.0— 3.0— 3.0— 3.0— 3.0ns ZZ setup time tZZS 25—5—5—5—5—5—ns ZZ hold time tZZH 21—1—1—1—1—1—ns ZZ recoverytZZR20—20—20—20—20—20—nsGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Notes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Pipeline Mode Timing (SCD)Begin Read A Cont Cont Deselect Write B Read C Read C+1Read C+2Read C+3ContDeselecttHZtKQX tKQtLZtHtStOHZtOEtHtStHtStHtStHtStHtStStHtStHtStHtSBurst ReadtKCtKL tKH Single Write Single ReadQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)ABCDeselected with E1E1 masks ADSPE2 and E3 only sampled with ADSP and ADSCADSC initiated readCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQdGS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)Flow Through Mode Timing (SCD)Begin Read A ContCont Write B Read C Read C+1Read C+2Read C+3Read C Cont DeselecttHZtKQXtKQ tLZtH tStOHZtOEtHtS tHtS tHtStHtS tHtS tHtStHtS tHtS tH tS tHtS tKCtKL tKHABCQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)Q(C)E2 and E3 only sampled with ADSCADSC initiated readDeselected with E1Fixed HighCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQd。