AlteraFPGA开发软件安装指南

FPGA软件安装步骤

注意:把软件拷贝到没有中文和空格的目录下, 然后按照以下步骤进行安装( 请注意,步骤 2,3 不能调换,不然软 件运行的时候会出现错误) : 1. 安装 11.0_quartus_windows.exe; 2. 安装文件夹下 11.0_devices_windows 下的 setup.exe; 3. 安装 11.0sp1_quartus_windows.exe; 4. 通过 Crack_QII_11.0_SP1_Windows.rar 进行破解 (32bit 系统 使用 x86 的解补丁,64bit 系统使用 x64 的破解补丁) ; 5. 安装 11.0_legacy_nios2_windows.exe ; 6. 安装 11.0sp1_legacy_nios2_windows.exe ; 7. 安装 modelsim-win32-10.0c-se.exe 或 modelsim-win64-10.0c-se.exe(根据系统决定,32 位系统,选择 前者,否则,选择后者) ; 8. 根据 modelsim_se_10.0c.rar 进行破解; (一) 软件安装, 请看光盘 A/视频/NIOSII 视频教程 11.0(02)--软件 安装.wmv (二)USB Blaster 驱动的安装,请看光盘 A/视频/NIOSII 视频教程 11.0(05)--usb blaster 驱动安装 .wmv

21EDA-Altera-FPGA开发板使用入门

在自己做这个实验的时候,需要确认自己的开发软件是否已经安装好了,确认自己的下载器是否已经可以使用了。

如果还不熟悉的,可以看看下面两个文件QuartusII 9.0破解全过程.pdf下载器的安装.pdf实验要求:PC电脑一台,配置越高越好。

开发软件:QuartusII9.0SP2开发板型号:A-C8V4实验结果:学习Altera公司的FPGA开发软件QuartusII入门使用。

首先打开QuartusII9.0SP2的开发软件。

你有三种方法可以打开。

第一:如下图,桌面上有快捷图标。

双击就可以了。

第二:如下图,在开始菜单里面可以找到。

第三:如下图,在开始菜单里面也可以找到。

如下图:打开QII软件了如下图:我们可以把这个关闭了。

如下图:新建一个工程File->New Project Wizrd….如下图:点击Next如下图:这里我们要设置工程路径,工程名和顶层名。

点第一排三个点点那里如下图:我们把工程路径放在J盘下面FPGA_TEST文件夹;J:\FPGA_TEST设置好了,点击Next如下图:直接点击Next如下图:这里我们需要对CPU进行设置,也就是设置成和我们开发板对应的芯片。

Family 要选择Cyclone II如下图:如下图:选择芯片的封装,PQFP如下图:如下图:选择芯片的管教数目,我们这里是208个脚如下图:如下图:选择速度等级,我们这里选择8如下图:如下图:选择我们最后设置好的芯片。

然后点击Next如下图:然后点击Next如下图:然后点击Finish如下图:如下图:然后点击Next如下图:点击File->New 新建一个我们用来编写程序的窗口。

如下图:如果你使用Verilog语言,就选择Verilog HDL File 然后点击OK如下图:如果你使用VHDL语言,就选择VHDL File 然后点击OK 我们这里用VHDL作为演示如下图:会在右边出现程序编写的空白窗口。

如下图:假设我们已经编写了程序A-C8V4-开发板资料A\A-C8V4开发板资料\A-C8V4开发板-整理的VHDL程序\ 15实验十五:LED流水灯A (用这个里面的程序)如下图:我们的程序编写了,要保存File -> Save如下图:如下图:保存了之后,就要编译,如下图:我们编译的时候出错了。

第1章 FPGA开发简介-Altera FPGA系统设计实用教程(第2版)-李莉-清华大学出版社

下载电缆

ByteBlaster II

USB-Blaster

Ethernet Blaster

(1)完全符合设计人员的设计思路,从功能描述开 始,到物理实现的完成。

(2)设计更加灵活。 (3)设计易于移植和更改。 (4)易于进行大规模、复杂电路的设计实现。 (5)设计周期缩短。

1.4.2 典型FPGA开发流程

电路功能设计

设计输入

编译 综合

功能仿真

FPGA适配(布局布线)

时序仿真

配置

硬件环境要求高,软件投资大,通用性强,不面向具体 公司的PLD器件。

PLD制造厂商开发的专用软件工具则具有硬件环境要求 低,软件投资小的特点,并且很多PLD厂商的开发工具 是免费提供的,因此其市场占有率非常大;缺点是只针 对本公司的PLD器件,有一定的局限性。

1.4 基于FPGA的开发流程

1.4.1 FPGA设计方法概论 FPGA的设计方法属于自上而下的设计方法

第1章 FPGA开发简介

1.1 可编程逻辑器件概述 1.2 FPGA芯片 1.3 FPGA开发工具 1.4 基于FPGA的开发流程

1.1 可编程逻辑器件概述

可编程逻辑器件(Programmable Logic Device,简

称PLD)

可编程逻辑器件

PLD

低密度 PLD

高密度 PLD

PROM

PLA

PAL

GAL

EPLD CPLD FPGA

70年代初

70年代末 80年代初

80年代中期

80年代中期 及以后

图1-1 PLD器件的发展流程

低密度PLD的基本结构参考图

输入项 乘积项

或项

输

输

ALTERA FPGA EP2C5Q 开发板用户手册

ALTERA FPGA EP2C5Q 开发板用户手册上海亿家网络有限公司版权所有 © 上海亿家网络有限公司 2013。

保留一切权利。

非经上海亿家网络有限公司书面同意,任何单位和个人不得擅自摘抄、复制本手册内容的部分或全部,并不得以任何形式传播。

本手册中描述的产品中,可能包含上海亿家网络有限公司及其可能存在的许可人享有版权的软件,除非获得相关权利人的许可,否则,任何人不能以任何形式对前述软件进行复制、分发、修改、摘录、反编译、反汇编、解密、反向工程、转让、分许可以及其他侵犯软件版权的行为。

本手册描述了ALTERA FPGA EP2C5Q开发板的硬件资源、安装、使用和设计原理,用以指导开发板使用。

本手册对应开发板的主要用户为高校学生、电子爱好者、科研单位、企事业单位的开发设计人员,适合于产品原型的快速开发、学生参加各种电子设计大赛、学习FPGA技术入门、课程设计及毕业设计等,亦可用于系统设计前期快速评估,特别适合于FPGA、NIOSII、SOPC 快速入门和产品开发及验证。

1 安全警告和注意事项 (5)2开发板主要器件及硬件资源 (7)2.1 主要器件 (7)2.2 硬件资源 (7)2.3 PCB和尺寸 (9)3 开发板的安装和使用 (10)3.1 开发板安装 (10)3.2 开发板的使用 (11)4开发板设计详细说明 (17)4.1 电源电路 (17)4.2 时钟电路 (17)4.3 复位电路 (18)4.4 JTAG接口电路 (18)4.5 AS接口电路 (19)4.6 LED电路 (19)4.7 存储器SDRAM电路 (19)4.8外部扩展IO (21)5技术支持与保修 (23)5.1关于技术支持 (23)5.2 关于产品保修 (23)附录常见问题解答 (24)1安全警告和注意事项为正确、安全地使用本开发板,请您在使用前仔细阅读本安全警告和注意事项,并在使用时严格遵循。

说明如无特别说明,本节描述的“开发板”包含开发板本身及其配件。

Altera FPGA开发说明(QuartusII 7.2 & ModelSim 6.5)

Altera FPGA开发说明(QuartusII 7.2 & ModelSim 6.5)By ccx于2010-11-22一、说明1、本例程中的代码是用Verilog编写的,但本文并不探讨Verilog本身。

推荐王金明的一本书作为入门书籍,既讲到了Verilog,也讲到了QuartusII 的使用,还探讨了Modelsim的使用(很难得地讲到了Test Bench的编写)。

2、QuartusII 7.2软件的文本编辑器不支持中文输入,Modelsim 6.5的编辑窗口也不尽如人意。

使用Notepad++(目前只支持Windows平台,方便易用)也可使用Gvim(陆博推荐,因为linux系统中也有对应的编辑工具)3、本例中的程序功能说明一个4位二进制计数器,显示到FPGA开发板(DE2-70)的4个LED上。

4、本例的验证平台为Altera公司的DE2-70开发板二、使用QuartusII 7.2和ModelSim 6.5进行Altera FPGA开发2.1、FPGA开发流程图2.2、建立QuartusII项目这里不讨论原理图输入法,也不讨论多个模块如何组织在1个顶层模块之下。

在建立项目之前,我已经编写好counter.v文件,并把它放在E:\counter目录下。

打开QuartusII软件,File→New Project Wizard…,可开始建立项目的流程。

2.2.1、向导介绍建立项目时要做的工作2.2.1、填写目录、项目名、top-level entity名注意:top-level entity需要正确填写,因为本例中只有一个模块counter,而且其为top-level entity,所以填写如下。

2.2.2、为项目添加文件2.2.3、选定器件Cyclone II系列,器件编号为EP2C70F896C6(可以网上搜索该器件号的意思)。

2.2.4、EDA工具设置默认即可,但可以留意Simulation一项,因为之后用ModelSim 6.5做时序仿真与它有关。

ALTERA软件安装说明

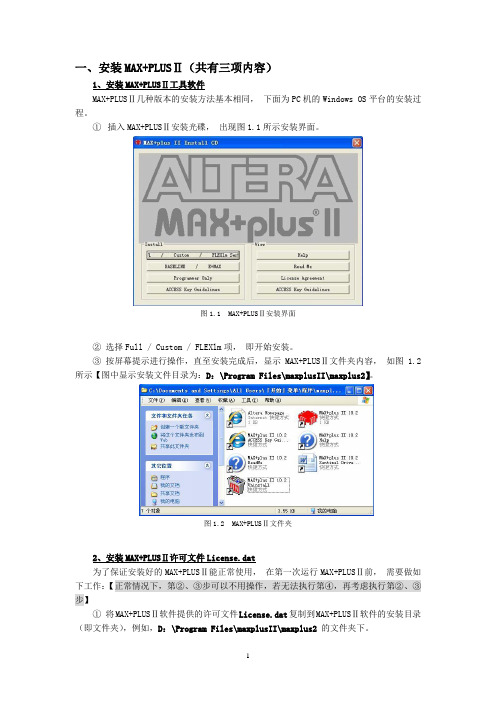

一、安装MAX+PLUSⅡ(共有三项内容)1、安装MAX+PLUSⅡ工具软件MAX+PLUSⅡ几种版本的安装方法基本相同,下面为PC机的Windows OS平台的安装过程。

①插入MAX+PLUSⅡ安装光碟,出现图1.1所示安装界面。

图1.1 MAX+PLUSⅡ安装界面②选择Full / Custom / FLEXlm项,即开始安装。

③按屏幕提示进行操作,直至安装完成后,显示MAX+PLUSⅡ文件夹内容,如图 1.2所示【图中显示安装文件目录为:D:\Program Files\maxplusII\maxplus2】。

图1.2 MAX+PLUSⅡ文件夹2、安装MAX+PLUSⅡ许可文件License.dat为了保证安装好的MAX+PLUSⅡ能正常使用,在第一次运行MAX+PLUSⅡ前,需要做如下工作:【正常情况下,第②、③步可以不用操作,若无法执行第④,再考虑执行第②、③步】①将MAX+PLUSⅡ软件提供的许可文件License.dat复制到MAX+PLUSⅡ软件的安装目录(即文件夹),例如,D:\Program Files\maxplusII\maxplus2的文件夹下。

②用文本编辑器打开MAX+PLUSⅡ软件安装目录下(例如:D:\Program Files\maxplusII\maxplus2)中的配置文件maxplus2.ini。

③在[Licensing]项下,添加如下申明语句后原名保存:LM_LICENSE_FILE=D:\Program Files\maxplusII\maxplus2\license.dat;④在桌面双击MAX+PLUSⅡ图标,或选择Windows 系统中“开始”菜单的程序项中的maxplusII(或Altera)组内的MAX+PLUSⅡ 10.2项(如图1.3),开始运行MAX+PLUSⅡ。

图1.3 MAX+PLUSⅡ的启动⑤进入MAX+PLUSⅡ界面后,选择菜单命令Option / License Setup,出现图 1.4所示License Setup界面。

EDA软件安装步骤

Quartus II 的版本,一般听到比较多的是5.1,7.1,8.1,9.1,但其实对于一般人而言,都差不多,基本能满足您的要求,只是5.1这些低版本编译速度慢一点,界面丑一点,玩过9.1的人,再看5.1可能会恶心了,视觉的冲击是没有谁不会去追求的。

实际上Quartus II 9.1 SP1也已经出来了,是个9.1的补丁升级版,但9.1应该能满足你们的要求,所以我这里抱歉我只做一个9.1的安装说明了。

貌似在网上我没去看过有没有相应的安装教程,或许可能是我没找过,所以,顺便给大家做个详细的教程,希望会有一点点的帮助,请大家笑纳。

安装文件有2个,一个是Quartus II 9.1的压缩包(要没软件的话来我寝室找Crazy Bingo,我不入地狱谁入地狱,呵呵),一个是破解文档的压缩包,详细安装说明,如下所示,其实安装简单,只是破解有那么一点点的麻烦,只是个窍门,方法很多!!!如有争议,请联系Crazy Bingo!!!如有不懂,请联系Crazy Bingo!!!一、Quartus II 9.1 软件的安装1、解压缩生成2、打开文件夹,双击quartus 里面的(地球人都知道)3、一个劲的next,不要怕,勇敢的孩子向前跑!!!4、很明显嘛,accept,不然没门,接受总比拒绝要好一点,是吧?5、随便填,当然你要像如下那样填也可以,Crazy Bingo他不会介意的。

6、要是你的C盘足够大的话,可以默认路径不改变,其实从文件系统的概念上来说,根本是会影响操作系统的速度,但是你要是要改变盘符的话,要注意两点(1)不能出现在中文路径下面(2)地址不能出现空格,否则有什么灵异事件发生,不要怪我。

下面是我改变的路径,反正只要最终地址不出现空格和汉字就可以了7、还是Next,既然选择了远方便不顾风雨兼程8、很明显嘛,当然是完全安装,要是你不想完全也没关系,我也不知道会有什么样的结果。

9、安装火热进行中,您请稍后。

QUARTUSII51安装说明

QuartusII 5.1安装说明1.软件简介Altera的Quartus II软件提供了完整的多平台设计环境,能满足各种FPGA、CPLD的设计需要,是片上可编程系统(SOPC)设计必需的综合性环境。

Quarttus II软件支持VHDL、Verilog、AHDL语言,原理图的设计,并支持多种语言嵌套使用。

Quartus II也可以利用第三方的综合工具,如:Leonardo Spectrum、Synplify Pro、FPGA ComplierII,并能直接调用这些工具。

同样,Quartus II具备仿真功能,同时也支持第三方的仿真工具,例如ModelSim、VCS、NC-V erilog、NC-VHDL、NC-Sim等。

Quartus II包括模块化的编译器。

编译器包括的功能模块有分析/综合器(Analysis&Synthesis)、适配器(Fitter)、装配器(Assembler)、时序分析器(Timing Analyzer)、设计辅助模块(Design Assistant)、EDA网表文件生成器(EDA Netlist Writer)、编辑数据接口(Compiler Database Interface)等。

可以通过选择Start Compilation来运行全局编译,也可以选择Start单独运行各个模块。

Quartus II还包含许多十分有用的LPM(Library of Parameterized Modules)模块,它们是复杂或者高级系统构建的重要组成部分,在SOPC设计中将被大量使用。

Altera提供的可参数化宏功能模块和LPM函数均基于Altera器件的结构做了优化设计。

在许多情况下,一些电路模块必须通过应用LPM才能构建。

例如一些片上存储器、DSP模块、LVDS驱动器、PLL等等。

这些模块可以通过MegaWizard Plug-In Manager(Tools菜单)来进行设计。

Altera FPGA下载配置

Altera FPGA下载配置很多兄弟对于CPLD下JTAG的下载很熟悉了,可转到FPGA来的时候,多多少少有些迷惑,怎么出现配置芯片了,为什么要用不同的下载电缆,不同的下载模式?我就自己知道的一点东西谈一些个人的见解,并发一些资料.1.FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone 系列。

使用Altera串行配置器件来完成。

Cyclone期间处于主动地位,配置期间处于从属地位。

配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

(见附图)PS则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

(见附图)JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera 下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

专用配置器件:epc型号的存储器常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列.除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升了配置速度。

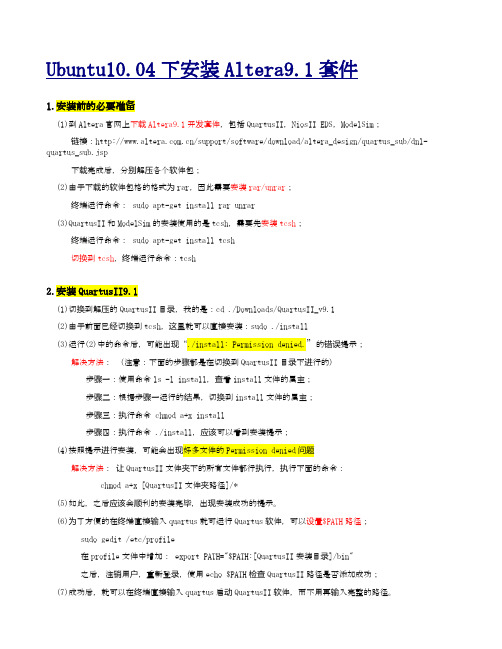

Ubuntu下安装Altera套件(Quartus,modelsim等)

Ubuntu10.04下安装Altera9.1套件1.安装前的必要准备(1)到Altera官网上下载Altera9.1开发套件,包括QuartusII,NiosII EDS,ModelSim;链接:/support/software/download/altera_design/quartus_sub/dnl-quartus_sub.jsp下载完成后,分别解压各个软件包;(2)由于下载的软件包格的格式为rar,因此需要安装rar/unrar;终端运行命令: sudo apt-get install rar unrar(3)QuartusII和ModelSim的安装使用的是tcsh,需要先安装tcsh;终端运行命令: sudo apt-get install tcsh切换到tcsh,终端运行命令:tcsh2.安装QuartusII9.1(1)切换到解压的QuartusII目录,我的是:cd ./Downloads/QuartusII_v9.1(2)由于前面已经切换到tcsh,这里就可以直接安装:sudo ./install(3)运行(2)中的命令后,可能出现“./install: Permission denied.”的错误提示;解决方法:(注意:下面的步骤都是在切换到QuartusII目录下进行的)步骤一:使用命令ls -l install,查看install文件的属主;步骤二:根据步骤一运行的结果,切换到install文件的属主;步骤三:执行命令 chmod a+x install步骤四:执行命令 ./install,应该可以看到安装提示;(4)按照提示进行安装,可能会出现好多文件的Permission denied问题解决方法:让QuartusII文件夹下的所有文件都行执行,执行下面的命令:chmod a+x [QuartusII文件夹路径]/*(5)如此,之后应该会顺利的安装完毕,出现安装成功的提示。

AlteraFPGASoC搭建步骤

AlteraFPGASoC搭建步骤Altera SoC 官⽅搭建指南:官⽅⽂档中除了讲解搭建⽅法之外,还有很多原理性的介绍,感兴趣的朋友可以⾃⼰阅读。

准备⼯作:1. 安装Altera官⽅提供的IDE ( 和 ), 不需要安装DS-5. ⽂档中的⼯作是基于v15.0版本2. ⼀块FPGA SoC开发板。

官⽅Guide中的硬件平台是友晶系列的DE0-Nano-SoC,但对⼤多Altera板⼦都适⽤3. ⼀台Linux主机4. ⼀张SD卡5. ⽹络可以访问github搭建步骤:1. ⽣成Preloader2.配置和编译Bootloader (U-Boot)3. ⽣成和编译Device Tree4. 测试系统(⼀)5. 配置和编译Linux Kernel6. ⽣成Root Filesystem7. 测试系统(⼆)搭建⽅法:1. ⽣成Preloader下载并解压GHRD,并解压⾄某⽬录:tar -xvzf atlas_linux_ghrd.tar.gz运⾏EDS配置环境变量的脚本<path-to-soceds-tools>/embedded/embedded_command_shell.sh运⾏BSP Editor⼯具:cd atlas_linux_ghrdbsp-editor &将弹出如下窗⼝:配置BSP Editor:File→New HPS BSP在弹出的窗⼝中,点击"Preloader settings directory"右侧的"..."按钮,选择“atlas_linux_ghrd/hps_isw_handoff/soc_system_hps_0”,然后点击Open。

完成后的界⾯如下图,点击确定:在⽣成的窗⼝中,选中"FAT_SUPPORT",其他的使⽤默认,结果如下图:点击Generate,正常结束后点击Exit退出。

Altera的FPGA下载常见问题经验小结

Altera的FPGA下载常见问题经验小结软件部分:对于QUARTUS II 4.0版本软件,在安装完成后,需要做如下设置,软件才能够正常工作。

第一:设置license。

第二:安装驱动:Win2000/XP:1、打开控制面板(开始->设置->控制面板)2、双击“添加/删除硬件”图标,启动添加/删除硬件向导,然后按下一步继续。

3、在“选择一个硬件任务”面板上,选择“添加/排除设备故障”,然后按下一步继续。

WIN2000将会在新的硬件检测窗口里搜索新的即插即用设备。

4、在“选择一个硬件设备”面板上,选择“添加新设备”。

按下一步继续。

5、在“查找新硬件”面板上,选择“否,我想从列表选择硬件“。

按下一步继续。

6、在”硬件类型“面板上,选择”声音、视频和游戏控制器“。

按下一步继续。

7、在”选择一个设备驱动程序“窗口,点击”从磁盘安装“按钮。

8、指定win2000.inf文件的完整路径(例如安装目录>\drivers\win2000)。

按下一步继续。

9、在“没有找到数字签名”窗口,点击“是”按钮。

10、在“选择一个设备驱动程序”窗口,如果您使用ByteblasterMV或AlteraByteBlasterII,请安装相应驱动。

11、在“开始硬件安装”窗口,点击下一步继续。

12、在“没有找到数字签名”窗口,点击“是”按钮,继续安装。

13、在“完成添加/删除硬件向导”窗口,点击“完成”按钮14、在弹出的系统对话选择是否重新启动计算机。

驱动程序要在重新启动后才能使用。

重新启动后,即可在quartusII里进行program了。

第三:programer设置。

点击桌面图标Quartus II 4.0启动软件。

A)在tools菜单下,执行Programer命令。

B)点击hardware setup,点击select hardware,选择Byteblaster,---→add hardware---→close.C)完成后,在Hardware setup 右侧出ByteBlaster[LPT1],mode 的下拉菜单有JTAG,Passive Serial,Active Serial programing为设置正确的标志。

FPGA程序下载手册

FPGA程序下载Altera器件下载Altera器件下载分两种,一是安装完整的altera器件集成开发环境quartus II,现在的最新版本为quartus II 11.1,然后使用开发环境中的下载组件进行下载。

另外也可以单独安装下载组件programmer完成程序烧写。

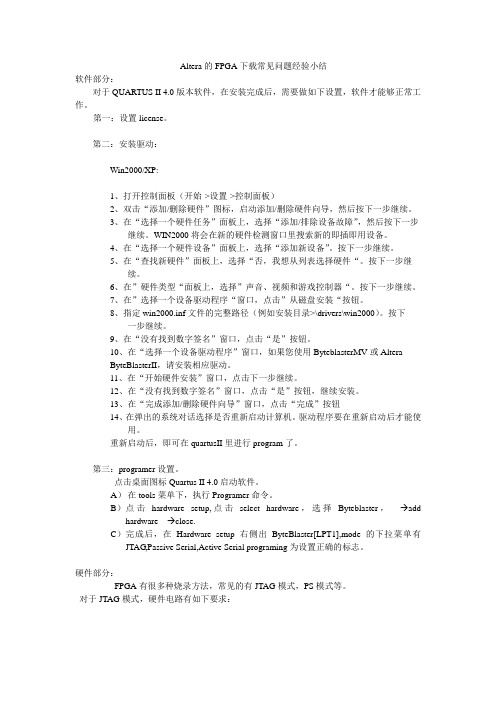

programmer的安装和使用。

以安装10.0sp1_programmer_windows.exe为例,过程如下图所示,均为默认即可。

安装完成后,连接usb-blaster下载器,分别连接到PC机的usb接口和板卡的JTAG接口,下载器连接好后再打开电源。

若驱动未安装,需要首先安装usb-blaster的驱动。

打开我的电脑-> 管理-> 设备管理器中找到相应的硬件,按下图所示步骤进行驱动安装,如果出现警告,点击继续。

驱动安装完成后,在安装路径中打开Quartus II 10.0sp1 Programmer。

如下图所示,在hardware setup中找到usb-blaster,然后点击close。

当下载板卡(硬件连接)准备好后,点击autodetect,显示器件列表,双击列表即可弹出文件选择窗口,最后选择相应的jic文件,并勾选program configure,点击start完成下载。

下载完成后需要对板卡进行重新上电。

Lattice器件下载ispVM System的安装和使用。

ispVMSystemV17.9.exe为例,全部过程均为默认,安装lattice器件的USB下载驱动时,也默认安装all drivers。

安装好后将Lattice 下载线的一端连接在PC机的usb口,另一端连接至板卡的JTAG接口(注意线的顺序),然后打开电源。

打开ispVM System,如下图所示。

点击scan按钮,系统会自动检测到器件,并显示器件列表,双击器件列表,弹出device information对话框,在器件部分选择板卡上的器件,在data部分点击browse选择要下载的bit文件。

ModelSim ALTERA 6.3g_p1使用方法

Modelsim ALTERA 6.31、安装1)打开运行81_modelsim_ae_windows.exe,如下图:安装时选择Full product安装。

当出现Install Hardware Security Key Driver时选择“否”。

当出现Add Modelsim To Path选择“是”。

出现Modelsim License Wizard时选择“Close”。

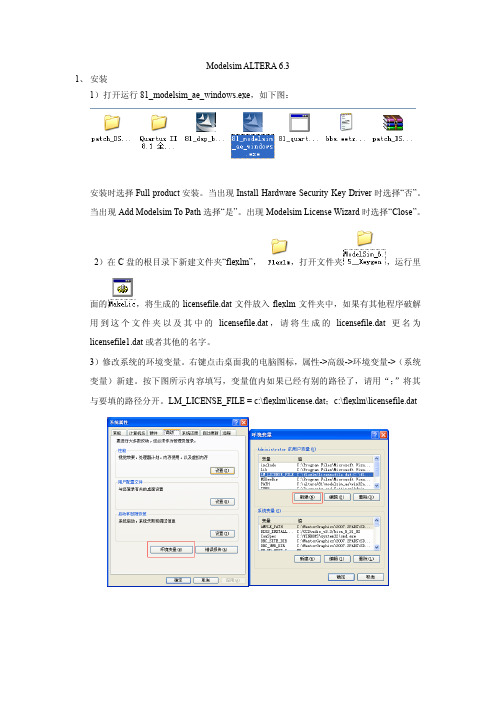

2)在C盘的根目录下新建文件夹“flexlm”,,打开文件夹,运行里面的,将生成的licensefile.dat文件放入flexlm文件夹中,如果有其他程序破解用到这个文件夹以及其中的licensefile.dat,请将生成的licensefile.dat更名为licensefile1.dat或者其他的名字。

3)修改系统的环境变量。

右键点击桌面我的电脑图标,属性->高级->环境变量->(系统变量)新建。

按下图所示内容填写,变量值内如果已经有别的路径了,请用“;”将其与要填的路径分开。

LM_LICENSE_FILE = c:\flexlm\license.dat;c:\flexlm\licensefile.dat4)安装完成,运行!2、Modelsim ALTERA 6.3的使用方法Modelsim的仿真主要有以下几个步骤:建立库并映射库到物理目录;编译原代码(包括Testbench;执行仿真。

1)建立库运行Modelsim ALTERA 6.3,点击工具栏的“File”—>“Change Directory…”选择你要建立库的位置:仿真库是存储已编译设计单元的目录,modelsim中有两类仿真库,一种是工作库,默认的库名为work,另一种是资源库。

Work库下包含当前工程下所有已经编译过的文件。

所以编译前一定要建一个work库,而且只能建一个work库。

资源库存放work库中已经编译文件所要调用的资源,这样的资源可能有很多,它们被放在不同的资源库内。

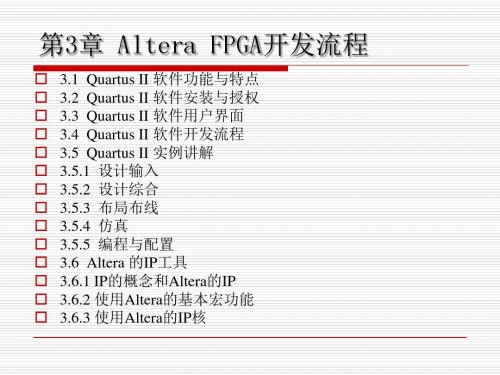

AlteraFPGA开发流程

资源管理窗

五、编译状态显示窗 编译状态显示窗主要在编译过程中显示各个过程的进度。 包括语法检查,综合进度,布局布线时间 等。 六、工程工作区 工程工作区主要在设计过程中显示各种设置窗口、编辑 串口和显示窗口等,也是用户使用 Quartus II 软件的主要交互区。 七、信息显示窗 信息显示窗主要显示当前软件的工作状态或工程进行的 操作,其最主要功能还是显示编译过程中产 生的各项信息,这些信息包括普通信息、警告、错误等。 在编译过程中遇到错误时,可以通过错误 信息锁定错误发生点,方便用户查找和修改设计。

创建工程

创建工程

创建工程

3. 进行项目名称的设定、工作名和顶层实体名要求相同,工程目录可以随意 设置,但必须是英文的目录,工程名和顶层实体 名也要求是英文名字,我们的工程名和顶层实体 名为clock,选择Next。

创建工程

创建工程

4.可以为工程添加先期已经输入的设计文件,指定用 户自定义的元件库的路径,这里我们没有事先输入好 的文件,也没有自定义的元件库,点击Next进入下一 步。

创建工程

创建工程

5. 用户指定目标器件,根据开发板的所使用的 器件来选择,实际开发中,通过查看核心板的 参考手册来获取所使用的器件具体型号,可以 使用窗口右边的Filters来加快器件的选择,选 择完毕点击Next。

三、工具栏 工具栏中包含常用命令的快捷图标。鼠标移动到图 标时,鼠标下方会出现此图标对应的含义,每种图 标在菜单栏也能找到相应命令菜单。用户可根据个 人需要放置一些常用功能快捷图标,提高设计效率。 四、资源管理窗 资源管理窗用于显示当前工程中所有相关的资源文 件。在编译后,结构层次标签栏里会显示整个工程 设计的结构,并且还列出了每个文件占用的资源情 况。 文件标签栏里显示了所有源文件的目录和名称。设 计单元标签栏里将显示所有设计单元,包括它们的 类型。

fpga软件的使用流程

FPGA软件的使用流程1. 准备工作在开始使用FPGA软件之前,需要完成以下准备工作:•安装FPGA软件:根据硬件型号和供应商提供的资料,下载并安装相应的FPGA软件。

常见的FPGA软件包括Xilinx ISE、Altera Quartus等。

•学习基础知识:了解FPGA的基本原理,掌握HDL(硬件描述语言)的知识,例如Verilog或VHDL。

同时,理解FPGA的架构和工作流程也是必要的。

2. 创建新工程在使用FPGA软件之前,首先需要创建一个新的工程。

按照以下步骤进行:1.打开FPGA软件:双击桌面上的应用程序图标或通过开始菜单打开相应的应用程序。

2.选择“创建新工程”:在软件界面上找到“新建工程”或类似的选项,点击进入新工程界面。

3.命名工程:为工程命名,选择保存路径,并指定工程的类型(例如Xilinx或Altera)。

4.选择设备型号:根据所使用的FPGA硬件,选择相应的设备型号。

如果不清楚型号,可以参考FPGA供应商的技术手册或官方网站。

3. 设计RTL电路RTL(Register Transfer Level)是描述数字电路的一种方法,FPGA软件可以通过RTL描述用户的电路设计。

在设计RTL电路时,可以按照以下步骤进行:1.打开设计视图:在FPGA软件界面中,找到“设计视图”或类似选项,打开RTL设计界面。

2.添加模块:在设计界面上,选择“添加模块”或类似选项,将所需的模块添加到设计中。

3.连接模块:使用软件提供的连接工具,将各模块按照设计要求连接起来。

4.编写HDL代码:使用HDL语言(如Verilog或VHDL),编写每个模块的逻辑代码。

5.进行仿真:使用软件提供的仿真工具,对设计的RTL电路进行仿真验证。

4. 进行综合在完成RTL电路设计后,需要进行综合(Synthesis)操作,将RTL代码转化为FPGA支持的逻辑元件。

按照以下步骤进行:1.打开综合工具:在FPGA软件界面中,找到“综合”或类似选项,打开综合工具。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Altera FPGA开发软件安装指南安装顺序请参照下面软件的介绍顺序。

本文的顺序是参照Altera Complete Design Suite 中的软件的安装顺序介绍的。

一、MATLAB(要求R14或以后版本)1.注意:请将MA TLAB安装在英文路径下。

如安装路径,或项目路径包含中文,则运行DSP Builder时可能会出现错误。

解决方法是在项目中将路径改为英文的路径。

2.如果不使用DSP Builder,则MA TLAB不需要安装。

二、Quartus II 6. 0(6. 1)3.执行,在Quartus II Install CD页面(图1),执行第一项Install Quartus II and Related Software,安装Quartus II。

图1 Quartus II Install CD页面4.软件安装过程同其他软件没有区别,只是在第二步时有一个Choose the Software 窗口(图2),选择要安装的软件组件。

如果直接使用安装程序,将不会出现这个选择。

!特别注意:除了Quartus II 6.0以外,其余3个软件需要单独的安装程序,这里只是在前一个软件的安装完成后,自动启动下一个软件的安装程序。

与后面安装过程中选择安装组件有本质区别。

●Quartus II 6.0——安装Quartus II 6.0。

这项当然要打勾了。

●ModelSim-Altera——安装ModelSim的Altera专用版。

(详细版本说明参见本安装说明的ModelSim部分。

)●MegaCore IP Library——安装MegaCore IP库。

●Nios II Embedded Processor, Evaluation Edition——Nios II处理器开发工具评估版。

5.在拷贝文件时,如出现指定Disk2路径的提示,这时只需指定到路径:<安装目录>\disk2\quartus即可。

6.软件破解:1)对于6.0版本,拷贝crack目录下文件sys_到<软件安装目录>\win\(如D:\Altera\quartus60\win),覆盖原文件。

对于6.1版本,拷贝到<软件安装目录>\bin\。

2)用记事本打开,将里面HOSTID改成自己电脑网卡的MAC地址(不要加“-”)。

建议将其放置在软件安装目录(如D:\Altera)下。

(图3)3)启动Quartus II 6.0,出现Option选项窗口的License Setup页(图4)。

指定license文件的方法有两种。

在下面Network Interface Card (NIC) ID框有本机的MAC 地址(如果有2段,MAC地址是“,”后面那段)。

➢勾选Use LM_LICENSE_FILE variable,使用系统环境变量LM_LICENSE_FILE指定的license文件。

(推荐使用这种方法。

因为后面某些软件的license文件只能这么指定,所以这样可以避免license文件过于混乱,方便管理。

)LM_LICENSE_FILE变量的指定方法见图5、图6。

如果没有该变量则新建一个。

如果有其他软件亦使用这个变量,不同License路径值之间用“;”分隔。

➢在License file框指定文件位置。

图2 Choose the Software窗口图3 修改文件中的HOSTID图4 License Setup窗口!特别注意:文件存放的路径名称不能包含汉字和空格,但是空格可以用下划线“_”代替。

图5 系统属性(在控制面板中)的高级选项页图6 设置LM_LICENSE_FILE变量,指定License存放路径三、MegaCore IP Library(无破解,略)四、Nios II Embedded Design Suite1.安装过程略。

2.6.0版本的破解:将下面代码加入Quartus II的中,并将HOSTID改为本机MAC地址。

FEATURE 6AF8_00A2 alterad 2010.01 permanent uncounted 13CZ72D78404 \VENDOR_STRING=lh14qoK3vAB7WVp5s7yRgb HOSTID=************ SIGN="059E 8AE8 BAE9 8385 7087 D587 A894 8C27 0342 DB15 6D60 F43C 5F21 9ABB 3009 0916 88BF 96CE 6F22 552E 3690 C02D FF5F 705E 17AD 30C6 4EEF 29FA E1D2 5868FEATURE 6AF7_00A2 alterad 2010.01 permanent uncounted 13CZ72D78404 \VENDOR_STRING="iiiiiiiihdLkhIIIIIIIImPDuiaaaaaaaaP1X38DDDDDDDDmjz5cdddddddd4m GzGJJJJJJJJiqIh0uuuuuuuucYYWiVVVVVVVVcp0FVHHHHHHHHPUEakffffffffR2FFRkkkkk kkkqL$84"\HOSTID=************ SIGN="059E 8AE8 BAE9 8385 7087 D587 A894 8C27 0342 DB15 6D60 F43C 5F21 9ABB 3009 0916 88BF 96CE 6F22 552E 3690 C02D FF5F 705E 17AD 30C6 4EEF 29FA E1D2 58683.6.1版本的破解目前未知。

五、ModelSim SE(ver6.2b)1.执行执行安装。

2.出现选择安装选项时,选择Full Product。

(图7)图7 选择Full Product3.出现是否安装Security Key Driver(软件狗)的提示,选择“否”。

(图8)图8 不安装Security Key Driver4.出现Add ModelSim To Path的对话框,可以选“是”。

(图9)图9 允许添加ModelSim到系统的路径设置5.出现License Wizard对话框,点击Close关闭。

(图10)图10 License Wizard对话框6.打开,在hostid文本框中粘贴本机MAC地址,点击Generate,即可在<所在目录>中得到License文件。

7.合并license文件。

或者在系统环境变量中,修改变量LM_LICENSE_FILE,添加上一步得到的license文件路径。

8.ModelSim版本说明:●ModelSim-Altera:由Altera提供的ModelSim。

亦有其他器件公司提供的ModelSim版本。

与PE版差不多。

一般只支持单一语言和该公司的入门级库,可执行(语句)行数亦有所限制。

●ModelSim PE:ModelSim个人版。

●ModelSim SE:ModelSim专业版。

与PE版存在功能、执行速度(差别可达300~400%)、支持的库文件数量等的区别。

PE和SE版由Mentor Graphics公司提供。

六、DSP Builder 6.0(6.1)1.DSP Builder不是以单独的软件形式,而是以模块的形式安装在MA TLAB的Simulink 里的。

所以,请在安装DSP Builder之前安装MA TLAB软件,并且必须安装Simulink组件。

2.首先安装DSP Builder。

3.启动MATLAB,在命令行键入:cd <软件安装目录>\ Altlib(如cd D:\Altera\DSPBuilder\Altlib)4.键入命令:setup_dspbuilder即完成了DSP Builder的安装。

5.若上一步出现如下错误提示:Error using ==> setup_dspbuilderThe environment variable ‘DSPBUILDER_ROOTDIR’, required by DSP Builder, has not been set. Please refer to the DSP Documentation for details.请检查系统属性的高级选项页(图5)的环境变量是否有变量“DSPBUILDER_ROOTDIR”,且其值设置为DSP Builder的安装目录(如D:\Altera\DSPBuilder\)(图7)。

如仍然不行,注销并重新登陆Windows系统。

图7 检查环境变量DSPBUILDER_ROOTDIR6.破解:1)拷贝Crack目录下的文件到<DSP Builder安装目录>\Altlib\(如D:\Altera\DSPBuilder\Altlib)下覆盖原文件。

另外一种破解是使用破解器程序,需要指定原的位置,然后破解器会将破解。

(图8)图8 DSP-Builder_6.1的破解器2)合并License。

另外,也可以新建一个License文件:新建一个文本文件,加入代码,重命名为<name>.dat(如dspbuilder_。

)。

修改环境变量的LM_LICENSE_FILE变量,加入上述license文件的存放路径。

建议使用合并License的方法,因为Quartus的License一定是最好用的。

3)如果在使用DSP Builder中,设置模块SignalCompiler时,出现license错误,重新启动计算机。

若问题依然,检查以上步骤或寻找其他的破解。