封装中修改PAD

Cadence17.2 PadEditor入门指南

Cadence 17.2 Pad Editor 入门指南(2)创建自定义焊盘及封装Pad Editor 与Allegro PCB Designer 相互配合,可以做出各种类型的封装。

当我们需要制作相对简单的封装时,可以用Pad Editor图形库中现成的图形制作封装,但当我们接触到一个新的元器件时,封装的焊盘就需要自己动手进行制作。

本章,我就带大家制作一个SOIC 封装的自定义焊盘以及封装。

自定义焊盘的制作主要分为两步,第一步就是使用Allegro PCB Designer 建立一个图形文件,第二步就是用Pad Editor 利用这个图形文件建立焊盘。

一、焊盘图形文件的制作1.1 、新建一个Shape Symbol 符号:打开PCB Dedigner-->File-->New-->shape symbol首先给自己的图形起一个名字,选择好路径,类型选择Shape Symbol ,点击o k。

Allegro 的symbol类型有一下几个:Board symbol :板Board(wizard) :板向导Module :模块符号Package symbol :一般封装符号Package symbol(wizard) :一般封装符号向导Mechanical symbol :机械符号Shape symbol :形状符号Flash symbol :导通符号但我们常用的有一下五中,它们分别是Package Symbol 、Mechanical Symbol 、Format Symbol 、Shape Symbol 、Flash Symbol 。

每种Symbol 均有一个Symbol Drawing File( 符号绘图文件), 后缀名均为*.dra 。

此绘图文件只供编辑用, 不能给A llegro 数据库调用。

Allegro 能调用的Symbol 如下:1.1.1 、Package Symbol一般元件的封装符号, 后缀名为*.psm 。

pads元件封装制作教程

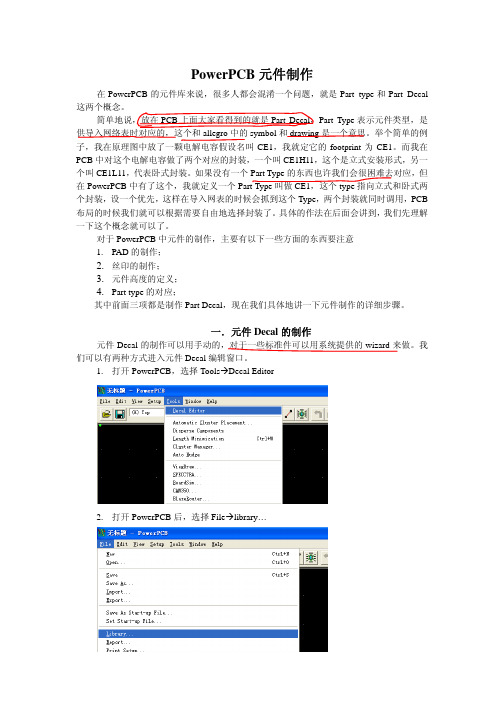

PowerPCB元件制作在PowerPCB的元件库来说,很多人都会混淆一个问题,就是Part type和Part Decal 这两个概念。

简单地说,放在PCB上面大家看得到的就是Part Decal,Part Type表示元件类型,是供导入网络表时对应的,这个和allegro中的symbol和drawing是一个意思。

举个简单的例子,我在原理图中放了一颗电解电容假设名叫CE1,我就定它的footprint为CE1。

而我在PCB中对这个电解电容做了两个对应的封装,一个叫CE1H11,这个是立式安装形式,另一个叫CE1L11,代表卧式封装。

如果没有一个Part Type的东西也许我们会很困难去对应,但在PowerPCB中有了这个,我就定义一个Part Type叫做CE1type指向立式和卧式两个封装,设一个优先,这样在导入网表的时候会抓到这个Type,两个封装就同时调用,PCB 布局的时候我们就可以根据需要自由地选择封装了。

具体的作法在后面会讲到,我们先理解一下这个概念就可以了。

对于PowerPCB中元件的制作,主要有以下一些方面的东西要注意1. PAD的制作;2. 丝印的制作;3. 元件高度的定义;4. Part type的对应;其中前面三项都是制作Part Decal,现在我们具体地讲一下元件制作的详细步骤。

一.元件Decal的制作元件Decal的制作可以用手动的,对于一些标准件可以用系统提供的wizard来做。

我们可以有两种方式进入元件Decal编辑窗口。

1. 打开PowerPCB,选择ToolsÆDecal Editor2. 打开PowerPCB后,选择FileÆlibrary…在这个图中,不论我们点击Decals,Parts等都看不到任何东西,因为我们还没有元件库在里面,这里,如果我们要新建一个元件库,须点击New Lib…,如要加载一个已有的元件库进来,则点击Lib. List…。

allegro 遇到的问题汇总 避免忘记

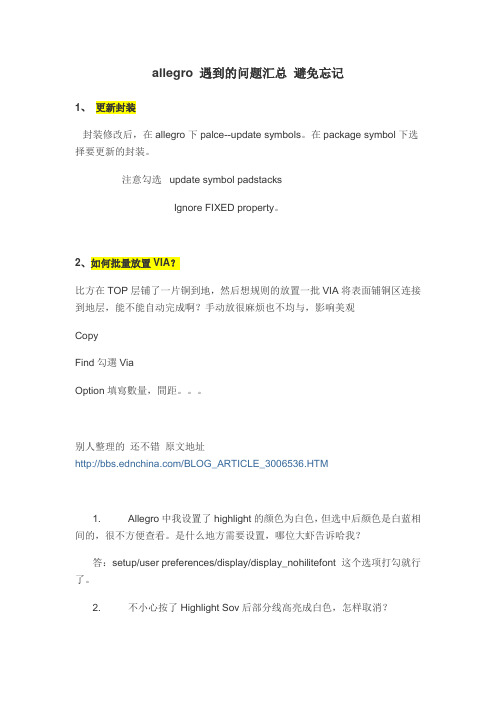

allegro 遇到的问题汇总避免忘记1、更新封装封装修改后,在allegro下palce--update symbols。

在package symbol下选择要更新的封装。

注意勾选update symbol padstacksIgnore FIXED property。

2、如何批量放置VIA?比方在TOP层铺了一片铜到地,然后想规则的放置一批VIA将表面铺铜区连接到地层,能不能自动完成啊?手动放很麻烦也不均与,影响美观CopyFind勾選ViaOption填寫數量,間距。

别人整理的还不错原文地址/BLOG_ARTICLE_3006536.HTM1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer 那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

芯片叠封技术 pad电容

芯片叠封技术 pad电容

芯片叠封技术是一种将多个芯片堆叠在一起,形成一个整体的封装结构的技术。

在芯片叠封技术中,PAD电容是指在芯片堆叠过程中,通过在芯片之间添加电容器来增加芯片之间的电容。

PAD电容的作用主要有以下几个方面:

1. 降低电源噪声:在芯片堆叠过程中,由于芯片之间的电源共享,会产生一些电源噪声。

通过在芯片之间添加PAD电容,可以提供更低的电源噪声,提高芯片的性能和可靠性。

2. 提高信号完整性:芯片之间的电容器可以提供更好的信号隔离,减少信号干扰,提高信号完整性。

3. 优化功耗和性能:通过在芯片堆叠过程中添加PAD电容,可以优化芯片的功耗和性能。

在高性能芯片中,PAD电容可以提供更好的电源稳定性和信号完整性,从而提高芯片的工作效率和性能。

4. 提高散热效果:PAD电容可以作为散热器的一部分,在芯片堆叠过程中有效地散热,提高芯片的散热效果。

PAD电容在芯片叠封技术中起到了重要的作用,可以提高芯片的电源稳定性、信号完整性、功耗和性能,并提供散热效果。

ALLEGRO封装教程

一、手工制作封装1、打开“PAD Designer”如下界面按实际需求填好后保存,如保存为cd160X30注:阻焊层比助焊层大约1MM即可2,启动Allegro PCB Ediror 选择“File”-“New”弹出对话框3、点击OK进入编辑界面,选择“SETUP”-“Design Parameters”弹出窗口4、选择“SETUP”-“Grids”打开以下窗口设置5.选择“SETUP”-“User Preference”打开以下界面6,添加管脚焊盘。

选择“LAYOUT”---“PINS”或者图标,然后设置控制面板”options”标签页中的相关选项7,设置好后,在命令窗口中输入放置的坐标如( x 0 0)按回车键确定添加。

注意,输入坐标时x要用小字母加空格8焊盘放置完成后添加Place_Bound_Top(放置约束)。

选择”SETUP”—“Areas-“—“Package Boundary”选项。

设置控制面板的”Options”然后用坐标输入放置9、设置封装限制高度,选择”SETUP”—“Areas-“—“Package Height”选项。

然后选择该封装。

设置控制面板的”Options”10、添加丝印外框。

选择“Add”—“Line”选项,设置控制面板中“Options”然后按封装要求画出丝印框11.添加标签,选择“LAYOUT”--“LABELS”—“RefDes”选择。

设置控制面板中“Options”单击屏幕区域出现文本输入框,输入标签如U* j* REF 右键单击选择“DONE ”12,选择“File”---“Save”选项,保存元件封装二、O RCAD和ALLEGRO交互式布局1,打开原理图,选中文件,然后选择“options”-----“Preferences”出现下界面三、更改坐标原点的方式1、打开文件,选择“SETUP”--“Design Parameter Editor”弹出以下界面2,第2种方式,选择“SETUP”—“Change Drawing Origin”然后单击需要设置成为坐标原点的地方四、O r CAD导出网络表打开原理图文件,选择设计文件,选择“Tloos”--“Create Netlst”弹出以下界面五、ALLEGRO导入网络表1,设置路径:选择“SETUP”-“User Preference”打开以下界面2、选择“File”--“Import”---“Logic”弹出以下界面。

allegro 封装更新到PCB中,不通过网络表实现

allegro更新封装封装修改后,在allegro下palce--update symbols。

在package symbol下选择要更新的封装。

注意勾选(建议全勾上)(1)update symbol padstacks(2)Reset customizable drill data--重置自定义钻孔数据。

如果要更新焊点的钻孔误差值, 钻孔符号, 钻孔符号字元, 及钻孔大小。

可勾选此项就会全部更新钻孔(3)Reset symbol text location and size--重置符号文本的位置和尺寸(4)Ignore FIXED property--忽略固定属性则表示在设计元件输入时,忽略元件的固定属性。

当满足替换条件或者其它更改删除时是否忽略有FIXED属性的元件、走线、网络等等。

Allegro brd文件更新封装及焊盘方法对于allegro软件,很多时候需要在其brd文件中更新元件的封装或是焊盘,本文主要介绍其更新元件封装及焊盘方法及操作步骤。

一、allegro 更新封装方法及操作步骤a) 在allegro中更改需要更新的元件封装,并保存,记住其封装名称;b) 打开brd文件,选择菜单中的Place->Update Symbols,即出现下图所示画面:c) 选择需要更新封装的元件,点击Refresh即完成封装更新。

二、allegro 更新焊盘方法及操作步骤a) 在Pad Designer中修改对应的焊盘,并保存,记住其焊盘名称;b) 用allegro软件打开brd文件;c) 选择Tools->Padstack->Replace,右侧的Option菜单即出现如下图所示的画面:d) 在此菜单中,选择需要更新的焊盘,点击Replace即完成元件焊盘封装更新。

pcb建封装pad的标准

pcb建封装pad的标准

PCB建封装PAD的标准因不同的封装类型和应用需求而异,以下是几种常

见的标准:

1. 欧规(European Standard):通常以公制(mm)表示,尺寸包括

14mm、10mm、7mm、5mm等。

2. 美规(American Standard):通常以英制(inch)表示,尺寸包括、、等。

3. JEDEC标准:是一种常见的电子封装标准,主要应用于集成电路封装。

常见的JEDEC标准包括SOIC、DIP、SIP等,尺寸范围也较广。

4. IPC标准:是一种电子互连行业标准,主要应用于PCB和电子组件之间

的互连。

IPC标准包括IPC-7351、IPC-7352等,对封装尺寸、间距、焊盘尺寸等都有详细的规定。

需要注意的是,不同的封装类型和应用需求会有不同的标准,因此在选择封装类型和尺寸时,需要根据具体的应用场景和要求进行选择。

同时,还需要考虑到PCB板的设计和制造工艺,以确保良好的电气性能和可靠性。

Allegro PCB封装库的设计与规范

这种管理方式的优点是占用的资源比较少,当要批量更新焊盘的时候只要更新PAD库里 的焊盘,再刷新一下电路板就ok,这就是为什么用Allegro打开PCB会比用Protel快的原因,资 源是一点点省下来的。

1 Allegro封装库基本介绍

与Protel封装的区别

Allegro 封装库的 PAD number是唯一的, Protel PCB封装库PAD number可以不唯一。 这就要求我们在设计原理图库的时候Pin number也要和Allegro封装库对应起来,否 则设计的电路图没法导入Allegro里作PCB设计。

例如:bga484_1r00_23x23 表示484 管脚,球间距为1mm,Body size 为23mm 乘以23mm 的BGA 封装。

qfp100_0r50_16x16 表示100 管脚,脚间距为0.5mm,最大外型尺寸为16mm 乘以 16mm 的QFP 封装。 3)SOP、SO、SSOP、TSOP、TSSOP 类封装元件: sop/tsop/ssop/tssop+管脚数_Pitch_Full size 宽度 例如: tssop8_0r65_4r90 表示管脚数为8,管脚间距为0.65mm,Full size 宽度为4.9mm 的 TSSOP封装。

2 Allegro封装库设计规范

PCB 封装名称的命名方法。

1)标准两管脚分立器件: 阻容感等贴装分立器件,根据国际标准命名法则0402、0603、1206、1210、1805…等,以 其实体英制大小进行标准命名。 2)集成芯片类封装元件: 比如:BGA、 QFP、QFN、PLCC、 DFN、SON等等类型芯片,命名规则为: 芯片类型+管脚数_Pitch_Full size

2 Allegro封装库设计规范

芯片的pad

芯片的pad

芯片的pad是用于连接芯片与外部电路的接口,它是负责传输信号与电能的重要部分。

芯片的pad具有以下主要特点:

1. 接口可靠性:芯片的pad需要具备良好的接触性能,以确保信号的稳定传输,同时能够抵抗环境的振动和温度变化的影响。

2. 电气特性:芯片的pad需要满足一定的电气特性,如阻抗匹配、信号完整性等,以保证信号的传输质量。

3. 封装形式:芯片的pad可以采用不同的封装形式,如BGA (Ball Grid Array)、QFN(Quad Flat No Leads)等,以满足

不同应用场景的需求。

4. 焊接方式:芯片的pad可以通过焊接方式与PCB板连接,

常见的焊接方式包括SMT(Surface Mount Technology)和

PTH(Plated Through Hole)。

5. 材料选择:芯片的pad需要选择适合的材料,如金属或者合金,来达到良好的电导性能和耐腐蚀性能。

在芯片设计和制造过程中,pad的布局和设计是非常重要的环节。

合理的pad布局可以提高芯片的性能和稳定性,减小信号失真和功耗。

一些常见的pad设计技巧包括增加pad焊盘的尺寸,使用焊膏墨水来提高焊接质量,增加pad的数量以提高芯片的引脚数等等。

总之,芯片的pad是芯片与外部电路之间的重要连接接口,它的可靠性、电气特性、封装形式、焊接方式和材料选择等方面

都对芯片的性能和稳定性有着重要的影响。

在芯片设计和制造中,合理的pad布局和设计是非常重要的环节。

ALLEGRO封装教程

一、手工制作封装1、打开“P AD Designer”如下界面按实际需求填好后保存,如保存为cd160X30注:阻焊层比助焊层大约1MM即可2,启动Allegro PCB Ediror 选择“File”-“New”弹出对话框3、点击OK进入编辑界面,选择“SETUP”-“Design Parameters”弹出窗口4、选择“SETUP”-“Grids”打开以下窗口设置5.选择“SETUP”-“User Preference”打开以下界面6,添加管脚焊盘。

选择“LAYOUT”---“PINS”或者图标,然后设置控制面板”options”标签页中的相关选项7,设置好后,在命令窗口中输入放置的坐标如( x 0 0)按回车键确定添加。

注意,输入坐标时x要用小字母加空格8焊盘放置完成后添加Place_Bound_T op(放置约束)。

选择”SETUP”—“Areas-“—“Package Boundary”选项。

设置控制面板的”Options”然后用坐标输入放置9、设置封装限制高度,选择”SETUP”—“Areas-“—“Package Height”选项。

然后选择该封装。

设置控制面板的”Options”10、添加丝印外框。

选择“Add”—“Line”选项,设置控制面板中“Options”然后按封装要求画出丝印框11.添加标签,选择“LAYOUT”--“LABELS”—“RefDes”选择。

设置控制面板中“Options”单击屏幕区域出现文本输入框,输入标签如U* j* REF 右键单击选择“DONE ”12,选择“File”---“Save”选项,保存元件封装二、O RCAD和ALLEGRO交互式布局1,打开原理图,选中文件,然后选择“options”-----“Preferences”出现下界面三、更改坐标原点的方式1、打开文件,选择“SETUP”--“Design Parameter Editor”弹出以下界面2,第2种方式,选择“SETUP”—“Change Drawing Origin”然后单击需要设置成为坐标原点的地方四、O r CAD导出网络表打开原理图文件,选择设计文件,选择“Tloos”--“Create Netlst”弹出以下界面五、ALLEGRO导入网络表1,设置路径:选择“SETUP”-“User Preference”打开以下界面2、选择“File”--“Import”---“Logic”弹出以下界面。

allegro制作PCB封装详细讲解

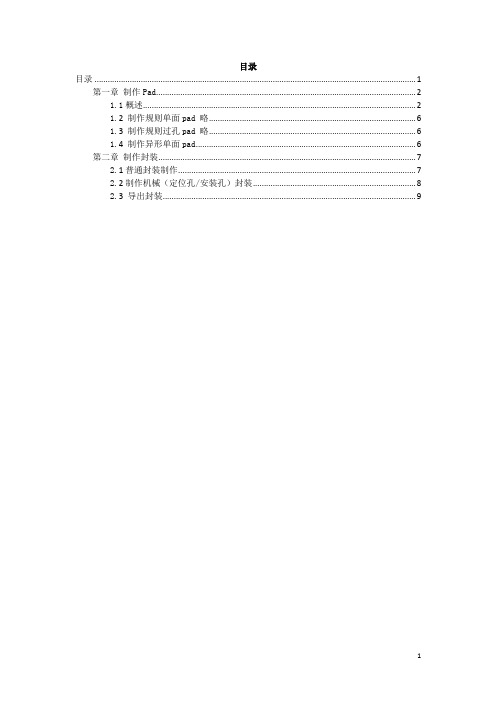

目录目录 (1)第一章制作Pad (2)1.1概述 (2)1.2制作规则单面pad略 (6)1.3制作规则过孔pad略 (6)1.4制作异形单面pad (6)第二章制作封装 (7)2.1普通封装制作 (7)2.2制作机械(定位孔/安装孔)封装 (8)2.3导出封装 (9)第一章制作Pad1.1概述一、Allegro中的Padstack主要包括1、元件的物理焊盘1)规则焊盘(Regular Pad)。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)2)热风焊盘(Thermal Relief)。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)3)抗电边距(Anti Pad)。

用于防止管脚和其他网络相连。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)。

2、阻焊层(soldermask):阻焊盘就是solder mask,是指板子上要上绿油的部分。

实际上这阻焊层使用的是负片输出,所以在阻焊层的形状映射到板子上以后,并不是上了绿油阻焊,反而是露出了铜皮。

通常为了增大铜皮的厚度,采用阻焊层上划线去绿油,然后加锡达到增加铜线厚度的效果。

3、助焊层(Pastemask):机器贴片的时候用的。

对应着所以贴片元件的焊盘、在SMT加工是,通常采用一块钢板,将PCB上对应着元器件焊盘的地方打孔,然后钢板上上锡膏,PCB在钢板下的时候,锡膏漏下去,也就刚好每个焊盘上都能沾上焊锡,所以通常阻焊层不能大于实际的焊盘的尺寸。

用“<=”最恰当不过。

4、预留层(Filmmask):用于添加用户自定义信息。

表贴元件的封装、焊盘,需要设置的层面以及尺寸5、Regular Pad:具体尺寸更具实际封装的大小进行设置。

推荐参照《IPC-SM-782A Surface Mount Design and Land Pattern Standard》。

6、Thermal Relief:通常要比规则焊盘尺寸大20mil,如果Regular Pad尺寸小于40mil,需要适当减小尺寸差异。

cadence封装中各层的区别作用

silkscreen top:是字符层,一般称顶层字符或元件面字符,为各元器件的外框及名称标识等,都用此层进行布局,个人认为最好与place_bound_top相同,且带有1脚标识。

assemly top:是装配层,就是元器件的实际大小,用来产生元器件的装配图。

也可以使用此层进行布局;外框尺寸应该为元件除焊盘外的部分(body size);place_bound_top:是元器件封装实际大小,用来防止两个元器件叠加在一起不报错。

外框尺寸需要包括焊盘在内。

1。

关于焊盘的准确尺寸,大家可以去网上下载软件LP Viewer ,我装的是LP Viewer 10.2,也许现在有更高的版本,这里有国际标准的封装及尺寸,画元器件焊盘及封装的时候,可以参考这个软件。

2.2.1 Regular Pad:具体尺寸更具实际封装的大小,可以参考LP Viewr里面的尺寸。

2.2 Thermal relief:热涨缩间隙,常用于相同NetList的填充铜薄与PAD 的间隙。

通常比Pad 直径大20mil(0.5mm),如果Pad 直径小于40mil,根据需要适当减小。

2.3 Anti Pad:抗电边距,常用于不同NetList的填充铜薄与PAD的间隙。

通常比Pad直径大20mil(0.5mm),如果Pad 直径小于40mil,根据需要适当减小。

2.4 SolderMask:通常比规则焊盘大4mil(0.1mm)。

2.5 Pastemask:通常和规则焊盘大小相仿。

2.6 Filmmask:应用比较少,用户自己设定。

再次归纳:1.贴片焊盘要有SolderMask_TOP和Pastemask_TOP。

通孔要有SolderMask_TOP和SolderMask_BOTTOM,因为两边都要露在外面。

盲孔要有SolderMask_TOP,因为一边露在外面。

埋孔焊盘不需要SolderMask和Pastemask,因为都在里面。

【阻焊层】干嘛用的?上面说就是涂绿油,蓝油,红油嘛,除了焊盘、过孔等不能涂『涂了你怎么能上、焊焊锡啊?是吧?』其他都要涂上阻焊剂,这个阻焊剂有绿色的蓝色的红色的。

PADS9.5从元器件封装到PCB布局布线

PADS9.5从元器件封装到PCB布局布线目录一、前序 (2)二、PADS设计流程简介 (2)三、常用设计参数的设置 (3)3.1 PADS Logic 设计参数设置 (3)3.1.1 常规设置 (4)3.1.2设计设置 (5)3.1.3 文本设置和线宽设置采用默认即可。

(5)四、PADS Logic元件库管理 (6)4.1 创建元件库 (6)4.2 新的元件类型的创建 (7)五、PASD Layout 元件库 (12)六、PADS原理图设计 (15)6.1 添加元件 (15)6.2 建立新连线 (15)6.3 更改已分配的额PCB封装 (15)七、PADS Logic文件输出 (18)7.1 创建Layout 网络表 (18)7.2 PADS Logic与PCB Layout 的相互更新 (18)八、PADS Layout PCB设计 (21)8.1 元器件布局 (21)8.2 按元器件类型自动排列 (21)8.3 布局感想 (22)8.4 PCB布局谈(转载) (23)8.5 PCB Layout 布线 (24)覆铜提示: (26)一、前序对于从校园到社会转变的我,进入一家新公司,学习到的知识都是全新的,闻所未闻的,一切都是从零开始。

面试进入一家新公司,从安装学习PADS9.5到完成PCB板的布局布线最终提交给厂家生产,用了一个月的时间。

时间过得很快,我亦有一些感想和心得愿意同大家共分享。

PADS9.5软件的安装,我就不再多说了,我会在下一篇文章里说的很详细,大家有需要的可以下载。

二、PADS设计流程简介软件安装完成之后就要进行PCB板的设计制作了,这里就有一个PADS设计流程的问题。

常规PADS设计流程:设计启动→建库→原理图设计→网表调入→布局→布线→验证优化→设计资料输出→加工。

(1)设计启动。

在设计准备阶段进行产品特性评估、元器件选型、准备元件、进行逻辑关系验证等工作。

(2)建库。

ALLEGRO问题集锦

Cadence Allegro 问题集锦2011-01-20 18:00:591、问:我在产生NC TAPE 文件时提示error,但并没有生成NCTAPE.LOG可供查找错误原因,望高手帮助!答:NCTAPE.LOG的内容其实也就是执行File/Viewlog命令弹出的文本中的内容。

您可以通过这个来查看,您不能产生log文件的原因可能是软件的关于TEXT的路径设置有问题。

您可以去SETUP/USER PERFERENCE中的CONFIG_PATH进行查看2、问:问一个入门的问题:从Capture导入的网表是不是要在Capture里把封装定义好?OrCAD里的封装如何查看?答:一般在Capture中需要定义属性(在原理图编辑器中选择物件查看他的属性)中选择Cadence-Allegro/SPECCTRAQuest/APD,然后查看PCB Footprint属性,这个属性一般是用来和Allegro中的封装做对应的,也就是这里填入的就是Allegro封装(请注意这里的封装是指的在Layout时候用到的封装)的名称,导出网络表的时候软件会做自动的抓取到生成的网络表中,这样在Allegro中导入网络表的时候Allegro才知道是抓取哪个元件,封装有两种:一种是在原理图中用的,一种是在Layout(Allegro)时候用的,我不知道您是希望在ORCAD中查看哪个封装,如果是后者的话在Capture中无法看到,但是如果您建立了Capture CIS的Database的话就可以看到了。

3、问:Allegro中的封装和OrCAD里的是否一致?答:对不起,我想问问您所指的ORCAD的封装是指原理图的封装还是指ORCAD LAYOUT 软件的封装呢,如果您是指的原理图中的封装的话那是两个完全不同的概念,一个是用在原理图中,我们叫他元件的SYMBOL,另一个呢是在进行Layout的时候需要用到的。

Capture 中要做的就是通过PCB Footprint属性进行原理图中的元件的SYMBOL和Allegro的封装进行对应,这样才能顺利的把网络表导入Allegro中。

dip波峰焊接 pad间距与引脚长度

dip波峰焊接pad间距与引脚长度摘要:I.引言- 介绍DIP 波峰焊接- 阐述研究的目的和意义II.DIP 波峰焊接中PAD 间距的影响- 定义PAD 间距- 分析PAD 间距对焊接质量的影响- 讨论PAD 间距的最佳范围III.DIP 波峰焊接中引脚长度的作用- 定义引脚长度- 探讨引脚长度对焊接稳定性的影响- 分析引脚长度的合理取值IV.PAD 间距与引脚长度的关系- 阐述两者之间的关系- 讨论在实际应用中如何平衡PAD 间距与引脚长度的取值V.结论- 总结全文内容- 对实际应用提出建议正文:I.引言DIP(Dual In-Line Package) 波峰焊接是一种常见的电子元件封装技术。

在DIP 焊接过程中,焊接头的波峰会沿着引脚的形状流动,使得焊接质量受到引脚形状、间距等因素的影响。

其中,PAD 间距和引脚长度是两个重要的参数,它们的合理设置对于保证焊接质量具有重要意义。

II.DIP 波峰焊接中PAD 间距的影响PAD 间距是指DIP 封装中相邻引脚之间的距离。

PAD 间距的大小会直接影响到焊接质量。

如果PAD 间距过大,焊接头在焊接过程中可能会出现不稳定的情况,导致焊接不良。

反之,如果PAD 间距过小,焊接头可能会发生重叠,造成焊接过度,导致焊点不清晰。

因此,在实际应用中需要选择合适的PAD 间距。

根据实际经验和实验数据,通常建议PAD 间距在0.4mm 到0.8mm 之间。

在这个范围内,焊接头可以稳定地焊接每个引脚,同时焊点也能够清晰可见。

III.DIP 波峰焊接中引脚长度的作用引脚长度是指DIP 封装中每个引脚的长度。

引脚长度的大小会直接影响到焊接稳定性。

如果引脚长度过短,焊接头可能会在焊接过程中出现过度的情况,导致焊接不良。

反之,如果引脚长度过长,焊接头可能会无法到达引脚的焊接区域,导致焊接不足。

因此,在实际应用中需要选择合适的引脚长度。

根据实际经验和实验数据,通常建议引脚长度在2mm 到5mm 之间。

bump pad 设计规则

bump pad 设计规则

在芯片封装中,Bump和PAD的设计规则因各自的作用和位置而有所不同。

Bump(凸点)的设计规则主要包括:

1. 大小和间距:凸点的尺寸(如直径和高度)以及它们之间的间距应根据封装类型和芯片规格进行选择。

太小或太密的凸点可能导致连接问题,而太大或太稀的凸点可能影响封装性能。

2. 材料选择:凸点材料应与芯片和封装基板相匹配,以确保良好的电导率和热导率。

不合适的材料可能导致连接不良或热膨胀系数不匹配等问题。

3. 形状和表面处理:凸点的形状(如圆锥形、圆柱形等)和表面处理(如镀金、镀锡等)对连接性能和可靠性有重要影响。

根据应用需求选择适当的形状和表面处理可以确保可靠的连接和降低故障风险。

PAD(焊盘)的设计规则主要包括:

1. 尺寸和布局:焊盘的尺寸(如直径和长度)和布局应根据封装类型、引脚数量和间距进行选择。

焊盘应足够大以支持可靠的连接,同时应保持适当的间距以防止短路和其他问题。

2. 材料选择:焊盘材料应与芯片、封装基板和凸点材料相匹配,以确保良好的电导率和热导率。

不合适的材料可能导致连接不良或热膨胀系数不匹配等问题。

3. 表面处理:焊盘的表面处理(如镀金、镀锡等)对连接性能和可靠性有重要影响。

根据应用需求选择适当的表面处理可以确保可靠的连接和降低故障风险。

4. 边缘距离:焊盘边缘与封装边缘的距离应保持在一个合理的范围内,以确保足够的空间进行连接和避免与封装边缘短路。

总之,Bump和PAD在芯片封装中都起着至关重要的作用,它们的设计规则应根据具体的应用需求、封装类型和材料选择进行细致的考虑和优化,以确保芯片封装的可靠性和性能。

一种PCB Layout中更新放置封装pad的方法[发明专利]

![一种PCB Layout中更新放置封装pad的方法[发明专利]](https://img.taocdn.com/s3/m/27f648911711cc7930b716cd.png)

专利名称:一种PCB Layout中更新放置封装pad的方法专利类型:发明专利

发明人:马保军,张治宇,谭小兵,齐前锋

申请号:CN201911422704.7

申请日:20191231

公开号:CN111241777A

公开日:

20200605

专利内容由知识产权出版社提供

摘要:本发明涉及PCB Layout中更新放置封装pad的方法,包括S1.选取矢量软件和PCB Layout 软件;S2.获取一个新需要建封装器件的DXF格式文件;S3.选取一个器件的封装原始档,作为第一DXF格式文件;S4.获取器件DXF规格书,作为第二DXF格式文件;S5.在矢量软件内同时打开第一DXF格式文件和第二DXF格式文件,并将第二DXF格式文件复制到第一DXF格式文件内,原点重合且在同个DXF格式文件内分别处于不同的图层;S6.将具有两个示例器件的DXF保存,作为第三DXF格式文件,并修改第三DXF格式文件里面两个不同层的名字;S7.在PCB Layout软件中导入第三DXF格式文件,选择具有与PCB Layout软件相对应丝印层的器件,添加PIN,完成封装制作。

本发明解决现有封装方法中无法更新放置封装及无法调用PAD的问题。

申请人:深圳市亿道数码技术有限公司

地址:518000 广东省深圳市宝安区新安街道上合社区33区大宝路83号美生慧谷科技园美谷5栋四楼、美谷5栋二楼-2、美谷6栋二楼-2、美谷6栋四楼

国籍:CN

代理机构:深圳市海盛达知识产权代理事务所(普通合伙)

代理人:赵雪佳

更多信息请下载全文后查看。

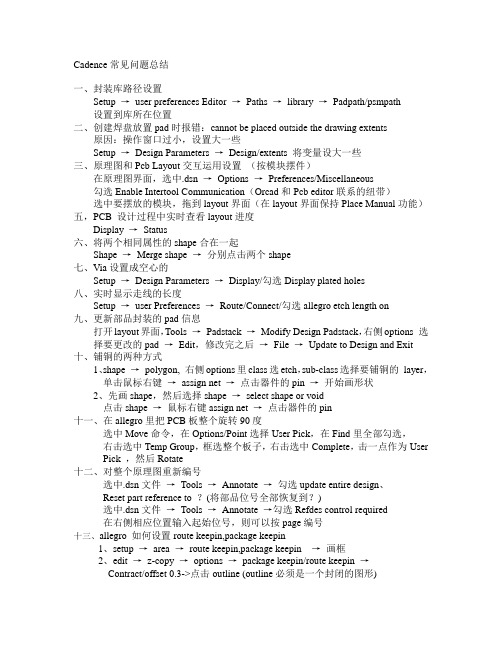

Cadence常见问题总结

Cadence常见问题总结一、封装库路径设置Setup →user preferences Editor →Paths →library →Padpath/psmpath设置到库所在位置二、创建焊盘放置pad时报错:cannot be placed outside the drawing extents原因:操作窗口过小,设置大一些Setup →Design Parameters →Design/extents 将变量设大一些三、原理图和Pcb Layout交互运用设置(按模块摆件)在原理图界面,选中.dsn →Options →Preferences/Miscellaneous勾选Enable Intertool Communication(Orcad和Pcb editor联系的纽带)选中要摆放的模块,拖到layout界面(在layout界面保持Place Manual功能)五,PCB 设计过程中实时查看layout进度Display →Status六、将两个相同属性的shape合在一起Shape →Merge shape →分别点击两个shape七、Via设置成空心的Setup →Design Parameters →Display/勾选Display plated holes八、实时显示走线的长度Setup →user Preferences →Route/Connect/勾选allegro etch length on九、更新部品封装的pad信息打开layout界面,Tools →Padstack →Modify Design Padstack,右侧options 选择要更改的pad →Edit,修改完之后→File →Update to Design and Exit十、铺铜的两种方式1、shape →polygon, 右侧options里class选etch,sub-class选择要铺铜的layer,单击鼠标右键→assign net →点击器件的pin →开始画形状2、先画shape,然后选择shape →select shape or void点击shape →鼠标右键assign net →点击器件的pin十一、在allegro里把PCB板整个旋转90度选中Move命令,在Options/Point选择User Pick,在Find里全部勾选,右击选中Temp Group,框选整个板子,右击选中Complete,击一点作为User Pick ,然后Rotate十二、对整个原理图重新编号选中.dsn文件→Tools →Annotate →勾选update entire design、Reset part reference to ?(将部品位号全部恢复到?)选中.dsn文件→Tools →Annotate →勾选Refdes control required在右侧相应位置输入起始位号,则可以按page编号十三、allegro 如何设置route keepin,package keepin1、setup →area →route keepin,package keepin →画框2、edit →z-copy →options →package keepin/route keepin →Contract/offset 0.3->点击outline (outline必须是一个封闭的图形)十四、Z-copy失灵首先检查被操作的对象是不是一个封闭的的图形,如果不是,那么就需要把若干segments合成一个整体,shape →compose shape,右侧active class →Board Geometry/outline,框选图中segments,生成shape之后,进行Z-copy,再删掉shape十五、在地平面上加via选择要添加的via →copy,右侧options可以设置via间距和数量十六、快速切换layer设置打开layout界面,Display →Color/Visbility,打开想要显示的内容,View →Color View Save →设置路径,勾选complete →save,将生成文件放到工程allegro目录下即可应用十七、刚安装完软件,手势需要同时按Ctrl+鼠标右键Setup →user preferences Editor →Ui/input →勾选no_dragup →ok经过该设置,画手势只用右键就行十八、设置快捷键Cadence/SPB_16.6/share/pcb/text/env打开env文件(以写字板方式打开)然后进行编辑十九、在原理图赋予器件封装信息双击原理图上元件,弹出对话框,在footprint处输入对应的封装信息,选中Footprint右击Display →勾选value only →apply二十、生成netlist选中.dsn →Tools →create netlist(net名字过长时,系统会自动Rename)如果生成过程中报错,则检查部品封装信息或者device有没有问题。

Cadence 元件封装及常见问题解决

Cadence 使用及注意事项目录1 PCB工艺规则.......................................... 错误!未定义书签。

2 Cadence的软件模块.................................... 错误!未定义书签。

Cadence的软件模块--- Pad Designer ................... 错误!未定义书签。

Pad的制作........................................... 错误!未定义书签。

PAD物理焊盘介绍..................................... 错误!未定义书签。

3 Allegro中元件封装的制作.............................. 错误!未定义书签。

PCB 元件(Symbol)必要的 CLASS/SUBCLASS ............... 错误!未定义书签。

PCB 元件(Symbol)位号的常用定义 .................... 错误!未定义书签。

PCB 元件(Symbol)字符的字号和尺寸 ................... 错误!未定义书签。

根据Allegro Board (wizard)向导制作元件封装......... 错误!未定义书签。

制作symbol时常遇见的问题及解决方法 ................. 错误!未定义书签。

4 Cadence易见错误总结.................................. 错误!未定义书签。

1 PCB工艺规则以下规则可能随中国国内加工工艺提高而变化(1)不同元件间的焊盘间隙:大于等于 40mil(1mm),以保证各种批量在线焊板的需要。

(2)焊盘尺寸:粘锡部分的宽度保证大于等于 10mil,如果焊脚(pin)较高,应修剪;如果不能修剪的,相应焊盘应增大…..(3)机械过孔最小孔径:大于等于 6mil。

Cadence17.2PadEditor入门指南(2)资料

Cadence 17.2 Pad Editor入门指南(2)创建自定义焊盘及封装Pad Editor与Allegro PCB Designer相互配合,可以做出各种类型的封装。

当我们需要制作相对简单的封装时,可以用Pad Editor图形库中现成的图形制作封装,但当我们接触到一个新的元器件时,封装的焊盘就需要自己动手进行制作。

本章,我就带大家制作一个SOIC封装的自定义焊盘以及封装。

自定义焊盘的制作主要分为两步,第一步就是使用Allegro PCB Designer建立一个图形文件,第二步就是用Pad Editor利用这个图形文件建立焊盘。

一、焊盘图形文件的制作1.1、新建一个Shape Symbol符号:打开PCB Dedigner-->File-->New-->shape symbol首先给自己的图形起一个名字,选择好路径,类型选择Shape Symbol,点击ok。

Allegro的symbol类型有一下几个:Board symbol :板Board(wizard) :板向导Module :模块符号Package symbol :一般封装符号Package symbol(wizard) :一般封装符号向导Mechanical symbol :机械符号Shape symbol :形状符号Flash symbol :导通符号但我们常用的有一下五中,它们分别是Package Symbol 、Mechanical Symbol、Format Symbol、Shape Symbol、Flash Symbol。

每种Symbol 均有一个Symbol Drawing File(符号绘图文件), 后缀名均为*.dra。

此绘图文件只供编辑用, 不能给Allegro 数据库调用。

Allegro 能调用的Symbol 如下:1.1.1、Package Symbol一般元件的封装符号, 后缀名为*.psm。