AML8726-MX SDIO Host Controller User Guide 20120702

8726C 8726W Addressable Remote Lamps 说明书

INTRODUCTIONThe 8726C (round plate) and 8726W (rectangular plate) Address-able Remote Lamps, shown in Figure 1, operate as an additional LED indicator for a device in the fire alarm control system’s addres-sable device circuit. The 8726C/8726W can be used when a device already has an accessory. The 8726C/8726W can be installed at any location of an addressable device circuit, and it remotely indicates the status of the device(s) in that same circuit.Mode of OperationThe 8726C/8726W has one mode of operation: Direct Addressing Mode. The two-position jumper P1 must be positioned to set the mode to Direct Addressing.When set and programmed to Direct Addressing Mode, system logic and programming determine when the ILED-H will blink.Controls and IndicatorsIn Direct Addressing mode, the LED on the 8726C/8726W is controlled by logic functions programmed using the CIS-4 Tool. In Direct Addressing mode, the 8726C/8726W blink color (red only) cannot be changed.PROGRAMMINGRefer to Figure 2 for the location of the programming holes and jumper P1.Direct Addressing ModeTo set the 8726C/8726W to Direct Addressing Mode follow the steps listed below:1.Determine a unique address for the 8726C/8726W.2.Set jumper P1 to position 2 and3.3.Connect the 8726C/8726W to the 8720 Programmer/Tester byinserting the plug from the cable provided with the 8720 Programmer/Tester into the programming holes on the 8726C/8726W board.4.Follow the instructions in the 8720 Programmer/Tester Manual, P/N 315-033260FA, to program the 8726C/8726W to the desired address. Record the device address on the label located on the 8726C/8726W front panel.INSTALLATION INSTRUCTIONS AND WIRING FORINTELLIGENT REMOTE LAMPSP/N 8726C AND 8726WFigure 18726C And 8726W Remote LampsSiemens Industry, Inc.Building Technologies Division • Florham Park, NJ Tel: (973) 593-2600 • Fax: (973) 593-6670Web: Figure 28726 Printed Circuit Board5.In the CIS-4 Programming Tool, assign the 8726C/8726W to an output zone. When an Input Group that is assigned to that Output Zone reports an off-normal event, the 8726C/8726W will blink red if the reported event type matches the output type selected for its zone. Refer to the CIS-4 Manual for further information.6.The 8726C/8726W can now be installed and wired to the system.WIRINGWARNING: Disconnect BATTERY and AC prior to working on equipment.Refer to the wiring diagram in Figure 3 below to wire the 8726C/8726W.NOTE: The 8726C/8726W is polarity insensitive. Switching Line1 and Line2 has no effect on performance.Recommended wire size:18 AWG minimum, 14 AWG maximumWire larger than 14 AWG can damage the connector.LINE2LINE1TO ADDRESSABLE DEVICE CIRCUITFigure 3Wiring The 8726C/8726WINSTALLATIONNOTE: Be sure to program the 8726C/8726W before installing the unit.The 8726C/8726W may be placed at any location on the address-able device circuit. Use a single-gang switch box (user supplied) for mounting the 8726W. Use a 4-inch octagonal conduit box (user supplied) for mounting the 8726C. Refer to Figure 4 for typical 8726C/8726W installation.The number of 8726C/8726W modules on the addressable device circuit must be included in the total count of intelligent field devices.For the restriction of the total number of devices in the FDLC loop,refer to the FDLC Installation Instructions, P/N 315-447360FA.ELECTRICAL RATINGSDO NOT USE REAR CONDUIT ENTRYFigure 4Mounting The 8726Wtn e r r u C t u p n I Am 1。

AML8726-MX UART Interface User Guide 20120522

Application NotesAML 8726-MXUART Interface User GuideAMLOGIC, Inc.3930 Freedom Circle Santa Clara, CA 95054U.S.A.AMLOGIC reserves the right to change any information described herein at any time without notice.AMLOGIC assumes no responsibility or liability from use of such information.Di s t ri bu t et oE md o o r!Table of Content1. GENERAL DESCRIPTION ............................................................................................................................................. 42. OVERVIEW ....................................................................................................................................................................... 43. FEATURES ........................................................................................................................................................................ 44.UART SIGNAL AND PIN MAPPING ............................................................................................................................ 5 4.1. S IGNAL ......................................................................................................................................................................... 5 4.2. P IN M APPING . (5)5. INTERRUPT (6)6. POWER MANAGEMENT ............................................................................................................................................... 77. RESET ................................................................................................................................................................................ 78.BAUD RATE ...................................................................................................................................................................... 8 8.1. I NPUT C LOCK ................................................................................................................................................................ 8 8.2.B AUD R ATE G ENERATION ............................................................................................................................................ 8 9. REGISTER DESCRIPTIONS (9)9.1. UART_A ...................................................................................................................................................................... 9 9.2. UART_B .................................................................................................................................................................... 14 9.3. UART_C .................................................................................................................................................................... 19 9.4. UART_AO ................................................................................................................................................................. 24 10. ADDRESS MAPPING ................................................................................................................................................. 29 11.ANDROID™/LINUX KERNE L (30)11.1. O PERATION M ACRO D EFINITION ............................................................................................................................ 30 11.2.R EGISTER M ACRO D EFINITION (30)Di s t ri bu t et oE md o o r!Revision HistoryRevision Number Revised Date By Changes0.1 Feb. 15, 2012 Kevin Zhu Initial release draft0.2 May. 22,2012 Kevin Zhu UART0~2 renamed to UART_A, UART_B and UART_CDi s t ri bu t et oE md o o r!1. General DescriptionAmlogic AML8726-MX is a highly integrated multimedia application processor SoC for Multimedia Internet Device (MID), tablet and Set Top Box (STB). It integrates a powerful CPU, a 2D/3D graphics subsystem and a state-of-the-art video decoding engine together with all major peripherals.This document is a user guide of universal asynchronous receiver/transmitter (UART) serial ports integrated in AML8726-MX.The guide provides:● An overview of UART interface ● The feature of UART● The UART interface pin selection ● The baud rate generation● The register definition that control and operate UART interface ● AML8726-MX UART in Android/Linux Amlogic porting2. OverviewEach AML8726-MX has four fully functional UARTs which use the same programming model. They are named as UART_A, UART_B, UART_C and UART_AO. The one with ‘AO ’ in the naming are located at the Always-On (AO) power domain, which cannot be powered off unless AML8726-MX is disconnected from power supply.The four UARTs are controlled separately. Each UART has a build-in standalone register set for controlling and data exchange.The UARTs in AML8726-MX can only operate in FIFO mode. UART_A has a 128-byte RX/TX FIFO and UART_B/UART_C/UART_AO has a 64-byte FIFO. If non-FIFO mode is required, the registers of UART should be fine tuned and a polling mechanism should be used to fulfill.Each UART has programmable interrupt generation circuit which will reduce the loading of processor and to improve communication performance.A baud-rate generator is also contained in each UART to provide flexible division of input clock by 1 to (216-1) or 1to (223-1) according to the setting in the internal register.3. FeaturesThe UARTs share the following features:● Each UART independent control register set● Independently controlled transmit and receive interrupts with FIFO threshold ● Programmable serial interface:⏹ 5-, 6-, 7- or 8-bit characters⏹ Even, odd or no parity detection ⏹ 1 stop bit generation⏹ Programmable baud rate● 64-byte transmit and receive FIFO (UART_B/UART_C/UART_AO) ● 128-byte transmit and receive FIFO (UART_A) ● Automatic frame error detection● Programmable RX, TX, RTS, CTS signal polarityDi s t ri bu t et oE md o o r!4. UART Signal and Pin Mapping4.1. SignalEach AML8726-MX UART function module has 4 external signals which can be connected to a series of GPIO pins via pin multiplex mapping circuit. The pins transmit digital CMOS-level signals only.The signals are described in the table below:Table 1. UART Signal DescriptionsName Type Description RX Input Serial data input to the receive shift register and Receive FIFO. TX Output Serial data output to external data set. CTS Input Clear to Send.When asserted, it indicates that the receiver is ready to exchange data.RTS Output Request to Send.When asserted, it notifies the receiver that the sender is ready to exchange data.4.2. Pin MappingIn AML8726-MX, only UART RX and TX signal are available. If CTS and RTS signal are required, please contact with Amlogic Sales.AML8726-MX has 11 GPIO banks. UART_A, UART_B and UART_C are located in Bank X and UART_AO is in the dedicated Bank AO. RX and TX signals of the UART function blocks can be multiplexed to the corresponding bank in pair.The relationship between pins and registers of each UART signal and GPIO bank is shown in the table below:Table 2. UART Signal Pin out MappingUART Module UART Signal Bank X Bank AOUART_AUART_RX_A GPIOX_14 UART_TX_A GPIOX_13UART_CTS_A GPIOX_15 UART_RTS_A GPIOX_16 UART_BUART_RX_B GPIOX_18 UART_TX_B GPIOX_17UART_CTS_B GPIOX_19 UART_RTS_B GPIOX_20 UART_CUART_RX_C GPIOX_22 UART_TX_C GPIOX_21UART_CTS_C GPIOX_23 UART_RTS_C GPIOX_24 UART_AOUART_RX_AO GPIOAO_1 UART_TX_AO GPIOAO_0UART_CTS_AO GPIOAO_2 UART_RTS_AO GPIOAO_3About GPIO function settings, please refer to AML8726-MX GPIO User Guide for detailed description.Di s t ri bu t et oE md o o r!5. InterruptThe UART interrupts are controlled in two levels: CPU and Function.In CPU level, the UART interrupts can be controlled and programmed by using the registers below:Table 3. Interrupt Control Register UART CPU LevelUART Module Offset Bit R/WUART_A 0x2690 bit 26 R UART_A interrupt flag. When interrupt happens, it will beset to 1.0x2691 bit 26 R/W Write 1 to this register bit to clean UART_A interrupt flag.0x2692 bit 26 R/W Interrupt mask. Set to 1 to mask UART_A interrupt (disableUART_A interrupt).0x2693 bit 26 R/W Fast interrupt enable. Set to 1 to enable UART_A interruptmultiplexing to CPU FAST interruptUART_B 0x2698 bit 11 R UART_B interrupt flag. When interrupt happens, it will beset to 1.0x2699 bit 11 R/W Write 1 to this register bit to clean UART_B interrupt flag.0x269A bit 11 R/W Interrupt mask. Set to 1 to mask UART_B interrupt (disableUART_A interrupt).0x269B bit 11 R/W Fast interrupt enable. Set to 1 to enable UART_B interruptmultiplexing to CPU FAST interruptUART_C 0x2698 bit 29 R UART_C interrupt flag. When interrupt happens, it will beset to 1.0x2699 bit 29 R/W Write 1 to this register bit to clean UART_C interrupt flag.0x269A bit 29 R/W Interrupt mask. Set to 1 to mask UART_C interrupt (disableUART_AO interrupt).0x269B bit 29 R/W Fast interrupt enable. Set to 1 to enable UART_C interruptmultiplexing to CPU FAST interruptUART_AO 0x2698 bit 26 R UART_AO interrupt flag. When interrupt happens, it will beset to 1.0x2699 bit 26 R/W Write 1 to this register bit to clean UART_AO interrupt flag.0x269A bit 26 R/W Interrupt mask. Set to 1 to mask UART_AO interrupt(disable UART_AO interrupt).0x269B bit 26 R/W Fast interrupt enable. Set to 1 to enable UART_AO interruptmultiplexing to CPU FAST interruptIn Function Level, the block registers need to be set to enable UART interrupt. ● UART_A: UART_A_CONTROL[27] and [28] must be set to 1. ● UART_B: UART_B_CONTROL[27] and [28] must be set to 1. ● UART_C: UART_C_CONTROL[27] and [28] must be set to 1. ● UART_AO: AO_UART_CONTROL[27] and [28] must be set to 1.For more details and other register setup, please refer to the Register Descriptions section.Di s t ri bu t et oE md o o r!6. Power ManagementThe UARTs in AML8726-MX can be shut down to save power consumption by using the register bits described below:Need verify● UART_A: i n EE domain; ● UART_B: i n EE domain; ● UART_C: in EE domain; ● UART_AO: in AO domain;Setting these bits to 0 will disable the UARTs function blocks and 1 will enable them. After system power-on or reset, UART modules are enabled on default.7. ResetFor the UART module in the AO power domain, it is possible to reset it by programming the register bit 0x0010[17] which is also in AO domain. Setting this bit to 1 will reset the I2C AO function blocks.Note: The receivers and transmitters of UARTs are disabled after system power-on or reset. Therefore software must program the registers to enable them, e.g., bit 12 and 13 in the corresponding control register should be set to 1.Di s t ri bu t et oE md oo r!8. Baud RateA build-in baud rate generator is implemented in AML8726-MX for each UART interface. The generator contains an input clock, a divider circuits and control registers.8.1. Input ClockThe input clock of the generator, named as UART_Clock, is configurable. The exact value of UART_Clock is based on AML8726-MX system software implementation.In Amlogic Android/Linux porting for AML8726-MX, the value of UART_Clock can be obtained by using the following process in software.1. Include clkdev.h at [linux_kernel_root]/arch/arm/include/asm/.2. Include clock.h at [linux_kernel_root]/arch/arm/mach-meson/include/mach/.3. Define a variable type struct clk.4. Define an unsigned int type variable uart_clock_rate.5. Use API clk_get_sys(“clk81”, NULL) to get clock structure.6. Use API clk_get_rate() to get the value of UART_Clock.The sample code is illustrated as below:#include <linux/clk.h> #include <asm/clkdev.h> #include <mach/clock.h>unsigned int uart_clock_rate; struct clk *uart_clockuart_clock = clk_get_sys(“clk81”, NULL); uart_clock_rate = clk_get_rate(uart_clock);8.2. Baud Rate GenerationAfter obtaining the uart_clock_rate, software can use the equation as shown below to generate correct baud rate.● UART_A:oror● UART_B:oror● UART_C:oror● UART_AO:ororDi s t ri bu t et oE md o o r!9. Register DescriptionsThese are 6 registers are defined and implemented in AML8726-MX for each UART. They are all 32-bit.9.1. UART_AWrite Buffer Register (UART_A_WFIFO)UART_A_WFIFO is the data entry of UART_A transmit FIFO. Writing to the register puts a byte data into the top of transmit FIFO. The data at the front of the FIFO transmits automatically until transmit FIFO empty.Table 4. UART_A_WFIFO register definitionName UART_A_WFIFO Offset 0x2130 Width 32-bit Bit R/W Name Default Description 31:8 R - 0 Reserved 7:0 W FIFO_WDATA - Write UART Transmit FIFO. The Write FIFO holds 64 bytesRead Buffer Register (UART_A_RFIFO)UART_A_RFIFO is the data entry of UART Read FIFO. It latches the value of data byte at the front of UART Read FIFO.Table 5. UART_A_RFIFO register definitionName UART_A_RFIFO Offset 0x2131 Width 32-bit Bit R/W Name Default Description 31:8 R - 0 Reserved 7:0 R FIFO_RDATA 0x00 Read a byte from UART FIFO.Di s t ri bu t et oE md o o r!UART_A Mode Register (UART_A_CONTROL)UART_A_CONTROL is a control register.Table 6. UART_A_CONTROL register definitionName UART_A_CONTROL Offset 0x2132 Width 32-bit Bit R/W Name Default Description 31 R/W RTS_INV 0 Invert RTS signal. 0: RTS active LOW. 1: RTS active HIGH 30 R/W ERR_MASK_EN 0 Error Mask enable. 0: disable error mask. 1: enable error mask. 29 R/W CTS_INV 0 Invert CTS signal. 0: CTS active LOW 1: CTS active HIGH. 28 R/W UART_TX_INT_EN 0 Transmit byte interrupt enable. When enabled, an interrupt will begenerated whenever a byte is read from Transmit FIFO. 0: disable transmit byte interrupt 1: enable transmit byte interrupt27 R/W UART_RX_INT_EN 0 Receive byte interrupt enable. When enabled, an interrupt will begenerated whenever a byte is written to Read FIFO. 0: disable receive byte interrupt 1: enable receive byte interrupt26 R/W UART_TX_INV 0 Invert TX signal. 0: TX active HIGH. 1: TX active LOW 25 R/W UART_RX_INV 0 Invert RX signal. 0: RX active HIGH. 1: RX active LOW 24 R/W UART_CLR_ERR 0 Clear error. Writing 1 to this register bit clears error.Note: This bit does not clear to 0 automatically. Please set the bit to 0 after clearing error manually.23 R/W UART_RX_RST 0 Reset receive state machine. Writing 1 to this register bit resetsreceive state machine.22 R/W UART_TX_RST 0 Reset transmit state machine. Write 1 to this register bit resettransmit state machine.21:20 R/W UART_DATA_LEN 00 Character length of data.00: 8-bit 01: 7-bit 10: 6-bit 11: 5-bit19 R/W PARITY_EN 1 Parity enable bit. 0: disable parity bit. 1: enable parity bit 18 R/W PARITY_TYPE 0 Parity type bit. 0: even parity. 1: odd parity 17:16 R/W STOP_BIT_LEN 0 Stop bit length.00: 1 stop bit 01: 2 stop bit 10-11: reserved.15 R/W TWO_WIRE_EN 0 Two-wire mode enables. 0: four-wire mode. 1: Two-wire mode 14 - - 0 Reserved 13 R/W UART_RX_EN 0 Receive enable. 0: disable receive function. 1: enable receivefunction12 R/W UART_TX_EN 0 Transmit enable. 0: disable transmit function. 1: enabletransmit function11:0 R/W BAUD_RATE 0x120 Baud rate setup. Please refer to Baud Rate Generation Sectionfor detail.Di s t ri bu t et oE md o o r!UART_A Status Register (UART_A_STATUS)UART_A_STATUS is a read-only register to indicate the status of UART interface.Table 7. UART_A_STATUS register definition Name UART_A_STATUS Offset 0x2133Width 32-bit Bit R/W Name Default Description31:27 - - 0x00 Reserved26 R UART_RECV_BUSY 0 Receive state machine busy indicator. Being set to 1indicates receive state machine is busy25 R UART_XMIT_BUSY 0 Transmit state machine busy indicator. Being set to 1indicates transmit state machine is busy24 R RECV_FIFO_OVERFLOW 0 Receive FIFO overflow indicator. Being set to 1 indicatesreceive FIFO overflows23 R CTS_LEVEL 0 CTS signal level.22 R TX_FIFO_EMPTY 0 Transmit FIFO Empty indicator. Being set to 1 indicatesTransmit FIFO is empty21 R TX_FIFO_FULL 0 Transmit FIFO Full indicator. Being set to1 indicatesTransmit FIFO is full.20 R RX_FIFO_EMPTY 0 Receive FIFO Empty indicator. Being set to 1 indicatesReceive FIFO is empty19 R RX_FIFO_FULL 0 Receive FIFO Full indicator. Being set to 1 indicatesReceive FIFO is full.18 R TX_FIFO_WERR 0 Transmit FIFO writing error indicator. The bit is set to 1 ifwriting data to Transmit FIFO when Transmit FIFO is full.Note: Please use register UART_A_CONTROL bit 24 toclear this bit. Refer to UART_A_CONTROL registerdefinition.17 R FRAME_ERR 0 Frame Error indicator. The bit is set to 1 if frame errordetected.Note: Please use register UART_A_CONTROL bit 24 toclear this bit. Refer to UART_A_CONTROL registerdefinition.16 R PARITY_ERR 0 Parity Error indicator. The bit is set to 1 if parity errordetected.Note: Please use register UART_CONTROL bit 24 to clearthis bit. Refer to UART_A_CONTROL register definition.15 - - 0 Reserved14:8 R TX_FIFO_DCNT 0 Transmit FIFO data count. The value is the number ofbytes in the Transmit FIFO.7 R - 0 Reserved6:0 R RX_FIFO_DCNT 0 Receive FIFO data count. The value is the number ofbytes in the Receive FIFO.Di s t r i b u t e t o E m d o o r !UART_A Interrupt Control Register (UART_A_MISC)UART_A_MISC is the register to control UART related interrupt.Table 8. UART_A_MISC register definition Name UART_A_MISC Offset 0x2134Width 32-bit Bit R/W Name Default Description31 - - 0 Reserved30 R/W USE old Rx Baud 0 he Rx baud rate generator was re-designed to compute abaud rate correctly. If you want to use the old (stupid) logic,you can set this bit to 1.29 R/W ASYNC_FIFO_PURGE 0 Set to 1 after all UART bytes have been received in order topurge the data into the async FIFO28 R/W ASYNC_FIFO_EN 0 Automatically send to async FIFO module enable1: enable automatic sending0:disable automatic sending27 R/W CTS_FIL_TB_SEL 0 CTS input filter time base selection.A digital signal filter can be used to filter the UART CTS signalinput.The filter has two parameters, the time base and the numberof time base.0: The time base is 111nS.1: The time base is 1uS.26-24 R/W CTS_FIL_SEL 0 CTS input filter times000: No filter.…111: Maximum filter time. The time is 7x 111= 777nS(CTS_FIL_TB_SEL = 0) or 7x 1=7uS (CTS_FIL_TB_SEL = 1)23-20 R/W BAUD_RATE_EXT 0 Extend the baud rate divider to 16-bits together withUART_A_STATUS[11:0]Baud_Rate = {Reg4[23:20],Reg2[11:0]}19 R/W RX_FIL_TB_SEL 0 RX input filter time base selection.A digital signal filter can be used to filter the UART RX signalinput.The filter has two parameters, the time base and the times oftime base.0: The time base is 111nS.1: The time base is 1uS.18:16 R/W RX_FIL_SEL 0 RX input filter times000: No filter.…111: Maximum filter time. The time is 7x 111= 777nS(RX_FIL_TB_SEL = 0) or 7x 1=7uS (RX_FIL_TB_SEL = 1)15:8 R/W XMIT_IRQ_CNT 32 Transmit FIFO threshold.UART generates an interrupt when the number of bytes inTransmit FIFO is below the value of these bits.7:0 R/W RECV_IRQ_CNT 15 Receive FIFO threshold.UART generates an interrupt when the number bytes inReceive FIFO is large than the value of these bits.Di s t ri b u t e t o E m d o o r !UART_A_REG5Table 9. UART_A_REG5 register definition Name UART_A_REG5 Offset 0x2135Width 32-bit Bit R/W Name Default Description31-24 R/W - 0 unused23 R/W USE New Baud rate. 0 Over the years, the baud rate has been extended byconcatenating bits from different registers. To takeadvantage of the full 23-bit baud rate generate (extended to23 bits to accommodate very low baud rates), you must setthis bit. If this bit is set, then the baud rate is configuredusing bits [22:0] below22:0 R/W NEW_BAUD_RATE: 0 If bit[23] = 1 above, then the baud rate for the UART iscomputed using these bits. This was added in MX toaccommodate lower baud rates.Di s t r i b u t e t o E m d o o r !9.2. UART_BWrite Buffer Register (UART_B_WFIFO)UART_B_WFIFO is the data entry of UART_B transmit FIFO. Writing to the register puts a byte data into the top of transmit FIFO. The data at the front of the FIFO transmits automatically until transmit FIFO empty.Table 10. UART_B_WFIFO register definition Name UART_B_WFIFO Offset 0x2137 Width 32-bitBit R/W Name Default Description31:8 R - 0 Reserved7:0 W FIFO_WDATA - Write UART Transmit FIFO.Read Buffer Register (UART_B_RFIFO)UART_B_RFIFO is the data entry of UART Read FIFO. It latches the value of data byte at the front of UART Read FIFO. Table 9. UART_B_RFIFO register definition Name UART_B_RFIFO Offset 0x2138 Width 32-bit Bit R/W Name Default Description 31:8 R - 0 Reserved 7:0 R FIFO_RDATA 0x00 Read a byte from UART FIFO.Di s t r i b u t e t o E m d o o r !UART_B Mode Register (UART_B_CONTROL)UART_B_CONTROL is a control register.Table 10. UART_B_CONTROL register definition Name UART_B_CONTROL Offset 0x2139Width 32-bit Bit R/W Name Default Description31 R/W RTS_INV 0 Invert RTS signal. 0: RTS active LOW. 1: RTS active HIGH30 R/W ERR_MASK_EN 0 Error Mask enable. 0: disable error mask. 1: enable error mask. 29 R/W CTS_INV 0 Invert CTS signal. 0: CTS active LOW 1: CTS active HIGH.28 R/W UART_TX_INT_EN 0 Transmit byte interrupt enable. When enabled, an interrupt will begenerated whenever a byte is read from Transmit FIFO.0: disable transmit byte interrupt1: enable transmit byte interrupt27 R/W UART_RX_INT_EN 0 Receive byte interrupt enable. When enabled, an interrupt will begenerated whenever a byte is written to Read FIFO.0: disable receive byte interrupt1: enable receive byte interrupt26 R/W UART_TX_INV 0 Invert TX signal. 0: TX active HIGH. 1: TX active LOW 25 R/W UART_RX_INV 0 Invert RX signal. 0: RX active HIGH. 1: RX active LOW 24 R/W UART_CLR_ERR 0 Clear error. Writing 1 to this register bit clears error.Note: This bit does not clear to 0 automatically. Please set the bitto 0 after clearing error manually.23 R/W UART_RX_RST 0 Reset receive state machine. Writing 1 to this register bit resetsreceive state machine.22 R/W UART_TX_RST 0 Reset transmit state machine. Write 1 to this register bit resettransmit state machine.21:20 R/W UART_DATA_LEN 00 Character length of data.00: 8-bit01: 7-bit10: 6-bit11: 5-bit19 R/W PARITY_EN 1 Parity enable bit. 0: disable parity bit. 1: enable parity bit 18 R/W PARITY_TYPE 0 Parity type bit. 0: even parity. 1: odd parity17:16 R/W STOP_BIT_LEN 0 Stop bit length.00: 1 stop bit01: 2 stop bit10-11: reserved.15 R/W TWO_WIRE_EN 0 Two-wire mode enables. 0: four-wire mode. 1: Two-wire mode 14 - - 0 Reserved13 R/W UART_RX_EN 0 Receive enable. 0: disable receive function. 1: enable receivefunction12 R/W UART_TX_EN 0 Transmit enable. 0: disable transmit function. 1: enabletransmit function11:0 R/W BAUD_RATE 0x120 Baud rate setup. Please refer to Baud Rate Generation Sectionfor detail.D i s t ri b u t e t o E m d o o r !UART_B Status Register (UART_STATUS)UART_B_STATUS is a read-only register to indicate the status of UART interface.Table 13. UART_B_STATUS register definition Name UART_B_STATUS Offset 0x213AWidth 32-bit Bit R/W Name Default Description31:27 - - 0x00 Reserved26 R UART_RECV_BUSY 0 Receive state machine busy indicator. Being set to 1indicates receive state machine is busy25 R UART_XMIT_BUSY 0 Transmit state machine busy indicator. Being set to 1indicates transmit state machine is busy24 R RECV_FIFO_OVERFLOW 0 Receive FIFO overflow indicator. Being set to 1 indicatesreceive FIFO overflows23 R CTS_LEVEL 0 CTS signal level.22 R TX_FIFO_EMPTY 0 Transmit FIFO Empty indicator. Being set to 1 indicatesTransmit FIFO is empty21 R TX_FIFO_FULL 0 Transmit FIFO Full indicator. Being set to1 indicatesTransmit FIFO is full.20 R RX_FIFO_EMPTY 0 Receive FIFO Empty indicator. Being set to 1 indicatesReceive FIFO is empty19 R RX_FIFO_FULL 0 Receive FIFO Full indicator. Being set to 1 indicatesReceive FIFO is full.18 R TX_FIFO_WERR 0 Transmit FIFO writing error indicator. The bit is set to 1 ifwriting data to Transmit FIFO when Transmit FIFO is full.Note: Please use register UART_B_CONTROL bit 24 toclear this bit. Refer to UART_B_CONTROL registerdefinition.17 R FRAME_ERR 0 Frame Error indicator. The bit is set to 1if frame errordetected.Note: Please use register UART_B_CONTROL bit 24 toclear this bit. Refer to UART_B_CONTROL registerdefinition.16 R PARITY_ERR 0 Parity Error indicator. The bit is set to 1 if parity errordetected.Note: Please use register UART_CONTROL bit 24 to clearthis bit. Refer to UART_B_CONTROL register definition.15 - - 0 Reserved14:8 R TX_FIFO_DCNT 0 Transmit FIFO data count. The value is the number ofbytes in the Transmit FIFO.7 R - 0 Reserved6:0 R RX_FIFO_DCNT 0 Receive FIFO data count. The value is the number ofbytes in the Receive FIFO.Di s t r i b u t e t o E m d o o r !UART_B Interrupt Control Register (UART_B_MISC)UART_B_MISC is the register to control UART related interrupt.Table 11. UART_B_MISC register definition Name UART_B_MISC Offset 0x213BWidth 32-bit Bit R/W Name Default Description31 - - 0 Reserved30 R/W USE old Rx Baud 0 he Rx baud rate generator was re-designed to compute abaud rate correctly. If you want to use the old (stupid) logic,you can set this bit to 1.29 R/W ASYNC_FIFO_PURGE 0 Set to 1 after all UART bytes have been received in order topurge the data into the async FIFO28 R/W ASYNC_FIFO_EN 0 Automatically send to async FIFO module enable1: enable automatic sending0:disable automatic sending27 R/W CTS_FIL_TB_SEL 0 CTS input filter time base selection.A digital signal filter can be used to filter the UART CTS signalinput.The filter has two parameters, the time base and the numberof time base.0: The time base is 111nS.1: The time base is 1uS.26-24 R/W CTS_FIL_SEL 0 CTS input filter times000: No filter.…111: Maximum filter time. The time is 7x 111= 777nS(CTS_FIL_TB_SEL = 0) or 7x 1=7uS (CTS_FIL_TB_SEL = 1)23-20 R/W BAUD_RATE_EXT 0 Extend the baud rate divider to 16-bits together withUART_B_STATUS[11:0]Baud_Rate = [BAUD_RATE_EXT: BAUD_RATE]19 R/W RX_FIL_TB_SEL 0 RX input filter time base selection.A digital signal filter can be used to filter the UART RX signalinput.The filter has two parameters, the time base and the times oftime base.0: The time base is 111nS.1: The time base is 1uS.18:16 R/W RX_FIL_SEL 0 RX input filter times000: No filter.…111: Maximum filter time. The time is 7x 111= 777nS(RX_FIL_TB_SEL = 0) or 7x 1=7uS (RX_FIL_TB_SEL = 1)15:8 R/W XMIT_IRQ_CNT 32 Transmit FIFO threshold.UART generates an interrupt when the number of bytes inTransmit FIFO is below the value of these bits.7:0 R/W RECV_IRQ_CNT 15 Receive FIFO threshold.UART generates an interrupt when the number bytes inReceive FIFO is large than the value of these bits.Di s t r i b u t e t o E m d o o r !。

AML8726中文

1. General Description(总体描述)AML8726‐M3是一款专门为平板电脑、机顶盒、电视、高清多媒体播放器而设计的有关于多媒体方案处理的芯片。

它是集合了强大功能的CPU/GPU,一个根据以前的基础发展起来的视频编解码引擎与主要的外围设备最终形成了一个低功耗的多媒体解码芯片。

ARM Cprtex-A9 CPU 是一个综合处理器,它是由32KBL1指令,32KB数据缓存,128KB最大L2统一指令来提高改善系统的性能。

此外,它还用NEON SIMD CO-处理器来提高多媒体软件的能力(图像)。

它能提供超过1GHz频率和支持外部存储设备(像存储卡之类)。

图形子系统由两个图形引擎和一个活动视频/图像输出通道组成,ARM Mali‐400 GPU能处理所有的OpenGL ES 1.1/2.0 and OpenVG图形程序,而2.5D图像处理器另外处理图像缩放、透明度(对比度)、旋转与颜色空间转换操作。

视频输出通道能执行高级图像修正和改进的工作,总之,CPU和GPU处理并管理着所有系统工作、网络、用户界面、游戏运行等。

三个另外的处理器代帮助Cortex-A9 CPU处理所有的音频、视频的解码处理---MediaCPU与MediaDSPs还有一个视频解码专用的硬件设备。

MediaCPU对音频进行优化和处理所有音频的解码,双重的MediaDSPs和视频解码专用设备能对所有的高清视频进行解码:H.264, MVC,MPEG‐1/2/4, VC‐1/WMV, AVS, RealVideo 和MJPEG streams. 这个视频解码引擎同时也能够解码JPEG图片,并且没有尺寸的限制。

AML8726‐M3集中完成音频/视频、输入/输出接口:包括TCON LVDS/ mini‐L VDS面板界面,TCON RGB888 TTL 面板界面,一个HDMI1.4a 3D输出,CEC 和PHY,四个支持视频DAC复合输出,CVBS, YPbPr and VGA 输出,一个完全支持CODEC解码的PA耳机和麦克风装置,12S和SPDIF数字音频信号输入/输出界面,一个PCM音频界面和一个ITU601/656摄像输入界面。

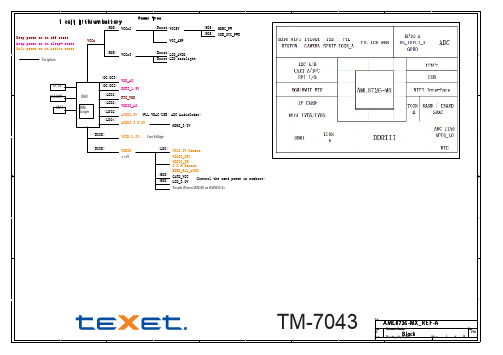

AML8726-MX_REF-A TM-7043xd

VCCx2

VCCx <MOS>

VCCx3

For option

<Boost> LCD_AVDD <Boost> LED backlight

D

<DC/DC3>

DC_IN USB PWR VBAT PMU PWM Charger

VDD_AO DDR3_1.5V RTC_VDD VDDIO_AO AVDD2.5V (PLL/VDAC/USB/ ADC/AudioCodac) HDMI_3.3V

5

4

3

2

1

1 cel l l i t hi um bat t er y

<MOS> Keep power on in off state keep power on in sleep# state Only power on in Active state

D

Power Tr ee <Boost> VCC5V VCC_AMP <MOS> <MOS> HDMI_PW USB_OTG_PWR

100K R 0402

!"#

G ND

R 16

G ND

1uF V INT C 0402 200 K _1% R 0402 C 0402 C 12 0.1uF C 13 1uF C 0402

L4 D18H2A C 27

G ND

10uF _6 .3V C 0805

G ND

V DD IO

C

DC/DC VDDIO

4.7uH_1 .5A L4 D18H2A V CCX

C 29 C 30

G ND

4.7uF _6 .3V C 0805 10uF _6 .3V C 0805 G ND

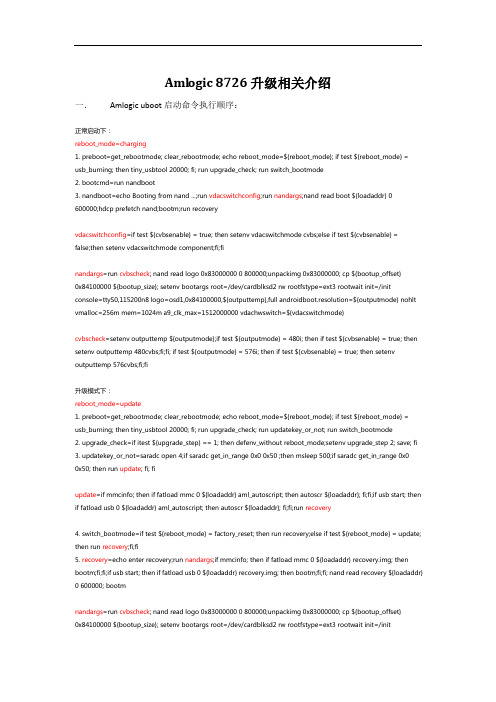

AMLOGIC 8726 升级相关介绍

Aml ogic 8726升级相关介绍一.Amlogic uboot启动命令执行顺序:正常启动下:reboot_mode=charging1. preboot=get_rebootmode; clear_rebootmode; echo reboot_mode=${reboot_mode}; if test ${reboot_mode} = usb_burning; then tiny_usbtool 20000; fi; run upgrade_check; run switch_bootmode2. bootcmd=run nandboot3. nandboot=echo Booting from nand ...;run vdacswitchconfig;run nandargs;nand read boot ${loadaddr} 0 600000;hdcp prefetch nand;bootm;run recoveryvdacswitchconfig=if test ${cvbsenable} = true; then setenv vdacswitchmode cvbs;else if test ${cvbsenable} = false;then setenv vdacswitchmode component;fi;finandargs=run cvbscheck; nand read logo 0x83000000 0 800000;unpackimg 0x83000000; cp ${bootup_offset}0x84100000 ${bootup_size}; setenv bootargs root=/dev/cardblksd2 rw rootfstype=ext3 rootwait init=/init console=ttyS0,115200n8 logo=osd1,0x84100000,${outputtemp},full androidboot.resolution=${outputmode} nohlt vmalloc=256m mem=1024m a9_clk_max=1512000000 vdachwswitch=${vdacswitchmode}cvbscheck=setenv outputtemp ${outputmode};if test ${outputmode} = 480i; then if test ${cvbsenable} = true; then setenv outputtemp 480cvbs;fi;fi; if test ${outputmode} = 576i; then if test ${cvbsenable} = true; then setenv outputtemp 576cvbs;fi;fi升级模式下:reboot_mode=update1. preboot=get_rebootmode; clear_rebootmode; echo reboot_mode=${reboot_mode}; if test ${reboot_mode} = usb_burning; then tiny_usbtool 20000; fi; run upgrade_check; run updatekey_or_not; run switch_bootmode2. upgrade_check=if itest ${upgrade_step} == 1; then defenv_without reboot_mode;setenv upgrade_step 2; save; fi3. updatekey_or_not=saradc open 4;if saradc get_in_range 0x0 0x50 ;then msleep 500;if saradc get_in_range 0x00x50; then run update; fi; fiupdate=if mmcinfo; then if fatload mmc 0 ${loadaddr} aml_autoscript; then autoscr ${loadaddr}; fi;fi;if usb start; then if fatload usb 0 ${loadaddr} aml_autoscript; then autoscr ${loadaddr}; fi;fi;run recovery4. switch_bootmode=if test ${reboot_mode} = factory_reset; then run recovery;else if test ${reboot_mode} = update; then run recovery;fi;fi5. recovery=echo enter recovery;run nandargs;if mmcinfo; then if fatload mmc 0 ${loadaddr} recovery.img; then bootm;fi;fi;if usb start; then if fatload usb 0 ${loadaddr} recovery.img; then bootm;fi;fi; nand read recovery ${loadaddr} 0 600000; bootmnandargs=run cvbscheck; nand read logo 0x83000000 0 800000;unpackimg 0x83000000; cp ${bootup_offset}0x84100000 ${bootup_size}; setenv bootargs root=/dev/cardblksd2 rw rootfstype=ext3 rootwait init=/initconsole=ttyS0,115200n8 logo=osd1,0x84100000,${outputtemp},full androidboot.resolution=${outputmode} nohlt vmalloc=256m mem=1024m a9_clk_max=1512000000 vdachwswitch=${vdacswitchmode}cvbscheck=setenv outputtemp ${outputmode};if test ${outputmode} = 480i; then if test ${cvbsenable} = true; then setenv outputtemp 480cvbs;fi;fi; if test ${outputmode} = 576i; then if test ${cvbsenable} = true; then setenv outputtemp 576cvbs;fi;fi串口调试模式下uboot下用bootm命令升级顺序#tftp 82000000 recovery.img#bootm1. 升级查找factory_update_param.aml文件的顺序:sdcard-->udisk如果在sdcard中找到了文件名为factory_update_param.aml的文件,则使用该文件升级系统,如果factory_update_param.aml文件中的命令行有错,导致无法升级,也不会去再找udisk中的factory_update_param.aml文件如果在sdcard中没有找到文件名为factory_update_param.aml的文件,就去udisk中找2.如果同时存在两个udisk时,recovery只会挂载第0个udisk(即靠近micro usb口的那个usb口上的udisk),如果udisk0中无factory_update_param.aml文件或factory_update_param.aml文件命令行有误,recovery也不会到udisk1去找factory_update_param.aml文件uboot是通过#define reboot_mode *((volatile unsigned long*)(P_AO_RTI_STATUS_REG1))此寄存器的值来判断是加载recovery分区还是加载boot分区(正常kernel)的U盘升级脚本factory_update_param.aml如下:--update_package=/udisk/g18ref-ota-20130716.zip--wipe_data--wipe_cachesd卡升级脚本factory_update_param.aml如下:--update_package=/sdcard/g18ref-ota-20130716.zip--wipe_data--wipe_cache二.Amlogic升级模式系统更新update.zip包的两种方式:1. Android在升级系统时获得update.zip包的方式有两种。

Amlogic S802?华曦达DV7819四核OTT机顶盒

Amlogic S802?华曦达DV7819四核OTT机顶盒说到华曦达DV7819,就不得不提一下,晶晨半导体的四核芯片S802。

早在2013年3月份的时候,晶晨就曝光了一款即将推出的四核芯片,当时是叫AML8726-M8(正式型号是S802),并宣称将会在2013年的4月发布。

由于种种原因Amlogic S802终于在2013年的10月份正式亮相,而所有的有意向的厂家,正式推出Amlogic S802也是在2014年以后的事情了。

华曦达科技DV7819则正是采用了Amlogic S802的主芯片。

OTT盒子主控处理器市场,晶晨半导体凭借对市场的准确把握提早布局, 加上自身在流媒体播放方面深厚的技术积累以及成熟的OTT盒子的解决方案,毫无争议地占据了主导地位。

(从上图我们就可以非常清晰的看出了,Amlogic M3、Amlogic 8726MX、Amlogic S802三款芯片的大致区别在哪里了。

所以说,S802的性能是高于其余两款。

)这真的可以算是“千呼万唤始出来,犹抱琵琶半遮面”普通消费者如果想了解此款芯片,其实可以记住12个字,那就是------“顶配四核,好而不贵,价格实惠”。

那么我们就来通过华曦达DV7819 OTT机顶盒来初步了解一下该款芯片的各项参数吧。

华曦达DV7819Cortex-A9r4四核 CPU首先,华曦达DV7819采用的是Amlogic S802,CPU采用台积电最先进的28nm HPM工艺,基于最新的Cortex-A9r4四核架构,单核主频高达2GHz。

对于CPU性能来说,除了架构之外,影响最大的就是主频了。

但是主频提高则会带来功耗以及芯片发热的提高。

要想解决这一问题,最好的办法就是提高芯片的制程工艺,芯片的集成度更高,单位面积更小,功耗及发热也会进一步更少。

所以晶晨S802采用了与高通最新的骁龙800系列处理器一样的台积电28nm HPM工艺。

据说这两款四核的CPU性能可达20000DMIPS,是四核Cortex-A7性能的近三倍。

国产四核主控处理器芯片一瞥

国产四核主控处理器芯片一瞥海思K3V2最早推出四核主控的本土芯片公司是海思,在去年3月份它就推出了基于ARM Cortex-A9处理器K3V2,不过该主控芯片也就是自产自销,还不能惠及广大国产平板电脑厂商。

K3V2处理器尺寸为12×12mm,号称是2012年初业界体积最小的四核A9架构处理器。

它采用台积电40nm制程,主频分为1.2GHz和1.5GHz,官方声称这款芯片能够在一系列的基准测试中超越Tegra3性能30%到50%。

K3V2内置两颗Vivante GC4000组成16核图形处理器,拥有32位渲染设计,能够支持35FPS的视频处理能力。

该芯片还采用了高端的64bit带宽DDR 内存设计来充分释放四核的性能,支持Mobile SDR/DDR SDRAM,提供片内8层总线并行访问,最高到30Gbps的片内带宽;支持8/16bit NANDFlash存储访问及Flash lock功能。

另外该方案特点还包括支持智能功耗性能调节、支持多种外设接口和传感检查功能、提供方案级完整的电源系统与多种充电方式等。

炬力ATM70292012年10月份,珠海炬力推出了其首个猫头鹰系列四核芯片ATM7029,它基于ARM Cortex-A9系列CPU,采用ARMv7-A架构,单核最高运行频率可达1.3GHz;图形处理方面采用了多核3D GPU与一颗专有的独立2D GPU;支持1080p视频编解码。

至于功耗,炬力表示ATM7029集成了领先的分模块独立电源域管理系统和智能调节背光技术,能做到待机时间长达1,000小时、视频连续播放14小时、游戏时长12小时、上网时间10小时。

ATM7029的特点还包括:带有炬力独创的QuickBoot技术,支持1秒瞬间启动,开机速度也仅需10秒,是全球开机最快的平板电脑方案之一;支持画中画,6路视频同时播放,即1屏6播;集成了USB3.0 PHY;内置HDMI 1.4a;支持最新制程60bit EEC NAND Flash等。

AML8726-MXL MXS GPIO User Guide 20130124

Application NotesAML 8726-MXL/MXSGPIO User GuideRevision 0.3 PRELIMINARYAMLOGIC, Inc.3930 Freedom Circle Santa Clara, CA 95054U.S.A. AMLOGIC reserves the right to change any information described herein at any time without notice.AMLOGIC assumes no responsibility or liability from use of such information.Di st r i b u t et oS ky n o o n !Table of Content1 GENERAL DESCRIPTION ...................................................................................................................................... 42 GPIO BANKS ............................................................................................................................................................. 43 GPIO GENERAL FUNCTIONAL REGISTER ......................................................................................................4 4PIN MULTIPLEXING ............................................................................................................................................... 9 4.1 GPIO F UNCTION S ETTING ..................................................................................................................................... 9 4.2 R EGISTER M ACRO D EFINITION .............................................................................................................................. 9 4.3 D EFAULT F UNCTION .............................................................................................................................................. 9 4.4 P IN M ULTIPLEXING .............................................................................................................................................. 10 4.4.1 GPIO Bank A .............................................................................................................................................. 10 4.4.2 GPIO Bank B .............................................................................................................................................. 10 4.4.3 GPIO Bank C .............................................................................................................................................. 11 4.4.4 GPIO Bank D .............................................................................................................................................. 12 4.4.5 GPIO Bank E .............................................................................................................................................. 12 4.4.6 GPIO Bank X .............................................................................................................................................. 13 4.4.7 GPIO Bank Z .............................................................................................................................................. 14 4.4.8 GPIO Bank AO ........................................................................................................................................... 15 4.4.9 GPIO Bank BOOT ...................................................................................................................................... 16 4.4.10 GPIO Bank CARD ...................................................................................................................................... 17 5 ADDRESS MAPPING . (17)Di st ri bu tet oS ky n o o n !Revision HistoryRevision Number Revised Date By Changes0.3 2013/01/15 Kevin Zhu Initial version releaseDi st ri bu tet oS ky n o o n !1 General DescriptionThis document is a general user guide of Amlogic AML8726-MXL/MXS GPIOs. In this document, it describes:● The selection of GPIO operation mode.● The input and output register of each GPIO. ● GPIO pin multiplex selection2 GPIO BanksAML8726-MXL/MXS GPIOs are organized as 10 banks: 8 general banks and 2 dedicated banks.The 8 general banks are:● Bank A: There are 6 pin outs in this bank between GPIOA_14 and GPIOA_27. ● Bank B: There are 18 pin outs in this bank between GPIOB_2 and GPIOB_23. ● Bank C: There are 10 pin outs in this bank between GPIOC_0 and GPIOC_13. ● Bank D: There are 8 pin outs in this bank between GPIOD_0 and GPIOD_9. ● Bank E: There are 7 pin outs in this bank between GPIOE_0 and GPIOE_11. ● Bank X: There are 23 pin outs in this bank between GPIOX_0 and GPIOX_28. ● Bank Z: There are 13 pin outs in this bank from GPIOZ_0 to GPIOZ_12.● Bank AO: There are 12 pin outs in this bank from GPIOAO_0 to GPIOAO_11.The 2 dedicated banks are:● Bank BOOT: There are 18 pin outs in this bank from BOOT_0 to BOOT_17. In most application, all pins inthis bank are used to connect boot device such as NAND Flash, eMMC or SD card.● Bank CARD: There are 8 pin outs in this bank between CARD_0 and CARD_8. In most application, allpins in this bank are used to connect memory card such SD card.Please avoid using pins in Bank BOOT and CARD as ordinary GPIOs.3 GPIO General Functional RegisterEach GPIO in each bank can be controlled and operated by four register sets:● OEN: It is mode definition register which uses to control the operation mode of each GPIO in the bank.⏹ “1”: Set the pin to input mode. It is the default mode after chip power-on/reset. In this mode, the GPIOis tri-state and input is valid.⏹ “0”: Set the pin to output mode. In this mode, the GPIO voltage level is controlled by OUT registers. ● OUT: It is to setup the output voltage level of each GPIO to logic HIGH or logic LOW.⏹ “1” Set the GPIO to logic HIGH. ⏹ “0” Set the GPIO to logic LOW.● IN: It is used only in input mode. It can be read and the value is the input logic voltage value. ● PU/PD: It is used to enable or disable build-in pull-up or pull-down resister of each GPIO.⏹ “1” Disable pull-up or pull-down resister. When disabled, the GPIO is High-Z. ⏹ “0” Enable pull-up or pull-down resister.The OEN, OUT, IN and PU/PD registers and mapping to each GPIO in each GPIO bank are listed in Table 1.Di st ri bu tet oS ky n o o n !Table 1. GPIO General Function Register Control BitsBGA Ball Number Package Name OEN(Read Write)OUT(Write Only)IN(Read Only)PU/PD(Read Write) IO TypeDefault State after resetBank A A20 GPIOA_14 0x200c bit[14] 0x200d bit[14] 0x200e bit[14] 0x203A bit[14] Tri-State Pull-up C19 GPIOA_15 0x200c bit[15] 0x200d bit[15] 0x200e bit[15] 0x203A bit[15] Tri-State Pull-up B19 GPIOA_16 0x200c bit[16] 0x200d bit[16] 0x200e bit[16] 0x203A bit[16] Tri-State Pull-up C18 GPIOA_19 0x200c bit[19] 0x200d bit[19] 0x200e bit[19] 0x203A bit[19] Tri-State Pull-up B18 GPIOA_25 0x200c bit[25] 0x200d bit[25] 0x200e bit[25] 0x203A bit[25] Tri-State Pull-up A18 GPIOA_270x200c bit[27]0x200d bit[27]0x200e bit[27]0x203A bit[27] Tri-State Pull-up Bank BC17 GPIOB_2 0x200F bit[2] 0x2010 bit[2] 0x2011 bit[2] 0x203B bit[2] Tri-State Pull-Down A17 GPIOB_3 0x200F bit[3] 0x2010 bit[3] 0x2011 bit[3] 0x203B bit[3] Tri-State Pull-Down B17 GPIOB_4 0x200F bit[4] 0x2010 bit[4] 0x2011 bit[4] 0x203B bit[4] Tri-State Pull-Down C16 GPIOB_5 0x200F bit[5] 0x2010 bit[5] 0x2011 bit[5] 0x203B bit[5] Tri-State Pull-Down B16 GPIOB_6 0x200F bit[6] 0x2010 bit[6] 0x2011 bit[6] 0x203B bit[6] Tri-State Pull-Down C15 GPIOB_7 0x200F bit[7] 0x2010 bit[7] 0x2011 bit[7] 0x203B bit[7] Tri-State Pull-Down D17 GPIOB_10 0x200F bit[10] 0x2010 bit[10] 0x2011 bit[10] 0x203B bit[10] Tri-State Pull-Down E17 GPIOB_11 0x200F bit[11] 0x2010 bit[11] 0x2011 bit[11] 0x203B bit[11] Tri-State Pull-Down E16 GPIOB_12 0x200F bit[12] 0x2010 bit[12] 0x2011 bit[12] 0x203B bit[12] Tri-State Pull-Down E15 GPIOB_13 0x200F bit[13] 0x2010 bit[13] 0x2011 bit[13] 0x203B bit[13] Tri-State Pull-Down D15 GPIOB_14 0x200F bit[14] 0x2010 bit[14] 0x2011 bit[14] 0x203B bit[14] Tri-State Pull-Down D14 GPIOB_15 0x200F bit[15] 0x2010 bit[15] 0x2011 bit[15] 0x203B bit[15] Tri-State Pull-Down B15 GPIOB_18 0x200F bit[18] 0x2010 bit[18] 0x2011 bit[18] 0x203B bit[18] Tri-State Pull-Down C14 GPIOB_19 0x200F bit[19] 0x2010 bit[19] 0x2011 bit[19] 0x203B bit[19] Tri-State Pull-Down B14 GPIOB_20 0x200F bit[20] 0x2010 bit[20] 0x2011 bit[20] 0x203B bit[20] Tri-State Pull-Down A14 GPIOB_21 0x200F bit[21] 0x2010 bit[21] 0x2011 bit[21] 0x203B bit[21] Tri-State Pull-Down C13GPIOB_22 0x200F bit[22] 0x2010 bit[22] 0x2011 bit[22] 0x203B bit[22] Tri-State Pull-Down A13GPIOB_230x200F bit[23]0x2010 bit[23]0x2011 bit[23]0x203B bit[23] Tri-State Pull-Down Bank CJ19GPIOC_0 0x2012 bit[0] 0x2013 bit[0] 0x2014 bit[0] 0x203C bit[0] Tri-State (24mA) Pull-Down H19 GPIOC_3 0x2012 bit[3] 0x2013 bit[3] 0x2014 bit[3] 0x203C bit[3] Tri-State Pull-Down H18 GPIOC_4 0x2012 bit[4] 0x2013 bit[4] 0x2014 bit[4] 0x203C bit[4] Tri-State Pull-Down T4 GPIOC_7 0x2012 bit[7] 0x2013 bit[7] 0x2014 bit[7] 0x203C bit[7] Tri-State Pull-Down R5 GPIOC_8 0x2012 bit[8] 0x2013 bit[8] 0x2014 bit[8] 0x203C bit[8] Tri-State Pull-Down T5GPIOC_90x2012 bit[9]0x2013 bit[9]0x2014 bit[9]0x203C bit[9]Tri-StatePull-DownDi st ri bu tet oS ky n o o n !U5 GPIOC_10 0x2012 bit[10] 0x2013 bit[10] 0x2014 bit[10] 0x203C bit[10] Tri-State (24mA) High-Z U4 GPIOC_11 0x2012 bit[11] 0x2013 bit[11] 0x2014 bit[11] 0x203C bit[11] Tri-State (24mA) High-Z AA1 GPIOC_12 0x2012 bit[12] 0x2013 bit[12] 0x2014 bit[12] 0x203C bit[12] Tri-State (24mA) High-Z AA2 GPIOC_130x2012 bit[13]0x2013 bit[13]0x2014 bit[13] 0x203C bit[13] Tri-State (24mA) High-Z Bank DE14 GPIOD_0 0x2012 bit[16] 0x2013 bit[16] 0x2014 bit[16] 0x203C bit[16] Tri-State (24mA) Pull-Down B13 GPIOD_1 0x2012 bit[17] 0x2013 bit[17] 0x2014 bit[17] 0x203C bit[17] Tri-State (24mA) Pull-Down C12 GPIOD_2 0x2012 bit[18] 0x2013 bit[18] 0x2014 bit[18] 0x203C bit[18] Tri-State Pull-Down B12 GPIOD_3 0x2012 bit[19] 0x2013 bit[19] 0x2014 bit[19] 0x203C bit[19] Tri-State Pull-Down C11 GPIOD_4 0x2012 bit[20] 0x2013 bit[20] 0x2014 bit[20] 0x203C bit[20] Tri-State Pull-Down B11 GPIOD_7 0x2012 bit[23] 0x2013 bit[23] 0x2014 bit[23] 0x203C bit[23] Tri-State Pull-Down C10 GPIOD_8 0x2012 bit[24] 0x2013 bit[24] 0x2014 bit[24] 0x203C bit[24] Tri-State Pull-Down B10 GPIOD_90x2012 bit[25] 0x2013 bit[25] 0x2014 bit[25]0x203C bit[25] Tri-State Pull-Down Bank EA10 GPIOE_0 0x2008 bit[0] 0x2009 bit[0] 0x200A bit[0] 0x2039 bit[0] Tri-State Pull-Up C9 GPIOE_1 0x2008 bit[1] 0x2009 bit[1] 0x200A bit[1] 0x2039 bit[1] Tri-State Pull-Up A9 GPIOE_2 0x2008 bit[2] 0x2009 bit[2] 0x200A bit[2] 0x2039 bit[2] Tri-State Pull-Up B9 GPIOE_3 0x2008 bit[3] 0x2009 bit[3] 0x200A bit[3] 0x2039 bit[3] Tri-State Pull-Up C8 GPIOE_4 0x2008 bit[4] 0x2009 bit[4] 0x200A bit[4] 0x2039 bit[4] Tri-State Pull-Up D9 GPIOE_10 0x2008 bit[10] 0x2009 bit[10] 0x200A bit[10] 0x2039 bit[10] Tri-State Pull-Up D8 GPIOE_110x2008 bit[11]0x2009 bit[11]0x200A bit[11] 0x2039 bit[11] Tri-State Pull-Up Bank XA3 GPIOX_0 0x2018 bit[0] 0x2019 bit[0] 0x201a bit[0] 0x203d bit[0] Tri-State Pull-Up B3 GPIOX_1 0x2018 bit[1] 0x2019 bit[1] 0x201a bit[1] 0x203d bit[1] Tri-State Pull-Up A2 GPIOX_2 0x2018 bit[2] 0x2019 bit[2] 0x201a bit[2] 0x203d bit[2] Tri-State Pull-Up B2 GPIOX_3 0x2018 bit[3] 0x2019 bit[3] 0x201a bit[3] 0x203d bit[3] Tri-State Pull-Up B1 GPIOX_4 0x2018 bit[4] 0x2019 bit[4] 0x201a bit[4] 0x203d bit[4] Tri-State Pull-Up C2 GPIOX_5 0x2018 bit[5] 0x2019 bit[5] 0x201a bit[5] 0x203d bit[5] Tri-State Pull-Up C1GPIOX_6 0x2018 bit[6] 0x2019 bit[6] 0x201a bit[6] 0x203d bit[6] Tri-State Pull-Up D3 GPIOX_7 0x2018 bit[7] 0x2019 bit[7] 0x201a bit[7] 0x203d bit[7] Tri-State Pull-Up D2 GPIOX_8 0x2018 bit[8] 0x2019 bit[8] 0x201a bit[8] 0x203d bit[8] Tri-State Pull-Up E3 GPIOX_9 0x2018 bit[9] 0x2019 bit[9] 0x201a bit[9] 0x203d bit[9] Tri-State Pull-Up E2 GPIOX_10 0x2018 bit[10] 0x2019 bit[10] 0x201a bit[10] 0x203d bit[10] Tri-State Pull-Up E4GPIOX_110x2018 bit[11]0x2019 bit[11]0x201a bit[11]0x203d bit[11]Tri-StatePull-UpDi st ri bu tet oS ky n o o n !F4 GPIOX_12 0x2018 bit[12] 0x2019 bit[12] 0x201a bit[12] 0x203d bit[12] Tri-State Pull-Up F5 GPIOX_13 0x2018 bit[13] 0x2019 bit[13] 0x201a bit[13] 0x203d Bit[13] Tri-State Pull-Up G5 GPIOX_14 0x2018 bit[14] 0x2019 bit[14] 0x201a bit[14] 0x203d bit[14] Tri-State Pull-Up H5 GPIOX_15 0x2018 bit[15] 0x2019 bit[15] 0x201a bit[15] 0x203d bit[15] Tri-State Pull-Up H4 GPIOX_16 0x2018 bit[16] 0x2019 bit[16] 0x201a bit[16] 0x203d bit[16] Tri-State Pull-Up E1 GPIOX_23 0x2018 bit[23] 0x2019 bit[23] 0x201a bit[23] 0x203d bit[23] Tri-State Pull-Up F3 GPIOX_24 0x2018 bit[24] 0x2019 bit[24] 0x201a bit[24] 0x203d bit[24] Tri-StatePull-UpF1 GPIOX_25 0x2018 bit[25] 0x2019 bit[25] 0x201a bit[25] 0x203d bit[25] Tri-State Pull-Up F2 GPIOX_26 0x2018 bit[26] 0x2019 bit[26] 0x201a bit[26] 0x203d bit[26] Tri-State Pull-Up G3 GPIOX_27 0x2018 bit[27] 0x2019 bit[27] 0x201a bit[27] 0x203d bit[27] Tri-State Pull-Up G2 GPIOX_280x2018 bit[28]0x2019 bit[28]0x201a bit[28]0x203d bit[28]Tri-State Pull-Up Bank ZE8 GPIOZ_0 0x2008 bit[16] 0x2009 bit[16] 0x200A bit[16] 0x2039 bit[16] Tri-State Pull-Up B8 GPIOZ_1 0x2008 bit[17] 0x2009 bit[17] 0x200A bit[17] 0x2039 bit[17] Tri-State Pull-Up C7 GPIOZ_2 0x2008 bit[18] 0x2009 bit[18] 0x200A bit[18] 0x2039 bit[18] Tri-State Pull-Up B7 GPIOZ_3 0x2008 bit[19] 0x2009 bit[19] 0x200A bit[19] 0x2039 bit[19] Tri-State Pull-Up C6 GPIOZ_4 0x2008 bit[20] 0x2009 bit[20] 0x200A bit[20] 0x2039 bit[20] Tri-State Pull-Up B6 GPIOZ_5 0x2008 bit[21] 0x2009 bit[21] 0x200A bit[21] 0x2039 bit[21] Tri-State Pull-Up A6 GPIOZ_6 0x2008 bit[22] 0x2009 bit[22] 0x200A bit[22] 0x2039 bit[22] Tri-State Pull-Up C5 GPIOZ_7 0x2008 bit[23] 0x2009 bit[23] 0x200A bit[23] 0x2039 bit[23] Tri-State Pull-Up A5 GPIOZ_8 0x2008 bit[24] 0x2009 bit[24] 0x200A bit[24] 0x2039 bit[24] Tri-State Pull-Up B5 GPIOZ_9 0x2008 bit[25] 0x2009 bit[25] 0x200A bit[25] 0x2039 bit[25] Tri-State Pull-Up C4 GPIOZ_10 0x2008 bit[26] 0x2009 bit[26] 0x200A bit[26] 0x2039 bit[26] Tri-State Pull-Up B4 GPIOZ_11 0x2008 bit[27] 0x2009 bit[27] 0x200A bit[27] 0x2039 bit[27] Tri-State Pull-Up C3 GPIOZ_120x2008 bit[28]0x2009 bit[28]0x200A bit[28]0x2039 bit[28]Tri-State Pull-Up Bank AOU20 GPIOAO_0 0xc8100024 bit[0] 0xc8100024 bit[16] 0xc8100028 bit[0] 0x000B bit[0] Tri-State Pull-Up U22 GPIOAO_1 0xc8100024 bit[1] 0xc8100024 bit[17] 0xc8100028 bit[1] 0x000B bit[1] Tri-State Pull-Up U21 GPIOAO_2 0xc8100024 bit[2] 0xc8100024 bit[18] 0xc8100028 bit[2] 0x000B bit[2] Tri-State Pull-Up T21 GPIOAO_3 0xc8100024 bit[3] 0xc8100024 bit[19] 0xc8100028 bit[3] 0x000B bit[3] Tri-State Pull-Up R20 GPIOAO_4 0xc8100024 bit[4] 0xc8100024 bit[20] 0xc8100028 bit[4] 0x000B bit[4] Tri-State Pull-Up R21 GPIOAO_5 0xc8100024 bit[5] 0xc8100024 bit[21] 0xc8100028 bit[5] 0x000B bit[5] Tri-State Pull-Up P20 GPIOAO_6 0xc8100024 bit[6] 0xc8100024 bit[22] 0xc8100028 bit[6] 0x000B bit[6] Tri-State Pull-Up P21GPIOAO_70xc8100024 bit[7]0xc8100024 bit[23]0xc8100028 bit[7]0x000B bit[7]Tri-StatePull-UpDi st ri bu tet oS ky n o o n !T18 GPIOAO_8 0xc8100024 bit[8] 0xc8100024 bit[24] 0xc8100028 bit[8] 0x000B bit[8] Tri-State Pull-Up R18 GPIOAO_9 0xc8100024 bit[9] 0xc8100024 bit[25] 0xc8100028 bit[9] 0x000B bit[9] Tri-State Pull-Up R19 GPIOAO_10 0xc8100024 bit[10] 0xc8100024 bit[26] 0xc8100028 bit[10] 0x000B bit[10] Tri-State Pull-Up P19 GPIOAO_110xc8100024 bit[11]0xc8100024 bit[27]0xc8100028 bit[11] 0x000B bit[11] Tri-State Pull-Up Bank BootN20 BOOT_0 0x2015 bit[0] 0x2016 bit[0] 0x2017 bit[0] 0x203D bit[0] Tri-State Pull-Up N22 BOOT_1 0x2015 bit[1] 0x2016 bit[1] 0x2017 bit[1] 0x203D bit[1] Tri-State Pull-Up N21 BOOT_2 0x2015 bit[2] 0x2016 bit[2] 0x2017 bit[2] 0x203D bit[2] Tri-State Pull-Up M20 BOOT_3 0x2015 bit[3] 0x2016 bit[3] 0x2017 bit[3] 0x203D bit[3] Tri-State Pull-Up M21 BOOT_4 0x2015 bit[4] 0x2016 bit[4] 0x2017 bit[4] 0x203D bit[4] Tri-State Pull-Up L20 BOOT_5 0x2015 bit[5] 0x2016 bit[5] 0x2017 bit[5] 0x203D bit[5] Tri-State Pull-Up L21 BOOT_6 0x2015 bit[6] 0x2016 bit[6] 0x2017 bit[6] 0x203D bit[6] Tri-State Pull-Up K20 BOOT_7 0x2015 bit[7] 0x2016 bit[7] 0x2017 bit[7] 0x203D bit[7] Tri-State Pull-Up K21 BOOT_8 0x2015 bit[8] 0x2016 bit[8] 0x2017 bit[8] 0x203D bit[8] Tri-State Pull-Up K22 BOOT_9 0x2015 bit[9] 0x2016 bit[9] 0x2017 bit[9] 0x203D bit[9] Tri-State Pull-Up J20 BOOT_10 0x2015 bit[10] 0x2016 bit[10] 0x2017 bit[10] 0x203D bit[10] Tri-State Pull-Up J22 BOOT_11 0x2015 bit[11] 0x2016 bit[11] 0x2017 bit[11] 0x203D bit[11] Tri-State Pull-Up J21 BOOT_12 0x2015 bit[12] 0x2016 bit[12] 0x2017 bit[12] 0x203D bit[12] Tri-State Pull-Up H20 BOOT_13 0x2015 bit[13] 0x2016 bit[13] 0x2017 bit[13] 0x203D bit[13] Tri-State Pull-Up H21 BOOT_14 0x2015 bit[14] 0x2016 bit[14] 0x2017 bit[14] 0x203D bit[14] Tri-State Pull-Up G20 BOOT_15 0x2015 bit[15] 0x2016 bit[15] 0x2017 bit[15] 0x203D bit[15] Tri-State Pull-Up K18 BOOT_16 0x2015 bit[16] 0x2016 bit[16] 0x2017 bit[16] 0x203D bit[16] Tri-State Pull-Up J18 BOOT_170x2015 bit[17]0x2016 bit[17]0x2017 bit[17]0x203D bit[17] Tri-State Pull-Up Bank CARDH3 CARD_0 0x201b bit[23] 0x201c bit[23] 0x201d bit[23] 0x203D bit[20] Tri-State Pull-Up H2 CARD_1 0x201b bit[24] 0x201c bit[24] 0x201d bit[24] 0x203D bit[21] Tri-State Pull-Up J3 CARD_2 0x201b bit[25] 0x201c bit[25] 0x201d bit[25] 0x203D bit[22] Tri-State Pull-Up J2 CARD_3 0x201b bit[26] 0x201c bit[26] 0x201d bit[26] 0x203D bit[23] Tri-State Pull-Up J1CARD_4 0x201b bit[27] 0x201c bit[27] 0x201d bit[27] 0x203D bit[24] Tri-State Pull-Up K3 CARD_5 0x201b bit[28] 0x201c bit[28] 0x201d bit[28] 0x203D bit[25] Tri-State Pull-Up L4 CARD_6 0x201b bit[29] 0x201c bit[29] 0x201d bit[29] 0x203D bit[26] Tri-State Pull-Up J5CARD_80x201b bit[31]0x201c bit[31]0x201d bit[31]0x203D bit[28]Tri-StatePull-UpDi st ri bu tet oS ky n o o n !4 Pin MultiplexingMost GPIOs of AML8726-MXL/MXS are multiplexed and have multi-functions. The function of each GPIO is controlled by register. The GPIO and function relationship is defined in all bank pin multiplexing tables.Amlogic provides Software Development Kit (SDK) with Linux Kernel for AML8726-MXL/MXS. In SDK, the GPIO function selection control register is defined as a set of Macro Definition. Each Macro Definition represents a register address of 32-bit data width.4.1 GPIO Function SettingTo set a GPIO pin to a given function, please follow the steps as below: 1. Look up in each bank pin multiplexing tables for the required function.2. According to corresponding abbreviated name of macro definition (REGX[b] or AO_REG[b]), check inTable 2 for its complete name in SDK to access the register. Meanwhile, direct access with address is also possible. For AO_REG, this is the only way since the macro definition for it is currently not defined yet. 3. Set bit [b] in the Macro register/Address to 1 to enable the function. The signal of function will bemultiplexed to the pin defined and can be operated at the position defined in BGA Ball Number column.Note: In principle, only one bit in each GPIO package should be set to 1 in order to enable a specific function. However, in case more than one bit is set, the last function setting is valid in a sequential operation.4.2 Register Macro DefinitionThe register macro definition name mapping in SDK and its address is shown below:Table 2. Register Macro Definition and its AddressName of Macro Definition In SDK Abbreviation in Table 3~8 Address Default Value after power-on/Reset PERIPHS_PIN_MUX_0 REG0 0x202C 0x0000 PERIPHS_PIN_MUX_1 REG1 0x202D 0x0000 PERIPHS_PIN_MUX_2 REG2 0x202E 0x0000 PERIPHS_PIN_MUX_3 REG3 0x202F 0x0000 PERIPHS_PIN_MUX_4 REG4 0x2030 0x0000 PERIPHS_PIN_MUX_5 REG5 0x2031 0x0000 PERIPHS_PIN_MUX_6 REG6 0x2032 0x0000 PERIPHS_PIN_MUX_7 REG7 0x2033 0x0000 PERIPHS_PIN_MUX_8 REG8 0x2034 0x0000 PERIPHS_PIN_MUX_9 REG9 0x2035 0x0000 - AO_REG 0x0005 0x00004.3 Default FunctionAfter power-on/reset, all GPIOs are working as GPIO until they are set. The default value of each pin multiplexing registers is 0.Di st ri bu tet oS ky n o o n !4.4 Pin Multiplexing4.4.1 GPIO Bank AThe GPIO Bank A is not pre-assigned to any specific function and can be multiplexed to any general purpose functions.4.4.2 GPIO Bank BThe GPIO Bank B can be multiplexed to functions as:LCD output: The parallel video data output to LCD panel. It is used to connect LCD panel data port.Table 3. GPIO Bank B Pin Multiplexing TableBGA Ball Number Package Name LCD output C17 GPIOB_2 LCD_R2 REG0[0] A17 GPIOB_3 LCD_R3 REG0[0] B17 GPIOB_4 LCD_R4 REG0[0] C16 GPIOB_5 LCD_R5 REG0[0] B16 GPIOB_6 LCD_R6 REG0[0] C15 GPIOB_7 LCD_R7 REG0[0] D17 GPIOB_10 LCD_G2 REG0[2] E17 GPIOB_11 LCD_G3 REG0[2] E16 GPIOB_12 LCD_G4 REG0[2] E15 GPIOB_13 LCD_G5 REG0[2] D15 GPIOB_14 LCD_G6 REG0[2] D14 GPIOB_15 LCD_G7 REG0[2] B15 GPIOB_18 LCD_B2 REG0[4] C14GPIOB_19 LCD_B3 REG0[4] B14 GPIOB_20 LCD_B4 REG0[4] A14 GPIOB_21 LCD_B5 REG0[4] C13 GPIOB_22 LCD_B6 REG0[4] A13GPIOB_23LCD_B7 REG0[4]Di st ri bu tet oS ky n o o n !The GPIO Bank C can be multiplexed to functions as: ● SPDIF: SDPIF serial digital audio input and output ● PWM: Pulse width modulation output● LVDS TCON-A: The TCON interface for mini-LVDS LCD panel.● HDMI: The control and configuration interface of HDMI TX including I2C interface, CEC and plug-indetection.Table 4. GPIO Bank C Pin Multiplexing TableBGA Ball Number Package Name SPDIF PWM Mini-LVDS TCONHDMI J19 GPIOC_0 PWM_A REG2[0]H19 GPIOC_3 TCON_1_A REG0[13] H18 GPIOC_4 TCON_2_A REG0[14] T4 GPIOC_7 TCON_5_A REG0[17] R5 GPIOC_8 SPDIF_in REG3[23] TCON_6_A REG0[18] T5 GPIOC_9 SPDIF_out REG3[24]TCON_7_A REG0[19]U5 GPIOC_10HDMI_HPD(5V) REG1[22] U4 GPIOC_11 HDMI_SDA(5V) REG1[23] AA1 GPIOC_12 HDMI_SCL(5V) REG1[24] AA2GPIOC_13HDMI_CEC REG1[25]Di st ri bu tet oS ky n o o n !The GPIO Bank D can be multiplexed to functions as: ● PWM: Pulse width modulation output● VGHL/LED_BL: PWM output to control panel VGHL and backlight ● LVDS TCON-B: The TCON interface for TTL LCD panel.Table 5. GPIO Bank D Pin Multiplexing TableBGA Ball Number Package Name PWM VGHL/ LED_BL Mini-LVDS TCONLCD TCON E14 GPIOD_0 PWM_C REG2[2] LCD_VGHL_PWMREG1[29] B13 GPIOD_1 PWM_D REG2[3]LED_BL_PWM REG1[28]C12 GPIOD_2 TCON_0_B REG0[22] TCON_STH1_B REG1[19] B12 GPIOD_3 TCON_1_B REG0[23] TCON_STV1_B REG1[18] C11GPIOD_4TCON_2_B REG0[24] TCON_OEH_B REG1[17] B11 GPIOD_7TCON_5_B REG0[27] TCON_CPH50_B REG1[11] TCON_CPH1 REG1[14] TCON_CPH2 REG1[13] TCON_CPH3 REG1[12] C10 GPIOD_8 TCON_6_B REG0[28] TCON_VCOM_B REG1[20]B10GPIOD_9PWM_A REG3[26]TCON_7_B REG0[29]4.4.5 GPIO Bank EThe GPIO Bank E can be multiplexed to functions as:● Digital Audio In and output: I2S digital audio input/output.Table 6. GPIO Bank E Pin Multiplexing TableBGA Ball Number Package Name Audio InAudio OutA10 GPIOE_0 I2S_IN_CH01 reg9[11]C9 GPIOE_1 I2S_IN_LR_CLK reg9[10] I2S_OUT_LR_CLKreg9[9] A9 GPIOE_2I2S_OUT_MCLKreg9[7] B9 GPIOE_3 I2S_IN_BCLK reg9[6]I2S_OUT_BCLKreg9[5] C8 GPIOE_4I2S_OUT_CH01reg9[4]D9 GPIOE_10 D8 GPIOE_11Di st ri bu tet oS ky n o o n !The GPIO Bank X can be multiplexed to functions as: ● UART: UART port A and B ● SDIO and SDXC● I2C Master and Slave interface ● ISO7816 smart card interface ● PCM interface● Clock out: The output of AML8726-MXL/MXS PLL clock to external peripheral devices.Table 7. GPIO Bank X Pin Multiplexing TableBGA Ball Number Package Name UART-A/BSDIO-A SDXC-A I2C Master I2C Slave ISO7816PCM Clock outA3 GPIOX_0 SD_D0_A REG8[5] SDXC_D0_A REG5[14] B3 GPIOX_1 SD_D1_A REG8[4] SDXC_D1_A REG5[13] A2 GPIOX_2 SD_D2_A REG8[3] SDXC_D2_A REG5[13] B2 GPIOX_3 SD_D3_A REG8[2]SDXC_D3_A REG5[13]B1 GPIOX_4 SDXC_D4_A REG5[12] PCM_OUT REG3[30] C2 GPIOX_5 SDXC_D5_A REG5[12] PCM_IN REG3[29] C1 GPIOX_6 SDXC_D6_A REG5[12] PCM_FS REG3[28] D3 GPIOX_7 SDXC_D7_A REG5[12] PCM_CLK REG3[27]D2 GPIOX_8 SD_CLK_A REG8[1] SDXC_CLK_A REG5[11] E3 GPIOX_9 SD_CMD_A REG8[0]SDXC_CMD_A REG5[10]E2 GPIOX_10E4 GPIOX_11 F4 GPIOX_12 CLK_OUT3 REG3[21]F5 GPIOX_13 UART_TX_A REG4[13]G5 GPIOX_14 UART_RX_A REG4[12] H5 GPIOX_15 UART_CTS_A REG4[11] H4 GPIOX_16 UART_RTS_A REG4[10]E1 GPIOX_23 UART_TX_B REG4[5] ISO7816_CLK REG4[15] F3 GPIOX_24 UART_RX_B REG4[4]ISO7816_DATA REG4[14]F1 GPIOX_25 I2C_SDA REG5[27] I2C_SDA REG5[25] F2 GPIOX_26 I2C_SCK REG5[26] I2C_SCK REG5[24] G3 GPIOX_27 I2C_SDA REG5[31] I2C_SDA REG5[29] G2 GPIOX_28I2C_SCK REG5[30]I2C_SCK REG5[28]Di st ri bu tet oS ky n o o n !The GPIO Bank Z can be multiplexed to functions as: ● ITU601 input: ITU601/656 video input interface● Clock out: The output of AML8726-MXL/MXS PLL clock to external peripheral devices.Table 8. GPIO Bank Z Pin Multiplexing TableBGA Ball Number Package NameITU601 In Clock OutE8GPIOZ_0FIR reg9[18] IDQ reg9[17]B8 GPIOZ_1 HS reg9[16]C7 GPIOZ_2 VS reg9[15] B7 GPIOZ_3 D0 reg9[14] C6 GPIOZ_4 D1 reg9[14] B6 GPIOZ_5 D2 reg9[14] A6 GPIOZ_6 D3 reg9[14] C5 GPIOZ_7 D4 reg9[14] A5 GPIOZ_8 D5 reg9[14] B5 GPIOZ_9 D6 reg9[14] C4 GPIOZ_10 D7 reg9[14] B4 GPIOZ_11 CLK reg9[13]C3GPIOZ_12CLK_OUT reg9[12]Di st ri bu tet oS ky n o o n !The Bank AO GPIO belongs to a special power domain, which is Always-On (AO), in AML8726-MXL/MXS. The AO power domain cannot be powered off unless disconnect AML8726-MXL/MXS from power supply.The GPIO Bank AO can be multiplexed to functions as: ● JTAG: The debug interface of chip.● Remote: The IR remote control analog signal input● UART: A dedicated UART interface in AO power domain ● UART PMIC: Dedicated UART interface for PMIC● I2C Master and Slave: The dedicated I2C Master and Slave interface in AO power domain ● CLOCK OUT: The output of AML8726-MXL/MXS PLL clock to external peripheral devices. ● WD GPIO:Table 9. GPIO Bank AO Pin Multiplexing TableBGA Ball Number Package Name JTAG RemoteUART UART PMICI2C Master I2C Slave Clock OutWD GPIOU20 GPIOAO_0 JTAG_TDO_SYS JTAG_TDO_MEDIAUART_TX_AO AO_REG[12] U22 GPIOAO_1 JTAG_TDI UART_RX_AO AO_REG[11]U21 GPIOAO_2 JTAG_TMS UART_CTS_AO AO_REG[10] UART_TX_PMIC AO_REG[26] I2C_SCK_AO AO_REG[8] I2C_CLK_SLAVE_AOAO_REG[4] T21 GPIOAO_3 JTAG_TCKUART_RTS_AO AO_REG[9]UART_RX_PMIC AO_REG[25] I2C_SDA_AO AO_REG[7] I2C_SDA_SLAVE_AOAO_REG[3] R20 GPIOAO_4 UART_TX_PMIC AO_REG[24] I2C_SCK_AO AO_REG[6] I2C_SCK_SLAVE_AOAO_REG[2] R21 GPIOAO_5 UART_RX_PMIC AO_REG[23]I2C_SDA_AO AO_REG[5]I2C_SDA_SLAVE_AOAO_REG[1]P20 GPIOAO_6 CLK_OUT2 AO_REG[22]WD_GPIO AO_REG[19]P21 GPIOAO_7REMOTE AO_REG[0]T18GPIOAO_8JTAG_TCKenable=AO_REG[14] disable=AO_REG[13]R18 GPIOAO_9 JTAG_TMS enable=AO_REG[14] disable=AO_REG[13]R19 GPIOAO_10 JTAG_TDIenable=AO_REG[14] disable=AO_REG[13]P19 GPIOAO_11 JTAG_TDO enable=AO_REG[14] disable=AO_REG[13]CLK_OUT AO_REG[21]Di st ri bu tet oS ky n o o n !The Bank BOOT is a dedicated GPIO bank to access bootable devices such as NAND Flash, eMMC and SD card. It can be multiplexed to functions as: ● SDIO-C: The SDIO port C interface ● SDXC-C: The SDXC port C interface ● NAND: The NAND flash interface ● eMMC: The eMMC flash interface ● I2C interface● SPI NOR interfaceTable 10. GPIO Bank BOOT Pin Multiplexing TableBGA Ball NumberPackage NameSDIO-C SDXC-CNAND /eMMC NAND RBI2C SPI NORN20 BOOT_0 SD_D0_C reg6[29] SDXC_D0_C reg4[30] NAND_IO_0 reg2[26] I2C_SDA reg3[31] N22 BOOT_1 SD_D1_C reg6[28] SDXC_D1_C reg4[29] NAND_IO_1 reg2[26] I2C_SCL reg3[31]N21 BOOT_2 SD_D2_C reg6[27] SDXC_D2_C reg4[29] NAND_IO_2 reg2[26] M20 BOOT_3 SD_D3_C reg6[26]SDXC_D3_C reg4[29] NAND_IO_3 reg2[26] M21 BOOT_4 SDXC_D4_C reg4[28] NAND_IO_4 reg2[26] L20 BOOT_5 SDXC_D5_C reg4[28] NAND_IO_5 reg2[26] L21 BOOT_6 SDXC_D6_C reg4[28] NAND_IO_6 reg2[26]K20 BOOT_7 SDXC_D7_C reg4[28]NAND_IO_7 reg2[26]K21 BOOT_8NAND_CE0 (bootable) reg2[25]K22 BOOT_9NAND_CE1 reg2[24]J20 BOOT_10 SD_CMD_C reg6[25] SDXC_CMD_Creg4[27] NAND_CE2 reg2[23]NAND_RB0 reg2[17]J22 BOOT_11 SD_CLK_C reg6[24]SDXC_CLK_C (bootable) reg4[26]NAND_CE3 reg2[22] NAND_RB1 reg2[16]J21 BOOT_12 NAND_ALE reg2[21] SPI_NOR_D_A enable=reg5[1] H20 BOOT_13 NAND_CLE reg2[20]SPI_NOR_Q_A enable=reg5[3] H21 BOOT_14 NAND_WEn_CLKreg2[19] SPI_NOR_C_A enable=reg5[2]G20 BOOT_15 NAND_REn_WRreg2[18]K18 BOOT_16 NAND_DQS reg2[27]J18BOOT_17SPI_NOR_CS_n_A enable=reg5[0]Di st ri bu tet oS ky n o o n !。

AML8726-MX平板电路图

5 5 5 5 5

( ( ( ( (

( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( -& 4, ( /:

0

'

(/>

8 6/( 68 8 6/( , 8 6/( 8 6/(: 8 66( 68 8 66( , 8 66(

68 , : <1 24 $( , 24 $( ( + ( + /

?

48$ :! 7!

)

) *

- 0 - * ? 2( */ )

) *

.

' ) (' ) (' ) ' ) 7!

9

(' ) ' ) 1 6 ' ) 2#( '/ - ' ) 7! *

) ))

)( (* * ' (' )

9

) ) )'

68 -? 6/ &8, 27-5 :!$ ) 6:/ -?) /, 5 /7! 7,:4 1- 4:4 7,:4 7,:4 =4 > 7,:4)=4 > 5?$5! ,@ 4! ,7! ) :!) - 4):! - 4 :! :! ,7!

0 2) 1 )7(,@ 5!B

* 0 * ! 1;5! *'

6/$($5 , (:! ' ( ' ' ) ' ) ? 0 ' (' ) ' 6/$ $, $5 $ 0 (' ) ' 8 /?, .

0 ))

* (:! 2#()/

(' ) ' ) (' ) ) ( + '

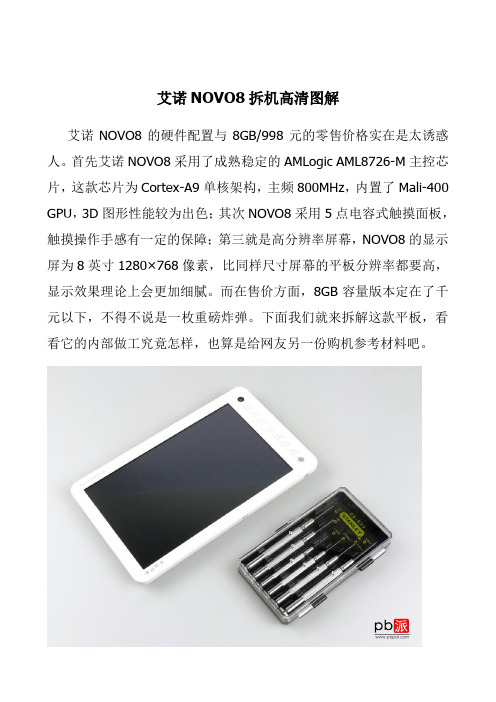

艾诺NOVO8拆机高清图解

艾诺NOVO8拆机高清图解艾诺NOVO8的硬件配置与8GB/998元的零售价格实在是太诱惑人。

首先艾诺NOVO8采用了成熟稳定的AMLogic AML8726-M主控芯片,这款芯片为Cortex-A9单核架构,主频800MHz,内置了Mali-400 GPU,3D图形性能较为出色;其次NOVO8采用5点电容式触摸面板,触摸操作手感有一定的保障;第三就是高分辨率屏幕,NOVO8的显示屏为8英寸1280×768像素,比同样尺寸屏幕的平板分辨率都要高,显示效果理论上会更加细腻。

而在售价方面,8GB容量版本定在了千元以下,不得不说是一枚重磅炸弹。

下面我们就来拆解这款平板,看看它的内部做工究竟怎样,也算是给网友另一份购机参考材料吧。

习惯了拆前先拍照留个念,因为拆后里面就有我的指纹印记了NOVO8机身背面有四颗隐藏起来的螺丝,先要将这四颗螺丝拧下才能打开外壳。

拧螺丝前先用镊子把橡胶帽取下。

橡胶帽取下后就能看到螺丝了。

依次拧掉四个边角的螺丝。

然后我们需要一根撬棒,没有撬棒会比较麻烦,因为前面板框的四周都是反向卡扣,需要稍稍按下才能弹开,有撬棒拆起来会容易很多,也不会弄伤外壳。

拆前面板框需要一定的耐心终于安全打开,我们发现NOVO8的触摸面板与屏幕紧紧粘在一起,这样也可以防止灰尘进入,我记得评测帖子的跟帖里就有网友提到这个问题,现在您可以放心了,进灰的可能性理论上不大。

这是按键和其对应的边框部分,按键背面为橡胶材质,所以寿命方面基本不用担心。

这是轨迹球背面,触点在主板上,这里只是机械转动的部分。

前面板框四周全是反向卡扣我们继续往下拆屏幕连同触摸面板一起可以被掀起来,底下就是电池和主板了。

到一定的固定作用。

依次拧下这两颗螺丝图上主板已经脱离后壳了,所以屏幕可以自然放下。

如果主板螺丝没有拧下来,屏幕是放不下去的,因为数据线会承担显示屏的重量。

如果有朋友也想拆NOVO8,此处一定要小心。

电池旁边的这个小塑料板就是NOVO8的WiFi天线了。

高性价比昂达Vi30双核版评测

高性价比昂达Vi30双核版评测第1页:昂达Vi30双核版评测泡泡网平板电脑频道7月31日在近期上市的国产平板中,昂达Vi3双核版以4:3比例的8吋屏幕,成为不少人的便携平板首选。

它及保证了理想内容的完整,同时在出行时有不会显得过于担负。

昂达Vi30双核版配有8英寸4:3显示屏,并具有5点电容触摸,运用平面钢化玻璃面板。

芯片搭载Cortex-A9双核架构的美国Amlogic8726-MX处置器,双核CPU1.5GHz主频。

采用40nm工艺处置器,单核芯片还要节能150%,配以独立PMU智能电源管理,让新品拥有290小时以上超长待机时间。

芯片内置先进的NEON技术SIMD引擎、VFP矢量浮点的协处置器,片面提升CPU的运算速度、Flash以及全高清视频的解码。

昂达(ONDA)Vi30双核版 (参数报价点评)基本参数产品类型WiFi版, 文娱平板操作系统Android 4.0中心数双核处置器晶晨AML8726-MX 1.5GHz显卡芯片Mali-400MP系统内存1GB DDR3存储容量8GB存储卡支持TF卡,最大支持32GB显示屏幕屏幕尺寸8.0英寸第2页:外观与昂达之前作风一脉相承从外观上看,Vi30双核版很像是Vi40的增加版。

正面全黑的配色,边框有点宽,虽然影响视觉感受,不过拿在手里时觉得很牢靠。

边角圆滑,全体显得大气稳重。

正面没有过多装饰,仅在下面有一个Home键。

单击可以进入桌面。

机身只要一颗30万像素的前置摄像头,用于视频聊天。

Vi30双核版反面是磨砂的雪白色金属质地,有效的阻挠了指纹的沾染。

手感很好。

ONDA 的Logo似有似无的浮如今中间,低调而美观。

上边黑色塑料部位是天线的位置,防止电磁屏蔽。

第3页:接口丰厚按键设计合理机身上的按键都设计在边角处。

虽然Android 4.0在义务栏上有虚拟按键,不过还是实体的方便一点。

机身右侧的电源键和音量键。

机身顶部的横竖屏锁定键。

底部一排借口区分为DC电源口、Micro-USB接口、HDMI接口、TF卡插槽/麦克风和耳机接口。

用于广播电视cpci监测仪的高速缓存电路

• 198•字媒体处理器代替普通处理器,就可以实现对视频技术的优化(黎盛威,论数字媒体技术在现代动画设计中的应用与探究,农家参谋,2019年第17期140页)。

3.1 数字媒体处理器视频技术优化过程中,数字媒体技术的选择非常关键。

正确的数字媒体技术选择,将会直接影响到视频技术的呈现效果,。

在视频技术中,应用数字媒体技术要将数字媒体技术与数字媒体处理器的形式引入其中,所以选择 Amlogic AML8726 开发平台作为高清数字媒体播放器是再好不过的。

通常情况下,数字媒体中心处理器选择的主频为 800 MHz,128 KB,CPU选取二级缓存,这样的选择能够为视频技术的运行性能的优化提供更大的可能性;还可以对1080P 的高清视频进行解码, MP4,AVI,WMV 等都是数字媒体比较支持的文件模式,一般情况下,在 Linux,Android 4.0 等多个操作模式中都可以运行。

另外,即便是进行高性能输出,有了数字媒体处理器也可以尽可能的减少损耗,使视频能够长时间播放。

这极大地改变了传统处理器效率低、性能差的弊端,让视频呈现出的效果更好(罗靖龙,浅析数字媒体技术对现代动画设计的影响研究,农家参谋,2019年第17期160页)。

处理器通常情况下具备较大的网络性能和接口,为了使视频技术属性能够增加,选择ARM Cortex ·A CPU 处理器,最高可达到1GHz频率,缓存速度可达128 KB,还可以利用NEON 技术对原有的 CPU 进行处理,解码Internet 应用程序范围的数字媒体,使用户的视频体验更完善。

由此可见,视频技术中,数字媒体处理器的应用是多么关键,传统视频技术若没有数字媒体技术的支持,要面临多么大的困难。

3.2 视频技术中数字媒体软件分析第一,数字媒体的治理。

UPnP AV 架构对数字媒体服务器供应数字媒体文件,在 UPnP协议基础上进行架构设计,可以实现对数字媒体视频内容的输送。

高清播放器主芯片分析

现在高清播放器,一般会有两种方案选择,第一,传统高清播放器方案。

第二,拿平板电脑方案做。

传统高清播放器方案主流芯片品牌Realtek1073 RT1185、RT1186RT1186多了安卓系统和3D都能支持WIFI SigmaDesigns SMP8635 SMP8653是8643的简化版SMP8671 Amlogic8626HMarvell88DE3010ALI3901平板电脑方案主流芯片品牌Amlogic AML8726-M3Realtek RK2918Telechips TCC9301samsung S5PV210全志A10A13安卓使用的芯片大概有三种瑞芯微RK2918、全志A10和AML8726-M3sigma SMP8643芯片作为sigma SMP8635芯片的升级产品,对BD蓝光片源的支持进行了优化,保证你可以看到原汁原味的蓝光电影效果,话说在以后固件更新后可以支持RM/RMVB格式。

还支持千兆网络,支持地面数字信号接收功能,可免费接收地面数字高清电视(如:央视高清等),兼作机顶盒之用。

(同时对互联网接入也有了很大提高,用户通过播放机的网线接口,可以很方便的随时浏览互联网的各类内容。

采用8643方案的产品一般价格在2千左右,号称高清播放机的终极产品。

还有一种sigma SMP8653是8643的简化版,价格便宜一些。

3901只能由厂家整合平台进去,这就要看厂家喜好了。

美如画整合的是VST和HDPFANS平台;瑞珀的是大众高清和HDP果子平台,其中大众高清是自己开发的平台,HDP果子平台也不清楚是否跟HDPFANS平台相同;开博尔整合的是非常高清平台。

118X芯片的机子几乎所有平台都有了,没有瑞珀的大众高清和HDP果子平台,而且还有更多的平台比如天天、好IMS等等,从资源上来说118X芯片完胜。

3901宣传的是低带宽下的流畅播放能力,所以带宽在4M或者以上者还是建议118X芯片的产品。

AML8726-MX原理图

C

<DC/DC2>

PMU

USB PWR

<LDO1> <LDO2>

VBAT

PWM Charger

<LDO2> <LDO4>

AVDD3.3/3.0V

C

<BUCK>

VCCK(1.2V)

<BUCK>

VDDIO

3.15V

<LDO>

VCC1.8V(Camera) VDDIO_CPU VDDIO_CM G/C/M Sensor HDMI_PLL_AVDD CARD_VCC LCD_3.0V (Control the card power in romboot)

TP54 TEST2

VCC5V

B

DC/DC VCCK

U4 1 2 16 VINA VIN VIN EN PG FB SS RT COMP EP AGND GND GND BS 13 C47 0.1uF C0402 VCCK_SW VCCKF FB = 0.827V L5 1.3V

C57

C32 C34 C54 22uF_6.3V 22uF_6.3V 0.1uF C0805 C0805 C0402

4.7uH_1.5A L4D18H2A VCCX

C29 C30

GND

2 4

USB_PWR GND

4.7uF_6.3V C0805 10uF_6.3V C0805 GND

电池焊接点

VBAT NC + CN20 VBAT01 2 VBAT0

DDR3_1.5V 22uF_6.3V C0805 0.1uF C0402 10uF_6.3V C0805 C17 C15

平板电脑采用的各系统芯片组性能与点评

平板电脑采用的各系统芯片组性能与点评【各系统芯片组性能与点评】一,AML8726-M方案这个是目前比较便宜的一个方案。

AML8726-M是AMLogic做的!中文名字叫晶晨半导体,是一家业界领先的半导体公司,在视频、音频和图像处理领域提供先进的产品解决方案,广泛应用于数字电视、数码相框、家庭媒体中心和机顶盒等消费电子产品中。

下面是厂商给出的简介:AML8726-M是一颗面向平板电脑和MID应用设计的芯片。

它集成了强大的CPU和GPU、2D/3D图像子系统、先进的视频解码引擎、以及所有主流外设接口,是一颗完整的多媒体片上系统芯片。

其主要特性包括:●ARM Cortex-A9 CPU, 最高频率到1GHz●高性能3D GPU●完善的2D图像处理器●全1080P高清视频解码●支持Adobe Flash Player 10.2●支持OpenGL ES 2.0●音频解码和视频管理专用媒体处理器●ITU 656/601摄像头输入端口跟I2S数字音频输入端口●所有标准音频/视频输出端口●支持DDR2和NAND/NOR 闪存结合低功耗和强大的多媒体处理性能,基于该芯片的解决方案是成本敏感的面向大众型安卓平板电脑/MID的理想选AML8726-M结构图总结:在基于65nm工艺,采用了ARMv7架构的Cortex-A9单核核心,能耗控制的不错,最高可达1GHz一般稳定在800MHZ的主频,多级流水架构,具备128KB二级缓存。

内置由ARM提供的Mali400GPU方案,支持OpenVG1.12D 图形以及OpenGL 1.1以及OpenGL 2.0 3D图形,支持6种纹理贴图,使得AML8726-M在运行速度和3D游戏的处理上的表现非常不错。

同时8726的影音视频解码硬件齐全,播放视频和音乐表现都非常优秀采用Android2.2系统方案,支持多种格式1080P视频解码,性能十分强劲。

当然它也是有缺点的!采用的65NM的工艺制程使得AML8726-M在性能上没有太大提升。

amlogic8726M MBX编译调试指南_2_3_4

AMLOGIC8726M MBX编译调试指南1、安装UBUNTU操作系统。

如安装UBUNTU虚拟机可参考:/Linux/2010-04/25829.htm2、安装编译器如果是Ubuntu Linux (32-bit x86):$ sudo apt-get install git-core gnupg sun-java6-jdk flex bison gperf libsdl-dev libesd0-dev libwxgtk2.6-dev build-essential zip curl libncurses5-dev zlib1g-dev如果是Ubuntu Linux (64-bit x86):$ sudo apt-get install git-core gnupg flex bison gperf build-essential zip curl sun-java6-jdk zlib1g-dev gcc-multilib g++-multilib libc6-dev-i386 lib32ncurses5-dev ia32-libsx11proto-core-dev libx11-dev lib32readline5-dev lib32z-dev配置JAVA编译环境(方法自己上网查询)编译器安装可参考下面网页:/wiki/index.php/Arm/Android/source/download.html3、编译ROOTFS$ cd ~/mydroid$ source build/envsetup.sh$ lunch选择12 (c03ref-user)$ make4、编译KERNEL•从下面地址下载GNU TOOLCHAIN/download/linux/ARM/gnutools/arm-2010q1-202-arm-none-linux-gnueabi-i686-pc-li nux-gnu.tar.bz2安装交叉编译器$ cd /opt$ sudo tar jxvf arm-2010q1-202-arm-none-linux-gnueabi-i686-pc-linux-gnu.tar.bz2配置交叉编译器$ cd kernel$ gedit env.sh修改路径export CROSS_COMPILE=/opt/arm-2010q1/bin/arm-none-linux-gnueabi-$ . env.sh编译uImage选择板子对应的kernel配置文件:$ make help如原理图为MBX版本选择meson_refc03_defconfig$ make meson_refc03_defconfig$ make menuconfigenable General setup->Initial RAM filesystem and RAM diskset "Initramfs source file" to root dir(../out/target/product/c03ef/root)$ make uImage$ cp ./arch/arm/boot/uImage ../out/target/product/c03ref/编译uImage_recovery选择recovery的kernel配置$ make help选择meson_refc03_recovery_defconfig$ make meson_refc03_recovery_defconfig$ make menuconfigset General setup->"Initramfs source file" to recovery root dir(../out/target/product/c03ref/recovery/root)$ make uImage$ cp ./arch/arm/boot/uImage ../out/target/product/c03ref/uImage_recovery5、编译update.zip升级包文件$ cd ~/mydroid$source build/envsetup.sh$ lunch选择12 (c03ref-user)$ make otapackage6、编译uboot选择uboot路径选择板子对应的uboot配置$ make help如果原理图对应的是MBX版本,选择:$make m1_dvbc_config$make即可得到编译的uboot文件(文件夹build目录下的u-boot-aml-ucl.bin文件)7、制作烧录SPI的SPI.BIN文件。

小米盒子主控:Amlogic8726-M3芯片解析

从11月9日雷军在微博宣告了小米盒子发布消息以来,经过数天等待,这款产品如期而来。

通过介绍我们了解到,小米盒子采用了 An droid 4.0系统,最高支持1080P高清输出,拥有HDMI接口和RT-45网线接口,能够覆盖绝大多数用户的使用需求。

除此以外,小米盒子还支持Mrico USB接口支持OTG功能,可以通过外部存储设备扩展小米盒子的存储空间。

目前小米盒子的拆机照片已经流出,它的主板整体体积并不大,中间部分是一枚主控芯片,从照片上我们可以看出,小米盒子采用的是Amlogic 8726-M3芯片,这款芯片应用并不算广泛,不过与之相近的其他两款型号“Amlogic 8726-M ”、“ Amlogic 8726-MX ”之前在平板电脑中使用较为普遍,并且赢得了不错的口碑。

小米盒子拆解:Amlogic 8726-M3芯片Amlogic中文名“晶晨半导体”,公司核心在美国,包括一些SOC设计、软件架构都在美国完成,有超过320名的工程师力量,有很强大的 AE和FAE的团队在中国,主要做一些本地支持。

目前 Amlogic主流的芯片产品有双核 AML8726-MX和单核AML8726-M小米盒子中使用到的AML8726-M3与单核AML8726-M比较接近,下面我们不妨了解一下。

Amlogic 8726-M3 芯片:Maih400 1GB DDR3-1066 SDRAM (此处为小米盒子规格) MLC Nand Flash : (2GB-32GB ) , 24bit ECCUSB Het USB OTG支持三轴重力感应 SD/MMC/TF Card I SX 可勿寺32GB支持 802A1 b/g/n支持前置/后置摄橡头 诵大支持1080P HDMI 高清输岀支持Android 4.K 垂统 Mali-400 GPU :面积4-7平万毫米〔具有畑B 二^高速緩存的^^ali-400 HP 所占用面积) 團形和通用运算标淮OpenGL ES 1.1/2. 0 <API> OpenVG 仁1二S6高速缓存8KB - 25EKB 二级書連缓祥 内存系统m 頻率240MHz (囲纳米低电圧工艺[LP ]) 3S5MHS &5纳米高电压工艺[GP ]》 三角形榆岀率阳兀/秒(冇5101工频率"F 成绩) 像素填充率 275V® (275MH15S 率下成绩)Mali-400 MP 是世界上第一个符合 OpenGL ES 2.0的多核GPU 可提供卓越的二维和三维加 速性能,最高可扩展至1080p 分辨率,同时使ARM 在能耗和带宽效率方面保持领先地位。

AML8726-M产线维修指南V0

A M L8726-M产线维修指南版本:V0.7说明:此维修指南主要针对A M L8726-M的M I D在生产中出现的问题进行相应的处理,主要基于R E F-A的版本,R E F-B也可以用作参考。

一、维修硬件需求:1、夹具:可以直接把G N D、T X、R X、V C C3.3V、N A N D_W E接出去。

2、U A R T小板,可以通过电脑看打印信息。

3、已经烧录u-b o o t的S P I小板,用顶针和P C B连接,可以用来启动机器。

二、软件需求:1、u-b o o t-512M-U a r t B.b i n和D D R I I地址线数据线的测试软件。

2、串口接收工具(可以使超级终端)。

三、其他工具:稳压电源、万用表、示波器、电脑、带u-b o o t的启动卡及升级文件等四、基本知识:M I D的程序分为3部分:u-b o o t、k e r n e l、r o o t f s,u-b o o t是启动c o d e,约300K;k e r n e l为底层的c o d e,约3M;r o o t f s为大c o d e,约65M。

其中u-b o o t分为256M的和512M 的两种,一般名称为u-b o o t-a m l.b i n和u-b o o t-512M-U a r t B.b i n,u-b o o t必须和平台内存对应(256M或512M),否则没法启动。

三部分的c o d e都是经过T F卡升级(烧录)到N N A N D F l a s h里面的,所以:第一步:把u-b o o t做到T F卡里面,做成启动卡(软件人员可以完成);第二步:把u-b o o t、k e r n e l、r o o t f s等升级文件直接拷贝到T F卡里;第三步:插卡,直接上电,M I D便可以升级。

升级主要分为如下几步:第一步:从启动卡启动u-b o o t——初始化D D R I I、N A N D等,电流会从100m A增加到200m A@5V;第二步:擦除N A N D,并从卡里面读取u-b o o t,烧到N A N D F l a s h里面,然后重启;第三步:然后把l o g o和k e r n e l烧到N A N D F l a s h里,接着跑k e r n e l;第四步:系统显示机器人界面,接着进入升级界面;第五步:升级完成以后,系统会自动重启,然后显示l o g o、机器人、a n d r o i d字样,然后进入系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。