BL8560-BPRD中文资料

全国巡回培训资料公共广播技术篇

系统+ESS解码方案,超强纠错能力

自动播放控制,全数码伺服

已升级

磁带录放卡座BL-8822S

特点: 微电脑控制,轻触式操作

全电子录、放转换电路

磁带录音,复制

双卡座放音功能,倍速自动控制

数字避雷器BL-8828A

特点: 4路独立输入、输出通道

每组通道输入电压70V—100V

自动播放控制,全数码伺服

受控于BL-8823A

已升级

数码调谐器BL-8826T

特点: 微电脑控制,轻触式操作

FM主立体声接收

可存40个电台频率记忆存储器

受控于BL-8823A

数控MP3录音播放器BL-8827A

特点: 内置数字音乐存储

2路录音话筒,1路线路录音

受控于BL-8823A

周边篇

周边培训内容:

、紧急录音报警器BL-8803T 、三十路报警矩阵BL-8804T 、十分区监听器BL-8805I 、音源信号分配器BL-8807B 、十六路电源时序器BL-8809S 、十分区器BL-8810S 、三十一段解码器BL-8811E 、数显十六路监听器BL-8812L 、数码音频矩阵分配器BL-8813A 、主备功放切换器BL-8815A 、十分区寻呼器BL-8818A

广州 南京

嘉逸酒店(五星级酒店) 长江三桥

共缆可寻址广播系列

共缆可寻址系统采用最新科技将多路调频闭路广播,外语教学,听力 考试,广播节目和数字可寻址控制信号进行共缆传输。也可以进入广播电 视闭路系统内进行混合,放大共网传输到客户所属各广播点实现真正的点 对点控制。系统采用数字闭路多频可寻址自动广播系统为主控,具有多节 目源共缆广播,背景音乐播放,日常教学广播,消防紧急广播等。

砷化镓放大模块与光传输设备优点及应用

A型光接收机设计方案 一) 型光接收机设计方案(一 型光接收机设计方案

欢迎登陆公司网 欢迎登陆公司网

1310nm光链路设计拓扑图 光链路设计拓扑图

BL8505 Datasheet(中文资料)

BL8505 Datasheet(中文资料)BL8505概述:BL8505 系列是PFM 控制的开关型DC/DC 升压稳压芯片。

0.8V 的启动电压、高达180mA 的负载驱动能力(当Vin=1.5V,Vout=3.3V)、87%的转换效率(Vin>2V,Vout=3.3V,Iout<100mA)使得BL8505 非常适合于便携式1~4 节普通电池应用的场合。

BL8505 在电路设计及生产中,特别针对开关电路固有的噪声问题进行了改良,极大的减小了对其周边电路的干扰。

BL8505 电路采用了高性能的参考电压电路结构,以及在生产中引入修正技术,保证了输出电压的高输出精度及低温度漂移。

BL8505 可提供SOT-89-3、TO-92 及SOT-23-5 等封装形式。

在SOT-23-5 等封装形式中,通过CE 使能端,可方便控制芯片的开关,使芯片的功耗达到最小。

BL8505特点:• 极强负载驱动能力:Vin=1V 时可提供3.3V、50mA 的负载电流,Vin=1.5V 时可提供3.3V、180mA 的负载电流• 0.8V 极低的启动电压(Iout=1mA 时)• 2.5V~5.0V 输出电压范围(0.1V 步进,可根据客户需求进行定制)• 输出电压精度可达±2%• 低输出电压温度漂移:±100ppm/℃• 仅需电感、电容、肖特基二极管三个外部元件• 效率高达87%• SOT89-3,TO-92,SOT-23-5 多种封装形式BL8505用途:• PDA、DSC、MP3 Player、电动玩具、无线鼠标等便携式电池供电设备• 单、双节电池供电设备的电源部分• 给LED 灯提供能源。

BL8558

BL8558

Vout(V)

2.9 2.8 2.7 2.6 2.5 2.4 2.3 2.2 2.1

2 0

200

400

600

Iload(mA)

电话:(0755)27858667 27858661 传真:(0755)27858707

Selection Guide: BL8558-XX X X

• Low output noise (47uVRMS)

voltage output, low power consumptionห้องสมุดไป่ตู้ low

• Standby Mode: 0.1uA

dropout voltage regulator.

• Low dropout Voltage: 0.46V@500mA (Typ.) • High Ripple Rejection: 66dB@100Hz (Typ.) • Low Temperature Coefficient: ±100ppm/°C • Excellent Line regulation: 0.05%/V • Build-in chip enable and discharge circuit

BL8558

Package Type:

SA:SOT-89-3

SB:SOT-89-3

RM:SOT-23-3 RN:SOT-23-5 T: TO-92

Features: P:Standard(defualt、lead free) C:Customized

限公司

Output Voltage: 12……1.2V

various kind of PCSs

• Battery Powered equipment

BL702 704 706 无线通信芯片数据手册说明书

BL702/704/706数据手册版本:2.1版权@2021Features•无线–2.4GHz射频收发器–蓝牙规范v5.0–蓝牙低功耗1Mbps和2Mbps–蓝牙®Long Range Coded500Kbps和125Kbps–Zigbee3.0,基本设备行为,Core Stack R21,绿色能源标准–IEEE802.15.4MAC/PHY–支持BLE/zigbee共存–集成balun,PA/LNA•MCU子系统–带FPU(浮点单元)的32位RISC CPU–一级缓存–1个RTC计时器,最长计数周期为1年–2个32位通用定时器–8个DMA通道–CPU频率可配置为1MHz至144MHz–JTAG开发支持–XIP QSPI Flash/pSRAM具备硬件解密功能•内存–132KB RAM–192KB ROM–1Kb eFuse–嵌入式Flash闪存(选配)–嵌入式pSRAM(BL704/BL706,选配)•安全机制–安全启动–安全调试端口–QSPI Flash即时AES解密(OTFAD)-AES-128和CTR+模式–支持AES128/192/256位加密引擎–支持MD5,SHA-1/224/256/384/512–真实随机数发生器(TRNG)–公钥加速器(PKA)•外设–USB2.0FS(全速)设备接口–红外遥控接口–1个SPI主/从机–2个UART支持ISO17987(本地互连网络)–1个I2C主机–1个I2S主/从–5个PWM通道–正交解码器–按键扫描矩阵接口–12位通用ADC–10位通用DAC–被动红外(PIR)检测–以太网RMII接口(BL704/BL706)–摄像头接口(BL706)–15(BL702)/23(BL704)/31(BL706)个GPIO(功能可配置)•电源管理模式–CPU正常运作BL702/704/706数据手册2/43@2021Bouffalo Lab–空闲模式–睡眠模式(可配置不同区域)–休眠模式–电源关闭模式–主动接收–主动发送•时钟架构–外部主时钟XTAL32MHz–外部低功耗和RTC时钟XTAL32/32.768kHz –内部RC32kHz振荡器–内部RC32MHz振荡器–内部系统PLL–内部音频PLLContents1概述 (9)2功能描述 (10)2.1CPU (11)2.2缓存 (11)2.3内存 (11)2.4DMA控制器 (11)2.5总线结构 (11)2.6中断 (13)2.7启动选项 (13)2.8电源管理单元 (13)2.9时钟架构 (13)2.10外设 (14)2.10.1GPIO (15)2.10.2UART (15)2.10.3SPI (15)2.10.4I2C (15)2.10.5I2S (15)2.10.6TIMER (15)2.10.7PWM (16)2.10.8IR(IR-remote) (16)2.10.9USB2.0(Full Speed) (16)2.10.10EMAC (16)2.10.11QDEC (16)2.10.12ADC (16)2.10.13DAC (17)2.10.14调试接口 (17)BL702/704/706数据手册3管脚定义 (18)4电气特性 (26)4.1绝对最大额定值 (26)4.2运行条件 (26)4.2.1电源特性 (27)4.2.2温度特性 (27)4.2.3通用工作条件 (27)4.2.4GPADC特性 (27)5产品使用 (30)5.1湿敏等级(MSL) (30)5.2静电放电(ESD) (31)5.3回流焊接曲线(Reflow Profile) (31)6参考设计 (33)7封装信息QFN32 (34)8封装信息QFN40 (36)9封装信息QFN48 (38)10标志定义 (40)11订购信息 (41)12版本信息 (43)List of Figures1.1功能框图 (9)2.1系统框图 (10)2.2时钟框图 (14)3.1BL702管脚布局 (18)3.2BL704管脚布局 (19)3.3BL706管脚布局 (20)5.1Classification Profile(Not to scale) (31)6.1参考设计 (33)7.1QFN32封装图 (34)8.1QFN40封装图 (36)9.1QFN48封装图 (38)10.1标志定义 (40)11.1型号命名 (41)List of Tables2.1总线连接 (11)2.2地址映像 (12)2.2地址映像 (13)3.1管脚定义 (20)3.1管脚定义 (21)3.1管脚定义 (22)3.2GPIO Muxed Pins (23)3.2GPIO Muxed Pins (24)3.3UART信号映射表(Default) (25)3.4UART信号映射表(Example) (25)4.1电源的绝对最大额定值 (26)4.2建议电源值范围 (27)4.3建议温度值范围 (27)4.4一般操作条件 (27)4.5GPADC特性 (28)4.6ADC electrical characteristic (29)5.1Reference Conditions for Drying Mounted or Unmounted SMD Packages(User Bake:Floor life be-gins counting at time=0after bake) (30)5.2Classification Reflow Profiles (32)7.1尺寸说明(测量单位:毫米) (34)7.1尺寸说明(测量单位:毫米) (35)8.1尺寸说明(测量单位:毫米) (36)8.1尺寸说明(测量单位:毫米) (37)9.1尺寸说明(测量单位:毫米) (38)9.1尺寸说明(测量单位:毫米) (39)11.1订购选项 (42)12.1修改记录 (43)1概述BL702/BL704/BL706是用于物联网应用的高度集成的BLE和zigbee组合芯片组。

T85BCCDBB中文资料

5x7 mm TCVCXO T85B Series Description:The T85B Temperature Compensated Voltage Controllable Crystal Oscillator (TCVCXO) Series products provide Stratum III level frequency stability with voltage controlled frequency adjust in a miniature 5 x 7 mm ceramic SMD package.Features: •Available in frequencies from 5 to26 MHz with 10 MHz, 12.8 MHz,25 MHz, and other frequencies asstandards•+/-4.6 ppm overall frequency stability including 20 years aging •+/-5 ppm frequency pull range •CMOS and Clipped Sine Wave available•Standard 5 x 7 mm ceramic SMD package•RoHS-6 / Lead-free compliant •Tri-state controlFrequency Range, Operating Temperature, and Frequency Stability:Frequency RangeOperatingTemperatureProductCodeFrequencyStabilityStability(Overall)*ProductCode -20 to +70° C C +/- 0.28 ppm +/- 4.6 ppm A-40 to +85° C D +/- 0.50 ppm +/- 4.6 ppm B+/- 1.00 ppm -+/-4.6 ppm C5 to 26 MHz•Add +/- 1ppm setting calibration @ +25° C ; +/- 0.6 ppm for supply and load variation ; +/- 2.0 ppm for aging•To achieve +/- 4.6 ppm overall stability or better•For Frequency stabilities >= +/- 0.5 ppm with a clipped sinewave output the TV85B product should be selected•+/- 0.28 ppm is not available from –40 to 85° CAging: (typical at 10MHz after 30 days continuous operation)Frequency Timeframe Aging Product Code10 MHz 20 Years +/- 2.5 ppm N/APhase Noise:Frequency Offset Phase Noise (Typ.) Product Code1 Hz - 60 dBc/Hz10 Hz - 90 dBc/Hz100 Hz -120 dBc/Hz1 KHz -140 dBc/Hz10 KHz -155 dBc/Hz10.0 MHz100 KHz -155 dBc/HzN/A2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 1 of 4 Rev 1.2Supply Voltage (Vs):Power Supply (Vs) +3.3 Vdc +/-10%+5.0 Vdc +/-10%Product CodeCDCurrent Consumption:CMOS Clipped Sine WaveSupply Current 6 mA 3.5 mAEnvironmental:Storage Temperature-55 to +125° COutput Waveform:CMOS Clipped Sine WaveHCMOS Output Levels (15pf load) "0" < 0.1(Vs); "1" > 0.9(Vs) Output Level 0.8 V p-p min.Rise / Fall Time <10ns (10% to 90%) Duty Cycle 45 to 55% @ 50% Logic 1 Product Code A BPulling Range:Tuning Range None (TCXO)+/- 5 ppmProduct CodeAB*Note: Only +/- 5 ppm minimum pull is available as a TCVCXOOrdering Options:Operating Temperature Frequency Stability Supply VoltageOutput WaveformPulling RangeOperating Frequency C A C A AD B D B B Cxx.xxxxMHz 2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571T85B C A C A B 10.0000MHzProduct Selection Code (refer to the above example):This part is RoHs compliant; -20 to +70° C, +/- 0.28 ppm, 3.3 volt CMOS output with +/- 5 ppm pull, 10MHz operating frequency** Not all combinations are available in this product.Outline Drawing & Pin Out:Page 2 of 4 Rev 1.22545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 3 of 4 Rev 1.2How to Order This Product:Contact Bliley Technologies with Product Selection Code from Ordering Options Section above.Attn:Sales @ BlileyFax: 814-833-2712Phone: 814-838-3571Email: info@Web: Date: ____________From:Name: ____________________ Company: ___________________Fax: ______________________ Phone: _____________________Email: _________________________________________________Quantities to Quote: ______________ Target Price: $___________Application / Reference #: _________________________________2545 West Grandview Blvd Erie, PA. 16506 Tel (814) 838-3571 Page 4 of 4 Rev 1.2。

BL8560-VPRD中文资料

7) Load transient response

-8Total 10 Pages

8/8/2006

元器件交易网

BL8560

Package Information:

3) Dropout Voltage vs. Output Current

4) Supply Current vs. Input Voltage

-7Total 10 Pages

8/8/2006

元器件交易网

BL8560

5) Ripple rejection vs. Frequency 6) Line transient response

-4Total 10 Pages

8/8/2006

元器件交易网

BL8560

Electrical Characteristics

BL8560, for arbitrary output voltage

Symbol

Parameter

Conditions

Min

Typ

Max

Units

-1Total 10 Pages

8/8/2006

元器件交易网

BL8560

Selection Guide BL8560 X X XX Pin Assignment

Pin Description

Pin Number

SOT-23-6C SOT-23-6D

SOT-23-6D

BL8560-WPRD

8/8/2006

元器件交易网

BL8560

Product Marking information:

SOT-23-6C SOT-23-6D

BL8550

Ver1.0

2/6

BL8550

推荐工作条件:

名称 输入电压范围 环境温度

最小 -50

推荐

主要参数和工作特性:

参数

Vout

∆Vout

∆Vout

Dropout Voltage Current Limit Quiescent Current Temperature Stability

参数说明

输出电压

电压线性度 (note1) 负载线性度 (note1,2) 输入输出电压 差(note3) 最大负载电流 静态电流

BL8550 可提供 SOT-89-3 多种脚位封装形 式,根据客户需求也可以提供无铅化的封 装。

BL8550

400mA 低压差线性稳压器

特点:

• 可提供多种固定电压输出版本(固定电压

包括 1.8V,2.5V,2.85V,3.3V,5V 等,其 他电压规格可根据用户需求定制)

• 输出电流为 400mA • 输出电压精度高达±1% • 电压线性度为 0.2% • 负载线性度为 0.4% • 环境温度:TA 的范围是-50℃~140℃

SOT-89-3 -------------------------------------------------------------------------------------------0.5W 贮存温度 Ts --------------------------------------------------------------------------------------------65~150°C 焊接温度和时间 --------------------------------------------------------------------------------------300°C,10S

TDA8560中文资料

1996 Jan 08

2

元器件交易网

Philips Semiconductors Product specification

2 × 40 W/2 Ω stereo BTL car radio power amplifier with diagnostic facility

BLOCK DIAGRAM

V P1 3 input 1 1 mute switch Cm VP2 10

TDA8560Q

TDA8560Q

VA 365 Ω 18 kΩ power stage mute switch 4 output 1A

Cm

PROTECTIONS Load dump Soar Thermal Short - circuit Reverse polarity

Байду номын сангаас

元器件交易网

Philips Semiconductors Product specification

2 × 40 W/2 Ω stereo BTL car radio power amplifier with diagnostic facility

SHORT-CIRCUIT PROTECTION When a short-circuit occurs at one or more outputs to ground or to the supply voltage, the output stages are switched off until the short-circuit is removed and the device is switched on again, with a delay of approximately 20 ms, after removal of the short-circuit. During this short-circuit condition, pin 12 is continuously low. When a short-circuit across the load of one or both channels occurs the output stages are switched off during approximately 20 ms. After that time it is checked during approximately 50 µs to see whether the short-circuit is still present. Due to this duty cycle of 50 µs/20 ms the average current consumption during this short-circuit condition is very low (approximately 40 mA).

BC856BW中文资料

PNP Silicon AF Transistors

BC 856W ... BC 860W

Features

q For AF input stages and driver applications q High current gain q Low collector-emitter saturation voltage q Low noise between 30 Hz and 15 kHz q Complementary types: BC 847W, BC 848W,

mV 75 300 250 650

Base-emitter saturation voltage1) IC = 10 mA, IB = 0.5 mA IC = 100 mA, IB = 5 mA

VBEsat – –

700 – 850 –

Base-emitter voltage IC = 2 mA, VCE = 5 V IC = 10 mA, VCE = 5 V

IC

Collector peak current

ICM

Total power dissipation, TS = 115 ˚C Ptot

Junction temperature

Tj

Storage temperature range

Tstg

Thermal Resistance Junction - ambient1) Junction - soldering point

3

–

10 –

2.7 – 4.5 – 8.7 –

1.5 – 2.0 – 3.0 –

200 – 330 – 600 –

18 – 30 – 60 –

BL8530

第三,一般来说,不考虑效率问题,小电感可以带动的负载能力强于大电感。但是由于在相同

负载条件下,大电感的电流纹波和最大的电流值小,所以大电感可以使得电路在更低的输入电压下

参考电压电路提供稳定的参考电平。并且由于采用内部的修正技术,保证了输出电压精度达到 ±2%,同时由于参考电压经过精心的温度补偿设计考虑,使得芯片的输出电压的温度漂移系数小于 100ppm/℃。

高增益的误差放大器保证了在不同输入电压和不同负载电流情况下稳定的输出电压。为了减小 输出电压的纹波和噪声,误差放大器采用司密特比较器结构,同时具备很快的响应速度。

Rswon ILXleak VCEH VCEL Fosc Maxdty

BL8506

典型应用:

• • • • •

逻辑电路复位 电池电压检测 电压窗口比较 后备电源管理 电源故障电路监测

选型指南: BL8506-XX X XX

引脚排列图:

封装形式: RM: SOT-23-3 RN: SOT-23-5 SM: SOT-89-3 SC: SC-82AB T: TO-92 输出方式: A:N 沟道开路漏级输出 C:CMOS 输出

Vin从高 到低

4.0 输出电压 (V) 4.4 4.6 4.8 3.0 2.0 1.0 0.0

Vin从低 到高

Vin从低 到高

4.2

4.4

4.6

4.8

4.0

4.2

4.0

4.2

4.4

4.6

4.8

输入电压 (V)

输入电压 (V)

输入电压 (V)

Ver1.0

7/9

BL8506

输入电压 (V)

输入电压 (V)

输入电压 (V)

检测电压 4.4V ( -40C)

检测电压 4.4V ( 25C)

检测电压 4.4V ( 70C)

Vin从高 到低 Vin从低 到高

4.0 输出电压 (V) 3.0 2.0 1.0 0.0 4.0

Vin从高 到低

4.0 输出电压 (V) 3.0 2.0 1.0 0.0

2) 不同温度下功耗电流(功耗电流随输入电压的变化)

检测电压 0.9V 1.E-05 1.E-05

检测电压 2.7V

功耗电流 (A)

-40ºC 1.E-07 25ºC 70ºC 1.E-08 0 1 2 3 输入电压 (V) 4 5 6

功耗电流 (A)

1.E-06

1.E-06

BL8505应用电路

BL8505应用电路BL8505应用电路BL8505是BOOST 结构、电压型PFM 控制模式的DC-DC 转换电路。

外部只需要一个电感、一个输出电容、和一个肖特基二极管就可以提供2.5V~5.0V 的稳定的低噪声输出电压。

芯片内部包括输出电压反馈和修正网络、启动电路、震荡电路、参考电压电路、PFM 控制电路、过流保护电路以及功率管。

PFM 控制电路是BL8505 的核心,该模块根据其他模块传递的输入电压信号、负载信号和电流信号来控制功率管的开关,从而达到控制电路恒压输出的作用。

在PFM 控制系统中,固定震荡频率和脉宽,稳定的输出电压是根据输入-输出电压比例以及负载情况通过消脉冲来调节在单位时间内功率管导通时间来实现。

震荡电路提供基准震荡频率和固定的脉宽。

参考电压电路提供稳定的参考电平,由于采用内部的修正技术,保证输出电压精度达到±2%,同时由于参考电压经过精心的温度补偿设计考虑,使得芯片的输出电压的温度漂移系数小于100ppm/℃。

高增益的误差放大器保证了在不同输入电压和不同负载电流情况下稳定的输出电压。

为了减小输出电压的纹波和噪声,误差放大器采用司密特比较器结构,并且有很快的响应速度。

BOOST 结构DC-DC 转换器的功耗损失主要是由于电感的寄生串联电阻、肖特基二极管的正向导通压降、功率管的导通电阻以及控制功率管信号的驱动能力这四个方面;当然芯片本身消耗的静态功耗在低负载的情况下也会影响转换效率。

所以为了获得教高的转换效率,除了用户选择合适的电感、肖特基二极管和电容外,芯片本身包含导通电阻很小的功率管,功率管有驱动能力很强的驱动电路驱动,保证功率管开关沿口很陡,大大减小了开关的功率损耗。

LM8562中文资料

元器件交易网

LM8562

Allowable Operating Conditions at Ta = –20 to +70°C, VSS = 0 V

Parameter Supply voltage Standby voltage Input high-level voltage Input low-level voltage Input high-level voltage Input low-level voltage Input high-level voltage Input mid-level voltage Input low-level voltage Input high-level voltage Input low-level voltage Input level hold time Input chattering time

Package Dimensions

unit : mm

3029A-DIP28S

[LM8562]

Features

(1) Duplex LED display (LM8560-use LED panel usable) (2) Two alarms on chip (600 Hz, 1200 Hz) (3) Up, down/fast, slow time setting available (easy setting) (4) 12/24-hour mode, 50/60 Hz selectable (provided that it is

VDD = –9 V ± 10% VDD = –9 V R = 180 kΩ, C = 3300 pF

min 32

16

2

DC –10

SC8560中文资料

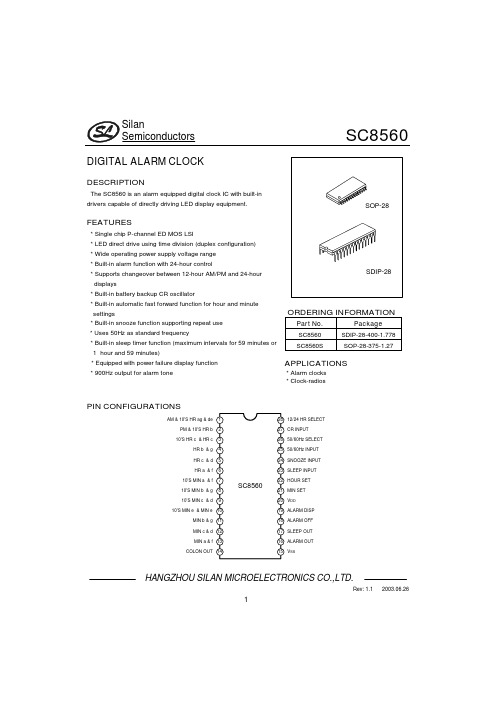

HANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.261DIGITAL ALARM CLOCKDESCRIPTIONThe SC8560 is an alarm equipped digital clock IC with built-in drivers capable of directly driving LED display equipment.FEATURES* Single chip P-channel ED MOS LSI* LED direct drive using time division (duplex configuration) * Wide operating power supply voltage range * Built-in alarm function with 24-hour control* Supports changeover between 12-hour AM/PM and 24-hour displays* Built-in battery backup CR oscillator* Built-in automatic fast forward function for hour and minute settings* Built-in snooze function supporting repeat use * Uses 50Hz as standard frequency* Built-in sleep timer function (maximum intervals for 59 minutes or 1 hour and 59 minutes)* Equipped with power failure display function* 900Hz output for alarm toneORDERING INFORMATIONPart No.PackageSC8560 SDIP-28-400-1.778SC8560S SOP-28-375-1.27APPLICATIONS* Alarm clocks * Clock-radiosPIN CONFIGURATIONSAM & 10'S HR ag & de10'S HR c & HR cPM & 10'S HR b HR b & g HR c & d HR a & f 10'S MIN a & f 10'S MIN b & g 10'S MIN c & d10'S MIN e & MIN e MIN b & g MIN c & d MIN a & f COLON OUT 12/24 HR SELECT CR INPUT 50/60Hz SELECT 50/60Hz INPUT SNOOZE INPUT SLEEP INPUTHOUR SET MIN SET V DDALARM DISP ALARM OFF SLEEP OUT ALARM OUT V SSHANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.262BLOCK DIAGRAM50/60H z 12/24H R C R I n p u t50/60H z I n p u tM i n u t e S e tH o u r S e tA l a r m D i s p l a yS l e e p D i s p l a yS n o o z e I n p u tO F F O u t p u t O u t p u tO u t p u t A M & 10'S H R a g & d eP M & 10'S H R b0'S H R c & H R cH R b &gH R c &dH R a &f0'S M I N a &f10'S M I N b &g10'S M I N c &d10'S M I N e & M i n ei n b &gM i n c &di n a &fHANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.263ABSOLUTE MAXIMUM RATINGS (Ta =25°C, Vss =0V)CharacteristicSymbolConditionValueUnitMaximum Supply Voltage V DD max.-15.0 ~ + 0.3 V Input Voltage 1V IN(1) 50/60Hz input -15.0 ~ + 0.3 V Input Voltage 2 (except pin 26) V IN(2) Except 50/60Hz input -15.0 ~ + 0.3 V Output VoltageV OUT-15.0 ~ + 0.3 V Input Clamp current( pin 26) I IN 50/60Hz input -0.4 ~ +0.4 mA Allowable Power Dissipation P D Ta=70°C 700 mWOperating Temperature Topr -30 ~ +70 °C Storage TemperatureTstg-55+125°CELECTRICAL CHARACTERISTICS (Tamb=25°C, V DD =-12.0V, V SS =0V,Unless otherwise specified)ParameterSymbolTest conditions MinTypMaxUnitSupply Voltage V DD-14.0 -7.5 VInput “H” level Voltage V IH(1) 50/60Hz Input -1.0 V Input “L” level Voltage V IL(1) 50/60Hz Input V DD +2V Input “H” level Voltage V IH(2) Except 50/60Hz input -1.5 V Input “L” level VoltageV IL(2) Except 50/60Hz inputV DD +2V50/60 Hz input pin input voltage V AC-INV LEDVInput “H” level current(1) I IH1 50/60Hz Input, V IN =V SS 10 μA Input “L” level current(1) I IL1 50/60Hz Input, V IN =V DD 10 μA Input “H” level current(2) I IH2Input pins other than 50/60Hz Input,V IN =V SS20μA Input “L” level current(2) I IL2Input pins other than 50/60Hz Input,V IN =V DD10 μA Output “H” level current(1) I OH1Alarm output and sleep output, V OH =V SS -1V5 mA Output leakage current(1) I OF1Alarm output and sleep output, V OUT =V DD10 μA Output “H” level current(2) I OH2AM& 10’S HR ag&de (24H mode),V OUT =V DD -1V 36 mA Output leakage current(2) I OF2AM& 10’S HR ag&de (24H mode),V OUT =V DD20 μA Output “H” level current(3)I OH3Segment Output other than those listed above , V OUT =Vss-1V18 mA (To be continued)HANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.264(Continued)ParameterSymbolTest conditionsMin Typ Max UnitOutput leakage current(3) I OF3Segment Output other than those listed above, V OUT =V DD20μA Power failure detection voltage V DF -7.5 -5.0VConsumption currentI CC Output set to off and pull-down attached input set to open 5 7 mABackup oscillator stability factor fs Standard value,900Hz, V DD = -9V 10%-10 10 % Backup oscillator accuracyfaStandard value,900Hz, V DD = -9V-10 10 % DESCRIPTION OF OPERATIONSTerminal DescriptionOperating Description50/60 Hz Input:Built-in Shumidt circuit enable noise elimination at 50/60Hz commercial frequencies with use of a simple CR filter. Built-in pull-up resistor.CR Input When the AC power supply is interrupted, the time counter switches to a holding state and a built-in oscillator promptly begins operation. If 50/60Hz input continuous for 3 clocks without arriving, this oscillator’s output is activated and functions as the time counter clock in place of 50/60Hz input. The frequency levelof this clock oscillator is determined according to the CK Value. While the above mentioned oscillator is operating using backup mode, all segment output is switched to OFF. (Note) When the backup oscillator is in use due to an AC power supply interruption, the 50/60Hz input pin must be maintained open or at a Vss level.50/60Hz Selective Input When 50/60 selective input is connected to Vss,50Hz use is enable. When 50/60selective input is left open, V DD is activated using an internal pull-down resistor and the setting is switched to enable use at 60Hz.Display Mode Selective Input (Alarm Select/Sleep Select )Since the pull-down resistor is built-in, selection from four display modes is possible using two SPST switches (single-pole and single-throw switches). Table l shows these display mode selections.Time Setting InputThere are two setting inputs for use with “hour” and “minute”. Time content settings shown in Table 2 are possible by activating Vss to these pins. A pull-down resister is built-in.12/24H Select Input Leaving this pin unconnected (V DD ) causes the 12-hour basis to be selected,connecting this pin to V SS cause the 24-hour basis to be selected .An internal pull-down resistor is provided.(To be continued)HANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.265(Continued)Terminal DescriptionOperating DescriptionPower Failure Detection display If the power supply voltage drops and is applied again, all the on-segments flashand the power failure indication mode is entered. The power failure indicationmode is released by applying V SS to “hour set” or “ minutes set”.Alarm Operation and Alarm OutputThe alarm signal outputs when alarm content marches the time .When not resetby either snooze input or alarm off input, output continues after l hour and 59 minutes. This output signal consists of 900 Hz 2 Hz intermittent (50% duty) modulation signals. When the need arises, a filter can be applied to alter the alarm signal to a DC signal.Snooze InputWhen the alarm is sounding and instantly activating Vss to this pin, alarm output is set to OFF for a period between 8 and 9 minutes after which time the alarm signalis once again output .The snooze function can be used repeatedly in l hour and 59 minutes intervals. A pull-down resist is built-in. Activating Vss to the snooze pin when the alarm is OFF resets the sleep timer counter to [0:00].(This is known as the one-touch sleep timer reset function.)Alarm Off InputActivating this input pin to Vss instantly sets alarm output to OFF. A pull-down resistor is built-in.Sleep Timer and Sleep Output:Sleep output can turn on the radio and can be set for time intervals of 59 minutes or l hour and 59 minutes. Refer to Table 2 for the proper selection procedure (59minutes or l hour and 59 minute selection). This sleep timer is constructed using a down counter and when the counter content arrives at [00], output is set to off and the radio turns off .Adding Vss to snooze input turns sleep output off, when sleep output is on.TABLE 1:DISPLAY MODESSelective Input AlarmSleepDisplay Mode Digit No.1Digit No.2Digit No.3Digit No.4NC NC Time display 10’s place for hour ,AM/PM Hour 10’s place for minute Minute VssNC Alarm display10’s place for hour ,AM/PMHour10’s place for minuteMinute NC Vss Sleep display Clear Hour10’s place forminute Minute VssVss Second displayClearMinute10’s place for secondSecondNote: Activating Vss using two inputs simultaneously (alarm select and sleep select), the display mode is switchedto display seconds.HANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.266TABLE 2:SETTING CONTENTSDisplay ModeSet lnputFunctionsHOURlmmediately adds 1 to hour digits and then assigns an additional 1. at a speed of 2 Hz , after each 1/4 to 3/4 second .MIN lmmediately adds 1 to minute digits and then assigns an additional 1. at a speed of 2 Hz, after each 1/4 to 3/4 second . Seconds are reset.TimeBOTH Operates both as outline above. HOUR(Note)Second digits are cleared to [00].MIN Time holds. Second (Alarm &Sleep)BOTH Resets hour and minute digits as [0:00] when operating in 24-Hmode or [12:00] when operating in 12-H mode.HOURlmmediately adds 1to hour digits and then assigns an additional 1, at a speed of 2 Hz, after each 1/4to 3/4 second.MIN lmmediately adds 1 to minute digits and then assigns an additional 1, at a speed of 2 Hz, after each 1/4to 3/4 second.Alarm BOTH Resets hour and minute digits to [0:00] when operating in 24-hour mode or [12:00] when operating in, 12-hour mode.-Sets sleep counter to [0:59] instantly when V DD is activated to sleep select. HOUR Sets sleep counter to [1:59] instantly when V DD is activated to sleep select and hour at the same time.MIN Sleep counter looses 1 at a speed of 2 Hz SleepBOTHSleep counter looses 1 at a speed of 2 HzOnce conditions have been switched to reset or hold, input of other functions is locked until HOUR and MIN input have separated. Note:When the digital reading for seconds is between 30 and 59 seconds, 1 is added to digits for minutes as the digital reading for seconds resets to [00]HANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.267CLOCK-RADIO APPLICATION CIRCUIT (Positive Power Supply)12T h i s c i r c u i t i s u s e d a s n o i s e i n t e r f e r e n c e s t r i p p e r f o r t h e L W b a n d .( B a c k u p c o n t r o l i s e n a b l e d e x c e p t f o r b a t t e r y b a c k u p m o d eC y c l e 212 H o u r D i s p l a y a n d 60H z C i r c u i t D i a g r a mHANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.268CLOCK APPLICATION CIRCUIT (Negative Power Supply)12u t p u t i s n o t u s e d , C R i n p u t i s c o n n e c t e d t o V s s .C y c l e 212 H o u r s D i s p l a y a n d 60H z C i r c u i t d i a g r a mSOP-28-375-1.27 UNIT:mmHANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.269HANGZHOU SILAN MICROELECTRONICS CO.,LTD.Rev: 1.1 2003.06.2610Attachment Revision HistoryDataREVDescription Page2000.12.31 1.0 Original2003.06.26 1.1 Add ”SOP-28-375-1.27”Add” ORDERING INFORMATION”DEL”FUNCTIONS”1, 9 11。

BL8565型号的正电压输出、低噪声、低功耗、低掉电电压线性调节电源说明书

500mA High PSRR, Low Dropout Voltage Linear RegulatorREV1.0-Revised DEC 2007BL8565DESCRIPTIONBL8565 series is a group of positive voltage output, low noise,low power consumption, low dropout voltage regulator.BL8565 can provide output value in the range of 1.5V~4.5V every 0.1V step. It also can be customized on command.BL8565 includes high accuracy voltage reference, error amplifier, current limit circuit and output driver module with discharge capability.BL8565 has excellent load and line transient response and good temperature characteristics, which can assure the stability of chip and power system. And it uses trimming technique to guarantee output voltage accuracy within ±2%.BL8565 is available in SOT-89-3 packages which is lead free.FEATURES• Low Power Consumption: 20uA (Typ.) • Low output noise (47uVRMS)• Low dropout Voltage: 0.16V@300mA(Typ.)• High Ripple Rejection: 73dB@100Hz(Typ.)• Low Temperature Coefficient: ±100ppm/°C• Excellent Line regulation: 0.05%/V• Build-in chip enable and discharge circuit • Output Voltage Range: 1.5V~4.5V(customized on command every 0.1V step)• Highly Accurate: ±2% • Output Current LimitAPPLICATIONS• Power Management for Computer,MotherBoard, Graphic Card• LCD Monitor and LCD TV • DVD Decode Board• Reference Voltage Source• Regulation after Switching PowerTYPICAL APPLICATIONNOTE: Input capacitor (Cin=1uF) and Output capacitor (Cout=3.3uF/4.7uF) arerecommended in all application circuit.ELECTRICAL CHARACTERISTICSBL8565BL8565 □1□2□3□4□5CodeDescription□1 Temperature&Rohs:C:-40~85°C ,Pb Free Rohs Std. □2 Package type: C3A:SOT-89-3(A) C3B:SOT-89-3(B) C3C:SOT-89-3(C) □3 Packing type:TR:Tape&Reel (Standard) □4 Output voltage: e.g. 15=1.5V 18=1.8V 45=4.5V □5 Voltage accuracy: Blank(default)=±2%MARKING DESCRIPTONAD : Product Code XX: Output Voltage Vout Code Vout Code Vout Code 2.5V 25 3.8V 38 2.6V 26 3.9V 39 2.7V 27 4.0V 40 1.5V 15 2.8V 28 4.1V 41 1.6V 16 2.9V 29 4.2V 42 1.7V 17 3.0V 30 4.3V 43 1.8V 18 3.1V 31 4.4V 44 1.9V 19 3.2V 32 4.5V 45 2.0V 20 3.3V 33 2.1V 21 3.4V 34 2.2V 22 3.5V 35 2.3V 23 3.6V 36 2.4V 24 3.7V 37YY:LOT NO.Z: The Year of manufacturing,”7” stands for year 2007,”8” stands for year 2008,and “0” stands for year 2010.Z: The week of manufacturing. ”A” stands for week 1,”Z” stands for week 26,”A ” stands for week 27,” Z ” stands for week 52.Product Classification BL8565CC3ATR □□□MarkingADXXA YYBZZ AD:Product CodeXX: Output VoltageA:Package YY:Lot No.B:FabCode ZZ:Data CodeProduct Classification BL8565CC3BTR □□□MarkingADXXBYYBZZ AD:Product Code XX: Output VoltageB:PackageYY:Lot No. B:FabCodeZZ:Data CodeProduct Classification BL8565CC3CTR □□□MarkingADXXC YYBZZ AD:Product CodeXX: Output VoltageC:Package YY:Lot No.B:FabCodeZZ:Data CodeVss Ground PinVin Supply Voltage Input VoutOutput VoltageABSOLUTE MAXIMUM RATINGParameter ValueMax Input Voltage 8VOperating Junction Temperature(Tj) 125°COutput Current 500mAAmbient Temperature(Ta) -40°C –85°CPowerSOT-89-3 500mWDissipationStorage Temperature(Ts) -40°C -150°CLead Temperature & Time 260°C,10SNote:Exceed these limits to damage to the device.Exposure to absolute maximum rating conditions may affect device reliability.RECOMMENDED WORK CONDITIONSItem Min Recommended Max. Unit Input Voltage Range 6 V Ambient Temperature -40 85 °CELECTRICAL CHARACTERISTICS(Test Conditions: Cin=1uF,Cout=3.3uF,TA=25°C, unless otherwise specified. )NOTE:Vdrop=Vin1-(Vout2*0.98) Vout2 is the output voltage when Vin=Vout1+1.0V and Iout=500mA.Vin1 is the input voltage at which the output voltage becomes 98% of Vout1 after gradually decreasing the input voltage. BLOCK DIAGRAMExplanationBL8565 series is a group of positive voltage output, low noise, low power consumption, low dropout voltage regulator.BL8565 can provide output value in the range of 1.5V~4.5V every 0.1V step. It also can be customized on command.BL8565 includes high accuracy voltage reference, error amplifier, current limit circuit and output driver module.BL8565 has excellent load and line transient response and good temperature characteristics, which can assure the stability of chip and power system. And it uses trimming technique to guarantee output voltage accuracy within±2%.2) Output Voltage vs. Input Voltage 1) Output Voltage vs. Output Current (with outputshort protection)3) Dropout Voltage vs. Output Current 4) Ripple rejection vs. FrequencyCin=Cout=1uF Iout=25mA vout=3.3V6) Load transient responseCin=Cout=1uF Vin=4.5v Vout=3.3V4v5vvinvoutvinvout 4v5v1mA Output Current Output Voltage1mA50mA50mAOutput CurrentOutput VoltagePACKAGE LINEPackage SOT-89-3 Devices per reel 1000Pcs Unit mm Package dimension:。

bl8530 原理

bl8530 原理

BL8530是一个DC-DC升压稳压芯片,其原理基于PFM控制的开关型电路。

它的工作过程可以简单描述为:当BL8530的LX端内部的N沟道MOS场效应管为低电平时,电池对电感L充电蓄能;当LX端为高电平时,电池电

压与电感L两端产生的感生电压(此电压为电池电压的数倍)叠加后通过肖特基二极管给电容C2充电,这样在C2两端获得的便是升高的电压。

此外,BL8530具有的启动电压、高达200mA的负载驱动能力(当Vin=,ut=时),以及极低的静态功耗(Iq<),非常适合于便携式1~4节普通电池应用的场合。

在电路设计及生产中,BL8530针对开关电路固有的噪声问

题进行了改良,极大的减小了对其周边电路的干扰。

以上信息仅供参考,如需了解更多信息,建议查阅BL8530芯片的规格书或咨询相关技术人员。

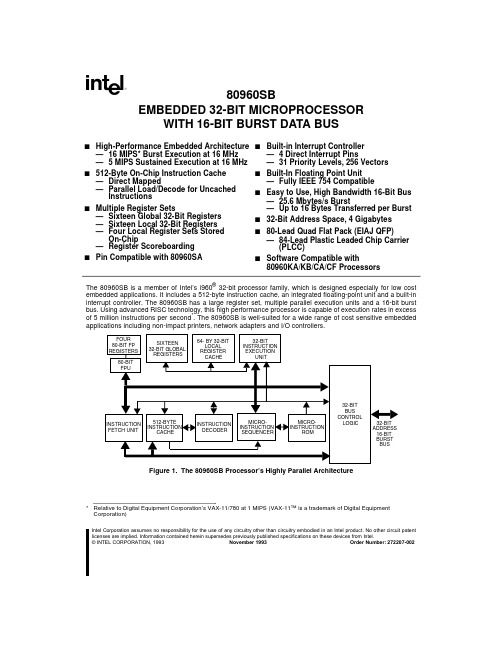

80960SB资料

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel.© INTEL CORPORATION, 1993November 1993Order Number: 272207-00280960SBEMBEDDED 32-BIT MICROPROCESSORWITH 16-BIT BURST DATA BUSThe 80960SB is a member of Intel’s i960® 32-bit processor family, which is designed especially for low cost embedded applications. It includes a 512-byte instruction cache, an integrated floating-point unit and a built-in interrupt controller. The 80960SB has a large register set, multiple parallel execution units and a 16-bit burst bus. Using advanced RISC technology, this high performance processor is capable of execution rates in excess of 5 million instructions per second *. The 80960SB is well-suited for a wide range of cost sensitive embedded applications including non-impact printers, network adapters and I/O controllers.Figure 1. The 80960SB Processor’s Highly Parallel Architecture*Relative to Digital Equipment Corporation’s VAX-11/780 at 1 MIPS (VAX-11™ is a trademark of Digital Equipment Corporation)s High-Performance Embedded Architecture —16 MIPS* Burst Execution at 16 MHz — 5 MIPS Sustained Execution at 16 MHzs 512-Byte On-Chip Instruction Cache—Direct Mapped —Parallel Load/Decode for Uncached Instructionss Multiple Register Sets—Sixteen Global 32-Bit Registers —Sixteen Local 32-Bit Registers —Four Local Register Sets Stored On-Chip —Register Scoreboardings Pin Compatible with 80960SA s Built-in Interrupt Controller — 4 Direct Interrupt Pins —31 Priority Levels, 256 Vectors s Built-In Floating Point Unit —Fully IEEE 754 Compatible s Easy to Use, High Bandwidth 16-Bit Bus —25.6 Mbytes/s Burst —Up to 16 Bytes Transferred per Burst s 32-Bit Address Space, 4 Gigabytes s 80-Lead Quad Flat Pack (EIAJ QFP)—84-Lead Plastic Leaded Chip Carrier (PLCC)s Software Compatible with80960KA/KB/CA/CF ProcessorsINSTRUCTION FETCH UNIT 512-BYTE INSTRUCTION CACHE INSTRUCTION DECODER MICRO-INSTRUCTION SEQUENCER MICRO-INSTRUCTION ROM 32-BIT BUS CONTROL LOGIC 32-BIT INSTRUCTION EXECUTION UNIT64- BY 32-BIT LOCAL REGISTER CACHE SIXTEEN 32-BIT GLOBAL REGISTERS 32-BIT ADDRESS16-BIT BURST BUSFOUR80-BIT FPREGISTERS80-BITFPUiiCONTENTS PAGE1.0 THE i960® PROCESSOR (1)1.1 Key Performance Features (2)1.1.1 Memory Space And Addressing Modes (4)1.1.2 Data Types (4)1.1.3 Large Register Set (4)1.1.4 Multiple Register Sets (5)1.1.5 Instruction Cache (5)1.1.6 Register Scoreboarding (5)1.1.7 Floating-Point Arithmetic (6)1.1.8 High Bandwidth Bus (6)1.1.9 Interrupt Handling (7)1.1.10 Debug Features (7)1.1.11 Fault Detection (7)1.1.12 Built-in T estability (7)1.1.13 CHMOS (7)2.0 ELECTRICAL SPECIFICATIONS (11)2.1 Power and Grounding (11)2.2 Power Decoupling Recommendations (11)2.3 Connection Recommendations (11)2.4 Characteristic Curves (11)2.5 T est Load Circuit (13)2.6 ABSOLUTE MAXIMUM RATINGS* (14)2.7 DC Characteristics (14)2.8 AC Specifications (15)3.0 MECHANICAL DATA (20)3.1 Packaging (20)3.2 Pin Assignment (20)3.3 Pinout (22)3.4 Package Thermal Specifications (26)4.0 WAVEFORMS (27)5.0 REVISION HISTORY ................................................................................................................................3380960SBEMBEDDED 32-BIT MICROPROCESSORWITH 16-BIT BURST DATA BUSiiiLIST OF FIGURESPAGE Figure 1The 80960SB Processor’s Highly Parallel Architecture ................................................................0Figure 280960SB Programming Environment ...........................................................................................1Figure 3Instruction Formats ......................................................................................................................4Figure 4Multiple Register Sets Are Stored On-Chip ..................................................................................6Figure 5Connection Recommendation for LOCK ....................................................................................11Figure 6Typical Supply Current vs. Case T emperature ...........................................................................12Figure 7Typical Current vs. Frequency (Room T emp) .............................................................................12Figure 8Typical Current vs. Frequency (Hot T emp) .................................................................................13Figure 9Capacitive Derating Curve .........................................................................................................13Figure 10Test Load Circuit for Three-State Output Pins ............................................................................13Figure 11Drive Levels and Timing Relationships for 80960SB Signals .....................................................15Figure 12Processor Clock Pulse (CLK2) ...................................................................................................18Figure 13RESET Signal Timing .................................................................................................................18Figure 14HOLD Timing ..............................................................................................................................19Figure 1580-Lead EIAJ Quad Flat Pack (QFP) Package ..........................................................................20Figure 1684-Lead Plastic Leaded Chip Carrier (PLCC) Package .............................................................21Figure 17Non-Burst Read and Write T ransactions Without Wait States ....................................................27Figure 18Quad Word Burst Read T ransaction With 1, 0, 0, 0, 0, 0, 0, 0 Wait States ................................28Figure 19Burst Write T ransaction With 2, 1, 1, 1 Wait States (6-8 Bytes T ransferred) ..............................29Figure 20Accesses Generated by Quad Word Read Bus Request, Misaligned One Byte from Quad Word Boundary 1, 0, 0, 0, 0, 0, 0, 0 Wait States 30Figure 21Interrupt Acknowledge Cycle ......................................................................................................31Figure 22Cold Reset Waveform ................................................................................................................32LIST OF TABLESTable 180960SB Instruction Set ..............................................................................................................3Table 2Memory Addressing Modes .........................................................................................................4Table 3Sample Floating-Point Execution Times (µs) at 16 MHz ..............................................................6Table 480960SB Pin Description: Bus Signals ........................................................................................8Table 580960SB Pin Description: Support Signals ................................................................................10Table 6DC Characteristics .....................................................................................................................14Table 780960SB AC Characteristics (10 MHz) ......................................................................................16Table 880960SB AC Characteristics (16 MHz) ......................................................................................17Table 980960SB QFP Pinout — In Pin Order ........................................................................................22Table 1080960SB QFP Pinout — In Signal Order ...................................................................................23Table 1180960SB PLCC Pinout — In Pin Order ......................................................................................24Table 1280960SB PLCC Pinout — In Signal Order .................................................................................25Table 1380960SB QFP Package Thermal Characteristics ......................................................................26Table 1480960SB PLCC Package Thermal Characteristics .. (26)180960SB1.0THE i960® PROCESSORThe 80960SB is a member of the 32-bit architecturefrom Intel known as the i960 processor family. Thesemicroprocessors were especially designed to servethe needs of embedded applications. The embeddedmarket includes applications as diverse as industrialautomation, avionics, image processing, graphicsand networking. These types of applications requirehigh integration, low power consumption, quickinterrupt response times and high performance.Since time to market is critical, embedded micropro-cessors need to be easy to use in both hardware and software designs.All members of the i960 processor family share a common core architecture which utilizes RISC technology so that, except for special functions, the family members are object-code compatible. Each new processor in the family adds its own special set of functions to the core to satisfy the needs of a specific application or range of applications in theembedded market.Figure 2. 80960SB Programming EnvironmentSIXTEEN 32-BIT GLOBAL REGISTERS SIXTEEN 32-BIT LOCAL REGISTERS g0g15r0r15 FOUR 80-BIT CONTROL REGISTERSFLOATING POINT REGISTERS ARCHITECTURALLYDEFINEDDATA STRUCTURESFFFF FFFFHINSTRUCTIONSTREAMINSTRUCTIONEXECUTIONPROCESSOR STATEREGISTERSINSTRUCTION POINTERARITHMETIC CONTROLSPROCESS CONTROLSTRACE CONTROLS ADDRESS SPACELOAD STORE0000 0000H INSTRUCTIONCACHE FETCH280960SB1.1Key Performance FeaturesThe 80960SB architecture is based on the mostrecent advances in microprocessor technology andis grounded in Intel’s long experience in the designand manufacture of embedded microprocessors.Many features contribute to the 80960SB’s excep-tional performance:rge Register Set. Having a large number ofregisters reduces the number of times that aprocessor needs to access memory. Moderncompilers can take advantage of this feature tooptimize execution speed. For maximum flexi-bility, the 80960SB provides thirty-two 32-bitregisters and four 80-bit floating point registers.(See Figure 2.)2.Fast Instruction Execution. Simple functionsmake up the bulk of instructions in mostprograms so that execution speed can beimproved by ensuring that these core instruc-tions are executed as quickly as possible. Themost frequently executed instructions — suchas register-register moves, add/subtract,logical operations and shifts — execute in oneto two cycles. (Table 1 contains a list of instruc-tions.)3.Load/Store Architecture. One way to improveexecution speed is to reduce the number oftimes that the processor must access memoryto perform an operation. As with otherprocessors based on RISC technology, the80960SB has a Load/Store architecture. Assuch, only the LOAD and STORE instructionsreference memory; all other instructionsoperate on registers. This type of architecturesimplifies instruction decoding and is used incombination with other techniques to increaseparallelism.4.Simple Instruction Formats. All instructionsin the 80960SB are 32 bits long and must bealigned on word boundaries. This alignmentmakes it possible to eliminate the instructionalignment stage in the pipeline. T o simplify theinstruction decoder, there are only fiveinstruction formats; each instruction uses onlyone format. (See Figure 3.)5.Overlapped Instruction Execution. Load operations allow execution of subsequent instructions to continue before the data has been returned from memory, so that these instructions can overlap the load. The 80960SB manages this process transparently to software through the use of a register score-board. Conditional instructions also make use of a scoreboard so that subsequent unrelated instructions may be executed while the condi-tional instruction is pending.6.Integer Execution Optimization. When the result of an arithmetic execution is used as an operand in a subsequent calculation, the value is sent immediately to its destination register.At the same time, the value is put on a bypass path to the ALU, thereby saving the time that otherwise would be required to retrieve the value for the next operation.7.Bandwidth Optimizations. The 80960SB gets optimal use of its memory bus bandwidth because the bus is tuned for use with the on-chip instruction cache: instruction cache line size matches the maximum burst size for instruction fetches. The 80960SB automatically fetches four words in a burst and stores them directly in the cache. Due to the size of the cache and the fact that it is continually filled in anticipation of needed instructions in the program flow, the 80960SB is relatively insen-sitive to memory wait states. The benefit is that the 80960SB delivers outstanding performance even with a low cost memory system.8.Cache Bypass. If a cache miss occurs, the processor fetches the needed instruction then sends it on to the instruction decoder at the same time it updates the cache. Thus, no extra time is spent to load and read the cache.380960SBTable 1. 80960SB Instruction Set Data MovementArithmetic Logical Bit and Bit Field LoadStoreMoveLoad Address Add Subtract Multiply DivideRemainderModuloShiftExtended MultiplyExtended Divide And Not And And Not Or Exclusive Or Not Or Or Not Nor Exclusive NorNotNandRotateSet Bit Clear Bit Not Bit Check Bit Alter Bit Scan For Bit Scan Over Bit Extract ModifyComparisonBranch Call/Return Fault CompareConditional CompareCompare and IncrementCompare and DecrementUnconditional Branch Conditional Branch Compare and Branch Call Call Extended Call System Return Branch and Link Conditional Fault Synchronize Faults DebugMiscellaneous Decimal Floating Point Modify Trace ControlsMarkForce Mark Atomic Add Atomic Modify Flush Local RegistersModify ArithmeticControlsScan Byte for EqualTest Condition Code Move Add with Carry Subtract with Carry Move Real Scale Round Square Root Sine Cosine TangentArctangentLogLog BinaryLog NaturalExponentClassifyCopy Real ExtendedCompareSynchronousConversion Synchronous LoadSynchronous Move Convert Real to Integer Convert Integer to Real480960SB Figure 3. Instruction FormatsControl Compare andBranchRegister toRegister Memory Access---ShortMemory Access---Long Opcode DisplacementOpcode Displacement Reg/Lit Reg M DisplacementOpcode Opcode Opcode Reg Reg Reg Reg/Lit Base Base M Modes Mode Ext’d Op Reg/LitX Offset Scale xx Offset1.1.1Memory Space And Addressing Modes The 80960SB offers a linear programmingenvironment so that all programs running on theprocessor are contained in a single address space.Maximum address space size is 4Gigabytes (232bytes).For ease of use the 80960SB has a small number ofaddressing modes, but includes all those necessaryto ensure efficient execution of high-level languagessuch as C.Table 2 lists the memory addressingmodes.Table 2. Memory Addressing Modes•12-Bit Offset •32-Bit Offset •Register-Indirect •Register + 12-Bit Offset •Register + 32-Bit Offset •Register + (Index-Register x Scale-Factor)•Register x Scale Factor + 32-Bit Displacement •Register + (Index-Register x Scale-Factor) +32-Bit Displacement Scale-Factor is 1, 2, 4, 8 or 161.1.2Data TypesThe 80960SB recognizes the following data types:Numeric:•8-, 16-, 32- and 64-bit ordinals •8-, 16-, 32- and 64-bit integers •32-, 64- and 80-bit real numbers Non-Numeric:•Bit •Bit Field •T riple Word (96 bits)•Quad-Word (128 bits)1.1.3Large Register Set The 80960SB programming environment includes a large number of registers. In fact, 32 registers are available at any time. The availability of this many registers greatly reduces the number of memory accesses required to perform algorithms, which leads to greater instruction processing speed.There are two types of general-purpose register:local and global. The global registers consist ofsixteen 32-bit registers (g0 though g15) and four580960SB 80-bit registers (fp0 through fp3). These registersperform the same function as the general-purposeregisters provided in other popular microprocessors.The term global refers to the fact that these registersretain their contents across procedure calls.The local registers, on the other hand, are procedurespecific. For each procedure call, the 80960SBallocates 16 local registers (r0 through r15). Eachlocal register is 32 bits wide. Any register can also beused for single or double-precision floating-pointoperations; the 80-bit floating-point registers areprovided for extended precision.1.1.4Multiple Register SetsTo further increase the efficiency of the register set,multiple sets of local registers are stored on-chip(See Figure 4). This cache holds up to four localregister frames, which means that up to threeprocedure calls can be made without having toaccess the procedure stack resident in memory.Although programs may have procedure calls nestedmany calls deep, a program typically oscillates backand forth between only two to three levels. As aresult, with four stack frames in the cache, the proba-bility of having a free frame available on the cachewhen a call is made is very high. In fact, runs ofrepresentative C-language programs show that 80%of the calls are handled without needing to accessmemory.If four or more procedures are active and a newprocedure is called, the 80960SB moves the oldestlocal register set in the stack-frame cache to aprocedure stack in memory to make room for a newset of registers. Global register g15 is the framepointer (FP) to the procedure stack.Global and floating point registers are not exchangedon a procedure call, but retain their contents, makingthem available to all procedures for fast parameterpassing.1.1.5Instruction CacheTo further reduce memory accesses, the 80960SBincludes a 512-byte on-chip instruction cache. Theinstruction cache is based on the concept of localityof reference; most programs are not usuallyexecuted in a steady stream but consist of manybranches, loops and procedure calls that lead to jumping back and forth in the same small section of code. Thus, by maintaining a block of instructions in cache, the number of memory references required to read instructions into the processor is greatly reduced.T o load the instruction cache, instructions are fetched in 16-byte blocks; up to four instructions can be fetched at one time. An efficient prefetch algorithm increases the probability that an instruction will already be in the cache when it is needed.Code for small loops often fits entirely within the cache, leading to a great increase in processing speed since further memory references might not be necessary until the program exits the loop. Similarly,when calling short procedures, the code for the calling procedure is likely to remain in the cache so it will be there on the procedure’s return.1.1.6Register Scoreboarding The instruction decoder is optimized in several ways.One optimization method is the ability to overlap instructions by using register scoreboarding.Register scoreboarding occurs when a LOAD moves a variable from memory into a register. When the instruction initiates, a scoreboard bit on the target register is set. Once the register is loaded, the bit is reset. In between, any reference to the register contents is accompanied by a test of the scoreboard bit to ensure that the load has completed before processing continues. Since the processor does not need to wait for the LOAD to complete, it can execute additional instructions placed between the LOAD and the instruction that uses the register contents, as shown in the following example:ld data_2, r4ld data_2, r5Unrelated instruction Unrelated instruction add r4, r5, r6In essence, the two unrelated instructions between LOAD and ADD are executed “for free” (i.e., take no apparent time to execute) because they are executed while the register is being loaded. Up to three load instructions can be pending at one time with three corresponding scoreboard bits set. By exploiting this feature, system programmers and compiler writers have a useful tool for optimizing execution speed.680960SB Figure 4. Multiple Register Sets Are Stored On-Chipr 15r 0310ONE OF FOUR LOCAL REGISTER SETS REGISTER CACHE LOCAL REGISTER SET1.1.7Floating-Point Arithmetic In the 80960SB, floating-point arithmetic has been made an integral part of the architecture. Having the floating-point unit integrated on chip provides two advantages. First, it improves the performance of the chip for floating-point applications, since no additional bus overhead is associated with floating-point calculations, thereby leaving more time for other bus operations such as I/O. Second, the cost of using floating-point operations is reduced because a separate coprocessor chip is not required.The 80960SB floating-point (real-number) data types include single-precision (32-bit), double-precision (64-bit) and extended precision (80-bit) floating-point numbers. Any registers may be used to executefloating-point operations.The processor provides hardware support for bothmandatory and recommended portions of IEEEStandard 754 for floating-point arithmetic, includingall arithmetic, exponential, logarithmic and othertranscendental functions.T able 3 shows executiontimes for some representative instructions.1.1.8 High Bandwidth Bus The 80960SB CPU resides on a high-bandwidthaddress/data bus. The bus provides a direct commu-nication path between the processor and the memory and I/O subsystem interfaces. The processor uses the bus to fetch instructions,manipulate memory and respond to interrupts. Bus features include:•16-bit data path multiplexed onto the lower bits of the 32-bit address path •Eight 16-bit half-word burst capability which allows transfers from 1 to 16 bytes at a time •High bandwidth reads and writes with25.6MBytes/s burst (at 16 MHz)Table 4 defines bus signal names and functions;Table 5 defines other component-support signalssuch as interrupt lines.Table 3. Sample Floating-Point Execution Times(µs) at 16 MHzFunction32-Bit 64-Bit Add0.60.8Subtract0.60.8Multiply1.12.0Divide2.0 4.5Square Root5.86.1Arctangent15.820.5Exponent17.719.5Sine23.825.9Cosine 23.825.9780960SB1.1.9Interrupt Handling The 80960SB can be interrupted in one of two ways:by the activation of one of four interrupt pins or by sending a message on the processor’s data bus.The 80960SB is unusual in that it automatically handles interrupts on a priority basis and can keep track of pending interrupts through its on-chip interrupt controller. Two of the interrupt pins can be configured to provide 8259A-style handshaking for expansion beyond four interrupt lines.1.1.10Debug FeaturesThe 80960SB has built-in debug capabilities. There are two types of breakpoints and six trace modes.Debug features are controlled by two internal 32-bit registers, the Process-Controls Word and the T race-Controls Word. By setting bits in these control words,a software debug monitor can closely control how the processor responds during program execution.The 80960SB provides two hardware breakpoint registers on-chip which, by using a special command, can be set to any value. When the instruction pointer matches either breakpoint register value, the breakpoint handling routine is automati-cally called.The 80960SB also provides software breakpoints through the use of two instructions: MARK and FMARK. These can be placed at any point in a program and cause the processor to halt execution at that point and call the breakpoint handling routine.The breakpoint mechanism is easy to use and provides a powerful debugging tool.Tracing is available for instructions (single step execution), calls and returns and branching. Each trace type may be enabled separately by a special debug instruction. In each case, the 80960SB executes the instruction first and then calls a trace handling routine (usually part of a software debug monitor). Further program execution is halted until the routine completes, at which time execution resumes at the next instruction. The 80960SB’s tracing mechanisms, implemented completely in hardware, greatly simplify the task of software test and debug.1.1.11Fault DetectionThe 80960SB has an automatic mechanism to handle faults. Fault types include floating point,trace and arithmetic faults. When the processor detects a fault, it automatically calls the appropriate fault handling routine and saves the current instruction pointer and necessary state information to make efficient recovery possible. Like interrupt handling routines, fault handling routines are usually written to meet the needs of specific applications and are often included as part of the operating system or kernel.For each of the fault types, there are numerous subtypes that provide specific information about a fault. For example, a floating point fault may have the subtype set to an Overflow or Zero-Divide fault.The fault handler can use this specific information to respond correctly to the fault.1.1.12Built-in TestabilityUpon reset, the 80960SB automatically conducts an exhaustive internal test of its major blocks of logic.Then, before executing its first instruction, it does a zero check sum on the first eight words in memory to ensure that the memory image was programmed correctly. If a problem is discovered at any point during the self-test, the 80960SB asserts its and will not begin program execution. Self test takes approximately 47,000 cycles to complete.System manufacturers can use the 80960SB’s self-test feature during incoming parts inspection. No special diagnostic programs need to be written. The test is both thorough and fast. The self-test capability helps ensure that defective parts are discovered before systems are shipped and, once in the field,the self-test makes it easier to distinguish between problems caused by processor failure and problems resulting from other causes.1.1.13CHMOSThe 80960SB is fabricated using Intel’s CHMOS IV (Complementary High Speed Metal Oxide Semicon-ductor) process. The 80960SB is available at 10MHz in the QFP package and at 10and 16 MHz in the PLCC package.880960SBTable 4. 80960SB Pin Description: Bus Signals (Sheet 1 of 2)NAME TYPE DESCRIPTIONCLK2I SYSTEM CLOCK provides the fundamental timing for 80960SB systems. It is divided by two inside the 80960SB to generate the internal processor clock.A31:16O T.S.ADDRESS BUS carries the upper 16 bits of the 32-bit physical address to memory. It is valid throughout the burst cycle; no latch is required.AD15:1, D0I/O T.S.ADDRESS/DATA BUS carries the low order 32-bit addresses and 16-bit data to and from memory. AD15:4 must be latched since the cycle following the address cycle carries data on the bus.A3:1O T.S.ADDRESS BUS carries the word addresses of the 32-bit address to memory. These three bits are incremented during a burst access indicating the next word address of the burst access. Note that A3:1 are duplicated with AD3:1 during the address cycle.ALEO T.S.ADDRESS LATCH ENABLE indicates the transfer of a physical address.ALE is asserted during a T a cycle and deasserted before the beginning of the T d state. It is active HIGH and floats to a high impedance state during a hold cycle (T h ).AS O T.S.ADDRESS STATUS indicates an address state.AS is asserted every T a state and deasserted during the following T d state.AS is driven HIGH during reset.W/R O T.S.WRITE/READ specifies, during a T a cycle, whether the operation is a write or read. It is latched on-chip and remains valid during T d cycles.DENO T.S.DATA ENABLE is asserted during T d cycles and indicates transfer of data on the AD lines. The AD lines should not be driven by an external source unless DEN is asserted. When DEN is asserted, outputs from the previous cycle are guaranteed to be three-stated. In addition,DEN deasserted indicates inputs have been captured; therefore input hold times can be disregarded.DEN is driven HIGH during reset.DT/RO T.S.DATA TRANSMIT / RECEIVE indicates the direction of data transfer to and from the bus. It is low during T a and T d cycles for a read or interrupt acknowledgment; it is high during T a and T d cycles for a write. DT/R never changes state when DEN is asserted. DT/R is driven HIGH during reset.READY IREADY indicates that data on AD lines can be sampled or removed. If READY is not asserted during a T d cycle, the T d cycle is extended to the next cycle by inserting a wait state (T w ).I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state。

OPB856Z;OPB856;中文规格书,Datasheet资料

OPB856ZWide Gap Optical SensorFeatures:x Designed for Industrial applications x Threaded housing (M12 X 1 TH), Nut included x Molded connectors mates with Molex 03-06-2023 plug. x Emitter (White) and Senor (Black) housing color coded Product Photo HereDescription:The OPB856 emitter and sensor pair that consists of an LED (935 nm) and a Phototransistor designed to operate efficiently with each other. They are mounted in a threaded (M12x1TH) color-coded housing. The LED (white) and the Phototransistor (black) are designed to easily panel mount in through a 0.4724” (12.0 mm) hole. A 12 mm nut is included for each housing. Both components is designed to electrically mate with a Molex (03-06-2023) connector. The OPB856 pair are designed to operate with separation distances between the LED and Phototransistor up to 12” (30.48 cm). For Custom electrical, wire and cabling and connectors are available. Contact your local representative or OPTEK for more information.Applications:x x x x xNon-contact interruptive object sensing Assembly line automation Machine automation Equipment security Machine safetyOptical Pair Part Number OPB856ZOrdering InformationLED Peak Wavelength 935 nm Sensor Transistor Connector Type Use Molex 03-06-202311LEDPhototransistor22HousingPlug Pin for PlugLED - WhiteMOLEX 03-06-2023 Male MOLEX 02-06-6122Sensor - BlackMOLEX 03-06-2023 Female MOLEX 02-06-7104White HousingPin # 1 2 LED Anode Cathode 1 2Black HousingPin # Phototransistor Emitter CollectorRoHSOPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible. Issue A .1 01/06 Page 1 of 3OPTEK Technology Inc. — 1645 Wallace Drive, Carrollton, Texas 75006 Phone: (972) 323-2200 or (800) 341-4747 FAX: (972) 323-2396 sensors@ /OPB856ZWide Gap Optical SensorAbsolute Maximum Ratings (TA=25°C unless otherwise noted)Storage & Operating Temperature Range Lead Soldering Temperature [1/16 inch (1.6 mm) from case for 5 seconds with soldering iron] Input Diode (See OP165 for additional information) Continuous Forward DC Current Reverse Voltage Power Dissipation(1) Output Phototransistor (See OP505 for additional information) Collector-Emitter Voltage Emitter-Collector Voltage Power Dissipation(1)-40° C to +85° C 260° C40 mA 2V 100 mW30 V 5V 100 mWElectrical Characteristics (TA = 25rC unless otherwise noted)SYMBOL PARAMETER MIN TYP MAX UNITS TEST CONDITIONSInput Diode (See OP9999 for additional information) VF IR Forward Voltage Reverse Current 1.7 100 V µA IF = 20 mA VR = 2 VOutput Phototransistor (See OP9999 for additional information) V(BR)CEO V(BR)ECO ICEO Combined IC(ON) On-State Collector Current(3) 1.8 mA VCE = 5 V, IF = 20 mA, d = 2”( (50.8 mm)(2) Collector-Emitter Breakdown Voltage Emitter-Collector Breakdown Voltage Collector Dark Current 30 5 100 V V nA IC = 100 µA IE = 100 µA VCE = 10 V, IF = 0, EE = 0Notes: (1) Derate linearly 1.67 mW/° C above 25 ° C.. (2) Distance between lenses along the optical axis is “d”. (3) All parameters tested using pulse technique.OPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible. Issue A .1 01/06 Page 2 of 3 OPTEK Technology Inc. — 1645 Wallace Drive, Carrollton, Texas 75006 Phone: (972) 323-2200 or (800) 341-4747 FAX: (972) 323-2396 sensors@ /OPB856ZWide Gap Optical SensorNormalized Collector Current vs. Distance between Emitter and Sensor2.0 1.8 1.6Normalized at d = 2.0" IF = 20mA VCE = 5VNormalized Output Current1.4 1.2 1.0 0.8 0.6 0.4 0.2 0.05 mA 10 mA 20 mA 30 mA 40 mA 50 mA0.02.04.06.08.010.012.014.0Distance to Reflective Surface (inches)OPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible. OPTEK Technology Inc. — 1645 Wallace Drive, Carrollton, Texas 75006 Phone: (972) 323-2200 or (800) 341-4747 FAX: (972) 323-2396 sensors@ Issue A .1 01/06 Page 3 of 3/分销商库存信息:OPTEK-TECHNOLOGY OPB856Z OPB856。

士兰微电子 SC8560带LED驱动的数字闹钟电路 说明书

数字位 4

分个位

分个位 分个位 秒个位

杭州士兰微电子股份有限公司

http:

版本号:1.1 2008.06.02 共10页 第4页

SC8560

表 2: 设置内容

显示模式 设置输入

功能说明

小时

按下后立即将小时位加 1,随后以 2Hz 的速率,在每个 1/4 秒和 3/4 秒时加 1。

备控制。

SC8560

版本号:1.1 2008.06.02 共10页 第6页

图 1、 12小时显示和60Hz输入线路

时钟应用电路(负电源使用)

杭州士兰微电子股份有限公司

http:

蜂鸣器

f=900Hz

12HR NC

60Hz NC

28 27 26 25 24 23 22 21 20 19 18 17 16 15

-0.4 ~ +0.4 700

-30 ~ +70 -55 ~ +125

单位 V V V V mA

mW °C °C

电气参数(除非特殊说明,Tamb=25°C,VSS=0V)

参数 工作电压 输入高电平 输入低电平 输入高电平 输入低电平 50/60Hz端输入电压 输入高电平电流1 输入低电平电流1 输入高电平电流2

10'S MIN c&d

10'S MIN e & MIN e

MIN b&g

MIN c&d

MIN a&f

Colon Out

1 2 3 4 5 6 7 8 9 10 11 12 13 14

正半周 负半周

管脚复用LED屏

注: 1、

共阴极

2、

a

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

-5Total 10 Pages

8/8/2006

元器件交易网

BL8560

Typical Application Circuit Application hints

Explanation

-6Total 10 Pages

8/8/2006

Product Name

BL8560-APRD BL8560-BPRD BL8560-CPRD BL8560-DPRD BL8560-EPRD BL8560-FPRD BL8560-GPRD BL8560-HPRD BL8560-IPRD

5.0V/3.3V

SOT-23-6C

BL8560-WPRC

-2Total 10 Pages

元器件交易网

BL8560

Typical Performance Characteristics 1) Output Voltage vs. Output Current (with output short protection) 2) Output Voltage vs. Input Voltage

Vout Vin Vout Vout Iout

Vout T Vout

Electrical Characteristics by Output Voltage

Output Voltage Vout (V) Dropout Voltage, VDIF (V) Condition Typ. Max.

-9Total 10 Pages

8/8/2006

元器件交易网BL8560 Nhomakorabea

- 10 Total 10 Pages

8/8/2006

SOT-23-6D

BL8560-WPRD

8/8/2006

元器件交易网

BL8560

Product Marking information:

SOT-23-6C SOT-23-6D

元器件交易网

BL8560

Dual,Low noise, 150mA LDO regulator Features General Description

Applications

BL8560 Typical Application Circuit

BL8560 Typical Performance Characteristics

Product Name

BL8560-APRC BL8560-BPRC BL8560-CPRC BL8560-DPRC BL8560-EPRC BL8560-FPRC BL8560-GPRC BL8560-HPRC BL8560-IPRC

Package Type

SOT-23-6D SOT-23-6D SOT-23-6D SOT-23-6D SOT-23-6D SOT-23-6D SOT-23-6D SOT-23-6D SOT-23-6D

-4Total 10 Pages

8/8/2006

元器件交易网

BL8560

Electrical Characteristics

BL8560, for arbitrary output voltage

Symbol

Parameter

Conditions

Min

Typ

Max

Units

Symbol

Function

Product Classification Output Voltage Package Type

1.5V/2.5V 1.5V/2.8V 1.5V/3.0V 1.5V/3.3V 1.5V/4.0V 1.8V/1.8V 1.8V/2.5V 1.8V/2.8V 1.8V/3.0V SOT-23-6C SOT-23-6C SOT-23-6C SOT-23-6C SOT-23-6C SOT-23-6C SOT-23-6C SOT-23-6C SOT-23-6C

-3Total 10 Pages

8/8/2006

元器件交易网

BL8560

Block Diagram

Absolute Maximum Ratings

Recommended Work Conditions

Item Min Recommended Max unit

-1Total 10 Pages

8/8/2006

元器件交易网

BL8560

Selection Guide BL8560 X X XX Pin Assignment

Pin Description

Pin Number

SOT-23-6C SOT-23-6D

3) Dropout Voltage vs. Output Current

4) Supply Current vs. Input Voltage

-7Total 10 Pages

8/8/2006

元器件交易网

BL8560

5) Ripple rejection vs. Frequency 6) Line transient response

Vin

Vout

7) Load transient response

-8Total 10 Pages

8/8/2006

元器件交易网

BL8560

Package Information: