RT9818G-12GV中文资料

RT9818

RESET/

RESET

NC

4

3

1

2

VDD

GND

SC-70-4 (R-Type)

VDD

3

1

2

RESET/ RESET

GND

SOT-23-3

VDD

3

1

2

GND

RESET/ RESET

SOT-23-3 (L-Type)

NC

NC

5

4

123

RESET/ VDD GND RESET

SOT-23-5

1

2

3

RESET/ VDD GND RESET

−100%matte tin (Sn) plating.

1

RT9818

Pin Configurations

VDD

3

1

2

GND

RESET/ RESET

SC-70-3

GND

NC

4

3

1

2

RESET/ RESET

VDD

SC-70-4

Preliminary

(TOP VIEW)

450ms Options z Low Functional Supply Voltage 0.9V z N-Channel Open-Drain Output z Small SC-70-3, SC-70-4, SOT-23-3, SOT-23-5,

SOT-89 Packages z RoHS Compliant and 100% Lead (Pb)-Free

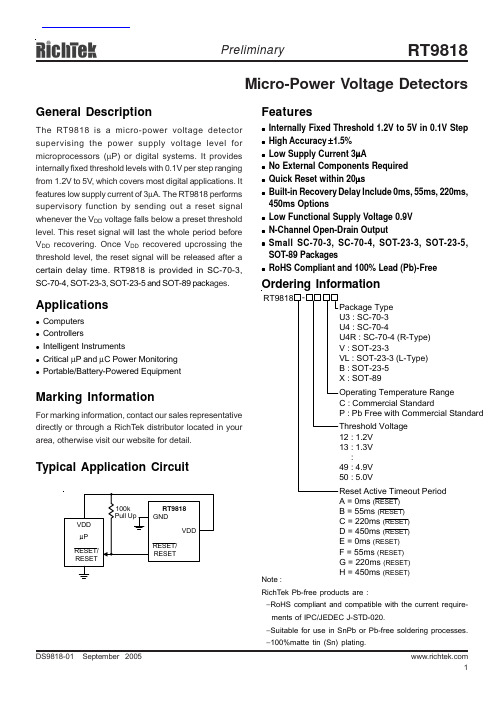

Ordering Information

RT9818 -

Package Type U3 : SC-70-3 U4 : SC-70-4 U4R : SC-70-4 (R-Type) V : SOT-23-3 VL : SOT-23-3 (L-Type) B : SOT-23-5 X : SOT-89

RT9818E-50PVL中文资料

VDD μP

RESET/ RESET

100k Pull Up

RT9818 GND

VDD

RESET/ RESET

Note : RichTek Pb-free and Green products are :

`RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

Ordering Information

RT9818 -

Package Type U3 : SC-70-3 V : SOT-23-3 VL : SOT-23-3 (L-Type) B : SOT-23-5 X : SOT-89 Y : SC-82 YR : SC-82 (R-Type)

Operating Temperature Range P : Pb Free with Commercial Standard G : Green (Halogen Free with Commer-

z Storage Temperature Range ---------------------------------------------------------------------------------------- −65°C to 125°C

z ESD Susceptibility (Note 2) HBM (Human Body Mode) ------------------------------------------------------------------------------------------ 2kV MM (Machine Mode) -------------------------------------------------------------------------------------------------- 200V

RT9818C-50GV中文资料

Packages z RoHS Compliant and 100% Lead (Pb)-Free

Functional Pin Description

Pin Name GND RESET RESET VDD

Pin Function Ground Active Low Open-Drain Reset Output Active High Open-Drain Reset Output Power Pin

Typical Application Circuit

VDD μP

RESET/ RESET

100k Pull Up

RT9818 GND

VDD

RESET/ RESET

Note : RichTek Pb-free and Green products are :

`RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

NC

4

3

1

2

RESET/ RESET

VDD

SC-82

RESET/

RESET

NC

4

3

1

2

VDD

GND

SC-82 (R-Type)

(TOP VIEW)

VDD

3

1

2

GND

RESET/ RESET

东芝芯片资料

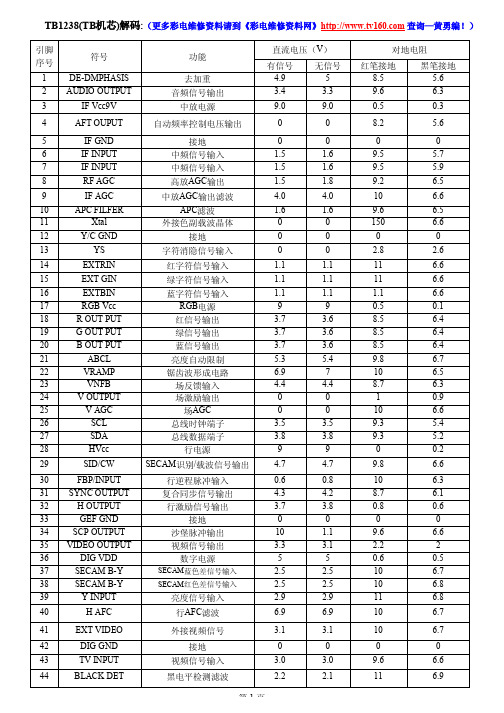

0 900Ω 600Ω 19.5K 15K 13K 19K

LA7833引脚功能

引脚

1 2 3 4 4 6 7

功能

接地端 场输出 自举升压电源端 场激励输入 负反馈输入及相位补偿 电源端 场逆程脉冲输出

直流电压

0V 13.6V 25.5V 0.8V 0.8V 26V 1.4V

纹波滤波电路引脚 第二伴音中频输出 调频直流反馈滤波电路引脚

电压

1.8V 0V 1.3V

+2.5V

+5V 2.45V 2.45V

1V 6.4V 0V 0V 2.3V 1.6V 0V +5V 3.6V 4.3V 0V 8V 8.8V 3.5V 5.6V 3.4V 3.5V

RXIK档对地电阻(黑表笔接地)

场AGC 总线时钟端子 总线数据端子

行电源 SECAM识别/载波信号输出

行逆程脉冲输入 复合同步信号输出 行激励信号输出

接地 沙堡脉冲输出 视频信号输出

数字电源

SECAM蓝色差信号输入 SECAM红色差信号输入

亮度信号输入 行AFC滤波

外接视频信号

接地 视频信Leabharlann 输入黑电平检测滤波直流电压(V)

有信号 4.9

800Ω 0

12.5K

12.8K

6K 13K 13K 13K 12.8K 13.2K

0 12.8K 13K 11.5K

1K 12.5K 12K

0 900Ω 600Ω 12.5K 12.2K 11.5K 12K

红笔接地 R×1K档

800Ω 0

19K

27K

5.5K 20K 20K 18K 28K 28K

华为CG9812 V500R005产品概述

华为CG9812产品概述(V500R005)华为技术有限公司2015年4月目录1 产品简介 (1)1.1 产品定位 (1)1.2 接口与协议 (2)2 产品特点 (4)2.1 先进的软硬件平台 (4)2.2 多接入性 (5)2.3 灵活的话单处理 (5)2.4 大容量和强大的处理性能 (5)2.5 可扩容性 (5)2.6 高可靠性 (6)2.7 方便实用的操作维护功能 (6)3 产品结构 (7)3.1 硬件结构 (7)3.1.1 机柜 (7)3.1.2 机框 (8)3.1.3 硬件组件设计标准 (10)3.2 软件结构 (11)4 业务与功能 (14)4.1 网元接口功能 (14)4.2 话单处理功能 (14)4.3 计费接口功能 (15)5 操作与维护 (16)5.1 话单浏览查询功能 (16)5.2 安全管理功能 (16)5.3 配置管理功能 (17)5.4 性能管理功能 (17)5.5 故障管理功能 (17)6 可靠性 (19)6.1 硬件可靠性 (19)6.2 软件可靠性 (20)6.3 话单可靠性 (21)7 技术指标 (23)7.1 性能指标 (23)7.2 对外接口规格指标 (23)7.3 可靠性指标 (24)7.4 功耗参数 (24)7.5 机柜参数 (25)7.6 环境指标 (25)7.7 EMC指标 (26)8 环境要求 (29)8.1 储存环境 (29)8.2 运输环境 (31)8.3 运行环境 (33)插图目录图1-1 CG典型组网 (2)图1-2 CG的接口与协议 (3)图3-1 N68E-22机柜 (8)图3-2 机框前视图 (9)图3-3 机框后视图 (10)图3-4 软件结构 (11)图3-5 AP进程 (12)表格目录表1-1 接口与协议 (3)表7-1 CG9812的性能指标 (23)表7-2 CG9812外部接口规格指标 (24)表7-3 可靠性指标 (24)表7-4 机柜物理参数 (25)表7-5 环境适应性 (25)表7-6 -48V电源端口传导发射指标 (26)表7-7 辐射发射指标要求 (26)表7-8 传导敏感度指标 (26)表7-9 辐射敏感度指标 (27)表7-10 静电放电指标 (27)表7-11 电子脉冲群指标 (27)表7-12 浪涌指标 (28)表8-1 气候环境要求 (29)表8-2 机械活性物质的浓度要求 (30)表8-3 化学活性物质的浓度要求 (30)表8-4 机械应力要求 (31)表8-5 气候环境要求 (31)表8-6 机械活性物质的浓度要求 (32)表8-7 化学活性物质的浓度要求 (32)表8-8 机械应力要求 (33)表8-9 气候环境要求 (34)表8-10 机械活性物质的浓度要求 (34)表8-11 化学活性物质的浓度要求 (34)表8-12 机械应力要求 (35)1 产品简介关于本章介绍CG的产品定位、接口与协议等。

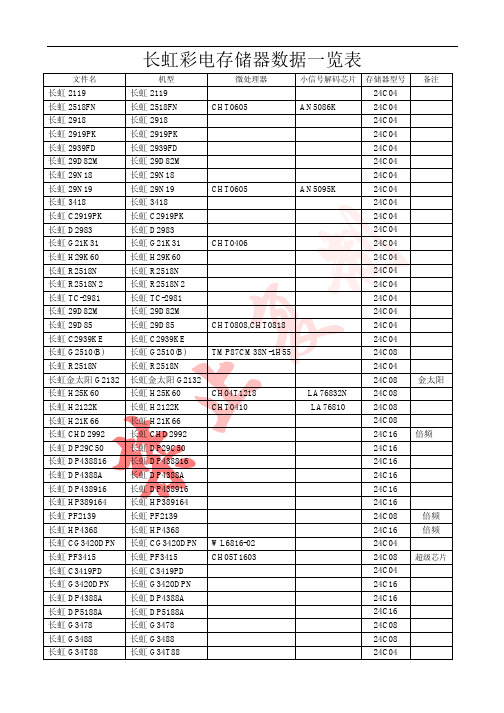

长虹存储器

微处理器

CHT0605

CHT0605 CHT0406

CHT0808,CHT0818 TMP87CM38N-1H55 CH04T1218 CHT0410

WL6816-02 CH05T1603

小信号解码芯片

AN5086K AN5095K

LA76832N LA76810

存储器型号

24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C04 24C08 24C04 24C08 24C08 24C08 24C08 24C16 24C16 24C16 24C16 24C16 24C16 24C08 24C16 24C04 24C08 24C04 24C16 24C16 24C16 24C08 24C08 24C04

TMP87CM38N-1H55

CHT0605 M37102M8-AB2SP 87CP38N-1P08

TB1238

AN5095 TA8759 TB1238

24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C04 24C08 24C04 24C08 24C04 24C04 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C08 24C04 24C01 24C16

RT-121919中文资料

ECONOLINE - DC/DC-Converter

RT Series, 1 Watt, DIP14, Isolated Outputs (Dual Output) Features

● ● ● ● ●

Twin Independent Outputs Output/Output Isolation 1kVDC Power Sharing on Outputs Input/Output Isolation 1kVDC No Heatsink Required

9 10 11 14 NC = No Connection

10.00

7.62

7.10

2.0

15.24

3.05

Re2.54

1.00 ø+0.15/–0

XX.X ± 0.5 mm XX.XX ± 0.25 mm

14 PIN DIP Package

3rd angle projection

1

7

Bottom View

14 11 10 9 8

Pin Connections Pin # 1 7 8 Dual –Vin NC –Vout 2 +Vout 2 –Vout 1 +Vout 1 +Vin

19.90

RT-051212 RECOM ****

Output Power (Watts) 2.0 1.5 1.0 Safe Operating Area 0.5 0 -40 0 50 100 125 150 85 Operating Temperature ˚C

100mVp-p max. 70% min. 1.000VDC min. 10 GΩ min. 20pF min./94pF max. 1 Second 100kHz typ. –40°C to +85°C (see Graph) -55°C to +125°C 2.7g

MID 方案可选器件

(no SATA, over $20)

Rockchip RK2918 Coretex A8

(no SATA/CVBS)

Qualcom QSD8250 Coretex A8

TI Omap 36xx Coretex A8

(no SATA/CVBS)

Marvell Amarda610 Coretex A8

接近传感器

当你把手机靠近耳朵时,接近传感器会立刻把屏幕关起来来节省电源以及避 免误触屏幕。

Epson crystaห้องสมุดไป่ตู้ (PM: Derek.Wang)

MC-146 32.768K 12.5PF +-20PPM TG-5010LH 26M 04A FOR TD-

SCDMA

TG-5010LH 19.2M 06A FOR

Telechips TCC8803 MID Main Functions

Andriod2.2/2.3 WiFi: Atheros 6102/6302 3G: - Huawei 3G module:EM660C, EM660,

EM770/EM770W, MU509 - Huawei 3G dongle: -- EVDO: EC122, EC169C, -- WCDMA: E1750, E1752, K3765 - ZTE MF210 - Mobile Peak:3G module and dongle K80 DTV: CMMB, ISDB-T, DVB-T ATV: RDA GPS: SIRF A3, UBLOG Bluetooth: CSR(BC04/06/07), RDA

2.Wifi Chip Antenna: size: 5.2*3.7*0.7mm 2.0*1.2*0.55mm

RT9818E-49GB资料

NC

4

3

1

2

RESET/ RESET

VDD

SC-82

RESET/

RESET

NC

4

3

1

2

VDD

GND

SC-82 (R-Type)

(TOP VIEW)

VDD

3

1

2

GND

RESET/ RESET

SC-70-3

VDD

3

1

2

RESET/ RESET

GND

SOT-23-3

VDD

3

1

2

GND

RESET/ RESET

RT9818

Absolute Maximum Ratings (Note 1)

z Terminal Voltage (with Respect to GND)

VDD ------------------------------------------------------------------------------------------------------------------------ −0.3V to 6.0V z All Other Inputs -------------------------------------------------------------------------------------------------------- −0.3V to VDD+0.3V

Typical Application Circuit

VDD μP

RESET/ RESET

100k Pull Up

RT9818 GND

VDD

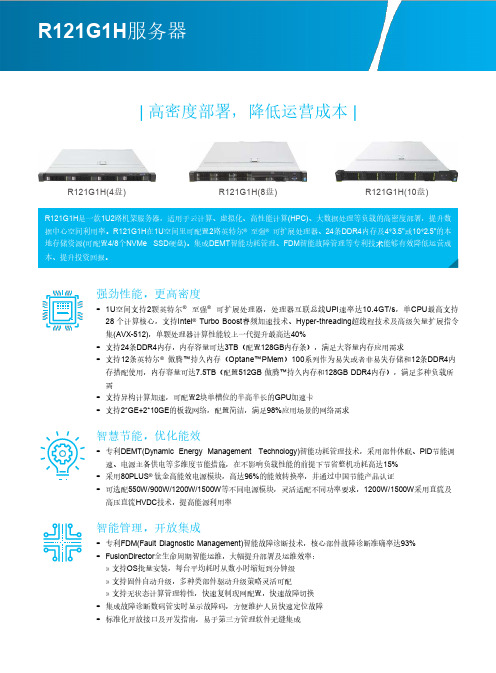

R121G1H 服务器说明书

| 高密度部署,降低运营成本 |R121G1H(4盘) R121G1H(8盘) R121G1H(10盘)R121G1H是一款1U2路机架服务器,适用于云计算、虚拟化、高性能计算(HPC)、大数据处理等负载的高密度部署,提升数据中心空间利用率。

R121G1H在1U空间里可配置2路英特尔®至强®可扩展处理器、24条DDR4内存及4*3.5"或10*2.5"的本地存储资源(可配置4/8个NVMe SSD硬盘)。

集成DEMT智能功耗管理、FDM智能故障管理等专利技能够有效降低运营成本、提升投资回报。

强劲性能,更高密度•1U空间支持2颗英特尔®至强®可扩展处理器,处理器互联总线UPI速率达10.4GT/s,单CPU最高支持28 个计算核心,支持Intel®Turbo Boost睿频加速技术、Hyper-threading超线程技术及高级矢量扩展指令集(AVX-512),单颗处理器计算性能较上一代提升最高达40%•支持24条DDR4内存,内存容量可达3TB(配置128GB内存条),满足大容量内存应用需求•支持12条英特尔®傲腾™持久内存(Optane™PMem)100系列作为易失或者非易失存储和12条DDR4内存搭配使用,内存容量可达7.5TB(配置512GB 傲腾™持久内存和128GB DDR4内存),满足多种负载所需•支持异构计算加速,可配置2块单槽位的半高半长的GPU加速卡•支持2*GE+2*10GE的板载网络,配置简洁,满足98%应用场景的网络需求智慧节能,优化能效•专利DEMT(Dynamic Energy Management Technology)智能功耗管理技术,采用部件休眠、PID节能调速、电源主备供电等多维度节能措施,在不影响负载性能的前提下节省整机功耗高达15%•采用80PLUS®钛金高能效电源模块,高达96%的能效转换率,并通过中国节能产品认证•可选配550W/900W/1200W/1500W等不同电源模块,灵活适配不同功率要求,1200W/1500W采用直流及高压直流HVDC技术,提高能源利用率智能管理,开放集成•专利FDM(Fault Diagnostic Management)智能故障诊断技术,核心部件故障诊断准确率达93%•FusionDirector全生命周期智能运维,大幅提升部署及运维效率:»支持OS批量安装,每台平均耗时从数小时缩短到分钟级»支持固件自动升级,多种类部件驱动升级策略灵活可配»支持无状态计算管理特性,快速复制现网配置,快速故障切换•集成故障诊断数码管实时显示故障码,方便维护人员快速定位故障•标准化开放接口及开发指南,易于第三方管理软件无缝集成1/2个第一代英特尔® 至强® 可扩展处理器3100/4100/5100/6100/8100系列,最高205W 1/2个第二代英特尔® 至强® 可扩展处理器3200/4200/5200/6200/8200系列,最高205W 内存24个DDR4内存插槽,最高2933MT/s ,最多12条英特尔®傲腾™持久内存100系列,最高2666MT/sRAID 支持可选配支持RAID0、1、10、5、50、6、60等,支持Cache 超级电容保护,提供RAID 级别迁移、磁盘漫游、自诊断、Web 远程设置等功能PCIe 扩展 最多5个PCIe 3.0扩展槽位,包括1个RAID 卡专用的PCIe 扩展卡,1个灵活LOM 插卡风扇7个热拔插对旋风扇,支持N+1冗余• iBMC 芯片集成1个专用管理GE 网口,提供全面的故障诊断、自动化运维、硬件安全加固等管理特性• iBMC 支持Redfish 、SNMP 、IPMI2.0等标准接口;提供基于HTML5/VNC KVM 的远程管理界面;支持免CD 部署和Agentless 特性 管理简化管理复杂度• 可选配管理软件,提供无状态计算、OS 批量部署、固件自动升级等高级管理特性,实现全生命周期智能化、自动化管理安全特性支持加电密码、管理员密码、TPM 2.0、安全面板等安全特性产品认证 CCC尺寸(高x 宽x 深)3.5英寸硬盘机箱尺寸:43 mm×447 mm×748 mm 2.5英寸硬盘机箱尺寸:43 mm×447 mm×708 mm形态1U 机架服务器支持多种不同的硬盘配置,硬盘支持热插拔:可配置个英寸硬盘 个硬盘与2~4SAS/SATA 硬盘,总硬盘数≦10)可配置个英寸硬盘个硬盘与硬盘,总硬盘数≦1可配置个英寸硬盘 可配置英寸硬盘可配置4个3.5英寸SAS/SATA/SSD 硬盘 支持Flash 存储: 双支持2个单槽位的半高半长的GPU 异构加速卡。

华为GGSN9811功能描述

华为GGSN9811功能描述(V800R005)华为技术有限公司2013年2月目录华为GGSN9811功能描述 (1)基本功能描述 (1)1WGFD-010000 基本业务 (1)2WGFD-020000 支持GPRS用户和3G用户同时接入网络 (3)3WGFD-030000 计费 (6)4WGFD-050000 QOS和流量管理 (9)5WGFD-060000 路由 (12)6WGFD-070000 可靠性 (14)7WGFD-080000 操作维护 (16)8WGFD-090000 安全 (20)9WGFD-100000 Radius 功能 (25)10WGFD-140000 SNMP (26)11WGFD-230000 跟踪功能 (26)12WGFD-160000 支持NTP V3 (29)13WGFD-110000 VPN (30)14WGFD-200000 VLAN功能 (31)15WGFD-220000 Eth-Trunk功能 (31)16WGFD-240000 GGSN负荷分担控制功能 (32)17WGFD-170200 APN鉴权方式可选 (32)可选功能描述 (34)1WGFD-010105 空闲PDP上下文去活功能 (34)2WGFD-031100 支持热计费功能 (34)3WGFD-040000 内容计费 (35)4WGFD-050400 支持会话类QOS保证 (37)5WGFD-110300 L2TP VPN (37)6WGFD-120000 IPSec功能 (38)7WGFD-130000 合法监听 (39)8WGFD-150000 支持IPv6的PDP上下文 (40)9WGFD-17000 APN可选功能项 (40)10WGFD-260000 支持多HPLMN (42)11WGFD-270000 支持HSPA (42)12WGFD-280000 流媒体感知功能 (43)13WGFD-300000 支持Gy接口在线计费 (44)14WGFD-310000 IMS/Go接口 (44)15WGFD-320000 接入网络类型反射 (45)备选功能描述 (47)1WGFD-010000 基本业务 (47)2WGFD-050000 QOS和流量管理 (48)3WGFD-060000 路由 (51)4WGFD-100000 Radius (52)5WGFD-110100 MPLS VPN (54)6WGFD-180000 移动IP (54)7WGFD-19000 支持CAMEL3智能预附费业务 (54)8WGFD-290000 GGSN Proxy功能 (55)9WGFD-330000 差异化服务 (56)10WGFD-340000 SSH (56)11WGFD-350000 CHR (57)华为GGSN9811功能描述本文是对华为GGSN9811产品功能清单的概括性描述。

SSD1289中文手册

- GD = ‘0’, G0 is 1st output Gate, Gate sequence G0, G1, G2, G3, …, G318, G319 - GD = ‘1’, G1 is 1st output Gate, Gate sequence G1, G0, G3, G2, …, G319, G318

动电路。当一个像素点=18 位时,262144 种可能的颜色可以被显示。

增压器和稳压电路 这两个功能块产生 VGH, VGOFFL, VCOM levels 和操作 LCD 所必须的

Vlcd0~63 所需电压。

震荡电路 这个模块是一个片上的低能耗的 RC 震荡电路。此震荡电路为 DC-DC 电平转

换电路提供时钟。这个时钟也用于提供显示时钟。

SSD1289 嵌入了 DC-DC 变压器和电压转换器,用于提供芯片驱动所有外部底 层元件所必需的电压。芯片包含的一个通用电压发生电路用于驱动 TFT 显示器的 反电极。另外还有一个整合的伽马控制电路,用于配合软指令以提供最大的灵活 性和最佳的显示效果。

DS1289 工作的最低电压能低到 1.16V,同时提供不同的节电模式。它适用于 任何需要长时间运行的,用便携式电池驱动的紧凑型设备。 2 特点 工作电压:VDD = 1.65V-1.95V (不规则的逻辑输入)

4 页要显示的数据形成一个 RAM 地址块存储在 GDDRAM 中。每个地址块将形 成基本的滚动地址单元。多种类型的区域滚动可以由软件根据命令“Set area Scroll” and “Set Scroll Start”设置。

Gamma(γ)/Grayscale(灰度级)电压发生器 灰度级电压电路根据灰度级γ调整电阻所设定的灰度等级产生一个 LCD 驱

绿叶特克斯顿 IM 689 电缆弯曲机操作、服务和零件说明书

SAFETY ALERT SYMBOL

Immediate hazards which, if not avoided, WILL result in severe personal injury or death.

The symbol above is used to call your attention to instructions concerning your personal safety. Watch for this symbol. It points out important safety precautions. It means “ATTENTION! Become alert! Your personal safety is involved!” Read the message that follows and be alert to the possibility of personal injury or death.

OPERATION, SERVICE AND PARTS INSTRUCTION MANUAL

880 HYDRAULIC BENDER

999 6196.2

Read and understand this material before operating or servicing this tool. Failure to understand how to safely operate this tool could result in an accident causing serious injury or death.

Greenlee Textron / Subsidiary of Textron Inc.

2

4455 Boeing Dr., Rockford, IL 61109-2988 815/397-7070

AW9818TQR_产品手册

第 1 行 LED 驱动端口 第 2 行 LED 驱动端口 第 3 行 LED 驱动端口 第 4 行 LED 驱动端口 第 5 行 LED 驱动端口 第 6 行 LED 驱动端口 第 7 行 LED 驱动端口 第 8 行 LED 驱动端口 第 9 行 LED 驱动端口 第 10 行 LED 驱动端口 第 11 行 LED 驱动端口 VBAT 电源输入引脚 第 7 列驱动 LED 扫描端口 第 6 列驱动 LED 扫描端口 第 5 列驱动 LED 扫描端口 第 4 列驱动 LED 扫描端口 第 3 列驱动 LED 扫描端口 第 2 列驱动 LED 扫描端口 第 1 列驱动 LED 扫描端口 时钟输入、输出引脚 I2C 器件地址选择 I2C 数据总线 I2C 时钟总线 地电平 VDD 电源输入引脚 外部电容引脚 中断输出引脚,低电平有效 关断控制,低电平有效 地电平

绝对最大额定值(注 1)

参数

电源电压 VDD 电源电压 VBAT SCL, SDA, SHDN, INTN, CLKIO 最大功耗 (PDmax,package@ TA=25℃)

封装热阻 θJA 最大结温 TJmax 存储温度范围 引脚温度 (焊接 10 秒) ESD 范围 (注 2) HBM,所有引脚 Latch-up

1 2 3 4 5 6 7 8

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29

引脚名称 描述

R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 VBAT C7 C6 C5 C4 C3 C2 C1 CLKIO AD SDA SCL GND VDD CAP INTN SHDN GND

y CLKIO 引脚可输出内部 OSC 时钟 (4MHz)、或选择外部输入时钟

同方ROTA综合布线产品手册(2021-01)

同方ROTA综合布线产品手册(2021-01) 同方ROTA综合布线产品手册同方ROTA综合布线产品手册2021年01月1 / 159同方ROTA综合布线产品手册目录公司简介 (4)同方股份有限公司简介 ........................................................................... .. (4)网络产品简介 ........................................................................... (5)铜缆系列 (6)屏蔽线缆 ........................................................................... ........................................................ 7 非屏蔽线缆 ........................................................................... .................................................. 12 室外非屏蔽线缆 ........................................................................... ........................................ 19 低烟无卤 ........................................................................... ...................................................... 21 大对数线缆 ........................................................................... .. (25)铜缆配线架系列 (28)屏蔽配线架 ........................................................................... .................................................. 28 非屏蔽配线架 ........................................................................... .............................................. 31 理线器............................................................................ ......................................................... 36 语音配线架 ........................................................................... .. (38)模块、面板、地插 (40)屏蔽模块 ........................................................................... ...................................................... 40 非屏蔽模块 ........................................................................... .. (43)面板 ............................................................. 49 地面插座 (57)弱电地插 ........................................................................... (57)强电地插 ........................................................................... ...................................................... 60 地插支架 ........................................................................... (63)跳线、水晶头、工具 (66)屏蔽跳线 ........................................................................... ...................................................... 66 非屏蔽跳线 ........................................................................... .................................................. 69 语音跳线 ........................................................................... (72)水晶头 (75)屏蔽水晶头 ........................................................................... .................................................. 75 非屏蔽水晶头 ........................................................................... . (76)工具 ............................................................. 79 光缆系列 (81)室内光缆 ........................................................................... (81)室外光缆 ........................................................................... ...................................................... 85 非自承式蝶型引入光缆 ........................................................................... (93)光纤配线架 (94)FP700A型光纤配线架 ........................................................................... ............................... 94 FP750A型光纤配线架 ........................................................................... ............................... 97 FP710A型光纤配线架 ........................................................................... ............................. 100 FP780A型光纤配线架 ........................................................................... .. (104)耦合器、跳线、尾纤 (107)2 / 159同方ROTA综合布线产品手册光纤耦合器 ........................................................................... ................................................ 107 光纤跳线 ........................................................................... .................................................... 111 光纤尾纤 ........................................................................... . (113)机柜系列 (115)19英寸网络机柜、服务器机柜 ........................................................................... (115)MPO系列 ........................................................ 118 电子配线架 ...................................................... 131 资质文件 (137)信息产业部报告 ........................................................................... . (139)UL认证 ........................................................................... ....................................................... 140 RoHS认证 ........................................................................... ................................................... 143 CE认证(模块、屏蔽线缆) ......................................................................... ..................... 148 外观专利证书(节选) ......................................................................... (152)成功案例汇总表 (153)3 / 159同方ROTA综合布线产品手册公司简介同方股份有限公司简介1997年6月25日,清华同方股份有限公司正式成立。

吉拉G1 230V 2067 05 2067 12 PoE 2069 05 2069 12 24V

Gira G1230 V 206705 / 206712 PoE 206905 / 206912 24 V 207705 / 207712 [ZH] 安装和操作说明书供安装人员使用重要提示:请在使用前仔细阅读。

请妥善保管,以备日后阅读。

目录1 Gira G1 的结构.........................................页码52用户界面...............................................页码6 2.1用户界面的结构.........................................页码6 2.2状态栏.................................................页码7 2.3导航栏.................................................页码7 2.4操作区域...............................................页码8 2.4.1瓷砖视图...............................................页码8 2.4.2详细视图...............................................页码9 2.5直接功能...............................................页码93设置 Gira G1............................................页码10 3.1首次基本配置...........................................页码10 3.2更新 Gira G1............................................页码10 3.3时间和日期.............................................页码10 4设置...................................................页码11 4.1系统菜单...............................................页码13 4.1.1选择直接功能...........................................页码13 4.1.2系统...................................................页码14 4.1.2.1日期/时间..............................................页码14 4.1.2.2无线配置...............................................页码15 4.1.2.3配置网络...............................................页码16 4.1.2.4网络连接方式...........................................页码17 4.1.2.5设置距离传感器.........................................页码17 4.1.2.6允许的 KNX 通信........................................页码18 4.1.3视图配置...............................................页码18 4.1.3.1选择首页...............................................页码19 4.1.3.2确定偏好...............................................页码19 4.1.3.3功能排序...............................................页码20 4.1.3.4还原默认值.............................................页码215设置 KNX 建筑功能......................................页码22 5.1配置 KNX 设备..........................................页码22 5.2KNX 功能...............................................页码23 5.3PoE 拓扑结构...........................................页码24 5.3.1主线路中的 Gira G1......................................页码24 5.3.2局部线路中的 Gira G1....................................页码26 5.4无线拓扑结构...........................................页码28 5.4.1通过 KNX IP 路由器连接基本配置计算机(建议)............页码28 5.4.2通过 KNX USB 接口连接基本配置计算机....................页码29 6操作 KNX 建筑功能......................................页码30 6.1接通(开关功能).......................................页码30 6.1.1瓷砖视图...............................................页码30 6.1.2详细视图...............................................页码31 6.2接通(按键功能).......................................页码31 6.2.1瓷砖视图...............................................页码31 6.2.2详细视图...............................................页码316.3调光...................................................页码32 6.3.1瓷砖视图...............................................页码32 6.3.2详细视图...............................................页码33 6.4百叶窗/卷帘门(分步移动)..............................页码34 6.4.1瓷砖视图...............................................页码34 6.4.2详细视图...............................................页码34 6.5百叶窗定位.............................................页码35 6.5.1瓷砖视图...............................................页码35 6.5.2详细视图...............................................页码36 6.6卷帘门定位.............................................页码37 6.6.1瓷砖视图...............................................页码37 6.6.2详细视图...............................................页码37 6.7模式分机...............................................页码38 6.7.1瓷砖视图...............................................页码38 6.7.2详细视图...............................................页码39 6.8编码器.................................................页码40 6.8.1瓷砖视图...............................................页码40 6.8.2详细视图...............................................页码40 6.9状态显示...............................................页码41 6.10室温控制器.............................................页码42 6.10.1瓷砖视图...............................................页码42 6.10.2详细视图...............................................页码42 6.11定时器.................................................页码44 6.11.1创建开关时间...........................................页码44 6.11.2删除开关时间...........................................页码45 6.11.3启动和关闭一项功能的所有开关时间.......................页码46 6.12功能文件夹.............................................页码47 7设置门通信.............................................页码48 7.1将 Gira G1 与门通信系统连接.............................页码48 7.2建立与 DCS-IP 网关的连接................................页码49 7.2.1访问数据...............................................页码50 8操作门通信系统.........................................页码51 8.1用户界面的结构.........................................页码51 8.2操作呼叫...............................................页码52 8.2.1接受呼叫...............................................页码52 8.2.2结束呼叫...............................................页码52 8.2.3再次接听呼叫...........................................页码53 8.3关闭铃声...............................................页码53 8.4开门...................................................页码53 8.5启动摄像机.............................................页码53 8.6门通信系统菜单.........................................页码54 8.6.1呼叫室外机.............................................页码54 8.6.2选择摄像机.............................................页码54 8.6.3响铃音调...............................................页码55 8.6.4开门器自动模式.........................................页码55 8.6.5访问数据...............................................页码55 8.6.6语音音量...............................................页码56 8.6.7铃声音量...............................................页码56 9天气预报...............................................页码579.1设置天气预报...........................................页码57 9.1.1添加气象站.............................................页码57 9.1.2更改气象站的顺序.......................................页码58 9.1.3删除气象站.............................................页码589.2读取天气数据...........................................页码5910附录...................................................页码60 10.1故障报警...............................................页码60 10.2通过磁铁手动重启设备...................................页码60 10.3可选符号的列表.........................................页码61 10.4Gira G1 的尺寸..........................................页码64 10.5PoE 连接模块的端子分配.................................页码6511保修.....................................................页码65Gira G1 的结构[1]触屏[2]LED[3]距离传感器[4]话筒[1]解锁口[2]声道图1正面视图图2侧面视图用户界面2.1用户界面的结构Gira G1 的用户界面分为 5 个区域:[1]状态栏 [请见 2.2][2]信息栏(显示已打开哪些应用程序)[3]导航栏 [请见 2.3][4]操作区域 [请见 2.4][5]定位帮助对于每一项可用的功能或页面,在屏幕下缘处均有一个圆形图标。

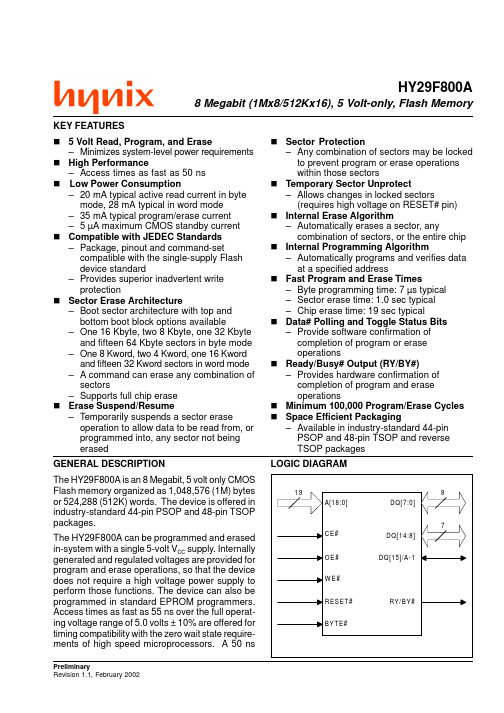

HY29F800ATG-12资料

KEY FEATURESn 5 Volt Read, Program, and Erase–Minimizes system-level power requirements n High Performance–Access times as fast as 50 ns n Low Power Consumption–20 mA typical active read current in byte mode, 28 mA typical in word mode –35 mA typical program/erase current – 5 µA maximum CMOS standby current n Compatible with JEDEC Standards–Package, pinout and command-set compatible with the single-supply Flash device standard–Provides superior inadvertent write protectionn Sector Erase Architecture–Boot sector architecture with top and bottom boot block options available–One 16 Kbyte, two 8 Kbyte, one 32 Kbyte and fifteen 64 Kbyte sectors in byte mode –One 8 Kword, two 4 Kword, one 16 Kword and fifteen 32 Kword sectors in word mode – A command can erase any combination of sectors–Supports full chip erase n Erase Suspend/Resume–Temporarily suspends a sector eraseoperation to allow data to be read from, or programmed into, any sector not being erased n Sector Protection–Any combination of sectors may be locked to prevent program or erase operations within those sectorsn Temporary Sector Unprotect–Allows changes in locked sectors(requires high voltage on RESET# pin)n Internal Erase Algorithm–Automatically erases a sector, anycombination of sectors, or the entire chip n Internal Programming Algorithm–Automatically programs and verifies data at a specified addressn Fast Program and Erase Times–Byte programming time: 7 µs typical –Sector erase time: 1.0 sec typical –Chip erase time: 19 sec typicaln Data# Polling and Toggle Status Bits–Provide software confirmation of completion of program or erase operationsn Ready/Busy# Output (RY/BY#)–Provides hardware confirmation of completion of program and erase operationsn Minimum 100,000 Program/Erase Cycles n Space Efficient Packaging–Available in industry-standard 44-pin PSOP and 48-pin TSOP and reverse TSOP packages PreliminaryRevision 1.1, February 2002GENERAL DESCRIPTIONThe HY29F800A is an 8 Megabit, 5 volt only CMOS Flash memory organized as 1,048,576 (1M) bytes or 524,288 (512K) words. The device is offered in industry-standard 44-pin PSOP and 48-pin TSOP packages.The HY29F800A can be programmed and erased in-system with a single 5-volt V CC supply. Internally generated and regulated voltages are provided for program and erase operations, so that the device does not require a high voltage power supply to perform those functions. The device can also be programmed in standard EPROM programmers.Access times as fast as 55 ns over the full operat-ing voltage range of 5.0 volts ± 10% are offered for timing compatibility with the zero wait state require-ments of high speed microprocessors. A 50 nsLOGIC DIAGRAMHY29F800A8 Megabit (1Mx8/512Kx16), 5 Volt-only, Flash Memory元器件交易网2Rev. 1.1/Feb 02HY29F800Aversion operating over 5.0 volts ± 5% is also avail-able. To eliminate bus contention, the HY29F800A has separate chip enable (CE#), write enable (WE#) and output enable (OE#) controls.The device is compatible with the JEDEC single power-supply Flash command set standard. Com-mands are written to the command register using standard microprocessor write timings, from where they are routed to an internal state-machine that controls the erase and programming circuits. De-vice programming is performed a byte at a time by executing the four-cycle Program Command.This initiates an internal algorithm that automati-cally times the program pulse widths and verifies proper cell margin.The HY29F800A ’s sector erase architecture allows any number of array sectors to be erased and re-programmed without affecting the data contents of other sectors. Device erasure is initiated by ex-ecuting the Erase Command. This initiates an in-ternal algorithm that automatically preprograms the array (if it is not already programmed) before ex-ecuting the erase operation. During erase cycles,the device automatically times the erase pulse widths and verifies proper cell margin.To protect data in the device from accidental or unauthorized attempts to program or erase the device while it is in the system (e.g., by a virus),the device has a Sector Protect function which hardware write protects selected sectors. The sector protect and unprotect features can be en-abled in a PROM programmer. Temporary Sector Unprotect, which requires a high voltage, allows in-system erasure and code changes in previously protected sectors.Erase Suspend enables the user to put erase on hold for any period of time to read data from, or program data to, any sector that is not selected for erasure. True background erase can thus be achieved. The device is fully erased when shipped from the factory.Addresses and data needed for the programming and erase operations are internally latched during write cycles, and the host system can detect completion of a program or erase operation by observing the RY/BY# pin, or by reading the DQ[7](Data# Polling) and DQ[6] (toggle) status bits.Reading data from the device is similar to reading from SRAM or EPROM devices. Hardware data protection measures include a low V CC detector that automatically inhibits write operations during power transitions.The host can place the device into the standby mode. Power consumption is greatly reduced in this mode.BLOCK DIAGRAM元器件交易网HY29F800A PIN CONFIGURATIONSCONVENTIONSUnless otherwise noted, a positive logic (active High) convention is assumed throughout this docu-ment, whereby the presence at a pin of a higher, more positive voltage (nominally 5VDC) causes assertion of the signal. A ‘#’ symbol following the signal name, e.g., RESET#, indicates that the sig-nal is asserted in a Low state (nominally 0 volts).Whenever a signal is separated into numbered bits, e.g., DQ[7], DQ[6], ..., DQ[0], the family of bits may also be shown collectively, e.g., as DQ[7:0].The designation 0xNNNN (N = 0, 1, 2, . . . , 9, A, . . . , E, F) indicates a number expressed in hexadeci-mal notation. The designation 0bXXXX indicates a number expressed in binary notation (X = 0, 1).元器件交易网3 Rev. 1.1/Feb 02HY29F800AMEMORY ARRAY ORGANIZATIONThe 1 Mbyte Flash memory array is organized into nineteen blocks called sectors (S0, S1, . . . , S18).A sector is the smallest unit that can be erased and which can be protected to prevent accidental or unauthorized erasure. See the ‘Bus Operations’and ‘Command Definitions’ sections of this docu-ment for additional information on these functions. In the HY29F800A, four of the sectors, which com-prise the boot block, vary in size from 8 to 32Kbytes (4 to 16 Kwords), while the remaining fif-teen sectors are uniformly sized at 64 Kbytes (32 Kwords). The boot block can be located at the bottom of the address range (HY29F800AB) or at the top of the address range (HY29F800AT). Table 1 defines the sector addresses and corre-sponding address ranges for the top and bottom boot block versions of the HY29F800A.元器件交易网4Rev. 1.1/Feb 02元器件交易网HY29F800A1.X indicates Don’t Care.2.Address in Byte Mode is A[18:-1].3.Address in Word Mode is A[18:0].5 Rev. 1.1/Feb 02HY29F800A1 Notes:1.L = VIL , H = VIH, X = Don’t Care, DOUT= Data Out, DIN= Data In. See DC Characteristics for voltage levels.2.Address is A[18:-1] in Byte Mode and A[18:0] in Word Mode.3.DQ[15] is the A[-1] input in Byte Mode (BYTE# = L).BUS OPERATIONSDevice bus operations are initiated through the internal command register, which consists of sets of latches that store the commands, along with the address and data information, if any, needed to execute the specific command. The command register itself does not occupy any addressable memory location. The contents of the command register serve as inputs to an internal state ma-chine whose outputs control the operation of the device. Table 2 lists the normal bus operations, the inputs and control levels they require, and the resulting outputs. Certain bus operations require a high voltage on one or more device pins. Those are described in Table 3.Read OperationData is read from the HY29F800A by using stan-dard microprocessor read cycles while placing the address of the byte or word to be read on the device’s address inputs, A[18:0] in Word mode (BYTE# = H) or A[18:-1] in Byte mode (BYTE# = L) . As shown in Table 2, the host system must drive the CE# and OE# inputs Low and drive WE# High for a valid read operation to take place. The device outputs the specified array data on DQ[7:0] in Byte mode and on DQ[15:0] in Word mode. Note that DQ[15] serves as address input A[-1] when the device is operating in Byte mode.The HY29F800A is automatically set for reading array data after device power-up and after a hard-ware reset to ensure that no spurious alteration of the memory content occurs during the power tran-sition. No command is necessary in this mode to obtain array data, and the device remains enabled for read accesses until the command register con-tents are altered.This device features an Erase Suspend mode. While in this mode, the host may read the array data from any sector of memory that is not marked for erasure. If the host attempts to read from an address within an erase-suspended sector, or while the device is performing an erase or byte/ word program operation, the device outputs sta-tus data instead of array data. After completing a programming operation in the Erase Suspend mode, the system may once again read array data with the same exceptions noted above. After com-pleting an internal program or internal erase algo-rithm, the HY29F800A automatically returns to the read array data mode.The host must issue a hardware reset or the soft-ware reset command (see Command Definitions) to return a sector to the read array data mode if DQ[5] goes high during a program or erase cycle, or to return the device to the read array data mode while it is in the Electronic ID mode.Write OperationCertain operations, including programming data and erasing sectors of memory, require the host to write a command or command sequence to the HY29F800A. Writes to the device are performed元器件交易网6Rev. 1.1/Feb 02HY29F800A1, 2Notes:1.L = VIL , H = VIH, X = Don’t Care. See DC Characteristics for voltage levels.2.Address bits not specified are Don’t Care.3.See text for additional information.4.SA = sector address. See Table 1.5.DQ[15] is the A[-1] input in Byte Mode (BYTE# = L).by placing the byte or word address on the device’s address inputs while the data to be written is input on DQ[7:0] in Byte mode (BYTE# = L) and on DQ[15:0] in Word mode (BYTE# = H). The host system must drive the CE# and WE# pins Low and drive OE# High for a valid write operation to take place. All addresses are latched on the fall-ing edge of WE# or CE#, whichever happens later. All data is latched on the rising edge of WE# or CE#, whichever happens first.The ‘Device Commands’ section of this document provides details on the specific device commands implemented in the HY29F800A.Output Disable OperationWhen the OE# input is at VIH , output data from thedevice is disabled and the data bus pins are placed in the high impedance state.Standby OperationWhen the system is not reading from or writing to the HY29F800A, it can place the device in the Standby mode. In this mode, current consump-tion is greatly reduced, and the data bus outputs are placed in the high impedance state, indepen-dent of the OE# input. The Standby mode can invoked using two methods.The device enters the CE# CMOS Standby mode if the CE# and RESET# pins are both held at VCC ± 0.5V. Note that this is a more restricted voltage range than VIH. If both CE# and RESET# are heldHigh, but not within VCC± 0.5V, the device will be in the CE# TTL Standby mode, but the standby current will be greater.The device enters the RESET# CMOS Standbymode when the RESET# pin is held at VSS± 0.5V.If RESET# is held Low but not within VSS± 0.5V, the HY29F800A will be in the RESET# TTL Standby mode, but the standby current will be greater. See Hardware Reset Operation section for additional information on the reset operation.The device requires standard access time (tCE) forread access when the device is in either of the standby modes, before it is ready to read data. If the device is deselected during erasure or pro-gramming, it continues to draw active current until the operation is completed.Hardware Reset OperationThe RESET# pin provides a hardware method ofresetting the device to reading array data. When the RESET# pin is driven Low for the minimum specified period, the device immediately termi-nates any operation in progress, tri-states the data bus pins, and ignores all read/write commands for元器件交易网7 Rev. 1.1/Feb 028Rev. 1.1/Feb 02HY29F800Athe duration of the RESET# pulse. The device also resets the internal state machine to reading array data. If an operation was interrupted by the as-sertion of RESET#, it should be reinitiated once the device is ready to accept another command sequence to ensure data integrity.Current is reduced for the duration of the RESET#pulse as described in the Standby Operation sec-tion above.If RESET# is asserted during a program or erase operation, the RY/BY# pin remains Low (busy) until the internal reset operation is complete, which re-quires a time of t READY (during Automatic Algo-rithms). The system can thus monitor RY/BY# to determine when the reset operation completes,and can perform a read or write operation t RB after RY/BY# goes High. If RESET# is asserted when a program or erase operation is not executing (RY/BY# pin is High), the reset operation is completed within a time of t RP . In this case, the host can per-form a read or write operation t RH after the RE-SET# pin returns High .The RESET# pin may be tied to the system reset signal. Thus, a system reset would also reset thedevice, enabling the system to read the boot-up firmware from the Flash memory.Sector Protect/Unprotect OperationsHardware sector protection can be invoked to dis-able program and erase operations in any single sector or combination of sectors. This function is typically used to protect data in the device from unauthorized or accidental attempts to program or erase the device while it is in the system (e.g.,by a virus) and is implemented using programming equipment. Sector unprotection re-enables the program and erase operations in previously pro-tected sectors.Table 1 identifies the nineteen sectors and the address range that each covers. The device is shipped with all sectors unprotected.The sector protect/unprotect operations require a high voltage (V ID ) on address pin A[9] and the CE#and/or OE# control pins, as detailed in Table 3.When implementing these operations, note that V CC must be applied to the device before applying V ID , and that V ID should be removed before remov-ing V CC from the device.元器件交易网9Rev. 1.1/Feb 02HY29F800AThe flow chart in Figure 1 illustrates the proce-dure for protecting sectors, and timing specifica-tions and waveforms are shown in the specifica-tions section of this document. Verification of pro-tection is accomplished as described in the Elec-tronic ID Mode section and shown in the flow chart.The procedure for sector unprotection is illustrated in the flow chart in Figure 2, and timing specifica-tions and waveforms are given at the end of this document. Note that to unprotect any sector, all unprotected sectors must first be protected prior to the first unprotect write cycle.Sectors can also be temporarily unprotected as described in the next section.Temporary Sector Unprotect Operation This feature allows temporary unprotection of pre-viously protected sectors to allow changing the data in-system. T emporary Sector Unprotect mode is activated by setting the RESET# pin to V ID . WhileFigure 2. Sector Unprotect Procedurein this mode, formerly protected sectors can be programmed or erased by invoking the appropri-ate commands (see Device Commands section).Once V ID is removed from RESET#, all the previ-ously protected sectors are protected again. Fig-ure 3 illustrates the algorithm.Electronic ID Mode OperationThe Electronic ID mode provides manufacturer and device identification and sector protection verifi-cation through identifier codes output on DQ[7:0]or DQ[15:0]. This mode is intended primarily for programming equipment to automatically match a device to be programmed with its corresponding programming algorithm. The Electronic ID infor-mation can also be obtained by the host through a command sequence, as described in the Device Commands section.Operation in the Electronic ID mode requires V ID on address pin A[9], with additional requirements元器件交易网10Rev. 1.1/Feb 02HY29F800A1.Any number of Flash array read cycles are permitted.2.Additional data cycles may follow. See text.3.Any number of Electronic ID read cycles are permitted.DEVICE COMMANDSDevice operations are initiated by writing desig-nated address and data command sequences into the device. A command sequence is composed of one, two or three of the following sub-segments:an unlock cycle , a command cycle and a data cycle . Table 4 summarizes the composition of the valid command sequences implemented in the HY29F800A, and these sequences are fully de-scribed in Table 5 and in the sections that follow.Writing incorrect address and data values or writ-ing them in the improper sequence resets the HY29F800A to the Read mode.Read/Reset 1, 2 CommandsThe HY29F800A automatically enters the Read mode after device power-up, after the RESET#input is asserted and upon the completion of cer-tain commands. Read/Reset commands are not required to retrieve data in these cases.A Read/Reset command must be issued in order to read array data in the following cases:n If the device is in the Electronic ID mode, a Read/Reset command must be written to re-turn to the Read mode. If the device was in the Erase Suspend mode when the device entered the Electronic ID mode, writing the Read/Re-set command returns the device to the Erase Suspend mode.Figure 3. Temporary Sector Unprotect for obtaining specific data items as listed in Table 2:n A read cycle at address 0xXXX00 retrieves the manufacturer code (Hynix = 0xAD).n A read cycle at address 0xXXX01 returns the device code:-HY29F800AT = 0xD6 in Byte mode, 0x22D6in Word mode.-HY29F800AB = 0x58 in Byte mode, 0x2258in Word mode.n A read cycle containing a sector address (Table 1) in A[18:12] and the address 0x02 in A[7:0]returns 0x01 if that sector is protected, or 0x00if it is unprotected.Note: When in the Electronic ID bus operation mode,the device returns to the Read mode when V ID is removed from the A[9] pin. The Read/Reset command is not re-quired in this case.n If DQ[5] (Exceeded Time Limit) goes High dur-ing a program or erase operation, writing the Read/Reset command returns the sectors to the Read mode (or to the Erase Suspend mode if the device was in Erase Suspend).The Read/Reset command may also be used to abort certain command sequences:元器件交易网11Rev. 1.1/Feb 02HY29F800AX = D o n ’t C a r e P A = A d d r e s s o f t h e d a t a t o b e p r o g r a m m e d R A = M e m o r y a d d r e s s o f d a t a t o b e r e a d P D = D a t a t o b e p r o g r a m m e d a t a d d r e s s P A R D = D a t a r e a d f r o m l o c a t i o n R A d u r i n g t h e r e a d o p e r a t i o n S A = S e c t o r a d d r e s s o f s e c t o r t o b e e r a s e d o r v e r i f i e d (s e e N o t e 3 a n d T a b l e 1).S T A T U S = S e c t o r p r o t e c t s t a t u s : 0x 00 = u n p r o t e c t e d , 0x 01 = p r o t e c t e d .N o t e s :1.A l l v a l u e s a r e i n h e x a d e c i m a l. D Q [15:8] a r e d o n ’t c a r e f o r u n l o c k a n d c o m m a n d c y c l e s .2.A l l b u s c y c l e s a r e w r i t e o p e r a t i o n s u n l e s s o t h e r w i s e n o t e d .3.A d d r e s s i s A [10:0] i n W o r d m o d e a n d A [10:-1] i n B y t e m o d e . A [18:11] a r e d o n ’t c a r e e x c e p t a s f o l l o w s :•F o r R A a n d P A , A [18:11] a r e t h e u p p e r a d d r e s s b i t s o f t h e b y t e t o b e r e a d o r p r o g r a m m e d .•F o r t h e s i x t h c y c l e o f S e c t o r E r a s e , S A = A [18:12] a r e t h e s e c t o r a d d r e s s o f t h e s e c t o r t o b e e r a s e d .•F o r t h e f o u r t h c y c l e o f S e c t o r P r o t e c t V e r i f y , S A = A [18:12] a r e t h e s e c t o r a d d r e s s o f t h e s e c t o r t o b e v e r i f i e d .4.T h e E r a s e S u s p e n d c o m m a n d i s v a l i d o n l y d u r i n g a s e c t o r e r a s e o p e r a t i o n . T h e s y s t e m m a y r e a d a n d p r o g r a m i n n o n -e r a s i n g s e c t o r s , o r e n t e r t h e E l e c t r o n i c I D m o d e , w h i l e i n t h e E r a s e S u s p e n d m o d e .5.T h e E r a s e R e s u m e c o m m a n d i s v a l i d o n l y d u r i n g t h e E r a s e S u s p e n d m o d e .6.T h e s e c o n d b u s c y c l e i s a r e a d c y c l e .7.T h e f o u r t h b u s c y c l e i s a r e a d c y c l e .8.E i t h e r c o m m a n d s e q u e n c e i s v a l i d . T h e c o m m a n d i s r e q u i r e d o n l y t o r e t u r n t o t h e R e a d m o d e w h e n t h e d e v i c e i s i n t h e E l e c t r o n i c I D c o m m a n d m o d e o r i f D Q [5] g o e s H i g h d u r i n g a p r o g r a m o r e r a s e o p e r a t i o n . I t i s n o t r e q u i r e d f o r n o r m a l r e a d o p e r a t i o n s .元器件交易网12Rev. 1.1/Feb 02HY29F800Aquence should be reinitiated once the reset op-eration is complete.Programming is allowed in any sequence. Only erase operations can convert a stored “0” to a “1”.Thus, a bit cannot be programmed from a “0” back to a “1”. Attempting to do so will set DQ[5] to “1”,and the Data# Polling algorithm will indicate that the operation was not successful. A Read/Reset command or a hardware reset is required to exit this state, and a succeeding read will show that the data is still “0”.Figure 4 illustrates the procedure for the Byte/Word Program operation.Chip Erase CommandThe Chip Erase command sequence consists of two unlock cycles, followed by the erase command,two additional unlock cycles and then the chip erase data cycle. During chip erase, all sectors of the device are erased except protected sectors.The command sequence starts the Automatic Erase algorithm, which preprograms and verifies the entire memory, except for protected sectors,for an all zero data pattern prior to electrical erase.The device then provides the required number of internally generated erase pulses and verifies cell erasure within the proper cell margins. The host system is not required to provide any controls or timings during these operations.Figure 4. Programming Proceduren In a Sector Erase or Chip Erase command se-quence, the Read/Reset command may be written at any time before erasing actually be-gins, including, for the Sector Erase command,between the cycles that specify the sectors to be erased (see Sector Erase command de-scription). This aborts the command and re-sets the device to the Read mode. Once era-sure begins, however, the device ignores Read/Reset commands until the operation is com-plete.n In a Program command sequence, the Read/Reset command may be written between the sequence cycles before programming actually begins. This aborts the command and resets the device to the Read mode, or to the Erase Suspend mode if the Program command se-quence is written while the device is in the Erase Suspend mode. Once programming begins, however, the device ignores Read/Re-set commands until the operation is complete.n The Read/Reset command may be written be-tween the cycles in an Electronic ID command sequence to abort that command. As described above, once in the Electronic ID mode, the Read/Reset command must be written to re-turn to the Read mode.Byte/Word Program CommandThe host processor programs the device a byte or word at a time by issuing the Program command sequence shown in Table 5. The sequence be-gins by writing two unlock cycles, followed by the Program setup command and, lastly, a data cycle specifying the program address and data. This initiates the Automatic Programming algorithm,which provides internally generated program pulses and verifies the programmed cell margin.The host is not required to provide further controls or timings during this operation. When the Auto-matic Programming algorithm is complete, the device returns to the Read mode. Several meth-ods are provided to allow the host to determine the status of the programming operation, as de-scribed in the Write Operation Status mands written to the device during execution of the Automatic Programming algorithm are ig-nored. Note that a hardware reset immediately terminates the programming operation. To ensure data integrity, the aborted program command se-元器件交易网13Rev. 1.1/Feb 02HY29F800ACommands written to the device during execution of the Automatic Erase algorithm are ignored. Note that a hardware reset immediately terminates the erase operation. To ensure data integrity, the aborted Chip Erase command sequence should be reissued once the reset operation is complete.When the Automatic Erase algorithm is finished,the device returns to the Read mode. Several methods are provided to allow the host to deter-mine the status of the erase operation, as de-scribed in the Write Operation Status section.Figure 5 illustrates the Chip Erase procedure.Sector Erase CommandThe Sector Erase command sequence consists of two unlock cycles, followed by the erase com-mand, two additional unlock cycles and then the sector erase data cycle, which specifies which sector is to be erased. As described later in this section, multiple sectors can be specified for era-sure with a single command sequence. During sector erase, all specified sectors are erased se-quentially. The data in sectors not specified for erasure, as well as the data in any protected sec-tors, even if specified for erasure, is not affected by the sector erase operation.The Sector Erase command sequence starts the Automatic Erase algorithm, which preprograms and verifies the specified unprotected sectors for an all zero data pattern prior to electrical erase.The device then provides the required number of internally generated erase pulses and verifies cell erasure within the proper cell margins. The hostFigure 5. Chip Erase Proceduresystem is not required to provide any controls or timings during these operations.After the sector erase data cycle (the sixth bus cycle) of the command sequence is issued, a sec-tor erase time-out of 50 µs, measured from the rising edge of the final WE# pulse in that bus cycle,begins. During this time, an additional sector erase data cycle, specifying the sector address of an-other sector to be erased, may be written into an internal sector erase buffer. This buffer may be loaded in any sequence, and the number of sec-tors specified may be from one sector to all sec-tors. The only restriction is that the time between these additional data cycles must be less than 50µs, otherwise erasure may begin before the last data cycle is accepted. To ensure that all data cycles are accepted, it is recommended that host processor interrupts be disabled during the time that the additional cycles are being issued and then be re-enabled afterwards.Note: The device is capable of accepting three ways of invoking Erase Commands for additional sectors during the time-out window. The preferred method, described above, is the sector erase data cycle after the initial six bus cycle command sequence. However, the device also accepts the following methods of specifying additional sectors during the sector erase time-out:n Repeat the entire six-cycle command sequence, speci-fying the additional sector in the sixth cycle.n Repeat the last three cycles of the six-cycle command sequence, specifying the additional sector in the third cycle.If all sectors scheduled for erasing are protected,the device returns to reading array data after ap-proximately 100 µs. If at least one scheduled sec-tor is not protected, the erase operation erases the unprotected sectors, and ignores the command for the scheduled sectors that are protected.The system can monitor DQ[3] to determine if the 50 µs sector erase time-out has expired, as de-scribed in the Write Operation Status section. If the time between additional sector erase data cycles can be insured to be less than the time-out, the system need not monitor DQ[3].Any command other than Sector Erase or Erase Suspend during the time-out period resets the device to reading array data. The system must then rewrite the command sequence, including any additional sector erase data cycles. Once the sec-tor erase operation itself has begun, only the Erase元器件交易网。

L9814 L9815产品型号系列用户手册说明书

97

0720716 14.5 0.5709 95 169 97 15

0720722 15.0 0.5906 98

98

0720739 15.5 0.6102 102

104

1489954 5/8 0.6250 104 178 105 16

0720745 16.0 0.6299 104

105

! WARNING: Cancer -

CARBIDE DRILLS

Standard Drilling Conditions

LIST 9814, 9815

Work Material Speed (SFM)

Cast Irons / Alloy Steels Mold Steels Hardened Steels Ductile Cast

Carbon Steels (20-30 HRC) (30-35 HRC) (40-50 HRC ) Irons

3

0.118 12700 0.003 10600 0.002 7400 0.002 5350 0.002 10600 0.002 6000 0.003 3000 0.002 16200 0.005 14800 0.004

4

0.157 9000 0.004 7500 0.003 5200 0.002 3800 0.002 7900 0.002 4200 0.003 2200 0.002 12100 0.006 11100 0.005

0720671 12.5 0.4921 82

84

1489931 1/2 0.5000 85 153 86 13

0720688 13.0 0.5118 86

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

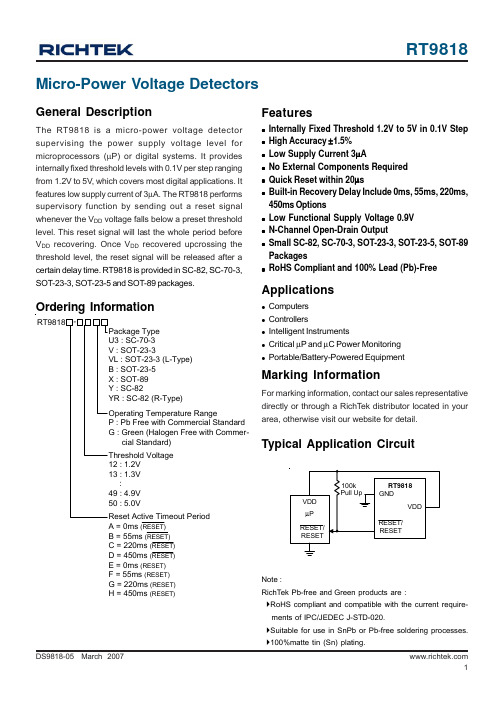

DS9818-05 March 2007

Features

z Internally Fixed Threshold 1.2V to 5V in 0.1V Step z High Accuracy ±1.5% z Low Supply Current 3μA z No External Components Required z Quick Reset within 20μs z Built-in Recovery Delay Include 0ms, 55ms, 220ms,

元器件交易网

RT9818

Micro-Power Voltage Detectors

General Description

The RT9818 is a micro-power voltage detector supervising the power supply voltage level for microprocessors (μP) or digital systems. It provides internally fixed threshold levels with 0.1V per step ranging from 1.2V to 5V, which covers most digital applications. It features low supply current of 3μA. The RT9818 performs supervisory function by sending out a reset signal whenever the VDD voltage falls below a preset threshold level. This reset signal will last the whole period before VDD recovering. Once VDD recovered upcrossing the threshold level, the reset signal will be released after a certain delay time. RT9818 is provided in SC-82, SC-70-3, SOT-23-3, SOT-23-5 and SOT-89 packages.

450ms Options z Low Functional Supply Voltage 0.9V z N-Channel Open-Drain Output z Small SC-82, SC-70-3, SOT-23-3, SOT-23-5, SOT-89

Packages z RoHS Compliant and 100% Lead (Pb)-Free

RT9818

Absolute Maximum Ratings (Note 1)

z Terminal Voltage (with Respect to GND)

VDD ------------------------------------------------------------------------------------------------------------------------ −0.3V to 6.0V z All Other Inputs -------------------------------------------------------------------------------------------------------- −0.3V to VDD+0.3V

`Suitable for use in SnPb or Pb-free soldering processes. `100%matte tin (Sn) plating.

1

元器件交易网

RT9818

Pin Configurations

GND

SOT-23-3 (L-Type)

NC

NC

5

4

123

RESET/ VDD GND RESET

SOT-23-5

1

2

3

RESET/ VDD GND RESET

SOT-89

Note : There is no pin1 indicator on top mark for SC-82 type, and pin 1 will be lower left pin when reading top mark from left to right. Pin2 of SC-82 is wider than other pins.

SC-70 / SC-82 ---------------------------------------------------------------------------------------------------------- 0.25W SOT-23-3 ---------------------------------------------------------------------------------------------------------------- 0.4W SOT-23-5 ---------------------------------------------------------------------------------------------------------------- 0.4W SOT-89 ------------------------------------------------------------------------------------------------------------------- 0.55W z Package Thermal Resistance (Note 4) SC-70 / SC-82, θJA ---------------------------------------------------------------------------------------------------- 400°C/W SOT-23-3, θJA ----------------------------------------------------------------------------------------------------------- 250°C/W SOT-23-5, θJA ----------------------------------------------------------------------------------------------------------- 250°C/W SOT-89, θJA ------------------------------------------------------------------------------------------------------------- 180°C/W z Lead Temperature (Soldering, 10sec.) ---------------------------------------------------------------------------- 260°C

Function Block DiagramVFra bibliotekDVSET

CMP

Timer

Threshold Voltage Setting

POR

Power On Reset

RESET/ RESET

N MOS

GND

2

DS9818-05 March 2007

元器件交易网

z Storage Temperature Range ---------------------------------------------------------------------------------------- −65°C to 125°C

z ESD Susceptibility (Note 2) HBM (Human Body Mode) ------------------------------------------------------------------------------------------ 2kV MM (Machine Mode) -------------------------------------------------------------------------------------------------- 200V

z Input Current, IVDD ----------------------------------------------------------------------------------------------------- 20mA z Power Dissipation, PD @ TA = 25°C

NC

4

3

1

2

RESET/ RESET

VDD

SC-82

RESET/

RESET

NC

4

3

1

2

VDD

GND

SC-82 (R-Type)

(TOP VIEW)

VDD

3

1

2

GND

RESET/ RESET

SC-70-3

VDD

3

1

2

RESET/ RESET

GND

SOT-23-3

VDD

3

1

2

GND

RESET/ RESET

Typical Application Circuit

VDD μP

RESET/ RESET