45纳米8亿个晶体管意味着什么?

纳米技术在通信领域的应用

纳米技术在通信领域的应用科学的发展速度,快得让人有些匪夷所思。

就中国来讲,在49年新中国成立前,中国一直都处于或大或小的战争中。

然而战争,就双方的武器装备,其悬殊之大,真让人望而胆怯。

在敌人的飞机大炮前,中国人有的只是大刀和步枪。

新中国成立后毛主席的一句话更说明了当时落后的情景,“现在我们能造什么?一辆汽车、一架飞机、一辆坦克?一辆拖拉机都不能造”。

再回首,那也是往事幕幕。

但是,时隔不久,现在的中国,不说汽车、拖拉机,不说飞机、坦克、大炮,就连眼睛看不到的物质世界都已早有所涉及。

观看遥远的星空,研制细小的纳米材料,还在这些领域取得了辉煌的成绩。

就纳米技术,纳米材料来说。

中国已在该领域投入了相当的资源,有些项目已走到了世界的前列。

纳米,其英文名是Nanometer,它是一个长度单位,1nm=10^-9m.约相当于45个原子串起来那么长,常被用于表示光的波长。

纳米计算机能够把建立在大量信息处理基础上的超高分辨合成孔径雷达,放到卫星上进行高精度的对地侦察,对合成孔径雷达来说,要获取高分辨率图像的关键是数字信息处理技术。

由于合成孔径雷达的数据率非常高,而成像处理过程又相当复杂,其数据如果要求实时计算出图像,就要求运算速度非常高。

这应用硅集成电路是达不到的,只能用纳米计算机来实现。

应用纳米电子学还可以提高光探测器、传感器和激光器的性能。

利用纳米电子学与纳米机械相结合,可以制成微机系统和微型机器人。

日本已经研制成直径仅为1—2mm的静电发动机和米粒大小的汽车。

德国已研制成功一架肉眼几乎看不见的直升飞机。

由于纳米技术是一门涉及电子、物理、化学、生物、医学、材料和机械等学科的高精尖技术,但目前还不是很成熟。

到2015年能制成单电子晶体管集成电路,从而促使单量子计算机、量子波计算机及单量子通信机和量子波通信的实现。

我们知道,世间物质按照导电情况分为导电体和非导电体(绝缘体)两大类。

纳米技术能使物质的导电状态发生质的飞跃。

半导体制程及摩尔定律

神秘的处理器制程工艺摩尔定律指导集成电路(IC,Integrated Circuit)工业飞速发展到今天已经40多年了。

在进入21世纪的第8个年头,各类45nm芯片开始批量问世,标志着集成电路工业终于迈入了低于50nm的纳米级阶段。

而为了使45nm工艺按时“顺产”,保证摩尔定律继续发挥作用,半导体工程师们做了无数艰辛的研究和改进—这也催生了很多全新的工艺特点,像大家耳熟能详的High-K、沉浸式光刻等等。

按照业界的看法,45nm工艺的特点及其工艺完全不同于以往的90nm、65nm,反而很多应用在45nm制程工艺上的新技术,在今后可能贯穿到32nm甚至22nm阶段。

今天就让我们通过一个个案例,来探索一下将伴随我们未来5年的技术吧。

你能准确说出45nm是什么宽度吗?得益于厂商与媒体的积极宣传,就算非科班出身,不是电脑爱好者的大叔们也能知道45nm比65nm更加先进。

但如果要细问45nm是什么的长度,估计很多人都难以给出一个准确的答案。

而要理解这个问题,就要从超大规模集成电路中最基本的单元—MOS(Metal Oxide Semiconductor金属氧化物半导体)晶体管说起。

我们用半导体制作MOS管就是利用其特殊的导电能力来传递0或者1的数字信号。

在栅极不通电的情况下,源区的信号很难穿过不导电的衬底到达漏区,即表示电路关闭(数字信号0);如果在栅极和衬底间加上电压,那么衬底中的电荷就会在异性相吸的作用下在绝缘氧化层下大量聚集,形成一条细窄的导电区,使得源区和漏区导通,那么电流就可以顺利从源区传递到漏区了(信号1)。

这便是MOS最基本的工作原理。

在一块高纯硅晶圆上(在工艺中称为“P型半导体衬底”)通过离子扩散的方法制作出两个N型半导体的阱——通俗地讲P型是指带正电的粒子较多,N型则是带负电的粒子比较多。

再通过沉积、光刻、氧化、抛光等工艺制造成如图中所示的MOS管,两个阱的上方分别对应源区(source)和漏区(drain),中间的栅区(gate)和下方的衬底中间用一层氧化绝缘层隔开。

从10微米到45纳米—英特尔45nm+High-K技术解析

的英 特 尔 3 6微 处 理 器 问世 ,包 括 8

2 . 个 晶体 管 ,也 是 15微 米 制 75万 .

程 技术

图 7Itl 0 0处理 器 e88 n 6 米制 程技术 微

5 I e 4 6 X 理 器 。 微 米 .n l 8 D 处 t 1 制程 技 术 ( 图 1 ) 如 0

7 ne P nim P o 理 器 , .Itl e t r 处 u

先后采用 06 米制程技术和 03 .微 .5

微 米 制程 技术 ( 图 1 ) 如 2

19 9 5年 1 ,英 特 尔 发 布 的 1月 P nim r e t P o处理 器 的 晶体 管 数 量升 u

尔 研 制成 功 了P S MO 硅栅 晶体 管 这 些 晶体 管 继 续 使 用传 统 的二 氧 化 硅

栅 介 质 ,最 大 的改 进 是 引 入 了新 的 多晶 硅栅 电极 。此 后 的 I tl 0 8 ne 8 0 处 理 器 依 然沿 用 了 1 米技 术 ,但 是 0微

集成 度 达到 了 3 0 5 0左 右 :

日 英特 尔 发 布迅 驰移 动 技术 平 台 , 其 中包 括 了英 特 尔 最 新 的移 动 处 理 器 P nim e t M 该 处理 器 采 用 了0 1 u .3

I tl 0 0处理 器 。 ne 0 0 理 器 ne 8 8 Itl 8 处 8

1 8 年4 , 特 尔发 布 了I tl 99 月 英 ne

46 8 DX处 理 器 这 款 处理 器 采 用 了 1

微 米 制程 技 术 ,所 包 含 的 晶 体 管数

量 达 到 了 l 8万个 。随 后 的几 年 间 , l

维普资讯

摩尔定律及其局限性对微处理器的影响

摩尔定律及其局限性对微处理器的影响一摩尔定律的来历摩尔定律是指集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

“摩尔定律”是由英特尔名誉董事长戈登·摩尔提出来的。

1965年,戈登·摩尔在准备一个关于计算机存储器发展趋势的报告时,整理了一份数据资料,结果却意外的发现了一个惊人的趋势。

每个新芯片大体上包含其之前版本的容量的晶体管,而且每个芯片的产生都是在前一个芯片产生后的18到24个月内。

这个趋势如果继续,计算能力相对于时间周期将会呈指数上升。

摩尔的观察资料,就是现在所谓的Moore定律,所阐述的趋势一直延续至今,且仍依然十分的准确。

人们还发现这不光适用于对存储器芯片的描述,也精确地说明了处理机能力和磁盘驱动器存储容量的发展。

该定律成为许多工业对于性能预测的基础。

在过去的三十余年的时间里,芯片上的晶体管数量增加了上万倍,1971年推出的第一款4004仅仅拥有2300个晶体管,而在今天45纳米级的“上海”处理器已经出现。

由于高纯硅的独特性,集成度越高,晶体管的价格越便宜,这样也就引出了摩尔定律的经济学效益,在20世纪60年代初,一个晶体管要10美元左右,但随着晶体管越来越小,直小到一根头发丝上可以放1000个晶体管时,每个晶体管的价格只有千分之一美分。

据有关统计,按运算10万次乘法的价格算,IBM704电脑为1美元,IBM709降到20美分,而60年代中期IBM耗资50亿研制的IBM360系统电脑已变为3.5美分。

到底什么是"摩尔定律'"?归纳起来,主要有以下三种"版本":1、集成电路芯片上所集成的电路的数目,每隔18个月就翻一番。

2、微处理器的性能每隔18个月提高一倍,而价格下降一半。

3、用一个美元所能买到的电脑性能,每隔18个月翻两番。

以上几种说法中,以第一种说法最为普遍,第二、三两种说法涉及到价格因素,其实质是一样的。

摩尔定律能走多远

对于计算能力的渴求得到满足,这是全球人们新增的计算能力 到了2602 MIPS/p,如果有人怀疑我们的计算能力的话,可以看 看打开笔记本和关闭笔记本要花费多少的时间才能真正打开、 关闭,就能知道具体的答案。 还有,我们认为未来的互联网将是嵌入式的互联网。最开始 的时候是人机对话,可以说地址是以人为单位的。今后不断地发 展,由于摩尔定律的不断应用,大量的对话像我们知道的不再是 需要人的对话了,这才有我们今天讨论IP地址不够用的问题。 我们认为在将来,可能会有150亿个互联网的设备需要在 网络上连接。从这里来看,更多的设备意味着有更多的晶体管。 以2004年来讲,全球人均拥有晶体管的数量已经达到了5千亿 个。所以,我们认为高计算量的需求远远没有达到极限。 同时,我们也认识到并不是在每一个场合都需要这么高的 计算量。但在我们追求摩尔定律的时候发现,当我们不断缩小集 成电路晶体管体积的时候,我们还发现带来了其它的新的很好 的性能。比如在2005年,我们把集成电路65纳米缩小到45纳 米,到2007年,我们发现不仅仅是晶体管的密度提高了两倍,切

40年。彳

(090418-4975)

权,要求N,I.I’不管盈利与否都布署删,NrI-I'已为此投资 府的津贴达到农村布署硎成本的l,3。E—Europe战略重

2000亿美元。政府给予加快折旧政策,并通过无息贷款支持,政 点—一建设更快速的互联网,以竞争价格提供广泛可用的宽带 接人。瑞典政府在2001—2007年已通过补助和税收激励提供了 8.2亿美元鼓励宽带网建设,2008年再提供5亿美元用于农村 网络,相当于50%的成本。美国国家宽带发展战略是2010年实 现一亿家庭用100 Mb/s上网,将来可扩展到1 Gbps。美国有人 提出“宽带应当是本世纪国家的需要,就像在上世纪将人送上月 球那样重要”。美国宽带化估计城市每户需250美元,农村每户 需1100美元,美国有1.15亿户,目前还有9700万户美国mF建议联邦政府、州

纳米

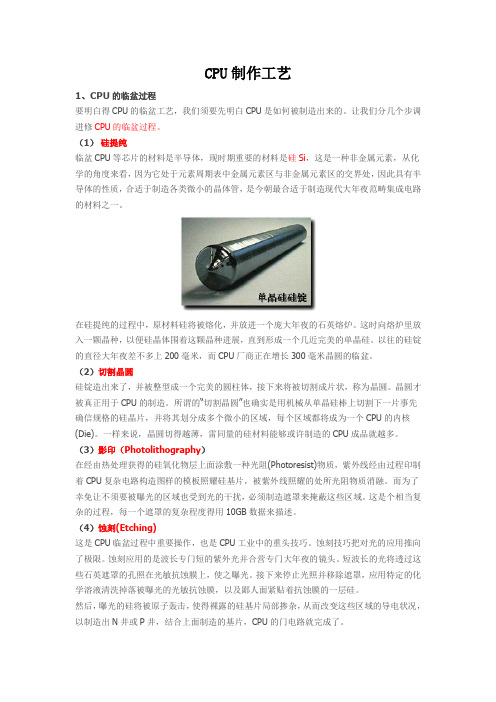

纳米颗粒在显微镜下观测,颗粒移动至左端代表数据 0,移动至右端代表数据 1

如果只是让纳米微粒随意移动, 要实现存储也相当困难。 所幸的是, 根据加电时间长短, 纳米微粒在纳米管中能提供阶段级的移动。当我们将 2V 电压以 20 纳秒的速度施加时,纳 米微粒移动的距离正好是 3 纳米。这样一来,我们只要掌握电流强度和通电时间,就能精 确移动纳米微粒。通过脉冲电流,更可以让纳米微粒持续地运动。

根据施加电压的不同,纳米粒子的运动速度也大不相同。 而通过变换电流方向,则能左右纳米粒子的移动方向。

在存储单元的内部结构上, 纳米存储器实际上就是一个将纳米颗粒封装到多层碳纳米管之中 的异质纳米存储结构。要制造它,我们需要让纳米颗粒和纳米管在 1000℃高温下穿过氩气 和处于高温分解状态的二茂铁之中, 然后再通过超声波振动将包含有纳米颗粒的纳米管扩散 到聚丙烯基板上。

间的连线宽度为90纳米。 我们知道, 1微米相当于1/60头发丝大小, 经过计算我们可以算出, 0.045微米(45纳米)相当于1/1333头发丝大小。可别小看这1/1333头发丝大小,这微小的 连线宽度决定了CPU的实际性能, CPU生产厂商为此不遗余力地减小晶体管间的连线宽度, 以 提高在单位面积上所集成的晶体管数量。采用45纳米制造工艺之后,与65纳米工艺相比,绝 对不是简单地令连线宽度减少了20纳米,而是芯片制造工艺上的一个质的飞跃。

整个纳米管的电阻变化,也因此产生了一致性。换句话说,纳米存储单元中用电压控制 纳米颗粒的位置变化写入数据后,将会直接导致电阻变化。也正因为如此,人们才能轻易的 在纳米管上写入读取数据。 在整个装置中, 最关键的一点在于如何让这些纳米颗粒能轻松地 被人们所随意移动, 以及如何无损的在不影响纳米颗粒位置状态的情况下获得它们的精确定 位。 更重要的是, 研究人员还希望能找到简单直观的移动和检测纳米颗粒位置的方法—要是 动辄就要动用电子显微镜,那这样的存储设备注定无法走出实验室。 四、总结 纳米技术从诞生至今已有 20 多 个春秋,在这期间,我国对纳米技术的重要性已经有 较高的认识,想方设法从经费上给予一定的支持。但尽管如此,我国通过这些项目对纳米技 术领域的研究与发达国家相比差距是很大的。不过,我们不应灰心丧气,因为我国具有一支 精干的纳米科研队伍, 并于近些年在纳米技术所涉及的不同领域中作出了卓越的成果, 这些 都是我们应该值得骄傲和自豪的。我们要抓住机遇,不畏挑战,拿出我们的耐心,信心,精 力和智慧,发展我国的纳米科技,使其屹立与世界不败之林。

45纳米技术的选择

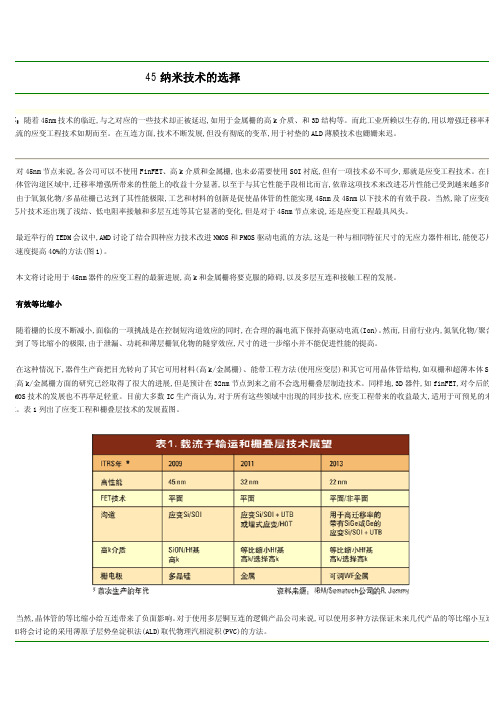

45 纳米技术的选择摘要:随着 45nm 技术的临近,与之对应的一些技术却正被延迟,如用于金属栅的高 k 介质、和 3D 结构等。

而此工业所赖以生存的,用以增强迁移率和驱 动电流的应变工程技术如期而至。

在互连方面,技术不断发展,但没有彻底的变革,用于衬垫的 ALD 薄膜技术也姗姗来迟。

对 45nm 节点来说,各公司可以不使用 FinFET、高 k 介质和金属栅,也未必需要使用 SOI 衬底,但有一项技术必不可少,那就是应变工程技术。

在目前 的晶体管沟道区域中,迁移率增强所带来的性能上的收益十分显著,以至于与其它性能手段相比而言,依靠这项技术来改进芯片性能已受到越来越多的重 。

由于氧氮化物/多晶硅栅已达到了其性能极限,工艺和材料的创新是促使晶体管的性能实现 45nm 及 45nm 以下技术的有效手段。

当然,除了应变硅以 芯片技术还出现了浅结、低电阻率接触和多层互连等其它显著的变化,但是对于 45nm 节点来说,还是应变工程最具风头。

最近举行的 IEDM 会议中,AMD 讨论了结合四种应力技术改进 NMOS 和 PMOS 驱动电流的方法,这是一种与相同特征尺寸的无应力器件相比,能使芯片的 整体速度提高 40%的方法(图 1)。

本文将讨论用于 45nm 器件的应变工程的最新进展,高 k 和金属栅将要克服的障碍,以及多层互连和接触工程的发展。

有效等比缩小 随着栅的长度不断减小,面临的一项挑战是在控制短沟道效应的同时,在合理的漏电流下保持高驱动电流(Ion)。

然而,目前行业内,氮氧化物/聚合硅 栅达到了等比缩小的极限,由于泄漏、功耗和薄层栅氧化物的隧穿效应,尺寸的进一步缩小并不能促进性能的提高。

在这种情况下,器件生产商把目光转向了其它可用材料(高 k/金属栅)、能带工程方法(使用应变层)和其它可用晶体管结构,如双栅和超薄本体 SOI 虽然高 k/金属栅方面的研究已经取得了很大的进展,但是预计在 32nm 节点到来之前不会选用栅叠层制造技术。

晶体管技术综述

晶体管技术综述作者:叶剑来源:《中国新通信》 2018年第4期晶体管的发明奠定了现代电子技术的基础,由晶体管引领的信息技术掀起了近代社会的第三次科技革命。

一、晶体管技术的快速发展1947 年美国贝尔实验室的三位科学家肖克利博士、布拉顿博士和巴丁博士,在导体电路中进行半导体锗晶体把声音信号放大的实验时惊奇地发现,在他们发明的器件中通过的一部分微量电流竟然可控制另一部分流过的大得多的电流,因而产生了放大效应。

这个器件就是——晶体管。

三位科学家因此共同荣获1956 年诺贝尔物理学奖。

1949 年肖克利博士研究成功了面结型晶体管,并于1951 年获得了美国第2569347 号专利“使用半导体材料的电路元件”。

其他改进还包括用硅代替锗,现在的晶体管大部分仍是这种面结型晶体管。

为避免遭受美国司法部的反垄断指控,贝尔实验室于1952 年向其他同行开放了该专利授权许可。

1960 年,贝尔实验室的Kahng 和Atalla 构造了第一个金属- 氧化物- 半导体晶体管(简称MOS 管),绝缘栅极场效应晶体管的一种。

1962 年,在RCA 器件集成研究组工作的Stanley,Heiman 和Hofstein 等人发现,可以通过扩散与热氧化在硅基板上形成导电带、高阻沟道区以及氧化层绝缘层来构筑晶体管,于是他们发明了第一个商业MOS 管,并获得了美国第3296508 号专利。

Hofstein 等在 1 平方英寸的单晶硅基板上制作了2000 个器件,发现95% 以上的器件工作良好。

MOS 管的出现简化了晶体管的制作工艺,提高了器件的稳定性和集成度,降低了制作成本。

因为制造成本低廉与使用面积较小、高整合度的优势,MOS 管在大型、超大型集成电路的领域里得到广泛应用。

二、晶体管技术的重要革新随着1965 年摩尔定律的提出,虽然MOS 晶体管的集成度和性能得到了快速提高,但也遇到了不少问题。

MOS 晶体管的硅材料中,空穴迁移率仅是电子迁移率的1/3 左右,为了使NMOS 和PMOS 的驱动电流基本一致,必须增大PMOS器件的宽长比,这样会影响电路的速度和集成度,降低电路的整体性能。

摩尔定律

发现人物

戈登·摩尔(Gordon Moore,1929-):英特尔公司(Intel)的创始人之一。 1929年1月3日,戈登·摩尔出生在加州旧金山的佩斯卡迪诺。父亲没有上过多少学,17 岁就开始养家,做一个

从技术的角度看,随着硅片上线路密度的增加,其复杂性和差错率也将呈指数增长,同 时也使全面而彻底的芯片测试几乎成为不可能。一旦芯片上线条的宽度达到纳米(10-9米) 数量级时,相当于只有几个分子的大小,这种情况下材料的物理、化学性能将发生质的变化, 致使采用现行工艺的半导体器件不能正常工作,摩尔定律也就要走到尽头。

发现背景

早在1959年,美国著名半导体厂商仙童公司首先推出了平面型晶体管,紧接着于1961 年又推出了平面型集成电路。这种平面型制造工艺是在研磨得很平的硅片上,采用一种所谓 “光刻”技术来形成半导体电路的元器件,如二极管、三极管、电阻和电容等。

只要“光刻”的精度不断提高,元器件的密度也会相应提高,从而具有极大的发展潜力。 因此平面工艺被认为是“整个半导体的工业键”,也是摩尔定律问世的技术基础。

从经济的角度看,正如摩尔第二定律所述,20-30亿美元建一座芯片厂,线条尺寸缩小 到0.1微米时将猛增至100亿美元,比一座核电站投资还大。由于花不起这笔钱,越来越多 的公司退出了芯片行业。

物理学家加来纪雄(Michio Kaku)是纽约城市大学一名理论物理学教授,称摩尔定律 在叱咤芯片产业47年风云之久后,正日渐走向崩溃。这将对计算机处理进程产生重大影响。 在未来十年左右的时间内,摩尔定律就会崩溃,单靠标准的硅材料技术,计算能力无法维持 快速的指数倍增长。

Penryn架构

Penryn架构I n t e l基于45纳米技术处理器的开发代号。

采用了45纳米高-k制造技术(采用铬合金高-K与金属栅极晶体管设计),并对酷睿微体系结构进行了增强。

45n m P e n r y n家族包含了3个产品线共7名成员,包括有双核心桌面处理器W o l f d a t e、四核心桌面处理器Yo r k f i e l d、双核心移动处理器P e n r y n、双核心X e o n D P处理器W o l f d a t e D P、四核心X e o n D P处理器H a r p e r t o w n、双核心X e o n M P处理器D u n n i n g t o n D C及四核心X e o n M P处理器D u n n i n g t o n Q C。

从架构上看,除了45n m工艺带来的电气改进之外新的P e n r y n微架构主要有5方面的改进:1.I n t e l W i d e D y n a m i c E x e c u t i o n(I n t e l宽动态执行)方面的改进着实从基础上提升了处理器的运算性能,包括快速16进制除法器、更快速的操作系统基础支持、增强的I n t e l虚拟化技术三个部分。

2.I n t e l A d v a n c e d S m a r t C a c h e(I n t e l先进智能缓存)则进一步提升了缓存性能,以符合未来多核心的趋势,其包括了更大容量的缓存以及更多路的缓存关联。

3.I n t e l S m a r t M e m o r y A c c e s s(I n t e l智能内存存取)提升了装载数据的速度,包括强化的存储转发结构和更高的总线带宽设计。

4.I n t e l A d v a n c e d D i g i t a l M e d i a B o o s t(I n t e l先进数字媒体增强)则是对数字媒体的一系列优化、增强,包括了S S E4指令集的加入,以及全新的S u p e r S h u ff l e E n g i n e超级传送引擎。

纳米工艺

Intel在IDFU制造过程当中工艺非常复杂的一个步骤,其过程就是使用一定波长的光在感光层中刻出相应的刻痕,由此改变该处材料的化学特性。这项技术对于所用光的波长要求极为严格,需要使用短波长的紫外线和大曲率的透镜,刻蚀过程还会受到晶圆上的污点的影响。每一步刻蚀都是一个复杂而精细的过程,设计每一步过程的所需要的数据量都可以用10GB的单位来计量,而且制造每块处理器所需要的刻蚀步骤都超过20步。制作工艺对于光刻蚀的影响十分巨大,这也就是CPU制造商疯狂追求制作工艺的最终原因。

cpu纳米 cpu纳米是什么意思

1.制作工艺的重要性

早期的微处理器都是使用0.5微米工艺制造出来的,随着CPU频率的增加,原有的工艺已无法满足产品的要求,这样便出现了0.35微米以及0.25微米工艺,不久以后,0.18微米、0.13微米以及90纳米制造的处理器产品也相继面世。另外一方面,早期芯片内部都是使用铝作为导体,但是由于芯片速度的提高,芯片面积的缩小,铝线已经接近其物理性能极限,所以芯片制造厂商必须找出更好的能够代替铝导线的新的技术,这便是我们常说的铜导技术。铜导线与铝导线相比,有很大的优势,具体表现在其导电性要优于铝,而且电阻小,所以发热量也要小于现在所使用的铝,从而可以有效地提高芯片的稳定性。我们今天所要介绍的65纳米技术也是向着这一方向发展。

2.何谓45纳米制作工艺

我们通常所说的CPU纳米制作工艺并非是加工生产线,实际上指的是一种工艺尺寸,代表在一块硅晶圆片上集成所数以万计的晶体管之间的连线宽度。按技术述语来说,也就是指芯片上最基本功能单元门电路和门电路间连线的宽度。以90纳米制造工艺为例,此时门电路间的连线宽度为90纳米。我们知道,1微米相当于1/60头发丝大小,经过计算我们可以算出,0.045微米(45纳米)相当于1/1333头发丝大小。可别小看这1/1333头发丝大小,这微小的连线宽度决定了CPU的实际性能,CPU生产厂商为此不遗余力地减小晶体管间的连线宽度,以提高在单位面积上所集成的晶体管数量。采用45纳米制造工艺之后,与65纳米工艺相比,绝对不是简单地令连线宽度减少了20纳米,而是芯片制造工艺上的一个质的飞跃。

摩尔定律极限 3纳米

摩尔定律极限 3纳米

摩尔定律是指每隔大约18-24个月,集成电路上的晶体管数量

将翻一番,而成本保持不变。

这个定律已经持续了几十年,推动了计算机技术的快速发展和晶体管的不断进化。

然而,随着技术的进步,晶体管的缩小已经接近了物理上的极限。

目前,晶体管的尺寸已经缩小到了数十纳米的级别。

在当前的技术和材料限制下,据估计,晶体管的尺寸可能在接近3

纳米时达到极限。

达到3纳米尺寸的晶体管将面临一系列挑战。

首先,随着晶体管尺寸的不断缩小,电子隧穿效应会变得更加显著,导致电流的泄漏增加,从而影响晶体管的性能和可靠性。

其次,由于尺寸的缩小,晶体管的制造难度也会增加,可能需要开发新的材料和工艺。

为了继续推动计算机技术的发展,研究人员正在寻找替代方案。

其中一种可能的方案是引入新的材料,如碳纳米管或二维材料,并开发新的制造技术。

此外,还有研究人员正在探索使用量子计算等新技术来替代传统的基于硅的晶体管。

总而言之,摩尔定律在晶体管尺寸缩小到3纳米时可能达到极限。

面对这个挑战,研究人员正在寻找新的材料和技术来继续推动计算机技术的发展。

芯片制程 nm -回复

芯片制程nm -回复什么是芯片制程nm?芯片制程nm(纳米米)是衡量集成电路(IC)制造工艺尺寸的单位之一。

nm代表纳米米,即十亿分之一米,也就是百分之一微米。

芯片制程nm 指的是制造芯片中铜线的最短尺寸或栅长。

如何测量芯片制程nm?测量芯片制程nm的速度和精度非常关键,因为芯片制程的小幅度差异可能会导致电子元器件的性能差异。

测量芯片制程nm的常用方法是使用扫描电子显微镜(SEM)。

SEM是一种使用电子束替代光束的显微镜,能够提供高分辨率和三维图像。

通过SEM,可以观察芯片表面的微观结构,并测量不同元件之间的距离、线宽等维度,从而确定芯片制程nm。

除了SEM,还有一些其他测量方法,比如原子力显微镜(AFM)、透射电子显微镜(TEM)等。

这些方法都能够提供高分辨率的图像,并进行尺寸测量。

芯片制程nm的发展历程随着技术的不断发展,芯片制程nm在过去几十年间有了快速的发展。

这一发展始于20世纪60年代,当时微处理器的最初版本只有几千个晶体管,并且制程尺寸在几十微米。

随着时间的推移,芯片制程尺寸逐渐缩小。

到了20世纪80年代,制程尺寸已经缩小到了几微米,晶体管数量也大大增加。

1990年代,芯片制程开始进入纳米尺寸,制程尺寸缩小到了100纳米左右。

这一时期,工艺技术和设备发展迅猛,正式开启了纳米时代。

进入21世纪,芯片制程nm进一步缩小。

2005年,半导体行业在制程尺寸方面实现了65nm,2008年达到了45nm制程。

之后,行业又相继推出了32nm、22nm、14nm以及更小尺寸的制程。

目前,行业已经进入到10nm和7nm的制程。

随着技术的发展,预计未来还将出现更小尺寸的芯片制程。

这种持续的缩小制程尺寸的趋势,可以称之为摩尔定律。

芯片制程nm对技术的影响芯片制程nm的不断缩小对技术发展和应用带来了深远的影响。

首先,芯片制程nm的缩小使得集成电路的功能更加强大,性能更出色。

随着制程尺寸的缩小,晶体管的数量和密度都得到了大幅度提升,使得芯片能够容纳更多的功能和计算能力。

TDP技术

TDP技术TDP是TotalDissipatedPowe r的缩写,中文翻译为“热设计功耗”,是反应一颗处理器热量释放的指标,它的含义是当处理器达到负荷最大的时候,释放出的热量,单位为瓦(W)。

在电脑上表示的是各个部件的功耗,尤其是电脑的CPU(中央处理器)GPU(图形处理器).是电脑耗电量的重要指标。

是CPU公司对某系列处理器给出的散热器设计参考的最高功率值。

TDP技术就是降低CPU功耗的节能技术。

CPU的TDP功耗并不是CPU的真正功耗。

功耗(功率)是CPU的重要物理参数,根据电路的基本原理,功率(P)=电流(A)×电压(V)。

所以,CPU的功耗(功率)等于流经处理器核心的电流值与该处理器上的核心电压值的乘积。

而TDP 是指CPU电流热效应以及其他形式产生的热能,他们均以热的形式释放。

显然CPU 的TDP小于CPU功耗。

换句话说,CPU的功耗很大程度上是对主板提出的要求,要求主板能够提供相应的电压和电流;而TDP是对散热系统提出要求,要求散热系统能够把CPU发出的热量散掉,也就是说TDP功耗是要求CPU的散热系统必须能够驱散的最大总热量。

现在CPU厂商越来越重视CPU的功耗,因此人们希望TDP功耗越小越好,越小说明CPU发热量小,散热也越容易,对于笔记本来说,电池的使用时间也越长。

Intel和AMD对TDP功耗的含义并不完全相同。

AMD的的CPU集成了内存控制器,相当于把北桥的部分发热量移到CPU上了,因此两个公司的TDP值不是在同一个基础上,不能单纯从数字上比较。

另外,TDP值也不能完全反映CPU的实际发热量,因为现在的CPU都有节能技术,实际发热量显然还要受节能技术的影响,节能技术越有效,实际发热量越小。

TDP功耗可以大致反映出CPU的发热情况,实际上,制约CPU发展的一个重要问题就是散热问题。

温度可以说是CPU的杀手,显然发热量低的CPU设计有望达到更高的工作频率,并且在整套计算机系统的设计、电池使用时间乃至环保方面都是大有裨益。

CPU的散热设计功耗(TDP)和实际功耗没有直接关系

CPU的散热设计功耗(TDP)和实际功耗没有直接关系展开全文当CPU的散热设计功耗(TDP: Thermal Design Power) 值最主要是提供给计算机系统厂商,散热片/风扇厂商,以及机箱厂商等等进行系统时使用的。

因为TDP的值表明,对应系列CPU 的最终版本在满负荷(CPU 利用率为100%的理论上)可能会达到的最高散热热量。

但是,TDP值并不等同于CPU的实际功耗,更没有算术关系。

CPU的实际功耗没有捷径获得,只能实际测试。

实际功耗对最终用户才有意义。

下图是英特尔公司中国应用设计中心(ADC) 设计的测试PC 功耗的简单工具对于一个系列的CPU,英特尔一般给出一个整体的TDP值,不会为每个系列的不同型号的CPU提供不同的TDP值,所以大家可以看到一大批不同型号的CPU都通用一个TDP值。

例如,英特尔已经发布的酷睿2 双核 6xxx 系列,4xxx 系列和奔腾双核 2xxx 系列,甚至这些系列后续的新型号,提供的散热设计功耗(TDP)值都为65W,CPU的主频跨度从1.6GHz 到3.0GHz,甚至将来更高主频的产品。

难道这些CPU的理论最高散热功耗都为65W(瓦)?不是的。

只有将来最高性能的型号在满负荷的时候可能会达到这个值。

为什么要这么做呢?为了方便系统的设计以及厂商对部件物料的管理。

因为散热片/风扇/机箱厂商以及计算机系统厂商只要设计或采用一套可以帮助CPU散热达到65W的方案,就可以在系统中采用符合TDP 65W的所有CPU。

否则,TDP值分的过细,厂商在管理部件上就太纷杂了,要为每一个型号的CPU配备贴切的散热片/风扇/机箱,为20种型号的CPU准备20种物料?好像没有人愿意这么做。

最终用户关注的是CPU的实际功耗,但是实际功耗和实际的应用联系在一起,而且和CPU采用的节能技术密切相关,所以无法得到统一的结果,即使有也是典型应用的实际测试值。

另外,CPU不能单独工作,必须和系统在一起的,所以我个人的意见还是要看系统的整体功耗,它才对最终用户才有实际意义。

CPU制作工艺

CPU制作工艺1、CPU的临盆过程要明白得CPU的临盆工艺,我们须要先明白CPU是如何被制造出来的。

让我们分几个步调进修CPU的临盆过程。

(1)硅提纯临盆CPU等芯片的材料是半导体,现时期重要的材料是硅Si,这是一种非金属元素,从化学的角度来看,因为它处于元素周期表中金属元素区与非金属元素区的交界处,因此具有半导体的性质,合适于制造各类微小的晶体管,是今朝最合适于制造现代大年夜范畴集成电路的材料之一。

在硅提纯的过程中,原材料硅将被熔化,并放进一个庞大年夜的石英熔炉。

这时向熔炉里放入一颗晶种,以便硅晶体围着这颗晶种进展,直到形成一个几近完美的单晶硅。

以往的硅锭的直径大年夜差不多上200毫米,而CPU厂商正在增长300毫米晶圆的临盆。

(2)切割晶圆硅锭造出来了,并被整型成一个完美的圆柱体,接下来将被切割成片状,称为晶圆。

晶圆才被真正用于CPU的制造。

所谓的“切割晶圆”也确实是用机械从单晶硅棒上切割下一片事先确信规格的硅晶片,并将其划分成多个微小的区域,每个区域都将成为一个CPU的内核(Die)。

一样来说,晶圆切得越薄,雷同量的硅材料能够或许制造的CPU成品就越多。

(3)影印(Photolithography)在经由热处理获得的硅氧化物层上面涂敷一种光阻(Photoresist)物质,紫外线经由过程印制着CPU复杂电路构造图样的模板照耀硅基片,被紫外线照耀的处所光阻物质消融。

而为了幸免让不须要被曝光的区域也受到光的干扰,必须制造遮罩来掩蔽这些区域。

这是个相当复杂的过程,每一个遮罩的复杂程度得用10GB数据来描述。

(4)蚀刻(Etching)这是CPU临盆过程中重要操作,也是CPU工业中的重头技巧。

蚀刻技巧把对光的应用推向了极限。

蚀刻应用的是波长专门短的紫外光并合营专门大年夜的镜头。

短波长的光将透过这些石英遮罩的孔照在光敏抗蚀膜上,使之曝光。

接下来停止光照并移除遮罩,应用特定的化学溶液清洗掉落被曝光的光敏抗蚀膜,以及鄙人面紧贴着抗蚀膜的一层硅。

专业继续教育-《战略性新兴产业基础知识》试题与答案

《战略性新兴产业基础知识》竞赛题目(选择题75题,判断题29题,问答题86题,共190题)一、选择题1.目前全球通用飞机占飞机总数的多少?(C)A 30%B 50%C 70%D 90%2.动力电池组是由多个蓄电池通过( A )方式组合起来电动使用要求.A.串联B.并联C.交联D.互联3.电动汽车的控制,都是建立在( A ) 的平台上的。

A.电子控制单元B.动力电池组C.电池管理系统D.电机4.哪类汽车包括传动系统、驱动电机、发电机、发动机、蓄电池组、交流器、动力分配器。

(A)A.混合动力汽车B.电动汽车C.燃料电池汽车D.太阳能电动汽车5.(C )是将电网的电能通过交/直流电力变换将能量储存到蓄电池的控制装置。

A.整车控制系统B.整车系统C.充电系统D.电机驱动系统6.下列哪项不属于电机驱动系统的要求( D )A.大功率B.体积小C.高效率D.环境适用性弱7.燃料电池电动汽车的电池能量转换效率可高达( A )A.60%~80%B.60%~70% C.70%~90%D.50%~70%8.电机驱动系统包括两部分( B )A.电机和传动系统B.电机和控制器C.发电机与发动机D.直流电机和交流电机9.铅酸电池目前被广泛用于限定车速( C )的各种场地车上。

A.等于50Km/h B.大于50Km/h C.小于50Km/h D.小于60Km/h10.混合动力整车控制的核心是( A )A.多能源管理系统B.电辅助制动系统C.电池管理系统D.均衡充电控制系统11.从整车控制系统的应用技术看,整车控制系统将朝( D )方向发展. A.专业化、网络化、集成化B.集成化、网络化、信息化C.专业化、信息化、精细化D.专业化、精细化、集成化12.下图的这部车是属于什么类型的汽车?(B)(MINI E,纯电动汽车)A.混合动力电动汽车B.纯电动汽车C.燃料电池汽车D.太阳能电动汽车13.发光二极管的英文缩写是(B)A.CBDB.LEDC.ELDD.BCD14.目前,对LED照明系统的光学设计主要采用计算机模拟的方式进行,常用的照明光学软件不包括以下的哪种?(A)A.Auto-CADB.Light—toolsC.TraceproD.ASAP15. LED的发光波长是由形成P-N结的半导体材料决定的,请问首先被制造出来的是什么样的LED?(A)A.红光LEDB.绿光LEDC.蓝光LEDD.黄光LED16.我国为了推动LED产业的发展,降低能源消耗,科技部推出了什么示范工程?(B)A.一城万盏B.十城万盏C.百城万盏D.千城万盏17.下面哪一项不是光伏发电系统的主要组成部分(C)A.太阳能电池板B.控制器C.转换器D.逆变器18.目前晶体硅光伏组件的使用寿命是多少年(C)A.5年B.15年C.30年D.45年19.基因和免疫诊断技术改变了临床的诊断模式,进入了诊断时代。