FPGA可编程逻辑器件芯片XC2S200E-FG456中文规格书

FPGA可编程逻辑器件芯片XC2S100-5FGG456C中文规格书

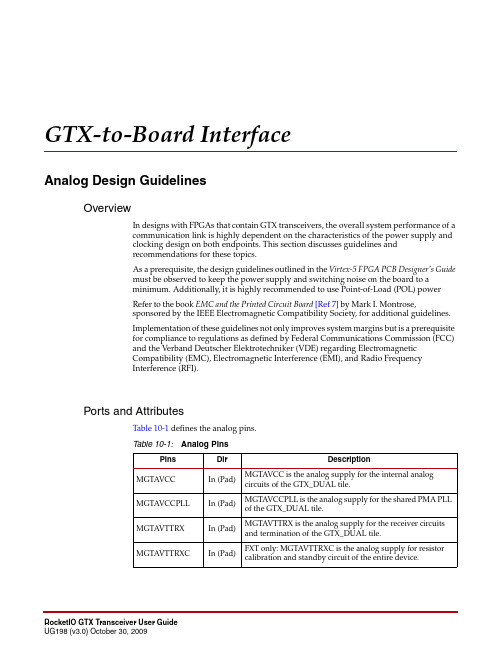

GTX-to-Board InterfaceAnalog Design GuidelinesOverviewIn designs with FPGAs that contain GTX transceivers, the overall system performance of acommunication link is highly dependent on the characteristics of the power supply andclocking design on both endpoints. This section discusses guidelines andrecommendations for these topics.As a prerequisite, the design guidelines outlined in the Virtex-5 FPGA PCB Designer’s Guidemust be observed to keep the power supply and switching noise on the board to aminimum. Additionally, it is highly recommended to use Point-of-Load (POL) powerRefer to the book EMC and the Printed Circuit Board[Ref7] by Mark I. Montrose,sponsored by the IEEE Electromagnetic Compatibility Society, for additional guidelines.Implementation of these guidelines not only improves system margins but is a prerequisitefor compliance to regulations as defined by Federal Communications Commission (FCC)and the Verband Deutscher Elektrotechniker (VDE) regarding ElectromagneticCompatibility (EMC), Electromagnetic Interference (EMI), and Radio FrequencyInterference (RFI).Ports and AttributesTable10-1 defines the analog pins.Table 10-1:Analog PinsPins Dir DescriptionMGTAVCC In (Pad)MGTAVCC is the analog supply for the internal analog circuits of the GTX_DUAL tile.MGTAVCCPLL In (Pad)MGTAVCCPLL is the analog supply for the shared PMA PLL of the GTX_DUAL tile.MGTAVTTRX In (Pad)MGTAVTTRX is the analog supply for the receiver circuits and termination of the GTX_DUAL tile.MGTAVTTRXC In (Pad)FXT only: MGTAVTTRXC is the analog supply for resistor calibration and standby circuit of the entire device.Chapter 10:GTX-to-Board InterfaceTable 10-2 defines the analog attributes.MGTAVTTRXC_RIn (Pad)TXT only: MGTAVTTRXC_R is the analog supply for resistor calibration and standby circuit of the right transceiver column.MGTAVTTRXC_L In (Pad)TXT only: MGTAVTTRXC_L is the analog supply for resistor calibration and standby circuit of the left transceiver column.MGTAVTTTX In (Pad)MGTAVTTTX is the analog supply for the transmittertermination and driver circuits and reference clock routing of the GTX_DUAL tile.MGTREFCLKP MGTREFCLKN In (Pad)Differential clock input pin pair (1) for the reference clock of the GTX_DUAL tile.MGTRREF In (Pad)FXT only: MGTRREF is the reference resistor input for the entire device.MGTRREF_R In (Pad)TXT only: MGTRREF_R is reference resistor input for the right transceiver column.MGTRREF_LIn (Pad)TXT only: MGTRREF_L is reference resistor input for the left transceiver column.Notes:1.This clock can only be accessed by the FPGA logic through the REFCLKOUT port.Table 10-2:Analog AttributesAttributeTypeDescriptionCLKINDC_BBooleanMust be set to TRUE. Oscillators driving the dedicated reference clock inputs must be AC coupled.When set to FALSE for testing, the common mode voltage of the driving circuit must match the common mode voltage of the differential clock input pair (MGTCLKP , MGTCLKN). The differential swing must not exceed the maximum differential swing of the clock input pair.(1, 2)CLKRCV_TRST BooleanWhen set to FALSE, switches off the internal termination resistors of the differential clock input pair. This results in a high-impedance input characteristic that is only intended for testing.When set to TRUE, the differential clock input pair is terminated with a 100Ω differential impedance. Each clock input in (MGTCLKP , MGTCLKN) is contacted via a 50Ω resistor to a midterm nominal voltage of 0.8V .(1, 2)TERMINATION_CTRL[4:0]5-bit BinaryControls the internal termination calibration circuit. Refer to Table 10-5, page 259 for encoding.Table 10-1:Analog Pins (Cont’d)PinsDir DescriptionResistor Calibration CircuitResistor Calibration CircuitThe resistor calibration circuit in the GTX transceiver is used to precisely calibrate the TX and RX termination resistors via an external precision reference resistor.Table 10-1 defines the resistor calibration circuit pins used for TX and RX termination resistor calibration.TERMINATION_IMP_0TERMINATION_IMP_1IntegerSelects the termination impedance for the TX driver and receiver.See Figure 10-4 calibrating the impedancevalues. Always set to 50, which selects the 50Ω termination impedance. The RocketIO™ GTX Transceiver Wizard automatically sets the TERMINATION_IMP_(0/1) attributes to 50.TERMINATION_OVRD BooleanSelects whether the external 59Ω(3)precision resistor connected to the MGTRREF pin or an override value is used, as defined by TERMINATION_CTRL[4:0].Notes:1.Violation of the rules outlined in this section result in a marginal or dysfunctional design, device degradation in the future, or device damage.2.Consult DS202: Virtex-5 FPGA Data Sheet for the common mode voltage values and the associated differential swing and operating conditions.3.The nominal value of the external precision resistor RREF connected to the MGTRREF pin is different for LXT/SXT devices and FXT/TXT devices. For LXT/SXT devices with GTP_DUAL tiles, RREF is 50Ω nominal. For FXT/TXT devices with GTX_DUAL tiles, RREF is 59Ω nominal.Table 10-2:Analog Attributes (Cont’d)AttributeTypeDescriptionTable 10-3:Resistor Calibration Circuit PinsPinsDir DescriptionMGTAVTTRXC In (Pad)FXT only: MGTAVTTRXC is the analog supply for resistor calibration and standby circuit of the entire device.MGTAVTTRXC_LIn (Pad)TXT only: MGTAVTTRXC_L is the analog supply for resistor calibration and standby circuit of the left transceiver column.MGTAVTTRXC_R In (Pad)TXT only: MGTAVTTRXC_R is the analog supply for resistor calibration and standby circuit of the right transceiver column.MGTRREF In (Pad)FXT only: MGTRREF is the reference resistor input for the entire device.MGTRREF_L In (Pad)TXT only: MGTRREF_L is reference resistor input for the left transceiver column.MGTRREF_RIn (Pad)TXT only: MGTRREF_R is reference resistor input for the right transceiver column.Chapter 10:GTX-to-Board InterfaceResistor Calibration Circuit。

FPGA可编程逻辑器件芯片XC2V1000-6FG456I中文规格书

Chapter 6 HD IOL ResourcesHD IOL FeaturesSingle Data Rate Flip-FlopsEach pin contains local single-data rate (SDR) flip-flop registers in the IOB for both data andtristate lines. Both output, input, and tristate SDR flip-flops use these blocks:•FDCE: Flip-flip with clock enable and asynchronous clear•FDPE: Flip-flop with clock enable and asynchronous preset•FDRE: Flip-flop with clock enable and synchronous reset•FDSE: Flip-flop with clock enable and synchronous setBoth data and tristate registers must be used in the same manner when they are used together (that is both SDR, DDR, or not registered at all).Double Data Rate Flip-FlopsEach pin contains local double-data rate (DDR) flip-flop registers in the IOL for both data andtristate lines. The DDR flip-flops in the input path use the IDDRE1 and the output and tristatepaths use the ODDRE1. When both data and tristate registers are used, it is required that Both data and tristate registers must be used in the same manner (that is both SDR, DDR, or notregistered at all).Uncalibrated IOB DelayEach pin has two uncalibrated delay blocks: one for the input delay (IDELAYE5) and one for the output path (ODELAYE5). Each individual block provides a uncalibrated delay of up toapproximately 1.8 ns for both data and tristate paths. When only the input portion of the IOB is used, the ODELAYE5 can be cascaded to the IDELAYE5 to provide the input path up toapproximately 3.6 ns of delay. Both IDELAYE5 and ODELAYE5 have 32 taps that can be changed incremented or decremented using the INC and CE pins, or can be dynamically changed usingthe CNTVALUEIN and LOAD pins.DPLLEach HDIO bank has an all-digital phase locked loop (DPLL) incorporated into the bank with the ability to phase shift the clock signal for optimal signal timing. The DPLL is used to generate new clock frequencies and to eliminate skew between clock and data paths as they reach the IDDR and ODDR registers.For the Versal VC1902, VC1802, and VM1802 devices, the following restrictions related to DPLL apply:•The minimum input clock frequency (FINMIN_DPLL) is 50 MHz instead of 10 MHz.•DPLL PD deskew function and ZHOLD mode are not supported in the listed devices. MMCMs and IDELAY have to be used instead.•DPLLs in HDIO banks are not supported in the listed devices.For more information, see the Versal ACAP Clocking Resources Architecture Manual (AM003).HD IOL PrimitivesThe IOL registers and delay blocks are intantiated in the design using HDL primtives.IDELAY and ODELAY PrimitivesUncalibrated Input DelayFigure 57: IDELAYE5 PrimitiveX22469-050519Table 96: IDELAYE5 AttributesAttribute Values DescriptionCASCADE FALSE, TRUE The CASCADE attribute is set to TRUE when the ODELAYE5 is used tocascade the IDELAYE5. This attribute enables an input delay greater than1.8 ns.Table 97: IDELAYE5 PortsPort I/O DescriptionDATAOUT Output Delayed data from the IOBCNTVALUEOUT<4:0>Output The CNTVALUEOUT pins are used for reporting the current tap value andreads out the amount of taps in the current delay.CASC_OUT Output Cascade delay to ODELAYE5 in cascade. The CASC_OUT pin is used whencascading from an IDELAYE5 to an ODELAYE5. The CASC_OUT port of theIDELAYE5 is connected to the CASC_IN of the ODELAYE5 in cascade. IDATAIN Input Data from input pinCASC_RETURN Input Cascade delay returning from the ODELAYE5 DATAOUT port. This port isused when cascading the ODELAYE5 and IDELAYE5.CNTVALUEIN<4:0>Input The CNTVALUEIN pins are used for dynamically switching the loadabletap value. The CNTVALUEIN is the number of taps required.CE Input Clock enable for the delay register clockCLK Input Clock used to sample LOAD, CE, and INCINC Input Increment and decrement are controlled by the enable signal (CE).•INC = 1 increments•INC = 0 decrementsLOAD Input Load counter value from the CNTVALUEIN bus when High.RST Input The reset pin (RST) is asynchronous with the CLK。

FPGA可编程逻辑器件芯片XC2S100E-5FG456C中文规格书

24,304

41

972,192

272

LX155T

808

32,800

33,608

41

1,344,800

272

LX220T

1,064

42,016

43,080

41

1,722,656

272

LX330T

1,596

63,024

64,620

41

2,583,984

272

SX35T

244

10,168

10,412

41

416,888

Virtex-5 FPGA Configuration Guide UG191 (v3.13) July 28, 2020

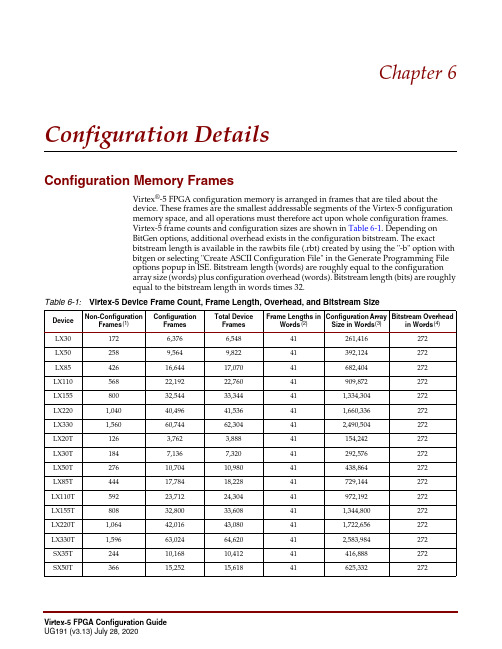

Chapter 6: Configuration Details

Virtex-5 FPGA Configuration Guide UG191 (v3.13) July 28, 2020

Table 6-1: Virtex-5 Device Frame Count, Frame Length, Overhead, and Bitstream Size

Device

Non-Configuration Frames (1)

Configuration Frames

Total Device Frames

Table 6-13: TIMER Register Description

Name

Bit Index

Description

TIMER_USR_MON

Watchdog is enabled during user mode:

25

0: Disabled

1: Enabled

FPGA可编程逻辑器件芯片XC2V2000-6FG456C中文规格书

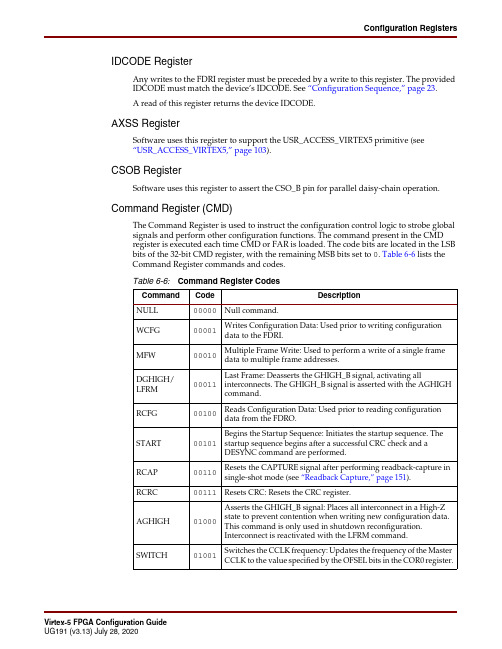

IDCODE RegisterAny writes to the FDRI register must be preceded by a write to this register. The provided IDCODE must match the device’s IDCODE. See “Configuration Sequence,” page23.A read of this register returns the device IDCODE.AXSS RegisterSoftware uses this register to support the USR_ACCESS_VIRTEX5 primitive (see“USR_ACCESS_VIRTEX5,” page103).CSOB RegisterSoftware uses this register to assert the CSO_B pin for parallel daisy-chain operation. Command Register (CMD)The Command Register is used to instruct the configuration control logic to strobe global signals and perform other configuration functions. The command present in the CMD register is executed each time CMD or FAR is loaded. The code bits are located in the LSB bits of the 32-bit CMD register, with the remaining MSB bits set to 0. Table6-6 lists the Command Register commands and codes.Table 6-6:Command Register CodesCommand Code DescriptionNULL00000Null command.WCFG00001Writes Configuration Data: Used prior to writing configuration data to the FDRI.MFW00010Multiple Frame Write: Used to perform a write of a single frame data to multiple frame addresses.DGHIGH/ LFRM 00011Last Frame: Deasserts the GHIGH_B signal, activating allinterconnects. The GHIGH_B signal is asserted with the AGHIGHcommand.RCFG00100Reads Configuration Data: Used prior to reading configuration data from the FDRO.START00101Begins the Startup Sequence: Initiates the startup sequence. The startup sequence begins after a successful CRC check and a DESYNC command are performed.RCAP00110Resets the CAPTURE signal after performing readback-capture in single-shot mode (see “Readback Capture,” page151).RCRC00111Resets CRC: Resets the CRC register.AGHIGH01000Asserts the GHIGH_B signal: Places all interconnect in a High-Z state to prevent contention when writing new configuration data. This command is only used in shutdown reconfiguration. Interconnect is reactivated with the LFRM command.SWITCH01001Switches the CCLK frequency: Updates the frequency of the Master CCLK to the value specified by the OFSEL bits in the COR0 register.Warm Boot Start Address Register (WBSTAR)The name of each bit position in the WBSTAR is given in Figure 6-6 and described in Table 6-12.DescriptionReservedPERSIST_DEASSERT_AT_DESYNCHReserved ReservedRBCRC_NO_PINRBCRC_EN ReservedBPI_1ST_READ_CYCLESBPI_PAGE_SIZEBit Index 313029282726252423222120191817161514131211109876543210ValueFigure 6-5:Configuration Options Register 1Table 6-11:Configuration Options Register 1 Description NameBit IndexDescriptionPERSIST_DEASSERT_AT_DESYNCH 17Enables deassertion of PERSIST with the DESYNCH commandRBCRC_NO_PIN 9Disables INIT_B as read back CRC error status output pinRBCRC_EN8Continuous readback CRC enable BPI_1ST_READ_CYCLES[3:2]First byte read timing:00: 1 C C LK 01: 2 C C LKs 10: 3 C C LKs 11: 4 C C LKs BPI_PAGE_SIZE [1:0]Flash memory page size:00: 1byte/word 01: 4 bytes/words 10: 8 bytes/words 11: ReservedChapter 6:Configuration DetailsWatchdogFPGA End of StartupTo use the Watchdog to monitor the bitstream configuration, set TIMER_CFG_MON to 1 and the desired TIMER_VALUE in a write to the TIMER register in the bitstream. The TIMER_VALUE should be adequate to cover the entire FPGA configuration time until startup is complete. Any wait time in startup for DCI match, DCM lock, or DONE should also be included.Once enabled, the watchdog timer starts to count down. If the timer reaches 0 and the FPGA has not reached the final state of startup, a watchdog time-out error occurs and triggers a fallback configuration.User OperationTo use the Watchdog to monitor the user logic, set TIMER_USR_MON to 1 and the desired TIMER_VALUE in a write to the TIMER register in the bitstream. The user must constantly reset the watchdog counter before it times out, either by the LTIMER command or by directly accessing the TIMER register. The watchdog is automatically disabled when the device is shut down or on power down (including shutdown).Table 8-6 shows an example bitstream for reloading the Watchdog using the LTIMER command.Table 8-7 shows an example bitstream for directly accessing the TIMER register:Table 8-6:Example Bitstream for Reloading the Watchdog with LTIMERConfiguration Data(hex)Explanation FFFFFFFF Dummy Word AA995566 Sync Word 20000000 Type 1 NO OP30008001 Type 1 Write 1 Words to CMD00000000 NULL 20000000 Type 1 NO OP30008001 Type 1 Write 1 Words to CMD00000011 LTIMER Command 20000000 Type 1 NO OP30008001 Type 1 Write 1 Words to CMD0000000D DESYNCH 20000000Type 1 NO OPTable 8-7:Example Bitstream for Accessing the TIMER RegisterConfiguration Data(hex)Explanation FFFFFFFF Dummy Word AA995566Sync WordChapter 9:Readback CRC。

FPGA可编程逻辑器件芯片XC2S200E-7FGG456I中文规格书

IOBsFor additional information, refer to the chapter entitled “Using I/O Resources” in UG331: Spartan-3 Generation FPGA User Guide.IOB OverviewThe Input/Output Block (IOB) provides a programmable, bidirectional interface between an I/O pin and the FPGA’s internal logic.A simplified diagram of the IOB’s internal structure appears in Figure7. There are three main signal paths within the IOB: the output path, input path, and 3-state path. Each path has its own pair of storage elements that can act as either registers or latches. For more information, see the Storage Element Functions section. The three main signal paths are as follows:•The input path carries data from the pad, which is bonded to a package pin, through an optional programmable delay element directly to the I line. There are alternate routes through a pair of storage elements to the IQ1 and IQ2 lines.The IOB outputs I, IQ1, and IQ2 all lead to the FPGA’s internal logic. The delay element can be set to ensure a hold time of zero.•The output path, starting with the O1 and O2 lines, carries data from the FPGA’s internal logic through a multiplexer and then a three-state driver to the IOB pad. In addition to this direct path, the multiplexer provides the option to inserta pair of storage elements.•The 3-state path determines when the output driver is high impedance. The T1 and T2 lines carry data from the FPGA’s internal logic through a multiplexer to the output driver. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements. When the T1 or T2 lines are asserted High, the output driver ishigh-impedance (floating, hi-Z). The output driver is active-Low enabled.•All signal paths entering the IOB, including those associated with the storage elements, have an inverter option. Any inverter placed on these paths is automatically absorbed into the IOB.Storage Element FunctionsThere are three pairs of storage elements in each IOB, one pair for each of the three paths. It is possible to configure each of these storage elements as an edge-triggered D-type flip-flop (FD) or a level-sensitive latch (LD).The storage-element-pair on either the Output path or the Three-State path can be used together with a special multiplexer to produce Double-Data-Rate (DDR) transmission. This is accomplished by taking data synchronized to the clock signal’s rising edge and converting them to bits synchronized on both the rising and the falling edge. The combination of two registers and a multiplexer is referred to as a Double-Data-Rate D-type flip-flop (FDDR). See Double-Data-Rate Transmission, page12 for more information.The signal paths associated with the storage element are described in Table5.Table 5:Storage Element Signal DescriptionStorageElementDescription FunctionSignalD Data input Data at this input is stored on the active edge of CK enabled by CE. For latch operation when theinput is enabled, data passes directly to the output Q.Q Data output The data on this output reflects the state of the storage element. For operation as a latch intransparent mode, Q will mirror the data at D.CK Clock input A signal’s active edge on this input with CE asserted, loads data into the storage element.CE Clock Enable input When asserted, this input enables CK. If not connected, CE defaults to the asserted state.SR Set/Reset Forces storage element into the state specified by the SRHIGH/SRLOW attributes. TheSYNC/ASYNC attribute setting determines if the SR input is synchronized to the clock or not. REV Reverse Used together with SR. Forces storage element into the state opposite from what SR does.In contrast, the 144-pin Thin Quad Flat Pack (TQ144) package and the 132-pin Chip-Scale Package (CP132) tie V CCO together internally for the pair of banks on each side of the device. For example, the V CCO Bank 0 and the V CCO Bank 1 lines are tied together. The interconnected bank-pairs are 0/1, 2/3, 4/5, and 6/7. As a result, Spartan-3 devices in the CP132 and TQ144 packages support four independent V CCO supplies.Note:The CP132 package is discontinued.Spartan-3 FPGA CompatibilityWithin the Spartan-3 family, all devices are pin-compatible by package. When the need for future logic resources outgrows the capacity of the Spartan-3 device in current use, a larger device in the same package can serve as a direct replacement. Larger devices may add extra V REF and V CCO lines to support a greater number of I/Os. In the larger device, more pins can convert from user I/Os to V REF lines. Also, additional V CCO lines are bonded out to pins that were “not connected” in the smaller device. Thus, it is important to plan for future upgrades at the time of the board’s initial design by laying out connections to the extra pins.The Spartan-3 family is not pin-compatible with any previous Xilinx FPGA family or with other platforms among the Spartan-3 Generation FPGAs.Rules Concerning BanksWhen assigning I/Os to banks, it is important to follow the following V CCO rules:•Leave no V CCO pins unconnected on the FPGA.•Set all V CCO lines associated with the (interconnected) bank to the same voltage level.•The V CCO levels used by all standards assigned to the I/Os of the (interconnected) bank(s) must agree. The Xilinx development software checks for this. Tables 8, 9, and 10 describe how different standards use the V CCO supply.•Only one of the following standards is allowed on outputs per bank: LVDS, LDT, LVDS_EXT, or RSDS. This restriction is for the eight banks in each device, even if the V CCO levels are shared across banks, as in the CP132 and TQ144 packages.•If none of the standards assigned to the I/Os of the (interconnected) bank(s) uses V CCO, tie all associated V CCO lines to2.5V.•In general, apply 2.5V to V CCO Bank 4 from power-on to the end of configuration. Apply the same voltage to V CCO Bank5 during parallel configuration or a Readback operation. For information on how to program the FPGA using 3.3Vsignals and power, see the 3.3V-Tolerant Configuration Interface section.If any of the standards assigned to the Inputs of the bank use V REF, then observe the following additional rules:•Connect all V REF pins within the bank to the same voltage level.•The V REF levels used by all standards assigned to the Inputs of the bank must agree. The Xilinx development software checks for this. Tables 8 and 10 describe how different standards use the V REF supply.If none of the standards assigned to the Inputs of a bank use V REF for biasing input switching thresholds, all associated V REF pins function as User I/Os.Exceptions to Banks Supporting I/O StandardsBank 5 of any Spartan-3 device in a VQ100, CP132, or TQ144 package does not support DCI signal standards. In this case, bank 5 has neither VRN nor VRP pins.Furthermore, banks 4 and 5 of any Spartan-3 device in a VQ100 package do not support signal standards using V REF (see Table8). In this case, the two banks do not have any V REF pins.ConfigurationSpartan-3 devices are configured by loading application specific configuration data into the internal configuration memory. Configuration is carried out using a subset of the device pins, some of which are "Dedicated" to one function only, while others, indicated by the term "Dual-Purpose", can be re-used as general-purpose User I/Os once configuration is complete.Depending on the system design, several configuration modes are supported, selectable via mode pins. The mode pins M0, M1, and M2 are Dedicated pins. The mode pin settings are shown in Table 26.The HSWAP_EN input pin defines whether the I/O pins that are not actively used during configuration have pull-up resistorsduring configuration. By default, HSWAP_EN is tied High (via an internal pull-up resistor if left floating) which shuts off the pull-up resistors on the user I/O pins during configuration. When HSWAP_EN is tied Low, user I/Os have pull-ups during configuration. The Dedicated configuration pins (CCLK, DONE, PROG_B, M2, M1, M0, HSWAP_EN) and the JTAG pins (TDI, TMS, TCK, and TDO) always have a pull-up resistor to VCCAUX during configuration, regardless of the value on the HSWAP_EN pin. Similarly, the dual-purpose INIT_B pin has an internal pull-up resistor to VCCO_4 or VCCO_BOTTOM, depending on the package style.Depending on the chosen configuration mode, the FPGA either generates a CCLK output, or CCLK is an input accepting an externally generated clock.A persist option is available which can be used to force the configuration pins to retain their configuration function even after device configuration is complete. If the persist option is not selected then the configuration pins with the exception of CCLK, PROG_B, and DONE can be used as user I/O in normal operation. The persist option does not apply to the boundary-scan related pins. The persist feature is valuable in applications that readback configuration data after entering the User mode.Table 27 lists the total number of bits required to configure each FPGA as well as the PROMs suitable for storing those bits. See DS123: Platform Flash In-System Programmable Configuration PROMs data sheet for more information.The maximum bitstream length that Spartan-3 FPGAs support in serial daisy-chains is 4,294,967,264 bits (4Gbits), roughly equivalent to a daisy-chain with 323 XC3S5000 FPGAs. This is a limit only for serial daisy-chains where configuration data is passed via the FPGA’s DOUT pin. There is no such limit for JTAG chains.Table 26:Spartan-3 FPGAs Configuration Mode Pin SettingsConfiguration Mode (1)M0M1M2Synchronizing ClockData WidthSerial DOUT (2)Master Serial 000CCLK Output 1Y es Slave Serial 111CCLK Input 1Y es Master Parallel 110CCLK Output 8No Slave Parallel 011CCLK Input 8No JTAG 11TC K Input1NoNotes:1.The voltage levels on the M0, M1, and M2 pins select the configuration mode.2.The daisy chain is possible only in the Serial modes when DOUT is used.Table 27:Spartan-3 FPGA Configuration DataDevice File Sizes Xilinx Platform Flash PROMSerial ConfigurationParallel ConfigurationXC3S50439,264XCF01S XCF08P XC3S2001,047,616XCF01S XCF08P XC3S4001,699,136XCF02S XCF08P XC3S10003,223,488XCF04S XCF08P XC3S15005,214,784XCF08P XCF08P XC3S20007,673,024XCF08P XCF08P XC3S400011,316,864XCF16P XCF16P XC3S500013,271,936XCF16PXCF16P。

FPGA可编程逻辑器件芯片XC2S400-4FG456C中文规格书

550

550

MHz

FX100T devices

PLL Maximum Output Frequency for FX130T devices

500

450

N/A

MHz

FOUTMIN TEXTFDVAR RSTMINPULSE FPFDMAX FPFDMIN TFBDELAY

PLL Maximum Output Frequency for LX220T, LX330T, SX95T, SX240T, and FX200T devices PLL Minimum Output Frequency(5) External Clock Feedback Variation Minimum Reset Pulse Width Maximum Frequency at the Phase Frequency Detector Minimum Frequency at the Phase Frequency Detector Maximum Delay in the Feedback Path

Outputs Clocks (High Frequency Mode)

32.00 135.00 64.00 270.00

2.0 90.00 32.00 160.00

32.00 120.00 64.00 240.00

2.0 80.00 32.00 140.00

32.00 120.00 64.00 240.00

0.36

TAXD

AX inputs to DMUX output

0.62

TBXB

BX inputs to BMUX output

0.41

Speed Grade

-2I

FPGA可编程逻辑器件芯片XC2S200E-6FGG456C中文规格书

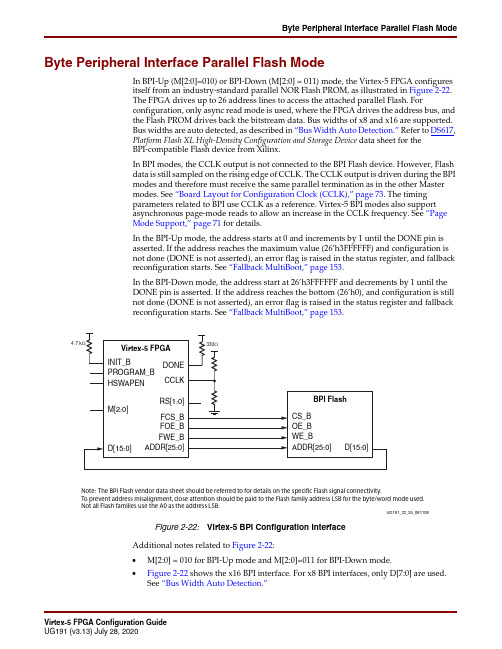

Byte Peripheral Interface Parallel Flash ModeByte Peripheral Interface Parallel Flash ModeIn BPI-Up (M[2:0]=010) or BPI-Down (M[2:0]=011) mode, the Virtex-5 FPGA configures itself from an industry-standard parallel NOR Flash PROM, as illustrated in Figure 2-22. The FPGA drives up to 26 address lines to access the attached parallel Flash. Forconfiguration, only async read mode is used, where the FPGA drives the address bus, and the Flash PROM drives back the bitstream data. Bus widths of x8 and x16 are supported. Bus widths are auto detected, as described in “Bus Width Auto Detection.” Refer to DS617, Platform Flash XL High-Density Configuration and Storage Device data sheet for the BPI-compatible Flash device from Xilinx.In BPI modes, the CCLK output is not connected to the BPI Flash device. However, Flash data is still sampled on the rising edge of CCLK. The CCLK output is driven during the BPI modes and therefore must receive the same parallel termination as in the other Master modes. See “Board Layout for Configuration Clock (CCLK),” page 73. The timing parameters related to BPI use CCLK as a reference. Virtex-5 BPI modes also support asynchronous page-mode reads to allow an increase in the CCLK frequency. See “Page Mode Support,” page 71 for details.In the BPI-Up mode, the address starts at 0 and increments by 1 until the DONE pin is asserted. If the address reaches the maximum value (26’h3FFFFFF) and configuration is not done (DONE is not asserted), an error flag is raised in the status register, and fallback reconfiguration starts. See “Fallback MultiBoot,” page 153.In the BPI-Down mode, the address start at 26’h3FFFFFF and decrements by 1 until the DONE pin is asserted. If the address reaches the bottom (26’h0), and configuration is still not done (DONE is not asserted), an error flag is raised in the status register and fallback reconfiguration starts. See “Fallback MultiBoot,” page 153.Additional notes related to Figure 2-22:∙M[2:0]=010 for BPI-Up mode and M[2:0]=011 for BPI-Down mode.∙Figure 2-22 shows the x16 BPI interface. For x8 BPI interfaces, only D[7:0] are used.See “Bus Width Auto Detection.”Figure 2-22:Virtex-5 BPI Configuration InterfaceUG191_c2_25_0611084.7 k Note: The BPI Flash vendor data sheet should be referred to for details on the specific Flash signal connectivity.To prevent address misalignment, close attention should be paid to the Flash family address LSB for the byte/word mode used. Not all Flash families use the A0 as the address LSB.Board Layout for Configuration Clock (CCLK)Chapter 2:Configuration InterfacesBoundary-Scan for Virtex-5 Devices Using IEEE Standard 1149.1Single Device ConfigurationTable3-4 describes the TAP controller commands required to configure a Virtex-5 device.Refer to Figure3-2 for TAP controller states. These TAP controller commands are issuedautomatically if configuring the part with the iMPACT software.Table 3-4: Single Device Configuration SequenceTAP Controller Step and Description Set and Hold# of Clocks TDI TMS TCK1.On power-up, place a logic 1 on the TMS, and clockthe TCK five times. This ensures starting in the TLR(Test-Logic-Reset) state.X152.Move into the RTI state.X013.Move into the SELECT-IR state.X124.Enter the SHIFT-IR state.X025.Start loading the CFG_IN instruction, LSB first:111000101096.Load the MSB of CFG_IN instruction when exitingSHIFT-IR, as defined in the IEEE standard.1117.Enter the SELECT-DR state.X128.Enter the SHIFT-DR state.X029.Shift in the Virtex-5 bitstream. Bitn (MSB) is the firstbit in the bitstream(1).bit1...bit n0(bits in bitstream)-110.Shift in the last bit of the bitstream. Bit0 (LSB) shiftson the transition to EXIT1-DR.bit01111.Enter UPDATE-DR state.X1112.Reset TAP by clocking five 1s on TMS X1513.Move into RTI state.X0114.Enter the SELECT-IR state.X1215.Move to the SHIFT-IR state.X0216.Start loading the JSTART instruction. The JSTARTinstruction initializes the startup sequence.1110011000917.Load the last bit of the JSTART instruction.11118.Move to the UPDATE-IR state.X1119.Move to the RTI state and clock the startupsequence by applying a minimum of 12 clock cyclesto the TCK.X01220.Move to the TLR state. The device is now functional.X13Notes:1.In the Configuration Register, data is shifted in from the right (TDI) to the left (TDO), MSB first. (Shifts into the Configuration Register aredifferent from shifts into the other registers in that they are MSB first.)Chapter 4:User PrimitivesCAPTURE_VIRTEX5The CAPTURE_VIRTEX5 primitive is used to capture I/O, CLB, and block RAM outputflip-flop status, and then read back through the configuration interface. The CAP input issampled by CLK to generate an internal gcap signal. The I/O and CLB flip-flop status arecaptured into an FPGA configuration memory cell when the gcap signal is High. There areoperation modes, a one-shot mode, or a continuous mode.In one-shot mode, after the first CAP falling edge, gcap is held to 0 to avoid furthercapturing. An explicit RCAP command is required to re-arm the capture circuit.In continuous mode, the CAP input is simply sampled by CLK, and becomes the gcapsignal, allowing the user to control when to capture.CAPTURE_VIRTEX5 should not operate simultaneously with the FRAME_ECC_VIRTEX5primitive or the Readback CRC function (see Chapter9, “Readback CRC”) becausecapturing a value into configuration memory might cause a false error.Table 4-2:CAPTURE_VIRTEX5 Pin TablePin Name Type DescriptionCLK Input Clock for sampling the CAP input.CAP Input Active-High capture enable. The CAP input is sampled bythe rising edge of CLK.ICAP_VIRTEX5The ICAP_VIRTEX5 primitive works the same way as the SelectMAP configurationinterface except it is on the fabric side, and ICAP has a separate read/write bus, as opposedto the bidirectional bus in SelectMAP. The general SelectMAP timing diagrams and theSelectMAP bitstream ordering information as described in the “SelectMAP ConfigurationInterface” section of this user guide are also applicable to ICAP. It allows the user to accessconfiguration registers, readback configuration data, or partially reconfigure the FPGAafter configuration is done.ICAP has three data width selections through the ICAP WIDTH parameter: x8, x16, andx32.The two ICAP ports cannot be operated simultaneously. The design must start from the topICAP, then switch back and forth between the two.Table 4-3:ICAP_VIRTEX5 Pin TablePin Name Type DescriptionCLK Input ICAP interface clockCE Input Active-Low ICAP interface select. Equivalent to CS_B inthe SelectMAP interface.WRITE Input0=WRITE, 1=READ. Equivalent to the RDWR_B signal inthe SelectMAP interface.I[31:0]Input ICAP write data bus. The bus width depends onICAP_WIDTH parameter. The bit ordering is identical tothe SelectMAP interface. See SelectMap Data Ordering inFigure2-19.。

FPGA可编程逻辑器件芯片XC2S400E-6FTG256I中文规格书

Readback and Configuration VerificationSpartan®-6 devices allow users to read configuration memory through the SelectMAP,ICAP, and JTAG interfaces. During readback, the user reads all configuration memorycells, including the current values on all user memory elements (LUT RAM, SRL16, andblock RAM).To read configuration memory, users must send a sequence of commands to the device toinitiate the readback procedure. Once initiated, the device dumps the contents of itsconfiguration memory to the SelectMAP or JTAG interface. The Accessing ConfigurationRegisters through the SelectMAP Interface section and IEEE Std 1149.1 JTAG describe thesteps for reading configuration memory.Users can send the readback command sequence from a custom microprocessor, CPLD, orFPGA-based system, or use iMPACT to perform JTAG-based readback verify. iMPACT, thedevice programming software provided with the ISE® software by Xilinx, can perform allreadback and comparison functions for Spartan-6 devices and report to the user whetherthere were any configuration errors.Once configuration memory is read from the device, the next step is to determine if thereare any errors by comparing the readback bitstream to the configuration bitstream. TheVerifying Readback Data section explains how this is done.Preparing a Design for ReadbackThere are two mandatory bitstream settings for readback using JTAG or SelectMAP: theBitGen security setting must not prohibit readback (-g Security:none), and bitstreamencryption must not be used. Additionally, if readback is to be performed through theSelectMAP interface, the port must be set to retain its function after configuration bysetting the persist option in BitGen (-g Persist:Yes), otherwise the SelectMAP data pinsrevert to user I/O, precluding further configuration operations. Beyond these security andencryption requirements, no special considerations are necessary to enable readbackthrough the boundary-scan port. Also, these requirements are not necessary when usingreadback via the ICAP. Limitations for readback are:•Performing a readback while the design is in operation (without providing ashutdown command) results in reading back invalid block RAM data. The actualcontents of the block RAM are unaffected.•Performing a readback (with or without a shutdown command) corrupts the contentsof block RAMs configured in 9K mode.Chapter 8:Readback CRC•In addition, the JTAG instruction register (IR) must not contain any configurationinstructions (CFG_IN, CFG_OUT, or ISC_ENABLE). When these instructions arepresent, at any time, the readback CRC logic can not access the configuration logicand cannot run. Any configuration operation performed via the JTAG interfaceshould finish by loading the IR with a value other than these three configurationinstructions.These dynamically changeable memory locations are masked during backgroundreadback:•Look-up tables (LUTs) configured as distributed RAM or shift registers are notchecked. In Spartan-6 FPGAs, only SLICEMs can be configured as these memoryelements. Due to the granularity of the LUT masking, any LUTs in the same verticalalignment as a LUTRAM or SRL16 in a given frame are not checked. To ensuremaximum coverage of the readback CRC, these LUTs used as memories must be keptin separate frames from the LUTs used for logic.•Block RAM content is dynamic, so it is not expected to be the same as the initialconfiguration; therefore, these elements are not checked.•Use of the PLL DRP is not masked; therefore, any change to the PLL results in a CRCerror.•The I/O interface DRP at the top and bottom can be masked; however, LUTs for CLBsin the same frame are also masked. Similarly, masking LUTs in the top or bottomframe will also mask the I/O interface.CRC MaskingConfiguration data is organized into frames. Each frame of data configures portions ofmultiple configurable logic blocks (CLBs), and multiple frames are needed to configure asingle CLB. The granularity of masking for the Spartan-6FPGA is at a single frame thatspans several CLBs. To understand the coverage of the CRC, it is necessary to understandthe masking details. Three masking scenarios are presented:•CLBs containing LUTs configured as distributed RAM•CLBs near top or bottom IOI DRP•CLBs near top or bottom IOI DRP with LUT configured as distributed RAMNote:Distributed RAM is a LUT configured as a distributed RAM or a shift register.Chapter 10:Advanced JTAG ConfigurationsJTAG Configuration/Readback3.Overwrite the FPGA configuration with a design that does not use inversion at the inputs.4.Modify the original design to avoid the IOB invert path.JSTART and JSHUTDOWN are instructions specific to the Spartan-6 architecture and configuration flow. In Spartan-6 devices, the TAP controller is not reset by thePROGRAM_B pin and can only be reset by bringing the controller to the TLR state. The TAP controller is reset on power up.For details on the standard boundary-scan instructions EXTEST, INTEST, and BYPASS, refer to IEEE Std 1149.1.Boundary-Scan ArchitectureSpartan-6 device registers include all registers required by IEEE Std 1149.1. In addition to the standard registers, the family contains optional registers for simplified testing and verification (Table 10-1).Boundary-Scan RegisterThe test primary data register is the boundary-scan register. Boundary-scan operation is independent of individual IOB configuration. Each IOB, bonded or unbonded, starts as bidirectional with 3-state control. Later, it can be configured to be an input, output, or 3-state only. Therefore, three data register bits are provided per IOB (Figure 10-1).When conducting a data register (DR) operation, the DR captures data in a parallel fashion during the CAPTURE-DR state. The data is then shifted out and replaced by new data during the SHIFT-DR state. For each bit of the DR, an update latch is used to hold the input data stable during the next SHIFT-DR state. The data is then latched during the UPDATE-DR state when TCK is Low.The update latch is opened each time the TAP controller enters the UPDATE-DR state. Care is necessary when exercising an INTEST or EXTEST to ensure that the proper data has been latched before exercising the command. This is typically accomplished by using the SAMPLE instruction.Table 10-1:Spartan-6 FPGA JTAG Registers Register Name Register LengthDescription Boundary-Scan Register 3bits per I/OControls and observes input, output, and output enable Instruction Register 6bitsHolds current instruction opcode and captures internal device status BYPASS Register 1bitBypasses the device Identification Register 32bitsCaptures the Device ID JTAG Configuration Register 16bitsAllows access to the configuration bus when using the CFG_IN or CFG_OUT instructions USERCODE Register 32bitsCaptures the user-programmable code User-Defined Registers (USER1,USER2, USER3, and USER4)Design specific Design specificChapter 10:Advanced JTAG Configurations。

FPGA可编程逻辑器件芯片XC2S200E-7FG456C中文规格书

ConfigurationSpartan-3 devices are configured by loading application specific configuration data into the internal configuration memory. Configuration is carried out using a subset of the device pins, some of which are "Dedicated" to one function only, while others, indicated by the term "Dual-Purpose", can be re-used as general-purpose User I/Os once configuration is complete.Depending on the system design, several configuration modes are supported, selectable via mode pins. The mode pins M0, M1, and M2 are Dedicated pins. The mode pin settings are shown in Table 26.The HSWAP_EN input pin defines whether the I/O pins that are not actively used during configuration have pull-up resistorsduring configuration. By default, HSWAP_EN is tied High (via an internal pull-up resistor if left floating) which shuts off the pull-up resistors on the user I/O pins during configuration. When HSWAP_EN is tied Low, user I/Os have pull-ups during configuration. The Dedicated configuration pins (CCLK, DONE, PROG_B, M2, M1, M0, HSWAP_EN) and the JTAG pins (TDI, TMS, TCK, and TDO) always have a pull-up resistor to VCCAUX during configuration, regardless of the value on the HSWAP_EN pin. Similarly, the dual-purpose INIT_B pin has an internal pull-up resistor to VCCO_4 or VCCO_BOTTOM, depending on the package style.Depending on the chosen configuration mode, the FPGA either generates a CCLK output, or CCLK is an input accepting an externally generated clock.A persist option is available which can be used to force the configuration pins to retain their configuration function even after device configuration is complete. If the persist option is not selected then the configuration pins with the exception of CCLK, PROG_B, and DONE can be used as user I/O in normal operation. The persist option does not apply to the boundary-scan related pins. The persist feature is valuable in applications that readback configuration data after entering the User mode.Table 27 lists the total number of bits required to configure each FPGA as well as the PROMs suitable for storing those bits. See DS123: Platform Flash In-System Programmable Configuration PROMs data sheet for more information.The maximum bitstream length that Spartan-3 FPGAs support in serial daisy-chains is 4,294,967,264 bits (4Gbits), roughly equivalent to a daisy-chain with 323 XC3S5000 FPGAs. This is a limit only for serial daisy-chains where configuration data is passed via the FPGA’s DOUT pin. There is no such limit for JTAG chains.Table 26:Spartan-3 FPGAs Configuration Mode Pin SettingsConfiguration Mode (1)M0M1M2Synchronizing ClockData WidthSerial DOUT (2)Master Serial 000CCLK Output 1Y es Slave Serial 111CCLK Input 1Y es Master Parallel 110CCLK Output 8No Slave Parallel 011CCLK Input 8No JTAG 11TC K Input1NoNotes:1.The voltage levels on the M0, M1, and M2 pins select the configuration mode.2.The daisy chain is possible only in the Serial modes when DOUT is used.Table 27:Spartan-3 FPGA Configuration DataDevice File Sizes Xilinx Platform Flash PROMSerial ConfigurationParallel ConfigurationXC3S50439,264XCF01S XCF08P XC3S2001,047,616XCF01S XCF08P XC3S4001,699,136XCF02S XCF08P XC3S10003,223,488XCF04S XCF08P XC3S15005,214,784XCF08P XCF08P XC3S20007,673,024XCF08P XCF08P XC3S400011,316,864XCF16P XCF16P XC3S500013,271,936XCF16PXCF16PSwitching CharacteristicsAll Spartan-3 devices are available in two speed grades: –4 and the higher performance –5. Switching characteristics in this document may be designated as Advance, Preliminary, or Production. Each category is defined as follows:Advance: These specifications are based on simulations only and are typically available soon after establishing FPGA specifications. Although speed grades with this designation are considered relatively stable and conservative, some under-reported delays may still occur.Preliminary: These specifications are based on complete early silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting preliminary delays is greatly reduced compared to Advance data.Production: These specifications are approved once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.Production-quality systems must use FPGA designs compiled using a Production status speed file. FPGAs designs using a less mature speed file designation may only be used during system prototyping or preproduction qualification. FPGA designs using Advance or Preliminary status speed files should never be used in a production-quality system.Whenever a speed file designation changes, as a device matures toward Production status, rerun the Xilinx ISE software on the FPGA design to ensure that the FPGA design incorporates the latest timing information and software updates.All specified limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the following applies: Parameter values apply to all Spartan-3 devices. All parameters representing voltages are measured with respect to GND.Selected timing parameters and their representative values are included below either because they are important as general design requirements or they indicate fundamental device performance characteristics. The Spartan-3 FPGA v1.38 speed files are the original source for many but not all of the values. The v1.38 speed files are available in Xilinx Integrated Software Environment (ISE) software version 8.2i.The speed grade designations for these files are shown in T able39. For more complete, more precise, and worst-case data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotated to the simulation netlist.Table 39:Spartan-3 FPGA Speed Grade Designations (ISE v8.2i or Later)Device Advance Preliminary ProductionXC3S50-4, -5 (v1.37 and later)XC3S200XC3S400XC3S1000XC3S1500XC3S2000XC3S4000XC3S5000-4, -5 (v1.38 and later)Spartan-3 FPGA Family: Pinout DescriptionsTable 70:Spartan-3 FPGA Pin DefinitionsPin Name Direction DescriptionI/O: General-purpose I/O pinsI/O User-defined as input, output,bidirectional, three-state output,open-drain output, open-sourceoutput User I/O:Unrestricted single-ended user-I/O pin. Supports all I/O standards except the differential standards.I/O_Lxxy_#User-defined as input, output,bidirectional, three-state output,open-drain output, open-sourceoutput User I/O, Half of Differential Pair:Unrestricted single-ended user-I/O pin or half of a differential pair. Supports all I/O standards including the differential standards.DUAL: Dual-purpose configuration pinsIO_Lxxy_#/DIN/D0, IO_Lxxy_#/D1,IO_Lxxy_#/D2,IO_Lxxy_#/D3,IO_Lxxy_#/D4,IO_Lxxy_#/D5,IO_Lxxy_#/D6,IO_Lxxy_#/D7Input during configurationPossible bidirectional I/O afterconfiguration if SelectMap port isretainedOtherwise, user I/O afterconfigurationConfiguration Data Port:In Parallel (SelectMAP) modes, D0-D7 are byte-wide configuration datapins. These pins become user I/Os after configuration unless theSelectMAP port is retained via the Persist bitstream option.In Serial modes, DIN (D0) serves as the single configuration data input.This pin becomes a user I/O after configuration unless retained by thePersist bitstream option.IO_Lxxy_#/CS_B Input during Parallel modeconfigurationPossible input after configuration if SelectMap port is retained Otherwise, user I/O after configuration Chip Select for Parallel Mode Configuration:In Parallel (SelectMAP) modes, this is the active-Low Chip Select signal. This pin becomes a user I/O after configuration unless the SelectMAP port is retained via the Persist bitstream option.IO_Lxxy_#/RDWR_B Input during Parallel modeconfigurationPossible input after configurationif SelectMap port is retainedOtherwise, user I/O afterconfiguration Read/Write Control for Parallel Mode Configuration:In Parallel (SelectMAP) modes, this is the active-Low Write Enable, active-High Read Enable signal. This pin becomes a user I/O after configuration unless the SelectMAP port is retained via the Persist bitstream option.IO_Lxxy_#/ BUSY/DOUT Output during configurationPossible output afterconfiguration if SelectMap port isretainedOtherwise, user I/O afterconfigurationConfiguration Data Rate Control for Parallel Mode, Serial DataOutput for Serial Mode:In Parallel (SelectMAP) modes, BUSY throttles the rate at whichconfiguration data is loaded. This pin becomes a user I/O afterconfiguration unless the SelectMAP port is retained via the Persistbitstream option.In Serial modes, DOUT provides preamble and configuration data todownstream devices in a multi-FPGA daisy-chain. This pin becomes auser I/O after configuration.IO_Lxxy_#/INIT_B Bidirectional (open-drain) duringconfigurationUser I/O after configuration Initializing Configuration Memory/Detected Configuration Error: When Low, this pin indicates that configuration memory is being cleared. When held Low, this pin delays the start of configuration. After this pin is released or configuration memory is cleared, the pin goes High. During configuration, a Low on this output indicates that a configuration data error occurred. This pin always has an internal pull-up resistor to VCCO_4 or VCCO_BOTTOM during configuration, regardless of the HSWAP_EN pin. This pin becomes a user I/O after configuration.DCI: Digitally Controlled Impedance reference resistor input pinsIO_Lxxy_#/VRN_# or IO/VRN_#Input when using DCIOtherwise, same as I/ODCI Reference Resistor for NMOS I/O Transistor (per bank):If using DCI, a 1% precision impedance-matching resistor is connectedbetween this pin and the VCCO supply for this bank. Otherwise, this pin isa user I/O.IO_Lxxy_#/VRP_# or IO/VRP_#Input when using DCIOtherwise, same as I/ODCI Reference Resistor for PMOS I/O Transistor (per bank):If using DCI, a 1% precision impedance-matching resistor is connectedbetween this pin and the ground supply. Otherwise, this pin is a user I/O.。

FPGA可编程逻辑器件芯片XC2S600E-6FGG456C中文规格书

Spartan-3 FPGA Design DocumentationThe functionality of the Spartan®-3 FPGA family is described in the following documents. The topics covered in each guide are listed.•UG331: Spartan-3 Generation FPGA User Guide •Clocking Resources•Digital Clock Managers (DCMs)•Block RAM•Configurable Logic Blocks (CLBs)-Distributed RAM -SRL16 Shift Registers -Carry and Arithmetic Logic•I/O Resources•Embedded Multiplier Blocks •Programmable Interconnect •ISE® Software Design Tools •IP C ores•Embedded Processing and Control Solutions •Pin Types and Package Overview •Package Drawings •Powering FPGAs•UG332: Spartan-3 Generation Configuration User Guide •Configuration Overview -Configuration Pins and Behavior -Bitstream Sizes•Detailed Descriptions by Mode-Master Serial Mode using Xilinx Platform Flash PROM-Slave Parallel (SelectMAP) using a Processor -Slave Serial using a Processor -JTAG Mode•ISE iMPACT Programming ExamplesCreate a Xilinx user account and sign up to receiveautomatic e-mail notification whenever this data sheet or the associated user guides are updated.For specific hardware examples, see the Spartan-3 FPGA Starter Kit board web page, which has links to various design examples and the user guide.DS099 (v3.1) June 27, 2013Product SpecificationThe output frequency (f CLKFX) can be expressed as a function of the incoming clock frequency (f CLKIN) as follows:f CLKFX = f CLKIN(CLKFX_MULTIPL Y/CLKFX_DIVIDE)Equation3 Regarding the two attributes, it is possible to assign any combination of integer values, provided that two conditions are met:•The two values fall within their corresponding ranges, as specified in Table18.•The f CLKFX frequency calculated from the above expression accords with the DCM’s operating frequency specifications.For example, if CLKFX_MULTIPL Y = 5 and CLKFX_DIVIDE = 3, then the frequency of the output clock signal would be 5/3 that of the input clock signal.DFS Frequency ModesThe DFS supports two operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DFS_FREQUENCY_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits the two DFS outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows both these outputs to operate at the highest possible frequencies. DFS With or Without the DLLThe DFS component can be used with or without the DLL component:Without the DLL, the DFS component multiplies or divides the CLKIN signal frequency according to the respective CLKFX_MULTIPL Y and CLKFX_DIVIDE values, generating a clock with the new target frequency on the CLKFX and CLKFX180 outputs. Though classified as belonging to the DLL component, the CLKIN input is shared with the DFS component. This case does not employ feedback loop; therefore, it cannot correct for clock distribution delay.With the DLL, the DFS operates as described in the preceding case, only with the additional benefit of eliminating the clock distribution delay. In this case, a feedback loop from the CLK0 output to the CLKFB input must be present.The DLL and DFS components work together to achieve this phase correction as follows: Given values for theCLKFX_MULTIPL Y and CLKFX_DIVIDE attributes, the DLL selects the delay element for which the output clock edge coincides with the input clock edge whenever mathematically possible. For example, when CLKFX_MULTIPL Y = 5 and CLKFX_DIVIDE = 3, the input and output clock edges will coincide every three input periods, which is equivalent in time to five output periods.Smaller CLKFX_MULTIPL Y and CLKFX_DIVIDE values achieve faster lock times. With no factors common to the two attributes, alignment will occur once with every number of cycles equal to the CLKFX_DIVIDE value. Therefore, it is recommended that the user reduce these values by factoring wherever possible. For example, given CLKFX_MULTIPL Y = 9 and CLKFX_DIVIDE = 6, removing a factor of three yields CLKFX_MULTIPL Y = 3 and CLKFX_DIVIDE = 2. While both value-pairs will result in the multiplication of clock frequency by 3/2, the latter value-pair will enable the DLL to lock more quickly.Table 18:DFS AttributesAttribute Description ValuesDFS_FREQUENCY_MODE Chooses between High Frequency and Low Frequency modes Low, HighCLKFX_MULTIPL Y Frequency multiplier constant Integer from 2 to 32 CLKFX_DIVIDE Frequency divisor constant Integer from 1 to 32Table 19:DFS SignalsSignal Direction DescriptionCLKFX Output Multiplies the CLKIN frequency by the attribute-value ratio (CLKFX_MULTIPL Y/CLKFX_DIVIDE) to generate a clock signal with a new target frequency.CLKFX180Output Generates a clock signal with same frequency as CLKFX, only shifted 180° out-of-phase.Both the Fixed Phase and Variable Phase operating modes employ this calculation. If the PHASE_SHIFT value is zero, then CLKFB and CLKIN will be in phase, the same as when the PS component is disabled. When the PHASE_SHIFT value is positive, the CLKFB signal will be shifted later in time with respect to CLKIN. If the attribute value is negative, the CLKFB signal will be shifted earlier in time with respect to CLKIN.The Fixed Phase ModeThis mode fixes the desired fine phase shift to a fraction of the T CLKIN, as determined by Equation4 and its user-selected PHASE_SHIFT value P. The set of waveforms insection [b] of Figure22 illustrates the relationship between CLKFB and CLKIN in the Fixed Phase mode. In the Fixed Phase mode, the PSEN, PSCLK and PSINCDEC inputs are not used andmust be tied to GND. Fixed phase shift requires ISE software version 10.1.03 or later.ConfigurationSpartan-3 devices are configured by loading application specific configuration data into the internal configuration memory. Configuration is carried out using a subset of the device pins, some of which are "Dedicated" to one function only, while others, indicated by the term "Dual-Purpose", can be re-used as general-purpose User I/Os once configuration is complete.Depending on the system design, several configuration modes are supported, selectable via mode pins. The mode pins M0, M1, and M2 are Dedicated pins. The mode pin settings are shown in Table 26.The HSWAP_EN input pin defines whether the I/O pins that are not actively used during configuration have pull-up resistorsduring configuration. By default, HSWAP_EN is tied High (via an internal pull-up resistor if left floating) which shuts off the pull-up resistors on the user I/O pins during configuration. When HSWAP_EN is tied Low, user I/Os have pull-ups during configuration. The Dedicated configuration pins (CCLK, DONE, PROG_B, M2, M1, M0, HSWAP_EN) and the JTAG pins (TDI, TMS, TCK, and TDO) always have a pull-up resistor to VCCAUX during configuration, regardless of the value on the HSWAP_EN pin. Similarly, the dual-purpose INIT_B pin has an internal pull-up resistor to VCCO_4 or VCCO_BOTTOM, depending on the package style.Depending on the chosen configuration mode, the FPGA either generates a CCLK output, or CCLK is an input accepting an externally generated clock.A persist option is available which can be used to force the configuration pins to retain their configuration function even after device configuration is complete. If the persist option is not selected then the configuration pins with the exception of CCLK, PROG_B, and DONE can be used as user I/O in normal operation. The persist option does not apply to the boundary-scan related pins. The persist feature is valuable in applications that readback configuration data after entering the User mode.Table 27 lists the total number of bits required to configure each FPGA as well as the PROMs suitable for storing those bits. See DS123: Platform Flash In-System Programmable Configuration PROMs data sheet for more information.The maximum bitstream length that Spartan-3 FPGAs support in serial daisy-chains is 4,294,967,264 bits (4Gbits), roughly equivalent to a daisy-chain with 323 XC3S5000 FPGAs. This is a limit only for serial daisy-chains where configuration data is passed via the FPGA’s DOUT pin. There is no such limit for JTAG chains.Table 26:Spartan-3 FPGAs Configuration Mode Pin SettingsConfiguration Mode (1)M0M1M2Synchronizing ClockData WidthSerial DOUT (2)Master Serial 000CCLK Output 1Y es Slave Serial 111CCLK Input 1Y es Master Parallel 110CCLK Output 8No Slave Parallel 011CCLK Input 8No JTAG 11TC K Input1NoNotes:1.The voltage levels on the M0, M1, and M2 pins select the configuration mode.2.The daisy chain is possible only in the Serial modes when DOUT is used.Table 27:Spartan-3 FPGA Configuration DataDevice File Sizes Xilinx Platform Flash PROMSerial ConfigurationParallel ConfigurationXC3S50439,264XCF01S XCF08P XC3S2001,047,616XCF01S XCF08P XC3S4001,699,136XCF02S XCF08P XC3S10003,223,488XCF04S XCF08P XC3S15005,214,784XCF08P XCF08P XC3S20007,673,024XCF08P XCF08P XC3S400011,316,864XCF16P XCF16P XC3S500013,271,936XCF16PXCF16P。

FPGA可编程逻辑器件芯片XC2S200-6FG456C中文规格书

VITA 57.1 FMC1 HPC Connector (Partially Populated)[Figure1-2, callout 30]The VC707 board implements two instances of the FMC HPC VITA 57.1 specification connector.This section discusses the FMC1 HPC J35 connector.Note:The FMC1 HPC J35 connector is a keyed connector oriented so that a plug-on card facesaway from the VC707 board.The VITA 57.1 FMC standard calls for two connector densities: a high pin count (HPC) and a lowpin count (LPC) implementation. A 400 pin 10x40 position connector form factor is used for bothversions. The HPC version is fully populated with all 400 pins present. The LPC version is partiallypopulated with 160 pins.The 10x40 rows of an FMC HPC connector provides pins for up to:•160 single-ended or 80 differential user-defined signals•10 GTX transceivers• 2 GTX clocks• 4 differential clocks•159 ground and 15 power connectionsThe VC707 board FMC1 HPC connector J35 implements a subset of the maximum signal and clockconnectivity capabilities:•80 differential user-defined pairs•34 LA pairs (LA00-LA33)•24 HA pairs (HA00-HA23)•22 HB pairs (HB00-HB21)•8 GTX transceivers• 2 GTX clocks• 2 differential clocksThe FMC1 HPC signals are distributed across GTX Quads 118 and 119. Each Quad has the VCCOvoltage connected to V ADJ.Note:The VC707 board VADJ voltage for the FMC1 HPC (J35) connector is determined by theFMC VADJ power sequencing logic described in FMC_VADJ Voltage Control.VITA 57.1 FMC2 HPC Connector (Partially Populated)[Figure1-2, callout 31]The VC707 board implements two instances of the FMC HPC VITA 57.1 specification connector.This section discusses the FMC2 HPC J37 connector.Note:The FMC2 HPC J37 connector is a keyed connector oriented so that a plug-on card facesaway from the VC707 board.The FMC standard calls for two connector densities: a High Pin Count (HPC) and a Low Pin Count(LPC) implementation. A 400pin 10x40 position connector form factor is used for both versions.The HPC version is fully populated with all 400 pins present. The LPC version is partially populatedwith 160 pins.C2FMC2_HPC_DP0_C2M_P (1)N2D1PWRCTL1_VCC4B_PG AL32C3FMC2_HPC_DP0_C2M_N (1)N1D4FMC2_HPC_GBTCLK0_M2C_P (1)K8C6FMC2_HPC_DP0_M2C_P (1)P8D5FMC2_HPC_GBTCLK0_M2C_N (1)K7C7FMC2_HPC_DP0_M2C_N (1)P7D8FMC2_HPC_LA01_CC_P LVCMOS18AF41C10FMC2_HPC_LA06_P LVCMOS18AD38D9FMC2_HPC_LA01_CC_N LVCMOS18AG41C11FMC2_HPC_LA06_N LVCMOS18AE38D11FMC2_HPC_LA05_P LVCMOS18AF42C14FMC2_HPC_LA10_P LVCMOS18AB41D12FMC2_HPC_LA05_N LVCMOS18AG42C15FMC2_HPC_LA10_N LVCMOS18AB42D14FMC2_HPC_LA09_P LVCMOS18AJ38C18FMC2_HPC_LA14_P LVCMOS18AB38D15FMC2_HPC_LA09_N LVCMOS18AK38C19FMC2_HPC_LA14_N LVCMOS18AB39D17FMC2_HPC_LA13_P LVCMOS18W40C22FMC2_HPC_LA18_CC_P LVCMOS18U36D18FMC2_HPC_LA13_N LVCMOS18Y40C23FMC2_HPC_LA18_CC_N LVCMOS18T37D20FMC2_HPC_LA17_CC_P LVCMOS18U37C26FMC2_HPC_LA27_P LVCMOS18P32D21FMC2_HPC_LA17_CC_N LVCMOS18U38C27FMC2_HPC_LA27_N LVCMOS18P33D23FMC2_HPC_LA23_P LVCMOS18R38C30FMC2_HPC_IIC_SCL U52.6D24FMC2_HPC_LA23_N LVCMOS18R39C31FMC2_HPC_IIC_SDA U52.5D26FMC2_HPC_LA26_P LVCMOS18N33C34GA0=0=GND D27FMC2_HPC_LA26_N LVCMOS18N34C35VCC12_P D29FMC2_HPC_TCK_BUF U19.13C37VCC12_P D30FMC1_TDO_FMC2_TDI U27.2C39VCC3V3D31FMC2_TDO_FPGA_TDI U46.3D32VCC3V3D33FMC2_HPC_TMS_BUF U19.16D34NCD35GA1=0=GND D36VCC3V3D38VCC3V3D40VCC3V3Table 1-28:J37 VITA 57.1 FMC 2 HPC Connections (Cont’d)J37FMC 2HPC PinSchematic Net NameI/O Standard U1 FPGA PinJ37 FMC 2 HPC PinSchematic Net NameI/O Standard U1 FPGA PinE2FMC2_HPC_HA01_CC_P LVCMOS18AD32F1FMC2_HPC_PG_M2C LVCMOS18AF29E3FMC2_HPC_HA01_CC_N LVCMOS18AD33F4FMC2_HPC_HA00_CC_P LVCMOS18AB33E6FMC2_HPC_HA05_P LVCMOS18Y32F5FMC2_HPC_HA00_CC_N LVCMOS18AC33E7FMC2_HPC_HA05_N LVCMOS18Y33F7FMC2_HPC_HA04_P LVCMOS18AB29E9FMC2_HPC_HA09_P LVCMOS18AE29F8FMC2_HPC_HA04_N LVCMOS18AC29E10FMC2_HPC_HA09_N LVCMOS18AE30F10FMC2_HPC_HA08_P LVCMOS18AA31E12FMC2_HPC_HA13_P LVCMOS18AE32F11FMC2_HPC_HA08_N LVCMOS18AA32E13FMC2_HPC_HA13_N LVCMOS18AE33F13FMC2_HPC_HA12_P LVCMOS18AF34E15FMC2_HPC_HA16_P LVCMOS18AG36F14FMC2_HPC_HA12_N LVCMOS18AG34E16FMC2_HPC_HA16_N LVCMOS18AH36F16FMC2_HPC_HA15_P LVCMOS18AE37E18FMC2_HPC_HA20_P LVCMOS18AD36F17FMC2_HPC_HA15_N LVCMOS18AF37E19FMC2_HPC_HA20_N LVCMOS18AD37F19FMC2_HPC_HA19_P LVCMOS18AC35E21FMC2_HPC_HB03_P LVCMOS18AT16F20FMC2_HPC_HA19_N LVCMOS18AC36E22FMC2_HPC_HB03_N LVCMOS18AU16F22FMC2_HPC_HB02_P LVCMOS18A V16E24FMC2_HPC_HB05_P LVCMOS18BA17F23FMC2_HPC_HB02_N LVCMOS18AW16E25FMC2_HPC_HB05_N LVCMOS18BB17F25FMC2_HPC_HB04_P LVCMOS18AU18E27FMC2_HPC_HB09_P LVCMOS18A V20F26FMC2_HPC_HB04_N LVCMOS18A V18E28FMC2_HPC_HB09_N LVCMOS18AW20F28FMC2_HPC_HB08_P LVCMOS18AY20E30FMC2_HPC_HB13_P LVCMOS18AT20F29FMC2_HPC_HB08_N LVCMOS18BA20E31FMC2_HPC_HB13_N LVCMOS18AT19F31FMC2_HPC_HB12_P LVCMOS18AU19E33FMC2_HPC_HB19_P LVCMOS18AP18F32FMC2_HPC_HB12_N LVCMOS18A V19E34FMC2_HPC_HB19_N LVCMOS18AP17F34FMC2_HPC_HB16_P LVCMOS18AR18E36FMC2_HPC_HB21_P LVCMOS18AN19F35FMC2_HPC_HB16_N LVCMOS18AR17E37FMC2_HPC_HB21_N LVCMOS18AN18F37FMC2_HPC_HB20_P LVCMOS18AK17E39V ADJF38FMC2_HPC_HB20_N LVCMOS18AL17F40V ADJTable 1-28:J37 VITA 57.1 FMC 2 HPC Connections (Cont’d)J37FMC 2HPC PinSchematic Net NameI/O Standard U1 FPGA PinJ37 FMC 2 HPC PinSchematic Net NameI/O Standard U1 FPGA PinAppendix B:VITA 57.1 FMC Connector Pinouts。

FPGA可编程逻辑器件芯片XC2S200-5FG456C中文规格书

0

SHIFT-IR

0

1 EXIT1-IR 1

0

PAUSE-IR

0

1 0 EXIT2-IR

1

UPDATE-IR

1

0

NOTE: The value shown adjacent to each state transition in this figure represents the signal present at TMS at the time of a rising edge at TCK.

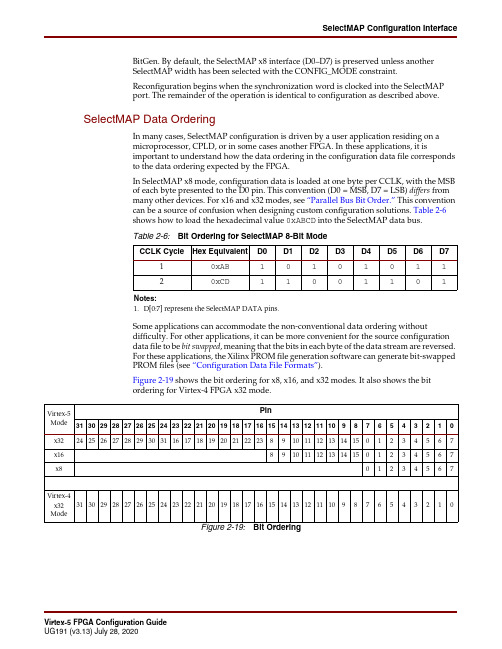

Table 2-6: Bit Ordering for SelectMAP 8-Bit Mode

CCLK Cycle Hex Equivalent D0 D1 D2 D3 D4 D5 D6 D7

1

0xAB

1

0

1

0

1

0

1

1

2

0xCD

1

1

0

0

1

1

0

1

Notes: 1. D[0:7] represent the SelectMAP DATA pins.

For details on the standard Boundary-Scan instructions EXTEST, INTEST, and BYPASS, refer to the IEEE Standard.

Virtex-5 FPGA Configuration Guide UG191 (v3.13) July 28, 2020

UG191_c3_02_050406

Figure 3-2: Boundary-Scan TAP Controller

Virtex-5 devices support the mandatory IEEE 1149.1 commands, as well as several Xilinx vendor-specific commands. The EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, USERCODE, and HIGHZ instructions are all included. The TAP also supports internal user-defined registers (USER1, USER2, USER3, and USER4) and configuration/readback of the device.

FPGA可编程逻辑器件芯片XC2S200E-5FGG456I中文规格书

DDR3 Memory[Figure1-2, callout 2]The memory module at J1 is a 1GB DDR3 small outline dual-inline memory module (SODIMM).It provides volatile synchronous dynamic random access memory (SDRAM) for storing user codeand data.•Part number: MT8JTF12864HZ-1G6G1 (Micron Technology)•Supply voltage: 1.5V•Configuration: 1GB (128 Mb x 64)•Datapath width: 64bits•Data rate: Up to 1,600MT/sThe VC707 XC7VX485T FPGA memory interface performance is documented in the Virtex-7 Tand XT FPGAs Data Sheet: DC and AC Switching Characteristics (DS183) [Ref2].The DDR3 interface is implemented across I/O banks 37, 38, and 39. Each bank is a 1.5Vhigh-performance bank having a dedicated DCI VRP/N resistor connection. An external 0.75Vreference VTTREF is provided for data interface banks 37 and 39. Any interface connected to thesebanks that requires a reference voltage must use this FPGA voltage reference. The connectionsbetween the DDR3 memory and the FPGA are listed in Table1-4.Table 1-4:DDR3 Memory Connections to the FPGAFPGA (U1) Pin Net Name I/O StandardJ1 DDR3 MemoryPin Number Pin NameA20DDR3_A0SSTL1598A0B19DDR3_A1SSTL1597A1C20DDR3_A2SSTL1596A2A19DDR3_A3SSTL1595A3A17DDR3_A4SSTL1592A4A16DDR3_A5SSTL1591A5D20DDR3_A6SSTL1590A6C18DDR3_A7SSTL1586A7D17DDR3_A8SSTL1589A8C19DDR3_A9SSTL1585A9B21DDR3_A10SSTL15107A10/AP B17DDR3_A11SSTL1584A11A15DDR3_A12SSTL1583A12_BC_N A21DDR3_A13SSTL15119A13F17DDR3_A14SSTL1580A14E17DDR3_A15SSTL1578A15D21DDR3_BA0SSTL15109BA0C21DDR3_BA1SSTL15108BA1Clock GenerationThe VC707 board provides five clock sources for the FPGA. Table 1-9 lists the source devices for each clock.Table 1-10 lists the pin-to-pin connections from each clock source to the FPGA.Table 1-9:VC707 Board Clock SourcesClock Name Clock Source DescriptionSystem Clock U51SiT9102 2.5V LVDS 200MHz Fixed Frequency Oscillator (SiTime).See System Clock (SYSCLK_P and SYSCLK_N).User ClockU34Si570 3.3V LVDS I 2C Programmable Oscillator, 156.250MHz default (Silicon Labs).See Programmable User Clock (USER_CLOCK_P and USER_CLOCK_N).User SMA Clock (differential pair)J31USER_SMA_CLOCK_P (Net name).See User SMA Clock (USER_SMA_CLOCK_P and USER_SMA_CLOCK_N).J32USER_SMA_CLOCK_N (Net name).See User SMA Clock (USER_SMA_CLOCK_P and USER_SMA_CLOCK_N).GTX SMA REF Clock (differential pair)J25SMA_MGT_REFCLK_C_P (Net name).See GTX SMA Clock (SMA_MGT_REFCLK_P and SMA_MGT_REFCLK_N).J26SMA_MGT_REFCLK_C_N (Net name).See GTX SMA Clock (SMA_MGT_REFCLK_P and SMA_MGT_REFCLK_N).Jitter AttenuatedClockU24Si5324C LVDS precision clock multiplier/jitter attenuator (Silicon Labs).See Jitter Attenuated Clock .Table 1-10:Clock Connections, Source to FPGAClock Source PinNet Name I/O StandardFPGA (U1) PinU51.5SYSCLK_N LVDS E18U51.4SYSCLK_P LVDS E19U34.5USER_CLOCK_N LVDS AL34U34.4USER_CLOCK_P LVDSAK34J26.1SMA_MGT_REFCLK_N N/A (MGT REFCLK INPUT)AK7J25.1SMA_MGT_REFCLK_P N/A (MGT REFCLK INPUT)AK8J32.1USER_SMA_CLOCK_N LVCMOS18AK32J31.1USER_SMA_CLOCK_PLVCMOS18AJ32U24.29Si5324_OUT_N N/A (MGT REFCLK INPUT)AD7U24.28Si5324_OUT_PN/A (MGT REFCLK INPUT)AD8Chapter 1:VC707 Evaluation Board FeaturesXADC Analog-to-Digital Converter7series FPGAs provide an analog front end XADC block. The XADC block includes a dual 12-bit,1MSPS analog-to-digital convertor (ADC) and on-chip sensors. See 7Series FPGAs XADC Dual12-Bit 1MSPS Analog-to-Digital Converter User Guide (UG480) [Ref11] for details on thecapabilities of the analog front end. Figure1-34 shows the XADC block diagram.Figure 1-34:XADC Block DiagramThe VC707 board supports both the internal FPGA sensor measurements and the externalmeasurement capabilities of the XADC. Internal measurements of the die temperature, VCCINT,VCCAUX, and VCCBRAM are available. The VC707 board VCCINT and VCCBRAM areprovided by a common 1.0 V supply.Jumper J42 can be used to select either an external differential voltage reference (VREF) or on-chipvoltage reference for the analog-to-digital converter.Appendix A:Default Switch and Jumper SettingsAppendix B:VITA 57.1 FMC Connector Pinouts。

FPGA可编程逻辑器件芯片XC2S200-5FGG456I中文规格书

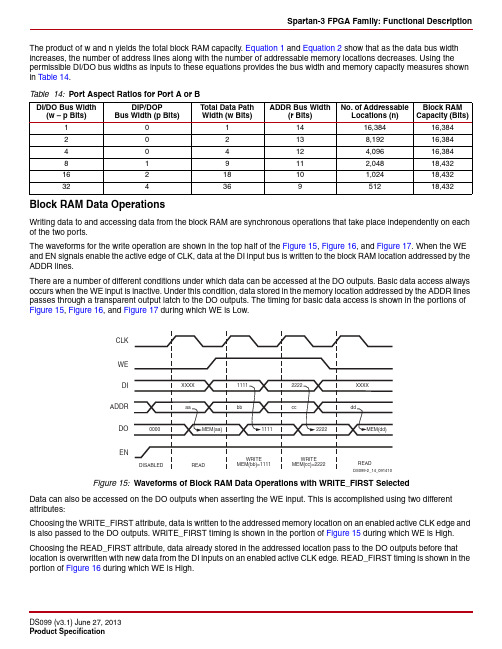

The product of w and n yields the total block RAM capacity. Equation 1 and Equation 2 show that as the data bus width increases, the number of address lines along with the number of addressable memory locations decreases. Using the permissible DI/DO bus widths as inputs to these equations provides the bus width and memory capacity measures shown in T able 14.Block RAM Data OperationsWriting data to and accessing data from the block RAM are synchronous operations that take place independently on eachof the two ports.The waveforms for the write operation are shown in the top half of the Figure 15, Figure 16, and Figure 17. When the WE and EN signals enable the active edge of CLK, data at the DI input bus is written to the block RAM location addressed by the ADDR lines.There are a number of different conditions under which data can be accessed at the DO outputs. Basic data access always occurs when the WE input is inactive. Under this condition, data stored in the memory location addressed by the ADDR lines passes through a transparent output latch to the DO outputs. The timing for basic data access is shown in the portions of Figure 15, Figure 16, and Figure 17 during which WE is Low.Data can also be accessed on the DO outputs when asserting the WE input. This is accomplished using two different attributes:Choosing the WRITE_FIRST attribute, data is written to the addressed memory location on an enabled active CLK edge and is also passed to the DO outputs. WRITE_FIRST timing is shown in the portion of Figure 15 during which WE is High.Choosing the READ_FIRST attribute, data already stored in the addressed location pass to the DO outputs before that location is overwritten with new data from the DI inputs on an enabled active CLK edge. READ_FIRST timing is shown in the portion of Figure 16 during which WE is High.Table 14:Port Aspect Ratios for Port A or BDI/DO Bus Width (w – p Bits)DIP/DOP Bus Width (p Bits)Total Data Path Width (w Bits)ADDR Bus Width(r Bits)No. of Addressable Locations (n)Block RAM Capacity (Bits)1011416,38416,384202138,19216,384404124,09616,384819112,04818,43216218101,02418,43232436951218,432Figure 15:Waveforms of Block RAM Data Operations with WRITE_FIRST SelectedFigure 16:Waveforms of Block RAM Data Operations with READ_FIRST SelectedChoosing a third attribute called NO_CHANGE puts the DO outputs in a latched state when asserting WE. Under this condition, the DO outputs will retain the data driven just before WE was asserted. NO_CHANGE timing is shown in the portion of Figure17 during which WE is High.Figure 17:Waveforms of Block RAM Data Operations with NO_CHANGE SelectedDedicated MultipliersAll Spartan-3 devices provide embedded multipliers that accept two 18-bit words as inputs to produce a 36-bit product. This section provides an introduction to multipliers. For further details, refer to the chapter entitled “Using Embedded Multipliers” in UG331.The input buses to the multiplier accept data in two’s-complement form (either 18-bit signed or 17-bit unsigned). One such multiplier is matched to each block RAM on the die. The close physical proximity of the two ensures efficient data handling. Cascading multipliers permits multiplicands more than three in number as well as wider than 18-bits. The multiplier is placed in a design using one of two primitives: an asynchronous version called MULT18X18 and a version with a register called MULT18X18S, as shown in Figure18. The signals for these primitives are defined in T able15.The CORE Generator system produces multipliers based on these primitives that can be configured to suit a wide range of requirements.Digital Clock Manager (DCM)Spartan-3 devices provide flexible, complete control over clock frequency, phase shift and skew through the use of the DCM feature. T o accomplish this, the DCM employs a Delay-Locked Loop (DLL), a fully digital control system that uses feedback to maintain clock signal characteristics with a high degree of precision despite normal variations in operating temperature and voltage. This section provides a fundamental description of the DCM. For further information, refer to the chapter entitled “Using Digital Clock Managers” in UG331.Each member of the Spartan-3 family has four DCMs, except the smallest, the XC3S50, which has two DCMs. The DCMs are located at the ends of the outermost Block RAM column(s). See Figure 1, page 3. The Digital Clock Manager is placed in a design as the “DCM” primitive.The DCM supports three major functions: •Clock-skew Elimination: Clock skew describes the extent to which clock signals may, under normal circumstances,deviate from zero-phase alignment. It occurs when slight differences in path delays cause the clock signal to arrive at different points on the die at different times. This clock skew can increase set-up and hold time requirements as well as clock-to-out time, which may be undesirable in applications operating at a high frequency, when timing is critical. The DCM eliminates clock skew by aligning the output clock signal it generates with another version of the clock signal that is fed back. As a result, the two clock signals establish a zero-phase relationship. This effectively cancels out clock distribution delays that may lie in the signal path leading from the clock output of the DCM to its feedback input.•Frequency Synthesis: Provided with an input clock signal, the DCM can generate a wide range of different output clock frequencies. This is accomplished by either multiplying and/or dividing the frequency of the input clock signal by any of several different factors.Figure 18:Embedded Multiplier PrimitivesTable 15:Embedded Multiplier Primitives DescriptionsSignal Name Direction FunctionA[17:0]Input Apply one 18-bit multiplicand to these inputs. The MULT18X18S primitive requires a setup time before the enabled rising edge of CLK.B[17:0]Input Apply the other 18-bit multiplicand to these inputs. The MULT18X18S primitive requires a setup time before the enabled rising edge of CLK.P[35:0]Output The output on the P bus is a 36-bit product of the multiplicands A and B. In the case of the MULT18X18S primitive, an enabled rising CLK edge updates the P bus.CLK Input (1)CLK is only an input to the MULT18X18S primitive. The clock signal applied to this input, when enabled by CE, updates the output register that drives the P bus.CE Input (1)CE is only an input to the MULT18X18S primitive. Enable for the CLK signal. Asserting this input enables the CLK signal to update the P bus.RST Input (1)RST is only an input to the MULT18X18S primitive. Asserting this input resets the output register on an enabled, rising CLK edge, forcing the P bus to all zeroes.Notes:1.The control signals CLK, CE and RST have the option of inverted polarity.Spartan-3 FPGA Family: DC and Switching CharacteristicsSpartan-3 FPGA Family: Pinout Descriptions。

FPGA可编程逻辑器件芯片XC2S300E-FG456中文规格书

FPGA可编程逻辑器件芯片XC2V1000-4FG456C中文规格书