XC9510H1333中文资料

Xeon处理器型号详解

英特尔至强处理器型号大全第1页:双核至强UP:3000、3100系列3000系列“Conroe”酷睿---扣肉2006年9月末英特尔发布了代号为“Conroe”(产品代码80557)的双核至强3000系列CPU,它只不过是英特尔主流“Conroe”的重新贴牌产品,商标采用了酷睿2 Duo(用于消费级的桌面产品),和其它大多数至强处理器不同,它们只支持单CPU运算,使用Socket T (LGA775),前端总线速度1066MHz,支持英特尔增强的自动降频和虚拟化技术,但不支持超线程。

主频二级缓存L2 CACHE 前端总线散热设计功耗3100系列“Wolfdale”狼之谷代号为“Wolfdale”(产品代码80570)3100系列双核至强CPU只是对英特尔主流产品Wolfdale进行了重新包装,采用相同的65纳米制造工艺和6MB二级缓存,和大多数至强不同,它们仅支持单CPU运算,使用Socket T (LGA775),前端总线1333MHz,支持增强的自动降频和虚拟化技术,但不支持超线程。

主频二级缓存L2 CACHE 前端总线散热设计功耗第2页:四核至强UP:3200、3300、3400和3500系列——英特尔的多核之路:四核、六核至强3200系列“Kentsfield”2007年1月7日,英特尔发布了重新包装过的四核(2x2)酷睿2 Quad处理器,即至强3200系列(产品代码80562),2x2四核心包括两个独立的双核芯片,包括三个型号X3210、X3220和X3230,分别运行在2.13GHz、2.4GHz 和2.66GHz。

和300系列类似,这些型号只支持单CPU运算,前端总线1066MHz,其目标定位于刀片服务器市场,X3220也当作Core2 Quad Q6600销售,X3230对应到Q6700。

主频二级缓存L2 CACHE 前端总线散热设计功耗3300系列“Yorkfield”英特尔发布重新包装的四核酷睿2 Quad Yorkfield Q9400和Q9x50处理器时,同期发布了至强3300系列(产品代码80569),它包含两个独立的双核芯片,采用了45纳米制造工艺,型号包括X3320、X3350、X3360和X3370,分别运行在2.50GHz、2.66GHz、2.83GHz和3.0GHz,每个芯片统一使用6MB二级缓存(但X3320每块芯片二级缓存只有3MB),前端总线1333MHz,所有型号都支持英特尔64位(x86-64实现),XD位和虚拟化技术,也支持按需供电,使用LAG775 Socket。

XC9536XL-5PCG44C中文资料

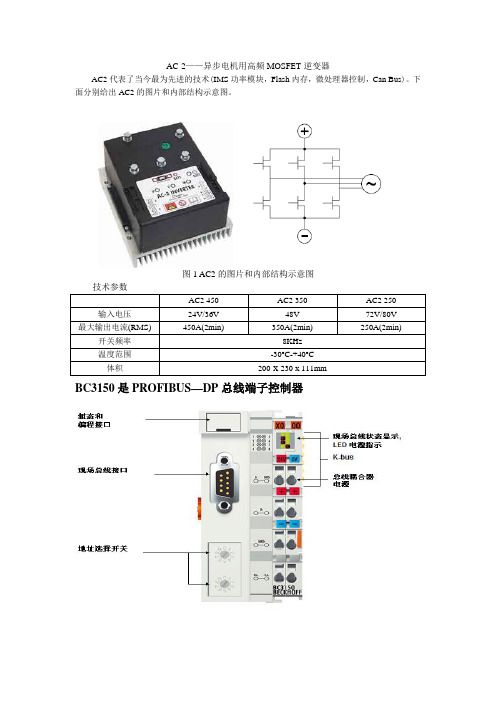

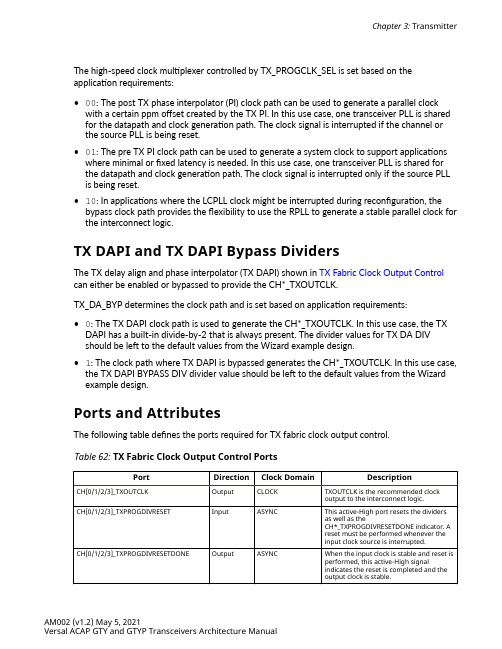

© 2006 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.Features• 5 ns pin-to-pin logic delays•System frequency up to 178 MHz •36 macrocells with 800 usable gates •Available in small footprint packages -44-pin PLCC (34 user I/O pins)-44-pin VQFP (34 user I/O pins)-48-pin CSP (36 user I/O pins)-64-pin VQFP (36 user I/O pins)-Pb-free available for all packages•Optimized for high-performance 3.3V systems -Low power operation-5V tolerant I/O pins accept 5 V, 3.3V, and 2.5Vsignals- 3.3V or 2.5V output capability-Advanced 0.35 micron feature size CMOSFast FLASH™ technology •Advanced system features -In-system programmable-Superior pin-locking and routability withFast CONNECT™ II switch matrix -Extra wide 54-input Function Blocks-Up to 90 product-terms per macrocell withindividual product-term allocation-Local clock inversion with three global and oneproduct-term clocks-Individual output enable per output pin-Input hysteresis on all user and boundary-scan pininputs-Bus-hold circuitry on all user pin inputs-Full IEEE Standard 1149.1 boundary-scan (JTAG) •Fast concurrent programming•Slew rate control on individual outputs •Enhanced data security features •Excellent quality and reliability-Endurance exceeding 10,000 program/erasecycles-20 year data retention-ESD protection exceeding 2,000V•Pin-compatible with 5V-core XC9536 device in the 44-pin PLCC package and the 48-pin CSP packageWARNING: Programming temperature range of T A = 0° C to +70° CDescriptionThe XC9536XL is a 3.3V CPLD targeted for high-perfor-mance, low-voltage applications in leading-edge communi-cations and computing systems. It is comprised of two54V18 Function Blocks, providing 800 usable gates with propagation delays of 5ns. See Figure 2 for architecture overview.Power EstimationPower dissipation in CPLDs can vary substantially depend-ing on the system frequency, design application and output loading. To help reduce power dissipation, each macrocell in a XC9500XL device may be configured for low-power mode (from the default high-performance mode). In addi-tion, unused product-terms and macrocells are automati-cally deactivated by the software to further conserve power.For a general estimate of I CC , the following equation may be used:I CC (mA) = MC HS (0.175*PT HS + 0.345) + MC LP (0.052*PT LP+ 0.272) + 0.04 * MC TOG (MC HS +MC LP )* fwhere:MC HS = # macrocells in high-speed configurationPT HS = average number of high-speed product terms per macrocellMC LP = # macrocells in low power configurationPT LP = average number of low power product terms per macrocellf = maximum clock frequencyMCTOG = average % of flip-flops toggling per clock (~12%)This calculation was derived from laboratory measurements of an XC9500XL part filled with 16-bit counters and allowing a single output (the LSB) to be enabled. The actual I CC value varies with the design application and should be veri-fied during normal system operation. Figure 1 shows the above estimation in a graphical form. For a more detailed discussion of power consumption in this device, see XilinxXC9536XL High Performance CPLDDS058 (v1.9) April 3, 2007Product Specificationapplication note XAPP114, “Understanding XC9500XLCPLD Power.”Figure 1: Typical I CC vs. Frequency for XC9536XLFigure 2: XC9536XL ArchitectureFunction Block outputs (indicated by the bold line) drive the I/O Blocks directly.2DS058 (v1.9) April 3, 2007Absolute Maximum Ratings (2)Recommended Operation ConditionsQuality and Reliability CharacteristicsDC Characteristic Over Recommended Operating ConditionsSymbol DescriptionValue Units V CC Supply voltage relative to GND –0.5 to 4.0V V IN Input voltage relative to GND (1)–0.5 to 5.5V V TS Voltage applied to 3-state output (1)–0.5 to 5.5VT STG Storage temperature (ambient)(3)–65 to +150o C T JJunction temperature+150o CNotes:1.Maximum DC undershoot below GND must be limited to either 0.5V or 10 mA, whichever is easier to achieve. During transitions, thedevice pins may undershoot to –2.0 V or overshoot to +7.0V, provided this over- or undershoot lasts less than 10 ns and with the forcing current being limited to 200 mA. External I/O voltage may not exceed V CCINT by 4.0V.2.Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stressratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.3.For soldering guidelines and thermal considerations, see the Device Packaging information on the Xilinx website. For Pb-freepackages, see XAPP427.Symbol ParameterMin Max Units V CCINT Supply voltage for internal logic and input buffersCommercial T A = 0o C to 70o C 3.0 3.6V Industrial T A = –40o C to +85o C3.0 3.6V V CCIO Supply voltage for output drivers for 3.3V operation 3.0 3.6V Supply voltage for output drivers for 2.5V operation 2.3 2.7V V IL Low-level input voltage 00.80V V IH High-level input voltage 2.0 5.5V V OOutput voltageV CCIOVSymbol ParameterMin Max Units T DR Data Retention20-Years N PE Program/Erase Cycles (Endurance)10,000-Cycles V ESDElectrostatic Discharge (ESD)2,000-VoltsSymbol ParameterTest ConditionsMin Max Units V OH Output high voltage for 3.3V outputs I OH = –4.0 mA 2.4-V Output high voltage for 2.5V outputs I OH = –500 μA 90%V CCIO-V V OL Output low voltage for 3.3V outputs I OL = 8.0 mA -0.4V Output low voltage for 2.5V outputs I OL = 500 μA-0.4V I IL Input leakage current V CC = Max; V IN = GND or V CC -±10μA I IH I/O high-Z leakage current V CC = Max; V IN = GND or V CC -±10μA I IHI/O high-Z leakage currentV CC = Max; V CCIO = Max; V IN = GND or 3.6V -±10μA V CC Min < V IN < 5.5V-±50μA C IN I/O capacitanceV IN = GND; f = 1.0 MHz-10pF I CCOperating supply current (low power mode, active)V IN = GND, No load; f = 1.0 MHz10 (Typical)mA4DS058 (v1.9) April 3, 2007AC CharacteristicsSymbol ParameterXC9536XL-5XC9536XL-7XC9536XL-10Units Min Max Min Max Min Max T PD I/O to output valid - 5.0-7.5-10.0ns T SU I/O setup time before GCK 3.7- 4.8- 6.5-ns T H I/O hold time after GCK 0-0-0-ns T CO GCK to output valid- 3.5- 4.5- 5.8ns f SYSTEM Multiple FB internal operating frequency-178.6-125-100MHzT PSU I/O setup time before p-term clock input 1.7- 1.6- 2.1-ns T PH I/O hold time after p-term clock input 2.0- 3.2- 4.4-ns T PCO P-term clock output valid - 5.5-7.7-10.2ns T OE GTS to output valid - 4.0- 5.0-7.0ns T OD GTS to output disable- 4.0- 5.0-7.0ns T POE Product term OE to output enabled -7.0-9.5-11.0ns T POD Product term OE to output disabled -7.0-9.5-11.0ns T AO GSR to output valid -10.0-12.0-14.5ns T PAO P-term S/R to output valid -10.5-12.6-15.3ns T WLH GCK pulse width (High or Low) 2.8- 4.0- 4.5-ns T APRPW Asynchronous preset/reset pulse width (High or Low)5.0-6.5-7.0-ns T PLHP-term clock pulse width (High or Low)5.0- 6.5-7.0-nsFigure 3: AC Load CircuitInternal Timing ParametersSymbol Parameter XC9536XL-5XC9536XL-7XC9536XL-10Units Min Max Min Max Min MaxBuffer DelaysT IN Input buffer delay- 1.5- 2.3- 3.5ns T GCK GCK buffer delay- 1.1- 1.5- 1.8ns T GSR GSR buffer delay- 2.0- 3.1- 4.5ns T GTS GTS buffer delay- 4.0- 5.0-7.0ns T OUT Output buffer delay- 2.0- 2.5- 3.0ns T EN Output buffer enable/disable delay-0-0-0ns Product Term Control DelaysT PTCK Product term clock delay- 1.6- 2.4- 2.7ns T PTSR Product term set/reset delay- 1.0- 1.4- 1.8ns T PTTS Product term 3-state delay- 5.5-7.2-7.5ns Internal Register and Combinatorial DelaysT PDI Combinatorial logic propagation delay-0.5- 1.3- 1.7ns T SUI Register setup time 2.3- 2.6- 3.0-ns T HI Register hold time 1.4- 2.2- 3.5-ns T ECSU Register clock enable setup time 2.3- 2.6- 3.0-ns T ECHO Register clock enable hold time 1.4- 2.2- 3.5-ns T COI Register clock to output valid time-0.4-0.5- 1.0ns T AOI Register async. S/R to output delay- 6.0- 6.4-7.0ns T RAI Register async. S/R recover before clock 5.07.510.0ns T LOGI Internal logic delay- 1.0- 1.4- 1.8ns T LOGILP Internal low power logic delay- 5.0- 6.4-7.3ns Feedback DelaysT F Fast CONNECT II feedback delay- 1.9- 3.5- 4.2ns Time AddersT PTA Incremental product term allocator delay-0.7-0.8- 1.0ns T SLEW Slew-rate limited delay- 3.0- 4.0- 4.5ns6DS058 (v1.9) April 3, 2007XC9536XL I/O Pins (2)XC9536XL Global, JTAG and Power Pins (1)Function Block Macro-cellPC44VQ44CS48VQ64BScanOrderFunction BlockMacro-cellPC44VQ44CS48VQ64BScan Order11240D6910521139D785112341C710102224438E5748135(1)43(1)B7(1)15(1)992342(1)36(1)E6(1)5(1)4514442C61196244337E7642156(1)44(1)B6(1)16(1)932540(1)34(1)F6(1)2(1)391682A619902639(1)33(1)G7(1)64(1)36177(1)1(1)A7(1)17(1)87273832G663331893C52084283731F5623019115B52281293630G56127110126A424782103529F46024111137B425752113428G45721112148A327722123327E356181131812B233692132923F250151141913B135662142822G148121152014C236632152721F14591162216C338602162620E24461172418D242572172519E1433118--D33954218--E449Notes:1.Global control pin.2.The pin-outs are the same for Pb-free versions of packages.Pin Type PC44VQ44CS48VQ64I/O/GCK1543B715I/O/GCK2644B616I/O/GCK371A717I/O/GTS14236E65I/O/GTS24034F62I/O/GSR 3933G764TCK 1711A130TDI 159B328TDO 3024G253TMS 1610A229V CCINT 3.3V 21, 4115, 35C1, F73, 37V CCIO 2.5V/3.3V3226G355GND 10, 23, 314, 17, 25A5, D1, F321, 41, 54No Connects--C4, D41, 4, 12, 13, 14, 18, 23, 26, 31, 32, 34, 40, 46, 47, 51, 52, 58, 59Notes:1.The pin-outs are the same for Pb-free versions of packages.Device Part Marking and Ordering Combination InformationDevice Ordering and Part Marking Number Speed(pin-to-pin delay)Pkg. SymbolNo. ofPins Package TypeOperating Range (1)XC9536XL-5PC44C 5 ns PC4444-pin Plastic Lead Chip Carrier (PLCC)C XC9536XL-5VQ44C 5 ns VQ4444-pin Quad Flat Pack (VQFP)C XC9536XL-5CS48C 5 ns CS4848-ball Chip Scale Package (CSP)C XC9536XL-5VQ64C 5 ns VQ6464-pin Quad Flat Pack (VQFP)C XC9536XL-7PC44C 7.5 ns PC4444-pin Plastic Lead Chip Carrier (PLCC)C XC9536XL-7VQ44C 7.5 ns VQ4444-pin Quad Flat Pack (VQFP)C XC9536XL-7CS48C 7.5 ns CS4848-ball Chip Scale Package (CSP)CXC9536XL-7VQ64C 7.5 ns VQ6464-pin Quad Flat Pack (VQFP)C XC9536XL-7PC44I 7.5 ns PC4444-pin Plastic Lead Chip Carrier (PLCC)I XC9536XL-7VQ44I 7.5 ns VQ4444-pin Quad Flat Pack (VQFP)I XC9536XL-7CS48I 7.5 ns CS4848-ball Chip Scale Package (CSP)I XC9536XL-7VQ64I 7.5 ns VQ6464-pin Quad Flat Pack (VQFP)I XC9536XL-10PC44C 10 ns PC4444-pin Plastic Lead Chip Carrier (PLCC)C XC9536XL-10VQ44C 10 ns VQ4444-pin Quad Flat Pack (VQFP)C XC9536XL-10CS48C 10 ns CS4848-ball Chip Scale Package (CSP)C XC9536XL-10VQ64C 10 ns VQ6464-pin Quad Flat Pack (VQFP)C XC9536XL-10PC44I 10 ns PC4444-pin Plastic Lead Chip Carrier (PLCC)I XC9536XL-10VQ44I 10 ns VQ4444-pin Quad Flat Pack (VQFP)I XC9536XL-10CS48I 10 ns CS4848-ball Chip Scale Package (CSP)I XC9536XL-10VQ64I 10 ns VQ6464-pin Quad Flat Pack (VQFP)I XC9536XL-5PCG44C 5 ns PCG4444-pin Plastic Lead Chip Carrier (PLCC); Pb-freeC XC9536XL-5VQG44C5 nsVQG4444-pinQuad Flat Pack (VQFP); Pb-freeCNotes:1.Due to the small size of chip scale packages, part marking on these packages does not follow the abovesample and the complete part number cannot be included in the marking. Part marking on chip scale packages by line:·Line 1 = X (Xilinx logo), then truncated part number (no XC), i.e., 95xxxXL.·Line 2 = Not related to device part number.·Line 3 = Not related to device part number.·Line 4 = Package code, speed, operating temperature, three digits not related to part number. Package codes: C1 = CS48, C2 = CSG48.8DS058 (v1.9) April 3, 2007XC9536XL-5CSG48C 5 ns CSG4848-ball Chip Scale Package (CSP); Pb-free C XC9536XL-5VQG64C 5 ns VQG6464-pin Quad Flat Pack (VQFP); Pb-free C XC9536XL-7PCG44C 7.5 ns PCG4444-pin Plastic Lead Chip Carrier (PLCC); Pb-freeC XC9536XL-7VQG44C 7.5 ns VQG4444-pin Quad Flat Pack (VQFP); Pb-free C XC9536XL-7CSG48C 7.5 ns CSG4848-ball Chip Scale Package (CSP); Pb-free C XC9536XL-7VQG64C 7.5 ns VQG6464-pin Quad Flat Pack (VQFP); Pb-free C XC9536XL-7PCG44I 7.5 ns PCG4444-pin Plastic Lead Chip Carrier (PLCC); Pb-freeI XC9536XL-7VQG44I 7.5 ns VQG4444-pin Quad Flat Pack (VQFP); Pb-free I XC9536XL-7CSG48I 7.5 ns CSG4848-ball Chip Scale Package (CSP); Pb-free I XC9536XL-7VQG64I 7.5 ns VQG6464-pin Quad Flat Pack (VQFP); Pb-free I XC9536XL-10PCG44C 10 ns PCG4444-pin Plastic Lead Chip Carrier (PLCC); Pb-freeC XC9536XL-10VQG44C 10 ns VQG4444-pin Quad Flat Pack (VQFP); Pb-free C XC9536XL-10CSG48C 10 ns CSG4848-ball Chip Scale Package (CSP); Pb-free C XC9536XL-10VQG64C 10 ns VQG6464-pin Quad Flat Pack (VQFP); Pb-free C XC9536XL-10PCG44I 10 ns PCG4444-pin Plastic Lead Chip Carrier (PLCC); Pb-freeIXC9536XL-10VQG44I 10 ns VQG4444-pin Quad Flat Pack (VQFP); Pb-free I XC9536XL-10CSG48I 10 ns CSG4848-ball Chip Scale Package (CSP); Pb-free I XC9536XL-10VQG64I10 nsVQG6464-pinQuad Flat Pack (VQFP); Pb-freeINotes:1. C = Commercial: T A = 0° to +70°C; I = Industrial: T A = –40° to +85°C.Device Ordering and Part Marking Number Speed(pin-to-pin delay)Pkg. SymbolNo. ofPins Package TypeOperating Range (1)Warranty DisclaimerTHESE PRODUCTS ARE SUBJECT TO THE TERMS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT /warranty.htm. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF THE PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED ON THE THEN-CURRENT XILINX DATA SHEET FOR THE PRODUCTS. PRODUCTS ARE NOT DESIGNED TO BE FAIL-SAFE AND ARE NOT WARRANTED FOR USE IN APPLICATIONS THAT POSE A RISK OF PHYSICAL HARM OR LOSS OF LIFE. USE OF PRODUCTS IN SUCH APPLICATIONS IS FULLY AT THE RISK OF CUSTOMER SUBJECT TO APPLICABLE LAWS AND REGULATIONS.Further ReadingThe following Xilinx links go to relevant XC9500XL CPLD documentation, including XAPP111, Using the XC9500XL Timing Model, and XAPP784, Bulletproof CPLD Design Practices. Simply click on the link and scroll down.Data Sheets, Application Notes, and White Papers.PackagingRevision HistoryThe following table shows the revision history for this document.Date Version Revision09/28/98 1.0Initial Xilinx release.08/28/00 1.1Added VQ44 package.06/20/02 1.2Updated I CC equation, page 1. Removed -4 device. Added industrial availability to -7device. Added additional I IH test conditions and measurements to DC Characteristics table.06/18/03 1.3Updated T SOL from 260 to 220o C. Added Device Part Marking and updated OrderingInformation.08/21/03 1.4Updated Package Device Marking Pin 1 orientation.07/15/04 1.5Added Pb-free documentation09/15/04 1.6Added T APRPW specification to AC Characteristics.07/15/05 1.7Move to Product Specification03/22/06 1.8Add Warranty Disclaimer.04/03/07 1.9Add programming temperature range warning on page 1.10DS058 (v1.9) April 3, 2007。

倍福PLC卡件介绍

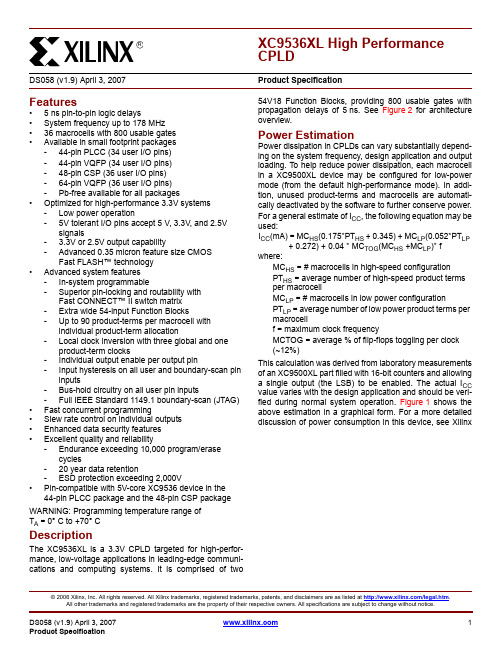

AC-2——异步电机用高频MOSFET逆变器AC2代表了当今最为先进的技术(IMS功率模块,Flash内存,微处理器控制,Can Bus)。

下面分别给出AC2的图片和内部结构示意图。

图1 AC2的图片和内部结构示意图BC3150是PROFIBUS—DP总线端子控制器总线端子控制器是带 PLC 控制功能的总线耦合器。

控制器有一个 PROFIBUS-DP 现场总线接口,可在 PROFIBUS-DP 系统中作为智能从站使用。

“紧凑型”总线端子控制器 BC3150 比较小巧而且经济。

BC3150 通过 K-BUS 总线扩展技术,可连接多达 255 个总线端子。

PROFIBUS 控制器自动检测波特率,最大可至 12 M波特率,使用两个地址选择开关分配地址。

总线端子控制器使用符合 IEC 61131-3 标准的 TwinCAT 进行编程。

组态和编程接口用于装载 PLC 程序,如果使用软件 PLC TwinCAT,则其 PLC 程序也可通过现场总线装载。

所连接的总线端子的输入/输出在 PLC 的缺省设置中被赋值。

可对每个总线端子进行配置,使其直接通过现场总线实现与上层控制单元的数据交换。

同样,预处理的数据也可通过现场总线实现总线端子控制器和上层控制器之间的数据交换。

BK3150是PRORIBUS—DP总线端子耦合器PROFIBUS-DP “紧凑型”总线耦合器 BK3150 扩展了 Beckhoff 总线端子系统,比较小巧而经济。

可以连接多达 64 个总线端子;若采用端子总线扩展技术,则可连接多达 255 个总线端子。

PROFIBUS 总线耦合器具有自动波特率检测功能,速率最大可以达到 12 Mbaud ,2 个地址选择开关用作地址分配。

对于现场总线连接,有提供 1 个 D-sub9 针接口,用于订货号为 ZS1031-3000 或 ZB3100 的 PROFIBUS 接头。

CX1020-0xxx 基本 CPU 模块CX1020 基本 CPU 模块通过一个功能更为强大的 1GHz Intel® M CPU 对现有CX1000 系列产品进行了扩展。

G.SKILL DDR3内存型号参考清单说明书

G.SKILL F3-3000C12Q-16GTXDG16GB (4 x 4GB )SS--- 1.65V●●●G.SKILL F3-2933C12D-8GTXDG8GB (2 x 4GB )SS--12-14-14-35 1.65V●●G.SKILL F3-2933C12Q-16GTXDG16GB (4 x 4GB )SS--12-14-14-35 1.65V●●●G.SKILL F3-2800C11Q-16GTXD(XMP)16GB(4GBx4)DS--11-13-13-35 1.65V●●CORSAIR CMD16GX3M4A2666C11 (XMP)4GB DS--11-13-13-35 1.65V●●●G.SKILL F3-2666C11Q-16GTXD(XMP)16GB(4GBx4)DS--11-13-13-35 1.65V●●●Team TXD34G2666HC11CBK8GB ( 2x 4GB )SS--11-13-13-35 1.65V●●●Team TXD38G2666HC11CBK16GB ( 2x 8GB )DS--11-13-13-35 1.65V●●G.SKILL F3-2600CL10Q-16GBZMD(XMP)16GB(4x 4GB)DS--10-12-12-31 1.65V●●G.SKILL F3-2600CL11Q-32GBZHD(XMP)32GB(8GBX4)DS--11-13-13-35 1.65V●●ADATA AX3U2600GW8G1116GB ( 2x 8GB )DS--11-13-13-35 1.65V●●CORSAIR CMGTX8(XMP)8GB (2GBx 4)SS--10-12-10-27 1.65V●●G.SKILL F3-2400C10D-8GTX(XMP)8GB(2x 4GB)SS--10-12-12-31 1.65V●●●G.SKILL F3-19200CL11Q-16GBZHD(XMP1.3)16GB ( 4GB x4 )DS--11-11-11-31 1.65V●●G.SKILL F3-19200CL 10Q-32GBZHD(XMP)8GB DS--10-12-12-31 1.65V●●●KINGMAX FLLE88F-C8KKAA HAIS(XMP)2GB SS--10-11-10-30 1.8V●●●KINGSTON KHX24C11T2K2/8X(XMP)4GB DS--- 1.65V●●●ADATA AX3U2400GW8G1116GB ( 2x 8GB )DS--11-13-13-35 1.65V●●ADATA AX3U2400G4G10-DG2(XMP)4GB DS--10-12-12-31 1.65V●●Team TXD38G2400HC10QBK8GB DS--10-12-12-31 1.65V●●●KINGSTON KHX2250C9D3T1K2/4GX(XMP)4GB ( 2x 2GB )DS--- 1.65V●●●GEIL GET34GB2200C9DC(XMP)2GB DS--9-10-9-28 1.65V●●GEIL GET38GB2200C9ADC(XMP)4GB DS--9-11-9-28 1.65V●●KINGMAX FLKE85F-B8KJAA-FEIS(XMP)2GB DS--- 1.5V●●CORSAIR CMT16GX3M4X2133C9(XMP 1.3)16GB ( 4GB x4 )DS--9-11-10-27 1.50V●●●CORSAIR CMT4GX3M2A2133C9(XMP)4GB(2x 2GB)DS--9-10-9-24 1.65V●●●CORSAIR CMT4GX3M2B2133C9(XMP)4GB(2x 2GB)DS--9-10-9-27 1.50V●CORSAIR CMT8GX3M2B2133C9(XMP)8GB ( 4GB x 2)DS--9-11-9-27 1.50V●●●G.SKILL F3-17000CL9Q-16GBZH(XMP1.3)16GB ( 4GB x4 )DS--9-11-10-28 1.65V●●●G.SKILL F3-17000CL11Q2-64GBZLD(XMP)8GB DS--11-11-11-31 1.5V●●●G.SKILL F3-2133C11Q-32GZL(XMP)8GB DS--11-11-11-31 1.5V●●●GEIL GE34GB2133C9DC(XMP)2GB DS--9-9-9-28 1.65V●●GEIL GU34GB2133C9DC(XMP)4GB(2 x 2GB)DS--9-9-9-28 1.65V●●KINGSTON KHX2133C11D3K4/16GX(XMP)16GB ( 4GB x4 )DS--- 1.65V●●●KINGSTON KHX2133C11D3T1K2/16GX(XMP)16GB(8GB x 2)DS--- 1.6V●●●KINGSTON KHX21C11T1BK2/16X(XMP)16GB(8GBx2)DS--- 1.6V●●●KINGSTON KHX2133C9AD3T1K2/4GX(XMP)4GB ( 2x 2GB )DS--- 1.65V●●●KINGSTON KHX2133C9AD3X2K2/4GX(XMP)4GB(2 x 2GB)DS--9-11-9-27 1.65V●●●KINGSTON KHX2133C9AD3T1K4/8GX(XMP)8GB(4 x 2GB)DS--9-11-9-27 1.65V●KINGSTON KHX21C11T1BK2/8X(XMP)8GB(4GBx2)DS--- 1.6V●●●KINGSTON KHX2133C9AD3T1FK4/8GX(XMP)8GB(4x 2GB)DS--- 1.65V●●KINGSTON KHX21C11T3K4/32X8GB DS--- 1.65V●●●ADATA AX3U2133XW8G1016GB ( 2x 8GB )DS--10-11-11-30 1.65V●●●ADATA AX3U2133XC4G10-2X(XMP)4GB DS--10-11-11-30 1.65V●●●ADATA AX3U2133XW8G10-2X(XMP)8GB DS--10-11-11-30 1.65V●●●Team TXD34096M2133HC11-L4GB SS--- 1.5V●●●Team TLD38G2133HC11ABK8GB DS--11-11-11-31 1.65V●●●Apacer78.AAGD5.9KD(XMP)6GB(3 x 2GB)DS--9-9-9-27 1.65V●●●CORSAIR CMZ4GX3M2A2000C10(XMP)4GB(2 x 2GB)SS--10-10-10-27 1.50V●●●CORSAIR CMT6GX3M3A2000C8(XMP)6GB(3 x 2GB)DS--8-9-8-24 1.65V●●●G.SKILL F3-16000CL9D-4GBFLS(XMP)4GB(2 x 2GB)DS--9-9-9-24 1.65V●●G.SKILL F3-16000CL9D-4GBTD(XMP)4GB(2 x 2GB)DS--9-9-9-27 1.65V●●G.SKILL F3-16000CL6T-6GBPIS(XMP)6GB (3x 2GB )DS--6-9-6-24 1.65V●●●GEIL GUP34GB2000C9DC(XMP)4GB(2 x 2GB)DS--9-9-9-28 1.65V●●KINGSTON KHX2000C9AD3T1K2/4GX(XMP)4GB ( 2x 2GB )DS--- 1.65V●●KINGSTON KHX2000C9AD3W1K2/4GX(XMP)4GB ( 2x 2GB )DS--- 1.65V●●KINGSTON KHX2000C9AD3W1K3/6GX(XMP)6GB ( 3x 2GB )DS--- 1.65V●●KINGSTON KHX2000C9AD3T1K3/6GX(XMP)6GB (3x 2GB )DS--- 1.65V●●CORSAIR CMT4GX3M2A1866C9(XMP)4GB(2 x 2GB)DS--9-9-9-24 1.65V●●●CORSAIR CMT6GX3MA1866C9(XMP)6GB(3 x 2GB)DS--9-9-9-24 1.65V●●CORSAIR CMZ8GX3M2A1866C9(XMP)8GB(2 x 4GB)DS--9-10-9-27 1.50V●●●CRUCIAL BLE4G3D1869DE1TXO.16FMD(XMP)4GB DS--9-9-9-27 1.5V●●●CRUCIAL BLT4G3D1869DT1TX0.13FKD(XMP)4GB DS--9-9-9-27 1.5V●●●CRUCIAL BLT4G3D1869DT2TXOB.16FMR(XMP)4GB DS--9-9-9-27 1.5V●●G.SKILL F3-14900CL9Q-16GBZL(XMP1.3)16GB ( 4GB x4 )DS--9-10-9-28 1.5V●●●G.SKILL F3-14900CL10Q2-64GBZLD(XMP1.3)64GB ( 8GBx 8 )DS--10-11-10-30 1.5V●●●G.SKILL F3-14900CL9D-8GBXL(XMP)8GB(2 x 4GB)DS--9-10-9-28 1.5V●●G.SKILL F3-14900CL9Q-8GBXL(XMP)8GB(2GBx4)DS--9-9-9-24 1.6V●●●KINGSTON KHX1866C9D3K4/16GX(XMP)16GB ( 4GB x4 )DS--- 1.65V●●●KINGSTON KHX1866C11D3P1K2/8G8GB ( 4GB x 2)DS--- 1.5V●●●KINGSTON KHX1866C9D3K2/8GX(XMP)8GB(4GBX2)DS--- 1.65V●●●KINGSTON KHX18C10T3K4/32X8GB DS--- 1.5V●●●ADATA AX3U1866XW8G1016GB ( 2x 8GB )DS--10-11-10-30 1.5V●●●Team TLD38G1866HC10SBK8GB DS--10-11-10-30 1.5V●●●APACER4GB UNB PC3-12800 CL114GB SS APACER AM5D6008BQQSCK--●●●Apacer78.B1GE3.9L10C4GB DS Apacer KZZC AM5D5908DEQSCK--●●●APACER8GB UNB PC3-12800 CL118GB DS APACER AM5D6008BQQSCK--●●●CORSAIR CMD12GX3M6A1600C8(XMP)12GB(6x2GB)DS--8-8-8-24 1.65V●●●CORSAIR CMZ32GX3M4X1600C10(XMP)32GB(8GBx4)DS--10-10-10-27 1.50V●●●CORSAIR CMP4GX3M2A1600C8(XMP)4GB(2 x 2GB)DS--8-8-8-24 1.65V●●●CORSAIR CMP4GX3M2A1600C9(XMP)4GB(2 x 2GB)DS--9-9-9-24 1.65V●●●CORSAIR CMP4GX3M2C1600C7(XMP)4GB(2 x 2GB)DS--7-8-7-20 1.65V●●●CORSAIR CMX4GX3M2A1600C9(XMP)4GB(2 x 2GB)DS--9-9-9-24 1.65V●●●CORSAIR TR3X6G1600C8 G(XMP)6GB(3 x 2GB)DS--8-8-8-24 1.65V●●●CORSAIR TR3X6G1600C8D G(XMP)6GB(3 x 2GB)DS--8-8-8-24 1.65V●●●CORSAIR TR3X6G1600C9 G(XMP)6GB(3 x 2GB)DS--9-9-9-24 1.65V●●●CORSAIR CMP8GX3M2A1600C9(XMP)8GB(2 x 4GB)DS--9-9-9-24 1.65V●●●CORSAIR CMZ8GX3M2A1600C7R(XMP)8GB(2 x 4GB)DS--7-8-7-20 1.50V●●CORSAIR CMX8GX3M4A1600C9(XMP)8GB(4 x 2GB)DS--9-9-9-24 1.65V●●●CORSAIR CMZ8GX3M1A1600C10(XMP)8GB DS--10-10-10-27 1.50V●●●Crucial BL25664BN1608.16FF(XMP)6GB(3 x 2GB)DS--- 1.65V●●●G.SKILL F3-12800CL7D-4GBRH(XMP)4GB(2 x 2GB)SS--7-7-7-24 1.6V●●●G.SKILL F3-12800CL7D-4GBRM(XMP)4GB(2 x 2GB)DS--7-8-7-24 1.6V●●●G.SKILL F3-12800CL8D-4GBRM(XMP)4GB(2 x 2GB)DS--8-8-8-24 1.60V●●G.SKILL F3-12800CL9D-4GBECO(XMP)4GB(2 x 2GB)DS--9-9-9-24XMP 1.35V●●G.SKILL F3-12800CL9D-4GBRL(XMP)4GB(2 x 2GB)DS--9-9-9-24 1.5V●●●G.SKILL F3-12800CL7D-8GBRH(XMP)8GB(2 x 4GB)DS--7-8-7-24 1.6V●●●G.SKILL F3-12800CL8D-8GBECO(XMP)8GB(2 x 4GB)DS--8-8-8-24XMP 1.35V●●●G.SKILL F3-12800CL9D-8GBRL(XMP)8GB(2 x 4GB)DS--9-9-9-24 1.5V●●●G.SKILL F3-12800CL10S-8GBXL(XMP)8GB DS--10-10-10-30-●●●GEIL GET316GB1600C9QC(XMP)16GB ( 4x 4GB )DS--9-9-9-28 1.6V●●●HYNIX HMT351U6CFR8C-PB4GB DS HYNIX H5TQ2G83CFR PBC--●●●KINGMAX FLGE85F-B8KJ9A FEIS(XMP)2GB DS--- 1.5V●●●KINGMAX FLGE85F-B8MF7 MEEH(XMP)2GB DS--7 1.8V/1.9V●KINGSTON KHX1600C9D3P1K2/4G4GB(2 x 2GB)SS--- 1.5V●●●KINGSTON KHX1600C9D3K3/12GX(XMP)12GB(3x4GB)DS--9-9-9-27 1.65V●●●KINGSTON KHX1600C9D3T1BK3/12GX(XMP)12GB(3x4GB)DS--9-9-9-27 1.65V●●KINGSTON KHX1600C9D3K4/16GX(XMP)16GB ( 4GB x4 )DS--- 1.65V●●●KINGSTON KHX16C9K2/1616GB(8GBx2)DS--- 1.5V●●KINGSTON KHX1600C9AD3/2G2GB DS--- 1.65V●●●KINGSTON KVR1600D3N11/2G-ES2GB DS KTC D1288JPNDPLD9U11-11-11-28 1.35V-1.5V●●●KINGSTON KHX1600C7D3K2/4GX(XMP)4GB ( 2x 2GB )DS--- 1.65V●●●KINGSTON KHX1600C8D3K2/4GX(XMP)4GB(2 x 2GB)DS--8 1.65V●●●KINGSTON KHX1600C8D3T1K2/4GX(XMP)4GB(2 x 2GB)DS--8 1.65V●●●KINGSTON KHX1600C9D3K2/4GX(XMP)4GB(2 x 2GB)DS--9 1.65V●●●KINGSTON KHX1600C9D3LK2/4GX(XMP)4GB(2 x 2GB)DS--9XMP 1.35V●●●KINGSTON KHX1600C9D3X2K2/4GX(XMP)4GB(2 x 2GB)DS--9-9-9-27 1.65V●●●KINGSTON KVR16N11/4(矮版)4GB DS KINGSTON D2568GEROPGGBU- 1.5V●●●KINGSTON KHX1600C9D3T1K3/6GX(XMP)6GB ( 3x 2GB )DS--- 1.65V●●KINGSTON KHX1600C9D3K3/6GX(XMP)6GB(3 x 2GB)DS--9 1.65V●●KINGSTON KHX1600C9D3T1BK3/6GX(XMP)6GB(3 x 2GB)DS--9-9-9-27 1.65V●●●KINGSTON KHX1600C9D3K2/8GX(XMP)8GB(2 x 4GB)DS--- 1.65V●●KINGSTON KHX1600C9D3P1K2/8G8GB(2 x 4GB)DS--- 1.5V●●●KINGSTON KHX16C10B1K2/16X(XMP)8GB DS--- 1.5V●●●KINGSTON KHX16C9P1K2/16(XMP)8GB DS--- 1.5V●●●PSC AL9F8L93B-GN2E4GB SS PSC XHP284C3G-M--●●●PSC ALAF8L93B-GN2E8GB DS PSC XHR425C3G-M--●●●Transcend8G DDR3 1600 DIMM CL118GB DS SEC 222 HYKO6MD9639W--●●●Transcend8G DDR3 1600 DIMM CL118GB DS Transcend E223X8BO648S--●●●ADATA AD3U1600C2G11-B2GB SS-N/A--●●●ADATA AD3U1600W4G11-B4GB SS ADATA F209X8BR6413--●●●ADATA AX3U1600GW8G916GB ( 2x 8GB )DS--9-9-9-24 1.5V●●●ADATA AX3U1600W8G1116GB ( 2x 8GB )DS--11-11-11-28 1.5V●●●ADATA AXDU1600GW8G9B16GB ( 2x 8GB )DS--11-11-11-28 1.5V●●●ADATA AD3U1600C4G11-B4GB DS-N/A--●●●ADATA AD3U1600W8G11-B8GB DS ADATA F211X8B0640A--●●SanMax SMD-4G68HP-16KZ4GB DS HYNIX H5TQ2G83BFR PBC--●●●TEAM TED34G1600HC11BK4GB DS--11-11-11-28-●●●TEAM TLD34G1600HC9BK(XMP)4GB DS--9-9-24 1.5V●●●Team TED38G1600HC11BK8GB DS--11-11-11-28-●●●A-DATA AD3U1333C2G92GB SS A-DATA3CCD-1509HNA1126L--●●●A-DATA AX3U1333C2G9-BP2GB SS----●●●A-DATA AD31333G002GMU2GB DS--8-8-8-24 1.65-1.85V●●Apacer78.A1GC6.9L12GB DS Apacer AM5D5808DEWSBG--●●●Apacer78.A1GC6.9L12GB DS Apacer AM5D5808FEQSBG9-●●●Apacer AU02GFA33C9NBGC2GB DS Apacer AM5D5808APQSBG--●●●Apacer78.B1GDE.9L10C4GB DS Apacer AM5D5908CEHSBG--●●●CORSAIR TR3X6G1333C9 G6GB(3x 2GB)SS--9-9-9-24 1.50V●●●CORSAIR CMD24GX3M6A1333C9(XMP)24GB(6x4GB)DS--9-9-9-24 1.60V●●CORSAIR TW3X4G1333C9D G4GB(2 x 2GB)DS--9-9-9-24 1.50V●●●CORSAIR CM3X4GA1333C9N24GB DS CORSAIR256MBDCJGELC04011369-9-9-24-●●●CORSAIR CMX4GX3M1A1333C94GB DS--9-9-9-24 1.50V●●●CORSAIR CMD8GX3M4A1333C78GB(4 x 2GB)DS--7-7-7-20 1.60V●●●Crucial CT25664BA1339.16FF2GB DS Micron9KF27D9KPT9-●●●Crucial BL25664BN1337.16FF (XMP)6GB(3 x 2GB)DS--7-7-7-24 1.65V●●●ELPIDA EBJ21UE8EDF0-DJ-F2GB DS ELPIDA J1108EDSE-DJ-F- 1.35V(low voltage)●●●G.SKILL F3-10666CL8D-4GBECO(XMP)4GB(2 x 2GB)DS--8-8-8-8-24XMP 1.35V●●●G.SKILL F3-10666CL7T-6GBPK(XMP)6GB(3 x 2GB)DS--7-7-7-18 1.5~1.6V●G.SKILL F3-10666CL7D-8GBRH(XMP)8GB(2 x 4GB)DS--7-7-7-21 1.5V●●●GEIL GG34GB1333C9DC4GB(2 x 2GB)DS GEIL GL1L128M88BA12N9-9-9-24 1.3V(low voltage)●●●GEIL GV34GB1333C9DC4GB(2 x 2GB)DS--9-9-9-24 1.5V●●●GEIL GVP34GB1333C7DC4GB(2 x 2GB)DS--7-7-7-24 1.5V●●●Hynix HMT325U6BFR8C-H92GB SS Hynix H5TQ2G83BFRH9C--●●●Hynix HMT125U6TFR8A-H92GB DS Hynix H5TC1G83TFRH9A- 1.35V(low voltage)●●●Hynix HMT351U6BFR8C-H94GB DS Hynix H5TQ2G83BFRH9C--●●●KINGMAX FLFE85F-C8KF9 CAES2GB SS KINGMAX KFC8FMFXF-DXX-15A--●●●KINGMAX FLFE85F-C8KL9 NAES2GB SS KINGMAX KFC8FNLXF-DXX-15A--●●●KINGMAX FLFE85F-C8KM9 NAES2GB SS KINGMAX KFC8FNMXF-BXX-15A--●●KINGMAX FLFE85F-B8KL9 NEES2GB DS KINGMAX KKB8FNWBFGNX-26A--●●●KINGMAX FLFF65F-C8KL9 NEES4GB DS KINGMAX KFC8FNLXF-DXX-15A--●●●KINGMAX FLFF65F-C8KM9 NEES4GB DS KINGMAX KFC8FNMXF-BXX-15A--●●●KINGSTON KVR1333D3N9/2G(矮版)2GB SS Hynix H5TQ2G83AFRH9C9-●●●KINGSTON KVR1333D3S8N9/2G2GB SS Micron IID77 D9LGK- 1.5V●●●KINGSTON KVR1333D3S8N9/2G-SP(矮版)2GB SS ELPIDA J2108BCSE-DJ-F- 1.5V●●●KINGSTON KVR1333D3N9/2G(矮版)2GB DS ELPIDA J1108BFBG-DJ-F9 1.5V●●●KINGSTON KVR1333D3N9/2G-SP(矮版)2GB DS KTC D1288JEMFNGD9U- 1.5V●●●KINGSTON KVR1333D3N9/2G-SP(矮版)2GB DS KINGSTON D1288JPSFPGD9U- 1.5V●●●KINGSTON KHX1333C7D3K2/4GX(XMP)4GB(2 x 2GB)DS--7 1.65V●●●KINGSTON KHX1333C9D3UK2/4GX(XMP)4GB(2 x 2GB)DS--9XMP 1.25V●●KINGSTON KVR1333D3N9/4G(矮版)4GB DS ELPIDA J2108BCSE-DJ-F- 1.5V●●●KINGSTON KVR1333D3N9/4G4GB DS KTC D2568JENCNGD9U- 1.5V●●●KINGSTON KVR1333D3N9/4G4GB DS Hynix H5TQ2G83AFR--●●●KINGSTON KVR1333D3N9/4G-SP(矮版)4GB DS KINGSTON D2568JENCPGD9U- 1.5V●●●Micron MT8JTF25664AZ-1G4D12GB SS Micron OJD12D9LGK--●●●Micron MT8JTF25664AZ-1G4M12GB SS MICRON IJM22 D9PFJ--●●●Micron MT16JTF51264AZ-1G4D14GB DS Micron OLD22D9LGK--●●●NANYA NT4GC64B8HG0NF-CG4GB DS NANYA NT5CB256M8GN-CG--●●●PSC AL8F8G73F-DJ22GB DS PSC A3P1GF3FGF--●●●SAMSUNG M378B5773DH0-CH92GB SS SAMSUNG K4B2G0846D--●●●SAMSUNG M378B5673FH0-CH92GB DS SAMSUNG K4B1G0846F--●●●SAMSUNG M378B5273CH0-CH94GB DS SAMSUNG K4B2G0846C--●●●SAMSUNG M378B1G73AH0-CH98GB DS SAMSUNG K4B4G0846A-HCH9--●●Super Talent W1333UB2GS2GB DS SAMSUNG K4B1G0846F9-●●●Super Talent W1333UB4GS4GB DS SAMSUNG K4B2G0846C--●●●Super Talent W1333UX6GM6GB(3x 2GB)DS Micron0BF27D9KPT9-9-9-24 1.5V●●●Transcend JM1333KLN-2G2GB SS HYNIX H5TQ2G83BZRH9C--●●●Transcend8G DDR3 1333 DIMM CL98GB DS Transcend E207X8BO643Y--●●Transcend8G DDR3 1333 DIMM CL98GB DS-N/A--●●●KINGSTEK KSTD3PC-106002GB SS MICRON PE911-125E--●●●TEAM TED34G1333HC9BK4GB DS--9-9-9-24-●●TEAM TED38G1333HC9BK8GB DS--9-9-9-24-●●●Crucial CT25664BA1067.16FF2GB DS Micron9HF22D9KPT7-●●●ELPIDA EBJ21UE8EDF0-AE-F2GB DS ELPIDA J1108EDSE-DJ-F- 1.35V(low voltage)●●●KINGSTON KVR1066D3N7/2G2GB DS ELPIDA J1108BFSE-DJ-F- 1.5V●●●KINGSTON KVR1066D3N7/4G4GB DS Hynix H5TQ2G83AFR7 1.5V●●●4 DIMM Slots• 1 DIMM: Supports one module inserted in any slot as Single-channel memory configuration• 2 DIMM: Supports one pair of modules inserted into eithor the yellow slots or the dark brown slots as one pair of Dual-channel memory configuration• 4 DIMM: Supports 4 modules inserted into both the yellow and dark brown slots as two pairs of Dual-channel memory configuration-When installing total memory of 4GB capacity or more, Windows 32-bit operation system may only recognize less than 3GB. Hence, a total installed memory of less than 3GB is recommended.-It is recommended to install the memory modules from the yellow slots for better overclocking capability.-The default DIMM frequency depends on its Serial Presence Detect (SPD), which is the standard way of accessing information from a memory module.Under the default state, some memory modules for overclocking may operate at a lower frequency than the vendor-marked value.。

CS5340-CZZR中文资料

Single-Ended Analog Input

AINR Switch-Cap ADC

High-Pass Filter

Low-Latency Digital Filters

Serial Port

VL 1.8 V to 5 V

Auto-detect MCLK Divider

Master Clock

Slave Mode Auto-detect

2. PIN DESCRIPTION .............................................................................................................................. 13 3. TYPICAL CONNECTION DIAGRAM ................................................................................................... 14 4. APPLICATIONS ................................................................................................................................... 15

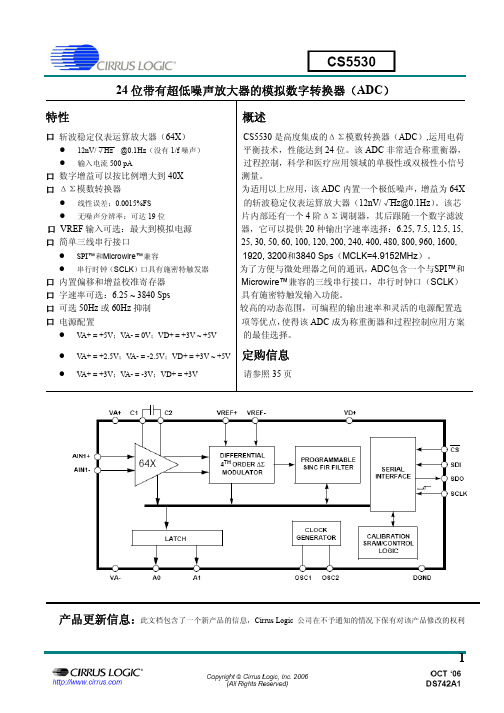

192 kHz 101 dB Dynamic Range at 5 V -94 dB THD+N 90 mW Power Consumption High-Pass Filter to Remove DC Offsets Analog/Digital Core Supplies from 3.3 V to 5 V Supports Logic Levels between 1.8 V and 5 V Auto-detect Mode Selection in Slave Mode Auto-Detect MCLK Divider Pin Compatible with CS5341

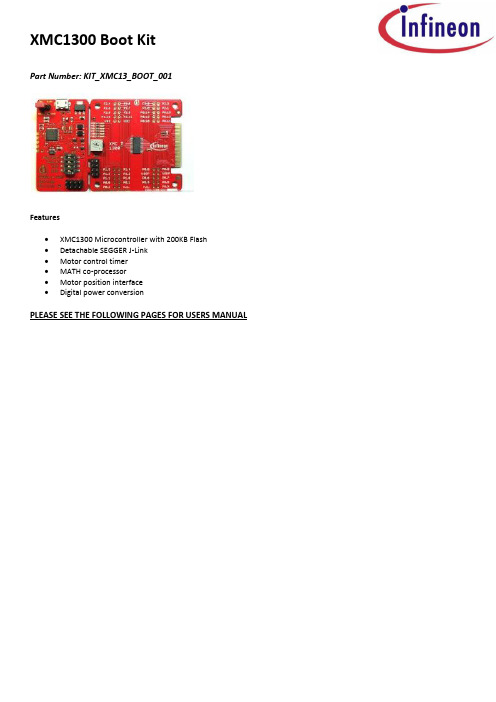

XMC1300 Boot Kit用户手册说明书

XMC1300 Boot KitPart Number: KIT_XMC13_BOOT_001Features∙XMC1300 Microcontroller with 200KB Flash∙Detachable SEGGER J-Link∙Motor control timer∙MATH co-processor∙Motor position interface∙Digital power conversionPLEASE SEE THE FOLLOWING PAGES FOR USERS MANUALXMC1300 CPU Card For XMC1000 FamilyCPU-13A-V1XMC1300 CPU CardBoard User's Manual Revision 2.0, 2013-12-18Edition 2013-12-18Published byInfineon Technologies AG81726 Munich, Germany© 2013 Infineon Technologies AGAll Rights Reserved.Legal DisclaimerThe information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.InformationFor further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office ().WarningsDue to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or otherTrademarks of Infineon Technologies AGAURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, EconoPACK™, CoolMOS™, CoolSET™, CORECONTROL™, CROSSAVE™, DAVE™, DI-POL™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPIM™,EconoPACK™,EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™, I²RF™, ISOFACE™, IsoPACK™, MIPAQ™, ModSTACK™,my-d™, NovalithIC™, OptiMOS™, ORIGA™, POWERCODE™, PRIMARION™, PrimePACK™, PrimeSTACK™, PRO-SIL™, PROFET™, RASIC™, ReverSave™, SatRIC™, SIEGET™, SINDRION™, SIPMOS™, SmartLEWIS™, SOLID FLASH™, TEMPFET™, thinQ!™, TRENCHSTOP™, TriCore™.Other TrademarksAdvance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of D ECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektr onix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.Last Trademarks Update 2011-11-11Table of Contents1Overview (7)1.1Key Features (7)1.2Block Diagram (7)2Hardware Description (8)2.1Power Supply (8)2.2Reset (9)2.3Clock Generation (9)2.4Boot Option (9)2.5Debug Interface and virtual com port (9)2.6LED (9)2.7Potentiometer (10)2.8Application Card connector (10)3Production Data (12)3.1Schematics (12)3.2Layout and Geometry (15)3.3Bill of Material (15)List of FiguresFigure 1Block Diagram of XMC1300 CPU Card (7)Figure 2XMC1300 CPU Card (8)Figure 3Power Supply circuit (8)Figure 4LEDs circuit (10)Figure 5Potentiometer Circuit (10)Figure 6Pinout of the 2x30 pin edge connector (11)Figure 7Schematic 1 of 2 XMC1300 CPU Card (13)Figure 8Schematic 2 of 2 XMC1300 CPU Card (14)Figure 9XMC1300 CPU Card layout and geometry (15)List of TablesTable 1Debug connector X201 (9)Table 2LEDs Pinout (10)Table 3XMC1300 CPU Card (15)IntroductionThis document describes the features and hardware details of the XMC1300 CPU Card. This board is mounted with ARM® Cortex TM-M0 based XMC1300 Microcontroller from Infineon Technologies AG. This board is part of Infineon’s XMC1000 Application Kits1 OverviewThe XMC1300 CPU board (CPU-13A-V1) houses the XMC1300 Microcontroller and a 2x30 pin edge for application expansion. The board along with application cards (e.g. Colour LED Card, White LED Card) demonstrates the capabilities of XMC1300. The main use case for this board is to demonstrate the generic features of XMC1300 device including tool chain. The focus is safe operation under evaluation conditions. The board is neither cost nor size optimized and does not serve as a reference design.1.1 Key FeaturesThe XMC1300 CPU Card is equipped with the following features∙XMC1300 (ARM®Cortex TM-M0 based) Microcontroller, TSSOP38∙Connection to XMC1300 application cards via card edge connector∙Detachable J-Link debugger and UART virtual COM port, with micro USB connector∙Six user LEDs∙Potentiometer, connected to analog input P2.5∙Power supply via Micro-USB connector1.2 Block DiagramFigure 1 shows the functional block diagram of the XMC1300 CPU Card.Features include:−On board Debugger, for downloading and debugging of application code−Virtual com port for uart communication with terminal program e.g. Hyperterminal.−2x30 card edge connector, for extension to application card e.g. Colour LED Card and White LED Card.− 6 User LEDs connected to GPIO P0.0, P0.1, P0.6, P0.7, P0.8 and P0.9−Variable resistor R110 connected to Analog input P2.5−All the pins of XMC1300 are accessible via the connector JP101, JP102, JP103 and JP104Figure 1 Block Diagram of XMC1300 CPU Card2 Hardware DescriptionThe following sections give a detailed description of the hardware and how it can be used.Figure 2 XMC1300 CPU Card2.1 Power SupplyXMC1300 CPU Card is powered from the micro USB connector (5V); however, there is a current limit that can be drawn from the host PC through USB. If the CPU-13A-V1 board is used to drive other application board (e.g. Colour LED Card, White LED Card) and the total current required exceeds 500mA, then the board needs to be powered by external power supply connected to VDD and GND connection on board.The XMC1300 device can operate by power supply of 1.8V till 5.5Vdc. On this board, 5Vdc is used to power the XMC1300 device. However, if user wants to power the XMC1300 device with 3.3Vdc, then, set Jumper at JP201 to 3.3V side.Figure 3 Power Supply circuit2.2 ResetXMC1300 does not have a reset pin, hence, user can unplug and replug the USB cable to achieve power-on master reset.2.3 Clock GenerationNo external clock source is required. XMC1300 has two internal oscillators DCO1 and DCO2. DCO1 has a clock output of 64MHz. DCO2 is used to generate the standby clock running at 32.768KHz which used for Real Time Clock too. The main clock, MCLK and fast peripherial clock, PCLK, are generated from DCO1’s output.2.4 Boot OptionAfter power-on reset with master reset, XMC1300 device will enter different boot mode depend on the BMI (Boot Mode Index) value stored in XMC1300’s f lash configuration sector 0 (CS0). The BMI value pre-programmed on the XMC1300 device on CPU Card is User mode with debug enabled, hence, the XMC1300 device will start to run the application code in its embedded Flash after power on reset.2.5 Debug Interface and virtual com portXMC1300 CPU Card has on-board debugger which supports Serial Wire Debug (SWD) and Single Pin Debug (SPD) as debug interface. SPD is a proprietary debugging protocol from Infineon Technologies and it requires only 1 pin for debug communication. The debugger also provides a virtual COM port which support UART communication via P1.3 (rx-in) and P1.2 (tx-out) of XMC1300. There is a 2x5 pins Header Debug connector X201.Table 1 Debug connector X2012.6 LEDThe port pins P0.0, P0.1, P0.6, P0.7, P0.8 and P0.9 are connected to LED101, LED102, LED103, LED104, LED105 and LED106 respectively. The LED is turn on by output ‘L ow’ at the port pin.Figure 4 LEDs circuit2.7 PotentiometerXMC1300 CPU Card provides a potentiometer R110 for ease of use and testing of the on-chip analog to digital converter. The potentiometer is connected to the analog input P2.5. The analog output of the potentiometer is the same the VDDP voltage supplied to the XMC1300 device.Figure 5 Potentiometer Circuit2.8 Application Card connectorXMC1300 CPU Card has a 2x30 pins card edge connector. The mating connector is SAMTEC HSEC8-130-01-L-RA-XX.Figure 6 Pinout of the 2x30 pin edge connector3 Production Data3.1 SchematicsThis chapter contains the schematics for the XMC1300 CPU Card:∙Figure 7: CPU, Pin Headers, Potentiometer and LED and 60pin Edge connector ∙Figure 8: On-board Debugger, Power Supply3.2 Layout and GeometryFigure 9 XMC1300 CPU Card layout and geometry 3.3 Bill of Materialw w w.i n f i n e o n.c o m。

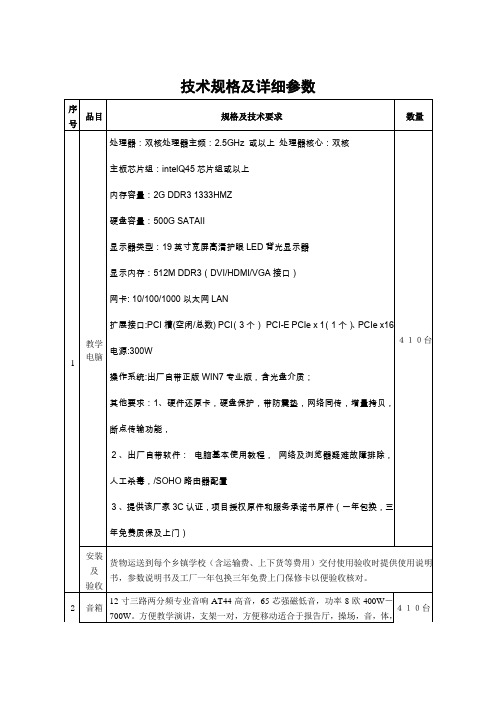

技术规格及详细参数

双发双收,环向锁定。199个UHF频率通道可选用,抗干扰,使用距离100M以上。数字音量控制系统,轻触式按键设置,易于设定和操作。接收器和发射器同时具有LCD液晶显示功能,所有工作状态清楚显示。参考品牌范围:惠威、爱浪、博士、飞浪

安装及

验收

调式安装线材包(1.5M卡农连接线两根,四芯插各4个,300支无氧铜音响线100米,音响移动固定架子等)货物运送到每个乡镇学校(含运输费、上下货等费用)交付使用验收时提供使用说明书,参数说明书及工厂3年免费保修卡以便验收核对。

网卡: 10/100/1000以太网LAN

扩展接口:PCI槽(空闲/总数) PCI(3个)PCI-E PCIe x 1(1个)、PCIe x16

电源:300W

操作系统:出厂自带正版WIN7专业版,含光盘介质;

其他要求:1、硬件还原卡,硬盘保护,带防震垫,网络同传,增量拷贝,断点传输功能,

2、出厂自带软件:电脑基本使用教程,网络及浏览器疑难故障排除,人工杀毒,/SOHO路由器配置

410台

扩声功放

功率:立体声输出:650W+650W(8欧)输入电平0.775V,信燥比98dB,失真度小于0.03%.

频率响应20Hz-20kHz.

采用软启动方式,风扇速度自动调节,带液晶显示屏,功放输出保护:完全短路、过载、过温负载保护,可随时监控设备运行状态。(提供产品彩页加盖原工厂公章)ቤተ መጻሕፍቲ ባይዱ考品牌范围:惠威、爱浪、博士、飞浪

3、提供该厂家3C认证,项目授权原件和服务承诺书原件(一年包换,三年免费质保及上门)

410台

安装及

验收

货物运送到每个乡镇学校(含运输费、上下货等费用)交付使用验收时提供使用说明书,参数说明书及工厂一年包换三年免费上门保修卡以便验收核对。

深圳市佳鸿威 XC 系列可编程控制器 说明书(特殊指令篇)

目录前言..............................................................................................................................................- 1 - 本手册的内容构成..............................................................................................................- 1 - 手册的适用范围..................................................................................................................- 2 - 手册中的约定俗成..............................................................................................................- 3 - 关联手册..............................................................................................................................- 3 - 手册的获取途径..................................................................................................................- 4 - 1 PID控制功能 (1)1-1.概述 (2)1-2.指令形式 (2)1-3.参数设置 (4)1-3-1.寄存器定义表 (4)1-3-2.参数说明 (5)1-4.自整定模式 (7)1-5.高级模式 (8)1-6.应用要点 (9)1-7.程序举例 (9)2 C语言功能块 (11)2-1.概述 (12)2-2.指令形式 (12)2-3.操作步骤 (13)2-4.函数的导入、导出 (15)2-5.功能块的编辑 (16)2-6.程序举例 (17)2-7.应用要点 (18)2-8.函数表 (19)3 顺序功能块BLOCK (21)3-1.BLOCK基本概念 (23)3-1-1.BLOCK概述 (23)3-1-2.引入BLOCK的原因 (24)3-2.BLOCK的调用 (25)3-2-1.BLOCK的添加 (25)3-2-2.BLOCK的转移 (28)3-2-3.BLOCK的删除 (29)3-2-4.BLOCK的修改 (29)3-3.BLOCK内部指令的编辑 (31)3-3-1.命令语列表 (31)3-3-2.脉冲配置 (33)3-3-3.Modbus指令 (34)3-3-4.Wait指令 (34)3-3-5.变频器配置 (35)3-3-6.自由格式通讯 (39)3-4.BLOCK的执行方式 (41)3-5.BLOCK内部指令的编写要求 (44)3-6.BLOCK相关指令 (46)3-6-1.指令说明 (46)3-6-2.指令的执行时序 (48)3-7.BLOCK执行标志位/寄存器 (52)3-8.程序举例 (53)4 特殊功能指令 (55)4-1.脉宽调制[PWM] (57)4-2.频率测量[FRQM] (58)4-3.精确定时[STR]、[STRR]、[STRS] (60)4-4.中断[EI]、[DI]、[IRET] (63)4-4-1.外部中断 (63)4-4-2.定时中断 (67)附录1 特殊功能版本要求 (69)附录2 PLC资源冲突表 (70)本手册涉及XC系列可编程控制器的高级指令的应用,主要介绍XC系列可编程控制器的本体PID控制指令、C语言功能块、顺序功能块BLOCK、特殊功能指令等,各章节内容概览如下:1.PID控制功能本章重点介绍本体XC系列PID指令的应用,包括指令的调用、参数的设定,使用注意点,程序例等。

悍马主板说明书

环境安全性须知 z 灰尘、潮湿以及剧烈的温度变化都会影响主板的使用寿命,请尽量避免在这些恶劣环

境地方放置和使用。 z 本产品的标准使用环境温度为 0 度~40 度 (数据来自于主芯片要求)。 z 一般情况下,当环境温度变化过大, 可能导致接插件 (CONNECTOR) 之间产生接触性

- II -

安全指导

1. 请仔细阅读这些安全指导。 2. 请保留这份用户手册以便日后参考。 3. 在您开始安装之前请将设备放置于稳定可靠的平台上面。 4. 在您将设备连接电源供应器之前请确保电源电压合乎标准。 5. 设备上所有的警告,警示您都应该注意。 6. 在安装附加的接口与模块之前请将设备与连接器间的连接断开。 7. 决不能让任何液体流入机箱的开口处,这样的行为有可能会引起火灾或电击。 8. 不正确的电池替换可能会引起爆炸.请使用制造厂商建议的电池类型作替换。 9. 如果发生下列情形,请专职的服务人员为您检查您的设备:

商标布告 (按字母表的顺序排列)

所有的品牌,产品,徽标,商标和公司名称都是属于商标或注册商标各自的拥有者。 AMD, Phenom™ II x 4;Phenom™ II x 3;Phenom™ II x2;Athlon II™ x4;Athlon II™ x3;Athlon II™ x2;Sempron™是AMD有限公司的注册商标。 AMI ® 是American Megatrend, Inc.的注册商标。 Kensington 和 MicroSaver 是Kensington 科技集团的注册商标。 Microsoft 是Microsoft有限公司的注册商标。 Netware® 是Novell, Inc的注册商标。 AMD, AMD徽标是AMD有限公司在美国和其它国家的注册商标。 PS/2 和 OS®/2 是International Business Machines有限公司的注册商标。 PCMCIA 和 CardBus 是个人电脑存储卡国际联合会的注册商标。 Windows® 98/2000/ /XP/Vista/7 是Microsoft有限公司的注册商标。

CX系列产品使用与维护

2 英信CX系列安装部件图解

cx300 cx500 cx700

2.1 CX300

2.1.1 体系结构

存储 处理器

SP 光纤通道 x 2 镜像缓存 CPU FC 后备电源 风扇 电源 风扇 电源 风扇 后备电源

CMI

存储 处理器

SP 光纤通道 x 2 镜像缓存 CPU FC

A/C Input 一个HSSDC磁盘接口

2.2 CX500

2.2.1 体系结构

存储处理器 存储处理器

CMI

SP 光纤通道 x 2 镜像缓存 CPU FC CPU FC 后备电源 风扇 电源 风扇 风扇 后备电源 SP 光纤通道 x 2 镜像缓存 CPU FC CPU FC

CX500 - 部门存储

120K IOPS 和 760 MB/s 带宽 四个前端主机连接、四个后端磁盘连接 最多可支持 120 个驱动器(FC: 146 GB ATA:320 GB ) 4 GB 标准缓存

CX700 - 数据中心存储

200K IOPS 和 1,520 MB/s 带宽 八个前端主机连接、八个后端磁盘连接 最多可支持 240 个驱动器(FC:146 GB;ATA:320 GB) 8 GB 标准缓存

4.2 安装存储软件

1) 登录存储系统

在IE Browser中输入SP-A(或SP-B)的IP地址 输入用户名,密码admin/password

2) 进入存储系统主界面

3) 安装存储软件,NDU的进程

B 准备工作

一根NULL cable modem 一个管理电脑(Server, PC, Laptop) 在Laptop上安装Navisphere 6.x CLI IP地址, 子网掩码, 主机名, 网关 参阅CX-Series 初始化安装文档

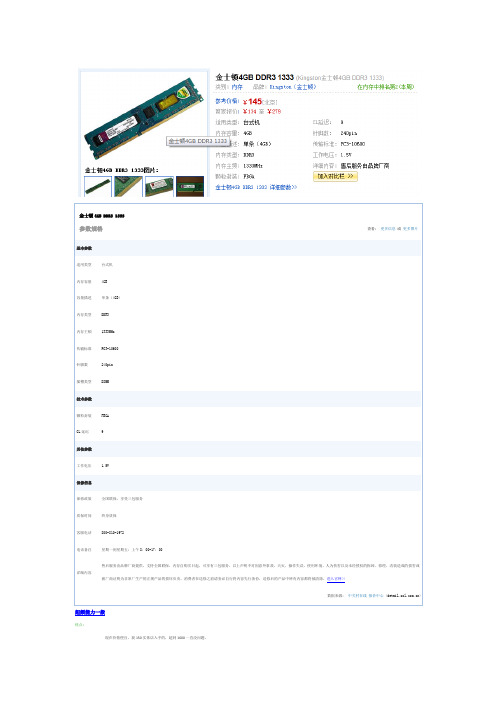

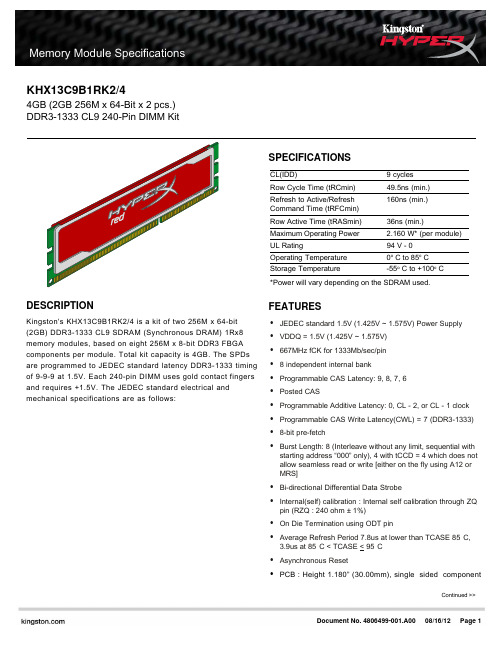

2011典型内存 4GB DDR3 1333

技术参数

CL延迟

9-9-9-24

其他参数

工作电压

1.5V

保修信息

保修政策

全国联保,享受三包服务

质保时间

终身质保

客服电话

800-810-1972

电话备注

星期一到星期五:上午8:00-17:00

详细内容

售后服务由品牌厂商提供,支持全国联保,内存自购买日起,可享有三包服务。以上声明不对因意外事故、天灾、操作失误、使用环境、人为伤害以及未经授权的拆卸、修理、改装造成的损害或被厂商证明为非原厂生产的正规产品的损坏负责。消费者在送修之前请务必自行将内容先行备份,送修后的产品中所有内容都将被清除。进入官网>>

数据来源:中关村在线报价中心()

超频能力一般

优点:

现在价格便宜,我150实体店入手的,超到1600一直没问题。

缺点:

超1866时开不了机,是不是内存体质差了点,难不成我买的是假货?我的主板都是华硕Z68-V PRO,能支持更高的频率。

总结:

价格可以,性能一般。

金士顿2GB DDR3 1333

保修信息

保修政策

全国联保,享受三包服务

质保时间

终身质保

客服电话

800-810-1972

电话备注

星期一到星期五:上午8:00-17:00

详细内容

售后服务由品牌厂商提供,支持全国联保,内存自购买日起,可享有三包服务。以上声明不对因意外事故、天灾、操作失误、使用环境、人为伤害以及未经授权的拆卸、修理、改装造成的损害或被厂商证明为非原厂生产的正规产品的损坏负责。消费者在送修之前请务必自行将内容先行备份,送修后的产品中所有内容都将被清除。进入官网>>

FPGA可编程逻辑器件芯片XC9536-10PCG44I中文规格书

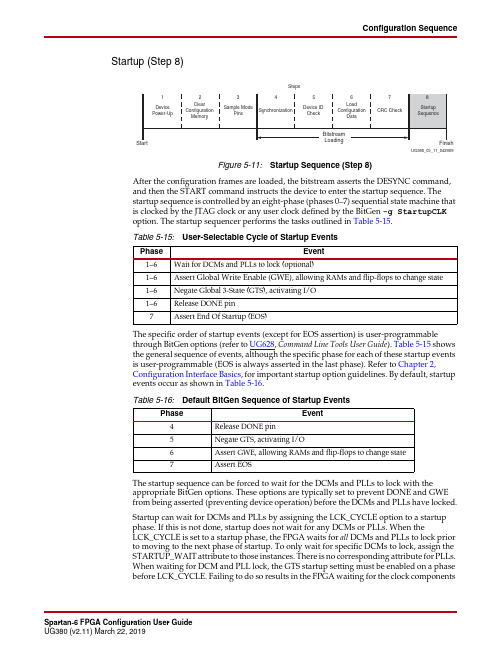

Configuration Sequence Startup (Step8)Figure 5-11:Startup Sequence (Step 8)After the configuration frames are loaded, the bitstream asserts the DESYNC command, and then the START command instructs the device to enter the startup sequence. Thestartup sequence is controlled by an eight-phase (phases 0–7) sequential state machine that is clocked by the JTAG clock or any user clock defined by the BitGen -g StartupCLK option. The startup sequencer performs the tasks outlined in Table5-15.Table 5-15:User-Selectable Cycle of Startup EventsPhase Event1–6Wait for DCMs and PLLs to lock (optional)1–6Assert Global Write Enable (GWE), allowing RAMs and flip-flops to change state1–6Negate Global 3-State (GTS), activating I/O1–6Release DONE pin7Assert End Of Startup (EOS)The specific order of startup events (except for EOS assertion) is user-programmablethrough BitGen options (refer to UG628, Command Line Tools User Guide). Table5-15 shows the general sequence of events, although the specific phase for each of these startup events is user-programmable (EOS is always asserted in the last phase). Refer to Chapter2,Configuration Interface Basics, for important startup option guidelines. By default, startup events occur as shown in Table5-16.Table 5-16:Default BitGen Sequence of Startup EventsPhase Event4Release DONE pin5Negate GTS, activating I/O6Assert GWE, allowing RAMs and flip-flops to change state7Assert EOSThe startup sequence can be forced to wait for the DCMs and PLLs to lock with theappropriate BitGen options. These options are typically set to prevent DONE and GWE from being asserted (preventing device operation) before the DCMs and PLLs have locked.Startup can wait for DCMs and PLLs by assigning the LCK_CYCLE option to a startup phase. If this is not done, startup does not wait for any DCMs or PLLs. When theLCK_CYCLE is set to a startup phase, the FPGA waits for all DCMs and PLLs to lock prior to moving to the next phase of startup. To only wait for specific DCMs to lock, assign the STARTUP_WAIT attribute to those instances. There is no corresponding attribute for PLLs.When waiting for DCM and PLL lock, the GTS startup setting must be enabled on a phase before LCK_CYCLE. Failing to do so results in the FPGA waiting for the clock componentsChapter 5:Configuration Detailsindefinitely and never completing startup. For additional information on using theLCK_CYCLE feature in master configuration modes, see Required Data Spacing between MultiBoot Images, page 138.The DONE signal is released by the startup sequencer on the cycle indicated by the user, but the startup sequencer does not proceed until the DONE pin actually sees a logic High. The DONE pin is an open-drain bidirectional signal with an internal pull-up by default. By releasing the DONE pin, the device simply stops driving a logic Low and the pin is weakly pulled High. Table 5-17 shows signals relating to the startup sequencer. Figure 5-12 shows the waveforms relating to the startup sequencer.In a Slave configuration mode, additional clocks are needed after DONE goes High to complete the startup events. In Master configuration mode, the FPGA provides these clocks. The number of clocks necessary varies depending on the settings selected for the startup events. A general rule is to apply eight clocks (with DIN all 1’s) after DONE has gone High. More clocks are necessary if the startup is configured to wait for the DCM and PLLs to lock (LCK_CYCLE).When using the external master clock (USERCCLK) pin, I/O standard becomes enabled at the EOS phase. As I/O standard changes from the default pre-configuration value to the user specified value, a glitch might appear. It is recommended to use clock enables or a reset to prevent glitches from affecting the design.Table 5-17:Signals Relating to the Startup SequencerSignal NameTypeAccess (1)DescriptionDONEBidirectional (2)DONE pin or Spartan-6 FPGA Status RegisterIndicates configuration is complete. Can be held Low externally to synchronize startup with other FPGAs. GWE StatusSpartan-6 FPGA Status RegisterGlobal Write Enable (GWE). When deasserted, GWE disables the CLB and the IOB flip-flops as well as other synchronous elements on the FPGA.GTSGlobal 3-State (GTS). When asserted, GTS disables all the I/O driversexcept for the configuration pins.DCM_LOCKDCM_LOCK indicates when all DCMs and PLLs have locked. This signal is asserted by default. It is active if the STARTUP_WAIT option is used on a DCM and the LCK_CYCLE option is used when the bitstream is generated.Notes:rmation on the Spartan-6 FPGA status register is available in Table 5-35, page 105. Information on accessing the device status register via JTAG is available in Table 6-5, page 124. Information on accessing the device status register via SelectMAP is available in Table 6-1, page 119.2.Open-drain output with internal pull-up by default; the optional driver is enabled using the BitGen DriveDone option.3.GWE is asserted synchronously to the configuration clock (CCLK) and has a significant skew across the part. Therefore, sequential elements might not be released synchronously to the system clock and timing violations can occur during startup. It is recommended to reset the design after startup and/or apply some other synchronization technique.Required Data Spacing between MultiBoot ImagesChapter 7:Reconfiguration and MultiBootChapter 9:Advanced Configuration InterfacesMultiple Device SelectMAP ConfigurationMultiple Spartan-6 devices in Slave SelectMAP mode can be connected on a common SelectMAP bus (Figure 9-3). In a SelectMAP bus, the D, CCLK, RDWR_B, BUSY,PROGRAM_B, DONE, and INIT_B pins share a common connection between all of the devices. To allow each device to be accessed individually, the CSI_B (Chip Select) inputs must not be tied together. External control of the CSI_B signal is required and is usually provided by a microprocessor or CPLD.If Readback is going to be performed on the device after configuration, the RDWR_B and BUSY signals must be handled appropriately. (For details, refer to Chapter 6, Readback and Configuration Verification .)Otherwise, RDWR_B can be tied Low and BUSY can be ignored. The BUSY signal never needs to be monitored when configuring Spartan-6 devices. Refer to Bitstream Loading (Steps 4-7), page 85 and to Chapter 6, Readback and Configuration Verification .Notes relevant to Figure 9-3:1.The DONE pin is by default an open-drain output requiring an external pull-up resistor. In this arrangement, the active DONE driver must be disabled.2.The INIT_B pin is a bidirectional, open-drain pin. An external pull-up resistor is required.3.The BitGen startup clock setting must be set for CCLK for SelectMAP configuration.4.The BUSY signals can be left unconnected if readback is not needed.5.An external controller such as a microprocessor or CPLD is needed to control configuration.Figure 9-3:Multiple Slave Device Configuration on an 8-Bit SelectMAP Bus。

XC9510AXXXSX资料