LMK04031BISQ中文资料

K4000001中文资料

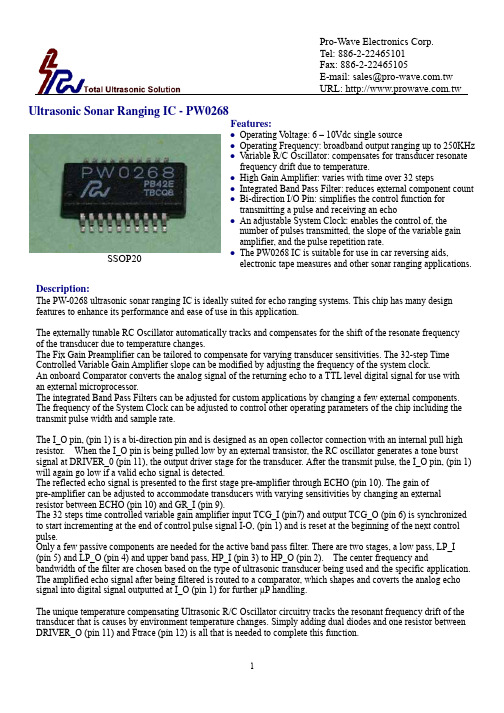

E-mail: sales@URL: Ultrasonic Sonar Ranging IC - PW0268Features:SSOP20 z Operating V oltage: 6 – 10Vdc single sourcez Operating Frequency: broadband output ranging up to 250KHz z Variable R/C Oscillator: compensates for transducer resonate frequency drift due to temperature.z High Gain Amplifier: varies with time over 32 stepsz Integrated Band Pass Filter: reduces external component count z Bi-direction I/O Pin: simplifies the control function for transmitting a pulse and receiving an echoz An adjustable System Clock: enables the control of, the number of pulses transmitted, the slope of the variable gain amplifier, and the pulse repetition rate.z The PW0268 IC is suitable for use in car reversing aids, electronic tape measures and other sonar ranging applications.Description:The PW-0268 ultrasonic sonar ranging IC is ideally suited for echo ranging systems. This chip has many design features to enhance its performance and ease of use in this application.The externally tunable RC Oscillator automatically tracks and compensates for the shift of the resonate frequencyof the transducer due to temperature changes.The Fix Gain Preamplifier can be tailored to compensate for varying transducer sensitivities. The 32-step Time Controlled Variable Gain Amplifier slope can be modified by adjusting the frequency of the system clock.An onboard Comparator converts the analog signal of the returning echo to a TTL level digital signal for use with an external microprocessor.The integrated Band Pass Filters can be adjusted for custom applications by changing a few external components. The frequency of the System Clock can be adjusted to control other operating parameters of the chip including the transmit pulse width and sample rate.The I_O pin, (pin 1) is a bi-direction pin and is designed as an open collector connection with an internal pull high resistor. When the I_O pin is being pulled low by an external transistor, the RC oscillator generates a tone burst signal at DRIVER_0 (pin 11), the output driver stage for the transducer. After the transmit pulse, the I_O pin, (pin 1) will again go low if a valid echo signal is detected.The reflected echo signal is presented to the first stage pre-amplifier through ECHO (pin 10). The gain ofpre-amplifier can be adjusted to accommodate transducers with varying sensitivities by changing an external resistor between ECHO (pin 10) and GR_I (pin 9).The 32 steps time controlled variable gain amplifier input TCG_I (pin7) and output TCG_O (pin 6) is synchronized to start incrementing at the end of control pulse signal I-O, (pin 1) and is reset at the beginning of the next control pulse.Only a few passive components are needed for the active band pass filter. There are two stages, a low pass, LP_I (pin 5) and LP_O (pin 4) and upper band pass, HP_I (pin 3) to HP_O (pin 2). The center frequency and bandwidth of the filter are chosen based on the type of ultrasonic transducer being used and the specific application. The amplified echo signal after being filtered is routed to a comparator, which shapes and coverts the analog echo signal into digital signal outputted at I_O (pin 1) for further µP handling.The unique temperature compensating Ultrasonic R/C Oscillator circuitry tracks the resonant frequency drift of the transducer that is causes by environment temperature changes. Simply adding dual diodes and one resistor between DRIVER_O (pin 11) and Ftrace (pin 12) is all that is needed to complete this function.E-mail: sales@ URL: Block DiagramI_OHP_OLP_OHP_ILP_ITCG_OGR_OTCG_IGR_IECHOVref Vcc GND Vreg CLK ORC3ORC1ORC2Ftrace Driver_OPin AssignmentI_O HP_O HP_I LP_O LP_I TCG_O TCG_I GR_O GR_I ECHOVref Vcc Vreg GND CLK ORC3ORC2ORC1Ftrace Driver_OPW02681092019181716151413121187654321E-mail: sales@ URL: Specifications:Unless otherwise specified, all data measured under Vcc = 9V , F = 40KHzParameter Symbol Condition Min.Typ. Max.Unit Supply V oltage Vcc Vreg = 4V 5.5 11 V Supply Current Icc Vcc = 6 ~ 10V 8 11 14 mA Regulated V oltage Vreg Vcc = 6 ~ 10V 3.8 4 5 V Stability of Vreg Vlr Vcc = 6 ~ 10V , ± 3%-3.0 0 +3.0 % Reference V oltage Vref Vcc = 6 ~10V ,RL>2K Ω0.4 0.44 0.5 VregOp-Amp Slew Rate SR Vin = 3Vpp 5 - - V/µS Comparator TriggerLevel Tcomp Over Vref 300 350 400 mVSystem ClockFrequency CLKf R=33K Ω C=22pF 610 660 710 KHzSystem ClockFrequency Range CLKr 0.001- 1500KHzUltrasonic OscillationFrequencyFoscf R=5.6K C=1000pF 38 40 42 KHzUltrasonic OscillationFrequency Range Foscr 0.001- 500 KHz2nd Amp Gain GR 29 30 31 dB Min(1x, 0dB) -1 0 +1 dBTime Controlled Gain Amplifier TCGainMax(58x, 35.2dB) 34 35 36 dB Bandwidth of 2nd Amp GRbw Gain = 50dB 150 170 200 KHzIdrv Driver_O - 20 40 mADriving CurrentIsink Driver_O - -20 -80 I_OVIH - 0.3 0.4 VccInput V oltage LevelI_OVIL 0.15 0.2 -I_OVOH - 0.9 1 VccOutput V oltage Level I_OVOL 0 0.05 -Input Low LevelCurrentI_OIOL - -10 -20 mAI_O Internal Pull UpResistanceRup 3.5 5 6.5 K ΩAbsolute Maximum RatingsDescription Symbol Condition Min. Max. Unit Supply V oltage Vcc 0 12 VOperation Temperature Topr -40 +85Storage Temperature Tstg -65 +150I_O Vcc -0.3 Vcc+0.3VMax. Pin Input V oltage VimaxOthers -0.3 Vreg+0.3Max. Input Current Iimax * -10 +10 mA*To prevent latch up, the instantaneous input current should be no large than 100mA for each pins.E-mail: sales@URL: Pins Description:Pin Name Description Pin Name Descriptionoutput 1 I_O Input/Output 11Driver_O Transducerdriving2 HP_O High pass filter output 12Ftrace Frequency tracing input3 HP_I High pass filter input 13ORC1 RC oscillator: terminal 14 LP_O Low pass filter output 14ORC2 RC oscillator: terminal 25 LP_I Low pass filter input 15ORC3 RC oscillator: terminal 36 TCG_O Time controlled gain output 16CLK System clock7 TCG_I Time controlled gain input 17GND Ground8 GR_O External adjustable gain output 18Vreg Regulated voltage for internalanalogue devicesgain input 19Vcc Power supplyadjustable9 GR_I External10 ECHO Receiving echo input 20Vref Reference voltage output Application Circuit:for car reversing aids (values should be changed for other applications)VrefVccE-mail: sales@ URL: Application NoteThe circuit shown on page 4 is a typical circuit for car reversing aids. The RC Oscillator generates a tone burst when a low level pulse is applied to the I_O pin, (pin 1).To accommodate tolerance variations of transducers during manufacturing, a 1K-ohm variable resistor (R1) isprovided to trim the output operating frequency. The range of adjustment is from 38.0 – 42.0 KHz. and allows for a better match of the drive signal to the resonate frequency of the transducer.The active burst number (number of pulses transmitted) is controlled by the pulse width of the low level signal applied to the I_O pin, (pin 1).The tone burst output, Driver_O (pin 11), drives the transducer through a MOSFET transistor and impedance matching transformer IFT. The inductance in the secondary winding of the transformer is designed to tune out the reactance of the parallel capacitance of the transducer.The high output voltage of the tone burst is snubbed by two diodes and the returning echo signal is passed on to the first stage pre-amplifier. The signal is then passed on to the second stage fix gain amplifier and finally to the third stage 32-step time controlled variable gain amplifier. The gain of the pre-amplifier should be properly set to meet the sensitivity needs of the transducer and application requirements.The center frequency of band-pass filter should be chosen to exactly match the frequency of the RC Oscillator and considerations for the width of pass-band filter should be made based on actual application requirements. If the amplified echo signal from the output of the band pass filter exceeds 0.35V + Vref, the comparator will output a low pulse to the I_O pin, (pin 1). The width of the low level pulse is proportional to the echo signal strength.The above description is summarized in the signal timing charts illustrated below.MCU output: H: 1ms/Div., V: 2.0V/Div.Driver_O (Pin 11): H: 1ms/Div., V: 2.0V/Div.Transducer Oscillation: H: 1ms/Div., V: 50V/Div.HP_O (Pin 2): H: 1ms/Div., V: 2.0V/Div.Output at Pin 1 I_O: H: 1ms/Div., V: 5.0V/Div.The RC oscillator will be enabled in the duration of input pulse. The maximum pulse width is 396 F and any time longer than this upper limit will be ignored.The next input pulse will be ignored if the pulse repetition rate is shorter than 9900 F + pulse width.F: Frequency of system clockE-mail: sales@URL: The resonate frequency of ultrasonic piezo transducers varies in an inversely proportional relationship to temperature. The lower the temperature, the higher the resonate frequency, the higher the temperature the lower the resonate frequency.This property of piezo transducers may cause a mismatch between transducer and drive signal with changes in ambient temperature and reduces efficiency of the system when the frequency of the drive circuit remains constant and does not track the resonate frequency shift of the transducer.Therefore it is desirable to have the output frequency of the drive source track the resonate frequency of the transducer with changes in ambient temperature. The Auto Frequency Tracking circuitry between Ftrace, (pin 12), and Drive_O, (pin 11) is used to accomplish this task.The voltage change at Ftrace (pin 11) varies in proportion to the forward bias voltage change across diodes D1, D2. This change is caused by the negative temperature coefficient of the diodes and the ratio of the resistor circuitR2/R3.A lower temperature increases the voltage drop across the diodes. This intern accelerates the charge rate of an internal integrator circuit controlling the R/C Oscillator, ORC3, (pin15). The net result is the adjustment to theR/C Oscillator increases the resonate frequency of the output, Drive_O, (pin11).Conversely, a higher temperature decreases the voltage drop across the diodes. This slows the charge rate of the internal integrator circuit controlling the R/C Oscillator. The net result of this adjustment is to decrease the resonate frequency of the output Drive_O, (pin 11).Choose values for the components R1, R2, R3 and C1 that will best track the characteristic resonate frequency shift curves due to temperature for a specific transducer.Recommended values for the following transducers are listed below.Used Transducer R1(Ohm) R2(Ohm) R3(Ohm) C1(pF) 400EP14D 3,300 1,500 511 2,200400EP18A 3,300 1,500 604 2,200235AC130 2,000 0 2,100 220For a fixed output of 40KHz at Drive_O (pin 11) simply remove D1, D2 and R2 and set R1 = 4,500 Ohm, C1 = 2,200 pF, and R3 = 511 Ohm.The system clock CLK (pin 16) controls the maximum input pulse width, the slope of time controlled gain amplifier and pulse repetition rate.For example, as illustrated in the block diagram, if the system clock is set to 660KHz (C2: 22pF, R4: 47K Ohm), then:(1)The maximum input pulse width is 396/F = 396/660K = 0.6 ms and any duration longer than 0.6ms will beignored.(2)The step duration of the 32 step time controlled gain amplifier is equal to 220/F = 0.333 ms, starting fromthe end of the pulse on the I_O pin, (pin 1).(3)The minimum pulse repetition rate is 9900/F + pulse width = 9900/F + 0.5 ms (20 bursts of 40KHz) =9900/660K + 0.5 = 15.5 ms.For long distance measurements of 18 meters (one way distance), the system clock should be set as follows: Min. Pulse Repetition Rate = 9900/F + 0.75 = 166 mS (30 bursts of 40KHz)Frequency of System Clock F = 60 KHzFor additional information about an 18-meter tape measure circuit, please consult with the factory.E-mail: sales@ URL: Time Controlled Gain Amplifier051015202530354005101520253035StepsG a i n (d B )The time controlled gain amplifier is stepping up once the input pulse falling. The time duration can be calculated as:T = 220/F F: Frequency of System ClockE-mail: sales@URL: Package and Dimensions:20 Pins, SSOP (150mil)E-mail: sales@ URL: E-mail: sales@URL: Symbol Min. Nom.Max.A 0.053- 0.069A1 0.004- 0.010A2 0.049- 0.065b 0.008- 0.012b1 0.0080.0100.011c 0.006- 0.010c1 0.0060.0080.009BSCD 0.341BSCE 0.236BSCE1 0.154BASe 0.025L 0.016- 0.050L1 0.041REFBASL2 0.010R 0.003- -R1 0.003- -θ0°- 8°θ1 5°- 15°θ2 0°- -aaa 0.004bbb 0.008ccc 0.004ddd 0.007eee 0.004Pro-Wave Electronics Corp.Tel: 886-2-22465101Fax: 886-2-22465105E-mail: sales@URL: 11Notes:1.Dimensioning and tolerancing per ANSI Y14.5M-1982.2.Dimensions in inches (angles in degrees)3.Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions orgate burrs shall not exceed 0.006” per end. Dimension E1 does not include interlead flash orprotrusions. Interlead flash or protrusions shall not exceed “0.006” per side. D1 and E1dimensions are determined at datum H.4.The package top may be smaller than the package bottom. Dimensions D and E1 are determinedat the outermost extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrsand interlead flash, but including any mismatch between the top and bottom of the plastic.5.Datum A and B to be determined at datum H.6.N is the maximum number of terminal position. (N=20)7.The dimensions apply to the flat section of the lead between 0.004 to 0.010 inches from the leadtip.8.Dimension b does not include dambar protrusion. Allowable dambar protrusion shall be 0.004”total in excess of b dimension at maximum material condition. The dambar can not be locatedon the lower radius of the foot.9.Refer to JEDEC MO-137 variation AD.JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATIONCopyright © 2004 Pro-Wave Electronics Corp. 9/15/2004Sonar Ranging Module SRM400The SRM400 is a sonar ranging module utilizing our new developed Sonar Ranging IC, PW-0268, which can work with all our PT or EP type transducers. SRM400 provides as a shortcut to develop car reversing systems or some other distance measurement systems for design engineers who are not very familiar with analog circuit and/or the operation of ultrasonic transducers. By using this module engineers can focus firstly on the other fields of digital circuit and software designs as well as some other mechanical issues. After first stage then you can either design your own analog circuit based on the module construction or consult with factory for making your own module for your special needs.Features:z Operating V oltage: 6 – 10Vdc single source z Operating Frequency: broadband output ranging up to 250KHzz Built-in variable RC oscillator matching transducers with different frequenciesz High Gain Amplifier: varies with time over 32 stepsz Integrated Band Pass Filter: reduces external component count,z Bi-direction I/O Pin: simplifies the control function for transmitting a pulse and receiving an echoz An adjustable System Clock: enables the control of, the number of pulses transmitted, the slope of the variable gain amplifier, and the pulse repetition ratez Board size: 27.9 * 18 mm (L*W)Specification:Operation voltage DC6 - 10V Operation current <20 mA DC10V Oscillation frequency Variable RC oscillator Amplifier gain Pre-Amplifier 14 dB 2nd Stage Amplifier 30 dB Time controlled 32 steps main amplifier 35 dB max. Fc: 38 KHzBandwidth: 20KHz Bandpass filter Insertion loss: 1 dBDriving voltage (no load) 130Vpp; pulse width 0.5ms Bi-directional I/OInput signal Open collector pull lowOutput 0..05*Vcc to 0.9*Vccdigital echo signalsMeasuring distance 25 – 150 cmSRM400 includes: 1. Module board2. 400EP14D enclosed type transducer of asymmetrical beam patterns, see detail specification of 400EP14D.3. Detail electrical schematicS. Square Enterprise Company Limited Pro-Wave Electronics CorporationP.O. Box 1-70 Chung Ho, Taiwan, ROC; E-mail: prowave@; Tel: 886-2-22465101(5 lines), 22459774; Fax: 886-2-22465105 ; Sonar Ranging ModuleSRM400Electronic Circuit DiagramWaveforms at different test points:works with transducer model 400EP14D against a hard target of size of 20cmL*20cmW*1cmT at distance of 50cm“A” Point: Control Pulse (from MCU) “B”Point: Tone bursts Signal H: 0.5ms/divV: 5V/div H: 0.5ms/div V: 5V/div“C” Point: Transducer loading “D” Point: 1st Pre-AmplifierH: 0.5ms/div V: 50V/div H: 0.5ms/div V: 20mV/div“E” Point: Main 32 Steps TCG Amplifier “F” Point: Digital Echo signal OutputH: 0.5ms/divV: 1V/divH: 0.5ms/div V: 5V/divRefer to PW-0268 Sonar Ranging IC for detail information.Model Number Nominal Frequency Hz Tolerance at 25 C PPM Temperature Stability –10 C to +70 C PPMLoad Capacitance pF Series Resistance Ohm Shunt Capacitance pF Drive LevelmW S40000 40,000 ±60 ±45 12.5 35,000 2.3 0.001S32768 32,768 ±20 ±30 12.5 35,000 2.3 0.001Matching TransformersSpecificationParts Number K4000001 K4000002 K4000003 K4000004 Operating Frequency40.0 KHz 40.0 KHz 40.0 KHz 40.0 KHz Variable Inductance (min.) 10.6 mH± 6%10.6 mH± 6%10.6 mH± 6% 10.6 mH± 6%Unloaded Q (min.) 70 100 25 47TurnRatio 1:10 1:10 1:10 1:10 Matching Transducer400EP14D 400EP14D (Temperature CompensatedType235SR130 400EP18AP.O. Box 1-70 Chung Ho, Taiwan, ROC;E-mail: prowave@;Tel: 886-2-22465101(5 lines), 22459774;Fax: 886-2-22465105 ; S. Square Enterprise Company Limited Pro-Wave Electronics Corporation。

gc0403 规格书

gc0403 规格书英文回答:The GC0403 is a 1/4-inch CMOS digital image sensor witha resolution of 1280 x 1024 pixels. It has a sensitivity of1.0 V/lux-sec and a dynamic range of 70 dB. The GC0403 is available in a variety of package options, including LGA, QFN, and CSP.Here are some of the key features of the GC0403:1/4-inch CMOS digital image sensor.Resolution: 1280 x 1024 pixels.Sensitivity: 1.0 V/lux-sec.Dynamic range: 70 dB.Available in a variety of package options.The GC0403 is a versatile image sensor that can be used in a variety of applications, including:Security cameras.Surveillance cameras.Automotive cameras.Medical imaging.Industrial inspection.中文回答:GC0403 是一款 1/4 英寸 CMOS 数码图像传感器,分辨率为1280 x 1024 像素。

它的灵敏度为 1.0 V/lux-sec,动态范围为 70 dB。

GC0403 有多种封装选项,包括 LGA、QFN 和 CSP。

以下是 GC0403 的一些主要特性:1/4 英寸 CMOS 数码图像传感器。

LMK03001DISQNOPB;LMK03001ISQXNOPB;LMK03001CISQXNOPB;中文规格书,Datasheet资料

LMK03000 FamilyPrecision Clock Conditioner with Integrated VCOGeneral DescriptionThe LMK03000 family of precision clock conditioners combine the functions of jitter cleaning/reconditioning, multiplication,and distribution of a reference clock. The devices integrate a Voltage Controlled Oscillator (VCO), a high performance In-teger-N Phase Locked Loop (PLL), a partially integrated loop filter, and up to eight outputs in various LVDS and LVPECL combinations.The VCO output is optionally accessible on the Fout port. In-ternally, the VCO output goes through a VCO Divider to feed the various clock distribution blocks.Each clock distribution block includes a programmable di-vider, a phase synchronization circuit, a programmable delay,a clock output mux, and an LVDS or LVPECL output buffer.This allows multiple integer-related and phase-adjusted copies of the reference to be distributed to eight system com-ponents.The clock conditioners come in a 48-pin LLP package and are footprint compatible with other clocking devices in the same family.Target Applications●Data Converter Clocking●Networking, SONET/SDH, DSLAM ●Wireless Infrastructure ●Medical●Test and Measurement ●Military / AerospaceFeatures●Integrated VCO with very low phase noise floor●Integrated Integer-N PLL with outstanding normalized phase noise contribution of -224 dBc/Hz ●VCO divider values of 2 to 8 (all divides)●Channel divider values of 1, 2 to 510 (even divides)●LVDS and LVPECL clock outputs ●Partially integrated loop filter●Dedicated divider and delay blocks on each clock output ●Pin compatible family of clocking devices ● 3.15 to 3.45 V operation●Package: 48 pin LLP (7.0 x 7.0 x 0.8 mm)●200 fs RMS Clock generator performance (10 Hz to 20MHz) with a clean input clockDeviceOutputsVCOTuning Range (MHz)RMS Jitter(fs)LMK03000C 3 LVDS5 LVPECL1185 - 1296400LMK03000800LMK03000D 1200LMK03001C 1470 - 1570400LMK03001800LMK03001D 1200LMK03033C 4 LVDS 4 LVPECL1843 - 2160500LMK03033800System Diagram20211440TRI-STATE ® is a registered trademark of National Semiconductor Corporation.PRODUCTION DATA information is current as ofpublication date. Products conform to specifications per 202114 SNAS381N Copyright © 1999-2012, Texas Instruments IncorporatedLMK03000 FamilyFunctional Block Diagram2Copyright © 1999-2012, Texas Instruments IncorporatedConnection Diagram48-Pin LLP Package20211402LMK03000 FamilyCopyright © 1999-2012, Texas Instruments Incorporated 3Pin DescriptionsPin #Pin Name I/O Description 1, 25GND-Ground2Fout O Internal VCO Frequency Output3, 8, 13, 16, 19, 22, 26, 30, 31, 33, 37,40, 43, 46Vcc1, Vcc2, Vcc3, Vcc4, Vcc5, Vcc6, Vcc7, Vcc8, Vcc9, Vcc10,Vcc11, Vcc12, Vcc13, Vcc14-Power Supply4CLKuWire I MICROWIRE Clock Input 5DATAuWire I MICROWIRE Data Input6LEuWire I MICROWIRE Latch Enable Input 7, 34, 35NC-No Connection to these pins9, 10LDObyp1, LDObyp2-LDO Bypass11GOE I Global Output Enable12LD O Lock Detect and Test Output 14, 15CLKout0, CLKout0*O LVDS Clock Output 017, 18CLKout1, CLKout1*O LVDS Clock Output 120, 21CLKout2, CLKout2*O LVDS Clock Output 223, 24CLKout3, CLKout3*O Clock Output 3(LVDS for LMK03033C/LMK03033 LVPECL for all other parts)27SYNC*I Global Clock Output Synchronization28, 29OSCin, OSCin*I Oscillator Clock Input; Should be AC coupled32CPout O Charge Pump Output36Bias I Bias Bypass38, 39CLKout4, CLKout4*O LVPECL Clock Output 441, 42CLKout5, CLKout5*O LVPECL Clock Output 544, 45CLKout6, CLKout6*O LVPECL Clock Output 647, 48CLKout7, CLKout7*O LVPECLClock Output 7DAP DAP-Die Attach Pad is GroundLMK03000 Family4Copyright © 1999-2012, Texas Instruments IncorporatedLMK03000 FamilyAbsolute Maximum Ratings (Note 1, Note 2)If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.Parameter Symbol Ratings Units Power Supply Voltage V CC-0.3 to 3.6VInput Voltage V IN-0.3 to (V CC + 0.3)VStorage Temperature Range T STG-65 to 150°CLead Temperature (solder 4 s)T L+260°CJunction Temperature T J125°CRecommended Operating ConditionsParameter Symbol Min Typ Max Units Ambient Temperature T A-402585°CPower Supply Voltage V CC 3.15 3.3 3.45VNote 1:"Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.Note 2:This device is a high performance integrated circuit with ESD handling precautions. Handling of this device should only be done at ESD protected work stations. The device is rated to a HBM-ESD of > 2 kV, a MM-ESD of > 200 V, and a CDM-ESD of > 1.2 kV.Package Thermal ResistancePackageθθJ-PAD (Thermal Pad)JA48-Lead LLP (Note 3)27.4° C/W 5.8° C/WNote 3:Specification assumes 16 thermal vias connect the die attach pad to the embedded copper plane on the 4-layer JEDEC board. These vias play a key role in improving the thermal performance of the LLP. It is recommended that the maximum number of vias be used in the board layout.Copyright © 1999-2012, Texas Instruments Incorporated5Electrical Characteristics(Note 4)(3.15 V ≤ Vcc ≤ 3.45 V, -40 °C ≤ T A ≤ 85 °C, Differential Inputs/Outputs; Vboost=0; except as specified. Typical values represent most likely parametric norms at Vcc = 3.3 V, T A = 25 °C, and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed).SymbolParameterConditionsMinTypMaxUnitsCurrent ConsumptionI CCPower Supply Current (Note 5)Entire device; one LVDS and one LVPECL clock enabled; no divide; no delay.161.8mAEntire device; All Outputs Off (no emitter resistors placed) 86 I CC PDPower Down CurrentPOWERDOWN = 11mAReference Oscillatorf OSCin squareReference Oscillator Input Frequency Range for Square WaveAC coupled; Differential (V OD )1200MHzV OSCin squareSquare Wave Input Voltage for OSCin andOSCin*0.21.6VppPLLf PDPhase Detector Frequency40MHzI SRCE CPoutCharge Pump Source CurrentV CPout = Vcc/2, PLL_CP_GAIN = 1x100 µA V CPout = Vcc/2, PLL_CP_GAIN = 4x 400 V CPout = Vcc/2, PLL_CP_GAIN = 16x 1600 V CPout = Vcc/2, PLL_CP_GAIN = 32x 3200 I SINK CPoutCharge Pump Sink CurrentV CPout = Vcc/2, PLL_CP_GAIN = 1x-100 µA V CPout = Vcc/2, PLL_CP_GAIN = 4x -400 V CPout = Vcc/2, PLL_CP_GAIN = 16x -1600 V CPout = Vcc/2, PLL_CP_GAIN = 32x-3200 I CPout TRI Charge Pump TRI-STATE ® Current 0.5 V < V CPout < Vcc - 0.5 V 210nA I CPout %MISMagnitude of Charge PumpSink vs. Source Current MismatchV CPout = Vcc / 2T A = 25°C3%I CPout VTUNE Magnitude of Charge PumpCurrent vs. Charge Pump VoltageVariation 0.5 V < V CPout < Vcc - 0.5 V T A = 25°C 4 %I CPout TEMP Magnitude of Charge Pump Current vs.Temperature Variation4 %PN10kHz PLL 1/f Noise at 10 kHz Offset (Note 6)Normalized to 1 GHz Output Frequency PLL_CP_GAIN = 1x -117 dBc/Hz PLL_CP_GAIN = 32x -122 PN1HzNormalized Phase Noise Contribution (Note 7)PLL_CP_GAIN = 1x -219 dBc/HzPLL_CP_GAIN = 32x-224LMK03000 Family6Copyright © 1999-2012, Texas Instruments IncorporatedSymbol Parameter Conditions Min Typ Max UnitsVCOf Fout VCO Tuning RangeLMK03000C/LMK03000/LMK03000D11851296MHzLMK03001C/LMK03001/LMK03001D14701570LMK03033C/LMK0303318432160|ΔT CL|Allowable Temperature Drift forContinuous LockAfter programming R15 for lock, nochanges to output configuration arepermitted to guarantee continuouslock. (Note 8)125°Cp Fout Output Power to a 50 Ω load driven by Fout(Note 10)LMK03000C/LMK03000/LMK03000D;TA= 25 °C3.3dBmLMK03001C/LMK03001/LMK03001D;TA= 25 °C2.7LMK03033C/LMK03033;TA= 25 °C-5 to 0K VCO Fine Tuning Sensitivity (Note 9)LMK03000C/LMK03000/LMK03000D7 to 9MHz/VLMK03001C/LMK03001/LMK03001D9 to 11LMK03033C/LMK0303314 to 26J RMS FoutFout RMS Period Jitter(12 kHz to 20 MHz bandwidth)LMK03000C/LMK03001C400fsLMK03000/LMK03001800LMK03000D/LMK03001D1200LMK03033C500LMK03033800L(f)Fout Fout Single Side Band Phase NoiseLMK03000CfFout= 1296 MHz(Note 11)10 kHz Offset-91.4dBc/Hz100 kHz Offset-116.81 MHz Offset-137.810 MHz Offset-156.9LMK03000CfFout= 1185 MHz(Note 11)10 kHz Offset-93.5100 kHz Offset-118.51 MHz Offset-139.410 MHz Offset-158.4LMK03001CfFout= 1570 MHz(Note 11)10 kHz Offset-89.6100 kHz Offset-115.21 MHz Offset-136.510 MHz Offset-156.0LMK03001CfFout= 1470 MHz(Note 11)10 kHz Offset-91.6100 kHz Offset-116.01 MHz Offset-137.910 MHz Offset-156.2LMK03033CfFout= 2160 MHz(Note 11)10 kHz Offset-83100 kHz Offset-1091 MHz Offset-13110 MHz Offset-152LMK03033CfFout= 1843 MHz(Note 11)10 kHz Offset-86100 kHz Offset-1111 MHz Offset-13410 MHz Offset-153LMK03000 FamilyCopyright © 1999-2012, Texas Instruments Incorporated7Symbol Parameter Conditions Min Typ Max Units Clock Distribution Section (Note 12, Note 13) - LVDS Clock OutputsJitterADD Additive RMS Jitter (Note 12)RL= 100 ΩDistribution Path =765 MHzBandwidth =12 kHz to 20 MHzCLKoutX_MUX= Bypass (nodivide or delay)20fsCLKoutX_MUX= Divided (nodelay)CLKoutX_DIV =475t SKEW CLKoutX to CLKoutY (Note 14)Equal loading and identical clockconfigurationRL= 100 Ω-30±430psV OD Differential Output Voltage RL= 100 Ω250350450mVΔV OD Change in magnitude of VODforcomplementary output statesRL= 100 Ω-5050mVV OS Output Offset Voltage RL= 100 Ω 1.070 1.25 1.370VΔV OS Change in magnitude of VOSforcomplementary output statesRL= 100 Ω-3535mVI SA I SB Clock Output Short Circuit Currentsingle-endedSingle-ended outputs shorted to GND-2424mAI SAB Clock Output Short Circuit CurrentdifferentialComplementary outputs tied together-1212mA Clock Distribution Section (Note 12, Note 13) - LVPECL Clock OutputsJitterADD Additive RMS Jitter (Note 12)RL= 100 ΩDistribution Path =765 MHzBandwidth =12 kHz to 20 MHzCLKoutX_MUX= Bypass (nodivide or delay)20fsCLKoutX_MUX= Divided (nodelay)CLKoutX_DIV =475t SKEW CLKoutX to CLKoutY (Note 14)Equal loading and identical clockconfigurationTermination = 50 Ω to Vcc - 2 V-30±330psVOHOutput High VoltageTermination = 50 Ω to Vcc - 2 V Vcc -0.98VV OL Output Low VoltageVcc -1.8VV OD Differential Output Voltage RL= 100 Ω660810965mVDigital LVTTL Interfaces (Note 15)VIHHigh-Level Input Voltage 2.0Vcc VVILLow-Level Input Voltage0.8VIIHHigh-Level Input Current V IH = Vcc-5.0 5.0µAIILLow-Level Input Current V IL = 0-40.0 5.0µAV OH High-Level Output Voltage I OH = +500 µAVcc -0.4VVOLLow-Level Output Voltage I OL = -500 µA0.4VDigital MICROWIRE Interfaces (Note 16)VIHHigh-Level Input Voltage 1.6Vcc VVILLow-Level Input Voltage0.4VIIHHigh-Level Input Current V IH = Vcc-5.0 5.0µAI IL Low-Level Input Current V IL = 0-5.0 5.0µALMK03000 Family8Copyright © 1999-2012, Texas Instruments IncorporatedSymbol Parameter Conditions Min Typ Max UnitsMICROWIRE TimingtCSData to Clock Set Up Time See Data Input Timing25nstCHData to Clock Hold Time See Data Input Timing8nstCWHClock Pulse Width High See Data Input Timing25nstCWLClock Pulse Width Low See Data Input Timing25nstESClock to Enable Set Up Time See Data Input Timing25nstCESEnable to Clock Set Up Time See Data Input Timing25nstEWHEnable Pulse Width High See Data Input Timing25nsNote 4:The Electrical Characteristics table lists guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.Note 5:See 3.5 for more current consumption / power dissipation calculation information.Note 6:A specification in modeling PLL in-band phase noise is the 1/f flicker noise, LPLL_flicker (f), which is dominant close to the carrier. Flicker noise has a 10 dB/decade slope. PN10kHz is normalized to a 10 kHz offset and a 1 GHz carrier frequency. PN10kHz = LPLL_flicker (10 kHz) - 20log(Fout / 1 GHz), where LPLL_flicker(f)is the single side band phase noise of only the flicker noise's contribution to total noise, L(f). To measure LPLL_flicker (f) it is important to be on the 10 dB/decadeslope close to the carrier. A high compare frequency and a clean crystal are important to isolating this noise source from the total phase noise, L(f). LPLL_flicker (f)can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL inband phase noise performance is the sum ofLPLL_flicker (f) and LPLL_flat(f).Note 7:A specification in modeling PLL in-band phase noise is the Normalized Phase Noise Contribution, LPLL_flat (f), of the PLL and is defined as PN1Hz =LPLL_flat (f) – 20log(N) – 10log(fCOMP). LPLL_flat(f) is the single side band phase noise measured at an offset frequency, f, in a 1 Hz Bandwidth and fCOMPis the phasedetector frequency of the synthesizer. LPLL_flat (f) contributes to the total noise, L(f). To measure LPLL_flat(f) the offset frequency, f, must be chosen sufficientlysmaller then the loop bandwidth of the PLL, and yet large enough to avoid a substantial noise contribution from the reference and flicker noise. LPLL_flat (f) can bemasked by the reference oscillator performance if a low power or noisy source is used.Note 8:Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction and stay in lock from the ambient temperature and programmed state at which the device was when register R15 was programmed. The action of programming the R15 register, even to the same value, activates a frequency calibration routine. This implies that the device will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reprogram the R15 register to ensure that the device stays in lock. Regardless of what temperature the device was initially programmed at, the ambient temperature can never drift outside the range of -40 °C ≤ T A≤ 85 °C without violating specifications. For this specification to be valid, the programmed state of the device must not change after R15 is programmed.Note 9:The lower sensitivity indicates the typical sensitivity at the lower end of the tuning range, the higher sensitivity at the higher end of the tuning rangeNote 10:Output power varies as a function of frequency. When a range is shown, the higher output power applies to the lower frequency and the lower output power applies to the higher frequency.Note 11:VCO phase noise is measured assuming the VCO is the dominant noise source due to a 75 Hz loop bandwidth. Over frequency, the phase noise typically varies by 1 to 2 dB, with the worst case performance typically occurring at the highest frequency. Over temperature, the phase noise typically varies by 1 to 2 dB, assuming the device is not reprogrammed. Reprogramming R15 will run the frequency calibration routine for optimum phase noise.Note 12:The Clock Distribution Section includes all parts of the device except the PLL and VCO sections. Typical Additive Jitter specifications apply to the clock distribution section only and this adds in an RMS fashion to the shaped jitter of the PLL and the VCO.Note 13:For CLKout frequencies above 1 GHz, the delay should be limited to one half of a period. For 1 GHz and below, the maximum delay can be used.Note 14:Specification is guaranteed by characterization and is not tested in production.Note 15:Applies to GOE, LD, and SYNC*.Note 16:Applies to CLKuWire, DATAuWire, and LEuWire.Serial Data Timing Diagram20211403 Data bits set on the DATAuWire signal are clocked into a shift register, MSB first, on each rising edge of the CLKuWire signal. On the rising edge of the LEuWire signal, the data is sent from the shift register to the addressed register determined by the LSB bits.After the programming is complete the CLKuWire, DATAuWire, and LEuWire signals should be returned to a low state. It is rec-ommended that the slew rate of CLKuWire, DATAuWire, and LEuWire should be at least 30 V/µs.LMK03000 Family Copyright © 1999-2012, Texas Instruments Incorporated9Charge Pump Current Specification Definitions20211431I1 = Charge Pump Sink Current at V CPout = Vcc - ΔV I2 = Charge Pump Sink Current at V CPout = Vcc/2I3 = Charge Pump Sink Current at V CPout = ΔV I4 = Charge Pump Source Current at V CPout = Vcc - ΔV I5 = Charge Pump Source Current at V CPout = Vcc/2I6 = Charge Pump Source Current at V CPout = ΔVΔV = Voltage offset from the positive and negative supply rails. Defined to be 0.5 V for this device.Charge Pump Output Current Magnitude Variation vs. Charge Pump Output Voltage20211432Charge Pump Sink Current vs. Charge Pump Output Source Current Mismatch20211433Charge Pump Output Current Magnitude Variation vs. Temperature20211434LMK03000 Family10Copyright © 1999-2012, Texas Instruments Incorporated分销商库存信息:NATIONAL-SEMICONDUCTORLMK03001DISQ/NOPB LMK03001ISQX/NOPB LMK03001CISQX/NOPB。

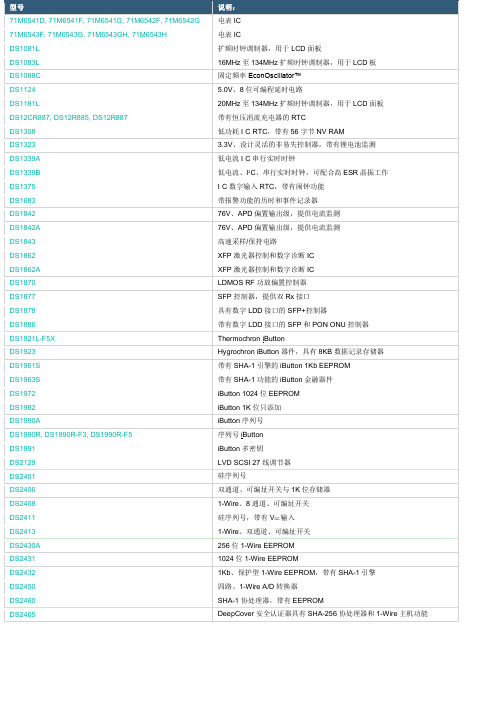

美信芯片中文数据资料

iButton 1024位EEPROM

DS1982

iButton 1K位只添加

DS1990A

iButton序列号

DS1990R, DS1990R-F3, DS1990R-F5

序列号iButton

DS1991

iButton多密钥

DS2129

LVD SCSI 27线调节器

DS2401

硅序列号

具有以太网和CAN接口的网络微控制器

DS8102

双通道Σ-Δ调制器与编码器

DS8113

智能卡接口

DS8113-KIT

DS8113 EMV评估板

DS8313, DS8314

智能卡接口

DS89C430, DS89C440, DS89C450

超高速闪存微控制器

DS89C450-KIT

DS89C450评估套件

12位、多通道ADC/DAC,带有FIFO、温度传感器和GPIO端口

MAX1224, MAX1225

1.5Msps、单电源、低功耗、真差分、12位ADC

MAX1258EVC16, MAX1258EVKIT

MAX1057、MAX1058、MAX1257和MAX1258评估板/评估系统

MAX1274, MAX1275

MAX1034, MAX1035

8/4通道、±VREF多量程输入、串行14位ADC

MAX1072, MAX1075

1.8Msps、单电源、低功耗、真差分、10位ADC

MAX1076, MAX1078

1.8Msps、单电源、低功耗、真差分、10位ADC,内置电压基准

MAX11014, MAX11015

DS9490B, DS9490R

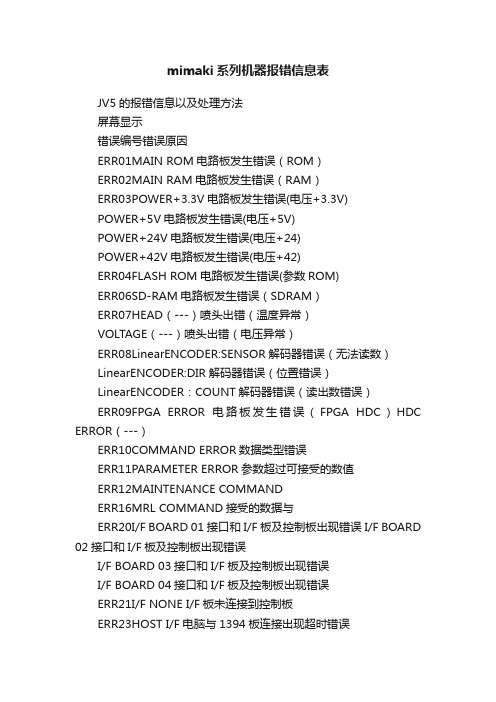

mimaki系列机器报错信息表

喷头出墨 !DO TEST DRAW 栈时间过

长

HEATER POWER OFF

加热器关 闭

PRE PRT AFT **C **C

加热器未 连接(左 BREAK 侧显示的 范例为前 加热器未 连接)

PRE PRT AFT **C **C

L.*>NC [JV5-01]

电热调节 器未连接 (左侧显 THERM 示的范例 为前加热 器的电热 调节器未 连接)

材料加热 器温度异 常

HEADWARM TEMP (---) HEADWARM BREAK (---) HEADWARM THERM (---)

喷头加热 器温度异 常

喷头加热 器未连接 喷头电热 调节器出 错

ERR212 WASTE INKTANK SENSOR

废墨瓶感 应器出错

ERR250 Y COORDINATES

SD-RAM控 制异常

收到的数 据不是版 本升级数 据

I/F板未 安装

I/F板操 作异常

主板与 I/F板连 接错误

电脑与 I/F板连 接超时

ROM0 清 除错误 ROM1 清 除错误 ROM0 写 入错误 ROM1 写 入错误 校验错误 无用信息 检查错误

ERR90 h'******* ERR92 h'******* ERR95 MODE SHIFT ERR98 I/F FORMAT ERR99 VERSION DATA ERR111 NCU ROM 00

**Washing liquid** **unfilling up**

清洁液未 注入

解决方法

相关描述

关闭电源 2-3分钟 后重新开 机如果问 题仍然出 现,联系 经销商。 关闭电源 2-3分钟 后重新开 机如果问 题仍然出 现,联系 经销商。 关闭电源 2-3分钟 后重新开 机如果问 题仍然出 现,联系 经销商。

mimaki系列机器报错信息表

mimaki系列机器报错信息表JV5的报错信息以及处理方法屏幕显示错误编号错误原因ERR01MAIN ROM电路板发生错误(ROM)ERR02MAIN RAM电路板发生错误(RAM)ERR03POWER+3.3V电路板发生错误(电压+3.3V)POWER+5V电路板发生错误(电压+5V)POWER+24V电路板发生错误(电压+24)POWER+42V电路板发生错误(电压+42)ERR04FLASH ROM电路板发生错误(参数ROM)ERR06SD-RAM电路板发生错误(SDRAM)ERR07HEAD(---)喷头出错(温度异常)VOLTAGE(---)喷头出错(电压异常)ERR08LinearENCODER:SENSOR解码器错误(无法读数)LinearENCODER:DIR解码器错误(位置错误)LinearENCODER:COUNT解码器错误(读出数错误)ERR09FPGA ERROR电路板发生错误(FPGA HDC)HDC ERROR(---)ERR10COMMAND ERROR数据类型错误ERR11PARAMETER ERROR参数超过可接受的数值ERR12MAINTENANCE COMMANDERR16MRL COMMAND接受的数据与ERR20I/F BOARD 01接口和I/F板及控制板出现错误I/F BOARD 02接口和I/F板及控制板出现错误I/F BOARD 03接口和I/F板及控制板出现错误I/F BOARD 04接口和I/F板及控制板出现错误ERR21I/F NONE I/F板未连接到控制板ERR23HOST I/F电脑与1394板连接出现超时错误ERR24I/F INITIAL I/F板与控制板初始操作错误ERR25FULL-SPEED电脑与USB2.PACKET SIZE OVER电脑与USB2.0板连接出错。

USB PROTOCOL电脑与USB2.1板连接出错。

USB ENVIRONMENT电脑与USB2.2板连接出错。

40系列CMOS电路型号功能

40193 CMOS 可预制四位二进制计数器

40194 CMOS 4位双向并行存取通用移位寄存器

4020 CMOS 14级二进制串行计数/分频器

40208 CMOS 4×4多端寄存器

4021 CMOS 异步8位并入同步串入/串出寄存器

4022 CMOS 八进制计数器/分频器

4010 CMOS 六缓冲器/转换器(同相)

40100 CMOS 32位双向静态移位寄存器

40101 CMOS 9位奇偶发生器/校验器

40102 CMOS 8位BCD可预置同步减法计数器

40103 CMOS 8位二进制可预置同步减法计数器

40104 CMOS 4位三态输出双向通用移位寄存器

40105 CMOS 先进先出寄存器

40106 CMOS 六施密特触发器

40107 CMOS 2输入双与非缓冲/驱动器

40108 CMOS 4×4多端寄存

40109 CMOS 四三态输出低到高电平移位器

4011 CMOS 四2输入与非门

40110 CMOS 十进制加减计数/译码/锁存/驱动

4035 CMOS 4位并入/并出移位寄存器

4038 CMOS 3位串行负逻辑加法器

4040 CMOS 12级二进制计数/分频器

4041 CMOS 四原码/补码缓冲器

4042 CMOS 四时钟控制 D 锁存器

4043 CMOS 四三态或非 R/S 锁存器

4502 CMOS 可选通六反相缓冲器

4503 CMOS 六三态同相缓冲器

4504 CMOS 六TTL-CMOS电平移位器

4506 CMOS 双二组2输入可扩展与或非门

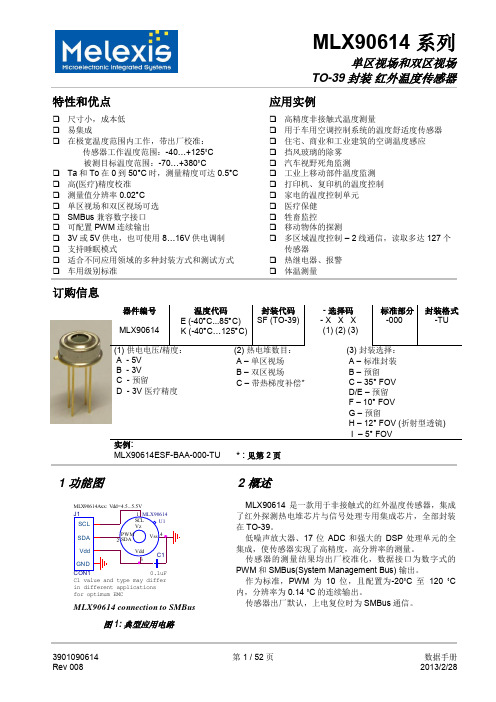

Datasheet MLX90614 中文 数据手册 rev008

10-位 PWM 输出模式是连续输出所测物体温度的标准配置,测量物体的温度范围为-20…120 °C,分辨 率为 0.14 °C。PWM 通过修改 EEPROM 内 2 个单元的值,实际上可以根据需求调整至任何温度范围,而这对 出厂校准结果并无影响。

传感器的测量结果均出厂校准化,数据接口为数字式的 PWM 和 SMBus(System Management Bus) 输出。

作为标准,PWM 为 10 位,且配置为-20˚C 至 120 ˚C 内,分辨率为 0.14 ˚C 的连续输出。

传感器出厂默认,上电复位时为 SMBus 通信。

3901090614 Rev 008

PWM 引脚也可配置为热继电器(输入是 To),这样可以实现简单且性价比高的恒温控制器或温度报警(冰 点/沸点)应用,其中的温度临界值是用户可编程的。在 SMBus 系统里,这个功能可以作为处理器的中断信号, 以此触发读取主线上从动器的值,并确定精度条件。

传感器有两种供电电压选择:5V 或 3V(电池供电)。其中,5V 也可简便的从更高供电电压(例如 8 至 16V)上通过外接元件调制。(具体请参考“应用信息”)

MLX90614 connection to SMBus

图 1: 典型应用电路

2 概述

MLX90614 是一款用于非接触式的红外温度传感器,集成 了红外探测热电堆芯片与信号处理专用集成芯片,全部封装 在 TO-39。

低噪声放大器、17 位 ADC 和强大的 DSP 处理单元的全 集成,使传感器实现了高精度,高分辨率的测量。

4000系列逻辑芯片

4000系列逻辑芯片4000系列逻辑芯片是由德州仪器(Texas Instruments)于1971年推出的一系列逻辑集成电路产品。

该系列芯片使用CMOS (互补型金属氧化物半导体)技术制造,可提供高速和低功耗的逻辑功能。

这些芯片广泛应用于电子设备的控制和数字逻辑电路设计中。

4000系列逻辑芯片采用14引脚DIP封装,方便与其他器件进行连接和布线。

该系列芯片的命名规则为CD4XXX,其中XXX代表具体的逻辑功能。

4000系列逻辑芯片主要包括以下几种类型的芯片:1. 4001:四位双输入的2输入与非门(NOR)芯片。

该芯片可用于实现逻辑与(AND)门、逻辑非(NOT)门等功能。

2. 4011:四位双输入的2输入与门(AND)芯片。

该芯片可用于实现逻辑或(OR)门、逻辑异或(XOR)门等功能。

3. 4013:双位双触发边沿触发器芯片。

该芯片可用于实现存储功能,用于时序逻辑电路设计。

4. 4026:双位5位数字计数器芯片。

该芯片可用于实现数字计数功能,在数字显示电路中被广泛应用。

5. 4060:十二位异步二进制计数器芯片。

该芯片可用于实现长时间计数功能,可应用于定时器设计等领域。

6. 4093:四位双输入的2输入门(NAND)芯片。

该芯片可用于实现逻辑与非(NAND)门、逻辑或非(NOR)门等功能。

4000系列逻辑芯片具有以下优点:1. 高集成度:4000系列芯片具有高度集成的特点,能够实现多种逻辑功能,并且可与其他芯片进行组合,实现更复杂的电路设计。

2. 低功耗:由于采用CMOS技术制造,4000系列芯片具有低功耗的特点。

在电池供电或需要节能的设备中,这种低功耗特性非常有价值。

3. 高可靠性:4000系列芯片具有高抗干扰性和稳定性,能够在各种复杂的工作环境下正常工作,具有较高的可靠性。

综上所述,4000系列逻辑芯片是一类具有高集成度、低功耗和高可靠性的逻辑集成电路产品。

其广泛应用于各种电子设备中,为数字电路设计和控制提供了有效的解决方案。

LMK01010资料

Parameter Power Supply Voltage Input Voltage Storage Temperature Range Lead Temperature (solder 4 s) Junction Temperature

Symbol

VCC VIN TSTG TL TJ

Ratings -0.3 to 3.6 -0.3 to (VCC + 0.3) -65 to 150

3

元器件交易网

LMK01000/LMK01010/LMK01020

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Each device features 8 clock outputs with independently programmable dividers and delay adjustments. The outputs of the device can be easily synchronized by an external pin (SYNC*).

— LMK01010: 8 LVDS outputs — LMK01020: 8 LVPECL outputs — Channel divider values of 1, 2 to 510 (even divides) — Programmable output skew control

LM4041AIM3-1.2资料

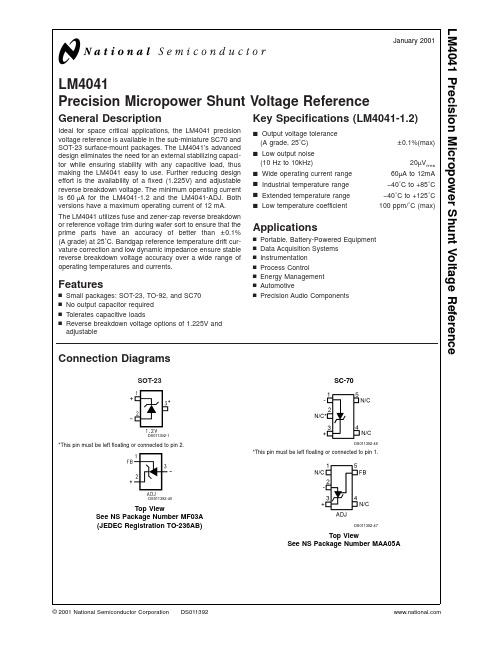

Key Specifications (LM4041-1.2)

j Output voltage tolerance (A grade, 25˚C)

j Low output noise (10 Hz to 10kHz)

j Wide operating current range j Industrial temperature range j Extended temperature range j Low temperature coefficient

Reverse Breakdown

Package

Voltage Tolerance at 25˚C and

M3 (SOT-23)

M7 (SC70)

Z (TO-92) NS

Average Reverse Breakdown Voltage Temperature

Supplied as 1000 Units Tape and

20 mA 10 mA

15V

306 mW 550 mW 241mW −65˚C to +150˚C

+215˚C +220˚C

Soldering (10 seconds)

+260˚C

ESD Susceptibility

Human Body Model (Note 3)

2 kV

Machine Model (Note 3)

RAD

Voltage or Reference Voltage Tolerance A = ±0.1%, B = ±0.2%, C = ±0.5%, D = ±1.0%, E = ±2.0%

2

LM4041

CMOS 4000系列数字集成电路型号功能表

CMOS 4000系列数字集成电路型号功能表4000系列4000 双3输入或非门加1输入反相器4001 四2输入或非门4002 双4输入或非门4006 18位串入串出静态移位寄存器4007 双互补对加反相器4008 4位二进制超前进位全加器4009 六缓冲器/电平变换器(反相)4010 六缓冲器/电平变换器(同相)4011 四2输入与非门4012 双4输入与非门4013 双D型触发器(带预置和清除端)4014 8位串入/并入串出移位寄存器4015 双4位串入并出移位寄存器4016 四双向模拟开关4017 十进制计数/分配器4018 可预置1/N计数器4019 四2选1数据选择器4020 14位二进制串行计数器4021 8位静态移位寄存器4022 八进制计数/分配器4023 三3输入与非门4024 7位二进制串行计数器/分频器4025 三3输入或非门4026 十进制计数/七段译码器4027 双J—K主从触发器4028 BCD十进制译码器4029 4位可预置/可逆计数器4030 四异或门4031 64位静态移位寄存器4032 三串行加法器(同相)4033 十进制计数/七段译码器4034 8位通用总线寄存器4035 4位并入/并出移位寄存器4038 三串行加法器(反相)4040 12位二进制计数器4041 四同相/反相缓冲器4042 四D型锁存器4043 四或非R—S锁存器(三态)4044 四与非R—S锁存器(三态)4045 21位计数器4046 锁相环4047 无稳态/单稳态多谐振荡器4048 8输入多功能门(三态可扩展)4049 六缓冲器/电平变换器(反相)4050 六缓冲器/电平变换器(同相)4051 单8通道模拟开关4052 双4通道模拟开关4053 三2通道模拟开关4054 四段液晶显示驱动4055 BCD—7段液晶显示译码/驱动器4056 BCD—7段液晶显示译码/驱动器4058 双4位锁存器4059 1/N计数器4060 14位二进制串行计数器/分频器4063 4位数值比较器4066 四双向模拟开关4067 单16通道模拟开关4068 8输入与非/与门4069 六反相器4070 四异或门4071 四2输入或门4072 双4输入或门4073 三3输入与门4075 三3输入或门4076 四D型寄存器(三态)4077 四异或非门4078 8输入或非/或门4081 四2输入与门4082 双4输入与门4085 双2路2输入与或非门4086 四2输入与或非门4089 二进制系数乘法器4093 四2输入与非施密特触发器4094 8位移位存贮总线寄存器4095 3输入J—K触发器4096 3输入J—K触发器4097 双8通道模拟开关4098 双可再触发单稳态触发器4099 8位可寻址锁存器4500系列4501 双4输入端与非门4502 六反相器/缓冲器4503 六缓冲器(三态)4504 六电平变换器4505 64位静态随机存贮器4506 双2输入可扩展或非门4507 四异或门4508 双4位D锁存器4510 可预置BCD可逆计数器4511 BCD-七段译码器 /驱动器4512 8选1数据选择器4513 BCD-七段译码器 /驱动器4514 4-16线译码器4515 4-16线译码器4516 可预置二进制可逆计数器4517 双64位静态移位寄存器4518 双BCD同步加计数器4519 4位与或选择器4520 双4位二进制同步加计数器4521 24组分频器4522 可预置BCD 同步1/N计数器4526 可预置4位二进制1/N计数器4527 BCD系数乘法器4528 双可重触发单稳态触发器4529 双四通道模拟开关4530 双5输入过半数逻辑门4531 12位奇偶校验器4532 8位优先编码器4534 实时五、十进制计数器4536 可编程定时器4538 双精密可重触发单稳态触发器4539 双4通道数选择器4541 可编程定时器4543 BCD-七段译码器 /驱动器4544 BCD-七段译码器 /驱动器4547 BCD-译码/大流动驱动器4549 近似函数寄存器4551 四2通道模拟开关4553 三数字BCD计数器4555 双4选1译码器4556 双4选1译码器4557 1-64位可变长度移位寄存器4558 BCD-七段译码器4559 近似函数寄存器4560 “N”BCD加法器4561 “9”求补器4562 128位静态移位寄存器4566 工业定时基准发生器4568 相位比较器和可编程计数器4569 双可预置BCD/二进计数器4572 四反相器输入或/与非门4574 四可编程电压比较器4582 超前进位电路4583 双施密特触发器4584 六施密特触发器4585 4位数值比较器4590 单4位锁存器4597 8位总线兼容锁存器(三态)4599 8位可寻址锁存器40000系列40100 32级静态左/右移位寄存器40101 9位奇偶发生器/校验器40102 可预置2位十进制减法计数器40103 可预置8位二进制减法计数器40104 4通用双向移位寄存器40105 16×4先入先出寄存器(三态)40106 六施密特触发器(反相)40107 双3输入与非缓冲器/驱动器40108 4×4多路寄存器(三态)40109 四电平变换器40110 十进制计数/锁存/译码/驱动40147 10~4线BCD优先编码器40160 可预置十进制计数器40161 可预置二进制计数器40162 可预置十进制计数器40163 可预置4位二进制计数器40174 六D型触发器40175 四D触发器40181 4位算术逻辑单元40182 超前进位发生器40192 可预置十进制可逆计数器40193 可预置二进制可逆计数器40194 4位双向通用移位寄存器40195 4位双向通用移位寄存器。

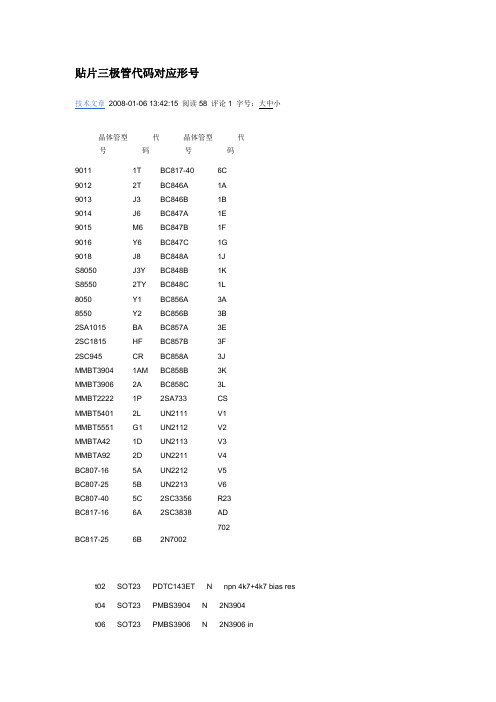

贴片三极管代码对应形号

贴片三极管代码对应形号技术文章2008-01-06 13:42:15 阅读58 评论1 字号:大中小晶体管型号代码晶体管型号代码9011 1T BC817-40 6C9012 2T BC846A 1A9013 J3 BC846B 1B9014 J6 BC847A 1E9015 M6 BC847B 1F9016 Y6 BC847C 1G9018 J8 BC848A 1JS8050 J3Y BC848B 1KS8550 2TY BC848C 1L8050 Y1 BC856A 3A8550 Y2 BC856B 3B2SA1015 BA BC857A 3E2SC1815 HF BC857B 3F2SC945 CR BC858A 3JMMBT3904 1AM BC858B 3KMMBT3906 2A BC858C 3LMMBT2222 1P 2SA733 CSMMBT5401 2L UN2111 V1MMBT5551 G1 UN2112 V2MMBTA42 1D UN2113 V3MMBTA92 2D UN2211 V4BC807-16 5A UN2212 V5BC807-25 5B UN2213 V6BC807-40 5C 2SC3356 R23BC817-16 6A 2SC3838 ADBC817-25 6B 2N7002702t02 SOT23 PDTC143ET N npn 4k7+4k7 bias res t04 SOT23 PMBS3904 N 2N3904t06 SOT23 PMBS3906 N 2N3906 inT1 IMT1A DA 2 x 2SA1037AK pnpT1 SOT23 BCX17 PNPT1 SOT23 BCX17 N BC327T1 SOT23 BSS63 N pnp 100V 0.1At11 SOT23 PDTA114TT N pnp + rest12 SOT23 PDTC114TT N npn + rest16 SOT323 PDTC114EU N npn + rest17 SOT323 PDTC124EU N npn + rest18 SOT23 PDTC143ZT N npn 4k7+47k bias res t19 SOT23 PDTA143ZT N pnp 4k7+47k bias res t1A SOT23 PMMT3904 N 2N3904t1A SOT323 PMST3904 N 2N3904t1B SOT23 PMBT2222 N 2N2222t1B SOT233 PMST2222 N 2N2222t1D SOT23 PMBTA42 N MPSA42 300V npnt1D SOT323 PMSTA42 N MPSA42 300V npnt1E SOT23 PMBTA43 N MPSA43 200V npnt1E SOT323 PMSTA43 N MPSA43 200V npnt1F SOT23 PMBT5550 N 2N5550 140V npnt1F SOT323 PMST5550 N 2N5550 140V npnt1G SOT23 PMMTA06 N MPSA06t1G SOT323 PMMTA06 N MPSA06t1H SOT323 MMBTA05 N MPSA05t1J SOT23 PMBT2369 N 2N2369t1J SOT323 PMBT2369 N 2N2369t1K SOT23 PMBT6428 N MPSA18 50Vt1K SOT323 PMBT6428 N MPSA18 50Vt1L SOT23 PMBT6429 N MPSA18 45Vt1L SOT323 PMBT6429 N MPSA18 45Vt1M SOT23 PMBTA13 N MPSA13 darlingtont1N SOT23 PMBTA14 N MPSA14 darlingtonT1N10 SOT223 MMFT1N10T1 MOSFETT1p SOT23 BCX17 N BC327t1P SOT23 PMBT2222A N 2N2222At1P SOT323 PMST2222A N 2N2222At1Q SOT23 PMBT5088 N MPSA18 Vce 30Vt1Q SOT323 PMST5088 N MPSA18 Vce 30Vt1R SOT323 PMST5089 N MPSA18 Vce 25VT1t SOT23 BCX17 N BC327T2 IMT2A DB 2 x 2SA1037AK pnpT2 SOT23 BCX18 PNPT2 SOT23 BCX18 N BC328T2 SOT23 HSMS-2862 D dual series HSMS-286B T2 SOT23 TN2460T MOSFETT2 SOT323 HSMS-286C D dual series HSMS-286B t23 SOT323 PDTA114TU N pnp +10k Wypr. rest24 SOT323 PDTC114TU N npn +10k resT2406 SOT223 MMFT2406T1 MOSFETt2A SOT23 PMBT3906 N 2N3906t2A SOT323 PMST3906 N 2N3906t2B SOT23 PMBT2907 N 2N2907t2D SOT23 PMBTA92 N MPSA92 pnp Vce 300Vt2D SOT323 PMSTA92 N MPSA92 pnp Vce 300V t2E SOT23 PMBTA93 N MPSA93 pnp Vce 200Vt2E SOT323 PMSTA93 N MPSA93 pnp Vce 200V t2F SOT23 PMBT2907A N 2N2907At2F SOT323 PMBT2907A N 2N2907At2G SOT23 PMBTA56 N MPSA56t2G SOT323 PMSTA56 N MPSA56t2H SOT23 PMBTA55 N MPSA55t2H SOT323 PMSTA55 N MPSA55t2L SOT23 PMBT5401 N 2N5401 pnp 150Vt2L SOT323 PMST5401 N 2N5401 pnp 150VT2p SOT23 BCX18 N BC328T2t SOT23 BCX18 N BC328t2T SOT23 PMBT4403 N 2N4403t2T SOT323 PMST4403 N 2N4403t2U SOT23 PMBTA63 N MPSA63 darlingtont2V SOT23 PMBTA64 H MPSA64 darlingtont2X SOT23 PMBT4401 N 2N4401t2X SOT323 PMST4401 N 2N4401T3 SOT23 BSS63 PNPT3 SOT23 BSS63 N BSS68T3 SOT23 HSMS-2863 A ca dual HSMS-286BT3 SOT323 HSMS-286E A ca dual HSMS-286BT3166 SOT223 MMFT3166T1 MOSFETT32 2SC4182 N npn RF fT 1.1GHz @3V hfe60-105 T33 2SC4182 N npn RF fT 1.1GHz @3V hfe85-150 T34 2SC4182 N npn RF fT 1.1GHz @3V hfe120-220 T35 SOT23 BSR20 PNPT36 SOT23 BSR20A PNPT4 SOT23 BCX17R PNPT4 SOT23 HSMS-2864 B cc dual HSMS-286BT4 SOT23R BCX17R R BC327T4 SOT323 HSMS-286F B cc dual HSMS-286BT4 SOT363 MBD330DW DL dual UHF schottky diode T42 2SC3545P N npn RF fT 2GHz Hfe 50-100T42 2SC4184 N npn RF fT1.8GHz hFE 40-80T43 2SC3545Q N UHF osc/mix fT 2GHz Hfe70-140 T43 2SC4184 N npn fT1.8GHz hFE 60-120T44 2SC3545R N npn RF fT 2GHz Hfe 120-250T44 2SC4184 N npn RF fT1.8GHz hFE 100-200T5 SOT143 HSMS-2865 S separate dual HSMS-286B T5 SOT23 BCX18R PNPT5 SOT23R BCX18R R BC328T52 SOT23 MMBTS102 TEMP.SENSORT53 SOT23 MMBTS103 TEMP.SENSORT55 SOT23 MMBTS105 TEMP.SENSORT6 SOT23 BSS63R PNPT6 SOT23R BSS63R R BSS68T6661 SOT223 MMFT6661T1 MOSFETT7 SOT23 BSR15 PNPT7 SOT23 BSR15 N 2N2907T7 SOT23 SST4117 JFETT71 SOT23 BSR15R PNPT71 SOT23R BSR15R R 2N2907T72 2SC4568 N npn RF ft 5.5GHz hFE 40-80T72 2SC4570 N npn RF ft 5.5GHz hFE 40-80T73 2SC4568 N npn RF ft 5.5GHz hFE 60-120T73 2SC4570 N npn RF ft 5.5GHz hFE 60-120T74 2SC4568 N npn RF ft 5.5GHz hFE 100-200T74 2SC4570 N npn RF ft 5.5GHz hFE 100-200T75 2SC4569 N npn RF fT 5GHz hFE 40-80T75 2SC4571 N npn RF fT 5GHz hFE 40-80T76 2SC4569 N npn RF fT 5GHz hFE 60-120T76 2SC4571 N npn RF fT 5GHz hFE 100-200T76 2SC4571 N npn RF fT 5GHz hFE 60-120T77 2SC4569 N npn RF fT 5GHz hFE 100-200T7p SOT23 BSR15 N 2N2907T7t SOT23 BSR15 N 2N2907T8 SOT23 BSR16 PNPT8 SOT23 BSR16 N 2N2907AT8 SOT23 SST4118 JFETT81 SOT23 BSR16R PNPT81 SOT23R BSR16R R 2N2907AT82 2SC4954 N npn RF fT12GHz @3V 5mAT82 2SC4956 WQ npn RF fT 12GHz @3V 5mA T83 2SC4955 WQ npn RF fT 12GHz @3V 10mA T84 2SC5177 N npn RF fT 13GHz @2V 7mAT84 2SC5178 WQ npn RF fT 13GHz @2V 7mA T84 2SC5179 npn RF fT 13GHz @2V 7mAT86 2SC5182 N npn RF fT 12GHz @2V 20mAT86 2SC5182 NN npn RF fT 12GHz @2V 20mA T86 2SC5183 WQ npn RF fT 12GHz @2V 20mA T88 2SC5191 N npn RF fT 8.5GHz @3V 20mA T88 2SC5192 WQ npn RF fT 8.5GHz @3V 20mA T88 2SC5193 N npn RF fT 8.5GHz @3V 20mA T89 2SC5288 WQ npn RFT8p SOT23 BSR16 N 2N2907AT8t SOT23 BSR16 N 2N2907AT9 SOT23 BSR18 PNPT9 SOT23 SST4119 JFETT90 2SC5289 WQ npn RFT92 2SC1977 WQ pnp RF fT 8.5GHzT92 SOT23 BSR18A PNPT92 SOT23 BSR18A N 2N3904T92P SOT23 BSR18A N 2N3904T93 2SC1978 WQ pnp RF fT 8.5GHzTA SOT23 KTY13A TEMP.SENSETB SOT23 KTY13B TEMP.SENSETC SOT23 KTY13C TEMP.SENSETD SOT23 KTY13D TEMP.SENSETFX SOT23 BAL99 V switching diodetG1 SOT23 PMBT5551 N 2N5551 npn Vce 140V tG1 SOT323 PMST5551 N 2N5551 npn Vce 140V TV SOT23 MMBF112 FETTV SOT23 MMBF112L F RF jfetU SOD323 BB545 I 20-2pF varicapU SOT143 BCV61A NPNU SOT23 BC848A NPNU SOT23 FMMT2369 NPNU SOT23 MMBT2369 NPNU SOT23 PMBT2369 NPNU SOT323 BC848AW NPNU1 SOT143 BGX50A diodax4U1 SOT143 BGX50A BQ quad ring Si sw diodes U1 SOT23 BCX19 NPNU1 SOT23 BCX19 N BC337U16 2SC4183 N npn RF 5V fT1GHz hFE 60-120 U17 2SC4183 N npn RF 5V fT1GHz hFE 90-180 U18 2SC4183 N npn RF 5V fT1GHz hFE 120-240 U1A SOT143 3SK230A UQ dg RF mosfetU1B SOT143 3SK230B UQ dg RF mosfetU1C SOT143 3SK231C UQ dg RF mosfetU1D SOT143 3SK231D UQ dg RF mosfetU1E SOT143 3SK252E UQ dg RF mosfetU1E SOT343 3SK254E UQ dg RF mosfetU1G SOT143 3SK253G UQ dg RF mosfetU1G SOT343 3SK255G UQ dg RF mosfetU1p SOT23 BCX19 N BC337U1t SOT23 BCX19 N BC337U2 SOT23 BCX20 NPNU2 SOT23 BCX20 N BC338U21 2SC4185 N npn RF 10V fT2.4GHz hFE40-80 U22 2SC4185 N npn RF 10V fT2.4GHz hFE60-120 U23 2SC4185 N npn RF 10V fT2.4GHz hFE90-180 U2t SOT23 BCX20 N BC338U3 SOT23 BSS64 NPNU3 SOT23 BSS64 N 120V 0.25A 0.2WU35 SOT23 BSR19 NPNU36 SOT23 BSR19A NPNU4 SOT23 BCX19R NPNU4 SOT23R BCX19R R BC337U5 SOT23 BCX20R NPNU5 SOT23R BCX20R R BC338U55 SOT143 3SK134B UQ dg mosfetU55 SOT343 3SK245 UQ dg mosfetU56 SOT143 3SK134B UQ dg mosfetU56 SOT343 3SK245 UQ dg mosfetU6 SOT23 BSS64R NPNU6 SOT23R BSS64R R 120V 0.25A 0.2WU65 SOT143 3SK135A UQ dg mosfetU66 SOT143 3SK135A UQ dg mosfetU7 SOT23 BSR13 NPNU7 SOT23 BSR13 N 2N2222U71 SOT143 3SK177 UQ dg GaAsfet Idss 5-15mA U71 SOT23 BSR13R NPNU71 SOT23R BSR13R R 2N2222U71 SOT343 3SK299 UQ dg GaAsfet Idss 5-15mA U72 SOT143 3SK177 UQ dg GaAsfet Idss10-25mAU72 SOT343 3SK299 UQ dg GaAsfet Idss 10-25mA U73 SOT143 3SK177 UQ dg GaAsfet Idss 20-35mA U73 SOT343 3SK299 UQ dg GaAsfet Idss 20-35mA U74 SOT143 3SK177 UQ dg GaAsfet Idss 30-40mA U74 SOT343 3SK299 UQ dg GaAsfet Idss 30-40mA U76 SOT143 3SK206 UQ dg GaAsfet Idss 10-25mA U77 SOT143 3SK206 UQ dg GaAsfet Idss 20-35mA U78 SOT143 3SK206 UQ dg GaAsfet Idss 30-50mA U79 SOT143 3SK206 UQ dg GaAsfet Idss 45-80mA U7p SOT23 BSR13 N 2N2222U7t SOT23 BSR13 N 2N2222U8 SOT23 BSR14 NPNU8 SOT23 BSR14 N 2N2222AU81 SOT23 BSR14R NPNU81 SOT23R BSR14R R 2N2222AU87 SOT143 3SK176A UQ dg mosfetU88 SOT143 3SK176A UQ dg mosfetU8p SOT23 BSR14 N 2N2222A。

MCP4021数字电位器

50 kΩ

5.5V

2.7V (注 7)

器件电阻

2.1 kΩ 5 kΩ 10 kΩ 50 kΩ

某一电压下的电流值

5.5V

2.7V

2.25 mA 1.4 mA 450 µA 90 µA

1.1 mA 450 µA 210 µA 40 µA

注释 MCP4022 包括 VWZSE MCP4024 包括 VWFSE

参数

符号 最小值 典型值 最大值

单位

条件

电刷电阻 (注 3,注 4) 标称的电阻温度系数

比率温度系数

RW

—

70

—

70

DR/DT

—

50

—

100

—

150

DVWA/DT —

10

125

Ω

325

Ω

—

ppm/°C

—

ppm/°C

—

ppm/°C

—

ppm/°C

满量程误差 零刻度误差 电位计积分非线性

VWFSE

-0.5

-8.5

+4.5

+8.5

LSb

-0.5 ±0.25

+0.5

LSb

-5.5

+2.5

+5.5

LSb

-0.5 ±0.25

+0.5

LSb

-3

+1

+3

LSb

-0.5 ±0.25

+0.5

LSb

-1

+0.25

+1

LSb

变阻器微分非线性 MCP4021 (注 4,注 8) MCP4022 和 MCP4024 (注 4)

LM4041中文资料

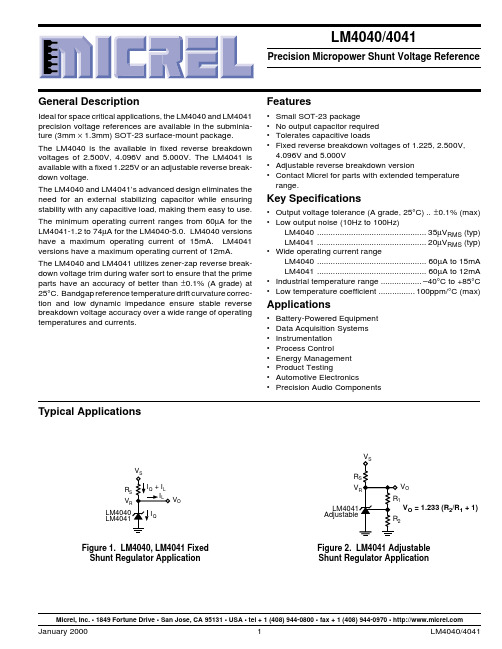

Typical ApplicationsV O V R V V OFigure 2. LM4041 Adjustable Shunt Regulator ApplicationFigure 1. LM4040, LM4041 Fixed Shunt Regulator Application V O = 1.233 (R 2/R 1 + 1)Micrel, Inc. • 1849 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 944-0970 • Part Number *Voltage Accuracy,Temp. Coefficient LM4041AIM3-1.2 1.225V ±0.1%, 100ppm/°C LM4041BIM3-1.2 1.225V ±0.2%, 100ppm/°C LM4041CIM3-1.2 1.225V ±0.5%, 100ppm/°C LM4041DIM3-1.2 1.225V ±1.0%, 150ppm/°C LM4041CIM3-ADJ 1.24V to 10V ±0.5%, 100ppm/°C LM4041DIM3-ADJ1.24V to 10V±1.0%, 150ppm/°CPin Configuration–FB +Adjustable Version SOT-23 (M3) PackageTop ViewFixed Version SOT-23 (M3) PackageTop View +–Pin 3 must float or be connected to pin 2.Part Number *Voltage Accuracy,Temp. Coefficient LM4040AIM3-2.5 2.500V ±0.1%, 100ppm/°C LM4040BIM3-2.5 2.500V ±0.2%, 100ppm/°C LM4040CIM3-2.5 2.500V ±0.5%, 100ppm/°C LM4040DIM3-2.5 2.500V ±1.0%, 150ppm/°C LM4040AIM3-4.1 4.096V ±0.1%, 100ppm/°C LM4040BIM3-4.1 4.096V ±0.2%, 100ppm/°C LM4040CIM3-4.1 4.096V ±0.5%, 100ppm/°C LM4040DIM3-4.1 4.096V ±1.0%, 150ppm/°C LM4040AIM3-5.0 5.000V ±0.1%, 100ppm/°C LM4040BIM3-5.0 5.000V ±0.2%, 100ppm/°C LM4040CIM3-5.0 5.000V ±0.5%, 100ppm/°C LM4040DIM3-5.05.000V±1.0%, 150ppm/°CExample Field Code _ _ A3rd CharacterA = ±0.1%B = ±0.2%C = ±0.5%D = ±1.0%Example FieldCode_ 2 _2nd Character 1 = 1.225V2 = 2.500V 4 = 4.096V 5 = 5.000V A = AdjustableExample: R2C represents Reference, 2.500V,±0.5% (LM4040CIM3-2.5)Note: If 3rd character is omitted, container will indicate tolerance.SOT -23 Package MarkingsExample Field Code R _ _1st CharacterR = ReferenceOrdering InformationAbsolute Maximum RatingsReverse Current.........................................................20mA Forward Current.........................................................10mA Maximum Output VoltageLM4041-Adjustable ...................................................15V Power Dissipation at T A = 25°C (Note 2)................306mW Storage Temperature...............................–65°C to +150°C Lead TemperatureVapor phase (60 seconds)..............................+215°C Infrared (15 seconds)......................................+220°C ESD SusceptibilityHuman Body Model (Note 3).................................2kV Machine Model (Note 3).. (200V)Operating Ratings (Notes 1 and 2)Temperature Range(T MIN ≤ T A ≤ T MAX )..........................–40°C ≤ T A ≤ +85°C Reverse CurrentLM4040-2.5..........................................60µA to 15mA LM4040-4.1..........................................68µA to 15mA LM4040-5.0..........................................74µA to 15mA LM4041-1.2..........................................60µA to 12mA LM4041-ADJ ........................................60µA to 12mA Output Voltage RangeLM4041-ADJ ..........................................1.24V to 10V+Functional Diagram LM4040, LM4041 Fixed Functional Diagram LM4041 Adjustable+LM4040-2.5 Electrical CharacteristicsBoldface limits apply for T A = T J = T MIN to T MAX; all other limits T A = T J = 25°C. The grades A, B, C, and D designate initial Reverse Breakdown Voltage tolerance of ±0.1%, ±0.2%, ±0.5%, and ±1.0 respectively.LM4040AIM3LM4040BIM3LM4040CIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits Limits(Limit)(Note 5)(Note 5)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 2.500VReverse Breakdown Voltage I R = 100µA±2.5±5.0±12mV (max) Tolerance±19±21±29mV (max) I RMIN Minimum Operating Current45µA606060µA (max)656565µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA20ppm/°C Voltage Temperature I R = 1mA151********ppm/°C (max) Coefficient I R = 100µA15ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.3mV Change with Operating0.80.80.8mV (max) Current Change 1.0 1.0 1.0mV (max)1mA ≤ I R 15mA 2.5mV0.60.60.6mV (max)8.08.08.0mV (max)Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.3ΩI AC = 0.1 I R0.80.80.9Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz35µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4040DIM3Symbol Parameter Conditions Typical Units(Note 4)Limits(Limit)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 2.500VReverse Breakdown Voltage I R = 100µA±25mV (max) Tolerance±49mV (max) I RMIN Minimum Operating Current45µA65µA (max)70µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA20ppm/°C Voltage Temperature I R = 1mA15150ppm/°C (max) Coefficient I R = 100µA15ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.3mV Change with Operating 1.0mV (max) Current Change 1.2mV (max)1mA ≤ I R 15mA 2.5mV8.0mV (max)10.0mV (max)Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.3ΩI AC = 0.1 I R 1.1Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz35µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4040-4.1 Electrical CharacteristicsBoldface limits apply for T A = T J = T MIN to T MAX; all other limits T A = T J = 25°C. The grades A, B, C, and D designate initial Reverse Breakdown Voltage tolerance of ±0.1%, ±0.2%, ±0.5%, and ± 1.0% respectively.LM4040AIM3LM4040BIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits(Limit)(Note 5)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 4.096VReverse Breakdown Voltage I R = 100µA±4.1±8.2mV (max) Tolerance±31±35mV (max) I RMIN Minimum Operating Current50µA6868µA (max)7373µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA30ppm/°C Voltage Temperature I R = 1mA20100100ppm/°C (max) Coefficient I R = 100µA20ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.5mV Change with Operating0.90.9mV (max) Current Change 1.2 1.2mV (max)1mA ≤ I R 15mA 3.5mV7.07.0mV (max)10.010.0mV (max)Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.5ΩI AC = 0.1 I R 1.0 1.0Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz80µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4040CIM3LM4040DIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits(Limits)(Note 5)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 4.096VReverse Breakdown Voltage I R = 100µA±20±41mV (max) Tolerance±47±81mV (max) I RMIN Minimum Operating Current50µA6873µA (max)7378µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA30ppm/°C Voltage Temperature I R = 1mA20100150ppm/°C (max) Coefficient I R = 100µA20ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.5mV Change with Operating0.9 1.2mV (max) Current Change 1.2 1.5mV (max)1mA ≤ I R 15mA 3.0mV7.09.0mV (max)10.013.0mV (max)Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.5ΩI AC = 0.1 I R 1.0 1.3Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz80µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4040-5.0 Electrical CharacteristicsBoldface limits apply for T A = T J = T MIN to T MAX; all other limits T A = T J = 25°C. The grades A, B, C, and D designate initial Reverse Breakdown Voltage tolerance of ±0.1%, ±0.2%, ±0.5%, and ± 1.0% respectively.LM4040AIM3LM4040BIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits(Limit)(Note 5)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 5.000VReverse Breakdown Voltage I R = 100µA±5.0±10mV (max) Tolerance±38±43mV (max) I RMIN Minimum Operating Current54µA7474µA (max)8080µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA30ppm/°C Voltage Temperature I R = 1mA20100100ppm/°C (max) Coefficient I R = 100µA20ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.5mV Change with Operating 1.0 1.0mV (max) Current Change 1.4 1.4mV (max)1mA ≤ I R 15mA 3.5mV8.08.0mV (max)12.012.0mV (max)Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.5ΩI AC = 0.1 I R 1.1 1.1Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz80µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4040CIM3LM4040DIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits(Limits)(Note 5)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 5.000VReverse Breakdown Voltage I R = 100µA±25±50mV (max) Tolerance±58±99mV (max) I RMIN Minimum Operating Current54µA7479µA (max)8085µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA30ppm/°C Voltage Temperature I R = 1mA20100150ppm/°C (max) Coefficient I R = 100µA20ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.5mV Change with Operating 1.0 1.3mV (max) Current Change 1.3 1.8mV (max)1mA ≤ I R 15mA 3.5mV8.010.0mV (max)12.015.0mV (max)Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.5ΩI AC = 0.1 I R 1.1 1.5Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz80µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4040 Typical CharacteristicsTest CircuitVLM4041-1.2 Electrical CharacteristicsBoldface limits apply for T A = T J = T MIN to T MAX; all other limits T A = T J = 25°C. The grades A, B, C, and D designate initial Reverse Breakdown Voltage tolerance of ±0.1%, ±0.2%, ±0.5%, and ± 1.0%, respectively.LM4041AIM3LM4041BIM3LM4041CIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits Limits(Limit)(Note 5)(Note 5)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 1.225V Reverse Breakdown Voltage I R = 100µA±1.2±2.4±6mV (max) Tolerance±9.2±10.4±14mV (max) I RMIN Minimum Operating Current45µA606060µA (max)656565µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA20ppm/°C Voltage Temperature I R = 1mA15±100±100±100ppm/°C (max)Coefficient I R = 100µA15ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.7mV Change with Operating 1.5 1.5 1.5mV (max) Current Change 2.0 2.0 2.0mV (max)1mA ≤ I R 15mA 4.0mV6.0 6.0 6.0mV (max)8.08.08.0mV (max) Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.5ΩI AC = 0.1 I R 1.5 1.5 1.5Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz20µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4041DIM3LM4041EIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits(Limit)(Note 5)(Note 5)V R Reverse Breakdown Voltage I R = 100µA 1.225V Reverse Breakdown Voltage I R = 100µA±12±25mV (max) Tolerance±24±36mV (max) I RMIN Minimum Operating Current45µA6565µA (max)7070µA (max)∆V R/∆T Average Reverse Breakdown I R = 10mA20ppm/°C Voltage Temperature I R = 1mA15±150±150ppm/°C (max) Coefficient I R = 100µA15ppm/°C (max)∆V R/∆I R Reverse Breakdown Voltage I RMIN≤ I R 1mA0.3mV Change with Operating 2.0 2.0mV (max) Current Change 2.5 2.5mV (max)1mA ≤ I R 15mA 2.5mV8.08.0mV (max)10.010.0mV (max) Z R Reverse Dynamic Impedance I R = 1mA, f = 120Hz0.3ΩI AC = 0.1 I R 2.0 2.0Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz35µV RMS∆V R Reverse Breakdown Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µALM4041-Adjustable Electrical CharacteristicsBoldface limits apply for T A = T J = T MIN to T MAX; all other limits T J = 25°C unless otherwise specified (SOT-23, see Note 7),I RMIN≤ I R < 12mA, V REF≤ V OUT≤ 10V. The grades C and D designate initial Reverse Breakdown Voltage tolerance of ±0.5% and±1%, respectively for V OUT = 5V.LM4041CIM3LM4041DIM3Symbol Parameter Conditions Typical Units(Note 4)Limits Limits(Limit)(Note 5)(Note 5)V REF Reference Breakdown Voltage I R = 100µA 1.233VV OUT = 5VReference Breakdown Voltage I R = 100µA±6.2±12mV (max) Tolerance (Note 8)±14±24mV (max) I RMIN Minimum Operating Current45µA6065µA (max)6570µA (max)∆V REF Reference Voltage I RMIN≤ I R 1mA0.7mV/∆I R Change with Operating SOT-23: 1.5 2.0mV (max) Current Change V OUT≥ 1.6V 2.0 2.5mV (max)(Note 7)1mA ≤ I R 15mA2mVSOT-23:46mV (max)V OUT≥ 1.6V68mV (max)(Note 7)∆V REF Reference Voltage Change I R = 1mA–1.3mV/V/∆V O with Output Voltage Change–2.0–2.5mV/V (max)–2.5–3.0mV/V (max)I FB Feedback Current60nA100150nA (max)120200nA (max)∆V REF Average Reference V OUT = 5V/∆T Voltage Temperature I R = 10mA20ppm/°C Coefficient I R = 1mA15±100±150ppm/°C (max) (Note 8)I R = 100µA15ppm/°C (max)Z OUT Dynamic Output Impedance I R = 1mA, f = 120HzI AC = 0.1 I RV OUT = V REF0.3ΩV OUT = 10V2Ω (max)e N Wideband Noise I R = 100µA10Hz ≤ f ≤ 10kHz20µV RMS∆V REF Reference Voltage t = 1000hrsLong Term Stability T = 25°C ±0.1°C120ppmI R = 100µAR S 30kV IN1Hz rateTest CircuitNote 1.Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specification and test conditions, see the ElectricalCharacteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2.The maximum power dissipation must be derated at elevated temperatures and is dictated by T JMAX (maximum junction temperature), θJA (junction to ambient thermal resistance), and T A (ambient temperature). The maximum allowable power dissipation at any temperature is PD MAX = (T JMAX – T A )/θJA or the number given in the Absolute Maximum Ratings, whichever is lower. For the LM4040 and LM4041,T JMAX = 125°C, and the typical thermal resistance (θJA ), when board mounted, is 326°C/W for the SOT-23 package.Note 3.The human body model is a 100pF capacitor discharged through a 1.5k Ω resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.Note 4.Typicals are at T J = 25°C and represent most likely parametric norm.Note 5.Limits are 100% production tested at 25°C. Limits over temperature are guaranteed through correlation using Statistical Quality Control (SQL)methods.Note 6.The boldface (over temperature limit for Reverse Breakdown Voltage Tolerance is defined as the room temperature Reverse Breakdown Voltage Tolerance ±[(∆V R /∆T)(65°C)(V R )]. ∆V R /∆T is the V R temperature coefficient, 65°C is the temperature range from –40°C to the reference point of 25°C, and V R is the reverse breakdown voltage. The total over temperature tolerance for the different grades follows:A-grade: ±0.75% = ±0.1% ±100ppm/°C × 65°C B-grade: ±0.85% = ±0.2% ±100ppm/°C × 65°C C-grade: ±1.15% = ±0.5% ±100ppm/°C × 65°C D-grade: ±1.98% = ±1.0% ±150ppm/°C × 65°CExample: The A-grade LM4040-2.5 has an over temperature Reverse Breakdown Voltage tolerance of ±2.5 × 0.75% = ±19mV.Note 7.When V OUT ≤ 1.6V, the LM4041-ADJ must operate at reduced I R . This is caused by the series resistance of the die attach between the die (–)output and the package (–) output pin. See the Output Saturation curve in the Typical Performance Characteristics section.Note 8.Reference voltage and temperature coefficient will change with output voltage. See Typical Performance Characteristics curves.LM4040 and LM4041 Electrical Characteristic NotesLM4041 Typical CharacteristicsLM4041 Typical Characteristics* Output Impedance vs. Freq.Test Circuit‡ Large Signal ResponseTest Circuit† Reverse CharacteristicsTest CircuitApplications InformationThe LM4040 and LM4041 have been designed for stable operation without the need of an external capacitor con-nected between the (+) and (–) pins. If a bypass capacitor is used, the references remain stable.Schottky DiodeLM4040-x.x and LM4041-1.2 in the SOT-23 package have a parasitic Schottky diode between pin 2 (–) and pin 3 (die attach interface connect). Pin 3 of the SOT-23 package must float or be connected to pin 1. LM4041-ADJs use pin 3 as the (–) output.Conventional Shunt RegulatorIn a conventional shunt regulator application (see Figure 1),an external series resistor (R S ) is connected between the supply voltage and the LM4040-x.x or LM4041-1.2 reference.R S determines the current that flows through the load (I L ) and the reference (I Q ). Since load current and supply voltage may vary, R S should be small enough to supply at least the minimum acceptable I Q to the reference even when the supply voltage is at its minimum and the load current is at its maximum value. When the supply voltage is at its maximum and I L is at its minimum, R S should be large enough so that the current flowing through the LM4040-x.x is less than 15mA, and the current flowing through the LM4041-1.2 or LM4041-ADJ is less than 12mA.R S is determined by the supply voltage (V S ), the load and operating current, (I L and I Q ), and the reference ’s reverse breakdown voltage (V R ).R s = (V s – V R ) / (I L + I Q )Adjustable RegulatorThe LM4041-ADJ ’s output voltage can be adjusted to any value in the range of 1.24V through 10V. It is a function of the internal reference voltage (V REF ) and the ratio of the external feedback resistors as shown in Figure 2. The output is found using the equation (1)V O = V REF ´ [ (R2/R1) + 1 ]where V O is the desired output voltage. The actual value of the internal V REF is a function of V O . The “corrected ” V REF is determined by (2)V REF ´ = V O (∆V REF / ∆V O ) + V Ywhere V O is the desired output voltage. ∆V REF / ∆V O is found in the Electrical Characteristics and is typically –1.3mV/V and V Y is equal to 1.233V. Replace the value of V REF ´ in equation (1) with the value found using equation (2).Note that actual output voltage can deviate from that pre-dicted using the typical ∆V REF / ∆V O in equation (2); for C-grade parts, the worst-case ∆V REF / ∆V O is –2.5mV/V and V Y = 1.248V.The following example shows the difference in output voltage resulting from the typical and worst case values of ∆V REF / ∆V O :Let V O = +9V. Using the typical values of ∆V REF /∆V O , V REF is 1.223V. Choosing a value of R1 = 10k Ω, R2 = 63.272k Ω.Using the worst case ∆V REF / ∆V O for the C-grade and D-grade parts, the output voltage is actually 8.965V and 8.946V respectively. This results in possible errors as large as 0.39%for the C-grade parts and 0.59% for the D-grade parts. Once again, resistor values found using the typical value of ∆V REF / ∆V O will work in most cases, requiring no further adjustment.Figure 4. Voltage Level DetectorR1120kR21MR1120k R21M12V Figure 3. Voltage Level DetectorFigure 8. Bidirectional Adjustable Clamp±2.4 to ±6VLM4041-ADJV OUTLM4041-ADJV OUTFigure 7. Bidirectional Adjustable Clamp±18V to ±2.4VIFigure 9. Floating Current DetectorV OUTLM4041-ADJFigure 6. Bidirectional Clamp±2.4VFigure 5. Fast Positive Clamp2.4V + ∆VD1D21N914R3240k R4240kR1LM4041-ADJ1.24V R1I OUT =1µA < I OUT = 100mAI Figure 10. Current SourceFigure 11. Precision Floating Current Detector* D1 can be any LED, V F = 1.5V to 2.2V at 3mA. D1 may act as an indicator. D1 willbe on if I THRESHOLD falls below the threshold current, except with I = O.Package InformationSOT-23 (M3)MICREL INC.1849 FORTUNE DRIVE SAN JOSE, CA95131USATEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.© 2000 Micrel Incorporated。

LMK04808BISQENOPB;LMK04806BISQENOPB;LMK04803BISQENOPB;LMK04808BISQNOPB;中文规格书,Datasheet资料