FX5545G0181V2T2中文资料

R500_中文版

可选择多种天线组 合使用,实现 Wi-Fi 的高可用性

两个 10/100/1000 Mbps 端口;一个配备 PoE

高增益定向天线单元,不仅可 提供信号增益,而且提供干扰 抑制,从而获得扩展的信号范 围、可靠性和高数据速率

所 有 ZoneFlex R500 智 能 Wi-Fi 接 入 点 均 集 成 软 件 控 制 型 PD-MRC( 极 化 分 集) 智 能 天 线, 可 提 供 高 达 4 dB 的 BeamFlex 额外信号增益和 10 dB 干扰抑制,可极大地增强 始终处于移动状态且不断变换方向的移动设备的性能。

借助 Smart/OS 实现先进的 WLAN 应用

与 Ruckus 智能 WLAN 控制器同时使用时, 每台 ZoneFlex R500 均可支持一系列增值应 用,诸如:访客网络、动态预共享密钥(动态 PSK)、热点身份认证、无线干扰检测等。借 助 Smart/OS,可创建多个 WLAN 并将其映射 到相同或不同的接入点或 VLAN。在集中托管的 配置下,ZoneFlex R500 可与各类认证服务器配合使用,如微 软活动目录、LDAP 和 RADIUS。

完成本地和远程管理

每台 ZoneFlex R500 均可以独立接入点身份通过基于 Web 的 GUI、使用 SNMP 或通过 Ruckus FlexMaster Wi-Fi 远程 管理系统进行管理。也可使用 Ruckus 智能 WLAN 控制器进行 本地管理。FlexMaster 是一种基 于 LINUX 的软件平台,使用行业标 准协议通过有线区域连接执行批量配 置、故障检测、监控和一系列故障排 除功能。企业可利用该控制器实现本 地管理和接入点控制、增加发射功率 控制和访客网络等增值服务。

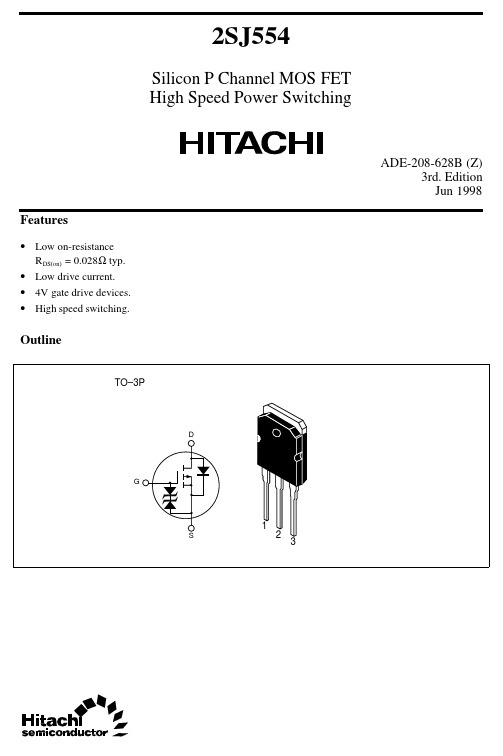

2SJ554中文资料

–3 V

–20

–10

–2.5 V

–2 V

0

–2 –4 –6 –8 –10

Drain to Source Voltage V DS (V)

Drain Current I D (A)

Typical Transfer Characteristics –50

V DS = –10 V 1VMTF5FTU –40

Drain to Source Voltage V DS (V)

5

2SJ554

Reverse Drain Current I DR (A) Repetitive Avalanche Energy E AR (mJ)

Reverse Drain Current vs.

Source to Drain Voltage –50

E Note3 AR

Channel dissipation

Pch Note2

Channel temperature

Tch

Storage temperature

Tstg

Note:

1. PW ≤ 10µs, duty cycle ≤ 1 % 2. Value at Tc = 25°C 3. Value at Tch = 25°C, Rg ≥ 50 Ω

1000 500 200

Switching Characteristics

t d(off) tf

100

tr

50

20

10 –0.1 –0.3

t d(on)

V GS = –10 V, V DD = –30 V PW = 5 µs, duty <= 1 %

–1 –3 –10 –30 –100

Drain Current I D (A)

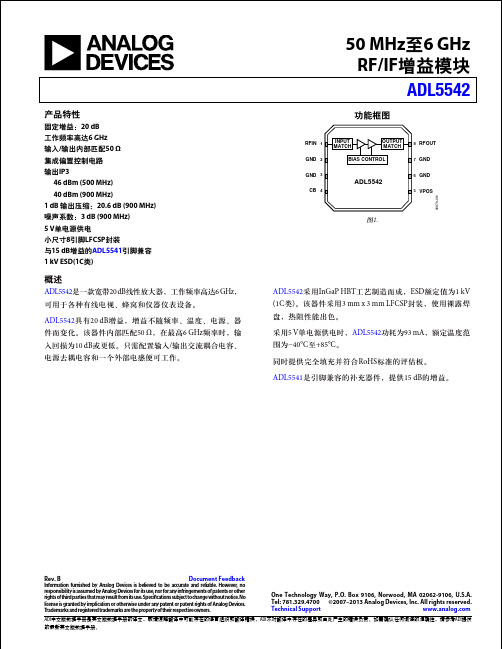

ADL5542 RF IF增益模块说明书

ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

50 MHz 至6 GHz RF/IF 增益模块ADL5542Rev. BDocument Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2007–2013 Analog Devices, Inc. All rights reserved. Technical Support 功能框图2GND 7GND1RFIN 8RFOUT3GND 6GND4CB 5VPOSINPUT MATCHOUTPUT MATCHBIAS CONTROL ADL554206879-001图1.产品特性固定增益:20 dB 工作频率高达6 GHz 输入/输出内部匹配50 Ω集成偏置控制电路输出IP3 46 dBm (500 MHz)40 dBm (900 MHz)1 dB 输出压缩:20.6 dB (900 MHz)噪声系数:3 dB (900 MHz)5 V 单电源供电小尺寸8引脚LFCSP 封装与15 dB 增益的ADL5541引脚兼容1 kV ESD(1C 类)概述ADL5542是一款宽带20 dB 线性放大器,工作频率高达6 GHz ,可用于各种有线电视、蜂窝和仪器仪表设备。

Inspiron 5545 笔记本电脑使用说明书

3 摄像头

您可通过摄像头进行视频聊天、拍摄照片和摄制视频。

4 右侧麦克风

提供高品质数字声音输入以进行录音和语音呼叫等。

视图

尺寸和重量

高度: 触摸屏 非触摸屏

宽度 厚度 重量:

触摸屏 非触摸屏

规格

22 毫米(0.87 英寸) 21.80 毫米(0.86 英寸) 380.40 毫米(14.98 英寸) 259 毫米(10.20 英寸)

存储 –40°C 至 65°C(–40°F 至 149°F)

0% 至 95%(无冷凝) 1.30 GRMS 160 G‡

–15.2 米至 10,668 米 (–50 英尺至 35,000 英尺)

尺寸和重量

系统信息

内存

端口和接口

通信

视频

音频

存储

介质卡读取器

显示屏

键盘

摄像头

触摸板

电池

电源适配器

计算机环境

2.38 千克(5.25 磅) 2.18 千克(4.81 磅) 注:便携式计算机ss重量视订购配置和制造差异而有所不同。

尺寸和重量

系统信息

内存

端口和接口

通信

视频

音频

存储

介质卡读取器

显示屏

键盘

摄像头

触摸板

电池

电源适配器

计算机环境

视图

系统信息

计算机型号 处理器 芯片组

规格

Inspiron 5545 • 配置 Radeon R5 显卡的 AMD A8-7100 APU • 配置 Radeon R6 显卡的 AMD A10-7300 APU AMD A76M FCH

触摸板

电池

电源适配器

计算机环境

mil-dtl-5541f中文版

MIL -DTL - 5541F铝和铝合金的化学转化膜1.范围范围。

此规格涉及通过与表面爲铝和铝合金的化学转化材料反应而组成的化学转化膜。

分类。

化学转化膜有如下类型和等级。

类型。

化学转化膜有如下类型(见:类型I—包含六价铬的组成物类型II—无六价铬的组成物等级。

通过于铝和铝合金化学反应贰组成的材料有如下等级(见和)等级1A—爲最大限度保护防止喷涂的或者未喷涂处的腐蚀、等级3—爲保护防止需低电性阻值处的腐蚀2. 适用文件大意:此部分所列文件在本说明的第三和第四部分都有详细列明。

本部分不包含此说明中其他章节所引用的文件,推荐的附加信息文件以及用作事例的文件。

爲确保此清单的完整性已作出很多努力,文件使用者应注意,必须满足章节3或4引用文件的要求,不管这些文件有没有在此列明。

政府文件规格和标准。

以下规格和标准组成本文件的一部分。

除非特别指定,这些文件的问题引用在恳请或合同中。

联邦标准FED-STD-141--- 喷涂、油漆、涂漆和其他相关材料:检验、抽验和测试的方法国防部标准MIL-PRF-23377 --- 涂底漆:环氧基树脂,高固形化MIL-DTL-81706--- 用于涂覆铝及铝合金的化学转化膜MIL-PRF-85582--- 涂底漆:环氧基树脂,waterborne( 这些文件的副本可以在网站或者在线查看,或者也可以从位于PA19111-5094费城4D大厦700罗宾逊大街的标准文件预定服务台索取)非政府出版物。

以下规格和标准组成本文件的一部分。

除非特别指定,这些文件的问题引用在恳请或合同中。

美国材料试验协会ASTM-B117 ---- 盐雾试验仪器操作ASTM-D3359--- 胶带附着力测试(这些文件副本可以从位于PA19428-2959 ,west conshohocken, ASTM 获得或者从网站了解)美国质量协会(ASQ)ASQ-Z --- 通过属性进行程序,抽样及台板检验(此文件副本可从位于美国密尔沃基市的美国质量协会获得或从网站了解到。

Genuinetek蜂易达手机信号放大器选型指南

Genuinetek蜂易达手机信号放大器选型指南家庭用户信号不好存在多种情况,根据不同情况,应选用不同的手机信号放大器。

针对不同情况有不同的解决方案,不可一刀切。

底层小区信号差室外街道有较好的信号,室内信号较差,这个是一般的情况,主要是周边的建筑把基站的信号挡住了造成的。

这种情况是很常见的,可以加装Genuinetek蜂易达FX-Std系列信号放大器解决。

农村、郊区信号差室外有微弱信号,室内基本没有信号,信号差是由于农村、郊区基站不够密集,有些地方距离基站较远,造成了信号微弱。

应选用TX侧输出功率较高,增益较大的FX-HS系列提高最大传输距离。

大型厂房、别墅信号差室外街道有较好信号,室内基本没有信号,信号差是由于别墅、厂房的房间里面的钢筋混凝土很难被900Mhz左右频率的手机信号穿过,信号被挡住了,应选用蜂易达RX侧最大输出功率较高的FX-Pro提高室内覆盖面积。

高层信号差高层的手机信号差的原因和以上几点都不同,其实高层的手机信号并不差,那为什么会仍然打不通电话呢?主要是因为高层可以接收到附近好几个基站传过来的信号,然而因为没有阻挡,所以信号强度也差不多,于是手机就会在几个基站之间频繁地切换,这就是所谓的“乒乓效应”;另外,手机还有可能会收到非相邻的基站的信号,由于手机只能在相邻的基站间进行切换,就会造成其实有一个更好信号的基站的信号手机能收到,却由于基站不相邻无法切换过去,造成所谓的“孤岛效应”。

据介绍,乒乓效应和孤岛效应是目前移动通信的难题,加装第二代的蜂信通手机信号放大器高层版可以有效改善,其原理和解决方案也跟上述情况不同。

乒乓效应会造成手机频繁切换经常掉线,孤岛效应会造成手机脱网。

Genuinetek 蜂易达的FX-Pro可以有效解决乒乓效应和孤岛效应。

越区切换因为越区切换不成功也会造成手机掉线。

移动的运营商是通过基站和手机发送电磁波通信而为用户服务的。

然后一般基站都是蜂窝状的,覆盖范围有限,在一个较大的区域内有可能会同时有几个不同的基站。

wifi 无线SIP电话机--飞音时代简介

产品性能

� 通过多家海外运营商的入网测试并取得批量应用,包括 KT (Korean Telecom), KCT, LG Telecom,SK Telecom等 � 优秀的语音质量和长时间 工作稳定性。

� � - G.729 PAMS value > 4.0 - G.711 PAMS value > 4.3

处理外销业务2009主力产品g501推出产品设计向mipscpu平台迁徙g501通过韩国移动运营商skt测试开始进入批量销售voip电话机产品ip300ip500获得韩国政府tta安全认证并开始进入批量销售飞音voipiad产品合计销售超过100万台北京飞音时代技术有限公司顺利通过国家高新技术企业复审2010推出无线voip解决方案包括支持无线的voipiad产品及wifiphone产品在深圳设立深圳爱斯瑞科科技有限公司负责硬件产品的设计及外协厂管理飞音voip终端产品进入印度市场2011voip电话机产品ip6xx系列ip652ip622ip542n推向市场并在俄罗斯批量应用韩国运营商kct定制ieee80211n无线路由器通过bmt测试开始批量销售支持wifi的桌面式voip电话ip542n获得市场青睐北京飞音时代获得第一份发明专利授权专利号

重点产品介绍-G502N

• 采用低成本的1T1R无线路由器芯片RT5350实现,CPU 内核为MISP24KEc 360MHz主频 • 支持2路 FXS 接口;满足双路同时工作时G.729 PESQ 大于4.0 • 综合性能高于CISCO 同类产品 SPA2102 • 得益于飞音强大的软件DSP设计能力,我们得以推出此款产品;此架构在1~2端口 IAD 设备上具有绝对性价比优势;

北京飞音时代技术有限公司

2012年版本 David Huang

AD5541JR中文资料

a

5 V, Serial-Input Voltage-Output, 16-Bit DACs

AD5541/AD5542

FEATURES Full 16-Bit Performance 5 V Single Supply Operation Low Power Short Settling Time Unbuffered Voltage Output Capable of Driving 60 k⍀

Zero Code Temperature Coefficient AD5542

Bipolar Resistor Matching

Bipolar Zero Offset Error

Bipolar Zero Temperature Coefficient

± 0.5 ± 1.0

± 0.5 ± 2.0

± 0.5 ± 4.0

Unipolar Operation AD5542, Bipolar Operation

LOGIC INPUTS

Input Current

VINL, Input Low Voltage VINH, Input High Voltage Input Capacitance3 Hysteresis Voltage3

AGND

REFF

REFS CS

LDAC SCLK

DIN

AD5542

RINV

CONTROL LOGIC

DGND VDD RFB

16-BIT DAC

16-BIT DATA LATCH SERIAL INPUT REGISTER

DGND

RFB INV VOUT AGNDF

AGNDS

PRODUCT HIGHLIGHTS 1. Single Supply Operation.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VishayLow Profile 3mm DC/DC Buck Converter0.8V to 4.5V*, 3A with 380W/in3 Power DensityEfficiency up to 95%FEATURES•Fully integrated DC/DC converter•Advanced development of FX5545G305•High efficiency over large load range•100% duty cycle•Power density - more than 380W/inch3•1µA shutdown current•2.5V to 6V input range (1Li+ and 3-cell NiCd or NiMH cells)•0.8V to 4.5V* output voltage•Programmable PWM/PSM controls•Low output ripple•BGA construction•Temperature range: - 40°C to + 85°C•No external components required•Output power 10W•Maximum current 3A•Low profile*Note: For higher putput voltage please consult factory atFunctionPAK@The DC/DC converter is a programmable topology synchronized Buck converter for today’s continuous changing portable electronic market. The DC/DC converter provides flexibility of utilizing various battery configurations and chemistries such as NiCd, NiMH, or Li+ with an input voltage range of 2.5V to 6V. An additional flexibility is provided with topology programmability to power multiple loads such as power amplifiers, microcontrollers, or baseband logic IC’s. For ultra-high efficiency, converters are designed to operate in synchronous rectified PWM mode under full load while transforming into externally controlled The DC/DC converter is available in 20-ports BGA package. In order to satisfy the stringent ambient temperature requirements, the DC/DC converter is designed to handle the industrial temperature range of - 40°C to + 85°C.APPLICATION•Cordless phones, PDAs and others•Supply voltage source for low-voltage chip sets•Point of Load (POL) applications such as drivers for FPGA’s, microprocessors, DSP’s amplifiers, etc.•Portable computers•Battery back-up supplies•CamerasORDERING INFORMATIONFX5545G008FUNCTIONSIZECIRCUIT IDENTIFIER - G008 or G018OUTPUT VOLTAGE - Example: 1.2V should be written as 1V2 as the V indicates the decimal point or ADJ for adjustable version - self selectable output voltage. G018ADJ is only available in the adjustable version for Vout = 0.9V - 1.3V. For design considerations please see ANF110PACKAGING - B1 = 10pcs in bulk; B5 = 50pcs in bulk; T1 = 13” reel; T2 = 7” reel.For lead (Pb)-free solder please add E2 suffix.VishayDIMENSIONS in inches [millimeters]L0.58 ± 0.01[14.7 ± 0.25]W0.48 ± 0.01[12.2 ± 0.25]A0.1 ± 0.01[2.54 ± 0.25]B0.09 ± 0.01[2.29 ± 0.25]C0.09 ± 0.01[2.27 ± 0.25]T0.126 max[3.2 max]Ball Diameter0.03 ± 0.001[0.762 ± 0.025]/doc?10119For adjustable version please refer to Self Selectable Output Voltageapplication note which is available at /doc?10116**Note: if not used must be connected ti Vin.***Note: N/C - If the output voltage is 0.9V and higher. For outputvoltage of 0.8V connect Vref to MCL4448 (Vishay RF PIN Diode).BOTTOM SIDEPIN CONFIGURATION*PIN CONNECTION1, 2SD3, 7SYNC**4, 8Vref***5, 9Vin6, 10PWM/PSM11, 12N/C13, 17GND14, 18Vout15, 19N/C16, 20GNDPin Configuration for Vo = 0.8V Pin Configuration for Vo = 0.9V - 4.5VRECOMMENDED PAD PATTERN in inches [millimeters]A D F0.1 ± 0.01[2.54 ± 0.25]0.03 ± 0.001[0.8 ± 0.02]0.02 ± 0.001[0.5 ± 0.02]TAPE AND REELSee Tape and Reel Information - T ype BVishay*Note: W D = Power DissipatedSTANDARD ELECTRICAL SPECIFICATIONSPARAMETER UNITCONDITIONMINTYPMAX InputVoltage Range V DC2.56Quiescent Current µAPSM mode 200Soft Start Time ms T SS for Vout = 3.3V 4T SS for Vout = 1.2V 2.6SD, PWM/PSM,SYNC Logic High V V H 2.4Logic Low VV L 0.8Normal Mode µA I DD 750PSM ModeµA I DD 250Shutdown Mode µAI DD1Shutdown Time ms T SS for Vout = 3.3V 4T SS for Vout = 1.2V 0.6Insulation T est Voltage V AC 60Hz 60sec 750ResistanceΩV ISO = 500 V DC 1 x 1011Leakage Current nA V ISO = 500 V DC5Output Power W 10VoltageV DC 0.8 to 4.5Voltage T olerance%For Vout = 0.9V and above (using external diode BAR065V forVout = 0.9V up to 1.3V) at 25°C Ambient T emp.- 3+3%For Vout = 0.8V up to 1.3V using external diode MCL4448 at25°C Ambient T emp.- 5+5T emp. Coefficient %/°C 0.15Ripple and Noise mVpp DC to 20 MHz80GeneralPackage Weight gr. 1.4Oscillator Frequency KHz 400SYNC Range F SYNC /F OSC1.2 1.5Temperature Operation °C - 40+ 85Storage °C - 55+ 125Operating Junction T emp.°C T j 150Thermal Impedance °C/W D *θJA82Rise Time Rise Time (PWM mode): Vin = 6V; Vout = 3.3V; lout = 3A Fall TimeFall Time (PWM mode): Vin = 6V; Vout = 3.3V; lout = 3AVishayPWM MODEVout Vs. lout*Vin = 4.0VVout Vs. Vin*Δ Temp Vs. lout*Above 25°C Ambient Temperature Vin = 6.0V; Vout = 3.3VEfficiency Vs. Lout*Vout = 3.3AVout Vs. lout*Vin = 4.0VVout Vs. Vin*Vin = 6VΔ Temp Vs. lout*Above 25°C Ambient Temperature Vin = 6.0V; Vout = 1.2VEfficiency Vs. lout*Vin = 4.0V; Vout = 1.2V* Note: Measurements were taken with Power supply: ZUP 20-40 from Nemic Lambda; Electronic load: 6063B from Agilent; Multimeter Fluke 45VishayVout Vs. lout* Vin = 4.0V Vout Vs. Vin*Vin = 6VEfficiency Vs. lout*Vin = 4.0V; Vout = 3.3VVout Vs. lout*Vin = 4.0VVout Vs. Vin*Efficiency Vs. lout*Vin = 4.0V; Vout = 1.2VPSM MODE* Note: Measurements were taken with Power supply: ZUP 20-40 from Nemic Lambda; Electronic load: 6063B from Agilent; Multimeter Fluke 45。