第五章组合逻辑电路典型例题分析

组合逻辑电路分析

5.1组合逻辑电路的分析 5.2组合逻辑电路的设计

序 关于组合逻辑电路

逻辑电路通常分为组合逻辑电路和时序逻辑电路两大类。组 合电路的定义是: 电路任一时刻的输出状态只由该时刻的输入所 决定, 而与电路的原状态无关。

组合电路就是由门电路组合而成, 电路中没有记忆单元, 一般 没有反馈通路。

1

100

1

101

1

110

1

路”。

111

0

例 2: 组合电路如图所示,分析该电路的逻辑功能。

A

& AB

B

ABAB

&

F

A

1

&

AB 1B

F ABAB ABAB AB AB

F AB AB AB AB

真值表

ABF

0 01 0 10 1 00 1 11

特点: 输入相同为“1”; 输入不同为“0”。

100

1

1

输入变量的取值中有奇数 1 0 1

1

0

个1时, L为1, 否则L为0,

110

0

0

电路具有为奇校验功能。 1 1 1

0

1

如要实现偶校验,电路应做何改变?

例 4: 分析下图的逻辑功能

. . & Y2 A A B

A B

. .

& Y1

. . A B

&

&

Y

. . Y3 B A B

(1) 写出逻辑表达式

(4) 分析逻辑功能

Y= AB +AB

=A B

逻辑式

A

=1

Y

B

逻辑符号

输入相同输出为“0”,输入相异输出为“1”,

组合逻辑电路习题解

时输出0,输入为0时输出1。 只有当所有输入都为1时, 只要有一个输入为1,输出

输出才为0。

就为0。

逻辑代数基本定律

同一律

A+0=A,A·1=A

零律

A+1=1,A·0=0

互补律

A+¬A=1,A·¬A=0

交换律

A+B=B+A,A·B=B·A

结合律

(A+B)+C=A+(B+C),(A·B)·C=A·(B·C)

ga…

gat…

实现逻辑与运算,符号为“·” 实现逻辑或运算,符号为

或“∧”,只有当所有输入 “+”或“∨”,只要有一

都为1时,输出才为1。

个输入为1,输出就为1。

实现逻辑非运算,符号为

实现逻辑与非运算,即先与 实现逻辑或非运算,即先或

“¬”或“—”,输入为1 后非,符号为“⊕”或“↑”, 后非,符号为“↓”或“⊖”,

包括真值表、逻辑表达式、 卡诺图和逻辑图四种表示方 法,它们之间可以相互转换 。

组合逻辑电的 分析与设计方法

分析方法包括根据逻辑图写 出逻辑表达式、列出真值表 、分析电路功能等步骤;设 计方法包括根据实际需求确 定输入/输出变量、列出真值 表、化简逻辑表达式、画出 逻辑图等步骤。

拓展延伸内容探讨

复杂组合逻辑电路的设计

对于较复杂的组合逻辑电路,可以采用分级设计的方法,将整体功能划分为若干个相对简 单的子功能,分别设计子电路,最后将子电路组合起来实现整体功能。

组合逻辑电路中的竞争与冒险

当多个输入信号同时变化时,可能会在输出端产生瞬间的错误信号,这种现象称为竞争; 如果这种错误信号持续时间较长,且不能被后续电路所忽略,则称为冒险。为了避免竞争 和冒险,可以采取增加冗余项、引入选通脉冲等方法。

第5章课后习题参考答案

第五章组合逻辑电路1.写出如图所示电路的输出信号逻辑表达式,并说明其功能。

(a)(b)解:(a)Y1ABC(判奇功能:1的个数为奇数时输出为1)Y2AB(AB)CABACBC(多数通过功能:输出与输入多数一致)(b)Y1(AB)A(AB)BABAB(同或功能:相同为1,否则为0)2.分析如图所示电路的逻辑功能(a)(b)(c)解:(a)Y1ABAB(判奇电路:1的个数为奇数时输出为1)0011(b)Y2(((AA)A)A)(判奇电路:1的个数为奇数时输出为1)0123YAM00(c)Y1 A M1(M=0时,源码输出;M=1时,反码输出)YAM233.用与非门设计实现下列功能的组合逻辑电路。

(1)实现4变量一致电路。

(2)四变量的多数表决电路解:(1)1)定变量列真值表:ABCDYABCDY0000110000000101001000100101000011010110010*******010*******011001110001110111112)列函数表达式:YABCDABC D ABCDABCD3)用与非门组电路(2)输入变量A、B、C、D,有3个或3个以上为1时输出为1,输人为其他状态时输出为0。

1)列真值表2)些表达式3)用与非门组电路4.有一水箱由大、小两台水泵ML和Ms供水,如图所示。

水箱中设置了3个水位检测元件A、B、C,如图(a)所示。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C点时水泵停止工作;水位低于C点而高于B点时Ms单独工作;水位低于B点而高于A点时ML单独工作;水位低于A点时ML和Ms同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

解:(1)根据要求列真值表(b)(b)(a)(2)真值表中×对应的输入项为约束项,利用卡诺图化简(c)(d)(c)(d)(e)得:MABCsMBL(ML、M S的1状态表示工作,0状态表示停止)(3)画逻辑图(e)5.某医院有—、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

组合逻辑电路习题(附答案)

例1 指出下图1所示电路的输出逻辑电平是高电平、低电平还是高阻态。

已知图(a)中的门电路都是74系列的TTL门电路,图(b)中的门电路为CC4000系列的CMOS门电路。

图1解: TTL门电路的输入端悬空时,相当于高电平输入,输入端接有电阻时,其电阻阻值大于1.4K时,该端也相当于高电平,电阻值小于0.8K时,该端才是低电平。

而CMOS逻辑门电路,输入端不管是接大电阻还是接小电阻,该端都相当于低电平(即地电位)。

所以有如下结论:(a) 1L为低电平状态;2L是低电平状态;3L是高电平状态;4L 输出为高阻状态;(b) 1L输出为高电平;2L输出是低电平状态;3L输出是低电平状态;例2 图例2所示为用三态门传输数据的示意图,图中n 个三态门连到总线BUS ,其中D 1、D 2、…、D n 为数据输入端,EN 1、EN 2、…、ENn 为三态门使能控制端,试说明电路能传输数据的原理。

图例2 解:由三态门电路符号可知,当使能端低电平时,三态门输出为高阻阻态,所以,只要给各三态门的使能端n EN EN EN ,,,21 依次为高电平时,则,1n D D 的数据就依次被传输到总线上去。

例3 某功能的逻辑函数表达式为L=∑m(1,3,4,7,12,14,15);(1)试用最少量的“与-非”门实现该函数;(2)试用最少量的“或-非”门实现该函数;解: (1)设变量为A 、B 、C 、D ,用卡诺图化简,结合“1”方格得:DBACDAABCDCBDBACDAABCDCBDCBAfL=+++==),,,((2)卡诺图中结合“0”方格,求最简的“或—与”表达式,得:DCADCBDBBADCADCBDBBAL+++++++++=++++++=))()()((例4 试用一片八选一数据选择器74LS151实现逻辑函数。

(1) ACD D ABC CD B A D C B A Z ++=),,,( (2) C B A C B A C B A C B A Z ++=),,(解:解例基本思路:选定多路选择器的地址输入变量,列出卡诺图,求出数据输入端的函数关系式;(1) 选定四变量函数中的ABC(A 2A 1A 0)为地址输入,卡诺图为画出的电路图为:(2) 选定多路选择器的地址变量为)(012A A A ABC ,由于地址数正好是变量数,所以数据输入端的逻辑关系一定是常量“0”和“1”。

(完整版)第五章组合逻辑电路典型例题分析

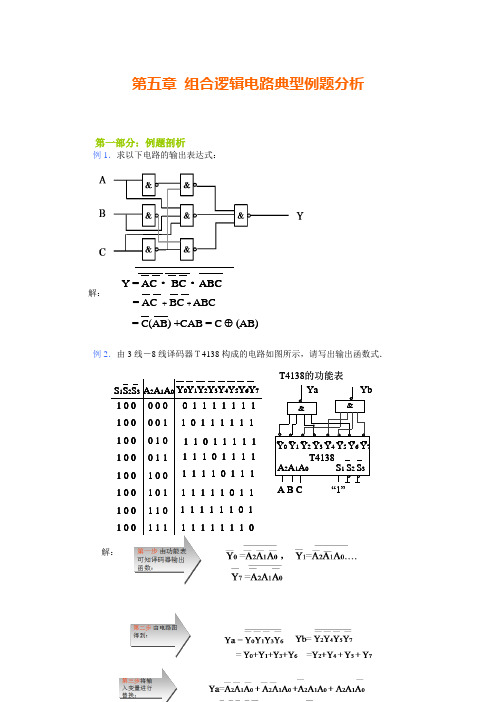

第五章 组合逻辑电路典型例题分析第一部分:例题剖析例1.求以下电路的输出表达式:解:例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式.解:Y = AC BC ABC= AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表&&Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7“1”T4138A B CA 2A 1A 0YaYbS 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0例3.分析如图电路,写出输出函数Z的表达式。

CC4512为八选一数据选择器。

解:例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。

(表中未出现的输入变量状态组合可作为约束项)CC4512的功能表A ⨯DIS INH 2A 1A 0Y1 ⨯0 10 00 00 00 00 00 00 00 0⨯⨯⨯⨯⨯0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1高阻态 0D 0D 1D 2D 3D 4D 5D 6D 7ZCC4512A 0A 1A 2D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7DIS INHD1DA B C D Y 0 0 0 0 10 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 ××××10 0 1 ××AB第一步画卡诺图第三步画逻辑电路图例5.写出下面组合电路的输出表达式,分析逻辑功能。

组合逻辑电路习题解答

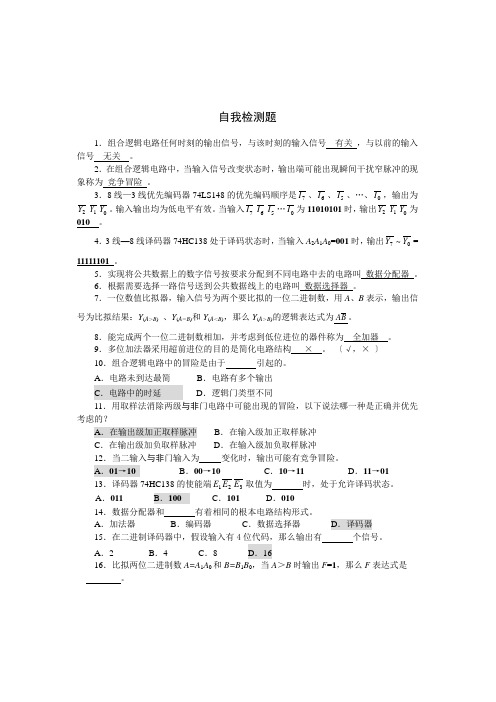

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为11010101时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 11111101 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比拟器,输入信号为两个要比拟的一位二进制数,用A 、B 表示,输出信号为比拟结果:Y (A >B ) 、Y (A =B )和Y (A <B ),那么Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

〔√,× 〕 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未到达最简 B .电路有多个输出C .电路中的时延D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→0113.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .01014.数据分配器和 有着相同的根本电路结构形式。

(完整版)组合逻辑电路习题及答案.

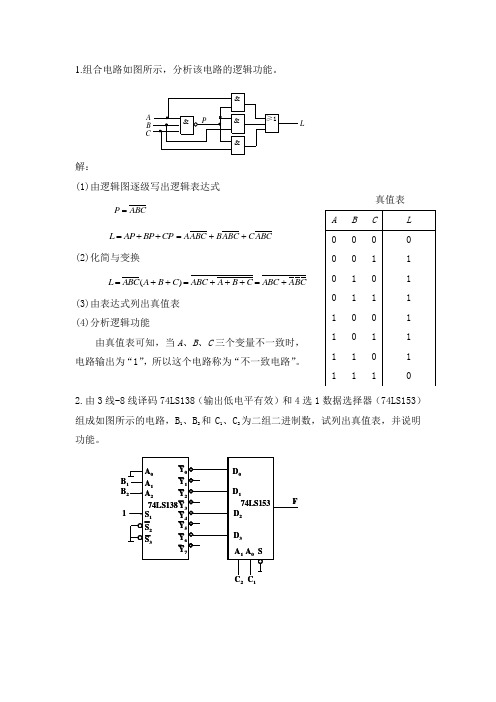

1.组合电路如图所示,分析该电路的逻辑功能。

解:(1)由逻辑图逐级写出逻辑表达式ABC P =CP BP AP L ++=ABC C ABC B ABC A ++= (2)化简与变换CB A ABC C B A ABC C B A ABC L +=+++=++=)((3)由表达式列出真值表(4)分析逻辑功能由真值表可知,当A 、B 、C 三个变量不一致时,电路输出为“1”,所以这个电路称为“不一致电路”。

2.由3线-8线译码74LS138(输出低电平有效)和4选1数据选择器(74LS153)组成如图所示的电路,B 1、B 2和C 1、C 2为二组二进制数,试列出真值表,并说明功能。

真值表A B CL解: 输出表达式: 212101122321F D C C D C C D C C D C C =+++021*********Y C C Y C C Y C C Y C C =⋅+⋅+⋅+⋅21021210212102121021A A A C C A A A C C A A A C C A A A C C =⋅+⋅+⋅+⋅2121212121212121B BC C B B C C B B C C B B C C =⋅+⋅+⋅+⋅功能说明:由地址码C 2C 1选择B 2B 1的最小项的反变量输出3.设计一个监视交通信号灯工作状态的逻辑电路。

正常情况下,红、黄、绿灯只有一个亮,否则视为故障状态,发出报警信号,提醒有关人员修理。

要求:(1)用门电路实现(2)用3-8线译码器实现(3)用4选1数据选择器实现。

解:(1)用门电路实现真值表B 2C 1C 0 00 11 01 1F21B B 21B B 21B 21B B①逻辑抽象输入变量:R 、A 、G ,红、黄、绿灯;灯亮为1,不亮为0。

输出变量:Z--故障信号,正常工作Z 为0,发生故障Z 为1。

列出真值表②写出函数式并化简 Z R A G RAG RA G RAG RAG =++++ 经卡诺图化简得: Z R A G RA RG AG =+++ ③画出电路图(2)用3-8线译码器实现①标准与或式 03567 Z R A G RAG RA G RAG RAG m m m m m =++++=++++ ②化成与非-与非式 0356703567Z m m m m m m m m m m =++++=⋅⋅⋅⋅ ③设R =A 2、A =A 1、G =A 0 则03567Z Y Y Y Y Y =⋅⋅⋅⋅ ④画连线图(3)用4选1数据选择器实现①标准与或式 Z R A G RAG RA G RAG RAG =++++S =1时 4选1 010*********Y D A A D A A D A A D A A =+++ ②确定输入变量和地址码的对应关系令A =A 1,G = A 0 ( )()()1Z R A G R AG R AG AG =+++⋅ 则:0D R = 12D D R == 31D =4.分别用74LS153(4选1数据选择器)和74LS152(8选1)实现函数F=AB+BC+AC 。

组合逻辑电路习题解答

习题写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能分析图所示电路,写出输出函数F 。

习题图 解:[]B A B BB A F ⊕=⊕⊕⊕=)(已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题图解:(1)ABD BC CD ABD BC CD L ++=••= (2)A C & && & L B A =1 =1 =1FF A B ? ?? ? ? F B A(3)根据真值表可知,四个人当中C 的权利最大。

分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)(3)当S 1S 0=00和S 1S 0=11S 1S 0=01时,该电路实现两输入或非门,当S 1S 0=10时,该电路实现两输入与非门。

(2)A 10电路逻辑功能为:“判输入ABC 是否相同”电路。

已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题图 解:(1)根据波形图得到真值表:C AB BC A C B A F ++=、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

组合逻辑电路分析

A B C(1) 写出Y 的最简与或式; (2) 列出电路的真值表; (3) 说明电路的逻辑功能;2.设计一个三输入端组合逻辑电路,当三个输入端信号电平相同时,输出为1,否则输出为0. 2005年(1)列出真值表。

(2)求出与或表达式并变换为与非—与非式。

(3)画出用与非门组成的逻辑图(输入端可直接使用后变量)。

1.逻辑函数Y 的真质表如下表所示,2006年(1)求出Y 的与或表达式(2)求出Y 的最简与非—与非表达式 (3)画出用与非门实现函数Y 的逻辑图。

(1)写出Y1、Y2、Y3的表达式; (2)写出Y 的最简与或门; (3)画出化简后的逻辑电路图。

A B C图3.31、组合逻辑电路的输入A 、B 、C 和输出F 的波形如图所示。

2008年 (1)列出真值表;(2)写出逻辑函数表达式并化简; (3)用最少的与非门实现。

1、只有一辆自行车,要求只有在A 同意的情况下,B 和C 才可以骑,但B 具有优先权,B 不骑时C 才可以骑。

(1)列出真值表。

(2)写出最简逻辑表达式,(3)试用与非门设计电路,画出逻辑电路图。

2009年三、简答题1. (8-5中)设一位二进制半加器的被加数为A ,加数为B ,本位之和为S ,向高位进位为C ,试根据真值表 1).写出逻辑表达式 2).画出其逻辑图。

真值表:2.(8-5难)设一位二进制全加器的被加数为A i,加数为B i,本位之和为S i,向高位进位为C i,来自低位的进位为C i-1,根据真值表1).写出逻辑表达式2).画出其逻辑图。

真值表:3.(8-1难)分析图示逻辑电路:1).列真值表2).写出逻辑表达式3).说明其逻辑功能。

=++,根据给出的4.(8-3难*)用一个74LS138译码器实现逻辑函数Y ABC ABC ABC部分逻辑图完成逻辑图的连接。

5.(8-1中)简单回答组合逻辑电路的设计步骤。

6.(8-1难)试用2输入与非门和反向器设计一个3输入(I0、I1、I2)、3输出(L0、L1、L2)的信号排队电路。

组合逻辑电路习题解答

(有些题答案错了)自我检测题1.组合逻辑电路任何时刻(de)输出信号,与该时刻(de)输入信号 有关 ,与以前(de)输入信号 无关 .2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲(de)现象称为 竞争冒险 .3.8线—3线优先编码器74LS148(de)优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y .输入输出均为低电平有效.当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 .4.3线—8线译码器74HC 处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = .5.实现将公共数据上(de)数字信号按要求分配到不同电路中去(de)电路叫 数据分配器 .6.根据需要选择一路信号送到公共数据线上(de)电路叫 数据选择器 .7.一位数值比较器,输入信号为两个要比较(de)一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )(de)逻辑表达式为B A .8.能完成两个一位二进制数相加,并考虑到低位进位(de)器件称为 全加器 .9.多位加法器采用超前进位(de)目(de)是简化电路结构 . (√, )10.组合逻辑电路中(de)冒险是由于 引起(de). A .电路未达到最简 B .电路有多个输出 C .电路中(de)时延 D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现(de)冒险,以下说法哪一种是正确并优先考虑(de)A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲 12.当二输入与非门输入为 变化时,输出可能有竞争冒险. A .01→10 B .00→10 C .10→11 D .11→0113.译码器74HC(de)使能端321E E E 取值为 时,处于允许译码状态.A .011B .100C .101D .01014.数据分配器和 有着相同(de)基本电路结构形式.A .加法器B .编码器C .数据选择器D .译码器15.在二进制译码器中,若输入有4位代码,则输出有 个信号. A .2 B .4 C .8 D .1616.比较两位二进制数A=A 1A 0和B=B 1B 0,当A >B 时输出F =1,则F 表达式是.A .B A F =.0101B B A A F ++= .0011B A B A F ++=17.集成4位数值比较器74LS85级联输入I A <B 、I A=B 、I A >B 分别接001,当输入二个相等(de)4位数据时,输出F A <B 、F A=B 、F A >B 分别为 . A .010 B .001 C .100 D .01118.实现两个四位二进制数相乘(de)组合电路,应有 个输出函数.A . 8B .9C .10D .11 19.设计一个四位二进制码(de)奇偶位发生器(假定采用偶检验码),需要 个异或门.A .2B .3C .4D .520.在图中,能实现函数C B B A F +=(de)电路为 .A B FCB AC F(a ) (b ) (c )图A .电路 (a )B .电路(b )C .电路(c )D .都不是习 题1.分析图所示组合逻辑电路(de)功能,要求写出与-或逻辑表达式,列出其真值表,并说明电路(de)逻辑功能.A B CS图解: CO =AB +BC +ACAC BC AB C B A ABC CO C B A ABC S +++++=+++=)()(AC BC AB C B A ABC )(+++=AC BC AB C AC BC AB B AC BC AB A ABC +++= A B AB C AC C A B C BC B A ABC +++= C B A C B A C B A ABC +++=真值表电路功能:一位全加器,A 、B 为两个加数,C 为来自低位(de)进位(似乎错了),S 是相加(de)和,CO 是进位.2.已知逻辑电路如图所示,试分析其逻辑功能.A B C图解:(1)逻辑表达式 ABC P =1,ABC B BP P ==12,ABC A AP P ==13,ABC C CP P ==14432P P P F =ABC C ABC A ABC B =ABC C ABC A ABC B ++=)(C B A ABC ++= ))((C B A C B A ++++=C AB C B A C B A BC A C B A C B A +++++=(2(3)功能从真值表看出,ABC=000或ABC=111时,F=0,而A、B、C取值不完全相同时,F=1.故这种电路称为“不一致”电路.3.试用与非门设计一组合逻辑电路,其输入为3位二进制数,当输入中有奇数个1时输出为1,否则输出为0.解:(1)真值表(2)ABCAF⋅⋅BAC+B=(无法用卡诺图化简)++=⋅ABCCBABCACBACCAB(3)逻辑图F4.4位无符号二进制数A( A3A2A1A0),请设计一个组合逻辑电路实现:当0≤A<8或12≤A<15时,F输出1,否则,F输出0.解:(1)真值表:(2)表达式(3)电路图1111111111100001101110110100A 3A 2A 1A0F 0A 3A 1A 2A 0F02123A A A A A F ++=(4)如果要求用与非门实现,则:01230123012302123A A A A A A A AA A A A A A A A A F =+=+=++=逻辑图:A A A A5.约翰和简妮夫妇有两个孩子乔和苏,全家外出吃饭一般要么去汉堡店,要么去炸鸡店.每次出去吃饭前,全家要表决以决定去哪家餐厅.表决(de)规则是如果约翰和简妮都同意,或多数同意吃炸鸡,则他们去炸鸡店,否则就去汉堡店.试设计一组合逻辑电路实现上述表决电路.解:(1)逻辑定义:A 、B 、C 、D 分别代表约翰、简妮、乔和苏.F =1表示去炸鸡店,F =0表示去汉堡店.(2)真值表(3)用卡诺图化简 (4)逻辑图AB 00CD01111000011110F0000001011111B CA FDF =AB +ACD +BCD6.试设计一个全减器组合逻辑电路.全减器是可以计算三个数、Y 、BI (de)差,即D =-Y -CI .当<Y +BI 时,借位输出BO 置位.解:设被减数为,减数为Y ,从低位来(de)借位为BI ,则1位全减器(de)真值表如图 (a)所示,其中D 为全减差,BO 为向高位发出(de)借位输出.(1)真值表0101110100011110X Y BID 0111010100011110XY BIBO由卡诺图得I B Y X D ⊕⊕=Y X B X YB B I I O ++=电路图Y XDBOBI7.设计组合逻辑电路,将4位无符号二进制数转换成格雷码.解:(1)列出4位二进制码→4位格雷码(de)转换真值表,如表所示.(2)根据真值表分别画出输出变量G 3,G 2,G 1,G 0(de)卡诺图,如图所示.化简后,得33B G =,232B B G ⊕=,121B B G ⊕=,010B B G ⊕=00001111000011110001101100011011B 3B 2B 1B 0G 20011110011000110001101100011011B 3B 2B 1B 0G 10101010101010110001101100011011B 3B 2B 1B 0G 0(3)由逻辑表达式得电路实现,如图所示.B 3B 2B 0B 0G 3G 2G 0G 08.请用最少器件设计一个健身房照明灯(de)控制电路,该健身房有东门、南门、西门,在各个门旁装有一个开关,每个开关都能独立控制灯(de)亮暗,控制电路具有以下功能:(1)某一门开关接通,灯即亮,开关断,灯暗;(2)当某一门开关接通,灯亮,接着接通另一门开关,则灯暗; (3)当三个门开关都接通时,灯亮.解:设东门开关为A ,南门开关为B ,西门开关为C .开关闭合为1,开关断开为0.灯为Z ,等暗为0,灯亮为1.根据题意列真值表如下:(2)画出卡诺图如图所示.010111100011110ABC Z=1=1A ZB C(3)根据卡诺图,可得到该逻辑电路(de)函数表达式:C B A ABC C B A C B A C B A Z ⊕⊕=+++=(3)根据逻辑函数表达式,可画出逻辑电路图如图所示.9.设计一个能被2或3整除(de)逻辑电路,其中被除数A 、B 、C 、D 是8421BCD 编码.规定能整除时,输出L 为高电平,否则,输出L 为低电平.要求用最少(de)与非门实现.(设0能被任何数整除)解:(1)真值表(2)用卡诺图化简101111××××11××0001111000011110AB CDL B DC A LD C B A D C B A D C B A L =++=++=(3)逻辑图10.如图所示为一工业用水容器示意图,图中虚线表示水位,A 、B 、C 电极被水浸没时会有高电平信号输出,试用与非门构成(de)电路来实现下述控制作用:水面在A 、B 间,为正常状态,亮绿灯G ;水面在B 、C 间或在A 以上为异常状态,点亮黄灯Y ;面在C 以下为危险状态,点亮红灯R .要求写出设计过程.A B C图解:(1)真值表(2)卡诺图化简A0BC100011110Y 010××××A0BC100011110G 001××××BA B A G ==1A CB AC B Y ⋅=+=A 0BC100011110R 100×××0×GCR =YR(3)逻辑图11.试用卡诺图法判断逻辑函数式Y (A ,B ,C ,D )=∑m (0,1,4,5,12,13,14,15)是否存在逻辑险象,若有,则采用增加冗余项(de)方法消除,并用与非门构成相应(de)电路.解:卡诺图如图(a )所示. 最简逻辑函数式为:AB C A Y +=此函数存在逻辑险象.只要如图所示增加冗余项C B 即可,逻辑式变为:C B AB C A C B AB C A Y ⋅⋅=++=用与非门构成(de)相应电路如图 (b)所示.AL 2C100011110AB CD00011110100110011110Y B(a ) (b )12.已知∑∑+=)14,2,1()13,12,11,10,9,8,7,3,0(),,,(d m D C B A Y ,求Y (de)无竞争冒险(de)最简与-或式.解:卡诺图如图所示:1×1000101110001111000011110AB CDY×11×0C B A CD A D B C A Y +++=上式中C B A 为冗余项,以消除竞争冒险.13.某一组合电路如图所示,输入变量(A ,B ,D )(de)取值不可能发生(0,1,0)(de)输入组合.分析它(de)竞争冒险现象,如存在,则用最简单(de)电路改动来消除之.F图解:解法1:从逻辑图得到以下表达式:AC D C B C B A F ++=根据表达式得到卡诺图:1100100010110110001111000011110AB CD F但由于从卡诺图可见,包围圈有两处相切,因此存在竞争冒险现象.可以通过相切点位置增加一个乘积项,得D AB D C A AC D C B C B A F ++++=进一步分析,当ACD =000时, B B F +=,由于输入变量(A ,B ,D )(de)取值不可能发生(0,1,0)(de)输入组合,因此,当ACD =000时,B 必然为0,不会产生竞争冒险.因此,D C A 这一项不需要增加,只需要增加D AB .电路图为:F解法二:如果逻辑表达式在某种取值下,出现A A F +=、B B F +=、C C F +=、D D F +=,就有可能出现竞争冒险.根据逻辑表达式AC D C B C B A F ++=,A A F +=和D D F +=不会出现. 当A =C =D =0,出现B B F +=,但由于输入变量(A ,B ,D )(de)取值不可能发生(0,1,0)(de)输入组合,因此,当ACD =000时,B 必然为0,因此也不会产生竞争冒险.只有当A =B =1,D =0,出现C C F +=,存在竞争冒险问题,加冗余项D AB 可消除竞争冒险.14.电路如图所示,图中①~⑤均为2线—4线译码器.(1)欲分别使译码器①~④处于工作状态,对应(de)C 、D 应输入何种状态(填表);(2)试分析当译码器①工作时,请对应A 、B (de)状态写出1310Y ~Y (de)状态(填表);(3)说明图(de)逻辑功能. 表 表13Y 12Y 11Y 10Y 23Y 22Y 21Y 20Y 33Y 32Y 31Y 30Y 43Y 42Y 41Y 40Y图解:逻辑功能:由74LS 构成(de)4线—16线译码器15.图所示电路是由3线-8线译码器74HC 及门电路构成(de)地址译码电路.试列出此译码电路每个输出对应(de)地址,要求输入地址A 7A 6A 5A 4A 3A 2A 1A 0用十六进制表示.A 3A 4A 5A 6A 7图解:由图可见,74HC(de)功能扩展输入端必须满足E 1=1、032==E E 才能正常译码,因此E 1=A 3=1;542A A E =,即A 4=1,A 5=1; 0763=+=A A E ,即A 6=0,A 7=0.所以,该地址译码器(de)译码地址范围为A 7A 6A 5A 4A 3A 2A 1A 0=00111A 2A 1A 0=00111000~00111111,用十六进制表示即为38H ~3FH.输入、输出真值表如表1所示.表1 地址译码器(de)真值表16.写出图所示电路(de)逻辑函数,并化简为最简与-或表达式.10B AC L图解:由图(a )写出逻辑函数并化简,得CC AB C B A C B A C B A Y Y Y Y Y Y Y Y L =+++=+++==6420642017.试用一片3线-8线译码器74HC 和最少(de)门电路设计一个奇偶校验器,要求当输入变量ABCD 中有偶数个1时输出为1,否则为0.(ABCD 为0000时视作偶数个1).解:ABCD D C AB D C B A D C B A D BC A D C B A CD B A D C B A F +++++++=ABCD D C B A D C B A CD B A D C AB D C B A D BC A D C B A ++++++++=D ABC C B A C B A C B A D C AB C B A BC A C B A )()(+++++++=D C AB C B A BC A C B A D C AB C B A BC A C B A )()(+++++++=D C AB C B A BC A C B A ⊕+++=)(D C AB C B A BC A C B A ⊕⋅⋅⋅=)(连接图AB C 100F18.用一个8线-3线优先编码器74HC148和一个3线-8线译码器74HC 实现3位格雷码→3位二进制(de)转换.解:根据下表可得到连线图:B 1B 0B 2G G G19.根据图所示4选1数据选择器,写出输出Z(de)最简与-或表达式.解:C A C A B CAB B A BC A B A Z ++=+++=20.由4选1数据选择器和门电路构成(de)组合逻辑电路如图所示,试写出输出E (de)最简逻辑函数表达式.解:D C C A D ABC D C B A CD B A CD B A E +=+++=图 图21.由4选1数据选择器构成(de)组合逻辑电路如图所示,请画出在图所示输入信号作用下,L (de)输出波形.A B C L图解:4选1数据选择器(de)逻辑表达式为:301201101001D A A D A A D A A D A A Y +++=将A 1=A ,A 0=B ,D 0=1,D 1=C ,C D =2,D 3=C 代入得ABC C B A BC A C B A C B A ABC C B A BC A B A Y ++++=+++=根据表达式可画出波形图:CA B L22.已知用8选1数据选择器74LS151构成(de)逻辑电路如图所示,请写出输出L (de)逻辑函数表达式,并将它化成最简与-或表达式.图解:(1)写出逻辑函数表达式:C AB C B A BC A C B A C B A L ++++=(2)用卡诺图化简1111010010110101L BCAB AC L +=23.用一个8选1数据选择器74LS151和非门实现:))()()((F B C A D A C B BF C A C B A E Y +++++++++=解:)(F B C A D A BC BF C A C B A E Y +++=)(F m F m m D m D m m F m F m m m E 2027376441+++++++++=)(7643210m F m m D m m m F m E ++++++=CBAE124.图所示是用二个4选1数据选择器组成(de)逻辑电路,试写出输出Z与输入M、N、P、Q之间(de)逻辑函数式.PN图解;P)(Z)(+=NMQ++NQNMQMNMQPPNNMQ+=M++MQPQPQMNNPNQ+=NQPP25.用二个4选1数据选择器实现函数L,允许使用反相器.BACDEEL+A+++=+AEBDEFBCEDCCDEABB解:BCEAEBCDL++=+++EBEDAADEFCBBCDEA+B+B+E+(=)++ECBDADFBECDACAAECDB++BEE(=)A++++AADFBEBECCDCADDC电路图26.一个组合逻辑电路有两个控制信号C1和C2,要求:(1)C2C1=00时,B=AF⊕(2)C2C1=01时,ABF=(3)C2C1=10时,B=F+A(4)C2C1=11时,ABF=试设计符合上述要求(de)逻辑电路(器件不限)解:方法一:真值表→卡诺图化简→逻辑图真值表卡诺图化简000011110C 2C 1AB00011110101110100101FAB C C B A C C B A C B A C A C C F 12122212++++=逻辑图F方法二:利用数据选择器和少量门电路实现27.试用4选1数据选择器74LS153(1/2)和最少量(de)与非门实现逻辑函数DCBDCCAF++=.解:DCBDCDDCADCBDCCAF+++=++=)(0⋅+++=+++=CDDCDCADCABDCBDCDCADCA令A1=C,A0=D,ABD=0,AD=1,D2=1,D3=0连线图:BA A28.P(P2P1P0)和Q(Q2Q1Q0)为两个三位无符号二进制数,试用一个74LS和一个74LS151和尽可能少(de)门电路设计如下组合电路:当P=Q 时输出F=1,否则F=0.解:P P P29.试用8选1数据选择器74LS151实现逻辑函数L =AB +AC .解:567m m m ABC C B A ABC C AB AC AB L ++=+++=+=130.用8选1数据选择器74LS151设计一个组合电路.该电路有3个输入A 、B 、C 和一个工作模式控制变量M ,当M =0时,电路实现“意见一致”功能(A ,B ,C 状态一致时输出为1,否则输出为0),而M =1时,电路实现“多数表决”功能,即输出与A ,B ,C 中多数(de)状态一致.解:CMAB C B MA BC A M ABC C B A M MABC C MAB C B MA BC A M ABC M C B A M F ++++=+++++=电路图M31.已知8选1数据选择器74LS151芯片(de)选择输入端A 2(de)引脚折断,无法输入信号,但芯片内部功能完好.试问如何利用它来实现函数F (A ,B ,C )=∑m (1,2,4,7).要求写出实现过程,画出逻辑图.解:对于LSTTL 集成芯片,某个输入引脚折断后该脚悬空,相当于输入高电平1.74LS151(de)高位地址端A 2折断后,输出不再响应D 0,D 1,D 2,D 3输入,8选1数据选择器只相当于一个4选1,此时地址输入为A 1A 0,数据输入为D 4,D 5,D 6,D 7,输出Y 等于7016015014017012601250124012D A A D A A D A A D A A D A A A D A A A D A A A D A A A Y +++=+++=与函数F 相比较ABCC B A C B A C B A m C B A F +++==∑)7,4,2,1(),,(不难看出,只要令AB 为地址,则D 4=C ,D 5=C ,D 6=C ,D 7=C .逻辑图如图所示.图 题(de)电路实现32.用三片四位数值比较器74LS85实现两个12位二进制数比较.解:74LS85(片0)A 3A 1A 2A 0B 3B 1B 2B 0I (A >B )I (A =B )I (A <B )Y (A >B )Y (A =B )Y (A <B )100w 2 v 2w 0w 1 v 1 v 074LS85(片1)A 3A 1A 2A 0B 3B 1B 2B 0I (A >B )I (A =B )I (A <B )Y (A >B )Y (A =B )Y (A <B )w 6W <VW >V W =V v 6w 4w 5 v 5 v 4w 7 v 7w 3 v 374LS85(片2)A 3A 1A 2A 0B 3B 1B 2B 0I (A >B )I (A =B )I (A <B )Y (A >B )Y (A =B )Y (A <B )w 10 v 10w 8w 9 v 9 v 8w 11 v 1133.用一片4位数值比较器74HC85和适量(de)门电路实现两个5位数值(de)比较.解:高4位加到比较器数值输入端,最低位产生级联输入.0V W I =)(B >A ,00V W I =)(B <A ,I (A=B )=W 0⊙V 0W <VW >V W =V W V34.用两个四位加法器74283和适量门电路设计三个4位二进制数相加电路.解:三个4位二进制数相加,其和应为6位.基本电路如图所示.两个加法器产生(de)进位通过一定(de)逻辑生成和(de)高两位.214CO CO S ⊕=, 215CO CO S ⋅=C O1C O2S 5S 4C O1∑A 3A 1A 2A 0B 3B 1B 2B 0S 3S 1S 2S 0CI 0C OX 0X 1X 2X 3Y 0Y 1Y 2Y 3C O2∑A 3A 1A 2A 0B 3B 1B 2B 0S 3S 1S 2S 0CI 0C OS 0S 1S 2S 3Z 0Z 1Z 2Z 335.A 、B 为4位无符号二进制数(B ≠0),用一个74LS283、非门和一个其它类型门电路实现:当A =(B -1)模16时,输出Y =1,否则为0. 解:∵ (B -1)模16即为B -1∴ A =B -1时Y =1,否则Y =0,即B -1-A =B +A +1-1=B +A 为0时,Y =1.A 0A 1A 2A 3Y36.A 、B 为四位二进制数,试用一片74283实现Y =4A +B . 解:Y =4A +B =A 3A 2A 1A 000+B 3B 2B 1B 0∑A 3A 1A 2A 0B 3B 1B 2B 0S 3S 1S 2S 0CI 0C OA 0A 1A 2A 3B 0B 1B 2B 3X 50X 4X 3X 2X 1X 037.用一片74283和尽量少(de)门电路设计余3码到2421码(de)转换.解:余3码到2421码(de)转换(de)真值表为:从真值表中可以看到,当A 3=0时,B =A -3,当A 3=1时,B =A +3B 0B 1B 2B 3A 313A38.设计一个一位8421BCD 码乘以5(de)电路,要求输出也为8421BCD码.要求:(1)用4线/16线译码器及门电路实现;(2)只用四位全加器74LS283实现;(3)不用任何器件实现.解:根据题意列出真值表(1)从真值表可写出逻辑表达式:B7=0,B3=0,B 1=0,B 6=∑m (8,9), B 5=∑m (4,5,6,7), B 4=∑m (2,3,6,7), B 0=B 2=∑m (1,3,5,7,9).0A 1A 2A 02(B 0)A 3456B 7B 3B 1(2)用全加器实现A 3A 2A 1A 00 1 0 10 0 A 3A 2A 1A 0A 3A 2A 1A 0×+A 1A 0用74283实现逻辑图与36题同. (3)不用任何器件实现B 7=0,B 6=A 3,B 5=A 2,B 4=A 1,B 3=0,B 2=A 0,B 1=0,B 0=A 039.利用两片并行进位加法器和必要(de)门电路设计一个8421BCD 码加法器.8421BCD 码(de)运算规则是:当两数之和小于等于9(1001)时,所得结果即为输出;当所得结果大于9时,则应加上6(0110).解:连线图如图所示.加法器1完成两个加数得初始加法,加法器2对加法器1输出进行修正.A 3A 1A 2A 0B B B B S 4S 0S 1S 2S 3。

组合逻辑电路题解

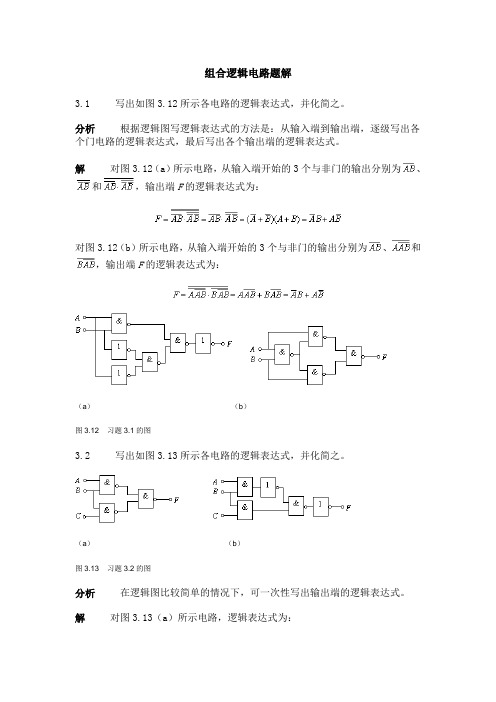

组合逻辑电路题解3.1 写出如图3.12所示各电路的逻辑表达式,并化简之。

分析根据逻辑图写逻辑表达式的方法是:从输入端到输出端,逐级写出各个门电路的逻辑表达式,最后写出各个输出端的逻辑表达式。

解对图3.12(a)所示电路,从输入端开始的3个与非门的输出分别为、和,输出端F的逻辑表达式为:对图3.12(b)所示电路,从输入端开始的3个与非门的输出分别为、和,输出端F的逻辑表达式为:(a)(b)图3.12 习题3.1的图3.2 写出如图3.13所示各电路的逻辑表达式,并化简之。

(a)(b)图3.13 习题3.2的图分析在逻辑图比较简单的情况下,可一次性写出输出端的逻辑表达式。

解对图3.13(a)所示电路,逻辑表达式为:对图3.13(b)所示电路,逻辑表达式为:3.3 证明如图3.14所示两个逻辑电路具有相同的逻辑功能。

(a)(b)图3.14 习题3.3的图分析如果两个逻辑电路的逻辑表达式或真值表完全相同,则它们具有相同的逻辑功能。

解对图3.14(a)所示电路,逻辑表达式为:对图3.14(b)所示电路,逻辑表达式为:因为两个逻辑电路的逻辑表达式完全相同,所以它们具有相同的逻辑功能。

3.4 分析如图3.15所示两个逻辑电路的逻辑功能是否相同?要求写出逻辑表达式,列出真值表。

(a)(b)图3.15 习题3.4的图解对图3.15(a)所示电路,逻辑表达式为:对图3.15(b)所示电路,逻辑表达式为:真值表如表3.12所示。

因为两个逻辑电路的逻辑表达式以及真值表完全相同,所以它们具有相同的逻辑功能。

表3.12 习题3.4的真值表A B C F1F20 0 0 0 0 1 0 1 00 1 11 0 0 1 0 1 1 1 0 1 1 1 011113.5 分析如图3.16所示两个逻辑电路,要求写出逻辑式,列出真值表,然后说明这两个电路的逻辑功能是否相同。

(a)(b)图3.16 习题3.5的图解对图3.16(a)所示电路,逻辑表达式为:对图3.16(b)所示电路,逻辑表达式为:真值表如表3.13所示。

(完整版)组合逻辑电路设计例题

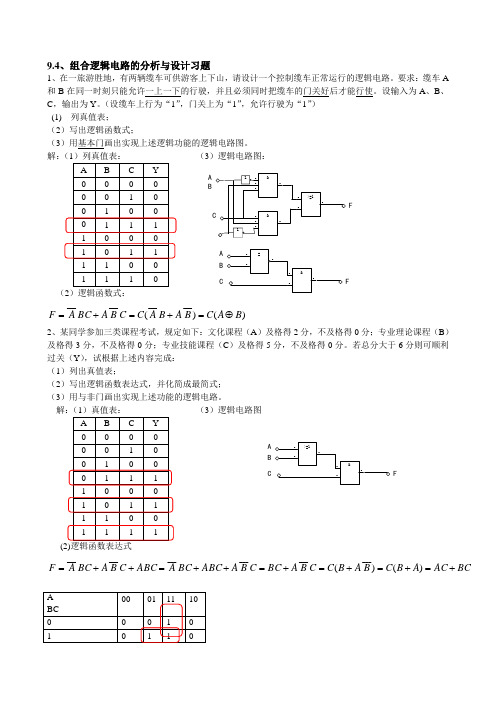

9.4、组合逻辑电路的分析与设计习题1、在一旅游胜地,有两辆缆车可供游客上下山,请设计一个控制缆车正常运行的逻辑电路。

要求:缆车A 和B在同一时刻只能允许一上一下的行驶,并且必须同时把缆车的门关好后才能行使。

设输入为A、B、C,输出为Y。

(设缆车上行为“1”,门关上为“1”,允许行驶为“1”)(1) 列真值表;(2)写出逻辑函数式;(3)用基本门画出实现上述逻辑功能的逻辑电路图。

解:(1)列真值表:(3)逻辑电路图:)()(____________BACBABACCBABCAF⊕=+=+=2、某同学参加三类课程考试,规定如下:文化课程(A)及格得2分,不及格得0分;专业理论课程(B)及格得3分,不及格得0分;专业技能课程(C)及格得5分,不及格得0分。

若总分大于6分则可顺利过关(Y),试根据上述内容完成:(1)列出真值表;(2)写出逻辑函数表达式,并化简成最简式;(3)用与非门画出实现上述功能的逻辑电路。

(3)逻辑电路图(2)逻辑函数表达式BCACABCBABCCBABCCBAABCBCAABCCBABCAF+=+=+=+=++=++=)()(__________________ABFAFBCAFBC3、中等职业学校规定机电专业的学生,至少取得钳工(A)、车工(B)、电工(C)中级技能证书的任意两种,才允许毕业(Y )。

试根据上述要求:(1)列出真值表;(2)写出逻辑表达式,并化成最简的与非—与非形式;(3)用与非门画出完成上述功能的逻辑电路。

解:(1(3)逻辑电路:(2)逻辑表达式:最简的与非—与非形式:ABC C AB C B A BC A F +++=_____________________________________________________________________________________________________________AB BC AC AB BC AC AB BC AC AB BC AC F ••=•+=++=++=4、用基本逻辑门电路设计一个一位二进制全加器,输入变量有:A 为被加数,B 为加数,C 为较低位的进位,输出函数为本位和S 及向较高位的进位H 。

组合逻辑电路例题

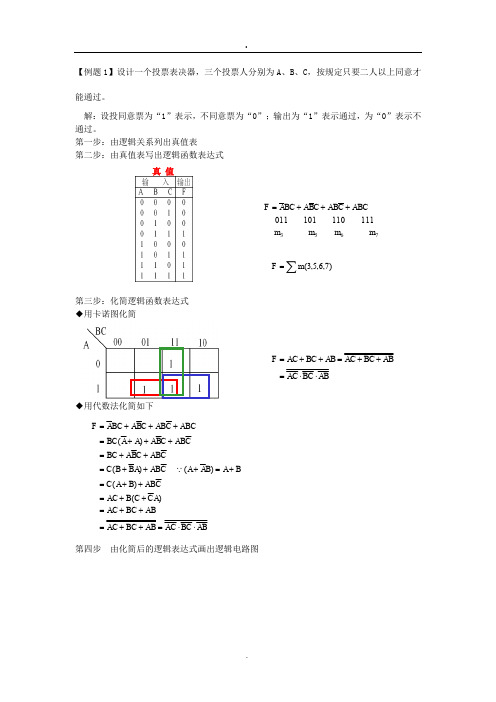

【例题1】设计一个投票表决器,三个投票人分别为A 、B 、C ,按规定只要二人以上同意才能通过。

解:设投同意票为“1”表示,不同意票为“0”;输出为“1”表示通过,为“0”表示不通过。

第一步:由逻辑关系列出真值表第二步:由真值表写出逻辑函数表达式第三步:化简逻辑函数表达式 ◆用卡诺图化简◆用代数法化简如下第四步 由化简后的逻辑表达式画出逻辑电路图7653111*********m m m m ABC C AB C B A BC A F +++=真值表∑=)7,6,5,3(mFABBC AC AB BC AC AB BC AC F ⋅⋅=++=++=AB BC AC AB BC AC AB BC AC A C C B AC C AB B A C B A B A A C AB A B B C C AB C B A BC C AB C B A A A BC ABC C AB C B A BC A F ⋅⋅=++=++=++=++=+=+++=++=+++=+++=)()()()()( F 高电平时,三极管导通,灯亮;低电平时三极管截止,灯灭。

【例题2】某汽车驾驶员培训班进行结业考试。

有三名评判员,其中A 为主评判员,B 、C 为副评判员。

评判时按少数服从多数原则,但若主评判认为合格,也可通过。

试用与非门构成逻辑电路实现评判的规定。

解:(1)根据逻辑设计要求,设定三个输入变量A 、B 、C ,并规定如下: 主评判A 意见:A =1 认为合格;A =0 认为不合格 副评判B 意见:B =1 认为合格;B =0 认为不合格副评判C 意见:C =1 认为合格;C =0 认为不合格 设输出变量Y :Y =1 认为通过;Y =0 认为不通过 (2)列真值表(3)根据真值表写出逻辑表达式(4)用卡诺图化简(5)画出逻辑电路图真值表∑=++++=++++=)7,6,5,4,3(76543m m m m m m ABC C AB C B A C B A BC AY ABC A BC A BC Y ⋅=+=+=【例题3】有一火灾报警系统,设有烟感、温感、紫外光感三种不同类型的火灾探测器。

(电子技术对口升学考试)组合逻辑电路的分析习题与解答

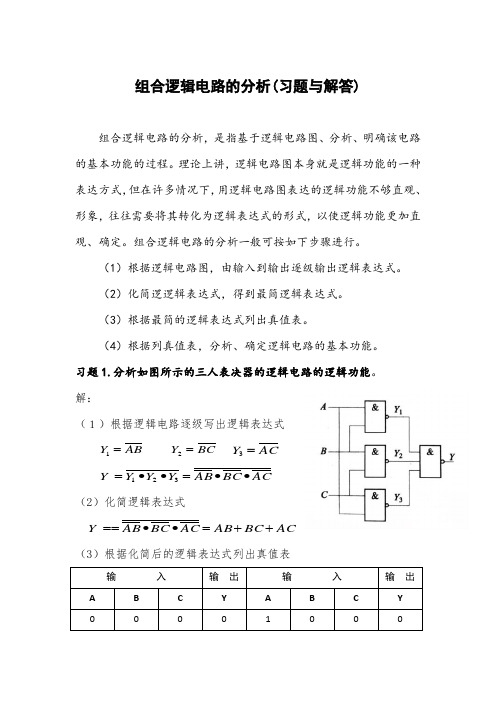

组合逻辑电路的分析(习题与解答)组合逻辑电路的分析,是指基于逻辑电路图、分析、明确该电路的基本功能的过程。

理论上讲,逻辑电路图本身就是逻辑功能的一种表达方式,但在许多情况下,用逻辑电路图表达的逻辑功能不够直观、形象,往往需要将其转化为逻辑表达式的形式,以使逻辑功能更加直观、确定。

组合逻辑电路的分析一般可按如下步骤进行。

(1)根据逻辑电路图,由输入到输出逐级输出逻辑表达式。

(2)化简逻逻辑表达式,得到最简逻辑表达式。

(3)根据最简的逻辑表达式列出真值表。

(4)根据列真值表,分析、确定逻辑电路的基本功能。

习题1.分析如图所示的三人表决器的逻辑电路的逻辑功能。

解:(1)根据逻辑电路逐级写出逻辑表达式AB Y=1BCY=2ACY=3ACBCABYYYY••=••=321(2)化简逻辑表达式ACBCABACBCABY++=••==(3)根据化简后的逻辑表达式列出真值表输入输出输入输出A B C Y A B C Y0 0 0 0 1 0 0 00 0 1 0 1 0 1 10 1 0 0 1 1 0 10 1 1 1 1 1 1 1 (4)由真值表可知,3个输入中至少有两个或两个以上的输入为1时,输出才为1,否则输出为0。

此电路为一个少数服从多数的三人表决器。

习题2.分析如图所示的逻辑电路的逻辑功能。

解:(1)根据逻辑电路逐级写出逻辑表达AB Y=1ABAY•=2ABBY•=3ABBABAYYY•••=•=32(2)化简逻辑表达式ABBABAYYY•••=•=32ABBABA•+•=BABA+=(3)根据化简后的逻辑表达式列出真值表输入输出A B Y0 0 00 1 11 0 11 1 0(4)由真值表可知,可知逻辑电路的功能:输入一致时,输出为0,输入不一致时,输出为1。

此电路的逻辑功能为同出0,异出1。

习题3.分析如图所示的逻辑电路的逻辑功能。

解:(1)根据逻辑电路逐级写出逻辑表达式BA Y=1ABY=2ABBAYYY+=+=21(2)化简逻辑表达式ABBAY+=此函数表达式已为最简与或表达式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五章 组合逻辑电路典型例题分析

第一部分:例题剖析

例1.求以下电路的输出表达式:

解:

例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式.

解:

Y = AC BC ABC = AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表

&

&

Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7

“1”

T4138

A B C

A 2A 1A 0Ya

Yb

S 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1

S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0

A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0

例3.分析如图电路,写出输出函数Z的表达式。

CC4512为八选一数据选择器。

解:

例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。

(表中未出现的输入变量状态组合可作为约束项)

CC4512的功能表

A ⨯

DIS INH 2A 1A 0Y

1 ⨯0 1

0 0

0 00 00 00 0

0 0

0 00 0

⨯⨯⨯⨯⨯0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1

高阻态

0D 0D 1D 2D 3D 4D 5D 6D 7

Z

CC4512

A 0A 1A 2

D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7

DIS INH

D

1

D

A B C D Y 0 0 0 0 1

0 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0

CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 ×

×

×

×10 0 1 ×

×

A

B

第一步画卡诺图第三步画逻辑电路图

例5.

写出下面组合电路的输出表达式,分析逻辑功能。

解:第一步写出表达式,进行化简。

第二步说明功能: 此电路为三变量中,取值为奇数个一时,Y输出为1,或者判奇数电路。

例6:四选一数据选择器框图如下图所示。

已知

用它实现函数:

(1)写出F的最小项表达式;

(2)在图上括号中把满足输出函数F的信号A、B、C及常量1、0填在括号中。

解:本题不难分析可得出如下结论:

若A=A1,B=A0,则D0=1,D1=1,D2=0,D3=C

&Y

A

B

C

&

&

&

&

&

&

Y = AB A ·AB B ·C ·AB A ·AB B ·AB A ·AB B ·C ·C

= A B C + A B C + A B C + A B C

= A B C

+

+

第二部分:即学即练

第五章组合逻辑电路自测练习

1、四选一数据选择器框图如下图所示。

已

知

用它实现函数:

(1)写出F的最小项表达式;

(2)在图上括号中把满足输出函数F的信号A、B、C及常量1、0填在括号中。

2、试分析下图电路的功能,写出输出Z的表达式。

双四选一数据选择器CC1419的功能表达式如下:

3、试写出下图所示门电路组成的逻辑电路的逻辑表达式和逻辑真值表,并分析其逻辑功能。

输入输出

S A B Y0Y1Y2Y3

1 φφ

0 0 0

0 1

1 0

1 1

4、如图所示3线-8线译码器T4138逻辑功能表达式为:

,,……,,

正常工作时,S1=1,。

写出Z1和Z2的表达式,列出真值表,说明电路功能。

5、试用四选一多路选择器实现函数

6、试分析下图所示电路,列出真值表,说明电路功能。

7、试用一片八选一多路选择器实现逻辑函数:

8、试用一片四选一多路选择器实现逻辑函数:

9、分析下图所示电路,列出真值表和Y3、Y2、Y1、Y0的逻辑表达式,说明电路功能。

10、试分析下图所示逻辑电路,列出真值表,写出Y1、Y2、Y3的逻辑表达式,说明电路功能。

11、分析下图所示电路,列出真值表,写出F的逻辑表达式,说明电路功能。

第五章组合逻辑电路自测题参考答案

1、

若A=A1,B=A0,则D0=1,D1=1,D2=0,D3=C

2、

3、S = 0 时,

输入输出

S A B Y0Y1Y2 Y3

1 ×× 1

1 1 1

0 0 0 1 1 1

0 1 1 0 1 1

1 0 1 1 0 1

1 1 1 1 1 0

功能:2线-4线译码器

4、

= (本位和)

=(进位)

功能:一位全加器。

真值表如下:

5、设:S1 = A1,S0 = A0 ,Z = Y

D1 = 0 D2 = V D3 = 1

输入输出

A B C Z2Z1

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

6

输入输出

A B Y0Y1Y2

0 0 0 1 0

0 1 0 0 1

1 0 1 0 0

1 1 0 1 0

7、设A = A2,B = A1,C = A0,F = Y

则D0 = D4 = D4 = D7 = 1,D2 = D3 = D5 = D6 = 0 电路如下图:

8、设A = A1,B = A0,F = Y

则 D0 = 1 ,D1 = 0

D2 = ,D3 = C

电路如下图:

9、Y0 = ,,,

功能:2线-4线译码器。

(真值表如下)。

10、

功能:4线-2线优先编码器(真值表略)。

11、F=AB+BC+AC,功能:多数表决电路。

真值表如下:

输入输出

A B C F

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1。