F971C685MBA中文资料

FLUKE-971说明书

971Temperature Humidity MeterPN 2441047 (Simplified Chinese)September 2005© 2005 Fluke Corporation, All rights reserved. Printed in TaiwanAll product names are trademarks of their respective companies.简介W小心为延长传感器的寿命,在仪表不使用时,请盖好传感器的保护罩。

Fluke 971 型(以下简称“仪表”)是一种由电池供电、用于测量相对湿度和温度的仪表。

通过数个操作方便的控制步骤,仪表就可显示其传感器周围空气的三种不同的温度值:环境温度、湿球温度和露点温度。

电气和安全符号W重要信息,请见用户手册B显示屏上显示此符号时表示电池电量不足。

P符合欧盟规范;符合澳洲标准。

)符合加拿大标准O电源开/关1971用户手册显示屏2Temperature Humidity Meter操作操作注意当把仪表从一个温度/湿度极限环境移动至另一个时,要等待一段时间让仪表稳定。

打开传感器的保护罩后,按O启动仪表的电源,然后开始读取测量值。

温度读数以摄氏度 (°C) 或华氏度 (°F) 显示。

要在 °C 与 °F 之间切换,取下电池仓门,将温标开关移动到所需要的位置。

请见图 1。

露点温度和湿球温度刚启动仪表时,仪表显示的是环境温度。

要显示露点温度(DP),按一下W。

再按一次W,可切换至湿球温度(WB )。

再按一次W则使仪表返回到环境温度。

选择露点温度和湿球温度时,显示屏上会有符号指示。

保持按下I键可使仪表冻结当前显示的读数。

它还使仪表停止读取测量值。

当 HOLD(保持)功能被启用时,显示屏上显示H。

要继续读取测量值,再按一次I键。

3971用户手册最小值最大值记录当 Min Max Record(最小值最大值记录)功能被启用时,如果一个新测量值大于或小于先前保存的最大或最小测量值,仪表将保存该新测量值。

BC548CZL1中文资料

BC548CZL1中⽂资料BC546B, BC547A, B, C, BC548B, CAmplifier Transistors NPN SiliconFeaturesPbFree Package is Available*MAXIMUM RATINGSMaximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.THERMAL CHARACTERISTICS*For additional information on our Pb?Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.TO?92CASE 29STYLE 17/doc/367855745.htmlMARKINGDIAGRAMBC54xxYWW GCOLLECTOR23EMITTERSee detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet. ORDERING INFORMATIONBC54xx = Specific Device CodeY= YearWW= Work WeekG= Pb?Free PackageELECTRICAL CHARACTERISTICS (T= 25°C unless otherwise noted)ON CHARACTERISTICSSMALL?SIGNAL CHARACTERISTICSBC547/BC5482.00.2Figure 3. Collector Saturation RegionI B , BASE CURRENT (mA)Figure 4. Base?Emitter Temperature CoefficientI C , COLLECTOR CURRENT (mA)1.21.62.00.40.8h F E , N O R M A L I Z E D D C C U R R E N T G A I NV C E , C O L L E C T O R ?E M I T T E R V O L T A G E (V )1.51.00.80.60.40.3Figure 5. Capacitances V R , REVERSE VOLTAGE (VOLTS) 10Figure 6. Current?Gain ? Bandwidth ProductI C , COLLECTOR CURRENT (mAdc)0.40.6 1.010201.02.0 6.080100200300400602040307.05.03.02.00.71.010202.050307.05.03.00.5C , C A P A C I T A N C E (p F )f , C U R R E N T ?G A I N ? B A N D W I D T H P R O D U C T (M H z )T 0.8 4.08.0BC546Figure 7. DC Current Gain I C , COLLECTOR CURRENT (mA)Figure 8. “On” VoltageI C , COLLECTOR CURRENT (mA)0.81.00.60.20.41.02.00.20.5Figure 9. Collector Saturation RegionI B , BASE CURRENT (mA)Figure 10. Base?Emitter Temperature CoefficientI C , COLLECTOR CURRENT (mA)1.01.21.62.00.02 1.0100200.10.40.8V C E , C O L L E C T O R ?E M I T T E R V O L T A G E (V O L T S ) V B , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θ0.2 2.0102001.0h F E , D C C U R R E N T G A I N (N O R M A L I Z E D )V , V O L T A G E (V O L T S )00.050.20.5 2.0 5.0?1.4?1.82.22.63.00.55.02050100Figure 11. Capacitance V R , REVERSE VOLTAGE (VOLTS)40Figure 12. Current?Gain ? Bandwidth ProductI C , COLLECTOR CURRENT (mA)0.10.2 1.0502.02.010100100200500502020106.04.01.010501005.0C , C A P A C I T A N C E (p F )f , C U R R E N T ?G A I N ? B A N D W I D T H P R O D U C TT 0.55.020DEVICE ORDERING INFORMATIONSpecifications Brochure, BRD8011/D.PACKAGE DIMENSIONSTO?92 (TO?226)CASE 29?11ISSUE ALNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.CONTOUR OF PACKAGE BEYOND DIMENSION R IS UNCONTROLLED.4.LEAD DIMENSION IS UNCONTROLLED IN P AND BEYOND DIMENSION K MINIMUM.PLANEDIMMIN MAX MIN MAX MILLIMETERSINCHES A 0.1750.205 4.45 5.20B 0.1700.210 4.32 5.33C 0.1250.165 3.18 4.19D 0.0160.0210.4070.533G 0.0450.055 1.15 1.39H 0.0950.105 2.42 2.66J 0.0150.0200.390.50K 0.50012.70L 0.250 6.35N 0.0800.105 2.04 2.66P 0.100 2.54R 0.115 2.93V0.1353.43STYLE 17:PIN 1.COLLECTOR2.BASE3.EMITTERON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an EqualOpportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

M9718系列说明书2010-12-13

16位

16位

精度

0.1%+0.15%FS

0.1%+0.25%FS

定功率模式(CW)(当输入电压和电流值≥满量程的10%)

量程

0-6000W

0-6000W

分辨率

1mW

10mW

精度

0.1%+0.15%FS

0.1%+0.25%FS

电压测量值

电压

0-19.999V

0-600V

分辨率

0.1mV

10mV

精度

M97系列可编程直流电子负载

用户使用手册

适用型号M9717/M9717B/M9718/M9718B/M9718D/M9718E/M9718F

版本号:V1.1

南京美尔诺电子有限公司版权所有

第一章简介

M97系列产品是美尔诺电子公司设计制造的新一代直流电子负载,采用高性能芯片, 高速,高精度设计,提供0.1mV,0.01mA的解析度, 外观新颖,生产工艺科学严谨,相比同类产品,更具性价比。广泛用于生产线(手机充电器,手机电池,电动车电池,开关电源,线性电源),科研机构,汽车电子,航空航天, 船舶,太阳能电池,燃料电池等行业。

MENU

CONFIG

INPUT RECALL

设置负载上电时的输入状态为上次关机时的状态或者为OFF状态

ON

负载开机时,恢复为关机前的状态。

OFF

负载开机时,输入状态为OFF,工作模式为CC。

KEY SOUND SET

键盘声音设置

ON

键盘有声音

OFF

键盘无声音

CONNECT MODE

连接模式

MAXTIDLEXING

多台

KC75118资料

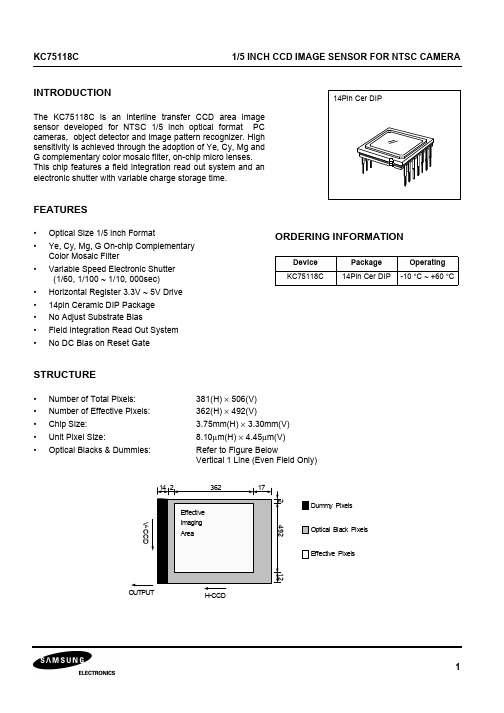

INTRODUCTIONThe KC75118C is an interline transfer CCD area imagesensor developed for NTSC 1/5 inch optical format PCcameras, object detector and image pattern recognizer. Highsensitivity is achieved through the adoption of Ye, Cy, Mg andG complementary color mosaic filter, on-chip micro lenses.This chip features a field integration read out system and anelectronic shutter with variable charge storage time.FEATURES•Optical Size 1/5 inch Format•Ye, Cy, Mg, G On-chip ComplementaryColor Mosaic Filter•Variable Speed Electronic Shutter(1/60, 1/100 ~ 1/10, 000sec)•Horizontal Register 3.3V ~ 5V Drive•14pin Ceramic DIP Package•No Adjust Substrate Bias•Field Integration Read Out System•No DC Bias on Reset GateSTRUCTURE•Number of Total Pixels:381(H) × 506(V)•Number of Effective Pixels:362(H) × 492(V)•Chip Size: 3.75mm(H) × 3.30mm(V)•Unit Pixel Size:8.10µm(H) × 4.45µm(V)•Optical Blacks & Dummies:Refer to Figure BelowVertical 1 Line (Even Field Only)ORDERING INFORMATIONDevice Package OperatingKC75118C14Pin Cer DIP-10 °C ~ +60 °CBLOCK DIAGRAMPIN DESCRIPTIONFigure 1. Block DiagramTable 1. Pin DescriptionPin Symbol DescriptionPin Symbol Description1ΦV4Vertical register transfer clock 48V DD Output stage drain bias 2ΦV3Vertical register transfer clock 39GND Ground 3ΦV2Vertical register transfer clock 210ΦSUB Substrate clock 4ΦV1Vertical register transfer clock 111V L Protection circuit bias 5NC No connection 12ΦRG Reset gate clock6GND Ground 13ΦH1Horizontal CCD transfer clock 1 7V OUTSignal output14ΦH2Horizontal CCD transfer clock 27V OUT 654321891011121314GND NCΦV1ΦV2ΦV3ΦV4V DD V LGNDΦH1ΦH2ΦRGΦSUBVertical Shift Register CCDVertical Shift Register CCDVertical Shift Register CCDVertical Shift Register CCDHorizontal Shift Register CCDCy Ye Mg Mg MgMg Mg Ye Ye Ye Ye Ye Ye Ye G G GG Cy Cy Cy Cy Cy GMgG Cy Cy (Top View)ABSOLUTE MAXIMUM RATINGS (NOTE)NOTE:The device can be destroyed, if the applied voltage or temperature is higher than the absolute maximum rating voltageor temperature.Table 2. Absolute Maximum RatingsCharacteristicsSymbolsMin.Max.Unit Substrate voltageSUB - GND -0.340V Vertical clock input voltageΦV1, ΦV3, - GND -0.330V ΦV2, ΦV4 - GND -0.317V ΦV1, ΦV3, - V L -0.330V ΦV2, ΦV4 - V L-0.317V ΦV1, ΦV2, ΦV3, ΦV4 - SUB-4010V Horizontal clock input voltageΦV1, ΦV2, - GND -0.316V ΦH1, ΦH2 - V L-0.316V Voltage difference between vertical and horizontal clock input pinsΦV1, - ΦV3-3030V ΦV2, - ΦV4-1616V ΦH1, ΦH2-1616V ΦH1, ΦH2 - ΦV4-1616V Output clock input voltage ΦRG - GND -0.316V Protection circuit bias voltage V L - SUB -400.3V Operating temperature T OP -1060°C Storage temperatureT STG-3080°CDC CHARACTERISTICSCLOCK VOLTAGE CONDITIONS Table 3. DC CharacteristicsItem Symbol Min.Typ.Max.Unit Remar Output stage drain bias V DD14.5515.015.45VReset gate voltage adjustment range V RGL0VProtection circuit bias voltage V L The lowest vertical clock levelOutput stage drain current I DD5mATable 4. Clock Voltage ConditionsItem Symbol Min.Typ.Max.Unit RemarkRead-out clock voltage V VT14.5515.015.45V High level Vertical transfer clock voltage V VM1 ~ V VM4-0.050.00.05V V VH = (V VH1+V VH2)/2V VL1 ~ V VL4-8.5-8.0-7.5V V VH = (V VH1+V VH2)/2 Horizontal transfer clock voltage VΦH 3.0 5.0 5.25V HighV HL -0.050.00.05V Low Charge reset clock voltage VΦRG 4.75 5.0 5.25V HighV RGLH - V RGLL0.8V Low Substrate clock voltage VΦSUB21.522.523.5V ShutterDRIVE CLOCK WAVEFORM CONDITIONS Read Out Clock WaveformVertical Transfer Clock WaveformHorizontal Transfer Clock Waveform DiagramReset Gate Clock Waveform DiagramV RGLH is the maximum value and V RGLL the minimum value of the coupling waveform in the period from Point A in the diagram about to R G riseV RGL = (V RGLH + V RGLL)/2, V FRG = V RGH - V RGLSubstrate Clock WaveformCLOCK EQUIVALENT CIRCUIT CONSTANTTable 5. Clock Equivalent Circuit ConstantItem Symboltwh twl tr tfUnit Min.Typ.Max.Min.Typ.Max.Min.Typ.Max.Min.Typ.Max.Read-out clockΦVH 2.50.50.5µsVertical clock ΦV1, ΦV2ΦV3, ΦV415250nsHorizontal clock ΦH155675567918718ns ΦH255675567918718nsReset clockΦRG253410785ns Substrate clockΦSUB 1.5 2.00.50.5µsEQUIVALENT CIRCUIT PARAMETERSTable 6. Equivalent Circuit ParametersItem Symbol Typ.Unit Remark Capacitance between vertical transfer clock and GND CΦV1, CΦV3520pFCΦV2, CΦV4390pF Capacitance between vertical transfer clocks CΦV12, CΦV34220pFCΦV23, CΦV41150pFCΦV13120pFCΦV2490pF Capacitance between horizontal transfer clock and GND CΦH1, CΦH224pF Capacitance between horizontal transfer clocks CΦH1238pF Capacitance between substrate clock and GND CΦSUB1120pFVertical transfer clock serial resistor RΦV1 ~ RΦV440ΩVertical transfer clock ground resistor RΦVGND15ΩHorizontal transfer clock serial resistor RΦH1, RΦH210ΩΩReset gate clock serial resistor RΦRG100OPERATING CHARACTERISTICSDevice Temperature = 25 °CNOTE:Test Temperature = 60 °CTESTING SYSTEMTable 7. Operating CharacteristicsItemSymbol Min.Typ.Max.Unit RemarkSensitivity S 3035mV/lux 1Saturation signal Y SAT 700mV 2SmearSM 0.0070.01%3Blooming margin BM 1,000times 4Uniformity U 20%5Dark signal (NOTE)D 2mV 6Dark shading (NOTE) ∆D 2mV 7Image lag Y LAG 0.5%8Flicker Y F Y 2%9Flicker red, blue F CR , F CB 5%10Color uniformity D SR , D SB 10%11Line stripe W, R, G, BL CW , L CR , L CG , L CB2%12Figure 2. Testing SystemCCD AMPLPF1S/HS/HLPF2AY C (3dB down at 4MHz)ChromaSignal OutputIlluminanceSignal OutputCCD Signal OutputC. D. S (3dB down at 1MHz)TEST CONDITION1. Use a light source with color temperature of 3,200K hallogen lamp and CM-500S for IR cut filter. The light source is adjusted in accordance with the average value of Y signals indicated in each item.COLOR FILTER ARRAYThe color filter array of this image sensor is shown in the right figure. this complementary mosaic CFA is used with the operation of field integration mode, where all of the photosensors are read out during each video field. The signals from two vertically-adjacent photosensor lines, such as line couple A1 or A2 for field A are summed when the signal charges are transferred into the vertical transfer CCD column. The read out line pairing is shifted down by one line for field B.The sensor output signals through the horizontal register (H-CCD) at line A1 are [G+Cy], [MG+Ye], [G+CY],[Mg+Ye]. These signals are processed in order to compose Y and C signals. By adding the two adjacent signals at line A1, Y signal is formed as followsC signal is composed by substracting the two adjacent signals at line A1Figure 3. Color Filter ArrayY 12---G Cy +()Mg Ye +()+[] 12---2B 3G 2R ++()==H - CCDA1A2BCy Ye GMg Cy Cy Cy YeYe Ye GGG Mg MgMgNext, the signals through H-CCD at line A2 are [Mg+Cy], [G+Ye], [Mg+Cy], [G+Ye]. Simmilary, Y and C signals are composed at line A2 as followsAccordingly, Y signal is balanced in relation to scanning lines, and C signal takes the form of R-Y and -(B-Y) onalternate lines.It is same for B field.TEST METHODS1. Measure the light intensities (L) when the averaged illuminance output value (Y) is the standard illuminance output value, 150mV (Y A ) and when half of 150mV (1/2 Y A ).2. Adjust the light intensity to 10 times that of Y signal output average value (Y A = 150mV) , then test Y signal minimum value (Y = Y SAT ).3. Adjust the light intensity to 500 times that of Y signal output average value (Y A = 150mV), then remove the read- out clock and drain the signal in photosensors by the electronic shutter operation in all the respective horizontal blanking times with the other clocks unchanged. Measure the maximum illuminance output value (Y SM ).4. Adjust the light intensity to 1,000 times of the value with which Y is Y A , then inspect whether there is blooming phenomenon or not.R Y = –Mg Ye +()G Cy +()–[] 2R G –()=Y 12---G Ye +()Mg Cy +()+[] 12---2B 3G 2R ++()==B Y –() G Ye +()Mg Cy +()–[] 2B G –()–==–S Y A 12---Y A–L YA L 12---Y A –-------------------------------=SM Y SM Y A -----------1500----------×110-------×100%()×=5. Measure the maximum and minimum illuminance output value (Y MAX , Y MIN ) when the light intensity is adjusted to make Y to be Y A .6. Measure Y D with the horizontal idling time transfer level as reference, when the device ambient temperature is 60 °C and all of the light sources are shielded.7. Follow test method 6, measure the maximum (D MAX ) and minimum illuminance output (D MIN ).8. Adjust the light intensity of Y signal output value by strobe light to 150mV (Y A ), calculate by below formula with measuring the image lag signal which is qenerated by below timing diagram.U Y MAX Y MIN–Y A-------------------------------------100%()×=∆D D MAX D MIN–=Y LAG Y lag 150⁄()100%()×=FLDSG1Strobe TimingOutputY Signal Output 150mVLightY Lag9. Adjust the light intensity of Y signal average value to 150mV (Y A ), calculate by below formula with measuring the signal differences (∆Y f [mV]) between fields.10. Adjust the light intensity to make Y = Y A using red (R) and blue (B) optical filters respectively, measure the differences (∆C R , ∆C B ) between the chroma signal values in even and odd fields and the averaged chroma signal values (C R , C B )., where i = R, B11. Adjust the light intensity to make Y = Y A using red (R) and blue (B) optical filters respectively, measure theminimum (C R,MIN and C B,MIN ) and maximum (C R,MAX and C B,MAX ) chroma signal values., where i = R, B12. Adjust the light intensity to make Y = 150mV(Y L ) using white (no filter, W), red (R), green (G) and blue (B) optical filters respectively, measure the illuminance signal difference values (∆Y LW , ∆Y LR , ∆Y LG , ∆Y LB ) between illuminance signal lines of the same field., where i = W, R, G, BF Y ∆Y f Y A ⁄()100%()×=F C i ∆C iC i---------100%()×=DS i C i MAX ,C i MIN,–Y i--------------------------------------------100%()×=L c i ∆Y Li Y L------------100%()×=SPECTRAL RESPONSE CHARACTERISTICSExcluding Light Source CharacteristicsFigure 4. Spectral Response CharacteristicsAPPLICATION CIRCUITSFigure 5. Application Circuits1234567891020191817161514131211891011121314K C 75118CKS7221D7654321ΦV4ΦV3ΦV2ΦV1ΦH2ΦH1ΦRG GNDVOUTVL NC ΦSUB GND VDD +-10µ/16V+-+-CCD Out-7.5V10µ/16VMA110100K1µ/35V1041003.9K2SK10701M15210310µ/16V+-1015VXSUB XV2XV1XSG1 XV3XSG2XV4ΦH2ΦH1RGREAD-OUT CLOCK TIMING CHARTFigure 6. Read-out Clock Timing ChartCLOCK TIMING CHART (VERTICAL SYNC.)Figure 7. Clock Timing Chart (Vertical Sync.)491492FLD VDHDSG1SG2V1V2V3V4CCD OUTCLP1135749049149213579246810246CLOCK TIMING CHART (HORIZONTAL SYNC.)Figure 8. Clock Timing Chart (Horizontal Sync.)H DH 1H 2R GS H PS H DV 1V 2V 3V 4C L P 1S U B3621101711011020PACKAGE DIMENSIONSFigure 9. Package DimensionsHANDLING INSTRUCTIONS•Static Charge PreventionCCD image sensors can be easily damaged by static discharge. Before handling, be sure to take the following protective measures.—Use non chargeable gloves, clothes or material. Also use conductive shoes.—When handling directly, use an earth band.—Install a conductive mat on the floor or working table to prevent generation of static electricity.—Ionized air is recommended for discharging when handling CCD image sensor.—For the shipment of mounted substrates, use boxes treated for the prevention of static charges.•Soldering—Make sure the package temperature does not exceed 80 °C.—Solder dipping in a mounting furnace causes damage to the glass and other defects. Use a grounded 30W soldering iron and solder each pin in less than 2 seconds. For repairs and and remount, cool sufficiently.—To dismount an imaging device, do not use a solder suction equipment. When using an electronic disoldering tool, use a thermal controller of the zero cross on/off type and connect to ground•Dust and Dirt Protection—Operate in the clean environments (around class 1000 will be appropriate).—Do not either touch glass plates by hand or have object come in contact with glass surface. Should dirt stick to a glass surface blow it off with an air blow (for dirt stuck through static electricity ionized air isrecommended).—Clean with a cotton bud and ethyl alcohol if the glass surface is grease stained. Be caerful not to scratch the glass.—Keep in case to protect from dust and dirt. To prevent dew condensation, preheat or precool when moving to a room with great temperature differences.—When a protective tape is applied before shipping, just before use remove the tape applied electrostatic protection. Do not reuse the tape.•Do not expose to strong light (sun rays) for long period, color filter are discolored.•Exposure to high temperature or humidity will affect the characteristics. accordingly avoid storage or usage in such conditions.•CCD image sensors are precise optical equipment that should not be subject to mechanical shocks.。

685使用说明书

ADEMCO 685 数字通讯接收机安装使用手册目录:1. 安装程序 12. 使用介绍(图5) 53. 通讯格式之定义74. 附件:91. 安装程序1.1. 旋开685 上盖的四颗镙丝1.2. 由於运输途中,可能使分别在板槽J1,J3及J5的显示驱动器卡,记忆体卡及中央处理器卡与板槽接触不良,因此必须使用各电路板两端白色的启出杆启出各电路板,再重新插入以确保各电路板与板槽接触正常.(图1)1.3. 检查各接线插头接触良好(如将来685 需要移动,也需要重覆此步骤1至3)1.4. 记忆体卡的安装(图2)1.4.1.将写有"685C" 的691 PROM芯片依图2插入记忆体卡之691 晶片槽内。

注意红色三角形在左下角方向1.4.2.依图2和你的周边设备设置跨接线位置1.5. 电话线卡(图3)1.5.1.将电话线卡由板槽J6 起插入1.5.2.连接电话接头1.5.3.调整组别号码旋钮开关(如电话线卡#1调为1,电话线卡#2调为2.....)此号码会显示在前板数字发光二极管GRP.NO. 处1.6. 685接线(图4)1.6.1.连接电话线1.6.2.连接并行式打印机(J105). 开启打印机电源(某些打印机其PIN9 必须和PIN16 连接起来才能正常操作)1.6.3.连接外接警号(J104为常闭开关输出,开关最大额定值为12 伏特直流2安培)(需外接电源12VDC)1.7. 检查以上各步骤,证实无误後连接电源(220VAC,50Hz) 1.8. 这时685被启动,各指示灯闪亮,打印机会打印出一段文字1.9. 接入後备电池(J106,J107为并联)后面前面图 1 685机内俯视图图3 电话线卡电源模块检测串行式打印机(20脚为准备好线):跨线2和3 检测串行式打印机(21脚为准备好线):跨线1和2 不检测串行式打印机:出厂时设置(跨线4和5)图2 记忆体卡设置2. 使用介绍(图5)2.1. 前板按钮功能2.1.1.AUTO/MANUAL 自动/手动开关a. 在AUTO 自动位置,如周边设备,如打印机,操作正常,则所有信息将自动输出.b. 在MANUAL 手动位置,任何信息将被储存在685记忆体中,直至操作员按下DISPLAY NEXT MESSAGE 显示下一信息键* 在AUTO 自动位置时,如685检测到周边设备故障,将自动切换至MANUAL手动模式. 685自动方式还与打印机、电脑选用设置及检测开关设置有关。

EKB00AA168L00中文资料

For technical questions, contact: aluminumcaps1@Document Number: 25013EKBVishay RoedersteinAluminum CapacitorsRadial StyleFEATURES•Polarized aluminum electrolytic capacitors,non-solid electrolyte•Radial leads, cylindrical aluminum case•Miniaturized, high CV-product per unit volume •Extended temperature range: 105 °C •RoHS compliantAPPLICATIONS•General purpose, industrial and audio-video•Coupling, decoupling, timing, smoothing, filtering,buffering in SMPS•Portable and mobile equipment (small size, low mass)Note10 % capacitance tolerance on request Component outlinesQUICK REFERENCE DATADESCRIPTIONUNIT VALUENominal case size (Ø D x L)mm 5 x 11 to 8 x 11.510 x 12.5 to 18 x 40Rated capacitance range C R µF 2.2 to 22 000Capacitance tolerance %± 20Rated voltage rangeV 6.3 to 100160 to 350400 to 450Category temperature range °C - 55 to + 105- 40 to + 105- 25 to + 105Load lifeh10002000Based on sectional specification IEC 60384-4/EN 130300Climatic category 55/105/5640/105/5625/105/56IEC 60068SELECTION CHART FOR C R , U R AND RELEVANT NOMINAL CASE SIZES (Ø D x L in mm)C R (µF)RATED VOLTAGE (V) (> 100 V see next page)6.31016253550631002.2→→→→→→ 5 x 11 5 x 113.3→→→→→→ 5 x 11 5 x 114.7→→→→→→ 5 x 11 5 x 116.8→→→→→→ 5 x 11 5 x 1110→→→→→→ 5 x 11 5 x 1115→→→→→→ 5 x 11 6.3 x 1122→→→→→→ 5 x 11 6.3 x 1133→→→→→ 5 x 11 6.3 x 118 x 11.547→→→→ 5 x 11→ 6.3 x 1110 x 12.568→→→ 5 x 11 6.3 x 11→8 x 11.510 x 16100→→ 5 x 11→ 6.3 x 11→8 x 11.510 x 20150→ 5 x 11→ 6.3 x 118 x 11.5→10 x 12.512.5 x 20220→ 5 x 11 6.3 x 11→8 x 11.510 x 12.510 x 1612.5 x 25330→ 6.3 x 11→8 x 11.510 x 12.510 x 1610 x 2016 x 25470→ 6.3 x 118 x 11.510 x 12.510 x 1610 x 2012.5 x 2016 x 256808 x 11.5→10 x 12.510 x 1612.5 x 1612.5 x 2012.5 x 2516 x 31.510008 x 11.510 x 12.510 x 1610 x 2012.5 x 2012.5 x 2516 x 2518 x 401500→10 x 1612.5 x 1612.5 x 2016 x 2016 x 2516 x 35.5-2200→10 x 2012.5 x 2012.5 x 2516 x 2516 x 31.516 x 35.5-330012.5 x 1612.5 x 2012.5 x 2516 x 2516 x 35.516 x 35.518 x 40-470012.5 x 2012.5 x 2516 x 2516 x 31.516 x 35.5---680012.5 x 2516 x 2516 x 31.518 x 35.5----10 00016 x 2516 x 35.518 x 35.5-----15 00016 x 35.518 x 35.5------22 00018 x 40-------Document Number: 25013For technical questions, contact: aluminumcaps1@EKBAluminum CapacitorsRadial StyleVishay RoedersteinNote10 % capacitance tolerance on requestSELECTION CHART FOR C R , U R AND RELEVANT NOMINAL CASE SIZES (Ø D x L in mm)C R (µF)RATED VOLTAGE (V)1602002503504004502.2→→ 6.3 x 11→8 x 11.510 x 12.53.3→ 6.3 x 11→8 x 11.510 x 12.510 x 164.7 6.3 x 11→8 x 11.5→10 x 12.510 x 166.88 x 11.5→10 x 12.5→10 x 1610 x 2010→→10 x 12.510 x 1610 x 2012.5 x 2015→→10 x 1610 x 2012.5 x 2012.5 x 2522→10 x 1610 x 2012.5 x 2012.5 x 2516 x 2533→10 x 2012.5 x 2012.5 x 2516 x 2516 x 31.547→12.5 x 2012.5 x 2516 x 2516 x 31.516 x 35.56812.5 x 2516 x 2016 x 2516 x 31.518 x 35.518 x 4010012.5 x 2516 x 2516 x 31.518 x 35.518 x 40-15016 x 2516 x 35.518 x 35.518 x 40--22016 x 31.518 x 35.518 x 40---33018 x 35.518 x 40----47018 x 40----- For technical questions, contact: aluminumcaps1@Document Number: 25013EKBVishay RoedersteinAluminum CapacitorsRadial StyleGENERAL NOTE•For Standard Packaging Quantity (SPQ) and Minimum Order Quantity (MOQ) please refer to our price list or contact customer service •For other packaging forms please refer to Vishay Roederstein General InformationNoteUnless otherwise specified, all electrical values apply at T a = 20 °C , P = 80to 120kPa, RH =45to 75 %.ORDERING EXAMPLEEKB 3300 µF/25 V, ± 20 %, size: 16 x 25 mm Leads: LongOrdering code: MALREKB00JG433E00K Leads: ShortOrdering code: MALREKB05...For 5 ≤ Ø D ≤ 8 mmLeads: Bent open, shortened and formed Ordering code: MALREKB09...For 10 ≤ Ø D ≤ 18 mmLeads: Shortened and formed Ordering code: MALREKB06 ...ELECTRICAL DATASYMBOL DESCRIPTIONU R rated voltageC R rated capacitance at 120 Hz tan δmax. dissipation factor at 120 HzR ESR calculated equivalent series resistance at 120Hz I Rrated ripple current (rms) at 120 Hz and upper category temperatureDocument Number: 25013For technical questions, contact: aluminumcaps1@EKBAluminum CapacitorsRadial StyleVishay RoedersteinELECTRICAL DATA AND ORDERING INFORMATIONU R (V)C R 120Hz (µF)DIMENSIONSD x L (mm)tan δ120 Hz R ESR 120Hz (Ω)I R120 Hz/105 °C(mA)WEIGHT (g)CATALOG NUMBER (Long Leads)6.36808 x 11.50.280.55348 1.10MALREKB00PB368B00K 10008 x 11.50.280.37422 1.10MALREKB00PB410B00K 330012.5 x 160.340.14983 3.00MALREKB00FD433B00K 470012.5 x 200.360.101219 4.00MALREKB00FE447B00K 680012.5 x 250.400.081480 5.00MALREKB00FG468B00K 10 00016 x 250.460.0618078.50MALREKB00JG510B00K 15 00016 x 35.50.560.05223311.0MALREKB00JL515B00K 22 00018 x 400.700.04265214.6MALREKB00KK522B00K 10150 5 x 110.24 2.121340.45MALREKB00AA315C00K 220 5 x 110.24 1.451620.45MALREKB00AA322C00K 330 6.3 x 110.240.962280.46MALREKB00BA333C00K 470 6.3 x 110.240.682720.46MALREKB00BA347C00K 100010 x 12.50.240.32544 2.05MALREKB00DC410C00K 150010 x 160.260.23680 2.20MALREKB00DD415C00K 220010 x 200.280.17844 3.10MALREKB00DE422C00K 330012.5 x 200.300.121148 4.00MALREKB00FE433C00K 470012.5 x 250.320.091421 5.00MALREKB00FG447C00K 680016 x 250.360.0717378.50MALREKB00JG468C00K 10 00016 x 35.50.420.06217211.0MALREKB00JL510C00K 15 00018 x 35.50.520.05248214.0MALREKB00KL515C00K 16100 5 x 110.20 2.651190.45MALREKB00AA310D00K 220 6.3 x 110.20 1.212030.46MALREKB00BA322D00K 4708 x 11.50.200.56349 1.10MALREKB00PB347D00K 68010 x 12.50.200.39488 2.05MALREKB00DC368D00K 100010 x 160.200.27648 2.20MALREKB00DD410D00K 150012.5 x 160.220.19862 3.00MALREKB00FD415D00K 220012.5 x 200.240.141055 4.00MALREKB00FE422D00K 330012.5 x 250.260.101323 5.00MALREKB00FG433D00K 470016 x 250.280.0816578.50MALREKB00JG447D00K 680016 x 31.50.320.06198210.0MALREKB00JS468D00K 10 00018 x 35.50.380.05240914.0MALREKB00KL510D00K 2568 5 x 110.16 3.121080.45MALREKB00AA268E00K 150 6.3 x 110.16 1.411850.46MALREKB00BA315E00K 3308 x 11.50.160.64324 1.10MALREKB00PB333E00K 47010 x 12.50.160.45449 2.05MALREKB00DC347E00K 68010 x 160.160.31591 2.20MALREKB00DD368E00K 100010 x 200.160.21782 3.10MALREKB00DE410E00K 150012.5 x 200.180.161017 4.00MALREKB00FE415E00K 220012.5 x 250.200.121235 5.00MALREKB00FG422E00K 330016 x 250.220.0915628.50MALREKB00JG433E00K 470016 x 31.50.240.07191610.0MALREKB00JS447E00K 680018 x 35.50.280.05233514.0MALREKB00KL468E00KEKBVishay Roederstein Aluminum CapacitorsRadial Style3547 5 x 110.14 3.95960.45MALREKB00AA247F00K 68 6.3 x 110.14 2.731320.46MALREKB00BA268F00K 100 6.3 x 110.14 1.861600.46MALREKB00BA310F00K 1508 x 11.50.14 1.24231 1.10MALREKB00PB315F00K 2208 x 11.50.140.84280 1.10MALREKB00PB322F00K 33010 x 12.50.140.56399 2.05MALREKB00DC333F00K 47010 x 160.140.40521 2.20MALREKB00DD347F00K 68012.5 x 160.140.27740 3.00MALREKB00FD368F00K 100012.5 x 200.140.19974 4.00MALREKB00FE410F00K 150016 x 200.160.141188 6.00MALREKB00JE415F00K 220016 x 250.180.1114268.50MALREKB00JG422F00K 330016 x 35.50.200.08185711.0MALREKB00JL433F00K 470016 x 35.50.220.06222414.0MALREKB00JL447F00K5033 5 x 110.12 4.82920.45MALREKB00AA233H00K 22010 x 12.50.120.72376 2.05MALREKB00DC322H00K 33010 x 160.120.48504 2.20MALREKB00DD333H00K 47010 x 200.120.34657 3.10MALREKB00DE347H00K 68012.5 x 200.120.23927 4.00MALREKB00FE368H00K 100012.5 x 250.120.161226 5.00MALREKB00FG410H00K 150016 x 250.140.1214428.50MALREKB00JG415H00K 220016 x 31.50.160.10144210.0MALREKB00JS422H00K 330016 x 35.50.180.07179411.0MALREKB00JL433H00K632.2 5 x 110.1060.29260.45MALREKB00AA122J00K3.3 5 x 110.1040.19320.45MALREKB00AA133J00K4.7 5 x 110.1028.22380.45MALREKB00AA147J00K 6.8 5 x 110.1019.50460.45MALREKB00AA168J00K 10 5 x 110.1013.26560.45MALREKB00AA210J00K 15 5 x 110.108.84680.45MALREKB00AA215J00K 22 5 x 110.10 6.03830.45MALREKB00AA222J00K 33 6.3 x 110.10 4.021160.46MALREKB00BA233J00K 47 6.3 x 110.10 2.821390.46MALREKB00BA247J00K 688 x 11.50.10 1.95197 1.10MALREKB00PB268J00K 1008 x 11.50.10 1.33239 1.10MALREKB00PB310J00K 15010 x 12.50.100.88340 2.05MALREKB00DC315J00K 22010 x 160.100.60451 2.20MALREKB00DD322J00K 33010 x 200.100.40603 3.10MALREKB00DE333J00K 47012.5 x 200.100.28844 4.00MALREKB00FE347J00K 68012.5 x 250.100.2011075.00MALREKB00FG368J00K 100016 x 250.100.1314908.50MALREKB00JG410J00K 150016 x 35.50.120.11177011.0MALREKB00JL415J00K 220016 x 35.50.140.08177011.0MALREKB00JL422J00K 330018 x 400.160.06268914.6MALREKB00KK433J00KELECTRICAL DATA AND ORDERING INFORMATIONU R (V)C R120Hz(µF)DIMENSIONSD x L(mm)tan δ120 HzR ESR120Hz(Ω)I R120 Hz/105 °C(mA)WEIGHT(g)CATALOGNUMBER(Long Leads)Document Number: 25013For technical questions, contact: aluminumcaps1@EKBAluminum CapacitorsRadial StyleVishay Roederstein1002.2 5 x 110.0848.23260.45MALREKB00AA122L00K3.3 5 x 110.0832.15320.45MALREKB00AA133L00K4.7 5 x 110.0822.58380.45MALREKB00AA147L00K 6.8 5 x 110.0815.60460.45MALREKB00AA168L00K 10 5 x 110.0810.61560.45MALREKB00AA210L00K 156.3 x 110.087.07780.46MALREKB00BA215L00K 22 6.3 x 110.08 4.82950.46MALREKB00BA222L00K 338 x 11.50.08 3.22137 1.10MALREKB00PB233L00K 4710 x 12.50.08 2.26190 2.05MALREKB00DC247L00K 6810 x 160.08 1.56251 2.20MALREKB00DD268L00K 10010 x 200.08 1.06332 3.10MALREKB00DE310L00K 15012.5 x 200.080.71477 4.00MALREKB00FE315L00K 22012.5 x 250.080.48630 5.00MALREKB00FG322L00K 33016 x 250.080.328568.50MALREKB00JG333L00K 47016 x 250.080.2310218.50MALREKB00JG347L00K 68016 x 31.50.080.16134410.0MALREKB00JS368L00K 100018 x 400.080.11192514.6MALREKB00KK410L00K 1604.7 6.3 x 110.1542.33340.46MALREKB00BA147M00K 6.88 x 11.50.1529.2649 1.10MALREKB00PB168M00K 6812.5 x 250.15 2.93273 5.00MALREKB00FG268M00K 10012.5 x 250.15 1.99331 5.00MALREKB00FG310M00K 15016 x 250.15 1.334508.50MALREKB00JG315M00K 22016 x 31.50.150.9059610.0MALREKB00JS322M00K 33018 x 35.50.150.6082214.0MALREKB00KL333M00K 47018 x 400.150.42101514.6MALREKB00KK347M00K 2003.3 6.3 x 110.1560.29290.46MALREKB00BA133S00K 2210 x 160.159.04111 2.20MALREKB00DD222S00K 3310 x 200.15 6.03149 3.10MALREKB00DE233S00K 4712.5 x 200.15 4.23208 4.00MALREKB00FE247S00K 6816 x 200.15 2.93279 6.00MALREKB00JE268S00K 10016 x 250.15 1.993688.50MALREKB00JG310S00K 15016 x 35.50.15 1.3351711.0MALREKB00JL315S00K 22018 x 35.50.150.9067114.0MALREKB00KL322S00K 33018 x 400.150.6085014.6MALREKB00KK333S00K 2502.2 6.3 x 110.1590.43230.46MALREKB00BA122N00K 4.78 x 11.50.1542.3340 1.10MALREKB00PB147N00K 6.810 x 12.50.1529.2656 2.05MALREKB00DC168N00K 1010 x 12.50.1519.8968 2.05MALREKB00DC210N00K 1510 x 160.1513.2692 2.20MALREKB00DD215N00K 2210 x 200.159.04121 3.10MALREKB00DE222N00K 3312.5 x 200.15 6.03175 4.00MALREKB00FE233N00K 4712.5 x 250.15 4.23227 5.00MALREKB00FG247N00K 6816 x 250.15 2.933038.50MALREKB00JG268N00K 10016 x 31.50.15 1.9940210.0MALREKB00JS310N00K 15018 x 35.50.15 1.3355414.0MALREKB00KL315N00K 22018 x 400.150.9069414.6MALREKB00KK322N00KELECTRICAL DATA AND ORDERING INFORMATIONU R (V)C R 120Hz (µF)DIMENSIONSD x L (mm)tan δ120 Hz R ESR 120Hz (Ω)I R120 Hz/105 °C(mA)WEIGHT (g)CATALOG NUMBER (Long Leads) For technical questions, contact: aluminumcaps1@Document Number: 25013EKBVishay RoedersteinAluminum CapacitorsRadial Style3503.38 x 11.50.2080.3834 1.10MALREKB00PB133O00K 1010 x 160.2026.5375 2.20MALREKB00DD210O00K 1510 x 200.2017.68100 3.10MALREKB00DE215O00K 2212.5 x 200.2012.06143 4.00MALREKB00FE222O00K 3312.5 x 250.208.04190 5.00MALREKB00FG233O00K 4716 x 250.20 5.642528.50MALREKB00JG247O00K 6816 x 31.50.20 3.9033210.0MALREKB00JS268O00K 10018 x 35.50.20 2.6540714.0MALREKB00KL310O00K 15018 x 400.20 1.7752314.6MALREKB00KK315O00K 4002.28 x 11.50.20120.628 1.10MALREKB00PB122X00K3.310 x 12.50.2080.3839 2.05MALREKB00DC133X00K4.710 x 12.50.2056.4447 2.05MALREKB00DC147X00K 6.810 x 160.2039.0162 2.20MALREKB00DD168X00K 1010 x 200.2026.5382 3.10MALREKB00DE210X00K 1512.5 x 200.2017.68118 4.00MALREKB00FE215X00K 2212.5 x 250.2012.061555.00MALREKB00FG222X00K 3316 x 250.208.042118.50MALREKB00JG233X00K 4716 x 31.50.20 5.6427610.0MALREKB00JS247X00K 6818 x 35.50.20 3.9037314.0MALREKB00KL268X00K 10018 x 400.20 2.6542714.6MALREKB00KK310X00K 4502.210 x 12.50.20120.627 2.05MALREKB00DC122P00K3.310 x 160.2080.3836 2.20MALREKB00DD133P00K4.710 x 160.2056.4443 2.20MALREKB00DD147P00K 6.810 x 200.2039.0156 3.10MALREKB00DE168P00K 1012.5 x 200.2026.5380 4.00MALREKB00FE210P00K 1512.5 x 250.2017.681075.00MALREKB00FG215P00K 2216 x 250.2012.061448.50MALREKB00JG222P00K 3316 x 31.50.208.0419310.0MALREKB00JS233P00K 4716 x 35.50.20 5.6424211.0MALREKB00JL247P00K 6818 x 400.203.9035214.6MALREKB00KK268P00KELECTRICAL DATA AND ORDERING INFORMATIONU R (V)C R120Hz(µF)DIMENSIONSD x L (mm)tan δ120 Hz R ESR 120Hz (Ω)I R120 Hz/105 °C(mA)WEIGHT (g)CATALOG NUMBER (Long Leads)LOW TEMPERATURE BEHAVIORIMPEDANCE RATIOZ(T2)/Z(T1)RATED VOLTAGE(V)T2/T1 6.31016253550 ~ 100160200 ~ 350400450- 25/+ 20 °C 54322234610- 40/+ 20 °C108643348--ADDITIONAL ELECTRICAL DATAPARAMETERCONDITIONSVALUECurrent Leakage current(T est conditions: U R , 20 °C)After 1 minute at U R I L1 ≤ 0.03 x C R x U R or 4 µA for U R ≤ 100 V (whichever is greater)After 2 minutes at U R I L2 ≤ 0.01 x C R x U R or 3 µA for U R ≤ 100 V (whichever is greater) After 5 minutes at U RI L5 ≤ 0.02 x C R x U R+ 15 µAfor U R > 100 V (whichever is greater)ResistanceEquivalent series resistance (ESR)Calculated from tan δmax.and C RESR = tan δ/2 π f C RDocument Number: 25013For technical questions, contact: aluminumcaps1@EKBAluminum CapacitorsRadial StyleVishay RoedersteinMULTIPLIER OF RIPPLE CURRENT (I R ) AS A FUNCTION OF FREQUENCYFREQUENCY(Hz)I R MULTIPLIER FOR U R ≤ 100 VC R ≤ 47 µFC R = 68 to 680 µFC R ≥ 1000 µF500.750.800.85120 1.00 1.00 1.00300 1.35 1.25 1.101000 1.55 1.35 1.15≥ 10 0002.001.501.15MULTIPLIER OF RIPPLE CURRENT (I R ) AS A FUNCTION OF FREQUENCYFREQUENCY(Hz)I R MULTIPLIER FOR U R 160 V to ≤ 450 VC R = 47 to 220 µFC R ≥ 330 µF500.800.90120 1.00 1.00300 1.25 1.101000 1.40 1.13≥ 10 0001.601.15TEST PROCEDURES AND REQUIREMENTSTESTPROCEDURE (QUICK REFERENCE)REQUIREMENTSLoad lifeT amb = 105 °C U R and I R appliedAfter 1000 hours Ø 5, Ø 6.3, Ø 8 mm After 2000 hours ≥ Ø 10 mmΔ C/C: ± 20 % of initial value I L ≤ spec. limittan δ ≤ 2 x spec. limitShelf lifeT amb = 105 °C No voltage applied After 1000 hoursAfter test: U R to be applied for 30 minutes 24 to 48 hours before measurementΔ C/C: ± 20 % of initial value I L ≤ spec.limittan δ ≤ 2 x spec. limitDisclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网Document Number: 。

66572资料

April 1996NEC Electronics Inc.A10616EU1V0DS00CMOS-8LHD3.3-Volt, 0.5-Micron CMOS Gate ArraysPreliminary DescriptionNEC's CMOS-8LHD gate-array family combines cell-based-level densities with the fast time-to-market and low development costs of gate arrays. With a unique heterogeneous cell architecture, CMOS-8LHD provides the very dense logic and RAM capabilities required to build devices for fast computer and communications systems.NEC delivers high-speed, 0.5-micron, drawn gate length (Leff=0.35-micron), three-level metal, CMOS technology with an extensive family of macros. I/O macros include GTL, HSTL, and pECL. TTL CMOS I/Os are provided with 5-V tolerance for applications requiring interface to 5-V logic. PCI signaling standards are also supported,including 3.3-V, 66 MHz PCI. The technology is enhanced by a set of advanced features, including phase-locked loops, clock tree synthesis, and high-speed memory. The CMOS-8LHD gate-array family of 3.3-V devices consists of 12 masters, offered in densities of 75K raw gates to 1.123 million raw gates. Usable gates range from 45K to 674K used gates.The gate-array family is supported by NEC's OpenCAD ®design system, a mixture of popular third-party EDA tools,and proprietary NEC tools. NEC proprietary tools include the GALET floorplanner, which helps to reduce design time and improve design speed, and a clock tree synthesis tool that automatically builds a balanced-buffer clock tree to minimize on-chip clock skew.Figure 1. CMOS-8LHD Package Options: BGA & QFPTable 1. CMOS-8LHD Family Features and BenefitsCMOS-8LHD ApplicationsThe CMOS-8LHD family is ideal for use in personal computer systems, engineering workstations, and telecommunications switching and transmission systems, where extensive integration and high speeds are primary design goals. With power dissipation of 0.21 µW/MHz/gate, CMOS-8LHD is also suited for lower-power applications where high performance is required.OpenCAD is a registered trademark of NEC Electronics Inc.CMOS-8LHD2Cell-Based Array ArchitectureThe CMOS-8LHD gate-array family is built with the Cell-Based Array (CBA) architecture licensed from the Silicon Architects Group of Synopsys. CBA architecture uses two types of cells: compute cells and drive cells.This heterogeneous cell architecture enables very high-density design. Compute cells are used to optimize intramacro logic. Drive cells are optimized for intermacro interconnect. The two cell types are also used to build macros with up to three different power/performance/area points.CBA has a rich macrocell library that is optimized for synthesis. RAM blocks are efficiently created from the CBA architecture, using compute cells as memory cores, and sense amplifiers and drive cells as word and address predecoder drivers.As shown in Figure 2, CBA is divided into I/O and array regions. The I/O region contains input and output buffers. The array region contains the gates used to build logic, RAM blocks, and other design features.Power Rail ArchitectureCMOS-8LHD provides additional flexibility for mixedvoltage system designs. As shown in Figure 2, the arrays contain two power rails: a 3.3-V rail, and V DD2.The V DD2 rail is used for interfaces such as 5-V PCI buffers where a clamping diode allows protection for up to an 11-V voltage spike, per the PCI revision 2.1specification.Figure 2. CBA Layout and Cell ConfigurationThe V DD2 rail is separated into sections to give flexibility for including two or more buses requiring special I/O voltage on one device. Each section can operate as an independent voltage zone, and sections can be linked together to form common voltage zones.Packaging and TestNEC utilizes BIST test structures for RAM testing. NEC also offers advanced packaging solutions including Plastic Ball Grid Arrays (PBGA), Plastic Quad Flat Packs (PQFP), and Pin Grid Arrays (PGA). Please call your local NEC ASIC design center representative for a listing of available master/package combinations.PublicationsThis data sheet contains preliminary specifications for the CMOS-8LHD gate-array family. Additional infor-mation will be available in NEC's CMOS-8LHD Block Library and CMOS-8LHD Design Manual . Call your local NEC ASIC design center representative or the NEC literature line for additional ASIC design information; see the back of this data sheet for locations and phone numbers.Table 2. CMOS-8LHD Base Array Line-upDevice Raw Gates Used Gates (1)Total Pads66562750404502416466563997925987518866565125216751292126656617963210777925266568202400121440268665692681281608763086657029792017875232466571359744215845356665725008643005184206657362054437232646866575802240481344532(1) Actual gate utilization varies depending on circuit implementation.Utilization is 60% for 3LM.3CMOS-8LHDInput/Output CapacitanceV DD =V I =0-V; f =1 MHzTerminal Symbol Typ Max Unit Input C IN 1020pF Output C OUT 1020pF I/OC I/O1020pF(1)Values include package pin capacitancePower ConsumptionDescription Limits Unit Internal gate (1)0.21µW/MHz Input buffer 2.546µW/MHz Output buffer10.60µW/MHzAbsolute Maximum RatingsPower supply voltage, V DD –0.5 to +4.6-VInput voltage, V I3.3-V input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 3.3-V fail-safe input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 5 V-tolerant (at V I < V DD + 3.0-V)–0.5 to +4.6-V Output Voltage, V O3.3-V output buffer (at V O < V DD + 0.5-V)–0.5 to +4.6-V 5-V-tolerant output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-V 5-V open-drain output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-VLatch-up current, I LATCH >1 A (typ)Operating temperature, T OPT –40 to +85°C Storage temperature, T STG–65 to +150°C (1) Assumes 30% internal gate switching at one timeCaution: Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.Recommended Operating ConditionsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C3.3-V Interface 5-V Interface5-V PCI 3.3-V PCIBlock BlockLevel LevelParameterSymbol Min Max Min Max Min Max Min Max Unit I/O power supply voltage V DD 3.0 3.6 3.0 3.6 3.0 5.5 3.0 3.6V Junction temperature T J 0+1000+1000+1000+100°C High-level input voltage V IH 2.0V DD 2.0 5.5 2.0V CC 0.5 V CCV CC V Low-level input voltage V IL 00.800.800.800.3 V CCV Positive trigger voltage V P 1.50 2.70 1.50 2.70————V Negative trigger voltage V N 0.60 1.60.60 1.6————V Hysteresis voltage V H 1.10 1.3 1.10 1.3————V Input rise/fall time t R , t F 0200020002000200ns Input rise/fall time, Schmittt R , t F1010————nsAC CharacteristicsV DD = 3.3-V ±0.3-V; T j = –40 to +125°C ParameterSymbol MinTypMax Unit Conditions Toggle frequency (F611)f TOG356MHzD-F/F; F/O = 2 mmDelay time2-input NAND (F322)t PD181ps F/O = 1; L = 0 mmt PD 186ps F/O = 2; L = typ (0.42 mm)Flip-flop (F611)t PD 573ps F/O = 1; L = 0 mm t PD 688ps F/O = 2; L = typ t SETUP 410ps —t HOLD 540ps —Input buffer (FI01)t PD 268ps F/O = 1; L = 0 mm t PD 312ps F/O = 2; L = typ Output buffer (9 mA) 3.3-V (FO01)t PD 1.316ns C L = 15 pF Output buffer (9 mA) 5-V-tolerant (FV01)t PD 1.228ns C L = 15 pF Output buffer (9 mA) 5-V-swing (FY01)t PD 1.517ns C L = 15 pF Output rise time (9 mA) (FO01)t R 1.347ns C L = 15 pF Output fall time (9 mA) (FO01)t F1.284nsC L = 15 pFCMOS-8LHD4(3)Rating is for only one output operating in this mode for less than 1 second.(4)Normal type buffer: I OH < I OL .(5)Balanced buffer: I OH = I OL .(6)Resistor is called 50ký to maintain consistency with previous families.Notes:(1)Static current consumption increases if an I/O block with on-chip pull-up/pull-down resistor or an oscillator is used. Call an NEC ASIC design center repre-sentative for assistance in calculation.(2)Leakage current is limited by tester capabilities. Specification listed representsthis measurement limitation. Actual values will be significantly lower.DC CharacteristicsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C ParameterSymbol Min Typ Max Unit Conditions Quiescent current (1)µPD66578I DDS 2.0300µA V I = V DD or GND µPD66575, 66573, 66572I DDS 1.0300µA V I = V DD or GND Remaining mastersI DDS 0.5200µA V I = V DD or GND Off-state output leakage current3.3-V buffers, 3.3-V PCII OZ ±10µA V O = V DD or GND 5-V-tolerant buffers, 5-V PCI I OZ ±14µA V O = V DD or GND 5-V open-drainI OZ ±14µA V O = V DD or GND Output short circuit current (3)I OS –250mA V O = GND Input leakage current (2)5-V PCI I IH +70, –70µA V IN = 2.7-V, 0.5-V 3.3-V PCI I I ±10µA V IN = V DD or GND RegularI I ±10–5±10µA V I = V DD or GND 50 k Ω pull-up I I –180–40µA V I = GND 5 k Ω pull-up I I –1400–350mA V I = GND 50 k Ω pull-down I I 30160µA V I = V DDResistor values50 k Ω pull-up (6)R pu 2075k Ω5 k Ω pull-upR pu 2.68.6k Ω50 k Ω pull-down (6)R pu 22.5100k ΩInput clamp voltageV IC –1.2V I I = 18 mA Low-level output current (ALL buffer types)3 mA I OL 3mA V OL = 0.4-V 6 mA I OL 6mA V OL = 0.4-V 9 mA I OL 9mA V OL = 0.4-V 12 mA I OL 12mA V OL = 0.4-V 18 mA I OL 18mA V OL = 0.4-V 24 mAI OL 24mA V OL = 0.4-V High-level output current (5-V-tolerant block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –3mA V OH = V DD –0.4-V 9 mA I OH –3mA V OH = V DD –0.4-V 12 mA I OH –3mA V OH = V DD –0.4-V 18 mA I OH –4mA V OH = V DD –0.4-V 24 mAI OH –4mA V OH = V DD –0.4-V High-level output current (3.3-V interface block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –6mA V OH = V DD –0.4-V 9 mA I OH –9mA V OH = V DD –0.4-V 12 mA I OH –12mA V OH = V DD –0.4-V 18 mA I OH -18mA V OH = V DD –0.4-V 24 mAI OH -24mA V OH = V DD –0.4-V Output voltage (5-V PCI)High-level output voltage V OH 2.4mA I OH = 2 mALow-level output voltage V OL 0.55mA I OL = 3 mA, 6 mA Output voltage (3.3-V PCI)High-level output voltage V OH 0.9 V DDmA I OH = 500 µA Low-level output voltage V OL 0.1 V DDmA I OL = 1500 µA Low-level output voltageV OL 0.1V I OL = 0 mA High-level output voltage, 5-V TTL V OH V DD –0.2V I OL = 0 mA High-level output voltage, 3.3-VV OHV DD –0.1VI OH = 0 mACMOS-8LHD5CMOS-8LHD6Document No. A10616EU1V0DS00For literature, call toll-free 7 a.m. to 6 p.m. Pacific time: 1-800-366-9782or FAX your request to: 1-800-729-9288©1996 NEC Electronics Inc./Printed in U.S.A.NEC ASIC DESIGN CENTERSWEST•3033 Scott Boulevard Santa Clara, CA 95054TEL 408-588-5008FAX 408-588-5017•One Embassy Centre9020 S.W. Washington Square Road,Suite 400Tigard, OR 97223TEL 503-671-0177FAX 503-643-5911THIRD-PARTY DESIGN CENTERSSOUTH CENTRAL/SOUTHEAST•Koos Technical Services, Inc.385 Commerce Way, Suite 101Longwood, FL 32750TEL 407-260-8727FAX 407-260-6227•Integrated Silicon Systems Inc.2222 Chapel Hill Nelson Highway Durham, NC 27713TEL 919-361-5814FAX 919-361-2019•Applied Systems, Inc.1761 W. Hillsboro Blvd., Suite 328Deerfield Beach, FL 33442TEL 305-428-0534FAX 305-428-5906NEC Electronics Inc.CORPORATE HEADQUARTERS2880 Scott Boulevard P.O. Box 58062Santa Clara, CA 95052TEL 408-588-6000No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. ALL DEVICES SOLD BY NECEL ARE COVERED BY THE PROVISIONS APPEARING IN NECEL TERMS AND CONDITIONS OF SALES ONLY. INCLUDING THE LIMITATION OF LIABILITY,WARRANTY, AND PATENT PROVISIONS. NECEL makes no warranty, express, statutory, implied or by description, regarding informa-tion set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems,aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. “Standard” quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools,industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliabilty requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death.If customers wish to use NECEL devices in applications not intended by NECEL, customer must contact the responsible NECEL sales people to determine NECEL’s willingness to support a given application.SOUTH CENTRAL/SOUTHEAST•16475 Dallas Parkway, Suite 380Dallas, TX 75248TEL 972-735-7444FAX 972-931-8680•Research Triangle Park2000 Regency Parkway, Suite 455Cary, NC 27511TEL 919-460-1890FAX 919-469-5926•Two Chasewood Park 20405 SH 249, Suite 580Houston, TX 77070TEL 713-320-0524FAX 713-320-0574NORTH CENTRAL/NORTHEAST•The Meadows, 2nd Floor 161 Worcester Road Framingham, MA 01701TEL 508-935-2200FAX 508-935-2234•Greenspoint Tower2800 W. Higgins Road, Suite 765Hoffman Estates, IL 60195TEL708-519-3945FAX 708-882-7564。

CR6850中文版技术设计指导书

9、CRM 工作模式:

在轻载或空载时,CR6850C 进入 CRM 工作模式,工作频率降低。频率的变化由取自电压反馈环的反馈电 压控制,当反馈电压低于内部门限电压时,振荡器频率线性减小到最小绿色工作频率,约 22KHz 左右 (RI=100KΩ) 。在此振荡频率工作时,MOSFET 的开关损耗和磁芯、电感、吸收电路等各部分的损耗均减小, 从而减小了总损耗。在正常工作或重载时,PWM 频率增大到最大工作频率,约 67kHz 左右(RI=100KΩ) ,工 作频率不受绿色工作模式的影响。

管脚信息: 管脚信息:

典型应用电路图: 典型应用电路图:

CR6850C 应用指导书

一、芯片工作原理

1.功能概述:

CR6853 是用于 36W 以内离线式开关电源 IC,其高集成度,低功耗的电流模 PWM 控制芯片,该芯片适用 于离线式 AC-DC 反激拓扑的小功率电源模块。芯片可以通过外接电阻改变工作频率;在轻载和无负载情况 下自动进入 PFM 和 CRM,这样可以有效减小电源模块的待机功耗,达到绿色节能的目的。CR6850C 具有很低 的启动电流,因此可以采用一个 2 兆欧姆的启动电阻。为了提高系统的稳定性,防止次谐波振荡, CR6850C 内置了同步斜坡补偿电路;而动态峰值限制电路减小了在宽电压输入(90V~264V)时最大输出功率的变化; 内置的前沿消隐电路可以消除开关管每次开启产生的干扰。CR6850C 内置了多种保护功能:过压保护 、逐 周期峰值电流限制、欠压锁定(可以用它实现短路和过流保护)以及输出驱动的高电平钳位在 16.8V 以下。 而驱动输出采用的图腾柱和软驱动有效降低了开关噪声。 CR6850C 提供 SOT23-6L, SOT-8 和 DIP-8 无铅封装。 由于 CR6850C 高度集成,使用外围元件较少。采用 CR6850C 可以简化反激式隔离 AC-DC 开关电源设计, 从而使设计者轻松的获得可靠的系统。

CR6855 电源IC规格书

满足能源之星EPS 2.0版VI级能效标准

应用领域:

电池充电器 数码产品适配器

AC-DC电源适配器 PC、TV辅助电源 开放式电源

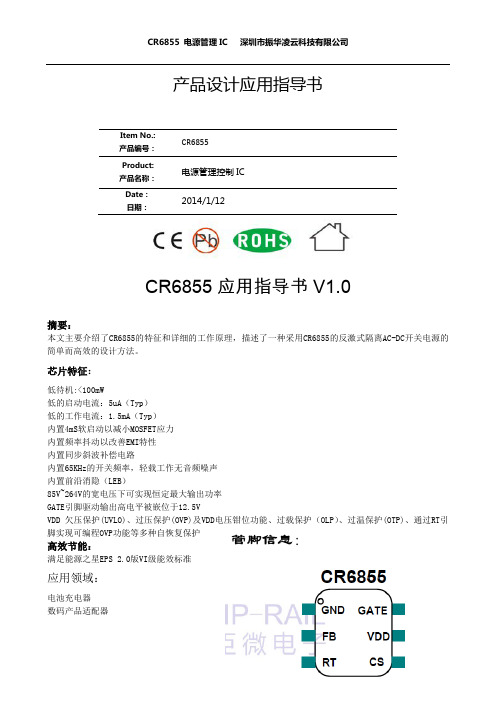

CR6855 电源管理 IC 深圳市振华凌云科技有限公司

一、芯片工作原理

1.功能概述:

CR6855是用于40W以内离线式开关电源IC,该IC具有优化的图腾驱动电路以及电流模式PWM控制器。PWM 控制器包含65KHz固定的频率振荡发生器以及各种保护。由振荡电路产生的频率抖动,可以改善EMI特性。 为了获得良好的效率和待机功耗,CR6855在重载或中等负载时,工作在PWM模式,频率为65KHz。当负载 逐渐减小时,振荡器的工作频率逐渐降低,最后稳定在22KHz左右。在空载和轻载时,电路采用间歇开关 模式,有效的降低了待机功耗,达到绿色节能的目的。CR6855具有很低的启动电流,若采用整流桥前启动, 可以使待机功耗降至100mW以内,满足能源之星EPS 2.0版VI级能效标准。为了提高系统的稳定性,防止 次谐波振荡,CR6855内置了同步斜坡补偿电路、内置恒定功率补偿电路,减小了在宽电压输入(85V~264V) 时最大输出功率的变化、内置的前沿消隐电路可以屏蔽开关管每次开启产生的干扰。CR6855内置了多种保 护功能:VDD 欠压保护(UVLO)、过压保护(OVP)及VDD电压钳位功能、过载保护(OLP)、外置可调过温保护 (OTP)、通过RT引脚实现可编程OVP功能,各种保护解除后均可自动恢复工作,以及输出驱动的高电平被嵌 位于12.5V以下。而驱动输出采用的图腾柱和软驱动,有效降低了开关噪声。 由于CR6855高度集成,使用外围元件较少。采用CR6855可简化反激式隔离AC-DC开关电源设计,从而使设 计者轻松的获得可靠的系统。

二、应用指导

TDA4685中文资料

元器件交易网

Philips Semiconductors

Product specification

Video processor with automatic cut-off control

FEATURES • Operates from an 8 V DC supply • Black level clamping of the colour difference, luminance and RGB input signals with coupling-capacitor DC level storage • Two analog RGB inputs, selected either by fast switch signals or via I2C-bus; brightness and contrast control of both RGB inputs • Saturation, contrast, brightness and white adjustment via I2C-bus • Same RGB output black levels for Y/CD and RGB input signals • Timing pulse generation from either a 2 or 3-level sandcastle pulse for clamping, vertical synchronization and cut-off timing pulses • Automatic cut-off control or clamped output selectable via I2C-bus • Automatic cut-off control with picture tube leakage current compensation • Cut-off measurement pulses after end of the vertical blanking pulse or end of an extra vertical flyback pulse • Two switch-on delays to prevent discolouration before steady-state operation • Average beam current and peak drive limiting • PAL/SECAM or NTSC matrix selection via I2C-bus • Emitter-follower RGB output stages to drive the video output stages • I2C-bus controlled DC output e.g. for hue-adjust of NTSC (multistandard) decoders. GENERAL DESCRIPTION The TDA4685 is a monolithic integrated circuit with a luminance and a colour difference interface for video processing in TV receivers. Its primary function is to process the luminance and colour difference signals from a colour decoder which is equipped e.g. with the multistandard decoder TDA4655 or TDA9160 plus delay line TDA4661 and the Picture Signal Improvement (PSI) IC, TDA467X, or from a feature module. ORDERING INFORMATION PACKAGE TYPE NUMBER NAME TDA4685 DIP28 DESCRIPTION plastic dual in-line package; 28 leads (600 mil) The required input signals are:

at89c1051中文资料

ØÙÚVk)Il rÛÁÜÃ ±´Î !ÛÁÜÃ ±´Î ÝÞßJàáV»ÒÓ

Ô Ð XÁÂâ ã äå £æ±

ç{»¼½ ¾¿À è Ð XÈÉÜ \zÁÜà èÈÉ Ð¤£ Ф¥ (zÁÜ{éáVÓ

\ ØêëVÒÓ

RS¨©

w yô|}áV$% õö 8ô|}áV di ëz:ôJ

2(. /45 ^5 {³ |2à}ÒO45IJìÜ45\~3454i{³ PJ; à2( N Z=*!IJ¨© èÏ2(45.¨©PJ

ÆÇ

www.tai-yan.co ÈÉ?ÊË m §ÌÌ

·

/b ÍÎÀ Ï bs Ð X Ð X^Ñ ¯ f_ ´µ¶ X Ф£ Ф¥ DEVÒÓ

wK&Vj452(ÒOk^^l rl eÂZ=*f8cÈmôghÂi tú:b2(

6n&cd:op23:bqrsÏ.

w ÛO45 $%

t RSV$% :l uvw*xfúV

电子器件采购平台: IC资料查询网站: 电子工程技术论坛:/bbs

# ( ÈÉU^ 2VÏ.]$ ® X#Q^WðñRS # »¼ |êeV>$%# ®)ô»îï ®)îï93 îï!Ü v\ï½

X

ê

t mn àgz\ }ZW ¡¢PÒ

W ¡¢B & Wmn\p¡¢

v è

ai

CMBA857中文资料

PNP EPITAXIAL PLANAR SILICON TRANSISTORCMBA857 SOT23MARKING : AS BELOWABSOLUTE MAXIMUM RATINGS DESCRIPTIONSYMBOL VALUE UNIT Collector -Base VoltageVCBO 60V Collector -Emitter VoltageVCEO 50V Emitter Base VoltageVEBO 6.0V Collector CurrentIC 200mA Collector Power DissipationPC 200mW Junction TemperatureTj 125deg C Storage TemperatureTstg -55 to +125deg CELECTRICAL CHARACTERISTICS (Ta=25 deg C unless otherwise specified)DESCRIPTION SYMBOL TEST CONDITION MIN TYPMAX UNIT Collector -Emitter VoltageVCEO IC=100uA, IB=050--V Collector Cut off CurrentICBO VCB=60V, IE=0--100nA Emitter Cut off CurrentIEBO VEB=6V, IC=0--100nADC Current GainhFE(1)IC=1mA,VCE=6V 150-500hFE(2)IC=0.1mA,VCE=6V 90--Collector Emitter Saturation VoltageVCE(Sat)IC=100mA,IB=10mA --0.30VBase Emitter Saturation VoltageVBE(Sat)IC=100mA,IB=10mA -- 1.0V Dynamic CharacteristicsTransition Frequencyft VCE=6V,IC=10mA,-200-MHz Collector Output CapacitanceCob VCB=6V, IE=0- 4.0-pF f=1MHzNoise FigureNF VCE=6V, IE=0.3mA --20dBf=100Hz, Rg=10kohmsCLASSIFICATION E F hFE(1)150-300250-500MARKING PAPBPIN CONFIGURATION (PNP)1 = BASE2 = EMITTER3 = COLLECTOR213Continental Device India LimitedAn ISO/TS 16949, ISO 9001 and ISO 14001 Certified CompanyTape Specification for SOT-23 Surface Mount DeviceSOT-23 Package Reel InformationReel specifications for W" Packing (13" reel)SOT-23 Formed SMD PackageSOT-23 T&R3K/reel 10K/reel136 gm/3K pcs 415 gm/10K pcs3" x 7.5" x 7.5"9" x 9" x 9"13" x 13" x 0.5"12.0K 51.0K 10.0K17" x 15" x 13.5"19" x 19" x 19"17" x 15" x 13.5"192.0K 408.0K 300.0K12 kgs 28 kgs 16 kgsPACKAGENet Weight/Qty DetailsSTANDARD PACKINNER CARTON BOXQty OUTER CARTON BOXQty Gr Wt SizeSizePacking Detailø329.2±0.5 / 178 ±0.514.47.9 – 10.9T R A I L E RF I X I NG T A P EL E A D E R9.2±0.5MAXø100.0±0.5 / 54.5 ±0.5ø2.0±0.5ø20.2 MINDETAIL Xø13.0+0.5–0.2All dimensions in m m330 / 180 mm – Antistatic Coated Plastic ReelNOTES:No. of Devices8m m Tape Size of Reel 330 mm (13")10,000 Pcs8m m Tape Size of Reel 180 mm (7")3,000 PcsThe bandolier of 330 mm reel contains at least 10,000 devices.The bandolier of 180 mm reel contains at least 3,000 devices.No m ore than 0.5% missing devices / reel. 50 empty compartm ents for 330 mm reel. 15 em pty com partments for 180 m m reel.Three consecutive empty places m ight be found provided this gap is followed by 6 consecutive devices.The carrier tape (leader) starts with at least 75 em pty positions (equivalent to 330 m m). In order to fix the carrier tape a self adhesive tape of 20 to 50 m m is applied. At the end of the bandolier at least 40 em pty positions (equivalent to 160 m m) are there.180or 3301.2.3.4.5.±±0.1All dimensions inmm±0.01±0.025NotesDisclaimerThe product information and the selection guides facilitate selection of the CDIL's Discrete Semiconductor Device(s)best suited for application in your product(s)as per your requirement.It is recommended that you completely review our Data Sheet(s)so as to confirm that the Device(s)meet functionality parameters for your application.The information furnished on the CDIL Web Site/CD is believed to be accurate and reliable.CDIL however,does not assume responsibility for inaccuracies or incomplete information.Furthermore,CDIL does not assume liability whatsoever,arising out of the application or use of any CDIL product; neither does it convey any license under its patent rights nor rights of others.These products are not designed for use in life saving/support appliances or systems.CDIL customers selling these products(either as individual Discrete Semiconductor Devices or incorporated in their end products),in any life saving/support appliances or systems or applications do so at their own risk and CDIL will not be responsible for any damages resulting from such sale(s).CDIL strives for continuous improvement and reserves the right to change the specifications of its products without prior notice.CDIL is a registered Trademark ofContinental Device India LimitedC-120 Naraina Industrial Area, New Delhi 110 028, India.Telephone + 91-11-579 6150 Fax + 91-11-579 9569, 579 5290e-mail sales@ 。

97105系列海隆防爆电磁阀

工作温度:

阀: -40°C ... +65°C (NBR), -25°C ... +80°C (HNBR) (取决于电磁线圈系统) 电磁线圈: 详见电磁线圈表 在+2°C以下使用时要保证 供气干燥以防结冰

材料

阀体: 不锈钢 1.4404/316, 黄铜 2.0401, 阳极氧化铝 3.0615 密封件: NBR (特殊丁腈橡胶)

技术参数

介质:

经过滤的,非润滑干燥的压缩空 气,仪表用空气,氮气或其他非 易燃中性干燥流体

工作方式:

先导电磁控制滑阀

安装位置:

任意,双电控建议水平安装

Approved

通径:

DN 6 mm, DN 8 mm

接口尺寸:

G 1/4, 1/4 NPT, G 1/2, 1/2 NPT

工作压力:

2,5 ... 8 bar 内部供气 0 ... 8 bar 外部供气

流量 (l/min) 1300 1300 2600 2600 1300 1300 2600 2600 1300 1300

重量 (kg) 0,5 0,5 0,5 0,5 0,7 0,7 0,7 0,7 0,7 0,7

图号 No. 1 1 2 2 3 3 4 4 5 5

型号*1) 9713535 9713545 9713555 9713565 9710535 9710545 9710555 9710565 9711535 9711545

513 4 2 4 2 513

阀体: 不锈钢

4

513 2

符号

513 2 1 2 4 1 3 513 2 4 2 4 1 2 3 513 2 3

流量 (l/min) 1300 1300 2600 2600 1300 1300 2600 2600 1300 1300

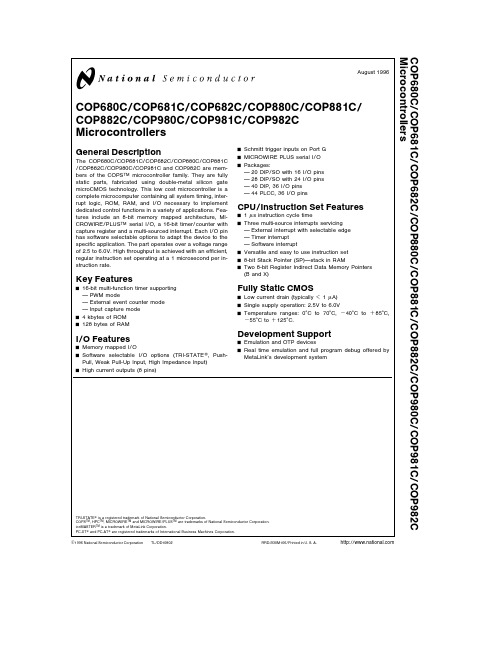

COP682C资料