Hardware Accelerated Rendering of Emissive Volumes

Tektronix MDO3000 Series 数字多功能作业仪用户指南说明书

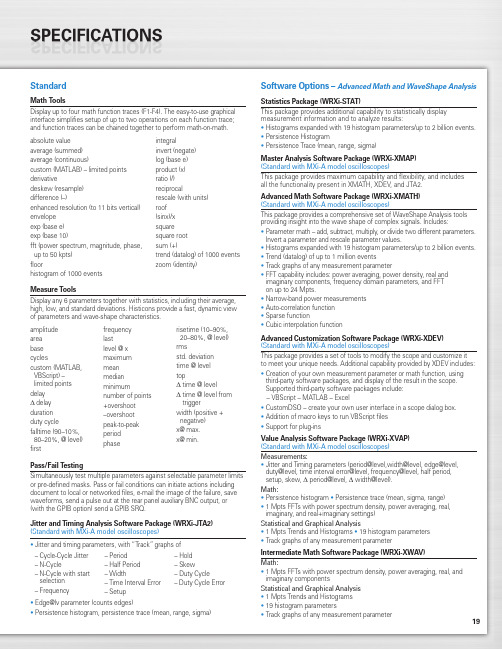

19StandardMath ToolsDisplay up to four math function traces (F1-F4). The easy-to-use graphical interface simplifies setup of up to two operations on each function trace;and function traces can be chained together to perform math-on-math.absolute value integralaverage (summed)invert (negate)average (continuous)log (base e)custom (MATLAB) – limited points product (x)derivativeratio (/)deskew (resample)reciprocaldifference (–)rescale (with units)enhanced resolution (to 11 bits vertical)roof envelope (sinx)/x exp (base e)square exp (base 10)square root fft (power spectrum, magnitude, phase,sum (+)up to 50 kpts) trend (datalog) of 1000 events floorzoom (identity)histogram of 1000 eventsMeasure ToolsDisplay any 6 parameters together with statistics, including their average,high, low, and standard deviations. Histicons provide a fast, dynamic view of parameters and wave-shape characteristics.Pass/Fail TestingSimultaneously test multiple parameters against selectable parameter limits or pre-defined masks. Pass or fail conditions can initiate actions including document to local or networked files, e-mail the image of the failure, save waveforms, send a pulse out at the rear panel auxiliary BNC output, or (with the GPIB option) send a GPIB SRQ.Jitter and Timing Analysis Software Package (WRXi-JTA2)(Standard with MXi-A model oscilloscopes)•Jitter and timing parameters, with “Track”graphs of •Edge@lv parameter (counts edges)• Persistence histogram, persistence trace (mean, range, sigma)Software Options –Advanced Math and WaveShape AnalysisStatistics Package (WRXi-STAT)This package provides additional capability to statistically display measurement information and to analyze results:• Histograms expanded with 19 histogram parameters/up to 2 billion events.• Persistence Histogram• Persistence Trace (mean, range, sigma)Master Analysis Software Package (WRXi-XMAP)(Standard with MXi-A model oscilloscopes)This package provides maximum capability and flexibility, and includes all the functionality present in XMATH, XDEV, and JTA2.Advanced Math Software Package (WRXi-XMATH)(Standard with MXi-A model oscilloscopes)This package provides a comprehensive set of WaveShape Analysis tools providing insight into the wave shape of complex signals. Includes:•Parameter math – add, subtract, multiply, or divide two different parameters.Invert a parameter and rescale parameter values.•Histograms expanded with 19 histogram parameters/up to 2 billion events.•Trend (datalog) of up to 1 million events•Track graphs of any measurement parameter•FFT capability includes: power averaging, power density, real and imaginary components, frequency domain parameters, and FFT on up to 24 Mpts.•Narrow-band power measurements •Auto-correlation function •Sparse function• Cubic interpolation functionAdvanced Customization Software Package (WRXi-XDEV)(Standard with MXi-A model oscilloscopes)This package provides a set of tools to modify the scope and customize it to meet your unique needs. Additional capability provided by XDEV includes:•Creation of your own measurement parameter or math function, using third-party software packages, and display of the result in the scope. Supported third-party software packages include:– VBScript – MATLAB – Excel•CustomDSO – create your own user interface in a scope dialog box.• Addition of macro keys to run VBScript files •Support for plug-insValue Analysis Software Package (WRXi-XVAP)(Standard with MXi-A model oscilloscopes)Measurements:•Jitter and Timing parameters (period@level,width@level, edge@level,duty@level, time interval error@level, frequency@level, half period, setup, skew, Δ period@level, Δ width@level).Math:•Persistence histogram •Persistence trace (mean, sigma, range)•1 Mpts FFTs with power spectrum density, power averaging, real, imaginary, and real+imaginary settings)Statistical and Graphical Analysis•1 Mpts Trends and Histograms •19 histogram parameters •Track graphs of any measurement parameterIntermediate Math Software Package (WRXi-XWAV)Math:•1 Mpts FFTs with power spectrum density, power averaging, real, and imaginary componentsStatistical and Graphical Analysis •1 Mpts Trends and Histograms •19 histogram parameters•Track graphs of any measurement parameteramplitude area base cyclescustom (MATLAB,VBScript) –limited points delay Δdelay duration duty cyclefalltime (90–10%, 80–20%, @ level)firstfrequency lastlevel @ x maximum mean median minimumnumber of points +overshoot –overshoot peak-to-peak period phaserisetime (10–90%, 20–80%, @ level)rmsstd. deviation time @ level topΔ time @ levelΔ time @ level from triggerwidth (positive + negative)x@ max.x@ min.– Cycle-Cycle Jitter – N-Cycle– N-Cycle with start selection – Frequency– Period – Half Period – Width– Time Interval Error – Setup– Hold – Skew– Duty Cycle– Duty Cycle Error20WaveRunner WaveRunner WaveRunner WaveRunner WaveRunner 44Xi-A64Xi-A62Xi-A104Xi-A204Xi-AVertical System44MXi-A64MXi-A104MXi-A204MXi-ANominal Analog Bandwidth 400 MHz600 MHz600 MHz 1 GHz 2 GHz@ 50 Ω, 10 mV–1 V/divRise Time (Typical)875 ps500 ps500 ps300 ps180 psInput Channels44244Bandwidth Limiters20 MHz; 200 MHzInput Impedance 1 MΩ||16 pF or 50 Ω 1 MΩ||20 pF or 50 ΩInput Coupling50 Ω: DC, 1 MΩ: AC, DC, GNDMaximum Input Voltage50 Ω: 5 V rms, 1 MΩ: 400 V max.50 Ω: 5 V rms, 1 MΩ: 250 V max.(DC + Peak AC ≤ 5 kHz)(DC + Peak AC ≤ 10 kHz)Vertical Resolution8 bits; up to 11 with enhanced resolution (ERES)Sensitivity50 Ω: 2 mV/div–1 V/div fully variable; 1 MΩ: 2 mV–10 V/div fully variableDC Gain Accuracy±1.0% of full scale (typical); ±1.5% of full scale, ≥ 10 mV/div (warranted)Offset Range50 Ω: ±1 V @ 2–98 mV/div, ±10 V @ 100 mV/div–1 V/div; 50Ω:±400mV@2–4.95mV/div,±1V@5–99mv/div,1 M Ω: ±1 V @ 2–98 mV/div, ±10 V @ 100 mV/div–1 V/div,±10 V @ 100 mV–1 V/div±**********/div–10V/div 1 M Ω: ±400 mV @ 2–4.95 mV/div, ±1 V @5–99 mV/div, ±10 V @ 100 mV–1 V/div,±*********–10V/divInput Connector ProBus/BNCTimebase SystemTimebases Internal timebase common to all input channels; an external clock may be applied at the auxiliary inputTime/Division Range Real time: 200 ps/div–10 s/div, RIS mode: 200 ps/div to 10 ns/div, Roll mode: up to 1,000 s/divClock Accuracy≤ 5 ppm @ 25 °C (typical) (≤ 10 ppm @ 5–40 °C)Sample Rate and Delay Time Accuracy Equal to Clock AccuracyChannel to Channel Deskew Range±9 x time/div setting, 100 ms max., each channelExternal Sample Clock DC to 600 MHz; (DC to 1 GHz for 104Xi-A/104MXi-A and 204Xi-A/204MXi-A) 50 Ω, (limited BW in 1 MΩ),BNC input, limited to 2 Ch operation (1 Ch in 62Xi-A), (minimum rise time and amplitude requirements applyat low frequencies)Roll Mode User selectable at ≥ 500 ms/div and ≤100 kS/s44Xi-A64Xi-A62Xi-A104Xi-A204Xi-A Acquisition System44MXi-A64MXi-A104MXi-A204MXi-ASingle-Shot Sample Rate/Ch 5 GS/sInterleaved Sample Rate (2 Ch) 5 GS/s10 GS/s10 GS/s10 GS/s10 GS/sRandom Interleaved Sampling (RIS)200 GS/sRIS Mode User selectable from 200 ps/div to 10 ns/div User selectable from 100 ps/div to 10 ns/div Trigger Rate (Maximum) 1,250,000 waveforms/secondSequence Time Stamp Resolution 1 nsMinimum Time Between 800 nsSequential SegmentsAcquisition Memory Options Max. Acquisition Points (4 Ch/2 Ch, 2 Ch/1 Ch in 62Xi-A)Segments (Sequence Mode)Standard12.5M/25M10,00044Xi-A64Xi-A62Xi-A104Xi-A204Xi-A Acquisition Processing44MXi-A64MXi-A104MXi-A204MXi-ATime Resolution (min, Single-shot)200 ps (5 GS/s)100 ps (10 GS/s)100 ps (10 GS/s)100 ps (10 GS/s)100 ps (10 GS/s) Averaging Summed and continuous averaging to 1 million sweepsERES From 8.5 to 11 bits vertical resolutionEnvelope (Extrema)Envelope, floor, or roof for up to 1 million sweepsInterpolation Linear or (Sinx)/xTrigger SystemTrigger Modes Normal, Auto, Single, StopSources Any input channel, External, Ext/10, or Line; slope and level unique to each source, except LineTrigger Coupling DC, AC (typically 7.5 Hz), HF Reject, LF RejectPre-trigger Delay 0–100% of memory size (adjustable in 1% increments, or 100 ns)Post-trigger Delay Up to 10,000 divisions in real time mode, limited at slower time/div settings in roll modeHold-off 1 ns to 20 s or 1 to 1,000,000,000 events21WaveRunner WaveRunner WaveRunner WaveRunner WaveRunner 44Xi-A 64Xi-A 62Xi-A104Xi-A 204Xi-A Trigger System (cont’d)44MXi-A64MXi-A104MXi-A204MXi-AInternal Trigger Level Range ±4.1 div from center (typical)Trigger and Interpolator Jitter≤ 3 ps rms (typical)Trigger Sensitivity with Edge Trigger 2 div @ < 400 MHz 2 div @ < 600 MHz 2 div @ < 600 MHz 2 div @ < 1 GHz 2 div @ < 2 GHz (Ch 1–4 + external, DC, AC, and 1 div @ < 200 MHz 1 div @ < 200 MHz 1 div @ < 200 MHz 1 div @ < 200 MHz 1 div @ < 200 MHz LFrej coupling)Max. Trigger Frequency with400 MHz 600 MHz 600 MHz 1 GHz2 GHzSMART Trigger™ (Ch 1–4 + external)@ ≥ 10 mV@ ≥ 10 mV@ ≥ 10 mV@ ≥ 10 mV@ ≥ 10 mVExternal Trigger RangeEXT/10 ±4 V; EXT ±400 mVBasic TriggersEdgeTriggers when signal meets slope (positive, negative, either, or Window) and level conditionTV-Composite VideoT riggers NTSC or PAL with selectable line and field; HDTV (720p, 1080i, 1080p) with selectable frame rate (50 or 60 Hz)and Line; or CUSTOM with selectable Fields (1–8), Lines (up to 2000), Frame Rates (25, 30, 50, or 60 Hz), Interlacing (1:1, 2:1, 4:1, 8:1), or Synch Pulse Slope (Positive or Negative)SMART TriggersState or Edge Qualified Triggers on any input source only if a defined state or edge occurred on another input source.Delay between sources is selectable by time or eventsQualified First In Sequence acquisition mode, triggers repeatedly on event B only if a defined pattern, state, or edge (event A) is satisfied in the first segment of the acquisition. Delay between sources is selectable by time or events Dropout Triggers if signal drops out for longer than selected time between 1 ns and 20 s.PatternLogic combination (AND, NAND, OR, NOR) of 5 inputs (4 channels and external trigger input – 2 Ch+EXT on WaveRunner 62Xi-A). Each source can be high, low, or don’t care. The High and Low level can be selected independently. Triggers at start or end of the patternSMART Triggers with Exclusion TechnologyGlitch and Pulse Width Triggers on positive or negative glitches with widths selectable from 500 ps to 20 s or on intermittent faults (subject to bandwidth limit of oscilloscope)Signal or Pattern IntervalTriggers on intervals selectable between 1 ns and 20 sTimeout (State/Edge Qualified)Triggers on any source if a given state (or transition edge) has occurred on another source.Delay between sources is 1 ns to 20 s, or 1 to 99,999,999 eventsRuntTrigger on positive or negative runts defined by two voltage limits and two time limits. Select between 1 ns and 20 sSlew RateTrigger on edge rates. Select limits for dV, dt, and slope. Select edge limits between 1 ns and 20 s Exclusion TriggeringTrigger on intermittent faults by specifying the normal width or periodLeCroy WaveStream Fast Viewing ModeIntensity256 Intensity Levels, 1–100% adjustable via front panel control Number of Channels up to 4 simultaneouslyMax Sampling Rate5 GS/s (10 GS/s for WR 62Xi-A, 64Xi-A/64MXi-A,104Xi-A/104MXi-A, 204Xi-A/204MXi-A in interleaved mode)Waveforms/second (continuous)Up to 20,000 waveforms/secondOperationFront panel toggle between normal real-time mode and LeCroy WaveStream Fast Viewing modeAutomatic SetupAuto SetupAutomatically sets timebase, trigger, and sensitivity to display a wide range of repetitive signalsVertical Find ScaleAutomatically sets the vertical sensitivity and offset for the selected channels to display a waveform with maximum dynamic range44Xi-A 64Xi-A 62Xi-A104Xi-A 204Xi-A Probes44MXi-A 64MXi-A104MXi-A 204MXi-AProbesOne Passive probe per channel; Optional passive and active probes available Probe System; ProBus Automatically detects and supports a variety of compatible probes Scale FactorsAutomatically or manually selected, depending on probe usedColor Waveform DisplayTypeColor 10.4" flat-panel TFT-LCD with high resolution touch screenResolutionSVGA; 800 x 600 pixels; maximum external monitor output resolution of 2048 x 1536 pixelsNumber of Traces Display a maximum of 8 traces. Simultaneously display channel, zoom, memory, and math traces Grid StylesAuto, Single, Dual, Quad, Octal, XY , Single + XY , Dual + XY Waveform StylesSample dots joined or dots only in real-time mode22Zoom Expansion TracesDisplay up to 4 Zoom/Math traces with 16 bits/data pointInternal Waveform MemoryM1, M2, M3, M4 Internal Waveform Memory (store full-length waveform with 16 bits/data point) or store to any number of files limited only by data storage mediaSetup StorageFront Panel and Instrument StatusStore to the internal hard drive, over the network, or to a USB-connected peripheral deviceInterfaceRemote ControlVia Windows Automation, or via LeCroy Remote Command Set Network Communication Standard VXI-11 or VICP , LXI Class C Compliant GPIB Port (Accessory)Supports IEEE – 488.2Ethernet Port 10/100/1000Base-T Ethernet interface (RJ-45 connector)USB Ports5 USB 2.0 ports (one on front of instrument) supports Windows-compatible devices External Monitor Port Standard 15-pin D-Type SVGA-compatible DB-15; connect a second monitor to use extended desktop display mode with XGA resolution Serial PortDB-9 RS-232 port (not for remote oscilloscope control)44Xi-A 64Xi-A 62Xi-A104Xi-A 204Xi-A Auxiliary Input44MXi-A 64MXi-A104MXi-A 204MXi-ASignal Types Selected from External Trigger or External Clock input on front panel Coupling50 Ω: DC, 1 M Ω: AC, DC, GND Maximum Input Voltage50 Ω: 5 V rms , 1 M Ω: 400 V max.50 Ω: 5 V rms , 1 M Ω: 250 V max. (DC + Peak AC ≤ 5 kHz)(DC + Peak AC ≤ 10 kHz)Auxiliary OutputSignal TypeTrigger Enabled, Trigger Output. Pass/Fail, or Off Output Level TTL, ≈3.3 VConnector TypeBNC, located on rear panelGeneralAuto Calibration Ensures specified DC and timing accuracy is maintained for 1 year minimumCalibratorOutput available on front panel connector provides a variety of signals for probe calibration and compensationPower Requirements90–264 V rms at 50/60 Hz; 115 V rms (±10%) at 400 Hz, Automatic AC Voltage SelectionInstallation Category: 300 V CAT II; Max. Power Consumption: 340 VA/340 W; 290 VA/290 W for WaveRunner 62Xi-AEnvironmentalTemperature: Operating+5 °C to +40 °C Temperature: Non-Operating -20 °C to +60 °CHumidity: Operating Maximum relative humidity 80% for temperatures up to 31 °C decreasing linearly to 50% relative humidity at 40 °CHumidity: Non-Operating 5% to 95% RH (non-condensing) as tested per MIL-PRF-28800F Altitude: OperatingUp to 3,048 m (10,000 ft.) @ ≤ 25 °C Altitude: Non-OperatingUp to 12,190 m (40,000 ft.)PhysicalDimensions (HWD)260 mm x 340 mm x 152 mm Excluding accessories and projections (10.25" x 13.4" x 6")Net Weight7.26kg. (16.0lbs.)CertificationsCE Compliant, UL and cUL listed; Conforms to EN 61326, EN 61010-1, UL 61010-1 2nd Edition, and CSA C22.2 No. 61010-1-04Warranty and Service3-year warranty; calibration recommended annually. Optional service programs include extended warranty, upgrades, calibration, and customization services23Product DescriptionProduct CodeWaveRunner Xi-A Series Oscilloscopes2 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 204Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 1 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 104Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 600 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 64Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 600 MHz, 2 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 62Xi-A(10 GS/s, 25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen Display 400 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 44Xi-A(25 Mpts/Ch in interleaved mode)with 10.4" Color Touch Screen DisplayWaveRunner MXi-A Series Oscilloscopes2 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 204MXi-A(10 GS/s, 25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen Display 1 GHz, 4 Ch, 5 GS/s, 12.5 Mpts/ChWaveRunner 104MXi-A(10 GS/s, 25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen Display 600 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 64MXi-A(10 GS/s, 25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen Display 400 MHz, 4 Ch, 5 GS/s, 12.5 Mpts/Ch WaveRunner 44MXi-A(25 Mpts/Ch in Interleaved Mode)with 10.4" Color Touch Screen DisplayIncluded with Standard Configuration÷10, 500 MHz, 10 M Ω Passive Probe (Total of 1 Per Channel)Standard Ports; 10/100/1000Base-T Ethernet, USB 2.0 (5), SVGA Video out, Audio in/out, RS-232Optical 3-button Wheel Mouse – USB 2.0Protective Front Cover Accessory PouchGetting Started Manual Quick Reference GuideAnti-virus Software (Trial Version)Commercial NIST Traceable Calibration with Certificate 3-year WarrantyGeneral Purpose Software OptionsStatistics Software Package WRXi-STAT Master Analysis Software Package WRXi-XMAP (Standard with MXi-A model oscilloscopes)Advanced Math Software Package WRXi-XMATH (Standard with MXi-A model oscilloscopes)Intermediate Math Software Package WRXi-XWAV (Standard with MXi-A model oscilloscopes)Value Analysis Software Package (Includes XWAV and JTA2) WRXi-XVAP (Standard with MXi-A model oscilloscopes)Advanced Customization Software Package WRXi-XDEV (Standard with MXi-A model oscilloscopes)Spectrum Analyzer and Advanced FFT Option WRXi-SPECTRUM Processing Web Editor Software Package WRXi-XWEBProduct Description Product CodeApplication Specific Software OptionsJitter and Timing Analysis Software Package WRXi-JTA2(Standard with MXi-A model oscilloscopes)Digital Filter Software PackageWRXi-DFP2Disk Drive Measurement Software Package WRXi-DDM2PowerMeasure Analysis Software Package WRXi-PMA2Serial Data Mask Software PackageWRXi-SDM QualiPHY Enabled Ethernet Software Option QPHY-ENET*QualiPHY Enabled USB 2.0 Software Option QPHY-USB †EMC Pulse Parameter Software Package WRXi-EMC Electrical Telecom Mask Test PackageET-PMT* TF-ENET-B required. †TF-USB-B required.Serial Data OptionsI 2C Trigger and Decode Option WRXi-I2Cbus TD SPI Trigger and Decode Option WRXi-SPIbus TD UART and RS-232 Trigger and Decode Option WRXi-UART-RS232bus TD LIN Trigger and Decode Option WRXi-LINbus TD CANbus TD Trigger and Decode Option CANbus TD CANbus TDM Trigger, Decode, and Measure/Graph Option CANbus TDM FlexRay Trigger and Decode Option WRXi-FlexRaybus TD FlexRay Trigger and Decode Physical Layer WRXi-FlexRaybus TDP Test OptionAudiobus Trigger and Decode Option WRXi-Audiobus TDfor I 2S , LJ, RJ, and TDMAudiobus Trigger, Decode, and Graph Option WRXi-Audiobus TDGfor I 2S LJ, RJ, and TDMMIL-STD-1553 Trigger and Decode Option WRXi-1553 TDA variety of Vehicle Bus Analyzers based on the WaveRunner Xi-A platform are available.These units are equipped with a Symbolic CAN trigger and decode.Mixed Signal Oscilloscope Options500 MHz, 18 Ch, 2 GS/s, 50 Mpts/Ch MS-500Mixed Signal Oscilloscope Option 250 MHz, 36 Ch, 1 GS/s, 25 Mpts/ChMS-500-36(500 MHz, 18 Ch, 2 GS/s, 50 Mpts/Ch Interleaved) Mixed Signal Oscilloscope Option 250 MHz, 18 Ch, 1 GS/s, 10 Mpts/Ch MS-250Mixed Signal Oscilloscope OptionProbes and Amplifiers*Set of 4 ZS1500, 1.5 GHz, 0.9 pF , 1 M ΩZS1500-QUADPAK High Impedance Active ProbeSet of 4 ZS1000, 1 GHz, 0.9 pF , 1 M ΩZS1000-QUADPAK High Impedance Active Probe 2.5 GHz, 0.7 pF Active Probe HFP25001 GHz Active Differential Probe (÷1, ÷10, ÷20)AP034500 MHz Active Differential Probe (x10, ÷1, ÷10, ÷100)AP03330 A; 100 MHz Current Probe – AC/DC; 30 A rms ; 50 A rms Pulse CP03130 A; 50 MHz Current Probe – AC/DC; 30 A rms ; 50 A rms Pulse CP03030 A; 50 MHz Current Probe – AC/DC; 30 A rms ; 50 A peak Pulse AP015150 A; 10 MHz Current Probe – AC/DC; 150 A rms ; 500 A peak Pulse CP150500 A; 2 MHz Current Probe – AC/DC; 500 A rms ; 700 A peak Pulse CP5001,400 V, 100 MHz High-Voltage Differential Probe ADP3051,400 V, 20 MHz High-Voltage Differential Probe ADP3001 Ch, 100 MHz Differential Amplifier DA1855A*A wide variety of other passive, active, and differential probes are also available.Consult LeCroy for more information.Product Description Product CodeHardware Accessories*10/100/1000Base-T Compliance Test Fixture TF-ENET-B †USB 2.0 Compliance Test Fixture TF-USB-B External GPIB Interface WS-GPIBSoft Carrying Case WRXi-SOFTCASE Hard Transit CaseWRXi-HARDCASE Mounting Stand – Desktop Clamp Style WRXi-MS-CLAMPRackmount Kit WRXi-RACK Mini KeyboardWRXi-KYBD Removable Hard Drive Package (Includes removeable WRXi-A-RHD hard drive kit and two hard drives)Additional Removable Hard DriveWRXi-A-RHD-02* A variety of local language front panel overlays are also available .† Includes ENET-2CAB-SMA018 and ENET-2ADA-BNCSMA.Customer ServiceLeCroy oscilloscopes and probes are designed, built, and tested to ensure high reliability. In the unlikely event you experience difficulties, our digital oscilloscopes are fully warranted for three years, and our probes are warranted for one year.This warranty includes:• No charge for return shipping • Long-term 7-year support• Upgrade to latest software at no chargeLocal sales offices are located throughout the world. Visit our website to find the most convenient location.© 2010 by LeCroy Corporation. All rights reserved. Specifications, prices, availability, and delivery subject to change without notice. Product or brand names are trademarks or requested trademarks of their respective holders.1-800-5-LeCroy WRXi-ADS-14Apr10PDF。

爱特梅尔maXTouch解决方案助力ASUS Eee Pad Transformer平板电脑触摸屏

包括 奥迪 、 思科 、 用 电气、 克希 010和硬件给予支持。 C D 通 洛 /. S A E是 以开发 应用 ,还 包括对蓝 牙低功耗标准的支持。 德马丁和西 门子在 内的其它全 球领 先企 环境为基础的模型 , 广泛用于航空航天和 而软件包 中包括 支持 B 4O H T .+ S和 B E L 业也都采用 QN X软件来 建立用于 电信 、 国防、 轨道交 通、 能源 以及 重型装 备产 业 的 AP。 、 ra c m 支持 WiF Di c , I4 B o d o —i rt e

包括 医疗 、 汽车和 工业设备 。

一

单 芯 片 B M4 1 2是业 界 首 款 适 用 提高 总体传输质量。 C 3 4 B M4 1 2组合芯 片解决 方案 的其 C 34 展示 了导航系统 、全数字 仪表 盘和 多媒 于 笔 记本 电脑 和上 网本 的 4 n W iF 0 m — i 1QN A 、 ×C R应用 平 台—— 该 演 示 1 E E8 21 n空时 体控 制台的最新进 展 ,其 中包括可 更换 蓝牙组合芯 片。与 B o d o 自 2 0 ra c m 0 8年 他特点包括 : 、提供 lE 0 .1 以 皮肤 的人机界面 、 在线音 乐广播 、 b i 以来交付的、较早 的 IC n e C组合 分组 编码 和 低 密 度 奇 偶 校 验 编码 选 项 , We k t n o crP t 网络 浏览器 以及 与智能手机 、平板 电脑 芯片 相 比 , C 3 4 ra — B M4 1 2进一 步 降低 了功 改进覆盖范围和功率效率 ;采用 B o d 或其 它移 动设备 的互联 互通 。其它 亮点 耗 , c m 的 S r do技术 , o mat i Au 以提供 宽带语 并改进 了共存性。这款 4 n 器件集 0m 包 括 Op n S 和 O e V 的 硬 件 图 成度 很高 , e GLE pn G 丢包 补偿 和 比特 纠错 , 从而极大地 改 占板面积 显著减 小 , 降低 了物 音 、

介绍全息技术英语作文

介绍全息技术英语作文Holographic technology is a cutting-edge innovationthat has revolutionized the way we perceive and interact with visual content. It creates three-dimensional images using light, and has a wide range of applications in various industries, including entertainment, healthcare, education, and more.One of the most exciting aspects of holographic technology is its potential to transform the entertainment industry. With holographic displays, performers can create stunning visual effects and immersive experiences for their audiences. This technology has the power to bring virtual characters and worlds to life in a way that was previously unimaginable.In the field of healthcare, holographic technology is being used to revolutionize medical imaging and training. Doctors can now use holographic images to better understand complex medical conditions, plan surgeries, and educatepatients about their treatment options. This has the potential to improve patient care and outcomes significantly.In the education sector, holographic technology is being used to create immersive learning experiences for students. By using holographic images and simulations, educators can bring abstract concepts to life and make learning more engaging and interactive. This can help students better understand and retain information, leading to improved academic performance.Another exciting application of holographic technology is in the field of design and engineering. Engineers and designers can use holographic images to visualize and manipulate 3D models of their projects, allowing them to make more informed decisions and streamline the design process. This has the potential to improve the efficiency and quality of their work significantly.Overall, holographic technology has the potential to revolutionize the way we interact with visual content invarious industries. Its ability to create immersive and interactive experiences makes it a powerful tool for entertainment, healthcare, education, design, and more. As the technology continues to advance, we can expect to see even more exciting applications and innovations in the future.。

NVIDIA显卡架构简介

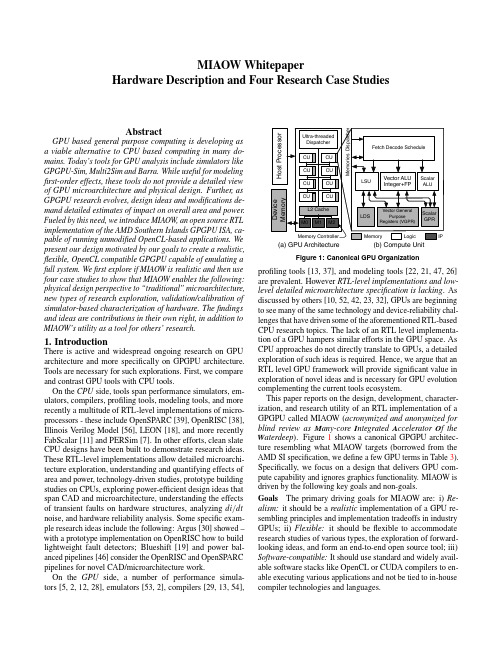

An Introduction to Modern GPU ArchitectureAshu RegeDirector of Developer TechnologyAgenda•Evolution of GPUs•Computing Revolution•Stream Processing•Architecture details of modern GPUsEvolution of GPUs(1995-1999)•1995 –NV1•1997 –Riva 128 (NV3), DX3•1998 –Riva TNT (NV4), DX5•32 bit color, 24 bit Z, 8 bit stencil •Dual texture, bilinear filtering•2 pixels per clock (ppc)•1999 –Riva TNT2 (NV5), DX6•Faster TNT•128b memory interface•32 MB memory•The chip that would not die☺Virtua Fighter (SEGA Corporation)NV150K triangles/sec 1M pixel ops/sec 1M transistors16-bit color Nearest filtering1995(Fixed Function)•GeForce 256 (NV10)•DirectX 7.0•Hardware T&L •Cubemaps•DOT3 –bump mapping •Register combiners•2x Anisotropic filtering •Trilinear filtering•DXT texture compression • 4 ppc•Term “GPU”introducedDeus Ex(Eidos/Ion Storm)NV1015M triangles/sec 480M pixel ops/sec 23M transistors32-bit color Trilinear filtering1999NV10 –Register CombinersInput RGB, AlphaRegisters Input Alpha, BlueRegistersInputMappingsInputMappingsABCDA op1BC op2DAB op3CDRGB FunctionABCDABCDAB op4CDAlphaFunctionRGBScale/BiasAlphaScale/BiasNext Combiner’sRGB RegistersNext Combiner’sAlpha RegistersRGB Portion Alpha Portion(Shader Model 1.0)•GeForce 3 (NV20)•NV2A –Xbox GPU •DirectX 8.0•Vertex and Pixel Shaders•3D Textures •Hardware Shadow Maps •8x Anisotropic filtering •Multisample AA (MSAA)• 4 ppcRagnarok Online (Atari/Gravity)NV20100M triangles/sec 1G pixel ops/sec 57M transistors Vertex/Pixel shadersMSAA2001(Shader Model 2.0)•GeForce FX Series (NV3x)•DirectX 9.0•Floating Point and “Long”Vertex and Pixel Shaders•Shader Model 2.0•256 vertex ops•32 tex+ 64 arith pixel ops •Shader Model 2.0a•256 vertex ops•Up to 512 ops •Shading Languages •HLSL, Cg, GLSLDawn Demo(NVIDIA)NV30200M triangles/sec 2G pixel ops/sec 125M transistors Shader Model 2.0a2003(Shader Model 3.0)•GeForce 6 Series (NV4x)•DirectX 9.0c•Shader Model 3.0•Dynamic Flow Control inVertex and Pixel Shaders1•Branching, Looping, Predication, …•Vertex Texture Fetch•High Dynamic Range (HDR)•64 bit render target•FP16x4 Texture Filtering and Blending 1Some flow control first introduced in SM2.0aFar Cry HDR(Ubisoft/Crytek)NV40600M triangles/sec 12.8G pixel ops/sec 220M transistors Shader Model 3.0 Rotated Grid MSAA 16x Aniso, SLI2004Far Cry –No HDR/HDR ComparisonEvolution of GPUs (Shader Model 4.0)• GeForce 8 Series (G8x) • DirectX 10.0• • • • Shader Model 4.0 Geometry Shaders No “caps bits” Unified ShadersCrysis(EA/Crytek)• New Driver Model in Vista • CUDA based GPU computing • GPUs become true computing processors measured in GFLOPSG80 Unified Shader Cores w/ Stream Processors 681M transistorsShader Model 4.0 8x MSAA, CSAA2006Crysis. Images courtesy of Crytek.As Of Today…• • • • GeForce GTX 280 (GT200) DX10 1.4 billion transistors 576 mm2 in 65nm CMOS• 240 stream processors • 933 GFLOPS peak • 1.3GHz processor clock • 1GB DRAM • 512 pin DRAM interface • 142 GB/s peakStunning Graphics RealismLush, Rich WorldsCrysis © 2006 Crytek / Electronic ArtsHellgate: London © 2005-2006 Flagship Studios, Inc. Licensed by NAMCO BANDAI Games America, Inc.Incredible Physics EffectsCore of the Definitive Gaming PlatformWhat Is Behind This Computing Revolution?• Unified Scalar Shader Architecture• Highly Data Parallel Stream Processing • Next, let’s try to understand what these terms mean…Unified Scalar Shader ArchitectureGraphics Pipelines For Last 20 YearsProcessor per functionVertex Triangle Pixel ROP MemoryT&L evolved to vertex shadingTriangle, point, line – setupFlat shading, texturing, eventually pixel shading Blending, Z-buffering, antialiasingWider and faster over the yearsShaders in Direct3D• DirectX 9: Vertex Shader, Pixel Shader • DirectX 10: Vertex Shader, Geometry Shader, Pixel Shader • DirectX 11: Vertex Shader, Hull Shader, Domain Shader, Geometry Shader, Pixel Shader, Compute Shader • Observation: All of these shaders require the same basic functionality: Texturing (or Data Loads) and Math Ops.Unified PipelineGeometry(new in DX10)Physics VertexFutureTexture + Floating Point ProcessorROP MemoryPixelCompute(CUDA, DX11 Compute, OpenCL)Why Unify?Vertex ShaderPixel ShaderIdle hardwareVertex ShaderIdle hardwareUnbalanced and inefficient utilization in nonunified architectureHeavy Geometry Workload Perf = 4Pixel Shader Heavy Pixel Workload Perf = 8Why Unify?Unified ShaderVertex WorkloadPixelOptimal utilization In unified architectureUnified ShaderPixel WorkloadVertexHeavy Geometry Workload Perf = 11Heavy Pixel Workload Perf = 11Why Scalar Instruction Shader (1)• Vector ALU – efficiency varies • • 4 MAD r2.xyzw, r0.xyzw, r1.xyzw – 100% utilization • • 3 DP3 r2.w, r0.xyz, r1.xyz – 75% • • 2 MUL r2.xy, r0.xy, r1.xy – 50% • • 1 ADD r2.w, r0.x, r1.x – 25%Why Scalar Instruction Shader (2)• Vector ALU with co-issue – better but not perfect • DP3 r2.x, r0.xyz, r1.xyz } 100% • 4 ADD r2.w, r0.w, r1.w • • 3 DP3 r2.w, r0.xyz, r1.xyz • Cannot co-issue • 1 ADD r2.w, r0.w, r2.w • Vector/VLIW architecture – More compiler work required • G8x, GT200: scalar – always 100% efficient, simple to compile • Up to 2x effective throughput advantage relative to vectorComplex Shader Performance on Scalar Arch.Procedural Perlin Noise FireProcedural Fire5 4.5 4 3.5 3 2.5 2 1.5 1 0.5 0 7900GTX 8800GTXConclusion• Build a unified architecture with scalar cores where all shader operations are done on the same processorsStream ProcessingThe Supercomputing Revolution (1)The Supercomputing Revolution (2)What Accounts For This Difference?• Need to understand how CPUs and GPUs differ• Latency Intolerance versus Latency Tolerance • Task Parallelism versus Data Parallelism • Multi-threaded Cores versus SIMT (Single Instruction Multiple Thread) Cores • 10s of Threads versus 10,000s of ThreadsLatency and Throughput• “Latency is a time delay between the moment something is initiated, and the moment one of its effects begins or becomes detectable”• For example, the time delay between a request for texture reading and texture data returns• Throughput is the amount of work done in a given amount of time• For example, how many triangles processed per second• CPUs are low latency low throughput processors • GPUs are high latency high throughput processors•GPUs are designed for tasks that can tolerate latency•Example: Graphics in a game (simplified scenario):•To be efficient, GPUs must have high throughput , i.e. processing millions of pixels in a single frame CPUGenerateFrame 0Generate Frame 1Generate Frame 2GPU Idle RenderFrame 0Render Frame 1Latency between frame generation and rendering (order of milliseconds)•CPUs are designed to minimize latency•Example: Mouse or keyboard input•Caches are needed to minimize latency•CPUs are designed to maximize running operations out of cache •Instruction pre-fetch•Out-of-order execution, flow control• CPUs need a large cache, GPUs do not•GPUs can dedicate more of the transistor area to computation horsepowerCPU versus GPU Transistor Allocation•GPUs can have more ALUs for the same sized chip and therefore run many more threads of computation•Modern GPUs run 10,000s of threads concurrentlyDRAM Cache ALU Control ALUALUALUDRAM CPU GPUManaging Threads On A GPU•How do we:•Avoid synchronization issues between so many threads?•Dispatch, schedule, cache, and context switch 10,000s of threads?•Program 10,000s of threads?•Design GPUs to run specific types of threads:•Independent of each other –no synchronization issues•SIMD (Single Instruction Multiple Data) threads –minimize thread management •Reduce hardware overhead for scheduling, caching etc.•Program blocks of threads (e.g. one pixel shader per draw call, or group of pixels)•Any problems which can be solved with this type of computation?Data Parallel Problems•Plenty of problems fall into this category (luckily ☺)•Graphics, image & video processing, physics, scientific computing, …•This type of parallelism is called data parallelism•And GPUs are the perfect solution for them!•In fact the more the data, the more efficient GPUs become at these algorithms •Bonus: You can relatively easily add more processing cores to a GPU andincrease the throughputParallelism in CPUs v. GPUs•CPUs use task parallelism•Multiple tasks map to multiplethreads•Tasks run different instructions•10s of relatively heavyweight threadsrun on 10s of cores•Each thread managed and scheduledexplicitly•Each thread has to be individuallyprogrammed •GPUs use data parallelism•SIMD model (Single InstructionMultiple Data)•Same instruction on different data•10,000s of lightweight threads on 100sof cores•Threads are managed and scheduledby hardware•Programming done for batches ofthreads (e.g. one pixel shader pergroup of pixels, or draw call)Stream Processing•What we just described:•Given a (typically large) set of data (“stream”)•Run the same series of operations (“kernel”or“shader”) on all of the data (SIMD)•GPUs use various optimizations to improve throughput:•Some on-chip memory and local caches to reduce bandwidth to external memory •Batch groups of threads to minimize incoherent memory access•Bad access patterns will lead to higher latency and/or thread stalls.•Eliminate unnecessary operations by exiting or killing threads•Example: Z-Culling and Early-Z to kill pixels which will not be displayedTo Summarize•GPUs use stream processing to achieve high throughput •GPUs designed to solve problems that tolerate high latencies•High latency tolerance Lower cache requirements•Less transistor area for cache More area for computing units•More computing units 10,000s of SIMD threads and high throughput•GPUs win ☺•Additionally:•Threads managed by hardware You are not required to write code for each thread and manage them yourself•Easier to increase parallelism by adding more processors•So, fundamental unit of a modern GPU is a stream processor…G80 and GT200 Streaming ProcessorArchitectureBuilding a Programmable GPU•The future of high throughput computing is programmable stream processing•So build the architecture around the unified scalar stream processing cores•GeForce 8800 GTX (G80) was the first GPU architecture built with this new paradigmG80 Replaces The Pipeline ModelHost Input Assembler Setup / Rstr / ZCull Geom Thread Issue Pixel Thread Issue128 Unified Streaming ProcessorsSP SP SP SPVtx Thread IssueSPSPSPSPSPSPSPSPSPSPSPSPTFTFTFTFTFTFTFTFL1L1L1L1L1L1L1L1L2 FB FBL2 FBL2 FBL2 FBL2 FBL2Thread ProcessorGT200 Adds More Processing PowerHost CPU System MemoryHost Interface Input Assemble Vertex Work Distribution Geometry Work Distribution Viewport / Clip / Setup / Raster / ZCull Pixel Work Distribution Compute Work DistributionGPUInterconnection Network ROP L2 ROP L2 ROP L2 ROP L2 ROP L2 ROP L2 ROP L2 ROP L2DRAMDRAMDRAMDRAMDRAMDRAMDRAMDRAM8800GTX (high-end G80)16 Stream Multiprocessors• Each one contains 8 unified streaming processors – 128 in totalGTX280 (high-end GT200)24 Stream Multiprocessors• Each one contains 8 unified streaming processors – 240 in totalInside a Stream Multiprocessor (SM)• Scalar register-based ISA • Multithreaded Instruction Unit• Up to 1024 concurrent threads • Hardware thread scheduling • In-order issueTPC I-Cache MT Issue C-CacheSP SP SP SP SP SP SP SPSFU SFU• 8 SP: Thread Processors• IEEE 754 32-bit floating point • 32-bit and 64-bit integer • 16K 32-bit registers• 2 SFU: Special Function Units• sin, cos, log, exp• Double Precision Unit• IEEE 754 64-bit floating point • Fused multiply-add DPShared Memory• 16KB Shared MemoryMultiprocessor Programming Model• Workloads are partitioned into blocks of threads among multiprocessors• a block runs to completion • a block doesn’t run until resources are available• Allocation of hardware resources• shared memory is partitioned among blocks • registers are partitioned among threads• Hardware thread scheduling• any thread not waiting for something can run • context switching is free – every cycleMemory Hierarchy of G80 and GT200• SM can directly access device memory (video memory)• Not cached • Read & write • GT200: 140 GB/s peak• SM can access device memory via texture unit• Cached • Read-only, for textures and constants • GT200: 48 GTexels/s peak• On-chip shared memory shared among threads in an SM• important for communication amongst threads • provides low-latency temporary storage • G80 & GT200: 16KB per SMPerformance Per Millimeter• For GPU, performance == throughput• Cache are limited in the memory hierarchy• Strategy: hide latency with computation, not cache• Heavy multithreading • Switch to another group of threads when the current group is waiting for memory access• Implication: need large number of threads to hide latency• Occupancy: typically 128 threads/SM minimum • Maximum 1024 threads/SM on GT200 (total 1024 * 24 = 24,576 threads)• Strategy: Single Instruction Multiple Thread (SIMT)SIMT Thread Execution• Group 32 threads (vertices, pixels or primitives) into warps• Threads in warp execute same instruction at a time • Shared instruction fetch/dispatch • Hardware automatically handles divergence (branches)TPC I-Cache MT Issue C-CacheSP SP SP SP SP SP SP SPSFU SFU• Warps are the primitive unit of scheduling• Pick 1 of 24 warps for each instruction slot• SIMT execution is an implementation choice• Shared control logic leaves more space for ALUs • Largely invisible to programmerDPShared MemoryShader Branching Performance• G8x/G9x/GT200 branch efficiency is 32 threads (1 warp) • If threads diverge, both sides of branch will execute on all 32 • More efficient compared to architecture with branch efficiency of 48 threadsG80 – 32 pixel coherence 48 pixel coherence 16 14 number of coherent 4x4 tiles 12 10 8 6 4 2 0% 20% 40% 60% 80% 100% 120% PS Branching EfficiencyConclusion:G80 and GT200 Streaming Processor Architecture• Execute in blocks can maximally exploits data parallelism• Minimize incoherent memory access • Adding more ALU yields better performance• Performs data processing in SIMT fashion• Group 32 threads into warps • Threads in warp execute same instruction at a time• Thread scheduling is automatically handled by hardware• Context switching is free (every cycle) • Transparent scalability. Easy for programming• Memory latency is covered by large number of in-flight threads• Cache is mainly used for read-only memory access (texture, constants).。

HARDWARE-ACCELERATED

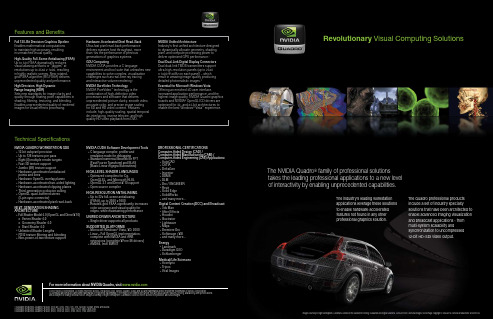

Revolutionary Visual Computing SolutionsHardware-Accelerated Pixel Read-Back Ultra-fast pixel read-back performance delivers massive host throughput, more than 10x the performance of previous generations of graphics systems.GPU ComputingNVIDIA CUDA provides a C languageenvironment and tool suite that unleashes new capabilities to solve complex, visualization challenges such as real-time ray tracing and interactive volume rendering.1NVIDIA PureVideo TechnologyNVIDIA PureVideo ™ technology is the combination of high-definition video processors and software that deliversunprecedented picture clarity, smooth video, accurate color, and precise image scaling for SD and HD video content. Featuresinclude, high-quality scaling, spatial temporal de-interlacing, inverse telecine, and high quality HD video playback from DVD.Features and BenefitsFull 128-Bit Precision Graphics Pipeline Enables mathematical computations to maintain high accuracy, resulting in unmatched visual quality.High-Quality Full-Scene Antialiasing (FSAA)Up to 32x FSAA dramatically reduces visual aliasing artifacts or “jaggies” at resolutions up to 2560 x 1600, resulting in highly realistic scenes. New rotated-grid FSAA algorithm (RG FSAA) delivers unprecedented quality and performance.High Precision, High Dynamic Range Imaging (HDR)Sets new standards for image clarity and quality through floating point capabilities in shading, filtering, texturing, and blending. Enables unprecedented quality of rendered images for visual effects processing.NVIDIA Unified ArchitectureIndustry’s first unified architecture designed to dynamically allocate geometry, shading, pixel, and compute processing power to deliver optimized GPU performance.1Dual Dual-Link Digital Display Connectors Dual dual-link TMDS transmitters support ultra-high-resolution panels (up to 2560 x 1600 @ 60Hz on each panel) − which result in amazing image quality producing detailed photorealistic images.3Essential for Microsoft Windows Vista Offering an enriched 3D user interface,increased application performance, and the highest image quality, NVIDIA Quadro graphics boards and NVIDIA ® OpenGL ICD drivers are optimized for 32- and 64-bit architectures to enable the best Windows ® Vista ™ experience.Technical SpecificationsNVIDIA QUADRO WORKSTATION GPU > 12-bit subpixel precision > Up to 128 textures per pass > Eight (8) multiple render targets > Fast 3D texture support > Jumbo (8K) texture support> Hardware-accelerated antialiased points and lines> Hardware OpenGL overlay planes> Hardware-accelerated two-sided lighting > Hardware-accelerated clipping planes > Third-generation occlusion culling > OpenGL quad-buffered stereo (3-pin sync connector)> Hardware-accelerated pixel read-back NEXT-GENERATION SHADING ARCHITECTURE> Full Shader Model 4.0 (OpenGL and DirectX 10) o Vertex Shader 4.0 o Geometry Shader 4.0 o Pixel Shader 4.0> Unlimited Shader Lengths> FP32 texture filtering and blending > Non-power-of-two texture supportNVIDIA CUDA Software Development Tools > C language compiler, profiler and emulation mode for debugging> Standard numerical libraries for FFT (Fast Fourier Transform) and BLAS (Basic Linear Algegra Subroutines)HIGH-LEVEL SHADER LANGUAGES > Optimized compilers for Cg, OpenGLSL, and Microsoft HLSL > OpenGL 2.1 and DirectX 10 support > Open source compilerHIGH-RESOLUTION ANTIALIASING > Up to 32x full-scene antialiasing (FSAA), up to 2560 x 1600> Rotated-grid FSAA significantly increases color accuracy and visual quality for edges, while maintaining performance UNIFIED DRIVER ARCHITECTURE > Single driver supports all products SUPPORTED PLATFORMS> Microsoft Windows ® Vista, XP, 2000 > Linux—Full OpenGL implementation, complete with NVIDIA and ARBextensions (complete XFree 86 drivers)> AMD64, Intel EM64TPROFESSIONAL CERTIFICATIONS Computer-Aided Design (CAD) /Computer-Aided Manufacturing (CAM) /Computer-Aided Engineering (CAE) Applications > AutoCAD > CATIA > DeltaGen > Inventor > PDMS > PLM> Pro / ENGINEER > Revit> Solid Edge > SolidWorks> and many more…Digital Content Creation (DCC) and Broadcast > 3ds Max > After Effects > Houdini > Illustrator > Lightwave > Maya> Premiere Pro > Softimage | XSI > and many more…Energy> Landmark> Paradigm GEO > Schlumberger Medical/Life Sciences > Accelyris > Tripos> Vital Images1 Available on NVIDIA Quadro FX 5600, 4700 X2, 3700, 1700, 570, 370, 3600M, 1600M, 570M, and 360M.2 Available on NVIDIA Quadro FX 5600, 5500, 4700 X2, 4600, 4500, 3700, 3500, and 3450.3 Available on NVIDIA Quadro FX 5600, 5500, 4700 X2, 4600, 3700, 3500, 1700, and 1500.For more information about NVIDIA Quadro, visit © 2007 NVIDIA Corporation. All rights reserved. NVIDIA, the NVIDIA logo, NVIDIA Quadro, Cuda, and SLI are trademarks and/or registered trademarks of NVIDIA Corporation.All company and product names are trademarks or registered trademarks of the respective owners with which they are associated. Features, pricing, availability, and specifications are all subject to change without notice. Images courtesy of Right Hemisphere, Landmark, UVPHACTORY, NVIDIA Corporation, and Vital Images,The industry’s leading workstation applications leverage these solutions to enable hardware-accelerated features not found in any other professional graphics solution.The Quadro professional products include a set of industry specialtysolutions that have been architected to enable advanced imaging visualization and broadcast applications - from multi-system scalability andsynchronization to uncompressed 12-bit HD-SDI video output.The NVIDIA Quadro ® family of professional solutionstakes the leading professional applications to a new level of interactivity by enabling unprecedented capabilities.Images courtesy of Right Hemisphere, Landmark, a brand of the Halliburton Drilling, Evaluation and Digital Solutions, UVPHACTORY, and Vital Images, Volvo Image Copyright © 2006 MFX / Percival Productions. www.mfx.se.NVIDIA Quadro Family | Sep 2007Ground-breaking Unified Architecture Delivers Unprecedented Performance The latest NVIDIA Quadro architecture takes application performance tonew levels by featuring the industry’sfirst unified architecture1. Designed to dynamically allocate geometry, shading, pixel, and compute processing power, the latest NVIDIA Quadro graphics boards deliver optimized Graphics Processing Unit (GPU) performance. The GPU pipeline efficiency is further multipliedby fast 3D and large texture transfers, NVIDIA’s crossbar memory architecture, enabling occlusion culling, lossless depth Z-buffer, and color compression. These elements combine to achieveunprecedented 3D performance: blazinggeometry performance, lightening-fastline performance and massive fill ratespowered by a dynamically configurablearray of thread processors. With ultra-fast pixel read-back performance,massive host throughput gains can beachieved for professional applications.However, the true measure of power isapplication performance and the newNVIDIA Quadro architecture doubles theperformance of the previous generation.Advanced ProgrammabilityEmpowers a New Classof ApplicationsThe latest NVIDIA Quadro FX graphicssolutions are the reference standard forShader Model 4.0 and next generationoperating systems enabling breakthroughultra-realistic, real-time visualizationapplications. Styling and productionrendering are integral functions of thedesign workflow and NVIDIA QuadroFX provides professionals the toolsto shorten the production processand enable faster time to market.The major CAD and DCC applicationvendors can take full advantage of theprogrammable NVIDIA Quadro architectureby enabling sophisticated shaders tosimulate a virtually unlimited range ofphysical characteristics, such as lightingeffects (dispersion, reflection, refraction,BRDF models) and even physical surfaceproperties (casting effects, porosity,molded surfaces). Real-time shaders allowaccurately matching visual images.All images have a smoother, moreappealing variation in color density, whichincreases visual realism and generatesphotorealistic rendered images.Certified for the HighestQuality Experience withthe Most DemandingWorkstation ApplicationsThe performance and power of theNVIDIA Quadro architecture arebuilt on a solid foundation of qualityengineering. This engineering excellenceis exemplified by the NVIDIA UnifiedDriver Architecture (UDA), which iscertified for quality by the entire spectrumof CAD and DCC applications.these effects to be combined and modifiedinteractively, something that is impossiblewith simple 2D static texture maps.Full 128-bit Floating PointPrecision Delivers the Industry’sHighest Workstation QualitySophisticated real-time effects typicallyinvolve multiple mathematical operations thatdemand high precision to maintain imagequality. The NVIDIA Quadro architecturefeatures true 128-bit IEEE floating pointprecision (32-bit fp per component),resulting in the highest level of accuracyand the ultimate in visual quality.The NVIDIA Quadro family delivers true16-bit and 32-bit floating point formats forThe Definition of Performance. The Standard for Quality.uncompromisedprofessional graphics to goThe NVIDIA Quadro FX professional solutions for mobile workstations deliver the fastest application performanceand the highest quality graphics. The NVIDIA Quadro FX mobile solutions enable the leading CAD, DCC, and visualization applications to solve the most complex professional visual computing challenges in a mobile form factor.integrated graphics to video solutionThe NVIDIA Quadro SDI solutions are ideal foron-air broadcast professionals across manyapplications, including virtual-set, sports, andweather news systems. The NVIDIA Quadro SDIsolution is the industry’s only fully integratedgraphics to video out product, and will compositelive video footage onto virtual backgrounds andsend the result to live video for TV broadcast. Thesolution also allows film production and post-production professionals to preview the results of3D compositing, editing, and color grading in realtime on HD broadcast monitors.c programming environmentfor the gpuThe NVIDIA CUDA™software development kitprovides a C language environment and toolssuite that unleashes new capabilities to solvecomplex, visualization challenges such asreal-time ray tracing and interactive volumerendering.1revolutionizingadvanced visualizationThe NVIDIA Quadro G-Sync deliversframe and genlock functionality tounprecedented levels of industrialrealism, visualization, and collaborativecapabilities. The NVIDIA Quadro G-Sync IIoption can be combined with the QuadroFX 5600 or 4600, and G-Sync I can becombined with the FX 5500 to provideadvanced multi-system visualizationand external signal synchronization.a quantum leap in visual computingThe NVIDIA Quadro Plex is a dedicatedvisual computing system (VCS) enablingbreakthrough levels of capability andproductivity for professionals ranging frommanufacturing designers and stylists toearth scientists to digital content creators.NVIDIA Quadro Plex provides the flexibility tobe deployed with any certified PCI Express®x16 platform. NVIDIA Quadro Plex achievesunmatched compute density, can bedeployed in a wide range of environments,and scales to meet the most demandingprofessional applications requirements.HP Mobile Workstation courtesy HP - image on screen courtesy ProE2000. Racetrack image © Sam Sharpe / The Sharpe Image / Corbis. Inside right page: Geographic imagery courtesy Landmark, a brand of the Halliburton Drilling, Evaluation and Digital Solutions. Video Wall image courtesy ORNL.scalable graphics performance NVIDIA Quadro graphics solutions feature NVIDIA® SLI™ multi-GPU technology2.A revolutionary platform innovation,SLI technology enables professional users to dynamically scale graphics performance, enhance image quality, and expand display real estate by combining multiple NVIDIA Quadro graphics solutions in a single system.Available NVIDIA Quadro Solutions Ultra-High-EndNVIDIA Quadro FX 5600 NVIDIA Quadro FX 5500 NVIDIA Quadro FX 4700 X2 High-EndNVIDIA Quadro FX 4600 NVIDIA Quadro FX 3700 NVIDIA Quadro FX 3500Mid-RangeNVIDIA Quadro FX 3450 NVIDIA Quadro FX 1700 NVIDIA Quadro FX 1500 Entry-LevelNVIDIA Quadro FX 570 NVIDIA Quadro FX 560 NVIDIA Quadro FX 550 NVIDIA Quadro FX 370 SpecialtyNVIDIA Quadro Plex VCS NVIDIA Quadro SDINVIDIA Quadro G-Sync MobileNVIDIA Quadro FX 3600M NVIDIA Quadro FX 1600M NVIDIA Quadro FX 570M NVIDIA Quadro FX 360M。

graphic device

graphic deviceGraphic DeviceIntroduction:In today's digital world, graphic devices play a crucial role in various industries, including gaming, entertainment, design, and advertising. Graphic devices are hardware components that enable the transformation of digital instructions into meaningful visual output. They are responsible for creating and rendering images, videos, animations, and various graphical elements. This document provides a comprehensive overview of graphic devices, discussing their types, functionalities, and importance in modern technology.Types of Graphic Devices:Graphic devices come in different forms and serve diverse purposes. The following are some commonly used types of graphic devices:1. Graphics Processing Unit (GPU):The Graphics Processing Unit, commonly known as GPU, is an essential component in computers, gaming consoles, and smartphones. Its primary function is to process and render graphical data. A GPU comprises several cores and is highly specialized in performing complex mathematical and geometric calculations. With the evolution of GPUs, real-time rendering and advanced visual effects have become possible in various applications.2. Video Card:Also known as a display adapter, a video card is an expansion card that generates and outputs visual data to a display device, such as a monitor or a projector. It connects to the computer's motherboard and processes the graphical instructions received from the CPU. The video card utilizes its built-in GPU to render the visual content, which is then transmitted to the display device for user interaction.3. Integrated Graphics:Integrated graphics refers to the graphical processing capabilities integrated into the computer's central processing unit (CPU). Unlike discrete graphic devices like GPUs or video cards, integrated graphics are a part of the overall CPU architecture. They are generally less powerful than dedicated graphic devices but can handle basic graphics tasks, such as web browsing, office applications, and light gaming.Functionalities of Graphic Devices:Graphic devices offer various functionalities that are vital for creating and presenting visually appealing content. Some of the key functionalities are as follows:1. Rendering:Rendering is the process of generating visual output from digital data. Graphic devices, especially GPUs, excel at rendering complex graphics, 3D models, and simulations. They perform calculations to determine the position, color, texture, and lighting effects of each pixel, resulting in realistic and immersive visuals.2. Image Processing:Graphic devices also have image processing capabilities. They can manipulate digital images by applying filters, adjusting brightness, contrast, and color levels. Image processing techniques are widely used in photography, video editing, and special effects creation.3. Video Playback and Encoding:Graphic devices are responsible for smooth video playback on various devices. They decode video files and display them on the screen in real-time. Additionally, graphic devices assist in video encoding, converting video files into different formats or compressing them for efficient storage and transmission.4. Gaming Support:One of the primary uses of graphic devices is in gaming. They handle complex calculations and render high-quality visuals, enabling immersive gaming experiences. With features like real-time ray tracing and advanced shading techniques, modern graphic devices greatly enhance the realism and detail in games.Importance of Graphic Devices:Graphic devices have revolutionized the way we interact with technology and consume visual content. Their significance can be highlighted through the following points:1. Enhanced Visual Experience:From high-definition videos to lifelike game graphics, graphic devices are instrumental in creating immersive visualexperiences. They bring digital content to life, making it more engaging and enjoyable for users.2. Productivity and Creativity:Graphic devices empower professionals in various industries by providing tools for advanced design, 3D modeling, and video editing. These devices enable efficient workflows and allow individuals to unleash their creative potential.3. Real-Time Performance:The computing power of graphic devices, particularly GPUs, allows for real-time rendering and quick response times. This is crucial in applications like virtual reality (VR), simulations, and live event graphics.4. Technological Advancements:Graphic devices continue to advance at a rapid pace, driving innovation in several areas. The development of high-performance GPUs has paved the way for breakthroughs in artificial intelligence, machine learning, and cryptocurrency mining.Conclusion:In conclusion, graphic devices are indispensable components of modern technology. Their ability to generate, process, and render visual content revolutionizes industries such as gaming, entertainment, design, and advertising. With their advanced functionalities and constantly improving performance, graphic devices continue to shape the way we perceive and interact with the digital world.。

用于低功耗、非刚性平面应用的柔性AMOLED器件

ห้องสมุดไป่ตู้

文章编号 :0 6 6 6 (o o 1— 0 0 0 10 — 2 g 2 l )1 0 1 —7

用于低 功耗 刚性平 面应 用 的 非 柔 性 AM 件 OL D器 E

r n e o e o u i n r p o t nt sa e b i g c e t d a g f v lt a y o p ru i e r e n r a e . r o i Ke wo d : y r s AM OL D; O —p w e ; l x be d s ly E lW o r f il ip a e

作 者 针 对 P OL D显 示器 展 望 了一 个 五 阶 段 H E 路 线 图 : 1 低 功耗 —— 显示 器 件 仍然 制 备 在 刚性 的 () 玻璃基板上 , 但具 有低 功耗 和 较 薄 的 外形 ;2) ( 非刚 性— — 去 掉 了玻 璃 基板 , 示器 件 更 薄且 不易 破碎 , 显 具 有 有 限 的柔性 ; 3) 弯 曲—— 显 示器 可 弯 曲且 各 ( 可 层 结 构 之间具 有 一 致性 ;4) 卷 曲— — 这 个 阶段 的 ( 可 显 示器 在 某 个 纬 度 非 常 柔 软 , 因此 可 以卷 成 一 卷 ; ( 任 意 形状— — 这 是 柔性 显 示 的终 极 阶段 , 示器 5) 显

文献 标识码 : B

Fe il lxbe AMOL EDsf rL w-P we ,Ru g d Ap l a in o o o r g e pi t s c o

Ruqn iig Ma, k c , n ui . o Mie Ha k a d J l J Br wn e

NVIDIA Quadro K5200 8GB 图形卡说明书

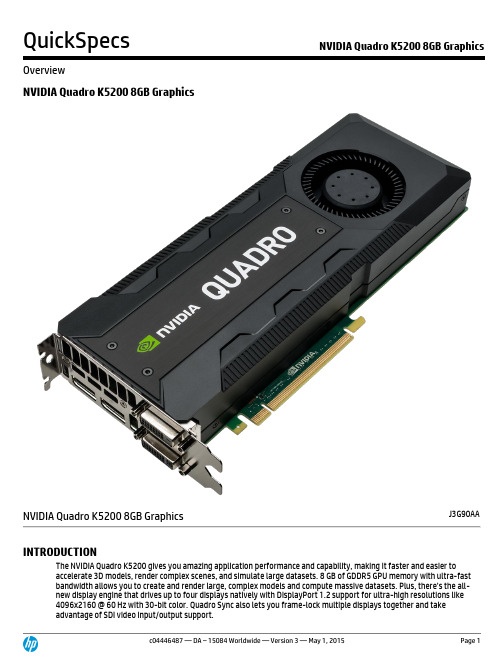

NVIDIA Quadro K5200 8GB GraphicsNVIDIA Quadro K5200 8GB Graphics J3G90AA INTRODUCTIONThe NVIDIA Quadro K5200 gives you amazing application performance and capability, making it faster and easier toaccelerate 3D models, render complex scenes, and simulate large datasets. 8 GB of GDDR5 GPU memory with ultra-fast bandwidth allows you to create and render large, complex models and compute massive datasets. Plus, there’s the all-new display engine that drives up to four displays natively with DisplayPort 1.2 support for ultra-high resolutions likeadvantage of SDI video input/output support.The NVIDIA Quadro K5200 is set to take on the most demanding workflows whether in product development, high end styling, near real-time photorealistic rendering, media and entertainment creations, and simulations/analysis. PERFORMANCE AND FEATURES∙Amazing graphics and rendering performance delivered by the highest end Kepler based GPU technology∙8GB GDDR5 ultra-fast memory supporting a wide memory path to minimize memory access performance penalties∙New display engine drives up to four displays natively with DisplayPort 1.2 support for ultra-high resolutions like 4096x2160 @ 60 Hz with 30-bit color∙NVIDIA SYNC allows multiple displays to be frame-locked together and supports SDI video input/output∙Support for large-scale, ultra-high resolution visualization using the NVIDIA® SVS platform which includes NVIDIA® Mosaic, NVIDIA® Sync and NVIDIA® Warp/Blend technologies∙2304 CUDA parallel processing cores well suited to accelerate demanding parallel computing workloads using CUDA∙Comes complete with all necessary ISV application certificationsCOMPATIBILITYThe NVIDIA Quadro K5200 is supported in the following HP Z Workstations:- Z440, Z640, Z840SERVICE AND SUPPORTThe NVIDIA Quadro K5200 has a one-year limited warranty or the remainder of the warranty of the HP product in which it is installed. Technical support is available seven days a week, 24 hours a day by phone, as well as online support forums.Parts and labor are available on-site within the next business day. Telephone support is available for parts diagnosis and installation. Certain restrictions and exclusions apply.TECHNICAL SPECIFICATIONSForm Factor Dimensions: 4.376” H x 10.5” LDual Slot, Full HeightCooling: ActiveWeight: 880 grams (without extender)Graphics Controller NVIDIA Quadro K5200GPU: GK110-850-B1 with 2304 CUDA coresPower: 150 WattsBus Type PCI Express 3.0 x16Memory Size: 8GB GDDR5Memory bandwidth: 192GB/sMemory Width: 256-bitConnectors 1 DVI-I1 DVI-D2 DisplayPort 1.2aFactory configured option: No adapter included with card.After market option kit: No adaptor included with card.Additional DVI to VGA, DisplayPort to VGA, DisplayPort to DVI, and DisplayPort to Dual-Link DVIadapters available as accessoriesMaximum Resolution DisplayPort:- up to 4096 x 2160 x 30 bpp @ 60Hz- supports High Bit Rate 2 (HBR2) and Multi-Stream Transport (MST)DL-DVI(I) output:- up to 2560 x 1600 x 32 bpp @ 60HzSingle Link-DVI(I) output:- up to 1920 x 1200 x 32 bpp @ 60HzVGA (via adapter cable):- 2048 × 1536 × 32 bpp at 85 HzImage Quality Features 10-bit internal display processing (hardware support for 10-bit scanout for both windoweddesktop and full screen, only available on Windows with Aero disabled and Linux).NVIDIA® 3D Vision™ technology, 3D DLP, Interleaved, and other 3D stere o format support.Full OpenGL quad buffered stereo support.Support for NVIDIA® Quadro® Mosaic, NVIDIA® nView® multi-display technology, NVIDIA®Enterprise Management Tools.Support for large-scale, ultra-high resolution visualization using the NVIDIA® SVS platform whichincludes NVIDIA® Mosaic, NVIDIA® Sync and NVIDIA® Warp/Blend technologies.Display Output Maximum number of displays- 4 direct attached monitors- 4 using DP 1.2a with MST and HBR2 enabled monitorsMaximum number of DisplayPort displays possible (may require MST and/or HBR2):- 4 1920x1200- 4 2560x1600- 2 4096x2160Maximum number of monitors across all available Quadro K5200 outputs is 4.Shading Architecture Shader Model 5.0Supported Graphics APIs OpenGL 4.4DirectX 11API su pport for NVIDIA’s CUDA™ C, CUDA C++, DirectCompute 5.0, OpenCL, Java, Python, Fortran Available Graphics Drivers Microsoft Windows 8.1Microsoft Windows 8Microsoft Windows 7Linux - Full OpenGL implementation, complete with NVIDIA and ARB extensionsHP qualified drivers may be preloaded or available from the HP support Web site:/country/us/en/support.htmlNotes 1. Factory configured Quadro K5200 does not include a video cable adapter. Video cable adaptersmust be ordered separately.2. A total maximum of 4 active monitors are supported across all display output types. This maybe accomplished by using daisy chained DisplayPort 1.2 displays (displays must support MST andHBR2).3.Configurations of a single Quadro K5200 graphics card in HP Z440 Workstation require the HPZ440 Fan and Front Card Guide Kit, configurable from the factory (CTO PN: G8T99AV) or as anAftermarket Option (AMO PN: J9P80AA).Summary of ChangesDate of change: Version History: Description of change:Sept 15, 2014 Version 1 Added Migrate to current template, add product photo December 3, 2014 From v1 to v2 Added Note for Z440 configurations.May 1, 2015 From v2 to v3 Changed Notes for Technical Specification section© Copyright 2015 Hewlett-Packard Development Company, L.P.The only warranties for HP products and services are set forth in the express warranty statements accompanying such products and services. Nothing herein should be construed as constituting an additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein. The information contained herein is subject to change without notice.。

阿利亚罗K-0169 Rev B 12通道多功能板说明书

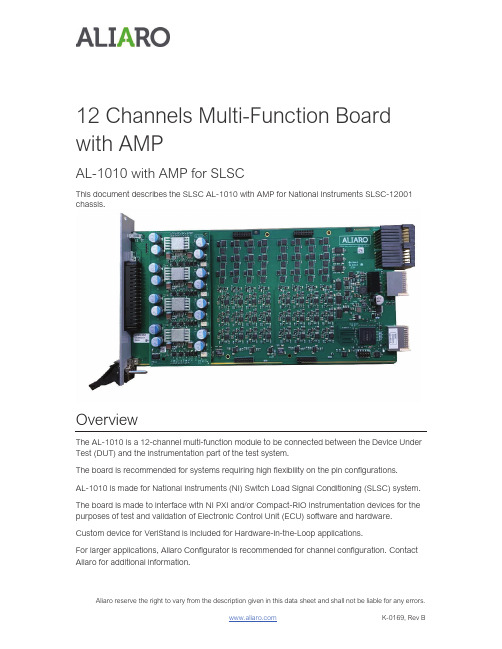

12 Channels Multi-Function Board with AMPAL-1010 with AMP for SLSCThis document describes the SLSC AL-1010 with AMP for National Instruments SLSC-12001 chassis.OverviewThe AL-1010 is a 12-channel multi-function module to be connected between the Device Under Test (DUT) and the instrumentation part of the test system.The board is recommended for systems requiring high flexibility on the pin configurations.AL-1010 is made for National Instruments (NI) Switch Load Signal Conditioning (SLSC) system. The board is made to interface with NI PXI and/or Compact-RIO instrumentation devices for the purposes of test and validation of Electronic Control Unit (ECU) software and hardware. Custom device for VeriStand is included for Hardware-In-the-Loop applications.For larger applications, Aliaro Configurator is recommended for channel configuration. Contact Aliaro for additional information.C ontents Overview (1)Description (3)Features (3)Detailed description (4)Installation (5)Electromagnetic Compatibility (5)Unpacking the module (5)Hardware Installation (6)Maintenance (7)Safety (7)Before using the AL-1010 (7)System Check (7)Calibration (7)Specification (8)Definition and conditions (8)Environmental Characteristics (8)Physical characteristics (8)Front connectors (J1 & J2) (9)General specification (10)Fault Insertion (10)Signal conditioning (All channels) (10)Digital I/O (10)Analogue Out – Amplifier (10)Functions (11)LabVIEW (11)Veristand (11)Configuration and Accessories (12)RTI Backplane (12)AL-1010 RTI Terminal Block (14)Safety Guidelines (15)Product Certifications and Declarations (15)CE Compliance (15)Electromagnetic Compatibility Standards (15)Environmental Management (16)Waste Electrical and Electronic Equipment (WEEE) (16)DescriptionThe AL-1010 provide multiple functions for fault insertion, signal conditioning and digital I/O, including pulsed (PWM) signals. The AL-1010 is fitted in pair through the RTI-backplane AL-1010-RTI.The AL-1010 RTI backplane is needed to reach fully flexibility and enables easy connection to NI PXIe and/or Compact-RIO instrumentation devices. Additional with add-on boards the functionality can be expanded further.Features960V, 10A per channel912 independent and isolated channels in three banks9Two common buses per bank with switches to each channel9Brake up switch for each channel9Programmable level threshold on each channel9Parallel connection possibility for high current signals9LabVIEW driver is available.9Custom Device is available.Detailed descriptionFigure 1, AL-1010 Block diagramThe AL-1010 board provides fault insertion, signal conditioning and digital I/O.Fault insertion functions:- Open circuit (DUT to Load)- Short to + and – (DUT to AUX 1 or AUX2)Signal conditioning functions:- Digital input (from DUT) signal conditioning using adjustable threshold (-28 - +28V) - Analogue signal (to DUT) with amplification (4 channels)- Analogue signal (from DUT)Digital I/O functions:- Read digital status (from DUT) using adjustable threshold- Read PWM signals (from DUT) using adjustable threshold (Frequency and duty cycle) - Generate digital signals (to DUT) using AUX1 (+) and AUX2 (-)- Generate PWM signals (To DUT) using AUX1 (+) and AUX2 (-)InstallationElectromagnetic CompatibilityThis product is intended for use in industrial locations. However, harmful interference may occur in some installations, when the product is connected to a peripheral device or test object, or if the product is used in residential or commercial areas. To minimize interference with radio and television reception and prevent unacceptable performance degradation, install, and use this product in strict accordance with the instructions in the product documentation. Furthermore, any modifications to the product not expressly approved by Aliarocould void your authority to operate it under your local regulatory rules.C aution To ensure the specified EMC performance, operate this product only withShielded cables and accessories.Unpacking the moduleCarefully inspect the shipping container and the module for damage.Check for visible damage to the exterior and interior of the damage.If damage appears to have been caused during shipment file a claim with the carrier.Retain the packing material for possible inspection and/or reshipment.If the chassis is damaged, do not install it and contact Aliaro.Hardware InstallationTo set up and use the module you need the following items:Hardwarex SLSC-12001 chassisx SLSC AL-1010 module(s)x SLSC AL-1010 RTIx SLSC AL-1010 RTI CBx Power cablex Power input connectorx Grounding wirex Grounding lugToolsx Screwdriver as needed for your applicationx Wire stripperDocumentationSLSC-12001 Chassis Getting Started Guide and SpecificationsC aution:Do not touch the contacts or remove the I/O boards or cables while the systemis energized.The SLSC chassis and the AL-1010 do not support hot plug-in. The entirechassis must be powered off when a module is inserted or removed.Procedure:1.Power off the main DC power source or disconnect the power source from the chassisbefore installing any modules or RTIs.2.Ensure that the chassis is powered off. The POWER LED should be off. If thePOWER LED is not off, do not proceed until it is off.3.Loosen the screws on the upper rear panel of the chassis.4.Position the RTI backplane at the desired slot and insert the securing screws, but do notfully tighten them.5.Insert a AL-1010 module into the same slot as its corresponding RTI while firmly holdingthe RTI in place until the RTI is firmly connected to the module.6.Repeat steps 4 and 5 for all required RTIs.7.Fully tighten the screws for all RTIs and the upper rear panel of the chassis. Note Waitinguntil all RTIs and modules are installed to fully tighten the screws ensures properalignment for future connections between modules and RTIs.8.Fully tighten the two module mounting screws on each newly installed module.9.Power on the SLSC chassisMaintenanceSafetyC aution Observe all instructions and cautions in the user documentation. Using themodel in a manner not specified can damage the model and compromise the built-insafety protection. Return damaged models to Aliaro for repair.Before using the AL-1010All input characteristics are DC, ACrms, or a combination unless otherwise specified. Maximum switching voltage (any polarity) 1100Vpeak. Every card provides a fully capable fault insertion with external control during simulations or testing. Relays can be configured with Aliaro Configurator, VeriStand and LabVIEWNote Steady state voltages applied to the AL-1010between any two I/O connector pins in excess of the maximum switching voltage specification may damage the module Note Signal connections through the AL-1010are intended to go through the DUTn pin connections. Signal paths that do not use the DUTn pin connections bypass the internal overcurrent limiting features and may exceed the module's thermal capabilities.System CheckThis chapter requires LabVIEW development and installation of LabVIEW drivers.To identify and control that the cards are inserted and work properly with the right firmware, LabVIEW provides basic VI scripts to check SLSC cards mounted in chassis1.Open LabVIEW and select “Help” in the top menu bar and press “FindExamples…” (This opens a new window with pre-built VI (Virtual Instruments) for different applications).2.Switch to the “Search” tab and enter keyword “SLSC” and double click.3.In the new filtered table (to the right) find and select VI called “Configuration.vi”.This VI can located every card(s) that is online in SLSC chassis.4.To find the newly inserted cards look for the SLSC chassis IP-address (in thetable to the right).Count the showing card(s) in the table and make up that there are as manymounted in the SLSC chassis as there are in the VI table for that specific IPaddress. (Can be 1 up to 11 cards per SLSC chassis)CalibrationRecommended warm-up time30 minCalibration interval Not required, recommended on system levelSpecificationDefinition and conditionsWarranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.The following characteristic specifications describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.x Typical specifications describe the performance met by most models.x Nominal specifications describe an attribute that is based on design, conformance testing, or supplemental testing.Specifications are Typical unless otherwise noted.Specifications are valid under the following conditions unless otherwise noted.The AL-1010 module is mounted in an SLSC chassis with the recommended cooling clearances and using a power supply that meets the specifications provided in the chassis user guide. For the entire temperature range of the chassis.Note These specifications only apply to the product as provided by Aliaro. Modifications to the module may invalidate these. Be certain to verify the performance of modifiedmodules.Caution Observe all instructions and cautions in the user documentation. Using themodel in a manner not specified can damage the model and compromise the built-insafety protection. Return damaged models to Aliaro for repair.Environmental CharacteristicsTemperatur e an d HumidityOperating temperature0 °C to 40 °CStorage temperature range-40 °C to 85 °COperating relative humidity range10% to 90%, noncondensingStorage relative humidity range5% to 95%, noncondensingPhysical characteristicsCategory Condition ValueModule Dimensions Excluding front handle144.32mm x 30.48mm x 281 mm(H x W x D)Front Panel Connector1x female Weidmuller 32 highdensityFront connectors (J1 & J2)See fig 1 for description of the functions.C autionThe pins are not indestructible, ports and pins will tare if not treated with care.PinDUT(J1) LOA D (J2) 1DUT Ch 1Load Ch 12DUT Ch 2Load Ch 23DUT Ch 3Load Ch 34DUT Ch 4Load Ch 45DUT Ch 5Load Ch 56DUT Ch 6Load Ch 67DUT Ch 7Load Ch 78DUT Ch 8Load Ch 89DUT Ch 9Load Ch 910DUT Ch 10Load Ch 1011DUT Ch 11Load Ch 1112DUT Ch 12Load Ch 1213DUT_GND AUX 1C 14ISO_GND AUX 2A 15AUX 1A AUX 2B 16AUX 1B AUX 2C(J1)(J2)General specificationC ategory C ondition V alueNo of channels 12No of banks 3Power supply 24VDC, +/-5%Channel to channel isolation (50Ω/100kHz) 40dBMax. Operating Voltage Any pin + 60VMin. Operating Voltage Any pin - 60VFault InsertionCategory Condition Specified value Typical valueMax. continuously current DUT to LoadDUT to AUX 1 /2All other pins 10 A (40A using parallel channels) 10 A (40A using parallel channels)100 mAMax peak current (<100 ms, 25 °C)DUT to LoadDUT to AUX 1/240A/50ms40A/50ms*Notice Exceeding the maximum pulsed current can damage the module. Signal conditioning (All channels)Category ValueThreashold, range -28- +28VThreashold, resolution 0,1VThreshold, bandwidth 20 kHzDigital I/OCategory ValuePWM frequency range 100-65 000 μs (15 hz -10 kHz) PWM frequency resolution 1 usPWM frequency accuracy +/- 25 ppmPWM duty cycle range 10-90 %PWM duty cycle resolution 1 usAnalogue Out – AmplifierCategory ValueNo of channels 4 (DUT ch 1-4)Power supply(Separate isolated supply)24VDC, +/-5%Current drive 200mA per channelFunctionsLabVIEWContact Aliaro Team for separate LabVIEW drivers.(Equal functions to the custom device in Veristand, see below)VeristandThe custom device provides following functions for the AL-1010 board:Parameter Description Unit RangeLoad Connect/disconnect selected channelto Aux 1 (Off/On) 0; 1Aux1 Connect/disconnect selected channelto Aux 1 (Off/On) 0; 1selectedchannelAux2 Connect/disconnectto Aux 2 (Off/On) 0; 1Threshold Sets the digital threshold of selected-28,0+28,0–(V)channel VoltDI Reads the logic value of the channelbased upon the threshold settings (Off/On) 0; 1Amplifier functions (Ch 1-4)Amp-Enable Enables the amplifier function (Off/On) 0; 1foramplificationtheGain Defineseach channel (Off/On) 0; 1PWM functionsPWM_Aux1 Enables PWM function using Aux1for selected channel (Off/On) 0; 1PWM_Aux2 Enables PWM function using Aux1for selected channel (Off/On) 0; 1PWM_Load Enables PWM function using Aux1for selected channel (Off/On) 0; 1PWM_Period Sets period for selected channel Time [μs] 100-65 000 μsDI-PWM_DutyCycle Sets duty cycle when using PWMfor selected channel % 10-100%Configuration and AccessoriesFor most applications, the AL-1010 needs to be configured with a backplane (AL-1010 RTI) combined with a connection block (AL-1010 RTI CB). The AL-1010 provides 2 expansion slots for add-on boards such as customized functionalities needed for the customer’s project.RTI BackplaneThe AL-1010 RTI is used to connect to two (2) SLSC modules (Left and Right) on the same board.Connector pinoutsJ1:1J1:4J1:2J1:3J1:6J1:5J2J3J4J3 Left board / J4 Right board (ERNI 064004 connector)P in S ignal T e rminal P in S ignal T erm i na l A1 Digital in, channel 1 J4:1 B1 Digital in, channel 7 J6:1A2 Digital in, channel 2 J4:2 B2 TS GND J8:4A3 Digital in, channel 3 J4:3 B3 Digital in, channel 8 J6:2A4 Digital in, channel 4 J4:4 B4 TS GND J8:4A5 Digital in, channel 5 J4:5 B5 Digital in, channel 9 J6:3A6 Digital in, channel 6 J4:6 B6 DUT GND J8:3A7 Analog in, channel 7 J2:1 B7 Digital in, channel 10 J6:4A8 Analog in, channel 8 J2:2 B8 DUT GND J8:3A9 Analog in, channel 9 J2:3 B9 Digital in, channel 11 J6:5A10 Analog in, channel 10 J2:4 B10 DUT Ref J8:1A11 Analog in, channel 11 J2:5 B11 Digital in, channel 12 J6:6A12 Analog in, channel 12 J2:6 B12 DUT Ref J8:1A13 DUT Reference J8:1 B13 Analog out, channel 7 J7:1A14 Analog in, channel 1 J3:1 B14 DUT Ref J8:1A15 Analog in, channel 2 J3:2 B15 Analog out, channel 8 J7:2A16 Analog in, channel 3 J3:3 B16 DUT Ref J8:1A17 Analog in, channel 4 J3:4 B17 Analog out, channel 9 J7:3A18 Analog in, channel 5 J3:5 B18 DUT GND J8:1A19 Analog in, channel 6 J3:6 B19 Analog out, channel 10 J7:4A20 Analog out, channel 1 J5:1 B20 TS GND J8:4A21 Analog out, channel 2 J5:2 B21 Analog out, channel 11 J7:5A22 Analog out, channel 3 J5:3 B22 TS GND J8:4A23 Analog out, channel 4 J5:4 B23 Analog out, channel 12 J7:6A24 Analog out, channel 5 J5:5 B24 NC (Internal use) J8:5A25 Analog out, channel 6 J5:6 B25 NC (Internal use) J8:6AL-1010 RTI Terminal BlockThe AL-1010 RTI Terminal Block is used to connect to two (2) SLSC modules (Left and Right) on the same board.System Overview of AL-1010 RTI and Terminal BlocksAL-1010 Terminal block Kadro-B037 AL1010 RTI TBSafety GuidelinesC autionsEnsure that hazardous voltage wiring is performed only by qualified personnel adhering to local electrical standards.Do not mix hazardous voltage circuits and human-accessible circuits on the same module. When device terminals are hazardous voltage LIVE, you must ensure that devices and circuits connected to the device are properly insulated from human contact.All wiring must be insulated for the highest voltage used.Product Certifications and DeclarationsRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information.To obtain product certifications and the DoC for Aliaro products, visit / certification.CE ComplianceThis product meets the essential requirements of applicable European Directives, as follows: x2014/35/EU; Low-Voltage Directive (safety)x2014/30/EU; Electromagnetic Compatibility Directive (EMC)x2011/65/EU; Restriction of Hazardous Substances (RoHS)Electromagnetic Compatibility StandardsThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:x EN 55011-2009 Industrial, scientific and medical equipment - Radio-frequency disturbance characteristics - Limits and methods of measurement CISPR 11:2009x EN 55032:2012 Electromagnetic compatibility of multimedia equipment - Emission requirements CISPR 32:2012x EN 61326-1-2013 Electrical equipment for measurement, control and laboratory use - EMC requirements - Part 1: General requirements IEC 61326-1:2012Environmental ManagementAliaro is committed to designing and manufacturing products in an environmentally responsible manner. Aliaro recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to Aliaro customers. For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment.This page contains the environmental regulations and directives with which Aliaro complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE)EU Customers At the end of the product life cycle, all Aliaro products must be disposed of according to local laws and regulations.For more information about how to recycle Aliaro products in your region, visit/environment/weee。

NVIDIA ConnectX-7 商品说明书