Atmel推出基于ARM926EJ-S 的嵌入式微处理器

AT91SAM9261片上系统介绍

AT91SAM9261片上系统介绍一.AT91SAM9261 SOC简介A T91SAM9261是atmel公司生产的以ARM926EJ-S ARM Thumb处理器为核心的完全片上系统(SOC),它扩展了DSP指令集和Jazelle Java加速器。

主时钟频率190MHz时性能高达210MIPS。

A T91SAM926是一个为带LCD显示应用而优化了的主机处理器。

它的集成LCD控制器支持BW而且达到16M色彩,主动和被动LCD显示。

16K字节的片上SRAM可配置为帧缓冲,能将LCD刷新对整体处理器性能上的影响降低到最小。

外部总线接口包括支持同步DRAM(SDRAM)和支持静态存储器的控制器,并有特殊接口电路以支持CompactFLASH 和NandFLASH。

A T91SAM9261集成了一个支持映射的基于ROM的Bootloader,例如从外部DataFlash 映射到外部SDRAM。

由软件控制的功率管理控制器(PMC)通过有选择的启用和关闭处理器、各种外设以及对工作频率的调节使得系统功率损耗保持最低。

A T91SAM9261还集成了宽范围的调试特性。

包括JTAG-ICE,一个专用的UART调试通道(DBUG)和嵌入式实时追踪。

这使所有应用和开发,特别是严格要求实时性的应用得以实现。

下面是A T91SAM9261的功能框图:二.处理器ARM926EJ-S介绍ARM926EJ-S是通用微处理器ARM9家族中的一员,属于V5TEJ版ARM架构,针对的是多任务应用,全存储器管理、高性能、小核心尺寸和低功耗都是它的特点。

ARM926EJ-S处理器支持32位ARM和16位THUMB指令集,使得用户能在高性能和高代码密度上取得平衡。

它支持8为JA V A指令集并且包括Java字节代码有效执行的功能部件,提供和JIT(Just In Time编译器)形似的Java性能,这些性能为下一代Java无线应用和嵌入式的设备提供了有效支持。

AT91SAM9G25中文介绍

AT91SAM9G25中文介绍概述SAM9G25是基于ARM926EJ-S内核,嵌入式微处理器单元,运行在400 MHz和连接外围设备,高数据带宽架构和一个小型封装选项,它用于工业应用的优化解决方案。

多层总线矩阵连接到2 x 8个DMA通道,以及专用的通信和接口外设的DMA,确保不间断的数据传输,以最小的处理器开销。

接口外围设备包括一个相机接口,支持直接连接到ITU-R BT。

601/6568位模式下的标准的传感器和高达12位的灰度传感器。

通讯外设包括一个软调制解调器支持专门的科胜讯的SmartDAA线路驱动器,HS(高达480 Mbps)USB主机和设备端口,片上收发器,FS USB主机,10/100以太网MAC,两个HS SD卡/ SDIO / MMC接口,USART接口(SPI),同步串行接口的I2S,多个TWIS和10位ADC。

外部总线接口集成为8银行DDR2/LPDDR,SDRAM / LPSDRAM,静态存储器,以及具体的电路,集成了ECC,高达24位的MLC/ SLC NAND闪存控制器提供支持。

SAM9G25是球间距为0.8mm,以及247球BGA封装,焊球间距为0.5mm的217球BGA封装,使得它非常适合于空间受限的应用。

性能•内核- ARM926EJ-S™ARM®Thumb®的处理器,运行速度高达400 MHz@1.0V + / - 10%- 16 KB的数据Cache,16 KB的指令高速缓存,存储器管理单元•存储器- 一个64字节的内部ROM嵌入引导程序:NAND Flash的启动,SD卡的DataFlash®或串行数据闪存。

可编程顺序。

- 一个32字节的内部SRAM,单周期存取系统的运行速度- 高带宽,多端口的DDR2控制器- 32位外部总线接口支持8银行DDR2/LPDDR,SDR / LPSDR的,静态的存储器- MLC / SLC NAND控制器,24位可编程的多比特错误纠正代码(PMECC)•系统运行速度高达133 MHz的- 上电复位单元,复位控制器,关闭控制器,周期间隔定时器,看门狗定时器和实时时钟- 引导模式选择选项,映射命令- 内部低功耗32 kHz的RC和快速工作频率为12MHz RC振荡器- 可选择的32768 Hz的低功耗振荡器和12 MHz振荡器- 优化的PLL为系统和一个PLL频率为480 MHz的USB高速- 12个32位AHB总线矩阵,大带宽传输层- 双外设桥专用的可编程时钟以获得最佳性能- 两个双端口8通道DMA控制器- 高级中断控制器和调试单元- 两个可编程的外部时钟信号•低功耗模式- 关闭控制器,4个32-bit电池备份寄存器- 时钟发生器和电源管理控制器- 非常慢的时钟工作模式,软件可编程功率优化功能•外设- ITU-R BT。

ARM926EJ-S

AT91SAM9260-EKAT91SAM9260-ek 是一款ARM926EJ-S 内核的工业级的开发板,支持JAVA,支持DSP扩展库CPU 内嵌100M 以太网,带有USB2.0协议的USB HOST 和Device 接口,支持SD /MMC卡和全功能9 线串口等。

主频180 MHz 达到200 MIPS ,带有MMU 存储器管理单元。

性能稳定,功能强大,是工业控制、网络通讯等应用的首选。

AT91SAM9260 开发板硬件资源:中央处理器── AT91SAM9260(ARM926EJ-S)主频180M(达到200 MIPS),工业级;带EBI支持外部存储器,支持PQFP208F封装── 8K字节的高速数据缓冲器,8K字节的高速指令缓冲器。

── 32K字节内部ROM,用于存储上电时的引导程序BOOT;──双4K字节内部SRAM;──64M Bytes NAND Flash(用户可自己更换为16M、64M 或128M 的NandFlash);──64M Bytes SDRAM(2 片16 位的SDRAM 芯片组成32 位接口);── 32Mbit serial DATAFLASH──512Kbit serial EEPROM串口──一个DEBU 串口── 一个串口为带有RTS/CTS握手控制的标准RS232 接口;── 另一个串口为标准9 线RS232 接口,可接Modem;CAN── 扩展一组SPI CAN总线接口网口── 一个100M 网口(AT91SAM9260内部MAC+外部PHY),带发送、接收和联结指示灯; USB 接口── 一个USB HOST(USB 2.0 Full Speed)接口;── 一个USB Device(USB 2.0 Full Speed)接口;存储卡接口── 一个MMC/SD 卡接口;调试和下载接口── 一个20 芯Multi-ICE 标准JTAG 接口,支持iar for arm 4.40以上版本,SDT2.51,ADS1.2 等调试 ;其他── RTC 实时时钟(带电池);── 一个5V电源LED,一个3V3电源LED;── 一个接在GPIO 口线上的高亮LED;── 一个RESET按键,一个中断唤醒按键;── 三个用户扩展连接口,引出了PIOA, PIOB, PIOC及D16~D31使用IMAGE SENSOR用户可自行从三个扩展连接口中引出。

DSP公司各主流芯片比较

DSP公司各主流芯片比较引言DSP芯片也称数字信号处理器,是一种专门适合于进行数字信号处理运算的微处理器具,其主机应用是实时快速地实现各种数字信号处理算法。

依照数字信号处理的要求,DSP芯片一样具有如下要紧特点:〔1〕在一个指令周期内可完成一次乘法和一次加法;〔2〕程序和数据空间分开,能够同时访问指令和数据;〔3〕片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;〔4〕具有低开销或无开销循环及跳转的硬件支持;〔5〕快速的中断处理和硬件I/O支持;〔6〕具有在单周期内操作的多个硬件地址产生器;〔7〕能够并行执行多个操作;〔8〕支持流水线操作,使取指、译码和执行等操作能够重叠执行。

在我们设计DSP应用系统时,DSP芯片选型是专门重要的一个环节。

在DSP系统硬件设计中只有选定了DSP芯片,才能进一步设计其外围电路及系统的其他电路。

因此说,DSP芯片的选择应依照顾用系统的实际需要而确定,做到既能满足使用要求,又不白费资源,从而也达到成本最小化的目的。

DSP实时系统设计和开发流程如图1所示。

要紧DSP芯片厂商及其产品德州仪器公司众所周知,美国德州仪器〔Texas Instruments,TI〕是世界上最知名的DSP芯片生产厂商,其产品应用也最广泛,TI公司生产的TMS320系列DSP芯片广泛应用于各个领域。

TI公司在1982年成功推出了其第一代DSP芯片TMS32020,这是DSP应用历史上的一个里程碑,从此,DSP 芯片开始得到真正的广泛应用。

由于TMS320系列DSP芯片具有价格低廉、简单易用、功能强大等特点,因此逐步成为目前最有阻碍、最为成功的DSP系列处理器。

目前,TI公司在市场上要紧有三大系列产品:〔1〕面向数字操纵、运动操纵的TMS320C2000系列,要紧包括TMS320C24x/F24x、TMS320LC240x/LF240x、TMS320C24xA/LF240xA、TMS320C28xx等。

基于跨层设计的嵌入式无线视频监控系统实现

基于跨层设计的嵌入式无线视频监控系统实现作者:黄刚习勇王丽洁侯靳勇来源:《现代电子技术》2010年第04期摘要:设计一种基于i.MX27的ARM9+Linux系统组成的嵌入式无线视频监控系统。

该系统采用H.264压缩编码和RTP/RTCP流媒体传输协议,实现了视频数据的压缩发送,同时在该系统上实现基于物理层网卡发送速率和RTP丢包率反馈信息相结合的跨层码率控制策略。

测试和应用结果表明,该系统取得了良好的视频效果,具有很好的应用前景。

关键词:跨层设计;无线视频传输;码率控制;嵌入式系统中图分类号:TP368.1文献标识码:A文章编号:1004-373X(2010)04-067-03Implementation of Embedded Wireless Video Transmission SystemBased on Cross-layer DesignHUANG Gang,XI Yong,WANG Lijie,HOU Jinyong(School of Electronic Science and Engineer,National University of DefenseTechnology,Changsha,410073,China)Abstract:The design of embedded video surveillance system based on ARM9 i.MX27 and Linux is described.This system combines H.264 standard with RTP/RTCP protocol to implement coding and transmission of video data.At the same time,a cross-layer rate control scheme based on physical transmitting rate of wireless card and the loss rate of RTP feedback packets are proposed and it is realized on the surveillance system.Experimental and application results show that this system works well and has a good foreground.Keywords:cross-layer design;wireless video transmission;rate control;embedded system0 引言传统的视频监控系统大都基于有线网络,由于布线困难等原因使其在一些特殊场合的应用受到很大限制。

DS-N32905开发板用户手册

苏州鼎尚信息技术有限公司

第 2 页/共 65 页

N32905 开发板用户手册

5.2 编译 Linux 内核.....................................................................................60 5.3 Linux 图形界面开发..............................................................................63

文档修改历史

2014-08-15 V1.0 文档创建 2015-01-29 V1.1 更新文档中一些文字性错误

苏州鼎尚信息技术有限公司

第 1 页/共 65 页

N32905 开发板用户手册

目录

一、产品特性 ........................................................................................................4

N32905 开发板用户手册

DS-N32905 开发板

鼎尚嵌入式 N32905 开发板采用台湾新唐科技的 ARM926EJ-S 内核的 N32905 微处理 器,N32905 运行主频 200MHz、SRAM 8KB、SDRAM 32MB,是专为嵌入式系统应用而设计的高 性能、低功耗的 32 位微处理器,适用于通信、工业、医疗、安防、仪器仪表、智能家居 等众多领域。

3.1 例程总览................................................................................................14

ARM8060嵌入式主板说明书

ARM8060嵌入式主板说明书北京阿尔泰科技发展有限公司Beijing Art Technology Development Co.,Ltd.!安全须知电气方面安全性为避免可能的电击造成严重损害,在移动主板之前,请先将主板的电源切断。

当您要加入硬件设备到系统中或者要移除系统中的硬件设备时,请务必先连接该设备的信号线,然后再连接电源线。

请确定电源的电压设置已调整到所规定的电压标准值。

操作方面的安全性在您安装主板以及加入硬件设备之前,请务必详细阅读本手册所提供的相关信息。

在使用本产品之前,请确定所有的排线、电源线都正确地连接好。

若您发现有任何重大的瑕疵,请尽快联系我们或您的经销商。

为避免发生电气短路情形,请务必将所有没用到的螺丝、回形针及其它零件收好,不要遗留在主板上。

灰尘、湿气以及剧烈的温度变化都会影响主板的使用寿命,因此请尽量避免放置在这些地方。

当操作系统启动过程中,请勿断电,为避免损坏主板芯片系统运行过程中,防止静电,最好不要用手接触主板若在本产品使用上有任何的技术性问题,请和我们的技术支持人员联系。

目录目录 (2)1.产品简介 (3)1.1产品概述 (3)1.2 产品特点 .................................................................................................................. 错误!未定义书签。

2产品特性 (11)2.1跳线说明 (11)2.2 外围设备接口连接 (11)2.3 软件特性 ................................................................................................................ 错误!未定义书签。

3.电气参数及机械特性 (18)附录A 订购信息 (19)附录B 应用程序开发环境 (19)1.产品简介1.1产品概述ARM8060是北京阿尔泰科技发展有限公司基于Atmel公司ARM926EJ-S内核的AT91SAM9261处理器,结合PC104总线规范设计的一款具有极高性价比、结构和尺寸极其紧凑并且功耗极低的工业级嵌入式主板,其上运行嵌入式Linux 或WinCE操作系统,可以处理多种计算任务。

ATSAM中文数据手册

11. ARM926EJ-S 处理器概论11.1 概论ARM926EJ-S 处理器是通用微处理器ARM9 家族中的一员。

ARM926EJ-S 属于5TEJ 版ARM 架构,针对的是多任务应用,包括全储存器管理,高性能,小核心尺寸和低功耗都是其重要的特点。

ARM926EJ-S 处理器支持32 位ARM 和16 位THUMB 指令集,使得用户能在高性能和高代码密度上取得平衡。

支持8 位Java 指令集并且包括Java 字节代码有效执行的功能部件,提供和JIT(Just-In-Time 编译器)相似的Java 性能,这些性能为下一代Java 无线和嵌入式的设备提供了有力支持。

为了提高DSP 性能,还包含了一个增强的乘法器设计。

ARM926EJ-S 处理器支持ARM 调试架构,包括对辅助硬件和软件调试的逻辑。

ARM926EJ-S 提供了一个完全高性能的处理器子系统,包括:●ARM9EJ-S 整核●一个存储器管理部件(MMU)●独立的指令和数据AMBA TM AHB 总线接口●独立的指令和数据TCM 接口11.2 方块图图11-1 ARM926EJ-S 内部功能方块图11.3 ARM9EJ-S 处理器11.3.1 ARM9EJ-S 运行状态ARM9EJ-S 处理器能用三种不同状态操作,每种状态带一个特殊指令集:●ARM 状态:32 位,字对齐ARM 指令●THUMB 状态:16 位,半字对齐的THUMB 指令●Jazelle 状态:可变长度,字节对齐的Jazelle 指令在Jazelle 状态,按字(words)取所有的指令。

11.3.2 状态切换ARM9EJ-S 核的操作状态在以下状态间切换:●用BX 和BLX 指令切换ARM 状态和THUMB 状态,并加载到PC●用BXJ 指令切换ARM 状态和Jazelle 状态所有的异常都在ARM 状态下进入,处理和退出。

如果一个异常发生在Thumb状态或Jazelle 状态,处理器还原到ARM 状态。

一体化低功耗宽频带数字地震仪研制

一体化低功耗宽频带数字地震仪研制彭朝勇;杨建思;薛兵;陈阳;朱小毅;张妍;李江【摘要】流动观测台网与固定观测台网的结合是当前地震观测技术系统发展的一个趋势.针对流动观测时地震计与地震数据采集器互相独立、携带不方便、功耗高的问题,自主研发了一款适合流动观测的集地震信号提取、数据采集、记录和服务为一体的数字地震仪.该仪器具有频带宽(60 s-80 Hz)、动态范围高(>140 dB)、功耗低(0.6 W)、携带方便(整机重量在15kg左右,包括供电系统、GPS天线和包装箱)等特点.详细介绍了该地震仪的外观结构、整体硬件结构、低功耗处理技术和所采用的灵敏度校正、标准方位和正交校正技术.对仪器的主要性能参数指标进行了严格的测试,并给出了具体的测试结果.该仪器研制完成后,投入到了青海玉树Ms7.1地震震后流动观测中.从半年的实际使用结果来看,该仪器能够满足流动观测的要求.【期刊名称】《地震学报》【年(卷),期】2014(036)001【总页数】10页(P146-155)【关键词】一体化;宽频带地震仪;低功耗;仪器校正;流动观测;玉树Ms7.1地震【作者】彭朝勇;杨建思;薛兵;陈阳;朱小毅;张妍;李江【作者单位】中国北京100081 中国地震局地球物理研究所;中国北京100036 中国地震局地震预测研究所;中国北京100081 中国地震局地球物理研究所;中国北京100036 中国地震局地震预测研究所;中国北京100036 中国地震局地震预测研究所;中国北京100036 中国地震局地震预测研究所;中国北京102628 北京港震机电技术有限公司;中国北京100036 中国地震局地震预测研究所【正文语种】中文【中图分类】P315.62引言流动数字地震台网作为“‘十五’中国数字地震观测网络”项目建成的新一代中国数字地震观测系统的一部分,在我国地震观测事业中发挥着重要作用(刘瑞丰等,2008;郑秀芬等,2009).流动数字地震观测设备必须满足流动性要求(郭建,刘光鼎,2009;陆其鹄等,2009),因此组成流动数字地震观测系统的各个设备必须具有体积小、重量轻、功耗低等特点(游庆瑜等,2003;李江等,2010).另外,流动观测现场一般都不具备交流电源,而是采用蓄电池或太阳能电池供电.在这种情况下,观测设备的功耗越低,则耗电越少,采用容量不太大的蓄电池或太阳能电池即可工作,从而有助于降低观测成本.当前,我国流动地震观测中使用的观测仪器,有进口的,也有国内自制的,基本都是将独自存在的地震计与地震数据采集器通过电缆连接而成(陈祖斌等,2006;王超等,2007).在这种情况下,进行流动观测时,需要同时运输地震计和地震数据采集器,增加了观测成本和安装成本.目前,国际上一体化低功耗宽频带数字地震仪的种类并不多,成为正常销售产品的只有英国Guralp公司生产的CMG-40TDE.在本项设备完成研制之前,我国还没有自行研制的用于野外流动地震观测的一体化数字地震仪.为此,在中国地震局统一组织下,中国地震局地震预测研究所开发出了新型的集地震信号提取、数据采集、记录和服务为一体的低功耗宽频带数字地震仪,并于2010年5月将该仪器投入到青海玉树MS7.1地震活动现场进行流动观测.1 整机系统总体设计与结构图1 宽频带数字地震仪总体结构Fig.1 Global structure of the broadbanddigital seismograph一体化低功耗宽频带数字地震仪研制项目组在经过充分的预研、调查和研制准备后,确定了总体技术方案.图1是该地震仪的外观和内部实体图.从图1可以看出,整机系统外观结构由以下部分组成:底座、三分向宽频带数字机械摆、4层电路板和机壳.底座上安装航空插座,向外提供各种输入/输出接口.为了减少接口数量,我们将网络通信接口和串口通信接口合二为一,只向外提供电源、通信和授时模块3个接口.另外,底座上还添加了3个底脚螺丝和一个水平气泡用于系统安装时调平.宽频带数字地震仪的机械摆通过扁平电缆与上层电路板之间进行连接.从底座伸出3根立柱,用于支撑4块电路板:前级放大电路板(AMP板)、反馈及采集电路板(ADC板)、电源及控制电路板(PWR板)和CPU板.AMP板生成驱动地震计电容极板的振荡信号,并完成地震计输出小信号的放大和解调;ADC板负责将地震计输出的模拟电平转换成数字量,并完成地震计反馈控制;PWR板提供仪器所有的数字电路供电(+3.3V)、模拟电路供电(±12V,±3.5V)以及部分控制电路供电;CPU板上运行Linux操作系统,提供数据采集管理、数据存贮、数据网络服务等功能.4层电路板之间分别用一定高度的有机玻璃套环进行定位,下方通过立柱上的小台阶进行定位,上方通过金属套环和顶丝固定在立柱上.为了便于携带安装,机壳上设计有拎手,同时在拎手上增加“N”方向指示.机壳上还设计了一个CF卡盖,方便用户在野外观测时随时更换CF卡.下面从硬件模块、低功耗处理和仪器校正等3个方面进行详细说明.1.1 硬件功能设计该地震仪对应的硬件结构如图2所示,由4大部分组成:宽频带地震计、数据采集、FPGA控制和微控制单元.图2 宽频带数字地震仪硬件结构Fig.2 Hardware structure of the broad-band digital seismograph1.1.1 宽频带地震计宽频带地震计是由一个垂直分向和两个水平分向组成的三位一体式结构的地震计.每个分向均为一体式独立结构,可以单独拆卸下来,其工作原理如图3所示.当地面运动时,由电容换能器产生的电压信号经放大后进入反馈网络产生反馈电流,流经反馈线圈产生反馈力.1.1.2 高精度数据采集一体化地震仪数据采集部分由前置放大、24位A/D转换、辅助采集通道、高稳定度晶体振荡电路等单元组成.为了将地震计输出的微小地震信号调整成24位A/D转换器所需要的信号大小,采集器三通道前置放大由3级基本电路组成.第一级小信号输入的放大电路采用场效应管组成的单端输入、双端输出的差分放大电路.使用场效应管可以提高输入阻抗,达到与电容换能器极板匹配的目的.第二级解调电路部分通过控制信号对高速模拟开关MAX353进行通道切换,从而达到调制目的.第三级放大电路由运算放大器LT6011和电容、电阻构成,形成差分平衡输出.实际使用中,该电路仅仅保留了直流增益.24位A/D转换器采用TI公司生产的ADS1281,其内部集成了可配置的数字滤波器.在电路连接上,采用引脚设置方式.在4.096MHz的工作时钟下,第一级SINC滤波器的抽取比为16;第二级为最小相位FIR数字滤波,抽取比为32.ADS1281的输出采样率为2kHz.辅助通道采样率固定为10Hz,用于电源电压量监测和宽频带地震计三分向零位监测.所采用的ADS7822是一种12位串行高速、采集速率可达75kHz的微功耗ADC芯片.ADS7822的输入端为“多选一”模拟开关,输入端采用高阻值电阻分压网络实现±10V的采集量程.由于ADS7822为单电源供电设计,模拟输入端电压范围不能超过供电电压范围,因此需要通过运算放大器对采集到的模拟量进行电平转化及平移.采集到的数字信号通过SPI接口送到CPU板.晶体振荡器主要提供数据采集ADS1281的采样时钟和可编程门阵列FPGA的时钟计数脉冲.选择稳定度优于10-6的TCXO模块,并带有压控输入端,在对钟的状态下,对晶振进行频率调节.TCXO晶振采用T11A(8.192MHz),其工作电压为3.3VDC±5%,频率稳定度≤±1.0×10-6,控制电压变化范围为0.5—2.5V(中心电压1.5VDC),频率牵引范围≥±10×10-6,斜率为正.由12位DAC7513提供TCXO的控制电压,通过CPU的SPI接口进行控制.1.1.3 FPGA控制逻辑一体化地震仪对数据采集通道、GPS码和SSC数据收发进行逻辑控制的所有功能仅由1枚FPGA芯片完成(Yu et al,2010).该芯片采用Altera公司出产的具有20 060个逻辑门的EP1C3T144C8芯片.FPGA控制逻辑采用模块化的设计方法,其中包括:① 数据采集模块.每个ADS1281对应一个采集模块,当检测到DRDY有效时,FPGA向ADS1281连续发送32个SCLK信号,同时读取输出的32位数据到32位移位寄存器,等32位数据读取完成时,移动该数据到锁存寄存器,并设置数据标识为“有效”,以便SSC数据上行模块获取该数据;②IRIG-B码接收模块.根据IRIG-B码格式对GPS输入信号进行解析并生成6个16位数据缓存到6个寄存器中;③ 秒沿处理模块.当PPS秒沿到时,获取4.096MHz晶振计数值并缓存;④SSC数据上行模块.定时检测每个锁存的寄存器是否有新的数据,如果有,则根据类型对数据增加数据类型标识,生成32位数据并通过SSC将数据发送到CPU;⑤SSC数据下行模块.当进行地震计标定处理时,将标定数据从CPU通过SSC传输到1 024字节的FIFO缓冲区,并按照每1ms 1个数据的方式发送到DA 控制器进行标定控制.1.1.4 微控制单元微控制单元选用Atmel公司的AT91SAM9263CPU.该CPU采用ARM926EJ-S核心,最高时钟为240MHz.CPU与FPGA之间采用同步串行控制器SSC进行数据接收与命令发送操作.由于SSC接口配置了专用外设DMA控制器PDC,显著降低了外设与存储器之间数据传输所需的时钟周期数,因此提高了微控制器的性能,数据传输效率高,CPU负荷小,不会出现采集数据丢失的现象.微控制单元内置嵌入式Linux操作系统,同时在操作系统核心内实现了数据采集管理、FIR数字滤波运算(同时进行1,10,20,50,100,200和500Hz线性相位和最小相位滤波计算)、地震计控制等功能,并通过网络接口提供实时数据服务和参数设置.软件系统的主要功能包括:参数设置与管理、实时数据记录(存储于8GB CF卡上)、地震事件检测与记录、网络数据服务(提供低延时网络数据传输功能,用于“预警”处理)、主动发送服务、串口数据服务、标定处控制(提供脉冲、正弦、伪随机二进制码等3种标定信号)、GPS时间服务、地震计调零、存储空间监测与管理和系统运行监控等(王洪体等,2006).1.2 低功耗处理为了降低整机系统功耗,使其能够适合流动观测的要求,在仪器设计时作了以下4种处理:①通过修改U-Boot和Linux内核程序,将ARM CPU主频频率由原来的200MHz降低到143MHz;② 增加了网络电源开断控制按钮,使得在不进行网络数据传输的情况下,用户可以关闭网络电源;③ 授时服务由原来的连续GPS授时模式,修改为间隔式GPS授时,即当一次GPS授时完成后,自动关闭GPS电源,并在下一次授时时,重新打开GPS电源进行服务;④LED显示15分钟后,自动关闭其背光电源.1.3 仪器校正传统的地震计与地震数据采集器分开设计的方式极少考虑对仪器的输出数据进行各种校正处理,主要是因为地震计与地震数据采集器不进行成套销售,或者由于某些公司只生产地震计或者地震数据采集器,所以用户方进行数据校正难度很大.采用一体化的设计,可以大大降低该项工作的难度,直接在仪器生产时就可以进行数据校正.1.3.1 灵敏度校正由于各台仪器的灵敏度往往都会有一些偏差,为了将3个通道的灵敏度都调节到500 counts/μm/s,需要对灵敏度因子进行修正.具体方法为:首先通过对比法(专业设备性能指标测试检测方法标准研究课题组,2011)得到地震仪的三分向灵敏度S,然后分别计算三分向灵敏度调节因子:将上式得到的调节因子K存入仪器的存储器中,最后在获取数据时自动乘以该因子就可以得到灵敏度校正后的输出结果.1.3.2 标准方位和正交性校正由于地震计内部装配误差等因素,地震计实际传感方向与标示方向并不一致.实际传感方向用xyz来表示,它们与ENU不重合,而是有一个小角度的误差,可采用如下公式进行消除:式中,vx,vy和vz是地震计原始记录的EW,NS和UD 3个地动速度分量;vEW,vNS和vUD是通过校正后输出的数据;αNS,αEW为地震计NS分向和EW分向的方位角;αUD为地震计垂直分向在水平面投影的方位角;βNS和βEW 分别为地震计NS分向和EW分向相对于水平面的仰角,βUD为地震计垂直分向偏离铅锤线的角度.6个角度量可通过对比法或者振动台法测得的结果经过拟合后得出(专业设备性能指标测试检测方法标准研究课题组,2011).2 系统测试2.1 简介样机完成后,我们分别于2010年3月和9月在中国地震局地震预测研究所测震实验室和河北沽源九连城地震计测试基地依据相关测试标准(Charles et al,2010;专业设备性能指标测试检测方法标准研究课题组,2011)对其进行了各项参数指标测试.在测试中使用的具体测试设备有:1)超低失真度信号发生器(DS360):失真度为-110dB.2)温湿度试验箱(SETH-020L):温度范围为-50—100℃,温控精度为0.1℃. 3)标准时钟:GPS授时,具有时、分、秒脉冲输出,准确度为1μs.4)甚低频振动测试系统:频率范围为0.000 2—250Hz(有中国计量科学院出具的检定证书和校准证书).2.2 主要参数指标测试及其结果1)灵敏度测试.测试时,将样机平稳地放在振动台台面中心,调整灵敏轴使其与振动方向平行,记录振动台输出信号的速度值.从计算机记录文件读取地震仪的输出数字值,获取到的测试结果如表1所示.2)线性度测试.由于地震计的频率特性为带通滤波器,不能使用静态直流信号输入进行测试,只能使用正弦信号进行交流测试.具体测试时,测试频率选择5Hz,然后通过调整标准信号源输出幅度x,同时记录样机的输出幅值y,最后进行线性拟合并求出线性度误差,测试结果见表2.表1 灵敏度测试结果Table 1 Test result of sensitivity测试频率/Hz响应灵敏度/(coun t·μm-1·s-1)UD EW NS 5.0 503.774 502.226 506.015表2 线性度测试结果Table 2 Test result of linearity频率/Hz信号源输入/V UD被测仪器输出/count线性拟合结果/count EW被测仪器输出/count count 1 1321265 1318186 1046320 1044447 1015009 101线性拟合结果/count NS被测仪器输出/count线性拟合结果/0.234% 0.179%0.117%3827 2 2640482 2637392 2091207 2088685 2028991 2027645 3 3957207 3956597 3134036 3132922 3041847 3041463 45274885 5275803 4176722 4177160 4055317 4055280 5 6591787 6595009 5218334 5221397 5067499 5069098 5.0 6 7910342 7914214 6261688 6265635 6080917 6082916 7 9228467 9233417 7306788 7309872 7094492 7096734 8 10549850 10552625 8352665 8354109 8109529 8110552 9 11872650 11871831 9399388 9298347 9124821 9124369 10 13199180 13191037 10448010 10442584 10141650 10138187线性度3)幅频特性测试.测试频点选择16个,分别为0.008 3,0.01,0.016 7,0.025,0.05,0.1,1,5,9,19,33,39,44,49,52和58Hz.系统实际测得的经过归一化后的幅频特性曲线如图4所示.4)动态范围测试.使用正弦波测量地震计有效观测频带内限幅电平与频率的关系.限幅电平描述了地震计观测大信号的能力,具体测试结果见图5.根据测试结果可得系统的动态范围大于140dB.表3 4种处理方式可节省的功耗Table 3 Saved power consumption for four processing modes处理方式可节省功耗/W 0.2关闭网络电源 0.3关闭GPS电源 0.2 LED显示关闭降低CPU主频0.35)系统功耗测试.按照1.2节中描述的方式对4种处理方法分别进行了功耗测试,具体测试结果见表3.从表3可以看出,4种处理方式均可明显降低整机系统功耗.在省电模式下可节省1W左右,而整机系统功耗也从原来的1.6W降低到了0.6W. 6)多采样率同时输出和低延时输出测试.整机系统在上电启动后,通过在台式机上同时运行多个客户端软件,并在每个软件界面上针对每个分向数据设置不同的采样率,验证了多采样率同时输出功能;通过客户端软件设置不同的输出间隔(分别为100,200,500ms和1s),验证了低延时输出功能.2.3 与同类型仪器的比较通过与Guralp公司生产的一体化宽频带地震仪CMG-40TDE对比,可以得出,该地震仪在频带范围、动态范围、系统功耗、灵敏度等方面与CMG-40TDE非常接近.从噪声水平方面来讲,CMG-40TDE是一款中等自噪声(Ringler,Hutt,2010)的地震仪,而该地震仪的噪声相对来说要低一些.另外,该地震仪在软件功能方面还具有CMG-40TDE和其它地震数据采集器不具备的一些特点:多采样率同时输出和低延时数据输出.多采样率同时输出可以大大提高地震仪产出数据的利用率,使得地震仪在同一时刻既可以输出50/100/200Hz数据用于常规的台站观测或者流动观测,又能输出1Hz数据用于全球地震学研究;而低延时数据输出方式则可以将该地震仪用于地震预警数据传输.3 试验研究2010年4月14日7时49分,在青海省玉树县(33.23°N,96.61°E)发生MS7.1地震,震源深度18km.玉树地震是继汶川地震后的又一次震灾严重的地震.玉树地震后,中国地震局科学技术司立即组织了“玉树地震综合科学考查”.其中,野外流动地震观测由中国地震局地球物理研究所与青海省地震局共同组成的流动地震观测科考队负责.根据中国地震局的统一部署和要求,整个科考队于2010年5月2日出发,共建立了两个观测项目:一个是在震源区架设由14个流动地震台站组成的密集台阵,分布在玉树地震断层两侧并覆盖震源区;另一个是北起青海花石峡,南至西藏内乌齐架设的由16个(其中4个与密集台阵共用)流动地震台站组成的600 km地震大剖面(图6).一体化宽频带地震仪共计12台,全部应用于第二个观测项目上,包括QSX(清水乡)、MAD(玛多台)、HHX(黑河乡)、YNG (野牛沟)、ZMT(扎马台)、ZDT (扎朵镇)、ZQT (珍秦台)、NQT (囊谦)、BZT (白扎乡)、JQT(吉曲台)、JSK(甲桑卡)和JDX(吉多乡).流动地震观测持续了半年,记录了大量的区域地震事件和远震事件.其中3级以上地震有30余次,4级以上地震有10余次,5级以上地震有2次.记录到的最大地震为MS5.9,发生于2010年5月29日10点29分,位于(33.3°N,96.3°E),震源深度为10km(波形见图7).根据这些记录到的余震资料,可以对地震序列的空间分布进行精确定位,反演地震的震源过程,并根据地震学方法得到震源区的深部结构图像,获得该震源区的构造异常分布和区域深部构造环境.图7 JDX台站记录到的2010年5月29日青海省玉树MS5.9地震Fig.7 The29May 2010 MS5.9earthquake in Yushu,Qinghai of China,recorded by the station JDX4 结论针对流动观测中传统的由于地震计与地震数据采集器单独存在而出现的运输不方便、功耗大的问题,本文详细介绍了一款将地震信号提取、数据采集、记录和服务集为一体的低功耗宽频带数字地震仪.该地震仪具有频带宽(60s—80Hz)、动态范围高(>140dB)、功耗低(0.6W左右)、携带方便(整机系统在15kg左右,包括供电系统、GPS天线和包装箱)等特点.另外,该仪器还具有多种采样率同时输出和低延时数据输出等其它同类仪器不具备的特点,进一步扩大了本仪器的应用范围.该仪器在研制过程中进行了大量的实验室和台站测试.仪器研制完成后,投入到了青海玉树MS7.1地震震后实际流动观测试验中,并取得了详尽的第一手观测资料.通过在青海玉树地震震后流动观测试验中的具体应用,不管从仪器的运输和携带上,还是从仪器的稳定运行上都可以得出,该仪器是一款非常适合流动观测的设备.与国外同类仪器相比,该仪器还具有很好的性价比.下一步将从更低的功耗、更轻的整机系统重量和更稳定的系统运行等3个方面着手,进一步提高该系统的各项性能指标.参考文献陈祖斌,滕吉文,林君,张林行.2006.BSR-2宽频带地震记录仪的研制[J].地球物理学报,49(5):1475--1481.Chen Z B,Teng J W,Lin J,Zhang L X.2006.Design of BSR-2broad band seismic recorder[J].Chinese J Geophys,49(5):1475--1481(in Chinese).郭建,刘光鼎.2009.无缆存储式数字地震仪的现状及展望[J].地球物理学进展,24(5):1540--1549.Guo J,Liu G D.2009.Current situation and expectation of cable-less seismic acquisition system[J].Progress in Geophys,24(5):1540--1549(in Chinese).李江,庄灿涛,薛兵,朱小毅,陈阳,朱杰,彭朝勇,叶鹏,梁鸿森,刘明辉,杨桂存,周银兴,林湛,李建飞.2010.宽频带海底地震仪的研制[J].地震学报,32(5):610--618.Li J,Zhuang C T,Xue B,Zhu X Y,Chen Y,Zhu J,Peng C Y,Ye P,Liang H S,Liu M H,Yang G C,Zhou Y X,Lin Z,Li J F.2010.Development of broadband ocean bottom seismogram(OBS)[J].Acta Seismologica Sinica,32(5):610--618(in Chinese).刘瑞丰,高景春,陈运泰,吴忠良,黄志斌,徐志国,孙丽.2008.中国数字地震台网的建设与发展[J].地震学报,30(5):533--539.Liu R F,Gao J C,Chen Y T,Wu Z L,Huang Z B,Xu Z G,SunL.2008.Construction and development of digital seismograph networks in China[J].Acta Seismologica Sinica,30(5):533--539(in Chinese). 陆其鹄,吴天彪,林君.2009.地球物理仪器学科发展研究报告[J].地球物理学进展,24(2):750--758.Lu Q H,Wu T B,Lin J.2009.A research report on development of instrument science for geophysics[J].Progress in Geophys,24(2):750--758(in Chinese).王超,宋克柱,唐进.2007.高性能水平地震数据采集系统设计与实现[J].吉林大学学报:工学版,37(1):168--172.Wang C,Song K Z,Tang J.2007.High performance data acquisition system for marine seismic survey[J].Journal of Jilin University:Engineering and Technology Edition,37(1):168--172(in Chinese). 王洪体,庄灿涛,薛兵,李江,陈阳,朱小毅,娄文宇,刘明辉.2006.数字地震观测网络通讯与记录系统[J].地震学报,28(5):540--545.Wang H T,Zhuang C T,Xue B,Li J,Chen Y,Zhu X Y,Lou W Y,Liu M H.2006.A network communication and recording system for digital seismic observation[J].Acta Seismologica Sinica,28(5):540--545(in Chinese).游庆瑜,刘福田,冉崇荣.2003.MC1微功耗宽频带数字地震仪[J].地球物理学报,46(3):347--351.You Q Y,Liu F T,Rang C R.2003.Micro-power broad digital seismograph [J].Chinese J Geophys,46(3):347-351(in Chinese).郑秀芬,欧阳飚,张东宁,姚志祥,梁建宏,郑洁.2009.“国家数字测震台网数据备份中心”技术系统建设及其对汶川大地震研究的数据支撑[J].地球物理学报,52(5):1412--1417.Zheng X F,Ouyang B,Zhang D N,Yao Z X,Liang J H,ZhengJ.2009.Technical system construction of Data Backup Centre for China Seismograph Network and the data support to researches on theWenchuan earthquake[J].Chinese J Geophys,52(5):1412--1417(in Chinese).专业设备性能指标测试检测方法标准研究课题组.2011.地震计测试方法及技术要求[R].北京:中国地震局地震预测研究所:3--38.Research Group of Standards for Professional Equipment Performance Testing Methods.2011.Seismometer Test Methods and Technical Requirements[R].Beijing:Institute of Earthquake Science,China Earthquake Administration:3--38(in Chinese).Charles R H,John R E,Fred F,Robert L N,Erhard W.2010.Guidelines for Standardized Testing of Broadband Seismometers and Accelerometers [R].Reston,Virginia:US Geological Survey:1--61.Ringler A T,Hutt C R.2010.Self-noise models of seismic instruments [J].Seism Res Lett,81(6):972--983.Yu X L,Sun Y R,Liu J Y,Miao J F.2010.Design and realization of synchronization circuit for GPS software receiver based on FPGA[J].Journal of Systems Engineering and Electronics,21(1):20--26.。

基于互联网的通信操作面板控制系统

基于互联网的通信操作面板控制系统于德海;李培杰【摘要】设计了一套基于Android手机远程控制操作面板的系统;该系统硬件平台集成了ARM芯片和其他外围设备,并移植了Linux系统;在此系统上使用Hamlib对不同型号的通信设备进行控制,并对设备获得的音频数据使用RTP协议实时传输到手机,对设备的参数信息使用UDP协议反馈给手机;同时手机通过P2P协议与ARM平台通信,并通过UDP协议发送控制命令来控制设备的操作面板。

%A system based on remote control operation panel of Android phone is designed .The system hardware platform integrates ARM chip and other peripheral equipment , and it transplants Linux system .Hamlib is used to control the communication equipment of different types , audio data obtained from the equipment is sent timely to the phone through RTP protocol , the parameters of the equip-ment is sent back to the phone through UDP protocol .Based on P2P protocol and ARM platform communication , the mobile phone sends the order to control the operation panel through UDP protocol .【期刊名称】《长春大学学报(自然科学版)》【年(卷),期】2016(026)003【总页数】5页(P39-43)【关键词】操作面板;Hamlib;实时音频传输;远程控制【作者】于德海;李培杰【作者单位】长春工业大学计算机科学与工程学院,长春130012;长春工业大学计算机科学与工程学院,长春130012【正文语种】中文【中图分类】TP311随着无线通信设备的发展,传统的通信设备也正在向着互联网+的时代发展。

恩智浦 ARM926EJ-S处理器 说明书

上,还有一个灵活的LCD控制器,它支持STN和TFT面板,并提供一 个专用DMA控制器和高达1024 x 768 的可编程显示分辨率及16M 色。 多个串行通信接口提高了设计灵活性,提供了较大的 缓冲区容 量,并可提供较高的处理能力。LPC3240和LPC3250 一个带DMA控制器的10/100 Ethernet MAC接口。 此外每个LPC32x0微控制器还有一个USB接口,支持DEVICE,HOST和 On-The-Go (OTG)工作、4个标准16C550 UART (一个支持IrDA)、3 个高速(高达921,600 bps)UART、2个快速I C总线(400 Kbps)接口 (支持从站、单主机和多主机)、2个SPI/SSP端口和自动键盘扫 描功能 (支持8x8键) 。 此外每个LPC32x0微控制器还有2个I S接口, 每个接口均有独立的输入通道和输出通道。每个通道均可独立运 行于3个管脚;而只需四个管脚,就可构成一个I S接口的输入和输 出。 每个LPC32x0微控制器都有一个带3个通道和一个触摸屏接口的 10-位、 400-kHz A/D转换器、 5个带捕获/比较通道的32-位定时器、 一个由实时时钟驱动的32-位定时器、11个PWM通道和一个看门狗 定时器。此外每个LPC32x0微控制器还有一个具有独立时钟和功率 耗域的实时时钟、一个专用32-kHz振荡器、一个安全数字(SD)接 口和一个能支持多达73个中断源的集成中断控制器。 数据传送是由一个8路通用DMA控制器进行管理的,该控制器可用 于SD端口、UART、I S端口、SPI接口或者存储器间的传送。 7层、32位104-MHz AHB矩阵为7个AHB主设备(D-高速缓存、I-高速 缓存、2个DMA、Ethernet MAC、USB控制器和LCD控制器)各提供一 条独立总线。这样便消除了仲裁延迟,除非出现两台主设备同时 尝试访问同一台从设备的情况。

2016嵌入式系统复习题

一、单项选择题下面关于哈佛结构描述正确的是( A )。

A、程序存储空间与数据存储空间分离B、存储空间与IO空间分离C、程序存储空间与数据存储空间合并D、存储空间与IO空间合并下面哪一种工作模式不属于ARM特权模式( A )。

A、用户模式B、管理模式C、软中断模式D、FIQ模式ARM9TDMI的工作状态包括( D )。

A、测试状态和运行状态B、挂起状态和就绪状态C、就绪状态和运行状态D、ARM状态和Thumb状态指令“LDMIA R0!, {R1, R2, R3, R4}”的寻址方式为( C )。

A、立即寻址B、寄存器间接寻址C、多寄存器寻址D、堆栈寻址5、对寄存器R1的内容乘以4的正确指令是( C )。

A、LSR R1,#2B、LSL R1,#2C、MOV R1,R1, LSL #2D、MOV R1,R1, LSR #26、下面指令执行后,改变R1寄存器内容的指令是( D )。

A、TST R1,#2B、ORR R1,R1,R1C、CMP R1,#2D、EOR R1,R1,R17、下面哪一种功能单元不属于I/O接口电路。

( D )A、USB控制器B、UART控制器C、以太网控制器D、LED8、下面哪个操作系统是嵌入式操作系统。

(B)A、Red-hat LinuxB、µCLinuxC、Ubuntu LinuxD、SUSE Linux9、使用Host-Target联合开发嵌入式应用,( B )不是必须的。

A、宿主机B、银河麒麟操作系统C、目标机D、交叉编译器10、下面哪个系统不属于嵌入式系统( D )。

A、MP3播放器B、GPS接收机C、“银河玉衡”核心路由器D、“天河一号”计算机系统11. RS232-C串口通信中,表示逻辑1的电平是( D )A、0VB、3.3VC、+5V~+15VD、-5V~-15V12. 下列不属于RISC计算机特点的是( C )。

A、流水线每周期前进一步。

B、更多通用寄存器。

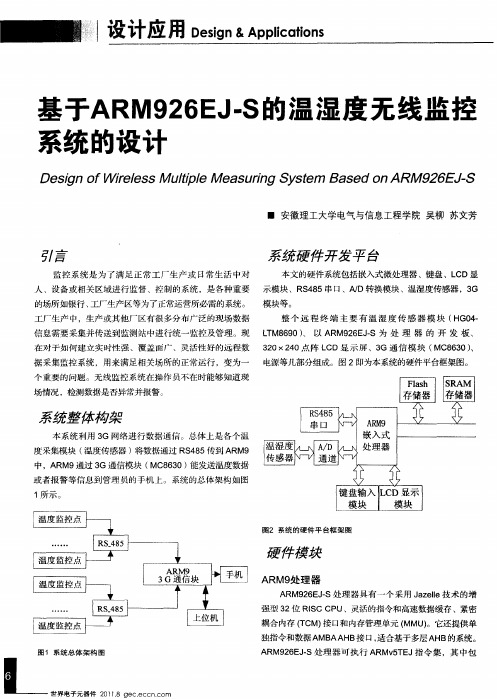

基于ARM926EJ-S的温湿度无线监控系统的设计

防止腐蚀性气体侵入 , 现场安装方便 。

液 晶显 示 模 块

本 系统 选用 J 3 0 4 B液 晶显 示模块来 显示相关 的 RD 2 2 0

数 据 采 集 的设 计 与 串 口传 输

对无线温度 监控系统 数据采集 的设计 和实现可分 为人

数据 或其他信息。J D 2 2 OB的工作 电压 为 33 R 3o 4 . V,液 晶 机界 面的设计 、数据采集 的通信 协议的制定 、数据采集 和 数据采集的 串口实现等几个部分 。 的对 比度可以通过编程来调节。液 晶显示控制器的主要工作 系统采集的现场数据通过串口发送到 AR 。数据的显 M9

在对 于如何建立 实时性强 、覆盖面 广、灵活性好的远程数 3 0×2 0点 阵 L 2 4 CD显 示屏 、3 G通 信 模 块 ( 8 3 、 MC 6 0)

据 采集 监控系统 ,用来满 足相关场所 的正常 运行 ,变为一 电源等几部分组成 。图 2即为本系统的硬件平台框架图。

个 重 要 的 问 题 。 无 线 监 控 系统 在 操 作 员不 在 时能 够 知 道 现

独指令和数据 A AA 接 口, MB HB 适合基于多层 AH B的系统 。

图 1 系统 总 体 架 构 图

AR 2 E - M9 6 JS处理 器可 执 行 A RMv T J指 令集 ,其 中包 5E

L …彻 … 一 m

括 功 能 得 到增 强 的 1 6 3 X 2位乘 法 器 ,可 进 行 单周 期 MA C运

引言

监 控系统 是 为 了满足 正常 工厂 生产 或 日常生 活 中对

系统硬件开ቤተ መጻሕፍቲ ባይዱ平台

本 文 的硬 件 系 统 包 括 嵌 入 式 微 处 理 器 、键 盘 、L D 显 C

LPC2214与AT91SAM9260功能对比

LPC2214与AT91SAM9260功能对比LPC2214 CPU所用功能表如下:剩余:P2.16;P2.17;P1.16;P3.26;P3.29;P1.17;P2.31;P2.30;P2.29;P2.28;P1.19;P0.6;P0.5;P0.4共14个10Mbps的速度已经足够;LPC2214芯片共有4个外部存储器组,其中铁电存储器占用Bank0,预留外部存储区占用Bank1,液晶占用Bank2,余下的Bank3可留给以太网芯片RTL8019AS使用;LPC2214芯片的两个SPI接口,A/D转换器占用SPI1,余下的SPI0也可以留给SPI接口的ENC28J60以太网芯片使用;另外以太网芯片的复位信号和中断信号还要占用2个I/O口。

ENC28J60是带有标准SPI接口的独立以太网芯片,SPI的速度最高10Mbps。

PMC-651系列装置采用的LPC2214芯片系统频率最高60MHz,外设时钟频率最高60MHz,其SPI 数据位速率最高为外设时钟的1/8,即7.5MHz。

ENC28J60只有28个引脚,可以大大简化电路设计。

ENC28J60采用3.3V供电,端口可以承受5V电压,端口作为输入没有问题,但是如果作为输出,可能会驱动能力不足,需要电压转换芯片。

LPC2214芯片的端口电压为3.3V,不存在这种问题。

图表 1 ENC28J60与微处理器的连接框图由上可知:在原有的基础上直接加以太网控制器来扩展以太网口是可行的。

ATMEL ARM9芯片AT91SAM9260集成了多项功能,包括一个配有数码相机接口、性能高达200 MIPS的ARM926EJ-S 内核;7个通用同步/异步收发器(USART);一个10/100以太网媒体访问控制器(MAC);一个12Mbps USB 设备和主机控制器以及相应的片上收发器;一个外部总线接口,能支持带有内置ECC、SD、SDIO 和多媒体卡(MMC) 接口的SDRAM、闪存以及NAND 闪存;3个同步串行控制器(SSC)、两个主/从串行外设接口(SPI)、一个3通道的16位定时器/计数器、双线接口(TWI)。

ATMEL芯片AT91SAM9G45

ATMEL 芯片AT91SAM9G45

介绍一款新的ATMEL 芯片AT91SAM9G45

推荐SAM9G45 开发板主频高达400MHz,可支持WinCE 和Linux 操

作系统的开发板调试,带有256MB NandFlash,2MB NorFlash,512KB EEPROM,4MB DataFlash,以及2 个64MB 的DDR2 SDRAM,并带有丰富的功能扩展:高速USB2.0(480MHz),音频输入,音频输出,10/100Mbps 网络,JTAG 调试接口,DBGU 串口,Micro SD 卡接口,SD/MMC 卡接口

AT91SAM9G45 芯片使用ARM926EJ-S 内核,它带有MMU 功能,有

一个64KB 的内部SRAM 和一个64KB 的内部ROM,并带有两个外部总线

接口,总共可支持4 块DDR2/LPDDR,SDRAM/LPSDR,静态存储器,CF

闪存或带ECC 校验的SLC NAND Flash。

AT91SAM9G45 芯片把用户接口的功能性和高速数据连接相结合,包

括LCD 控制器,电阻触摸屏,相机接口,音频,10/100M 以太网,高速

USB 和SDIO 等等。

随着处理器运行在400MHz 和多个速率超过100Mbps 的外设,AT91SAM9G45 使用高性能和带宽网络或本地存储媒体来提供良好的

用户体验。

AT91SAM9G45 支持最新的DDR2 和NAND 闪存接口来存储程序和数据。

一个与37 个DMA 通道相关的133M 的内部多层总线接口,以及一个双

外部总线接口,和一个能够用来配置紧密耦合内存(TCM)的64K 字节的分布。

ARM9系统的硬件设计

ARM9系统的硬件设计ARM9系统是一种高性能、低功耗的嵌入式处理器架构,广泛应用于智能手机、平板电脑、数字摄像机、网络设备等领域。

在设计ARM9系统的硬件时,需要考虑CPU、内存、外设接口、通信接口等多个方面,以提高系统性能和稳定性。

首先,作为ARM9系统的核心,CPU的选择至关重要。

ARM9处理器采用较为复杂的微结构设计,支持多种指令集,如ARM、Thumb、Jazelle等,具有较高的执行效率和代码密度。

在选择CPU时,需要根据系统的实际需求和预算情况进行合理的选择。

一般来说,可以选择一些主流的ARM9处理器,如ARM926EJ-S、ARM946E-S等。

其次,内存是ARM9系统中另一个重要的硬件组成部分。

内存主要包括RAM和ROM两部分,RAM用于存储程序和数据,ROM用于存储系统启动代码和固化程序。

在设计ARM9系统时,需要根据系统的实际需求选择合适的内存类型和容量,以保证系统的正常运行和高性能。

通常情况下,可以选择DDR SDRAM作为RAM,Flash作为ROM。

除了CPU和内存外,外设接口也是ARM9系统中的重要组成部分。

外设接口主要用于连接系统中的各种外设设备,如显示屏、键盘、鼠标、网卡等。

在设计ARM9系统时,需要考虑系统所需外设接口的类型和数量,选择合适的外设控制器和接口芯片,并保证其与CPU之间的数据传输速度和稳定性。

另外,通信接口也是ARM9系统中不可或缺的硬件组成部分。

通信接口用于连接系统与外部设备或网络之间的数据传输和通信,如UART、SPI、I2C、USB等接口。

在设计ARM9系统时,需要根据系统的通信需求选择合适的通信接口,并保证其与系统中其他硬件组件之间的兼容性和稳定性。

总的来说,设计ARM9系统的硬件需要全面考虑系统的实际需求和性能要求,合理选择CPU、内存、外设接口、通信接口等硬件组件,并进行良好的硬件布局和连接设计,以提高系统的性能和稳定性。

同时,还需要注意软硬件协同设计,保证软件和硬件之间的良好配合和协同工作,从而实现ARM9系统的稳定运行和高效工作。

ARM926EJ

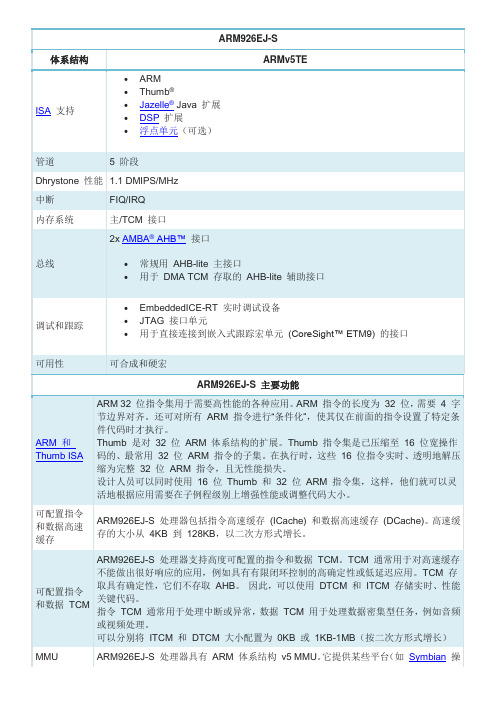

ARM926EJ-S体系结构ARMv5TEISA支持∙ARM∙Thumb®∙Jazelle® Java 扩展∙DSP扩展∙浮点单元(可选)管道 5 阶段Dhrystone 性能 1.1 DMIPS/MHz 中断FIQ/IRQ内存系统主/TCM 接口总线2x AMBA®AHB™接口∙常规用AHB-lite 主接口∙用于DMA TCM 存取的AHB-lite 辅助接口调试和跟踪∙EmbeddedICE-RT 实时调试设备∙JTAG 接口单元∙用于直接连接到嵌入式跟踪宏单元(CoreSight™ ETM9) 的接口可用性可合成和硬宏ARM926EJ-S 主要功能ARM 和Thumb ISA ARM 32 位指令集用于需要高性能的各种应用。

ARM 指令的长度为32 位,需要4 字节边界对齐。

还可对所有ARM 指令进行“条件化”,使其仅在前面的指令设置了特定条件代码时才执行。

Thumb 是对32 位ARM 体系结构的扩展。

Thumb 指令集是已压缩至16 位宽操作码的、最常用32 位ARM 指令的子集。

在执行时,这些16 位指令实时、透明地解压缩为完整32 位ARM 指令,且无性能损失。

设计人员可以同时使用16 位Thumb 和32 位ARM 指令集,这样,他们就可以灵活地根据应用需要在子例程级别上增强性能或调整代码大小。

可配置指令和数据高速缓存ARM926EJ-S 处理器包括指令高速缓存(ICache) 和数据高速缓存(DCache)。

高速缓存的大小从4KB 到128KB,以二次方形式增长。

可配置指令和数据TCM ARM926EJ-S 处理器支持高度可配置的指令和数据TCM。

TCM 通常用于对高速缓存不能做出很好响应的应用,例如具有有限闭环控制的高确定性或低延迟应用。

TCM 存取具有确定性,它们不存取AHB。

因此,可以使用DTCM 和ITCM 存储实时、性能关键代码。

指令TCM 通常用于处理中断或异常,数据TCM 用于处理数据密集型任务,例如音频或视频处理。

ARM926EJ-S特点

ARM九二六EJ-S Jazelle-增强型宏单元ARM926EJ-S宏单元是全面可合成的,并且它具有一款Jazelle技术增强型32位RISC CPU,容量灵活可变的指令和数据缓存,紧耦合存储器(TCM)接口和存储器管理单元(MMU)。

它还提供了独立的指令和数据AMBA总线规范AHB接口,特别适合基于多层AHB的系统。

ARM926EJ-S内核实现了ARMv5TEJ指令集,且包含一个增强型16x32位乘法器,能够在一个时钟周期内完成MAC运算。

ARMv5TEJ指令集包括16位定点DSP指令,可以增强许多信号处理算法和应用的性能,并支持Thumb和Java字节码的执行。

现在,ARM926EJ的硬化实现产品可以通过ARM代工计划获取应用∙下一代智能手机、通信设备和PDA∙3G基带和应用处理器∙基于平台操作系统的设备∙数码照相机∙音频和视频解码∙汽车信息娱乐系统特性∙32/16位RISC架构(ARMv5TEJ)∙32位ARM指令集,用于实现最高的性能和灵活性∙16位Thumb指令集,用于提高代码密度∙DSP指令扩展与单周期MAC运算∙ARM Jazelle技术∙支持包括Symbian OS、Windows CE和Linux在内的多种操作系统的MMU ∙容量灵活可变的指令和数据缓存∙带有等待状态支持的指令和数据TCM接口∙用于实时调试的EmbeddedICE-RT逻辑∙符合行业标准的AMBA总线AHB接口∙ETM接口,通过ETM9提供实时跟踪功能∙可选的MOVE协处理器,提供视频编码功能优势∙能够运行所有主流OS和现有中间件∙单芯片MCU、DSP和Java解决方案∙支持主流的Java运行时∙高效的Java字节码执行∙超低的Java功耗∙无可挑剔的Java JIT编译器性能∙Jazelle支持代码不会增加VM的大小∙简单的单处理器软件结构,不需要在整个MCU上进行软件分割∙一套开发工具包,用于降低开发成本并缩短开发周期时间∙业界领先的硬件供应商提供的多种来源∙代码兼容性支持向上移植到ARM10E系列∙工艺可移植的合成式设计∙为SoC设计人员提供的卓越的调试支持∙通过使用协处理器能够扩展指令集∙ARM-EDA参考方法交付物显著缩短了用于生成内核的专业技术实现以及生成行业标准视图和模型的时间。

ARM926EJ-S处理器

266MHZ 32位ARM926EJ-S处理器这款MCU带有全速HOST功能的USB OTG接口并连接了强大的外围设备。

其他设备包括7个UART,2个SPI,2个I2C,带有独立功耗域的实时时钟,NAND Flash和DDR存储器控制器,增加了设计的灵活性。

主要特点:●266MHz的32位ARM926EJ-S内核●90纳米工艺在掉电模式下的操作电压可降到0.9V●矢量浮点协处理器(VFP)●外部存储器接口:FLASH,SDR和DDR SDRAM ●65KB的SRAM,32KB的指令和数据缓存●带有全速HOST功能的USB OTG●通用的DMA控制器和内存管理单元●10位的A/D转换器●串行接口包括2个I2C接口, 2个SPI,7个UART●2个32位定时器和独立功耗域的实时时钟●SD存储卡接口●带仿真缓冲器的JTAG接口●内核电压是 1.35V(266MHz),或 1.2V(208MHz)●I/O引脚电压是1.8V,2.8V,3.0V●工作温度范围:-40℃到+85℃●LFBGA320封装(13x 13 x 0.9 mm3)应用:●工业●医疗器材●外围设备控制:打印机,扫描机,POS●GPS,电机,安全设备●网络控制功能特性:LPC3180/01是基于32位的,采用90纳米工艺具有一个矢量浮点协处理器和集成USB On-The-Go的ARM9内核的微控制器。

并且能够在低至0.9V的极低功耗模式下操作。

ARM9内核操作频率为266MHz,支持32KB 的数据缓存和32KB的指令缓存。

为NAND FLASH,SDRAM存储器和64KB的片上SRAM提供了外部存储器接口。

片上存储管理单元(MMU)支持实时操作系统,包括LINUX。

支持片上JA V A字节代码协处理器和认证应用。

向量浮点协处理器通过一个4到5的因数加速典型计算,并且在优化向量运算方式。

灵活的电源管理实现了高性能,尤其在浮点运算方面,当保留实时时钟和唤醒功能时可以关断核电源域。

基于ARM-Linux的MAX1303接口与驱动程序设计

基于ARM-Linux的MAX1303接口与驱动程序设计杨斌;满峰;姜秀杰;刘波【摘要】针对数据采集与处理系统的应用需求,设计了嵌入Linux的ARM9处理器LPC3250与16位AD采样芯片MAX1303的硬件接口和驱动程序.首先,描述了LPC3250和MAX1303的性能、特点以及硬件接口电路设计方案.然后,在硬件平台的基础上,详细地阐述了嵌入式Linux下MAX1303驱动程序的组成模块和具体实现方法,并给出了部分源代码以及对设备驱动的测试方法.测试结果表明,系统工作正常、稳定,采样结果正确,具有实际工程应用价值.%Aiming at the application requirement of data acquisition and processing system,the paper designs driver of MAX1303 based on embedded Linux and hardware interface circuit between LPC3250 and MAX1303.Firsdy,performance characteristics of both chips and scheme of hardware interface areintroduced.Secondly,on the bases of hardware platform,the composition and implemented method of MAX1303's driver under embedded Linux are elaborated in detail.Meanwhile,part of the source code and test methods of driver is given.The test results reveal that the system operations stably and has practical value.【期刊名称】《电子设计工程》【年(卷),期】2013(021)012【总页数】4页(P173-176)【关键词】LPC3250;MAX1303;SPI;嵌入式Linux;设备驱动【作者】杨斌;满峰;姜秀杰;刘波【作者单位】中国科学院空间科学与应用研究中心,北京100190;中国科学院研究生院,北京100049;中国科学院空间科学与应用研究中心,北京100190;中国科学院空间科学与应用研究中心,北京100190;中国科学院空间科学与应用研究中心,北京100190【正文语种】中文【中图分类】TH274在数据采集系统中,通常是通过传感器将自然世界的物理量转化成电量,电量是模拟量,必须经过模/数转换才能被系统的处理器读取。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Atmel推出基于ARM926EJ-S 的嵌入式微处理器

爱特梅尔公司 (Atmel Corporation) 宣布推出基于ARM926EJ-S 的嵌入式微处理器SAM9G10。

该器件是现有SAM9261S嵌入式微处理器的升级型号,扩大了性能功耗比的范围。

SAM9G10时钟频率为266 MHz (先前型款为188 MHz),总路线频率为133 MHz (先前则为94 MHz),在全功率模式下功耗不超过100 mW,比旧版本更进一步增强强了性能。

其它显着改进包括兼容RGB565的LCD控制器 (SAM9261S LCDC 则兼容IBGR555)、在所有I/O线路上提供施密特触发器 (Schmitt Trigger)、所有与外部总线接口 (EBI) 多任务之PIO线路的供电电压范围,从1.65V扩大到3.6V,使到1.8V NAND闪存可在其它PIO电压为3.3V时使用,并提升多媒体卡接口以增添SD输入/输出 (SDIO) 卡支持。

SAM9261S的推出,进一步扩展了爱特梅尔包括ARM和AVR32之32位微控制器产品系列。

为了让应用开发人员立即使用SAM9G10进行设计,爱特梅尔提供免费的Microsoft Windows Embedded CE和Linux 板级支持包 (Board Support Package, BSP),适合用于先进图形用户界面 (graphical user interfaces, GUI) 的 SAM9G10 和新近升级的SAM9R/RL 嵌入式微控制器。

除了操作系统内核之外,这些BSP还包括用于器件所有外设和接口的驱动程序,以及用于原始数据操作的代码模块。

两款BSP 均为应用代码开发提供了稳健的平台。

爱特梅尔ARM 微控制器市场总监Jacko Wilbrink评论道:“SAM9G10 是爱特梅尔建立基于ARM 的闪存微控制器和嵌入式微处理器的一条龙产品系列,为市场提供集合领先性能和更低功耗的微处理器的另一项举措。

而免费提供用于Linux 和WindowsCE 的全面的高质量板级支持包,已成为了我们嵌入式微处理器产品实现可持续的电子设备开发所不可或缺的部分。

”。