CAT809JSDI-T10中文资料

CAT809_810_cn

3脚微控制器电源监控电路-CAT809/810特性z对以下电源进行精密监控:+5.0V (+/- 5﹪, +/- 10﹪, +/- 20﹪),+3.3V (+/- 5﹪, +/- 10﹪),+3.0V (+/- 10﹪) 和+2.5V (+/- 5﹪)z提供2种输出配置:-CAT809:低有效复位-CAT810:高有效复位z在工业级温度范围的应用中可直接代替MAX809和MAX810z Vcc低至1.0V时复位有效z6uA的电源电流z抗电源的瞬态干扰z紧凑的3脚SOT23和SC70封装z工业级温度范围:-40℃~+85℃应用z计算机z服务器z手提电脑z线调制解调器(Cable modem)z无线通信z嵌入式控制系统z白色家电z功率计z智能仪器z PDA和手持式设备描述CAT809和CAT810是微控制器监控电路,用来监控数字系统的电源。

在工业级温度范围的应用中可直接代替MAX809和MAX810。

CAT809和CAT810产生一个复位信号,这个信号在电源电压低于预置的阈值时和电源电压上升到该阈值后的140ms内有效。

由于Catalyst半导体运用了底层浮动闸(floating gate)技术AE2TM,因此器件可以提供任何特定的复位阈值。

7个工业标准的阈值可支持+5.0V、+3.3V、+3.0V和+2.5V的系统。

CAT809的RESET是推挽输出(低有效),CAT810的RESET也是推挽输出(高有效)。

电源的快速瞬态变化可忽略,当Vcc低至1.0V时输出可保证仍处于正确状态。

CAT809/810可工作在整个工业级温度范围内(-40℃~+85℃),包含3脚SOT23和SC70两种封装形式。

阈值后缀选择器指定阈值电压阈值后缀名称4.63V L4.38V M4.00V J3.08V T2.93V S2.63V R2.32V Z管脚配置订购信息在器件型号的空白处插入后缀(L, M, J, T, S, R或Z)。

809芯片

809芯片809芯片是一款高性能、低功耗的嵌入式控制芯片,广泛应用于物联网、智能家居、智能穿戴设备等领域。

本文将从809芯片的核心特性、应用场景以及未来发展方向等方面进行详细介绍。

一、809芯片的核心特性1. 高性能:809芯片采用先进的处理器架构和高速时钟频率,能够快速、高效地处理各种复杂的运算任务,满足不同应用场景的需求。

2. 低功耗:809芯片采用先进的功耗管理技术,能够在保证高性能的同时,有效降低功耗,延长设备的续航时间,提升用户体验。

3. 多核架构:809芯片拥有多核心的处理器结构,能够同时处理多个任务,提高系统的并行处理能力,保证系统的稳定和高效性能。

4. 多种接口:809芯片支持多种常见的外设接口,包括UART、SPI、I2C等,方便与其他设备进行通信和数据交换。

5. 多种通信模块支持:809芯片支持多种无线通信模块,如蓝牙、Wi-Fi、NFC等,能够实现设备之间的高速数据传输和互联互通。

二、809芯片的应用场景1. 物联网:809芯片作为物联网设备的核心控制芯片,可以连接传感器、执行器等设备,实现物联网设备之间的数据传输和协同工作,广泛应用于智能家居、智能城市、智能农业等领域。

2. 智能家居:809芯片可以作为智能家居设备的控制中心,实现家电、照明、安防等设备之间的联动控制,提升家居生活的便利性和舒适性。

3. 智能穿戴设备:809芯片的低功耗和高性能使其成为制造智能手表、智能眼镜等智能穿戴设备的理想选择,能够提供多种功能,如健康监测、运动追踪、消息提醒等。

4. 工业自动化:809芯片可用于工业自动化设备的控制和监控,如机器人、自动化生产线等,能够提升生产效率和产品质量,降低人工成本。

5. 智慧医疗:809芯片可以应用于医疗设备的控制和监测,如智能健康监测设备、远程医疗等,可以实现患者的远程监护和快速响应,提高医疗质量和效率。

三、809芯片的未来发展方向1. 更强大的处理能力:随着技术的不断进步,809芯片的处理能力将会进一步提升,可以处理更加复杂的任务和数据,满足未来物联网和人工智能的需求。

80960SB资料

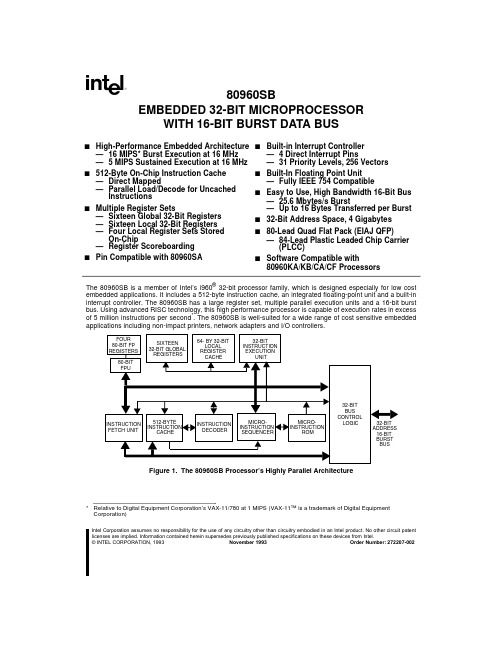

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel.© INTEL CORPORATION, 1993November 1993Order Number: 272207-00280960SBEMBEDDED 32-BIT MICROPROCESSORWITH 16-BIT BURST DATA BUSThe 80960SB is a member of Intel’s i960® 32-bit processor family, which is designed especially for low cost embedded applications. It includes a 512-byte instruction cache, an integrated floating-point unit and a built-in interrupt controller. The 80960SB has a large register set, multiple parallel execution units and a 16-bit burst bus. Using advanced RISC technology, this high performance processor is capable of execution rates in excess of 5 million instructions per second *. The 80960SB is well-suited for a wide range of cost sensitive embedded applications including non-impact printers, network adapters and I/O controllers.Figure 1. The 80960SB Processor’s Highly Parallel Architecture*Relative to Digital Equipment Corporation’s VAX-11/780 at 1 MIPS (VAX-11™ is a trademark of Digital Equipment Corporation)s High-Performance Embedded Architecture —16 MIPS* Burst Execution at 16 MHz — 5 MIPS Sustained Execution at 16 MHzs 512-Byte On-Chip Instruction Cache—Direct Mapped —Parallel Load/Decode for Uncached Instructionss Multiple Register Sets—Sixteen Global 32-Bit Registers —Sixteen Local 32-Bit Registers —Four Local Register Sets Stored On-Chip —Register Scoreboardings Pin Compatible with 80960SA s Built-in Interrupt Controller — 4 Direct Interrupt Pins —31 Priority Levels, 256 Vectors s Built-In Floating Point Unit —Fully IEEE 754 Compatible s Easy to Use, High Bandwidth 16-Bit Bus —25.6 Mbytes/s Burst —Up to 16 Bytes Transferred per Burst s 32-Bit Address Space, 4 Gigabytes s 80-Lead Quad Flat Pack (EIAJ QFP)—84-Lead Plastic Leaded Chip Carrier (PLCC)s Software Compatible with80960KA/KB/CA/CF ProcessorsINSTRUCTION FETCH UNIT 512-BYTE INSTRUCTION CACHE INSTRUCTION DECODER MICRO-INSTRUCTION SEQUENCER MICRO-INSTRUCTION ROM 32-BIT BUS CONTROL LOGIC 32-BIT INSTRUCTION EXECUTION UNIT64- BY 32-BIT LOCAL REGISTER CACHE SIXTEEN 32-BIT GLOBAL REGISTERS 32-BIT ADDRESS16-BIT BURST BUSFOUR80-BIT FPREGISTERS80-BITFPUiiCONTENTS PAGE1.0 THE i960® PROCESSOR (1)1.1 Key Performance Features (2)1.1.1 Memory Space And Addressing Modes (4)1.1.2 Data Types (4)1.1.3 Large Register Set (4)1.1.4 Multiple Register Sets (5)1.1.5 Instruction Cache (5)1.1.6 Register Scoreboarding (5)1.1.7 Floating-Point Arithmetic (6)1.1.8 High Bandwidth Bus (6)1.1.9 Interrupt Handling (7)1.1.10 Debug Features (7)1.1.11 Fault Detection (7)1.1.12 Built-in T estability (7)1.1.13 CHMOS (7)2.0 ELECTRICAL SPECIFICATIONS (11)2.1 Power and Grounding (11)2.2 Power Decoupling Recommendations (11)2.3 Connection Recommendations (11)2.4 Characteristic Curves (11)2.5 T est Load Circuit (13)2.6 ABSOLUTE MAXIMUM RATINGS* (14)2.7 DC Characteristics (14)2.8 AC Specifications (15)3.0 MECHANICAL DATA (20)3.1 Packaging (20)3.2 Pin Assignment (20)3.3 Pinout (22)3.4 Package Thermal Specifications (26)4.0 WAVEFORMS (27)5.0 REVISION HISTORY ................................................................................................................................3380960SBEMBEDDED 32-BIT MICROPROCESSORWITH 16-BIT BURST DATA BUSiiiLIST OF FIGURESPAGE Figure 1The 80960SB Processor’s Highly Parallel Architecture ................................................................0Figure 280960SB Programming Environment ...........................................................................................1Figure 3Instruction Formats ......................................................................................................................4Figure 4Multiple Register Sets Are Stored On-Chip ..................................................................................6Figure 5Connection Recommendation for LOCK ....................................................................................11Figure 6Typical Supply Current vs. Case T emperature ...........................................................................12Figure 7Typical Current vs. Frequency (Room T emp) .............................................................................12Figure 8Typical Current vs. Frequency (Hot T emp) .................................................................................13Figure 9Capacitive Derating Curve .........................................................................................................13Figure 10Test Load Circuit for Three-State Output Pins ............................................................................13Figure 11Drive Levels and Timing Relationships for 80960SB Signals .....................................................15Figure 12Processor Clock Pulse (CLK2) ...................................................................................................18Figure 13RESET Signal Timing .................................................................................................................18Figure 14HOLD Timing ..............................................................................................................................19Figure 1580-Lead EIAJ Quad Flat Pack (QFP) Package ..........................................................................20Figure 1684-Lead Plastic Leaded Chip Carrier (PLCC) Package .............................................................21Figure 17Non-Burst Read and Write T ransactions Without Wait States ....................................................27Figure 18Quad Word Burst Read T ransaction With 1, 0, 0, 0, 0, 0, 0, 0 Wait States ................................28Figure 19Burst Write T ransaction With 2, 1, 1, 1 Wait States (6-8 Bytes T ransferred) ..............................29Figure 20Accesses Generated by Quad Word Read Bus Request, Misaligned One Byte from Quad Word Boundary 1, 0, 0, 0, 0, 0, 0, 0 Wait States 30Figure 21Interrupt Acknowledge Cycle ......................................................................................................31Figure 22Cold Reset Waveform ................................................................................................................32LIST OF TABLESTable 180960SB Instruction Set ..............................................................................................................3Table 2Memory Addressing Modes .........................................................................................................4Table 3Sample Floating-Point Execution Times (µs) at 16 MHz ..............................................................6Table 480960SB Pin Description: Bus Signals ........................................................................................8Table 580960SB Pin Description: Support Signals ................................................................................10Table 6DC Characteristics .....................................................................................................................14Table 780960SB AC Characteristics (10 MHz) ......................................................................................16Table 880960SB AC Characteristics (16 MHz) ......................................................................................17Table 980960SB QFP Pinout — In Pin Order ........................................................................................22Table 1080960SB QFP Pinout — In Signal Order ...................................................................................23Table 1180960SB PLCC Pinout — In Pin Order ......................................................................................24Table 1280960SB PLCC Pinout — In Signal Order .................................................................................25Table 1380960SB QFP Package Thermal Characteristics ......................................................................26Table 1480960SB PLCC Package Thermal Characteristics .. (26)180960SB1.0THE i960® PROCESSORThe 80960SB is a member of the 32-bit architecturefrom Intel known as the i960 processor family. Thesemicroprocessors were especially designed to servethe needs of embedded applications. The embeddedmarket includes applications as diverse as industrialautomation, avionics, image processing, graphicsand networking. These types of applications requirehigh integration, low power consumption, quickinterrupt response times and high performance.Since time to market is critical, embedded micropro-cessors need to be easy to use in both hardware and software designs.All members of the i960 processor family share a common core architecture which utilizes RISC technology so that, except for special functions, the family members are object-code compatible. Each new processor in the family adds its own special set of functions to the core to satisfy the needs of a specific application or range of applications in theembedded market.Figure 2. 80960SB Programming EnvironmentSIXTEEN 32-BIT GLOBAL REGISTERS SIXTEEN 32-BIT LOCAL REGISTERS g0g15r0r15 FOUR 80-BIT CONTROL REGISTERSFLOATING POINT REGISTERS ARCHITECTURALLYDEFINEDDATA STRUCTURESFFFF FFFFHINSTRUCTIONSTREAMINSTRUCTIONEXECUTIONPROCESSOR STATEREGISTERSINSTRUCTION POINTERARITHMETIC CONTROLSPROCESS CONTROLSTRACE CONTROLS ADDRESS SPACELOAD STORE0000 0000H INSTRUCTIONCACHE FETCH280960SB1.1Key Performance FeaturesThe 80960SB architecture is based on the mostrecent advances in microprocessor technology andis grounded in Intel’s long experience in the designand manufacture of embedded microprocessors.Many features contribute to the 80960SB’s excep-tional performance:rge Register Set. Having a large number ofregisters reduces the number of times that aprocessor needs to access memory. Moderncompilers can take advantage of this feature tooptimize execution speed. For maximum flexi-bility, the 80960SB provides thirty-two 32-bitregisters and four 80-bit floating point registers.(See Figure 2.)2.Fast Instruction Execution. Simple functionsmake up the bulk of instructions in mostprograms so that execution speed can beimproved by ensuring that these core instruc-tions are executed as quickly as possible. Themost frequently executed instructions — suchas register-register moves, add/subtract,logical operations and shifts — execute in oneto two cycles. (Table 1 contains a list of instruc-tions.)3.Load/Store Architecture. One way to improveexecution speed is to reduce the number oftimes that the processor must access memoryto perform an operation. As with otherprocessors based on RISC technology, the80960SB has a Load/Store architecture. Assuch, only the LOAD and STORE instructionsreference memory; all other instructionsoperate on registers. This type of architecturesimplifies instruction decoding and is used incombination with other techniques to increaseparallelism.4.Simple Instruction Formats. All instructionsin the 80960SB are 32 bits long and must bealigned on word boundaries. This alignmentmakes it possible to eliminate the instructionalignment stage in the pipeline. T o simplify theinstruction decoder, there are only fiveinstruction formats; each instruction uses onlyone format. (See Figure 3.)5.Overlapped Instruction Execution. Load operations allow execution of subsequent instructions to continue before the data has been returned from memory, so that these instructions can overlap the load. The 80960SB manages this process transparently to software through the use of a register score-board. Conditional instructions also make use of a scoreboard so that subsequent unrelated instructions may be executed while the condi-tional instruction is pending.6.Integer Execution Optimization. When the result of an arithmetic execution is used as an operand in a subsequent calculation, the value is sent immediately to its destination register.At the same time, the value is put on a bypass path to the ALU, thereby saving the time that otherwise would be required to retrieve the value for the next operation.7.Bandwidth Optimizations. The 80960SB gets optimal use of its memory bus bandwidth because the bus is tuned for use with the on-chip instruction cache: instruction cache line size matches the maximum burst size for instruction fetches. The 80960SB automatically fetches four words in a burst and stores them directly in the cache. Due to the size of the cache and the fact that it is continually filled in anticipation of needed instructions in the program flow, the 80960SB is relatively insen-sitive to memory wait states. The benefit is that the 80960SB delivers outstanding performance even with a low cost memory system.8.Cache Bypass. If a cache miss occurs, the processor fetches the needed instruction then sends it on to the instruction decoder at the same time it updates the cache. Thus, no extra time is spent to load and read the cache.380960SBTable 1. 80960SB Instruction Set Data MovementArithmetic Logical Bit and Bit Field LoadStoreMoveLoad Address Add Subtract Multiply DivideRemainderModuloShiftExtended MultiplyExtended Divide And Not And And Not Or Exclusive Or Not Or Or Not Nor Exclusive NorNotNandRotateSet Bit Clear Bit Not Bit Check Bit Alter Bit Scan For Bit Scan Over Bit Extract ModifyComparisonBranch Call/Return Fault CompareConditional CompareCompare and IncrementCompare and DecrementUnconditional Branch Conditional Branch Compare and Branch Call Call Extended Call System Return Branch and Link Conditional Fault Synchronize Faults DebugMiscellaneous Decimal Floating Point Modify Trace ControlsMarkForce Mark Atomic Add Atomic Modify Flush Local RegistersModify ArithmeticControlsScan Byte for EqualTest Condition Code Move Add with Carry Subtract with Carry Move Real Scale Round Square Root Sine Cosine TangentArctangentLogLog BinaryLog NaturalExponentClassifyCopy Real ExtendedCompareSynchronousConversion Synchronous LoadSynchronous Move Convert Real to Integer Convert Integer to Real480960SB Figure 3. Instruction FormatsControl Compare andBranchRegister toRegister Memory Access---ShortMemory Access---Long Opcode DisplacementOpcode Displacement Reg/Lit Reg M DisplacementOpcode Opcode Opcode Reg Reg Reg Reg/Lit Base Base M Modes Mode Ext’d Op Reg/LitX Offset Scale xx Offset1.1.1Memory Space And Addressing Modes The 80960SB offers a linear programmingenvironment so that all programs running on theprocessor are contained in a single address space.Maximum address space size is 4Gigabytes (232bytes).For ease of use the 80960SB has a small number ofaddressing modes, but includes all those necessaryto ensure efficient execution of high-level languagessuch as C.Table 2 lists the memory addressingmodes.Table 2. Memory Addressing Modes•12-Bit Offset •32-Bit Offset •Register-Indirect •Register + 12-Bit Offset •Register + 32-Bit Offset •Register + (Index-Register x Scale-Factor)•Register x Scale Factor + 32-Bit Displacement •Register + (Index-Register x Scale-Factor) +32-Bit Displacement Scale-Factor is 1, 2, 4, 8 or 161.1.2Data TypesThe 80960SB recognizes the following data types:Numeric:•8-, 16-, 32- and 64-bit ordinals •8-, 16-, 32- and 64-bit integers •32-, 64- and 80-bit real numbers Non-Numeric:•Bit •Bit Field •T riple Word (96 bits)•Quad-Word (128 bits)1.1.3Large Register Set The 80960SB programming environment includes a large number of registers. In fact, 32 registers are available at any time. The availability of this many registers greatly reduces the number of memory accesses required to perform algorithms, which leads to greater instruction processing speed.There are two types of general-purpose register:local and global. The global registers consist ofsixteen 32-bit registers (g0 though g15) and four580960SB 80-bit registers (fp0 through fp3). These registersperform the same function as the general-purposeregisters provided in other popular microprocessors.The term global refers to the fact that these registersretain their contents across procedure calls.The local registers, on the other hand, are procedurespecific. For each procedure call, the 80960SBallocates 16 local registers (r0 through r15). Eachlocal register is 32 bits wide. Any register can also beused for single or double-precision floating-pointoperations; the 80-bit floating-point registers areprovided for extended precision.1.1.4Multiple Register SetsTo further increase the efficiency of the register set,multiple sets of local registers are stored on-chip(See Figure 4). This cache holds up to four localregister frames, which means that up to threeprocedure calls can be made without having toaccess the procedure stack resident in memory.Although programs may have procedure calls nestedmany calls deep, a program typically oscillates backand forth between only two to three levels. As aresult, with four stack frames in the cache, the proba-bility of having a free frame available on the cachewhen a call is made is very high. In fact, runs ofrepresentative C-language programs show that 80%of the calls are handled without needing to accessmemory.If four or more procedures are active and a newprocedure is called, the 80960SB moves the oldestlocal register set in the stack-frame cache to aprocedure stack in memory to make room for a newset of registers. Global register g15 is the framepointer (FP) to the procedure stack.Global and floating point registers are not exchangedon a procedure call, but retain their contents, makingthem available to all procedures for fast parameterpassing.1.1.5Instruction CacheTo further reduce memory accesses, the 80960SBincludes a 512-byte on-chip instruction cache. Theinstruction cache is based on the concept of localityof reference; most programs are not usuallyexecuted in a steady stream but consist of manybranches, loops and procedure calls that lead to jumping back and forth in the same small section of code. Thus, by maintaining a block of instructions in cache, the number of memory references required to read instructions into the processor is greatly reduced.T o load the instruction cache, instructions are fetched in 16-byte blocks; up to four instructions can be fetched at one time. An efficient prefetch algorithm increases the probability that an instruction will already be in the cache when it is needed.Code for small loops often fits entirely within the cache, leading to a great increase in processing speed since further memory references might not be necessary until the program exits the loop. Similarly,when calling short procedures, the code for the calling procedure is likely to remain in the cache so it will be there on the procedure’s return.1.1.6Register Scoreboarding The instruction decoder is optimized in several ways.One optimization method is the ability to overlap instructions by using register scoreboarding.Register scoreboarding occurs when a LOAD moves a variable from memory into a register. When the instruction initiates, a scoreboard bit on the target register is set. Once the register is loaded, the bit is reset. In between, any reference to the register contents is accompanied by a test of the scoreboard bit to ensure that the load has completed before processing continues. Since the processor does not need to wait for the LOAD to complete, it can execute additional instructions placed between the LOAD and the instruction that uses the register contents, as shown in the following example:ld data_2, r4ld data_2, r5Unrelated instruction Unrelated instruction add r4, r5, r6In essence, the two unrelated instructions between LOAD and ADD are executed “for free” (i.e., take no apparent time to execute) because they are executed while the register is being loaded. Up to three load instructions can be pending at one time with three corresponding scoreboard bits set. By exploiting this feature, system programmers and compiler writers have a useful tool for optimizing execution speed.680960SB Figure 4. Multiple Register Sets Are Stored On-Chipr 15r 0310ONE OF FOUR LOCAL REGISTER SETS REGISTER CACHE LOCAL REGISTER SET1.1.7Floating-Point Arithmetic In the 80960SB, floating-point arithmetic has been made an integral part of the architecture. Having the floating-point unit integrated on chip provides two advantages. First, it improves the performance of the chip for floating-point applications, since no additional bus overhead is associated with floating-point calculations, thereby leaving more time for other bus operations such as I/O. Second, the cost of using floating-point operations is reduced because a separate coprocessor chip is not required.The 80960SB floating-point (real-number) data types include single-precision (32-bit), double-precision (64-bit) and extended precision (80-bit) floating-point numbers. Any registers may be used to executefloating-point operations.The processor provides hardware support for bothmandatory and recommended portions of IEEEStandard 754 for floating-point arithmetic, includingall arithmetic, exponential, logarithmic and othertranscendental functions.T able 3 shows executiontimes for some representative instructions.1.1.8 High Bandwidth Bus The 80960SB CPU resides on a high-bandwidthaddress/data bus. The bus provides a direct commu-nication path between the processor and the memory and I/O subsystem interfaces. The processor uses the bus to fetch instructions,manipulate memory and respond to interrupts. Bus features include:•16-bit data path multiplexed onto the lower bits of the 32-bit address path •Eight 16-bit half-word burst capability which allows transfers from 1 to 16 bytes at a time •High bandwidth reads and writes with25.6MBytes/s burst (at 16 MHz)Table 4 defines bus signal names and functions;Table 5 defines other component-support signalssuch as interrupt lines.Table 3. Sample Floating-Point Execution Times(µs) at 16 MHzFunction32-Bit 64-Bit Add0.60.8Subtract0.60.8Multiply1.12.0Divide2.0 4.5Square Root5.86.1Arctangent15.820.5Exponent17.719.5Sine23.825.9Cosine 23.825.9780960SB1.1.9Interrupt Handling The 80960SB can be interrupted in one of two ways:by the activation of one of four interrupt pins or by sending a message on the processor’s data bus.The 80960SB is unusual in that it automatically handles interrupts on a priority basis and can keep track of pending interrupts through its on-chip interrupt controller. Two of the interrupt pins can be configured to provide 8259A-style handshaking for expansion beyond four interrupt lines.1.1.10Debug FeaturesThe 80960SB has built-in debug capabilities. There are two types of breakpoints and six trace modes.Debug features are controlled by two internal 32-bit registers, the Process-Controls Word and the T race-Controls Word. By setting bits in these control words,a software debug monitor can closely control how the processor responds during program execution.The 80960SB provides two hardware breakpoint registers on-chip which, by using a special command, can be set to any value. When the instruction pointer matches either breakpoint register value, the breakpoint handling routine is automati-cally called.The 80960SB also provides software breakpoints through the use of two instructions: MARK and FMARK. These can be placed at any point in a program and cause the processor to halt execution at that point and call the breakpoint handling routine.The breakpoint mechanism is easy to use and provides a powerful debugging tool.Tracing is available for instructions (single step execution), calls and returns and branching. Each trace type may be enabled separately by a special debug instruction. In each case, the 80960SB executes the instruction first and then calls a trace handling routine (usually part of a software debug monitor). Further program execution is halted until the routine completes, at which time execution resumes at the next instruction. The 80960SB’s tracing mechanisms, implemented completely in hardware, greatly simplify the task of software test and debug.1.1.11Fault DetectionThe 80960SB has an automatic mechanism to handle faults. Fault types include floating point,trace and arithmetic faults. When the processor detects a fault, it automatically calls the appropriate fault handling routine and saves the current instruction pointer and necessary state information to make efficient recovery possible. Like interrupt handling routines, fault handling routines are usually written to meet the needs of specific applications and are often included as part of the operating system or kernel.For each of the fault types, there are numerous subtypes that provide specific information about a fault. For example, a floating point fault may have the subtype set to an Overflow or Zero-Divide fault.The fault handler can use this specific information to respond correctly to the fault.1.1.12Built-in TestabilityUpon reset, the 80960SB automatically conducts an exhaustive internal test of its major blocks of logic.Then, before executing its first instruction, it does a zero check sum on the first eight words in memory to ensure that the memory image was programmed correctly. If a problem is discovered at any point during the self-test, the 80960SB asserts its and will not begin program execution. Self test takes approximately 47,000 cycles to complete.System manufacturers can use the 80960SB’s self-test feature during incoming parts inspection. No special diagnostic programs need to be written. The test is both thorough and fast. The self-test capability helps ensure that defective parts are discovered before systems are shipped and, once in the field,the self-test makes it easier to distinguish between problems caused by processor failure and problems resulting from other causes.1.1.13CHMOSThe 80960SB is fabricated using Intel’s CHMOS IV (Complementary High Speed Metal Oxide Semicon-ductor) process. The 80960SB is available at 10MHz in the QFP package and at 10and 16 MHz in the PLCC package.880960SBTable 4. 80960SB Pin Description: Bus Signals (Sheet 1 of 2)NAME TYPE DESCRIPTIONCLK2I SYSTEM CLOCK provides the fundamental timing for 80960SB systems. It is divided by two inside the 80960SB to generate the internal processor clock.A31:16O T.S.ADDRESS BUS carries the upper 16 bits of the 32-bit physical address to memory. It is valid throughout the burst cycle; no latch is required.AD15:1, D0I/O T.S.ADDRESS/DATA BUS carries the low order 32-bit addresses and 16-bit data to and from memory. AD15:4 must be latched since the cycle following the address cycle carries data on the bus.A3:1O T.S.ADDRESS BUS carries the word addresses of the 32-bit address to memory. These three bits are incremented during a burst access indicating the next word address of the burst access. Note that A3:1 are duplicated with AD3:1 during the address cycle.ALEO T.S.ADDRESS LATCH ENABLE indicates the transfer of a physical address.ALE is asserted during a T a cycle and deasserted before the beginning of the T d state. It is active HIGH and floats to a high impedance state during a hold cycle (T h ).AS O T.S.ADDRESS STATUS indicates an address state.AS is asserted every T a state and deasserted during the following T d state.AS is driven HIGH during reset.W/R O T.S.WRITE/READ specifies, during a T a cycle, whether the operation is a write or read. It is latched on-chip and remains valid during T d cycles.DENO T.S.DATA ENABLE is asserted during T d cycles and indicates transfer of data on the AD lines. The AD lines should not be driven by an external source unless DEN is asserted. When DEN is asserted, outputs from the previous cycle are guaranteed to be three-stated. In addition,DEN deasserted indicates inputs have been captured; therefore input hold times can be disregarded.DEN is driven HIGH during reset.DT/RO T.S.DATA TRANSMIT / RECEIVE indicates the direction of data transfer to and from the bus. It is low during T a and T d cycles for a read or interrupt acknowledgment; it is high during T a and T d cycles for a write. DT/R never changes state when DEN is asserted. DT/R is driven HIGH during reset.READY IREADY indicates that data on AD lines can be sampled or removed. If READY is not asserted during a T d cycle, the T d cycle is extended to the next cycle by inserting a wait state (T w ).I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state。

809协议解析

809协议解析摘要:一、809协议简介1.背景与起源2.主要特点二、809协议解析1.协议结构2.关键参数解读3.应用场景三、809协议在我国的实施与应用1.标准化进程2.行业应用案例四、809协议的优缺点分析1.优点2.缺点五、展望809协议的未来发展1.技术迭代与升级2.潜在挑战与应对策略正文:一、809协议简介1.背景与起源809协议,全称为“工业自动化系统与集成协议”,起源于20世纪80年代末,由美国仪表制造商协会(ISA)主导制定。

其目的是为了解决工业自动化领域设备与系统之间的通信问题,推动自动化技术的进步与发展。

2.主要特点809协议具有以下特点:(1)面向对象:以设备或系统功能为单位进行通信,实现设备间的互操作性。

(2)信息模型:定义了设备或系统功能所需的数据结构、数据类型和数据传输方式。

(3)协议分层:遵循ISO/OSI七层模型,实现不同层次设备之间的通信。

(4)可扩展性:支持子协议和扩展,可根据实际应用需求进行定制。

二、809协议解析1.协议结构809协议主要包括以下几个部分:(1)物理层:定义了通信介质的物理和电气特性,如电缆、波特率等。

(2)数据链路层:实现错误检测、流量控制和数据帧的传输,采用问答式通信。

(3)网络层:负责设备之间的寻址和路由,实现数据包的传输。

(4)传输层:提供可靠或不可靠的数据传输服务,实现设备间的数据交换。

(5)会话层:建立、管理和终止设备之间的会话。

(6)表示层:处理数据表示、编码和解码等问题。

(7)应用层:提供设备或系统功能的通信服务。

2.关键参数解读(1)设备地址:唯一标识一个设备,用于网络层和传输层通信。

(2)数据类型:定义了数据传输时使用的数据类型,如整型、浮点型等。

(3)传输速率:数据链路层和物理层之间的通信速率。

(4)错误检测:采用奇偶校验、循环冗余校验等方法实现数据传输过程中的错误检测。

3.应用场景809协议主要应用于工业自动化领域,如生产线控制系统、楼宇自控系统等,实现设备间的高效、可靠通信。

8090产品介绍

系统可靠性

NE80E

6

NE5000E核心路由器基本规格 NE5000E核心路由器基本规格

NE5000E单机 NE5000E单机 系统容量 转发性能 端口密度 系统结构 扩展

接口容量1.28Tbps 接口容量1.28Tbps 多框级联可扩充 交换容量2.56Tbps 交换容量2.56Tbps 至80Tbps 1600Mpps 64 × 10Gbps 最多64机框,性 最多64机框,性 能线性增加 4096 × 10Gbps

5

NE80E核心路由器基本规格 NE80E核心路由器基本规格

产品名称 系统容量 转发性能 端口密度 系统结构 NE80E 接口容量320Gbps,交换容量 接口容量320Gbps,交换容量 640Gbps 400Mpps 16 × 10Gbps 标准机箱,带LCD状态显示 标准机箱,带LCD状态显示 双主控热备份;网板3+1备份;电源、 双主控热备份;网板3+1备份;电源、 风扇1+1热备份 风扇1+1热备份 99.999% 99.999%

面对未来的挑战

我们与您携手共进

8090产品介绍 8090产品介绍

1

8090产品简介 8090产品简介

2

8090一体化机柜产品外观 8090一体化机柜产品外观

全框结构

LCD面板

• 双主控板 • 四交换网板 • 16块线路处理卡 16块线路处理卡

交换网板

接口板

半框结构

• 双主控板SRU 双主控板SRU • 2交换网板SFU 交换网板SFU • 8块线路处理卡

4

NE5000E/NE80E系列 NE5000E/NE80E系列 核心路由器网络定位

IP骨干网 IP骨干网 城域网核心路由器 大型行业企业网核心路由器 大型IDC出口路由器 大型IDC出口路由器 IDC 下一代互联网、 G/NGN承载网核心路由器 下一代互联网、3G/NGN承载网核心路由器 NE80E主要应用于10G NE80E主要应用于10G网络环境 80 10 NE5000E主要应用于40G和高密度10G NE5000E主要应用于40G和高密度10G网络环境 5000 40 10

cat d10 参数

cat d10 参数Cat D10是一款重型推土机,被广泛应用于各类大型土方工程中。

它以其卓越的性能和可靠的品质而闻名于世。

作为一名土方工程师,我有幸亲眼目睹了Cat D10的强大威力和出色表现,下面我将为大家详细介绍一下这款令人赞叹的机器。

一、外观设计Cat D10的外观设计简洁大气,整体线条流畅而有力,彰显了其强大的工程能力。

机身呈现出银灰色,给人一种坚固和可靠的感觉。

前端的大型推土板可以轻松地推平任何土地,而高大的车身更是显示出其霸气的一面。

二、卓越的性能Cat D10拥有强大的动力系统,搭载着一台高性能的发动机,可以输出巨大的动力,轻松应对各种复杂的地形。

它的履带采用了特殊的设计,具有优异的抓地力和稳定性,即使在崎岖不平的地势上也能够稳健前行。

此外,它还配备了先进的悬挂系统和转向系统,使得操作更加灵活和精准。

三、人性化设计Cat D10注重人机交互的设计理念,使得操作更加简单和便捷。

驾驶室宽敞明亮,视野开阔,操作台上的控制按钮布局合理,符合人体工程学原理,使得操作人员能够轻松掌握。

此外,驾驶室还配备了舒适的座椅,以及各种功能齐全的设施,为操作人员提供舒适的工作环境。

四、应用领域Cat D10广泛应用于各类土方工程中,如道路修建、矿山开采、堤坝建设等。

它可以轻松应对各种复杂的地质条件,如软土、硬土、石头等。

无论是挖掘、推土还是平整地面,Cat D10都能够胜任,并且效率高。

五、可靠性和维护Cat D10以其可靠性而闻名,它采用了高品质的材料和先进的制造工艺,确保了机器的稳定性和耐久性。

此外,它的维护也非常方便,各个部件都进行了精心设计,可以快速更换和维修,降低了维护成本和停机时间。

总结:Cat D10是一款强大而可靠的重型推土机,它以其卓越的性能和可靠的品质在土方工程领域中享有盛誉。

无论是面对任何复杂的地形和工程要求,Cat D10都能够胜任,为工程项目提供强有力的支持。

无论是土方工程师还是普通人,我们都不能不感叹Cat D10的卓越表现和出色性能,它的存在让土方工程变得更加高效、顺利。

星际音频JIB CT电缆测试器用户指南说明书

Table of Contents (1)Operation (2) (2)Connections (2)Select Test (2)Indications (3)Advanced Tests (3)Other Special Cables (4)Custom Cables (5)Warranty (7)Registration Card ...........................Back CoverIntroduction Battery InstallationIntroductionThank you for purchasing the Galaxy Audio JIB/CT Cable Tester. The CT is designed to test a wide variety of commonly used audio cables and quickly answer the question, “Is this cable good or bad?”A unique computer controlled circuit tests the cable 200 times per second, which allows the CT to detect and display intermittent problems that other cable testers fail to catch.The CT control panel simply consists of a rotary switch, one Green LED, and one Red LED. A quick reference chart is located on the bottom of the unit.TOP BOTTOMConnectors and Controls1Operation1. Battery Installation: Switch to OFF position. Remove the Battery Drawer and install a 9-volt alkaline battery, being careful to not pinch any of the wires when reinstalling the Drawer. Due to the low power consumption design and the Auto Shutoff feature, the battery life of a standard 9V alkaline should be over 100 hours. The Auto Shutoff feature switches off the CT after approximately 5 minutesof inactivity. To reset the CT after Auto Shutoff, simply rotate the switch to the “Off” position and then back to your previous setting. If the Red LED becomes too dim to see, replace the battery with a fresh 9V alkaline.2. Connections: Plug one end of the cable to be tested into the appropriate connector on the “A” side of the CT, and the other end of the cable into the “B” side. All of the connectors on the “A” side are duplicated on the “B” side except for the XLR jacks, where the “A” side has a Female XLR and the “B” side has a Male XLR. CAUTION: Do not connect the CT to any audio device or system. Damage may result to the CT and/or the audio device.3. Select Test: Rotate the switch to select the number of conductors within the cable.NOTE: For accurate results it is necessary to select the correct number of conductors within the cable under test. If in doubt, you may want to remove one of the connector covers to count the conductors emerging from the cable.The following chart lists the number of conductors found in commonly used audio cables. When speaking of 1/4” or 1/8” connectors, the terminology TRS (Tip, Ring, Sleeve) is used to describe the conductors as they appear on the plugs. A Mono cable (2 conductor) would use only the Tip and Sleeve (TS), while a Stereo or balanced cable (3 conductor) would use all three Tip, Ring, and Sleeve (TRS).24. Indications: As the Selector Switch is rotated from the OFF position, the Green LED will blink twice to indicate the CT is ready to test. The Red LED will then light momentarily to indicate the cable is being tested. If the cable fails the test, the Red LED will remain lit. If the cable passes the test, the Red LED will go out and the Green LED will light. At this point you may want to check for intermittent problems by flexing or wiggling the cable. Be aware that cables can become intermittent because of wiring problems or failure of the connector contacts. Any change in the LED indications, even if only momentary, means that the cable has an intermittent problem and cannot be relied upon.5. Advanced Tests: Most of the standard audio cables will test either Pass or Fail according to the indications described above. However, there are some alternative indications given for Pass and Fail for certain cables. The chart below describes some of these cables and what indications to expect.36. Other Special Cables: Male-to-Male or Female-to-Female XLR Cables: Use a known good adapter cable to “change the gender” of one of the cable ends by connecting it in series with the cable under test. Female TS or TRS connectors: Use a known good Male-to-Male cable to “change the gender” to Male by connecting it in series with the cable under test.47. Custom Cables. The CT is designed to test industry standard and commercially available cables and adapters. The CT may not give accurate results for cables wired otherwise.NOTES56ONE YEAR LIMITED WARRANTYThis warranty gives you specific legal rights, and you may also have other rights which may vary from state to state. This warranty is extended to the purchaser and to any purchaser from him/her for value.GALAXY AUDIO warrants the materials and workmanship of its products for a period of one year from the date of the original purchase.The following are not covered by the warranty:1. Damage to or deterioration of the exterior cabinet which occurs after delivery.2. Damage after initial delivery resulting from accident, misuse or neglect.3. Damage resulting from failure to follow instructions contained in the owner’s manual.4. Damage resulting from the performance of repairs by someone other than GALAXY AUDIO.5. Damage occurring during the shipment or delivery of any GALAXY AUDIO product to GALAXY AUDIO after initial delivery of the product to you.6. Damage to any GALAXY AUDIO product which has been altered, or on which theserial number has been effaced or removed.If your unit requires service, it must be returned, shipping charges prepaid to GALAXY AUDIO in the United States. (This warranty is not enforceable outside the U.S.) Please call or write GALAXY AUDIO, 601 E. Pawnee, Wichita, Kansas 67211, (316) 263-2852. We will then issue you to an RMA# (Return Merchandise Authorization) which will need to be applied to the returned item. Under no circumstances should you return your unit to the factory without receiving an RMA or written instruction to do so. If service is required, you must present the original or a copy of the bill of sale as a proof of date of purchase of your unit. Upon receipt of your unit for service, GALAXY AUDIO will repair or replace your unit as soon as possible, but in no event later than 30 days after the receipt of the unit. We will return the unit to you, shipping charges prepaid, provided the necessary repairs are covered by this warranty.IMPLIED WARRANTIES OF MERCHANT ABILITY AND FITNESS FOR PARTICULAR PURPOSE ARE LIMITED IN DURATION TO THE LENGTH OF THIS WARRANTY, UNLESS OTHERWISE PROVIDED FOR BY STATE LAW. GALAXY AUDIO’S LIABILITY IS LIMITED TO THE REPAIR OR REPLACEMENT, AT OUR OPTION, OF ANY DEFECTIVE PRODUCT, AND SHALL IN NO EVENT INCLUDE INCIDENTAL OR CONSEQUENTIAL DAMAGES OF ANY KIND. SOME STATES DO NOT ALLOW LIMITATIONS ON HOW LONG AN IMPLIED WARRANTY LASTS AND/OR DO NOT ALLOW THE EXCLUSION OR LIMITATION OF INCIDENTAL OR CONSEQUENTIAL DAMAGES, SO THE ABOVE LIMITATIONS AND EXCLUSIONS MAY NOT APPLY TO YOU.GALAXY AUDIO does not authorize any third party, including any dealer or Authorized Service Center, to assume any liability on behalf of GALAXY AUDIO or to make any warranty for GALAXY AUDIO.7GALAXY AUDIO601 E. PawneeWichita, KS 67211(316) 263-2852(800) 369-7768Fax: (316) 263-0642Specifications subject to change without notice. 8___________________________________________________________________N a m e ________________________P h o n e _____________A d d r e s s ________________________________________C i t y , S t a t e , Z i p ____________________________________e m a i l _______________________D e a l e r _______________________P u r c h a s e D a t e ________R e g i s t r a t i o nREGISTRATION CARDRegistration information is used ONLY by GALAXY AUDIO and will be kept strictly confidential.GALAXY AUDIO P.O. BOX 16285WICHITA, KS 67216-0285PLACE STAMP HERE。

809协议解析

809协议解析摘要:1.引言2.809协议概述3.809协议的主要内容4.809协议的应用场景5.809协议的优缺点6.我国在809协议方面的应用与发展7.结论正文:本文将对809协议进行详细解析,介绍其背景、主要内容、应用场景以及在我国的发展现状。

同时,对其优缺点进行探讨,以期帮助读者更好地理解和应用这一协议。

一、引言随着物联网、工业互联网等领域的快速发展,设备之间的互联互通成为了产业界关注的焦点。

为了满足这一需求,809协议应运而生。

这是一项用于工业自动化和控制系统领域的通信协议,具有较高的实时性、可靠性和安全性。

二、809协议概述809协议,全称为IEC 61850-9-2,是国际电工委员会(IEC)制定的一项通信协议。

它主要应用于电力系统自动化、铁路信号系统、过程自动化等领域。

该协议基于分层分布式系统的思想,将系统划分为多个层次,实现设备间的高效、可靠、安全通信。

三、809协议的主要内容809协议主要包括以下几个部分:1.物理层:定义了通信媒介、传输速率等物理参数。

2.数据链路层:实现帧同步、差错检测等功能。

3.网络层:负责数据路由和转发,实现设备间的通信。

4.传输层:提供可靠的数据传输服务,保证数据的完整性和及时性。

5.会话层:负责建立、管理和终止会话。

6.应用层:提供设备间通信的接口,包括数据模型、通信服务等功能。

四、809协议的应用场景809协议适用于以下场景:1.电力系统自动化:用于继电保护、故障检测等设备之间的通信。

2.铁路信号系统:实现信号设备、道岔设备等之间的互联互通。

3.过程自动化:应用于工业控制系统、生产线等领域。

4.其他实时控制系统:如智能交通、医疗设备等。

五、809协议的优缺点优点:1.实时性:809协议具有较高的实时性,满足工业自动化领域的实时性要求。

2.可靠性:采用多重校验机制,确保数据传输的可靠性。

3.安全性:提供安全防护机制,防止恶意攻击和数据泄露。

4.可扩展性:协议层次结构清晰,便于扩展和新功能的添加。

t10标准要求

T10标准要求T10是一个技术委员会,负责制定SCSI存储接口的标准。

SCSI (Small Computer System Interface)是一种用于连接计算机和外部设备(如硬盘、光驱、扫描仪等)的接口,支持多种传输协议和物理介质。

T10的标准要求主要有以下几个方面:T10的标准要求SCSI接口具有高速、高效、可靠、兼容、可扩展等功能性特点。

SCSI接口的速度和效率取决于传输协议和物理介质的选择,例如,串行连接的SAS(Serial Attached SCSI)比并行连接的SCSI更快更稳定。

SCSI接口的可靠性要求在传输过程中保证数据的完整性和一致性,通过采用差分信号、奇偶校验、循环冗余校验等技术来实现。

SCSI接口的兼容性要求能够支持不同厂商、不同型号、不同容量、不同协议的设备,通过采用通用命令集、自动协商、热插拔等技术来实现。

SCSI接口的可扩展性要求能够支持多个设备的连接,通过采用总线、链路、交换等技术来实现。

T10的标准要求SCSI接口具有防止数据丢失、损坏、泄露等安全性特点。

SCSI接口的安全性要求在传输过程中保证数据的保密性和完整性,通过采用加密、认证、签名等技术来实现。

SCSI接口的安全性还要求在设备故障或断电等情况下保证数据的可恢复性,通过采用缓存、日志、备份等技术来实现。

T10的标准要求SCSI接口遵循统一的规范和协议,以便于设备的互操作和管理。

T10的标准包括以下几个层次:物理层:定义了SCSI接口的物理连接方式,包括电缆、连接器、信号电平等。

链路层:定义了SCSI接口的数据传输方式,包括帧格式、流控制、错误检测等。

网络层:定义了SCSI接口的网络通信方式,包括地址分配、路由选择、拥塞控制等。

传输层:定义了SCSI接口的传输协议,包括命令格式、状态报告、异常处理等。

应用层:定义了SCSI接口的应用功能,包括设备类型、操作模式、性能参数等。

CYT809JS中文资料

CYT809

Symbol VCC ICC

Parameter Input Voltage Supply Current

Condition

Min 2.0 --

Typ

Max 5.5

Unit V µA

18

25

CYT809Lxx : CYT809Mxx : VTH Reset Threshold CYT809Jxx : CYT809Txx : CYT809Sxx : CYT809Rxx : Reset Threshold Temperature Coefficient(4) VCC to Reset Delay VCC = VTH to (VTH – 100mV) Reset Active Timeout Period VOL VOH RESET Output Voltage Low RESET Output Voltage High ISINK = 3mA ISOURCE = 800µA

元器件交易网

3-Pin Microprocessor Reset Monitor (Preliminary)

Ordering/Marking Information

Ordering Information CYT809xS Marking Information

CYT809

Pin No. 1 2 Symbol GND RESET Description Ground RESET output remains low while Vcc is below the reset voltage threshold and for 240msec(typ) after Vcc rises above reset threshold 3 Vcc Supply Voltage (typ.)

丝印809tl参数

丝印809tl参数丝印809tl是一款三极管,其参数如下:

型号:丝印809tl

类型:PNP

集电极电流(IC):500mA

集电极与基极反向击穿电压(BVCBO):40V 集电极与发射极反向击穿电压(BVCEO):25V 特征频率(fT):25MHz

直流放大系数(hFE):

功耗(PD):625mW

集电极发射极饱和压降(VCE(sat)):

集电极发射极击穿电压(VCEO):

集电极基极击穿电压(VCBO):50V

发射极基极反向击穿电压(BEBO):5V

集电极电流(IC)25℃:150mA

封装:SOT-23-3

这些参数提供了关于丝印809tl三极管性能的详细信息,如其在特定条件下的工作能力、耐压值以及直流放大系数等。

在实际应用中,请务必参考具体数据手册以获取准确的信息。

弱电智能化工程系统技术规范及功能说明书

2.7. 系统自诊断功能.........................................................................................14

2.8. 信息体制构成.............................................................................................14

1.1. 工程概况.......................................................................................................8

1.2. 设计范围.......................................................................................................8

第 2 页 共 154 页

星港隧道弱电智能化系统技术方案

4.1.3 架构合理..............................................................................................28 4.1.4 稳定性和安全性..................................................................................28 4.1.5 设计原则及依据..................................................................................29 4.3. 设计原则.....................................................................................................30 4.2.1 项目需求..............................................................................................30 4.2.2 设计思路..............................................................................................31 2.2.3 系统拓扑图..........................................................................................33 4.4. 功能要求.....................................................................................................35 4.3.1 强大的分布式架构/多级联网 .............................................................35 4.3.2 平台基本功能......................................................................................36 4.3.3 平台特色功能......................................................................................38 4.5. 智能分析系统模块.....................................................................................45 4.4.1 智能分析模块介绍..............................................................................45 4.4.2 星港隧道项目智能需求分析..............................................................47 4.4.3 智能卡特点及功能..............................................................................48 4.4.4 智能分析功能介绍..............................................................................51 4.6. 综合安保系统.............................................................................................52 4.5.1 视频系统和多系统联动......................................................................52 4.5.2 报警系统和视频联动..........................................................................53 4.7. 系统其它说明.............................................................................................53 4.6.1 分布式的存储管理..............................................................................53 4.6.2 实时报警..............................................................................................54 4.6.3 强大的心跳管理..................................................................................54 4.6.4 定制开发与第三方系统集成..............................................................54 4.6.5 系统网络模式......................................................................................54 4.6.7 技术实现..............................................................................................54 4.8. 技术要求.....................................................................................................55 4.7.1 1080P 高清网络枪型摄像机 ...............................................................55 4.7.2 全景球型一体化摄像机......................................................................56 4.7.3 交通监控高清网络枪型摄像机..........................................................57

809协议解析

809协议解析摘要:一、809协议概述二、809协议的主要内容1.协议的背景和目的2.协议的主要组成部分3.协议的关键概念和术语三、809协议的应用场景1.工业自动化领域2.物联网应用3.智能交通系统四、809协议在我国的发展现状1.政策支持与推广2.产业应用与发展3.标准制定与完善五、809协议的未来发展趋势1.技术创新与发展2.市场竞争与格局变化3.国际化与合作六、如何利用809协议提升产业效益1.技术实施与优化2.产业链上下游合作3.人才培养与技术创新七、总结与展望正文:一、809协议概述809协议,全称为“工业自动化领域通信协议”,是一种为工业自动化和控制系统设计的通信协议。

它旨在为各种工业自动化设备提供标准化、高性能、可靠的通信手段,以实现设备之间的互联互通。

809协议在全球范围内得到了广泛的应用,成为工业自动化领域的重要通信标准。

二、809协议的主要内容1.协议的背景和目的随着工业自动化技术的不断发展,设备种类和通信需求日益多样化,设备之间的互联互通成为制约工业自动化发展的瓶颈。

为解决这一问题,809协议应运而生。

其目的是为工业自动化设备提供一种通用、高效的通信方式,以降低设备开发和应用的复杂性。

2.协议的主要组成部分809协议主要包括以下几个部分:(1)物理层:定义了通信介质的物理和电气特性,如电缆、传输速率等。

(2)数据链路层:负责在通信链路上实现数据帧的传输,包括帧同步、差错控制、流量控制等功能。

(3)网络层:负责实现设备之间的寻址和路由功能,实现数据包在不同设备间的传输。

(4)传输层:提供可靠或不可靠的数据传输服务,实现设备间的高效通信。

(5)应用层:提供各种应用服务,如设备监控、数据采集等。

3.协议的关键概念和术语809协议中的一些关键概念和术语包括:(1)设备:指具有独立功能的工业自动化设备,如PLC(可编程逻辑控制器)、传感器等。

(2)站:指协议中的通信实体,可以是单个设备,也可以是多个设备的组合。

809协议解析

809协议解析【最新版】目录1.809 协议概述2.809 协议的结构和内容3.809 协议的解析方法4.809 协议的应用案例5.809 协议的优缺点分析正文一、809 协议概述809 协议,全称为“基于 Internet 的数字内容传输和播放控制协议”,是我国自主研发的一种数字内容传输和播放控制协议。

该协议主要应用于数字内容传输和播放控制领域,为内容提供商和用户提供了一种安全、高效的数字内容传输和播放解决方案。

二、809 协议的结构和内容809 协议主要包括三个部分:传输层、控制层和应用层。

1.传输层:负责数字内容的传输。

传输层采用 TCP/IP 协议,保证了数字内容的传输效率和可靠性。

2.控制层:负责数字内容的播放控制。

控制层采用客户端/服务器模式,用户通过客户端发送播放控制指令,服务器端根据指令进行相应的操作,实现了数字内容的播放控制。

3.应用层:负责数字内容的处理和呈现。

应用层根据数字内容的类型和格式,采用相应的解码器和渲染引擎,实现了数字内容的处理和呈现。

三、809 协议的解析方法809 协议的解析主要包括以下几个步骤:1.协议识别:通过协议头识别出 809 协议。

2.数据解析:将 809 协议的数据部分解析成传输层、控制层和应用层的数据。

3.数据处理:根据传输层、控制层和应用层的数据,进行相应的处理和操作。

4.数据呈现:将处理后的数据呈现给用户。

四、809 协议的应用案例809 协议广泛应用于数字内容传输和播放控制领域,例如在线视频、数字广播、网络游戏等。

五、809 协议的优缺点分析1.优点:(1)自主研发,符合我国国情和相关政策法规。

(2)安全可靠,保证了数字内容的传输和播放安全。

(3)传输效率高,采用了 TCP/IP 协议,保证了数字内容的传输效率。

(4)兼容性强,支持多种数字内容类型和格式。

2.缺点:(1)相对于国际通用协议,809 协议的普及程度较低。

809协议解析

809协议解析

(最新版)

目录

1.809 协议概述

2.809 协议的结构

3.809 协议的解析方法

4.809 协议的应用实例

5.809 协议的优缺点

正文

一、809 协议概述

809 协议,全称为 TCP/IP 协议族中的 HTTP/1.1 协议,是一种用于互联网上的应用层协议。

它的主要功能是在客户端和服务器之间进行数据传输和交换,使得客户端可以获取到服务器上的各种资源,如网页、图片等。

二、809 协议的结构

809 协议的基本结构是请求 - 响应模式。

客户端发起请求,服务器收到请求后进行处理并返回响应。

请求和响应的数据格式都遵循一定的规范,包括请求方法、URL、HTTP 协议版本、请求头、请求体等。

三、809 协议的解析方法

解析 809 协议主要分为以下几个步骤:

1.解析请求方法:请求方法包括 GET、POST、PUT、DELETE 等,代表了客户端对服务器的操作类型。

2.解析 URL:URL 包含了服务器的地址和请求的资源路径。

3.解析 HTTP 协议版本:HTTP 协议有多个版本,如 1.0、1.1 等,

不同版本的协议有不同的特性和功能。

4.解析请求头:请求头包含了客户端的一些信息,如用户代理、编码方式等。

5.解析请求体:请求体包含了客户端要发送给服务器的数据。

四、809 协议的应用实例

809 协议被广泛应用于互联网领域,如网页浏览、网络爬虫、API 接口调用等。

五、809 协议的优缺点

809 协议的优点包括:简单易用、跨平台、传输速度快等。

809协议解析

809协议解析

摘要:

1.809 协议简介

2.809 协议的主要组成部分

3.809 协议的工作原理

4.809 协议的应用领域

5.809 协议的发展趋势

正文:

809 协议,全称为“用于传输控制协议/因特网互联协议(TCP/IP)网络的809 协议”,是一种用于实现分布式数据库系统的通信协议。

它由国际标准化组织(ISO)制定,于1987 年首次发布,目前最新的版本是1999 年发布的ISO/IEC 80913。

809 协议的主要组成部分包括:

1.809 协议的层次结构

2.809 协议的传输服务

3.809 协议的传输协议

4.809 协议的连接机制

5.809 协议的报文格式

在809 协议的工作原理中,首先,客户端与服务器建立连接,然后通过该连接发送请求和接收响应。

在连接过程中,809 协议定义了一系列的报文格式和控制信息,以保证数据的正确传输。

具体来说,它包括以下几个步骤:

1.建立连接

2.发送请求

3.接收响应

4.关闭连接

809 协议广泛应用于分布式数据库系统、网络管理系统、办公自动化系统等领域。

在这些领域中,809 协议主要负责实现以下功能:

1.数据传输

2.数据交换

3.数据共享

4.数据同步

随着计算机技术的不断发展,809 协议也在不断地完善和升级。

在未来的发展趋势中,809 协议将朝着以下几个方向发展:

1.更高的传输速率

2.更好的安全性

3.更广泛的适用范围

4.更简单的操作方式

总的来说,809 协议作为一种重要的通信协议,在现代计算机网络中发挥着至关重要的作用。

809协议解析

809协议解析【实用版】目录1.809 协议简介2.809 协议的工作原理3.809 协议的解析方法4.809 协议在实际应用中的重要性正文一、809 协议简介809 协议,全称为 TCP/IP 协议族中的 HTTP 协议,是一种用于分布式、协作式和超文本信息系统的应用层协议。

该协议定义了客户端和服务器之间的通信规则,使得用户能够通过浏览器访问互联网上的各种资源,如网页、图片、视频等。

二、809 协议的工作原理HTTP 协议基于请求 - 响应模式进行工作。

用户通过浏览器向服务器发送请求,服务器接收到请求后,解析请求内容并返回相应的数据。

请求和响应的数据均以报文形式传输,报文由请求行、请求头、空行和响应数据组成。

三、809 协议的解析方法解析 HTTP 协议主要分为以下几个步骤:1.解析请求行:请求行包含请求方法、请求 URL 和 HTTP 协议版本。

常见的请求方法有 GET、POST、PUT、DELETE 等。

2.解析请求头:请求头包含客户端与服务器通信所需的元数据,如用户代理、请求时间、支持的语言等。

3.解析空行:空行用于分隔请求头和响应数据,表明请求头结束。

4.解析响应数据:响应数据包含响应状态码、响应头和响应正文。

常见的状态码有 200(成功)、404(未找到)等。

四、809 协议在实际应用中的重要性HTTP 协议在互联网领域具有举足轻重的地位。

它为互联网提供了一套统一的资源访问规范,使得用户可以方便地获取全球范围内的信息资源。

同时,HTTP 协议还为网络安全、数据传输效率等方面提供了保障。

总之,809 协议作为互联网的基础协议之一,对于现代网络信息系统的运行具有重要意义。

809协议解析

809协议解析【原创实用版】目录1.809 协议简介2.809 协议的工作原理3.809 协议的优缺点4.809 协议的应用领域5.809 协议的未来发展趋势正文一、809 协议简介809 协议,全称公共交通出行信息编码与传输规范,是我国公共交通领域内制定的一项行业标准。

该协议主要应用于公共交通出行信息编码、传输及数据交换等方面,旨在提高公共交通出行信息服务的准确性、实时性和可靠性。

二、809 协议的工作原理809 协议的工作原理主要包括三个方面:1.数据编码:809 协议对公共交通出行信息进行统一编码,包括线路、站点、班次、时刻等信息,便于传输和识别。

2.数据传输:编码后的数据通过无线通信技术进行传输,如 GPRS、3G、4G 等,以实现实时数据的快速更新和共享。

3.数据交换:接收方接收到传输的数据后,根据 809 协议规定的数据格式进行解码和处理,以满足公共交通出行信息服务的需求。

三、809 协议的优缺点809 协议的优点主要表现在:1.统一标准:通过制定统一的编码规范,实现了公共交通出行信息的标准化,方便了数据传输和交换。

2.实时性:809 协议支持实时数据的传输,有利于提高公共交通出行信息服务的实时性。

3.可扩展性:809 协议具有较强的可扩展性,可以适应不同地区、不同公共交通出行信息服务的需求。

缺点主要表现在:1.技术门槛较高:809 协议涉及到较多的技术领域,如通信技术、数据处理技术等,技术门槛较高。

2.系统稳定性要求较高:由于 809 协议涉及数据传输和交换,因此系统稳定性要求较高,否则可能影响公共交通出行信息服务的准确性和可靠性。

四、809 协议的应用领域809 协议主要应用于以下领域:1.公共交通出行信息服务:如实时公交、地铁查询等。

2.公共交通管理:如线路规划、运力调度等。

3.智慧城市建设:如智能交通、城市大数据等。

五、809 协议的未来发展趋势随着我国公共交通出行需求不断增长和智慧城市建设的推进,809 协议在未来将面临更多的发展机遇和挑战。

809协议解析

809协议解析摘要:一、809 协议简介1.809 协议的背景2.809 协议的作用二、809 协议的主要内容1.协议的基本概念2.数据传输格式3.传输速率4.传输距离5.信号处理三、809 协议的应用领域1.工业自动化2.智能交通3.智能家居4.医疗健康四、809 协议的优势与挑战1.优势a.传输速率快b.信号稳定c.成本低2.挑战a.兼容性问题b.安全性能待提高五、结论1.总结809 协议的特点2.对未来发展的展望正文:随着科技的发展,各类通信协议应运而生,以满足不同领域和场景的需求。

809 协议,作为我国自主研发的一种通信协议,近年来在各个领域得到了广泛应用。

本文将对809 协议进行解析,帮助大家更好地了解这一协议。

首先,我们需要了解809 协议的背景。

在21 世纪初,我国为了满足工业自动化、智能交通等领域的通信需求,开始研发809 协议。

该协议具有传输速率快、信号稳定、成本低等优点,可以有效提高通信效率,降低通信成本。

接下来,我们将详细介绍809 协议的主要内容。

首先,协议的基本概念。

809 协议是基于以太网的一种通信协议,采用了标准化的通信规范,使得不同设备之间的通信变得更加简单。

其次,数据传输格式。

809 协议采用了定长帧的数据传输格式,每个帧的长度固定,便于接收方处理。

再次,传输速率。

809 协议支持多种传输速率,可根据实际需求进行选择。

此外,传输距离。

809 协议支持长距离传输,最长可达100 公里。

最后,信号处理。

809 协议采用了先进的信号处理技术,确保了信号的稳定传输。

在了解了809 协议的基本内容后,我们再来看一下它在各个领域的应用。

工业自动化领域,809 协议可实现设备之间的快速、稳定通信,提高生产效率。

在智能交通领域,809 协议可实现交通信号控制、车辆监控等应用,有效缓解交通拥堵问题。

此外,在智能家居和医疗健康领域,809 协议也有广泛的应用。

虽然809 协议具有很多优势,但同时也面临着一些挑战。

TC10电子秤规格说明书

火灾报警控制柜驱动产品规格说明书(本说明书说明驱动产品的功能,性能指标,是测试工程师、文档工程师和开发人员交流的重要依据,是编写测试用例和帮助文档的重要依据。

下边几项是必须填写的,如果还有需要说明的部分,需要编写更多的内容)[项目经理填写]一、产品功能简介a)硬件功能概述(简要说明硬件设备功能):b)支持协议说明(说明支持的协议,特别是针对多协议的设备一定要说明该驱动支持哪种协议,对协议支持到什么程度)c)支持的硬件型号说明:二、驱动接口:(3.0开发包 3.0以前的开发包开发配置工具)(程序员必须填写,对于3.0开发包的编程规范参加附录,测试工程师按下面的规范要求执行测试)3.0开发包。

三、设备添加方式a)在组态王中定义设备时请选择:智能仪表\常熟双杰\TC10电子秤\COMb)c)对于串口设备通讯参数的推荐设置如下无需设置通信参数四、本设备的地址格式及地址范围地址格式范围:0-255地址格式:0五、寄存器列说明说明:1 DATA寄存器显示读取的数据。

其他寄存器可以完成相应的操作。

六、特殊寄存器详细说明(对于有特殊使用说明和含义的、在寄存器列表中描述不方便的在此进行详细描述,例如某个寄存器的含义解释比较多,在上面的表上不能详细说明。

或者对于一个通用驱动,针对不同型号设备寄存器支持的范围不同等)七、打包规格描述:(程序员需要提供此参数,此说明只用于测试工程师测试,用户文档中不列此项。

)相同设备,相同寄存器,最多5个打一个包。

一个读包的处理时间:(ms,针对有设备驱动)八、接收缓冲区的大小:(程序员需要提供此参数,此说明只用于测试工程师测试,用户文档中不列此项。

)九、重点测试部分说明(需要测试工程师重点测试部分的说明)十、程序员测试特殊说明(程序员在调试程序中发现的一些特殊需要说明的问题,例如某个寄存器写范围超过多大的数据就有问题了)十一、是否需要双机热备测试?十二、驱动运行需要涉及的其他软件的支持(备注:驱动运行需要安装的软件或需要调用的库文件或数据库文件的说明)十三、其他软硬件环境支持的简要操作说明和注意事项(备注:1,和通讯相关的硬件参数的设置,例如仪表需要设备某个参数才能和组态王通讯2,设备软件上影响通讯的参数的设置方法,例如对于plc设备,需要用软件对设备进行特殊的参数设置后,设备才能和组态王通讯,结合图片说明)十四、具体接线图的说明(有特殊连线要求的填写)十五、对于性能事项的特别说明十六、参考资料的说明附录:3.0接口程序编程规范关于程序的规范,会影响到测试环节的部分a)寄存器和通道号之间的0不做限制,0通道的0可输入可不输入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeDoc. No. MD-3004, Rev. ZCAT803, CAT809, CAT8103-Pin Microprocessor Power Supply SupervisorsFeATureSPrecision monitoring of +5.0V (-5%, -10%, -20%), +3.3V (-5%, -10%), +3.0V (-10%) and+2.5V (-5%) power suppliesOffered in three output configurations: - CAT803: Open-Drain Active LOW reset - CAT809: Push-Pull Active LOW reset - CAT810: Push-Pull Active HIGH resetDirect replacements for the MAX803, MAX809 and MAX810 in applications operating over the industrial temperature range reset valid down to V CC = 1.0V 6µA power supply current Power supply transient immunityIndustrial temperature range: -40ºC to +85ºC Available in RoHS-compliant SOT-23 and SC-70 packagesAPPLICATIOnSComputers Servers LaptopsCable modemsWireless communications embedded control systems White goods Power metersIntelligent instrumentsPDAs and ha ndheld equipment■■■■■■■■■■■■■■■■■■DESCRIPTIOnThe CAT803, CAT809, and CAT8 0 are supervisory circuits that monitor power supplies in digital systems. The CAT803, CAT809, and CAT8 0 are direct replacements for the MAX803, MAX809 and MAX8 0 in applications operating over the industrial temperature range.These devices generate a reset signal, which is asserted while the power supply voltage is below a preset threshold level and for at least 40 ms after the power supply level has risen above that level. The underlying floating gate technology, AE 2(TM) used by Catalyst Semiconductor, makes it possible to offer any custom reset threshold value. Seven industry standard threshold levels are offered to support +5.0V, +3.3V, +3.0V and +2.5V systems.The CAT803 has an open-drain RESET output (active LOW). The CAT803 requires a pull-up resistor on the reset output.The CAT809 features a push-pull RESET output (active LOW) and the CAT8 0 features a push-pull RESET output (active HIGH).Fast transients on the power supply are ignored and the output is guaranteed to be in the correct state at V cc levels as low as .0V.The CAT803, CAT809, and CAT8 0 are available in both the compact 3-pin SOT-23 and SC-70 packages.PIn COnfIGuRATIOn(CAT803)CAT809(CAT810)GNDRESET (RESET)V CC3-Lead SOT-233-Lead SC-70123THRESHOLD SuffIX SELECTORnominal Threshold Voltage Threshold SuffixDesignation4.63V L 4.38V M 4.00V J 3.08VT 2.93V S 2.63V R 2.32VZfor Ordering Information details, see page 11.CAT803, CAT809, CAT8102Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeV CCV CCRESETV CCPIn DESCRIPTIOnSPin numbernameDescriptionCAT803CAT809CAT810GNDGround22—RESET Active LOW reset. RESET is asserted if V CC falls below the reset thresh-old and remains low for at least 40ms after V CC rises above the reset threshold.——2RESET Active HIGH reset. RESET is asserted if V CC falls below the reset thresh-old and remains high for at least 40ms after V CC rises above the reset threshold.333V CCPower supply voltage that is monitored.BLOCK DIAGRAMSCAT803, CAT809, CAT8103Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeELECTRICAL CHARACTERISTICSV CC = Full range, T A = -40ºC to +85ºC unless otherwise noted. Typical values at T A = +25ºC and V CC = 5V for the L/M/J versions, V CC = 3.3V for the T/S versions, V CC = 3V for the R version and V CC = 2.5V for the Z version.Parameter SymbolConditions Min TypMax units V CC Range T A = 0ºC to +70ºC .0 5.5VT A = -40ºC to +85ºC .25.5Supply Current I CC T A = -40ºC to +85ºCV CC < 5.5V, J/L/M 820µA V CC < 3.6V, R/S/T/Z 6 5Reset Threshold VoltageV TH L Threshold T A = +25ºC 4.56 4.63 4.70V T A = -40ºC to +85ºC 4.50 4.75M Threshold T A = +25ºC 4.3 4.384.45T A = -40ºC to +85ºC 4.25 4.50J Threshold T A = +25ºC 3.93 4.00 4.06T A = -40ºC to +85ºC 3.89 4. 0T Threshold T A = +25ºC 3.04 3.08 3. T A = -40ºC to +85ºC 3.00 3. 5S Threshold T A = +25ºC 2.89 2.93 2.96T A = -40ºC to +85ºC 2.85 3.00R Threshold T A = +25ºC 2.59 2.63 2.66T A = -40ºC to +85ºC 2.55 2.70Z ThresholdT A = +25ºC 2.28 2.32 2.35T A = -40ºC to +85ºC2.252.38ABSOLuTE MAXIMuM RATInGS (1)Any pin with respect to ground -0.3V to +6.0V Input Current, V CC20mA Output Current, RESET, RESET 20mA Rate of Rise, V CC00V/µs Continuous Power Dissipation Derate 2.2mW/ºC above 70ºC (SC70) 75 mW Derate 4mW/ºC above 70ºC (SOT23)320 mW Operating Temperature Range -40ºC to +85ºC Storage Temperature Range -65ºC to + 05ºC Lead Soldering Temperature ( 0 sec)300ºCnote:( ) Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.CAT803, CAT809, CAT8104Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeELECTRICAL CHARACTERISTICS V CC = Full range, T A = -40ºC to +85ºC unless otherwise noted. Typical values at T A = +25ºC and V CC = 5V for L/M/J versions, V CC = 3.3V for T/S versions, V CC = 3V for R version and V CC = 2.5V for Z version.(continued)notes:( ) Production testing done at T A = +25ºC; limits over temperature guaranteed by design only.(2) ParameterSymbol ConditionsMinTyp (1)Maxunits Reset Threshold Tempco 30ppm/ºC V CC to Reset Delay (Note 2)T D V CC = V TH to (V TH - 00 mV)20µs Reset Active Timeout Period T RT A = -40ºC to +85ºC40240460msRESET Output Voltage Low (Open-drain active LOW, CAT803 and push-pull, active LOW, CAT809)V OL V CC = V TH min, I SINK = .2mA CAT803R/S/T/Z, CAT809R/S/T/Z 0.3VV CC = V TH min, I SINK = 3.2mA CAT803J/L/M, CAT809J/L/M 0.4V CC > .0V, I SINK = 50µA 0.3RESET Output Voltage High (Push-pull, active LOW, CAT809)V OH V CC = V TH max, I SOURCE = 500µA CAT809R/S/T/Z0.8 V CC VV CC = V TH max, I SOURCE = 800µA CAT809J/L/MV CC - .5RESET Output Voltage Low (Push-pull, active HIGH, CAT8 0)V OL V CC > V TH max, I SINK = .2mA CAT8 0R/S/T/Z0.3V V CC > V TH max, I SINK = 3.2mA CAT8 0J/L/M 0.4RESET Output Voltage High (Push-pull active HIGH, CAT8 0)V OH .8V < V CC V TH min, I SOURCE = 50µA0.8 V CCVCAT803, CAT809, CAT8105Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeTyPICAL OPERATInG CHARACTERISTICSV CC = Full range, T A = -40ºC to +85ºC unless otherwise noted. Typical values at T A = +25ºC and V CC = 5V for L/M/J versions, V CC =3.3V for T/S versions, V CC = 3V for R version and V CC = 2.5V for Z version.SUPPLY CURRENT VS. TEMPERATURE(NO LOAD, CAT8xxR/S/T/Z)121086420-50 0 50 100 150S U P P L Y C U R R E N T (µA )TEMPERATURE (˚C)POWER-DOWN RESET DELAY VS. TEMPERATURE(CAT8xxR/S/T/Z)1412108642P O W E R -D O W N R E S E T D E L A Y (µS )TEMPERATURE (˚C)POWER-UP RESET TIMEOUTVS. TEMPERATURE260240220200180160P O W E R -U P R E S E T T I M E O U T (m S )TEMPERATURE (˚C)NORMALIZED RESET THRESHOLDVS. TEMPERATURE1.000210.99980.99960.99940.99920.9990.99880 20 40 60 80 100 120N O R M A L I Z E D T H R E S H O L DTEMPERATURE (˚C)-50 0 50 100 150-50 0 50 100 150CAT803, CAT809, CAT8106Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without notice0V5V 0V5VRESET/OUTRESETV TH V CC0V5V DETAILED DESCRIPTIOnSRESET TIMInGThe reset signal is asserted LOW for the CAT803/ CAT809 and HIGH for the CAT8 0 when the power supply voltage falls below the threshold trip voltage and remains asserted for at least 40ms after the power supply voltage has risen above the threshold.figure 2. Maximum Transient Duration Without Causing a Reset Pulse vs. Reset Comparator OverdriveT R A N S I E N T D U R A T I O N (µs )V CC TRAnSIEnT RESPOnSEThe CAT803/CAT809/CAT8 0 protect µPs against brownout failure. Short duration transients of 4µsec or less and 00mV amplitude typically do not cause a false RESET.Figure 2 shows the maximum pulse duration of negative-going V CC transients that do not cause a reset condition.figure 1. Reset Timing DiagramAs the amplitude of the transient goes further below the threshold (increasing V TH - V CC ), the maximum pulse duration decreases. In this test, the V CC starts from an initial voltage of 0.5V above the threshold and drops below it by the amplitude of the overdrive voltage (V TH - V CC ).CAT803, CAT809, CAT8107Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeVALID RESET WITH V CC unDER 1.0VTo ensure that the CAT809 RESET pin is in a known state when V CC is under 1.0V, a >10kΩ pull-down resistor between RESET pin and GND is recommended. For the CAT8 0, a pull-up resistor from RESET pin to V CC is needed.Power SupplyFigure 3. reSeT Valid with V CC under 1.0V figure 4. RESET Valid with V CC under 1.1Vfigure 5. Bi-directional Reset Pin InterfacingPower SupplyBI-DIRECTIOnAL RESET PIn InTERfACInG The CAT809/8 0 can interface with µP/µC bi-directional reset pins by connecting a 4.7kΩ resistor in series with the CAT809/8 0 reset output and the µP/µC bi-directional reset pin.CAT803, CAT809, CAT8108Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeCAT803 OPEn-DRAIn reSeT APPLICATIOn The CAT803 features an open-drain RESET output and therefore needs a pull-up resistor on the output for proper operation, as shown on Figure 6. An advantage of the open-drain output includes the ability to “wire AND” several outputs together to form an inexpensive logic circuit. It is also possible to have the pull-up resistor connected to a different supply which can be higher than the CAT803 V CC pin. The value of the pull-up resistor is not critical in most applications, typical values being between 5kΩ and 10kΩ.Power Supplyfigure 6. Typical CAT803 Open-Drain Circuit ConfigurationCAT803, CAT809, CAT8109Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticePACKAGE OuTLInE DRAWInGSSOT-23 3-Lead (TB)notes:( ) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC standard TO-236.TOP VIEWSIDE VIEW END VIEWPACKAGE OUTLINE DRAWINGSOT-23 3-Lead (TP , TB)Doc. No. SOT233-007-0107/20/07(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC TO-236.SYMBOL MIN NOM MAXA 0.89 1.12 A1 0.013 0.10 b 0.37 0.50c 0.085 0.18 D 2.80 3.04 E 2.10 2.64 E1 1.20 1.40e 0.95 BSC e1 1.90 BSC L 0.400 REF L1 0.540 REFθ0º8ºfor current Tape and Reel information, download the PDf file from: /documents/tapeandreel.pdfCAT803, CAT809, CAT810Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeSC-70 3-Lead (SD)notes:( ) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC standard MO-203.for current Tape and Reel information, download the PDf file from: /documents/tapeandreel.pdfTOP VIEWSIDE VIEWEND VIEWθPACKAGE OUTLINE DRAWINGSC-70 3-Lead (SB, SD)Doc. No. SC703-046-0101/31/08(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MO-203.SYMBOL MIN NOM MAXA 0.80 1.10 A1 0.00 0.10 A2 0.80 0.90 1.00 b 0.15 0.30c 0.08 0.22 D 1.80 2.00 2.20 E 1.80 2.10 2.40 E1 1.15 1.25 1.35 e 0.65 BSC L 0.26 0.36 0.46L1 0.42 REF L2 0.15 BSCθ 0° 8°θ14°10°CAT803, CAT809, CAT810Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeEXAMPLE Of ORDERInG InfORMATIOn(2) (3) (4)Prefix Device #SuffixTOP MARKInGnotes:( ) All packages are RoHS-compliant (Lead-free, Halogen-free).(2) The standard lead finish is NiPdAu. Contact factory for other lead finishes.(3) The device used in the example above is a CAT809STBI-GT 0 (Push-Pull / Active Low Output, trip level of 2.85V to 3.00V NiPdAu, Tapeand Reel).(4) For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.Device(1)SOT-23 PbSn Finish (2)SOT-23 RoHS Matte Finish (2)SOT-23 RoHSniPdAu Finish (2)(3)SC70 PbSn Finish (2)SC70 RoHSMatte Finish (2)SC70 RoHSniPdAu Finish (2)(3)CAT803x N/A RPYM RNYM N/A RP__RN__CAT809x PAYM PBYM NRYM PA__PB__NR__CAT8 0xPCYMPDYMNSYMPC__PD__NS__notes:( ) All theshold trip level options have the same marking.(2) The “YM” in the SOT-23 package marking indicates the Year and Month of roduction and the “_” in the SC70 package marking indicates theassembly location.(3) All NiPdAu devices will be marked to indicate product type and package. Threshold and full part numbers will be provided on box and reellabels as well as all Shipping documents.CAT803, CAT809, CAT810 2Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticenote:( ) Contact Factory for availability.CAT803LSDI ( )CAT803LSDI-G CAT809LSDI ( )CAT809LSDI-G CAT8 0LSDI ( )CAT8 0LSDI-G CAT803MSDI ( )CAT803MSDI-G CAT809MSDI ( )CAT809MSDI-G CAT8 0MSDI ( )CAT8 0MSDI-G CAT803JSDI ( )CAT803JSDI-G CAT809JSDI ( )CAT809JSDI-G CAT8 0JSDI ( )CAT8 0JSDI-G CAT803TSDI ( )CAT803TSDI-G CAT809TSDI ( )CAT809TSDI-G CAT8 0TSDI ( )CAT8 0TSDI-G CAT803SSDI ( )CAT803SSDI-G CAT809SSDI ( )CAT809SSDI-G CAT8 0SSDI ( )CAT8 0SSDI-G CAT803RSDI ( )CAT803RSDI-G CAT809RSDI ( )CAT809RSDI-G CAT8 0RSDI ( )CAT8 0RSDI-G CAT803ZSDI ( )CAT803ZSDI-G CAT809ZSDI ( )CAT809ZSDI-G CAT8 0ZSDI ( )CAT8 0ZSDI-G CAT803LTBI ( )CAT803LTBI-G CAT809LTBI ( )CAT809LTBI-G CAT8 0LTBI ( )CAT8 0LTBI-G CAT803MTBI ( )CAT803MTBI-G CAT809MTBI ( )CAT809MTBI-G CAT8 0MTBI ( )CAT8 0MTBI-G CAT803JTBI ( )CAT803JTBI-G CAT809JTBI ( )CAT809JTBI-G CAT8 0JTBI ( )CAT8 0JTBI-G CAT803TTBI ( )CAT803TTBI-G CAT809TTBI ( )CAT809TTBI-G CAT8 0TTBI ( )CAT8 0TTBI-G CAT803STBI ( )CAT803STBI-G CAT809STBI ( )CAT809STBI-G CAT8 0STBI ( )CAT8 0STBI-G CAT803RTBI ( )CAT803RTBI-G CAT809RTBI ( )CAT809RTBI-G CAT8 0RTBI ( )CAT8 0RTBI-G CAT803ZTBI ( )CAT803ZTBI-GCAT809ZTBI ( )CAT809ZTBI-GCAT8 0ZTBI ( )CAT8 0ZTBI-GORDERInG PART nuMBERCAT803, CAT809, CAT8103Doc. No. MD-3004, Rev. Z© 2008 SCILLC. All rights reserved.Characteristics subject to change without noticeREVISIOn HISTORyDate rev.Description29-Oct-03N Updated VCC Transient Response text and Figure 230-Oct-03O Updated Power Up Reset Timeout vs. Temperature curve 3-Oct-04PCorrected temperature range Updated DescriptionUpdated Ordering InformationUpdated Absolute Maximum Ratings Updated Electrical Characteristics 23-Mar-04QUpdated DescriptionUpdated Ordering InformationUpdated Absolute Maximum Ratings Updated Electrical CharacteristicsUpdated Typical Operating Characteristics Updated Package Information25-Mar-04RChanged Preliminary designation to FinalUpdated Max Reset Active Timeout Period in Electrical Characteristics Updated package drawings 5-Oct-04S Updated top marking table 28-Feb-05TUpdated FeaturesUpdated Ordering Information Updated Top Marking7-Feb-06Q Updated Typical Operating Characteristics0-Aug-06UUpdated Features Updated DescriptionUpdated Max Reset Active Timeout Period in Electrical Characteristics Updated FigureUpdated Package Information Correct Revision Number 7-Oct-06VUpdated Top MarkingUpdated Detailed Description Adding CAT8032-Feb-07WUpdated Electrical Characteristics Updated FigureUpdated Ordering Information 20-Mar-07X Updated Detailed Descriptions3 -Jan-08YAdded MD- to Document Number Added Block DiagramsUpdated Package Outline DrawingsUpdated Example of Ordering Information Updated Ordering Part Number05-Nov-08ZChange logo and fine print to ON SemiconductorON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PuBLICATIOn ORDERInG InfORMATIOnLITERATuRE fuLfILLMEnT:Literature Distribution Center for On SemiconductorP.O. Box 5 63, Denver, Colorado 802 7 USAPhone: 303-675-2 75 or 800-344-3860 Toll Free USA/Canada fax: 303-675-2 76 or 800-344-3867 Toll Free USA/Canada Email: orderlit@ n. American Technical Support: 800-282-9855 Toll FreeUSA/CanadaEurope, Middle East and Africa Technical Support:Phone: 42 33 790 29 0Japan Customer focus Center:Phone: 8 -3-5773-3850On Semiconductor Website: Order Literature: /orderlitFor additional information, please contact your localSales Representative。