MSP430G2553学习笔记(数据手册)

电设工作小结之 MSP430G2553学习笔记―2

电设工作小结之 MSP430G2553学习笔记―2电设工作小结之-msp430g2553学习笔记―2电设工作小结之――msp430g2553学习笔记――2接通一篇:(四),adc101,adc10就是十位的ad,在g2553上加a0~a7八个可以外接的ad地下通道,a10收到片上的温度传感器上,其他的地下通道都直奔在内部的vcc或gnd上。

因为就是10为的ad所以计算公式如下:2,adc参考电压的选择:adc的参考电压可以为:由adc掌控寄存器0adc10ctl0掌控。

但是必须提升adc的精度的话,尽量不要用内部的参照电压,最出色外接一个比较稳定的电压做为参照电压,因为内部的产生的参照电压不是特别平衡或精度不是特别的高。

比如我在采用时碰到的情况如下:vref设为2.5v但实际的值大概为2.475v,选择vccvss作为参考,用电压表测得大概为3.58v还是不小的偏差的。

另外,在有可能的情况下,尽量使用很大的vr+和vr-,以增大纹波对取样结果的影响。

3,adc10的取样方式存有:单通道单次取样,单通道多次取样,多通道单次取样,多通道多次取样。

4,dtc:因为adc10只有一个采样结果存储寄存器adc10mem,所以除了在单通道单次采样的模式下,其他的三个模式都必须使用dct,否则转换结果会不停地被新的结果给覆盖。

dtc是转换结果传送控制,也就是转换结果可以不用cpu的干预,就可以自动地存储在指定的存储空间内。

使用这种方式转换速度快,访问方便,适用于高速采样模式中。

dtc的使用可以从下面的例子中很容易看明白:#include#include\uchars1[]={\uchars2[]={\voidadc_init(){adc10ctl1=conseq_3+inch_1;//2通道多次转换,最大转换通道为a1adc10ctl0=adc10sht_2+msc+adc10on+adc10ie;//adc10on,interruptenabl参照电压选默认值vcc和vss//采样保持时间为16xadc10clks,adc内核开,中断使能msc多次转换选择开//如果msc置位,则第一次开始转换时需要触发源触发一次,以后的转换会自动进行中断使能//采用dtc时,当一个块传输完结,产生中断//数据传送控制寄存器0adc10dtc0设置为默认模式:单传送块模式,单块传送完停止adc10dtc1=0x04;//数据传送控制寄存器14conversions定义在每块的传送数目一共采样4次所以单块传送4次//以后就暂停了传输因为就是两地下通道的,所以就是每个地下通道取样数据传输2次adc10ae0|=bit0+bit1;//p1.0p1.1adcoptionselect使能模拟输入脚a0a1//不晓得为什么,当p10p11都悬空时,取样值相同,用电压表测得悬空电压相同,但是当都接通取样源的时候,//取样就是相同的}voidmain(void){uintadc_sample[8]={0};//存储adc序列取样结果wdtctl=wdtpw+wdthold;bcsctl1=calbc1_12mhz;//设定cpu时钟dco频率为12mhzdcoctl=caldco_12mhz;p2dir|=bit3+bit4;//液晶的两条线init_lcd();adc_init();wr_string(0,0,s1);wr_string(0,3,s2);for(;;){adc10ctl0&=~enc;//adc不使能够其实这句话可以放到紧接着cpu唤起之后的,因为cpu唤起了,表明我们想的//转换数据传送完成了,如果adc继续转换,那么转换结果也不再传输,是无用的。

MSP430G系列数据手册

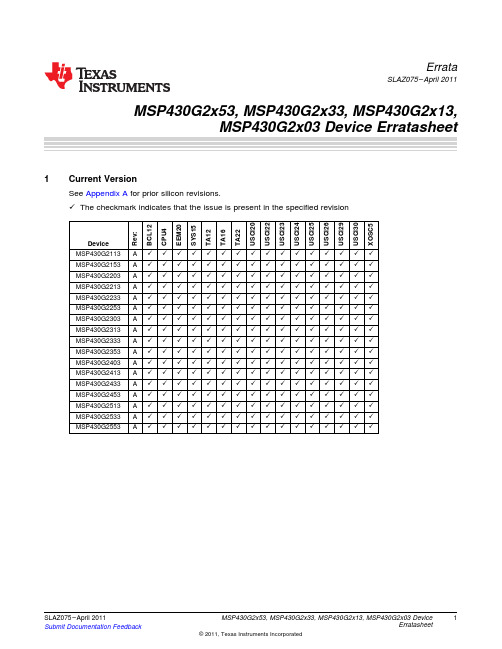

EEM20

Function Description

Workaround

Enhanced Emulation Module

Debugger might clear interrupt flags During debugging, read-sensitive interrupt flags might be cleared as soon as the debugger stops. This is valid in both single-stepping and free-run modes. None

• When switching RSEL from >13 to <12, use an intermediate frequency step. The intermediate RSEL value should be 13.

CURRENT RSEL 15

14 or 15 14 or 15 0 to 13

•

TARGET RSEL

RECOMMENDED TRANSITION SEQUENCE

14

Switch directly to target RSEL

13

Switch directly to target RSEL

0 to 12

Switch to 13 first, and then to target RSEL (two step sequence)

SLAZ075 – April 2011 Submit Documentation Feedback

MSP430G2x53, MSP430G2x33, MSP430G2x13, MSP430G2x03 Device

1

msp430g2553数据手册中文版

28 引脚

24 TSSOP 封

LF,

装

-

1

DCO,

VLO

20 引脚

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24

32 引脚 QFN 封装

28 引脚

24 TSSOP 封

LF,

装

-

1

DCO,

VLO

20 引脚

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24

32 引脚 QFN 封装

28 引脚

3

MSP430G2x53 MSP430G2x13

ZHCS178E – APRIL 2011 – REVISED JANUARY 2012

器件引出脚配置、MSP430G2x13 和 MSP430G2x53、20 引脚器件、 TSSOP 和 PDIP 封装

DVCC 1 P1.0/TA0CLK/ACLK/A0/CA0 2 P1.1/TA0.0/UCA0RXD/UCA0SOMI/A1/CA1 3 P1.2/TA0.1/UCA0TXD/PUCA0SIMO/A2/CA2 4 P1.3/ADC10CLK/CAOUT/VREF-/VEREF-/A3/CA3 5 P1.4/SMCLK/UCB0STE/UCA0CLK/VREF+/VEREF+/A4/CA4/TCK 6 P1.5/TA0.0/UCB0CLK/UCA0STE/A5/CA5/TMS 7

P2.0/TA1.0 8 P2.1/TA1.1 9 P2.2/TA1.1 10

N20 PW20 (TOP VIEW)

20 DVSS 19 XIN/P2.6/TA0.1 18 XOUT/P2.7 17 TEST/SBWTCK 16 RST/NMI/SBWTDIO 15 P1.7/CAOUT/UCB0SIMO/UCB0SDA/A7/CA7/TDO/TDI 14 P1.6/TA0.1/UCB0SOMI/UCB0SCL/A6/CA6/TDI/TCLK 13 P2.5/TA1.2 12 P2.4/TA1.2 11 P2.3/TA1.0

mps430G2553中文资料

时钟

I/O 封装类型

16

512 2x TA3

8

8

512 2x TA3

8

4

256 2x TA3

8

2

256 2x TA3

8

1

256 2x TA3

8

24

32 引脚 QFN 封装

28 引脚

24 TSSOP 封

LF,

装

-

1

DCO,

VLO

20 引脚

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24

32 引脚 QFN 封装

引导加 载器 (BSL)

嵌入式 仿真模

块 (EEM)

1

1

1

1

1

1

1

1

1

1

表 1. 提供的选项(1)(2) (接下页)

ZHCS178E – APRIL 2011 – REVISED JANUARY 2012

闪存 (KB)

RAM (B)

Timer_A

COMP_A+ 通道

10 通道 ADC

USCI A0/B0

典型应用包括低成本传感器系统,此类系统负责捕获模拟信号、将之转换为数字值、随后对数据进行处理以进行显 示或传送至主机系统。

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

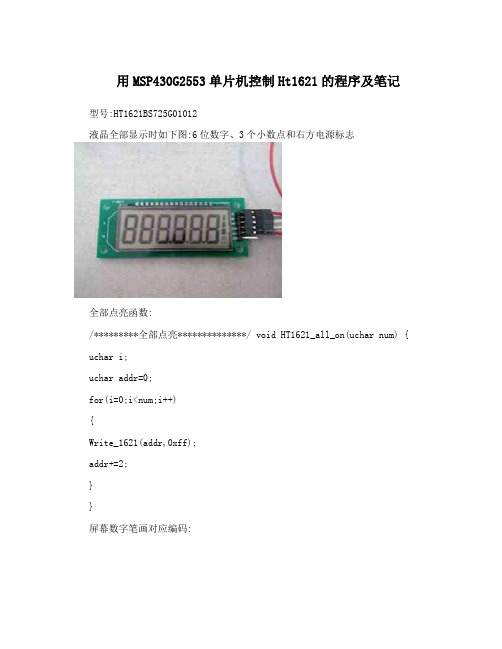

用MSP430G2553单片机控制Ht1621的程序及笔记

用MSP430G2553单片机控制Ht1621的程序及笔记型号:HT1621BS725G01012液晶全部显示时如下图:6位数字、3个小数点和右方电源标志全部点亮函数:/*********全部点亮**************/ void HT1621_all_on(uchar num) { uchar i;uchar addr=0;for(i=0;i<num;i++){Write_1621(addr,0xff);addr+=2;}}屏幕数字笔画对应编码:程序例子:#include "msp430g2553.h"#define uint unsigned int#define uchar unsigned char/***定义1621的端口******/#define DATA1 P2OUT|=BIT0//1621DATA端口#define DATA0 P2OUT&=~BIT0 #define WR1 P2OUT|=BIT1//1621WR0端口#define WR0 P2OUT&=~BIT1#define CS1 P2OUT|=BIT2//1621CS端口#define CS0 P2OUT&=~BIT2/******定义HT1621的命令*******/#define ComMode 0x52 //4COM,1/3bias 1000 010 1001 0#define RCosc 0x30 //内部RC振荡器(上电默认)1000 0011 0000#define LCD_on 0x06 //打开LCD 偏压发生器1000 0000 0 11 0#define LCD_off 0x04 //关闭LCD显示#define Sys_en 0x02 //系统振荡器开 1000 0000 0010 #define CTRl_cmd 0x80 //写控制命令#define Data_cmd 0xa0 //写数据命令char dispnum[6]={0x00,0x00,0x00,0x00,0x00,0x00};//用来存放要显示的数字const char num[]={0x7d,0x60,0x3e,0x7a,0x63,0x5b,0x5f,0x70,0x7f,0x7b};/*0,1,2,3,4,5,6,7,8,9*****//**************延时子程序**********/void delay_1us(void) //1us延时函数{asm("nop");}//N us延时函数void delaynus(uint n){uint i;for(i=0;i<n;i++)asm("nop");}void delay_1ms(void) //1ms延时函数 {unsigned int i;for (i=0;i<1140;i++); }void delay_nms(unsigned int n) //N ms延时函数 {unsigned int i=0;for (i=0;i<n;i++)delay_1ms();}/*****发送数据***********/void SendBit_1621(uchar sdata,uchar cnt) //data 的高cnt 位写入HT1621,高位在前{uchar i;for(i=0;i<cnt;i++){WR0;delaynus(20); //8M必须加,4M可省略if(sdata&0x80) DATA1;else DATA0;delaynus(20);//8M必须加,4M可省略WR1;delaynus(20); //8M必须加,4M可省略sdata<<=1;}delaynus(20);}/******送命令*****/void SendCmd_1621(uchar command){CS0;SendBit_1621(0x80,4); //写入标志码“100”和9 位command 命令,由于SendBit_1621(command,8); //没有使有到更改时钟输出等命令,为了编程方便CS1; //直接将command 的最高位写“0”}/******发送数据和命令**参数说明:addr:要在第几位显示***************************/ void Write_1621(uchar addr,uchar sdata) {addr<<=2;CS0;SendBit_1621(0xa0,3); //写入标志码“101”SendBit_1621(addr,6); //写入addr 的高6位,***6位显示SendBit_1621(sdata,8); //写入data的8位CS1;}/****清除显示********参数说明:num:要清除几位***********************/ void HT1621_all_off(uchar num) {uchar i;uchar addr=0;for(i=0;i<num;i++){Write_1621(addr,0x00);addr+=2;}}/*********全部点亮*******参数说明:num:要点亮几位***************************/ void HT1621_all_on(uchar num) { uchar i;uchar addr=0;for(i=0;i<num;i++){Write_1621(addr,0xff);addr+=2;}}/******全部点亮1621,显示同样的数字******* 参数说明:num:要显示几位****************************/void HT1621_all_on_num(uchar num,uchar xx){uchar i;uchar addr=0;for(i=0;i<num;i++){Write_1621(addr,xx);addr+=2;}}/*********(初始化1621)*************/ void Init_1621(void){SendCmd_1621(Sys_en);//系统振荡器开SendCmd_1621(RCosc); //内部RC振荡器SendCmd_1621(ComMode); //4COM,1/3bias 1000 010 1001 0 SendCmd_1621(LCD_on);//打开LCD 偏压发生器1000 0000 0 11 0}/***********初始化1621) *****************/ void LCDoff(void) {SendCmd_1621(LCD_off); }/*****Name: LCDon(初始化1621)***********/ void LCDon(void){SendCmd_1621(LCD_on); }void displayallnum(unsigned int n) //各位显示所有数码字符函数 { uchar i,j;uchar addr=0;for(i=0;i<n;i++){for(j=0;j<29;j++){Write_1621(addr,num[j]); delay_nms(100) ;}addr+=2;}}//测试第2位数码各位笔画,用于编写num数组 void displaybihua(void) { Write_1621(2,0x01);delay_nms(350) ;Write_1621(2,0x02);delay_nms(350) ;Write_1621(2,0x04);delay_nms(350) ;Write_1621(2,0x08);delay_nms(350) ;Write_1621(2,0x10);delay_nms(350) ;Write_1621(2,0x20);delay_nms(350) ;Write_1621(2,0x40);delay_nms(350) ;Write_1621(2,0x80);delay_nms(350) ; }//逐位显示各位8字+小数点void displayall8(void) {uchar i;HT1621_all_off(6);for(i=0;i<6;i++){Write_1621(2*i,0xff);delay_nms(50) ;}}//显示数组数据void displaydata(long int t,int p) {uchar i;dispnum[4]=num[t/10000];dispnum[3]=num[(t/1000)%10]; dispnum[2]=num[(t/100)%10]; dispnum[1]=num[(t/10)%10]; dispnum[0]=num[t%10];/*switch(p){case 1:sbi(dispnum[0], 4);break;case 2:sbi(dispnum[1], 4);break;case 3:sbi(dispnum[2], 4);break;default:break;}*/for(i=0;i<5;i++){Write_1621(i*2,dispnum[i]); }}void main(){WDTCTL = WDTPW + WDTHOLD; long int t=0;uchar i;P2DIR=0xff;Init_1621() ;//初始化HT1621_all_on(6);//全部点亮delay_nms(200);HT1621_all_off(16);//全部关闭delay_nms(50);for(i=0;i<10;i++){HT1621_all_on_num(6,num[i]);//点亮所有且显示相同数字delay_nms(100) ;}while(1){displaydata(t,2);t++;if(t>99999) t=0;delay_nms(20);}}。

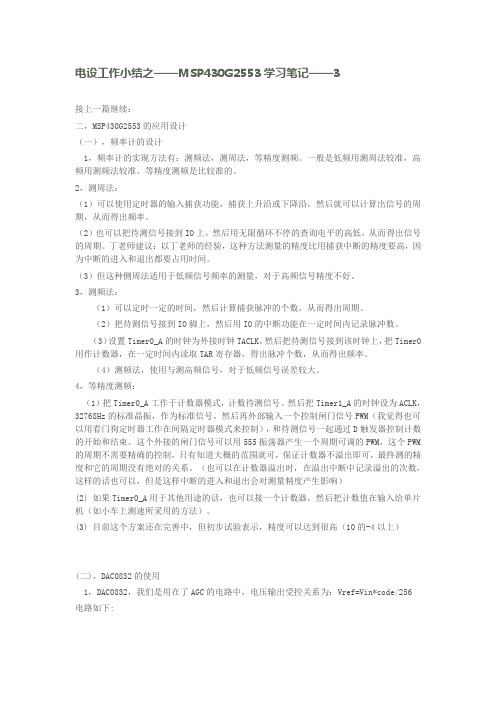

电设工作小结之——MSP430G2553学习笔记—3

电设工作小结之——MSP430G2553学习笔记——3接上一篇继续:二,MSP430G2553的应用设计(一),频率计的设计1,频率计的实现方法有:测频法,测周法,等精度测频。

一般是低频用测周法较准,高频用测频法较准。

等精度测频是比较准的。

2,测周法:(1)可以使用定时器的输入捕获功能,捕获上升沿或下降沿,然后就可以计算出信号的周期,从而得出频率。

(2)也可以把待测信号接到IO上,然后用无限循环不停的查询电平的高低,从而得出信号的周期。

丁老师建议:以丁老师的经验,这种方法测量的精度比用捕获中断的精度要高,因为中断的进入和退出都要占用时间。

(3)但这种侧周法适用于低频信号频率的测量,对于高频信号精度不好。

3,测频法:(1)可以定时一定的时间,然后计算捕获脉冲的个数,从而得出周期。

(2)把待测信号接到IO脚上,然后用IO的中断功能在一定时间内记录脉冲数。

(3)设置Timer0_A的时钟为外接时钟TACLK,然后把待测信号接到该时钟上,把Timer0用作计数器,在一定时间内读取TAR寄存器,得出脉冲个数,从而得出频率。

(4)测频法,使用与测高频信号,对于低频信号误差较大。

4,等精度测频:(1)把Timer0_A工作于计数器模式,计数待测信号。

然后把Timer1_A的时钟设为ACLK,32768Hz的标准晶振,作为标准信号。

然后再外部输入一个控制闸门信号PWM(我觉得也可以用看门狗定时器工作在间隔定时器模式来控制),和待测信号一起通过D触发器控制计数的开始和结束。

这个外接的闸门信号可以用555振荡器产生一个周期可调的PWM,这个PWM 的周期不需要精确的控制,只有知道大概的范围就可,保证计数器不溢出即可,最终测的精度和它的周期没有绝对的关系。

(也可以在计数器溢出时,在溢出中断中记录溢出的次数,这样的话也可以,但是这样中断的进入和退出会对测量精度产生影响)(2) 如果Timer0_A用于其他用途的话,也可以接一个计数器,然后把计数值在输入给单片机(如小车上测速所采用的方法)。

MSP430G2553数据手册

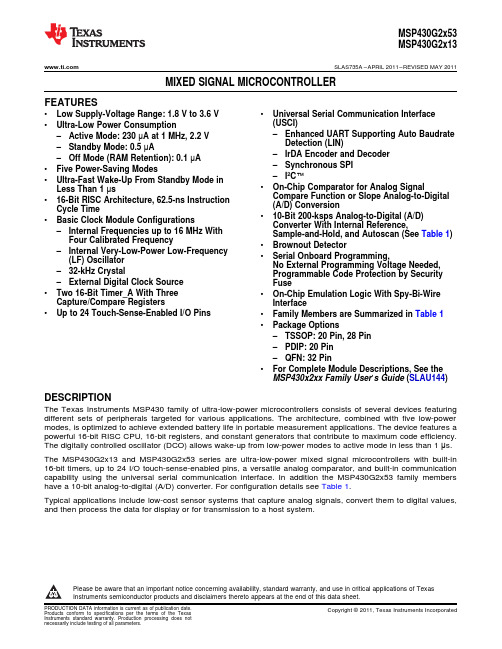

MSP430G2x53MSP430G2x13 SLAS735A–APRIL2011–REVISED MAY2011MIXED SIGNAL MICROCONTROLLERFEATURES•Low Supply-Voltage Range:1.8V to3.6V•Universal Serial Communication Interface(USCI)•Ultra-Low Power Consumption–Enhanced UART Supporting Auto Baudrate –Active Mode:230µA at1MHz,2.2VDetection(LIN)–Standby Mode:0.5µA–IrDA Encoder and Decoder –Off Mode(RAM Retention):0.1µA–Synchronous SPI•Five Power-Saving Modes–I2C™•Ultra-Fast Wake-Up From Standby Mode in•On-Chip Comparator for Analog Signal Less Than1µsCompare Function or Slope Analog-to-Digital •16-Bit RISC Architecture,62.5-ns Instruction(A/D)ConversionCycle Time•10-Bit200-ksps Analog-to-Digital(A/D)•Basic Clock Module ConfigurationsConverter With Internal Reference,–Internal Frequencies up to16MHz With Sample-and-Hold,and Autoscan(See Table1) Four Calibrated Frequency•Brownout Detector–Internal Very-Low-Power Low-Frequency•Serial Onboard Programming, (LF)OscillatorNo External Programming Voltage Needed,–32-kHz Crystal Programmable Code Protection by Security –External Digital Clock Source Fuse•Two16-Bit Timer_A With Three•On-Chip Emulation Logic With Spy-Bi-Wire Capture/Compare Registers Interface•Up to24Touch-Sense-Enabled I/O Pins•Family Members are Summarized in Table1•Package Options–TSSOP:20Pin,28Pin–PDIP:20Pin–QFN:32Pin•For Complete Module Descriptions,See theMSP430x2xx Family User’s Guide(SLAU144)DESCRIPTIONThe Texas Instruments MSP430family of ultra-low-power microcontrollers consists of several devices featuring different sets of peripherals targeted for various applications.The architecture,combined with five low-power modes,is optimized to achieve extended battery life in portable measurement applications.The device features a powerful16-bit RISC CPU,16-bit registers,and constant generators that contribute to maximum code efficiency. The digitally controlled oscillator(DCO)allows wake-up from low-power modes to active mode in less than1µs. The MSP430G2x13and MSP430G2x53series are ultra-low-power mixed signal microcontrollers with built-in 16-bit timers,up to24I/O touch-sense-enabled pins,a versatile analog comparator,and built-in communication capability using the universal serial communication interface.In addition the MSP430G2x53family members have a10-bit analog-to-digital(A/D)converter.For configuration details see Table1.Typical applications include low-cost sensor systems that capture analog signals,convert them to digital values, and then process the data for display or for transmission to a host system.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2011,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.MSP430G2x53MSP430G2x13SLAS735A–APRIL2011–REVISED Table1.Available Options(1)(2)Flash RAM COMP_A+ADC10USCI Package Device BSL EEM Timer_A Clock I/O(KB)(B)Channel Channel A0/B0Type MSP430G2553IRHB322432-QFNLF,MSP430G2553IPW282428-TSSOP 11165122x TA3881DCO,MSP430G2553IPW201620-TSSOPVLOMSP430G2553IN201620-PDIP MSP430G2453IRHB322432-QFNLF,MSP430G2453IPW282428-TSSOP 1185122x TA3881DCO,MSP430G2453IPW201620-TSSOPVLOMSP430G2453IN201620-PDIP MSP430G2353IRHB322432-QFNLF,MSP430G2353IPW282428-TSSOP 1142562x TA3881DCO,MSP430G2353IPW201620-TSSOPVLOMSP430G2353IN201620-PDIP MSP430G2253IRHB322432-QFNLF,MSP430G2253IPW282428-TSSOP 1122562x TA3881DCO,MSP430G2253IPW201620-TSSOPVLOMSP430G2253IN201620-PDIP MSP430G2153IRHB322432-QFNLF,MSP430G2153IPW282428-TSSOP 1112562x TA3881DCO,MSP430G2153IPW201620-TSSOPVLOMSP430G2153IN201620-PDIP MSP430G2513IRHB322432-QFNLF,MSP430G2513IPW282428-TSSOP 11165122x TA38-1DCO,MSP430G2513IPW201620-TSSOPVLOMSP430G2513IN201620-PDIP MSP430G2413IRHB322432-QFNLF,MSP430G2413IPW282428-TSSOP 1185122x TA38-1DCO,MSP430G2413IPW201620-TSSOPVLOMSP430G2413IN201620-PDIP MSP430G2313IRHB322432-QFNLF,MSP430G2313IPW282428-TSSOP 1142562x TA38-1DCO,MSP430G2313IPW201620-TSSOPVLOMSP430G2313IN201620-PDIP MSP430G2213IRHB322432-QFNLF,MSP430G2213IPW282428-TSSOP 1122562x TA38-1DCO,MSP430G2213IPW201620-TSSOPVLOMSP430G2213IN201620-PDIP MSP430G2113IRHB322432-QFNLF,MSP430G2113IPW282428-TSSOP 1112562x TA38-1DCO,MSP430G2113IPW201620-TSSOPVLOMSP430G2113IN201620-PDIP (1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .(2)Package drawings,thermal data,and symbolization are available at /packaging.2Submit Documentation Feedback Copyright©2011,Texas Instruments IncorporatedCA6/TDI/TCLK UC B0SOMI/UCB0SCL/A6//A7/CA7/TDO/TDI /UCB0SIMO/UCB0SDA P1.1/TA0.0//UCA0RXD/UCA0SOMI P1.2/TA0.1//UCA0TXD/PUCA0SIMO P1.4/SMCLK//VREF+/VEREF+/A4/UCB0STE/UCA0CLK P1.5/TA0.0//UCB0CLK/UCA0STECA6/TDI/TCLK UC B0SOMI/UCB0SCL/A6//A7/CA7/TDO/TDI /UCB0SIMO/UCB0SDA P1.1/TA0.0//UCA0RXD/UCA0SOMI P1.2/TA0.1//UCA0TXD/PUCA0SIMO P1.4/SMCLK//VREF+/VEREF+/A4/UCB0STE/UCA0CLK P1.5/TA0.0//UCB0CLK/UCA0STE RHB32(TOP VIEW)123456P 2.0/T A 1.07P 2.1/T A 1.18NC9P 2.2/T A 1.110P3.0/TA0.211P3.1/TA1.012P 3.2/T A 1.113P 3.3/T A 1.214P 3.4/T A 0.015P3.5/TA0.116P 2.3/T A 1.017P 2.4/T A 1.218P2.5/TA1.21920P3.6/TA0.221P3.7/TA1CLK/CAOUT 2223RST/NMI/SBWTDIO24TEST/SBWTCK 25X O U T /P 2.726X I N /P 2.6/T A 0.127A V S S 28D V S S 29A V C C 30D V C C 31P 1.0/T A 0C L K /A C L K /A 0/C A 032N C P1.3/ADC10CLK/CAOUT/VREF-/VEREF-/A3/CA3P1.1/TA0.0/A1/CA1/UCA0RXD/UCA0SOMI P1.2/TA0.1/A2/CA2/UCA0TXD/UCA0SIMO P1.4/SMCLK/CA4/TCK/VREF+/VEREF+/A4/UCB0STE/UCA0CLK P1.5/TA0.0/A5/CA5/TMS/UCB0CLK/UCA0STE P1.6/TA0.1/CA6/TDI/TCLK UC B0SOMI/UCB0SCL/A6/P1.7/CAOUT /CA7/TDO/TDI /UCB0SIMO/UCB0SDA/A7MSP430G2x53MSP430G2x13SLAS735A –APRIL 2011–REVISED MAY 2011Device Pinout,MSP430G2x13and MSP430G2x53,20-Pin Devices,TSSOP and PDIPNOTE:ADC10is available on MSP430G2x53devices only.NOTE:The pulldown resistors of port P3should be enabled by setting P3REN.x =1.Device Pinout,MSP430G2x13and MSP430G2x53,28-Pin Devices,TSSOPNOTE:ADC10is available on MSP430G2x53devices only.Device Pinout,MSP430G2x13and MSP430G2x53,32-Pin Devices,QFNNOTE:ADC10is available on MSP430G2x53devices only.Copyright ©2011,Texas Instruments IncorporatedSubmit Documentation Feedback 3MSP430G2x53MSP430G2x13SLAS735A –APRIL 2011–REVISED MAY 2011Functional Block Diagram,MSP430G2x53NOTE:Port P3is available on 28-pin and 32-pin devices only.Functional Block Diagram,MSP430G2x13NOTE:Port P3is available on 28-pin and 32-pin devices only.4Submit Documentation Feedback Copyright ©2011,Texas Instruments IncorporatedMSP430G2x53MSP430G2x13 SLAS735A–APRIL2011–REVISED MAY2011Table2.Terminal FunctionsTERMINALNO.I/O DESCRIPTIONNAME PW20,PW28RHB32N20P1.0/General-purpose digital I/O pinTA0CLK/Timer0_A,clock signal TACLK inputACLK/2231I/O ACLK signal outputA0ADC10analog input A0(1)CA0Comparator_A+,CA0inputP1.1/General-purpose digital I/O pinTA0.0/Timer0_A,capture:CCI0A input,compare:Out0outputUCA0RXD/USCI_A0receive data input in UART mode,331I/OUCA0SOMI/USCI_A0slave data out/master in SPI modeA1/ADC10analog input A1(1)CA1Comparator_A+,CA1inputP1.2/General-purpose digital I/O pinTA0.1/Timer0_A,capture:CCI1A input,compare:Out1outputUCA0TXD/USCI_A0transmit data output in UART mode,442I/OUCA0SIMO/USCI_A0slave data in/master out in SPI mode,A2/ADC10analog input A2(1)CA2Comparator_A+,CA2inputP1.3/General-purpose digital I/O pinADC10CLK/ADC10,conversion clock output(1)A3/ADC10analog input A3(1)553I/OVREF-/VEREF-/ADC10negative reference voltage(1)CA3/Comparator_A+,CA3inputCAOUT Comparator_A+,outputP1.4/General-purpose digital I/O pinSMCLK/SMCLK signal outputUCB0STE/USCI_B0slave transmit enableUCA0CLK/USCI_A0clock input/output664I/OA4/ADC10analog input A4(1)VREF+/VEREF+/ADC10positive reference voltage(1)CA4/Comparator_A+,CA4inputTCK JTAG test clock,input terminal for device programming and testP1.5/General-purpose digital I/O pinTA0.0/Timer0_A,compare:Out0outputUCB0CLK/USCI_B0clock input/output,UCA0STE/775I/O USCI_A0slave transmit enableA5/ADC10analog input A5(1)CA5/Comparator_A+,CA5inputTMS JTAG test mode select,input terminal for device programming and test(1)MSP430G2x53devices onlyCopyright©2011,Texas Instruments Incorporated Submit Documentation Feedback5MSP430G2x53MSP430G2x13SLAS735A–APRIL2011–REVISED Table2.Terminal Functions(continued)TERMINALNO.I/O DESCRIPTIONNAME PW20,PW28RHB32N20P1.6/General-purpose digital I/O pinTA0.1/Timer0_A,compare:Out1outputA6/ADC10analog input A6(1)CA6/142221I/O Comparator_A+,CA6inputUCB0SOMI/USCI_B0slave out/master in SPI mode,UCB0SCL/USCI_B0SCL I2C clock in I2C modeTDI/TCLK JTAG test data input or test clock input during programming and testP1.7/General-purpose digital I/O pinA7/ADC10analog input A7(1)CA7/Comparator_A+,CA7inputCAOUT/Comparator_A+,output152322I/OUCB0SIMO/USCI_B0slave in/master out in SPI modeUCB0SDA/USCI_B0SDA I2C data in I2C modeTDO/TDI JTAG test data output terminal or test data input during programming andtest(2)P2.0/General-purpose digital I/O pin8109I/OTA1.0Timer1_A,capture:CCI0A input,compare:Out0outputP2.1/General-purpose digital I/O pin91110I/OTA1.1Timer1_A,capture:CCI1A input,compare:Out1outputP2.2/General-purpose digital I/O pin101211I/OTA1.1Timer1_A,capture:CCI1B input,compare:Out1outputP2.3/General-purpose digital I/O pin111615I/OTA1.0Timer1_A,capture:CCI0B input,compare:Out0outputP2.4/General-purpose digital I/O pin121716I/OTA1.2Timer1_A,capture:CCI2A input,compare:Out2outputP2.5/General-purpose digital I/O pin131817I/OTA1.2Timer1_A,capture:CCI2B input,compare:Out2outputXIN/Input terminal of crystal oscillatorP2.6/192726I/O General-purpose digital I/O pinTA0.1Timer0_A,compare:Out1outputXOUT/Output terminal of crystal oscillator(3)182625I/OP2.7General-purpose digital I/O pinP3.0/General-purpose digital I/O pin-97I/OTA0.2Timer0_A,capture:CCI2A input,compare:Out2outputP3.1/General-purpose digital I/O pin-86I/OTA1.0Timer1_A,compare:Out0outputP3.2/General-purpose digital I/O pin-1312I/OTA1.1Timer1_A,compare:Out1outputP3.3/General-purpose digital I/O-1413I/OTA1.2Timer1_A,compare:Out2outputP3.4/General-purpose digital I/O-1514I/OTA0.0Timer0_A,compare:Out0output(2)TDO or TDI is selected via JTAG instruction.(3)If XOUT/P2.7is used as an input,excess current will flow until P2SEL.7is cleared.This is due to the oscillator output driver connectionto this pad after reset.6Submit Documentation Feedback Copyright©2011,Texas Instruments IncorporatedMSP430G2x53MSP430G2x13 SLAS735A–APRIL2011–REVISED MAY2011Table2.Terminal Functions(continued)TERMINALNO.I/O DESCRIPTIONNAME PW20,PW28RHB32N20P3.5/General-purpose digital I/O-1918I/OTA0.1Timer0_A,compare:Out1outputP3.6/General-purpose digital I/O-2019I/OTA0.2Timer0_A,compare:Out2outputP3.7/General-purpose digital I/OTA1CLK/-2120I/O Timer0_A,clock signal TACLK inputCAOUT Comparator_A+,outputRST/ResetNMI/162423I Nonmaskable interrupt inputSBWTDIO Spy-Bi-Wire test data input/output during programming and testTEST/Selects test mode for JTAG pins on Port1.The device protection fuse isconnected to TEST.172524ISBWTCK Spy-Bi-Wire test clock input during programming and testDVCC1129,30NA Supply voltageDVSS202827,28NA Ground referenceNC NA NA8,32NA Not connectedQFN Pad NA NA Pad NA QFN package pad.Connection to VSS is recommended.Copyright©2011,Texas Instruments Incorporated Submit Documentation Feedback7Program Counter PC/R0Stack Pointer SP/R1Status Register SR/CG1/R2Constant Generator CG2/R3General-Purpose Register R4General-Purpose Register R5General-Purpose Register R6General-Purpose Register R7General-Purpose Register R8General-Purpose Register R9General-Purpose Register R10General-Purpose Register R11General-Purpose Register R12General-Purpose Register R13General-Purpose RegisterR15General-Purpose Register R14MSP430G2x53MSP430G2x13SLAS735A –APRIL 2011–REVISED MAY 2011SHORT-FORM DESCRIPTIONCPUThe MSP430CPU has a 16-bit RISC architecture that is highly transparent to the application.All operations,other than program-flow instructions,are performed as register operations in conjunction with seven addressing modes for source operand and four addressing modes for destination operand.The CPU is integrated with 16registers that provide reduced instruction execution time.The register-to-register operation execution time is one cycle of the CPU clock.Four of the registers,R0to R3,are dedicated as program counter,stack pointer,status register,and constant generator,respectively.The remaining registers are general-purpose registers.Peripherals are connected to the CPU using data,address,and control buses,and can be handled with all instructions.The instruction set consists of the original 51instructions with three formats and seven address modes and additional instructions for the expanded address range.Each instruction can operate on word and byte data.Instruction SetThe instruction set consists of 51instructions with three formats and seven address modes.Each instruction can operate on word and byte data.Table 3shows examples of the three types of instruction formats;Table 4shows the address modes.Table 3.Instruction Word FormatsINSTRUCTION FORMATEXAMPLE OPERATION Dual operands,source-destination ADD R4,R5R4+R5--->R5Single operands,destination only CALL R8PC -->(TOS),R8-->PC Relative jump,un/conditionalJNEJump-on-equal bit =0Table 4.Address Mode Descriptions (1)ADDRESS MODES D SYNTAX EXAMPLE OPERATION Register ✓✓MOV Rs,Rd MOV R10,R11R10---->R11Indexed✓✓MOV X(Rn),Y(Rm)MOV 2(R5),6(R6)M(2+R5)---->M(6+R6)Symbolic (PC relative)✓✓MOV EDE,TONI M(EDE)---->M(TONI)Absolute ✓✓MOV &MEM,&TCDAT M(MEM)---->M(TCDAT)Indirect✓MOV @Rn,Y(Rm)MOV @R10,Tab(R6)M(R10)---->M(Tab+R6)M(R10)---->R11Indirect autoincrement✓MOV @Rn+,Rm MOV @R10+,R11R10+2---->R10Immediate✓MOV #X,TONIMOV #45,TONI #45---->M(TONI)(1)S =source,D =destination8Submit Documentation Feedback Copyright ©2011,Texas Instruments IncorporatedMSP430G2x53MSP430G2x13 SLAS735A–APRIL2011–REVISED MAY2011 Operating ModesThe MSP430has one active mode and five software selectable low-power modes of operation.An interrupt event can wake up the device from any of the low-power modes,service the request,and restore back to the low-power mode on return from the interrupt program.The following six operating modes can be configured by software:•Active mode(AM)–All clocks are active•Low-power mode0(LPM0)–CPU is disabled–ACLK and SMCLK remain active,MCLK is disabled•Low-power mode1(LPM1)–CPU is disabled–ACLK and SMCLK remain active,MCLK is disabled–DCO's dc generator is disabled if DCO not used in active mode•Low-power mode2(LPM2)–CPU is disabled–MCLK and SMCLK are disabled–DCO's dc generator remains enabled–ACLK remains active•Low-power mode3(LPM3)–CPU is disabled–MCLK and SMCLK are disabled–DCO's dc generator is disabled–ACLK remains active•Low-power mode4(LPM4)–CPU is disabled–ACLK is disabled–MCLK and SMCLK are disabled–DCO's dc generator is disabled–Crystal oscillator is stoppedCopyright©2011,Texas Instruments Incorporated Submit Documentation Feedback9MSP430G2x53MSP430G2x13SLAS735A–APRIL2011–REVISED Interrupt Vector AddressesThe interrupt vectors and the power-up starting address are located in the address range0FFFFh to0FFC0h. The vector contains the16-bit address of the appropriate interrupt handler instruction sequence.If the reset vector(located at address0FFFEh)contains0FFFFh(for example,flash is not programmed),the CPU goes into LPM4immediately after power-up.Table5.Interrupt Sources,Flags,and VectorsSYSTEM WORD INTERRUPT SOURCE INTERRUPT FLAG PRIORITYINTERRUPT ADDRESSPower-Up PORIFGExternal Reset RSTIFGWatchdog Timer+WDTIFG Reset0FFFEh31,highestFlash key violation KEYV(2)PC out-of-range(1)NMI NMIIFG(non)-maskableOscillator fault OFIFG(non)-maskable0FFFCh30 Flash memory access violation ACCVIFG(2)(3)(non)-maskableTimer1_A3TACCR0CCIFG(4)maskable0FFFAh29Timer1_A3TACCR2TACCR1CCIFG,TAIFG(2)(4)maskable0FFF8h28Comparator_A+CAIFG(4)maskable0FFF6h27Watchdog Timer+WDTIFG maskable0FFF4h26Timer0_A3TACCR0CCIFG(4)maskable0FFF2h25Timer0_A3TACCR2TACCR1CCIFG,TAIFGmaskable0FFF0h24(5)(4)USCI_A0/USCI_B0receive UCA0RXIFG,UCB0RXIFG(2)(5)maskable0FFEEh23 USCI_B0I2C statusUSCI_A0/USCI_B0transmit UCA0TXIFG,UCB0TXIFG(2)(6)maskable0FFECh22 USCI_B0I2C receive/transmitADC10ADC10IFG(4)maskable0FFEAh21 (MSP430G2x53only)0FFE8h20I/O Port P2(up to eight flags)P2IFG.0to P2IFG.7(2)(4)maskable0FFE6h19I/O Port P1(up to eight flags)P1IFG.0to P1IFG.7(2)(4)maskable0FFE4h180FFE2h170FFE0h16See(7)0FFDEh15See(8)0FFDEh to14to0,lowest0FFC0h(1)A reset is generated if the CPU tries to fetch instructions from within the module register memory address range(0h to01FFh)or fromwithin unused address ranges.(2)Multiple source flags(3)(non)-maskable:the individual interrupt-enable bit can disable an interrupt event,but the general interrupt enable cannot.(4)Interrupt flags are located in the module.(5)In SPI mode:UCB0RXIFG.In I2C mode:UCALIFG,UCNACKIFG,ICSTTIFG,UCSTPIFG.(6)In UART/SPI mode:UCB0TXIFG.In I2C mode:UCB0RXIFG,UCB0TXIFG.(7)This location is used as bootstrap loader security key(BSLSKEY).A0xAA55at this location disables the BSL completely.A zero(0h)disables the erasure of the flash if an invalid password is supplied.(8)The interrupt vectors at addresses0FFDEh to0FFC0h are not used in this device and can be used for regular program code ifnecessary.10Submit Documentation Feedback Copyright©2011,Texas Instruments IncorporatedSpecial Function Registers(SFRs)Most interrupt and module enable bits are collected into the lowest address space.Special function register bits not allocated to a functional purpose are not physically present in the device.Simple software access is provided with this arrangement.Legend rw:Bit can be read and written.rw-0,1:Bit can be read and written.It is reset or set by PUC.rw-(0,1):Bit can be read and written.It is reset or set by POR.SFR bit is not present in device.Table6.Interrupt Enable Register1and2Address76543210 00h ACCVIE NMIIE OFIE WDTIErw-0rw-0rw-0rw-0WDTIE Watchdog Timer interrupt enable.Inactive if watchdog mode is selected.Active if Watchdog Timer is configured in interval timer mode.OFIE Oscillator fault interrupt enableNMIIE(Non)maskable interrupt enableACCVIE Flash access violation interrupt enableAddress76543210 01h UCB0TXIE UCB0RXIE UCA0TXIE UCA0RXIErw-0rw-0rw-0rw-0UCA0RXIE USCI_A0receive interrupt enableUCA0TXIE USCI_A0transmit interrupt enableUCB0RXIE USCI_B0receive interrupt enableUCB0TXIE USCI_B0transmit interrupt enableTable7.Interrupt Flag Register1and2Address76543210 02h NMIIFG RSTIFG PORIFG OFIFG WDTIFGrw-0rw-(0)rw-(1)rw-1rw-(0) WDTIFG Set on watchdog timer overflow(in watchdog mode)or security key violation.Reset on V CC power-on or a reset condition at the pin in reset mode.OFIFG Flag set on oscillator fault.PORIFG Power-On Reset interrupt flag.Set on V CC power-up.RSTIFG External reset interrupt flag.Set on a reset condition at pin in reset mode.Reset on V CC power-up.NMIIFG Set via pinAddress76543210 03h UCB0TXIFG UCB0RXIFG UCA0TXIFG UCA0RXIFGrw-1rw-0rw-1rw-0UCA0RXIFG USCI_A0receive interrupt flagUCA0TXIFG USCI_A0transmit interrupt flagUCB0RXIFG USCI_B0receive interrupt flagUCB0TXIFG USCI_B0transmit interrupt flagMemory OrganizationTable8.Memory OrganizationMSP430G2153MSP430G2253MSP430G2353MSP430G2453MSP430G2553MSP430G2113MSP430G2213MSP430G2313MSP430G2413MSP430G2513 Memory Size1kB2kB4kB8kB16kBMain:interrupt vector Flash0xFFFF to0xFFC00xFFFF to0xFFC00xFFFF to0xFFC00xFFFF to0xFFC00xFFFF to0xFFC0 Main:code memory Flash0xFFFF to0xFC000xFFFF to0xF8000xFFFF to0xF0000xFFFF to0xE0000xFFFF to0xC000 Information memory Size256Byte256Byte256Byte256Byte256Byte Flash010FFh to01000h010FFh to01000h010FFh to01000h010FFh to01000h010FFh to01000h RAM Size256Byte256Byte256Byte512Byte512Byte0x02FF to0x02000x02FF to0x02000x02FF to0x02000x03FF to0x02000x03FF to0x0200 Peripherals16-bit01FFh to0100h01FFh to0100h01FFh to0100h01FFh to0100h01FFh to0100h 8-bit0FFh to010h0FFh to010h0FFh to010h0FFh to010h0FFh to010h 8-bit SFR0Fh to00h0Fh to00h0Fh to00h0Fh to00h0Fh to00hBootstrap Loader(BSL)The MSP430BSL enables users to program the flash memory or RAM using a UART serial interface.Access to the MSP430memory via the BSL is protected by user-defined password.For complete description of the features of the BSL and its implementation,see the MSP430Programming Via the Bootstrap Loader User's Guide(SLAU319).Table9.BSL Function Pins20-PIN PW PACKAGEBSL FUNCTION28-PIN PACKAGE PW32-PIN PACKAGE RHB20-PIN N PACKAGEData transmit3-P1.13-P1.11-P1.1Data receive7-P1.57-P1.55-P1.5Flash MemoryThe flash memory can be programmed via the Spy-Bi-Wire/JTAG port or in-system by the CPU.The CPU can perform single-byte and single-word writes to the flash memory.Features of the flash memory include:•Flash memory has n segments of main memory and four segments of information memory(A to D)of 64bytes each.Each segment in main memory is512bytes in size.•Segments0to n may be erased in one step,or each segment may be individually erased.•Segments A to D can be erased individually or as a group with segments0to n.Segments A to D are also called information memory.•Segment A contains calibration data.After reset segment A is protected against programming and erasing.It can be unlocked but care should be taken not to erase this segment if the device-specific calibration data is required.DCO(RSEL,DCO+1)DCO(RSEL,DCO)average DCO(RSEL,DCO)DCO(RSEL,DCO+1)32×f ×f f =MOD ×f +(32–MOD)×f PeripheralsPeripherals are connected to the CPU through data,address,and control buses and can be handled using all instructions.For complete module descriptions,see the MSP430x2xx Family User 's Guide (SLAU144).Oscillator and System ClockThe clock system is supported by the basic clock module that includes support for a 32768-Hz watch crystal oscillator,an internal very-low-power low-frequency oscillator and an internal digitally controlled oscillator (DCO).The basic clock module is designed to meet the requirements of both low system cost and low power consumption.The internal DCO provides a fast turn-on clock source and stabilizes in less than 1µs.The basic clock module provides the following clock signals:•Auxiliary clock (ACLK),sourced either from a 32768-Hz watch crystal or the internal LF oscillator.•Main clock (MCLK),the system clock used by the CPU.•Sub-Main clock (SMCLK),the sub-system clock used by the peripheral modules.The DCO settings to calibrate the DCO output frequency are stored in the information memory segment A.Main DCO Characteristics•All ranges selected by RSELx overlap with RSELx +1:RSELx =0overlaps RSELx =1,...RSELx =14overlaps RSELx =15.•DCO control bits DCOx have a step size as defined by parameter S DCO .•Modulation control bits MODx select how often f DCO(RSEL,DCO+1)is used within the period of 32DCOCLK cycles.The frequency f DCO(RSEL,DCO)is used for the remaining cycles.The frequency is an average equal to:Calibration Data Stored in Information Memory Segment ACalibration data is stored for both the DCO and for ADC10organized in a tag-length-value structure.Table10.Tags Used by the ADC Calibration TagsNAME ADDRESS VALUE DESCRIPTIONTAG_DCO_300x10F60x01DCO frequency calibration at V CC=3V and T A=30°C at calibrationTAG_ADC10_10x10DA0x08ADC10_1calibration tagTAG_EMPTY-0xFE Identifier for empty memory areasbels Used by the ADC Calibration TagsADDRESSLABEL SIZE CONDITION AT CALIBRATION/DESCRIPTIONOFFSETCAL_ADC_25T850x0010word INCHx=0x1010,REF2_5=1,T A=85°CCAL_ADC_25T300x000E word INCHx=0x1010,REF2_5=1,T A=30°CCAL_ADC_25VREF_FACTOR0x000C word REF2_5=1,T A=30°C,I VREF+=1mACAL_ADC_15T850x000A word INCHx=0x1010,REF2_5=0,T A=85°CCAL_ADC_15T300x0008word INCHx=0x1010,REF2_5=0,T A=30°CCAL_ADC_15VREF_FACTOR0x0006word REF2_5=0,T A=30°C,I VREF+=0.5mACAL_ADC_OFFSET0x0004word External VREF=1.5V,f ADC10CLK=5MHz CAL_ADC_GAIN_FACTOR0x0002word External VREF=1.5V,f ADC10CLK=5MHzCAL_BC1_1MHZ0x0009byte-CAL_DCO_1MHZ0x0008byte-CAL_BC1_8MHZ0x0007byte-CAL_DCO_8MHZ0x0006byte-CAL_BC1_12MHZ0x0005byte-CAL_DCO_12MHZ0x0004byte-CAL_BC1_16MHZ0x0003byte-CAL_DCO_16MHZ0x0002byte-BrownoutThe brownout circuit is implemented to provide the proper internal reset signal to the device during power on and power off.Digital I/OUp to three8-bit I/O ports are implemented:•All individual I/O bits are independently programmable.•Any combination of input,output,and interrupt condition(port P1and port P2only)is possible.•Edge-selectable interrupt input capability for all bits of port P1and port P2(if available).•Read/write access to port-control registers is supported by all instructions.•Each I/O has an individually programmable pullup/pulldown resistor.•Each I/O has an individually programmable pin oscillator enable bit to enable low-cost touch sensing.WDT+Watchdog TimerThe primary function of the watchdog timer(WDT+)module is to perform a controlled system restart after a software problem occurs.If the selected time interval expires,a system reset is generated.If the watchdog function is not needed in an application,the module can be disabled or configured as an interval timer and can generate interrupts at selected time intervals.Timer_A3(TA0,TA1)Timer0/1_A3is a16-bit timer/counter with three capture/compare registers.Timer_A3can support multiple capture/compares,PWM outputs,and interval timing.Timer_A3also has extensive interrupt capabilities. Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.Table12.Timer0_A3Signal ConnectionsINPUT PIN NUMBER DEVICE MODULE MODULE OUTPUT PIN NUMBERMODULEINPUT INPUT OUTPUTBLOCKPW20,N20PW28RHB32PW20,N20PW28RHB32SIGNAL NAME SIGNALP1.0-2P1.0-2P1.0-31TACLK TACLKACLK ACLKTimer NASMCLK SMCLKPinOsc PinOsc PinOsc TACLK INCLKP1.1-3P1.1-3P1.1-1TA0.0CCI0A P1.1-3P1.1-3P1.1-1ACLK CCI0B P1.5-7P1.5-7P1.5-5CCR0TA0V SS GND P3.4-15P3.4-14V CC V CCP1.2-4P1.2-4P1.2-2TA0.1CCI1A P1.2-4P1.2-4P1.2-2CAOUT CCI1B P1.6-14P1.6-22P1.6-21CCR1TA1V SS GND P2.6-19P2.6-27P2.6-26V CC V CC P3.5-19P3.5-18 P3.0-9P3.0-7TA0.2CCI2A P3.0-9P3.0-7 PinOsc PinOsc PinOsc TA0.2CCI2B P3.6-20P3.6-19CCR2TA2V SS GNDV CC V CCTable13.Timer1_A3Signal ConnectionsINPUT PIN NUMBER DEVICE MODULE MODULE OUTPUT PIN NUMBERMODULEINPUT INPUT OUTPUTBLOCKPW20,N20PW28RHB32PW20,N20PW28RHB32SIGNAL NAME SIGNAL-P3.7-21P3.7-20TACLK TACLKACLK ACLKTimer NASMCLK SMCLK-P3.7-21P3.7-20TACLK INCLKP2.0-8P2.0-10P2.0-9TA1.0CCI0A P2.0-8P2.0-10P2.0-9 P2.3-11P2.3-16P2.3-12TA1.0CCI0B P2.3-11P2.3-16P2.3-15CCR0TA0V SS GND P3.1-8P3.1-6V CC V CCP2.1-9P1.7-23P2.1-10TA1.1CCI1A P2.1-9P1.7-23P2.1-10 P2.2-10P2.2-12P2.2-11TA1.1CCI1B P2.2-10P2.2-12P2.2-11CCR1TA1V SS GND P3.2-13P3.2-12V CC V CCP2.4-12P2.4-17P2.4-16TA1.2CCI2A P2.4-12P2.4-17P2.4-16P2.5-13P2.5-18P2.5-17TA1.2CCI2B P2.5-13P2.5-18P2.5-17CCR2TA2V SS GND P3.3-14P3.3-13V CC V CC。

MSP430G2553手册解读

MSP430G2XX外设

• 欠压复位

– 可在上电和断电期间提供正确的复位信号 – 功耗包含于MCU最低功耗时(LPM4)所消耗电流之中

• 串行通信

– 支持 I2C 和 SPI 的 USI – 支持 I2C、SPI 以及 UART 的 USCI

• Comparator_A+

– – – – 可设定反相和同相输入 可选的 RC 输出滤波器 可直接输出至 Timer_A2 捕获输入 具有中断能力

LaunchPad 开发板上各部分介绍

USB 仿真器接口

片上仿真器模块 6针 eZ430 连接器 外置晶体接口 芯片引出脚 MSP430器件和插座

P1.3 按钮

LED和跳线 P1.0 & P1.6

电源连接器 复位按钮

MSP430系列功能框图

MSP430G2XX 无Port3

低压、 电源复 位保护

VLO Min. Puls Filter ACLK Peripherals

32768Hz

OSC_Fault

辅助时钟

MCLK CPU

主系统时钟

16MHz Biblioteka CO SMCLK Peripherals

子系统时钟

上电后: MCLK 和 SMCLK 由DCOCLK 提 供(约1.1 MHz) ACLK 由 LFXT1CLK 提供(LF 模式,6pF内部负载电容)

• 。此外,其还可提供板上Flash 仿真工具, 以直接连接至PC 轻松进行编程、调试和评 估。 • MSP-EXP430G2 采用IAR Embedded Workbench 集成开发环境(IDE) 或Code Composer Studio (CCS)编写、下载和调试 应用。 • 可提供板上Flash 仿真工具,以直接连接至 PC 轻松进行编程、调试和评估。

我的TLC2543学习笔记——基于msp430g2553单片机

我的TLC2543学习笔记——基于msp430g2553单⽚机还是贴不了图⽚我的TLC2543学习笔记Created on: 2012-9-8Author: zhang bin学习笔记for msp430g2553redesigned by zhang bin2012-09-08versions:12_09_01All Rights ReservedTLC2543具有4线制串⾏接⼝,分别为⽚选端(CS),串⾏时钟输⼊端(I/O CLOCK),串⾏数据输⼊端(DATA IN)和串⾏数据输出端(DATA OUT)(转换结束脚EOC可以不接)。

它可以直接与SPI器件进⾏连接,不需要其他外部逻辑。

同时,它还在⾼达4MHz的串⾏速率下与主机进⾏通信。

TLC2543的特点及引脚TLC2543是TI的12 bit串⾏A/D转换器,11个模拟输⼊通道。

使⽤开关电容逐次逼近技术完成,A/D转换过程.由于是串⾏输⼊结构,能够MCU的I/O资源.其特点有:1)12 bit分辨率A/D转换器;2)在⼯作温度范围内10us转换时间;3)11个模拟输⼊通道;4)3路内置⾃测试⽅式;5)采样率为66 kb/s;6)线性误差+1LSB(max);7)有转换结束(EOC)输出;8)具有单、双极性输出;9)可编程的MSB或LSB前导;10)可编程的输出数据长度.��� 12-Bit-Resolution A/D Converter��� 10-µs Conversion Time Over OperatingTemperature��� 11 Analog Input Channels��� 3 Built-In Self-Test Modes��� Inherent Sample-and-Hold Function��� Linearity Error . . . ±1 LSB Max��� On-Chip System Clock��� End-of-Conversion Output��� Unipolar or Bipolar Output Operation(Signed Binary With Respect to 1/2 theApplied Voltage Reference)��� Programmable MSB or LSB First��� Programmable Power Down��� Programmable Output Data Length��� CMOS Technology��� Application Report Available我⽤的tlc2543是直插的,引脚图如下:各引脚的详细说明如下:引脚号名称I/O说明1~9,11,12AIN0~AIN10I模拟量输⼊端。

MSP430G2553学习笔记

第一版MSP430G2553学习笔记Created on: 2012-8-18Author: zhang bin学习笔记for msp430g2553redesigned by zhang bin2012-08-18versions:12_08_01一,MSP430G2553单片机的各个功能模块(一),IO口模块,1,我们所用的MSP430G2553有两组IO口,P1和P2。

2,IO口的寄存器有:方向选择寄存器PxDIR,输出寄存器PxOUT,输入寄存器PxIN,IO口内部上拉或下拉电阻使能寄存器PxREN,IO口功能选择寄存器PxSEL和PxSEL2,IO口中断使能寄存器PxIE,中断沿选择寄存器PxIES,IO口中断标志寄存器PxIFG。

3,所有的IO都带有中断,其中所有的P1口公用一个中断向量,所有的P2口公用一个中断向量。

所以在使用中断时,当进入中断后,还要判断到底是哪一个IO口产生的中断,判断方法可以是判断各个IO口的电平。

4,中断标志PxIFG需要软件清除,也可以用软件置位,从而用软件触发一个中断。

注意:在设置PxIESx时根据PxINx有可能会引起相应的PxIFGx置位(具体的情况见用户指南),所以在初始化完IO口中断以后,正式使用IO中断前要先将对应的PxIFGx清零。

程序如下:void IO_interrupt_init() //IO中断初始化函数{P1REN |= BIT4+BIT5+BIT6+BIT7; // pullup 内部上拉电阻使能//使用中断时,使能内部的上拉电阻这样当该脚悬空是,电平不会跳变,防止悬空时电平跳变不停的触发中断P1OUT = BIT4+BIT5+BIT6+BIT7; // 当引脚上的上拉或下拉电阻使能时,PxOUT选择是上拉还是下来//0:下拉,1:上拉P1IE |= BIT4+BIT5+BIT6+BIT7; // interrupt enabled P13中断使能P1IES |= BIT4+BIT5+BIT6+BIT7; // Hi/lo edge 下降沿中断//P1IES &= ~BIT3; //上升沿触发中断P1IFG &= ~(BIT4+BIT5+BIT6+BIT7); //中断标志位清零}5,PxOUT:如果引脚选择了内部的上拉或下拉电阻使能,则PxOUT设定电阻是上拉还是下拉,0:下拉,1:上拉6,当IO口不用时,最好不要设为输入,且为浮动状态(这是IO口的默认状态),因为当输入为浮动时,输入电压有可能会在VIL和VIH之间,这样会产生击穿电流。

MSP430G2553寄存器资料讲解

MSP430G2553 学习笔记常用赋值运算符:清除:&=~ , 置位:|= , 测试:&= , 取反:A=看门狗模块:WDT (看门狗)IS1,IS0选择看门狗定时器的定时输出, T 是WDTCNT 的输入时钟源周期0 T x 2(15) 1 T x 2(13) 2 T x 2(9) 3T x 2(6)SSEL选择WDTCNT 的时钟源 0 SMCLK 1ACLKIS0、IS1、SSEL 可确定 WDT 定时时间, WDT 只能定时8种和时钟源相关的时间CNTCL当该位为1时,清除WDTCNT TMSEL工作模式选择看门狗模式1定时器模式NMI选择RST/NMI 引脚功能,在 PUC 后被复位0 RST/NMI引脚为复位端NMIES 选择中断的边沿触发方式0 上升沿触发NMI中断1 下降沿触发NMI中断HOLD 停止看门狗定时器工作,降低功耗0 WDT功能激活1 时钟禁止输入,计数停止WDT (看门狗)配置语句WDTCTL=WDTPW+WDTHOLD ;// 将 WDTPW+WDTHOLD 赋值给 WDTCTL,关闭看门狗定时器控制寄存器( Stop watchdogtimer)IE1 |= WDTIE ;// 使能 WDT 中断WDTCTL = WDT_ADL Y_1000 ;//WDT 1 s / 4 间隔计时器WDTCTL = WDTPW + WDTHOLD + WDTNMI + WDTNMIES ;//WDTCTL 由高8位口令和低8位控制命令组成,要写入操作 WDT的控制命令,出于安全原因必须先正确写入高字节看门狗口令。

口令为5AH,如果口令写错将导致系统复位。

读 WDTCTL时不需要口令。

这个控制寄存器还可以用于设置NMI引脚功能。

WDT 看门狗定时器(Watch Dog Timer),这是16位增计数器,由MSP430所选定的时钟电路产生的固定周期时钟信号对计数器进行加法计数。

MSP430G2553数据手册

8

512 2x TA3

8

8

256 2x TA3

8

8

256 2x TA3

8

8

256 2x TA3

8

8

512 2x TA3

8

-

USCI A0/B0

时钟

I/O 封装类型

24 32-QFN

28 引脚

24 TSSOP 封

LF,DC

装

1

O,VL

20 引脚

O

16 TSSOP 封

装

16

20 引脚 PDIP 封装

LF,DC

装

1

O,VL

20 引脚

O

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24 32-QFN

28 引脚

24 TSSOP 封

LF,DC

装

1

O,VL

20 引脚

O

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24 32-QFN

28 引脚

24 TSSOP 封

LF,DC

装

1

O,VL

20 引脚

3

MSP430G2x53 MSP430G2x13

ZHCS178D – APRIL 2011 – REVISED NOVEMBER 2011

器件引出脚配置、MSP430G2x13 和 MSP430G2x53、20 引脚器件、 TSSOP 和 PDIP 封装

DVCC 1 P1.0/TA0CLK/ACLK/A0/CA0 2 P1.1/TA0.0/UCA0RXD/UCA0SOMI/A1/CA1 3 P1.2/TA0.1/UCA0TXD/PUCA0SIMO/A2/CA2 4 P1.3/ADC10CLK/CAOUT/VREF-/VEREF-/A3/CA3 5 P1.4/SMCLK/UCB0STE/UCA0CLK/VREF+/VEREF+/A4/CA4/TCK 6 P1.5/TA0.0/UCB0CLK/UCA0STE/A5/CA5/TMS 7

mps430G2553中文资料

28 引脚

24 TSSOP 封

LF,

装

-

1

DCO,

VLO

20 引脚

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24

32 引脚 QFN 封装

28 引脚

24 TSSOP 封

LF,

装

-

1

DCO,

VLO

20 引脚

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24

32 引脚 QFN 封装

28 引脚

引导加 载器 (BSL)

嵌入式 仿真模

块 (EEM)

1

1

1

1

1

1

1

1

1

1

表 1. 提供的选项(1)(2) (接下页)

ZHCS178E – APRIL 2011 – REVISED JANUARY 2012

闪存 (KB)

RAM (B)

Timer_A

COMP_A+ 通道

10 通道 ADC

USCI A0/B0

24 TSSOP 封

LF,

装

-

1

DCO,

VLO

20 引脚

16 TSSOP 封

装

16

20 引脚 PDIP 封装

24

32 引脚 QFN 封装

28 引脚

24 TSSOP 封

LF,

装

-

1

DCO,

VLO

20 引脚

16 TSSOP 封

装

16

20 引脚 PDIP 封装

Copyright © 2011–2012, Texas Instruments Incorporated

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MSP430G2553学习笔记(数据手册)MSP430G2553性能参数(DIP-20) 工作电压范围:1.8~3.6V。

5种低功耗模式。

16位的RISC结构,62.5ns指令周期。

超低功耗:运行模式-230µA;待机模式-0.5µA;关闭模式-0.1µA;可以在不到1µs的时间里超快速地从待机模式唤醒。

基本时钟模块配置:具有四种校准频率并高达16MHz的内部频率;内部超低功耗LF振荡器;32.768KHz晶体;外部数字时钟源。

两个16 位Timer_A,分别具有三个捕获/比较寄存器。

用于模拟信号比较功能或者斜率模数(A/D)转换的片载比较器。

带内部基准、采样与保持以及自动扫描功能的10位200-ksps 模数(A/D)转换器。

16KB闪存,512B的RAM。

16个I/O口。

注意:MSP430G2553无P3口!MSP430G2553的时钟基本时钟系统的寄存器DCOCTL-DCO控制寄存器DCOxDCO频率选择控制1MODxDCO频率校正选择,通常令MODx=0注意:在MSP430G2553上电复位后,默认RSEL=7,DCO=3,通过数据手册查得DCO频率大概在0.8~1.5MHz之间。

BCSCTL1-基本时钟控制寄存器1XT2OFF不用管,因为MSP430G2553内部没有XT2提供的HF时钟XTS不用管,默认复位后的0值即可DIV Ax设置ACLK的分频数00 /101 /210 /411 /8RSELxDCO频率选择控制2BCSCTL2-基本时钟控制寄存器2SELMxMCLK的选择控制位00 DCOCLK01 DCOCLK10 LFXT1CLK或者VLOCLK11 LFXT1CLK或者VLOCLK DIVMx设置MCLK的分频数00 /101 /210 /411 /8SELSSMCLK的选择控制位0 DCOCLK1 LFXT1CLK或者VLOCLK DIVSx设置SMCLK的分频数00 /101 /210 /411 /8DCORDCO直流发生电阻选择,此位一般设00 内部电阻1 外部电阻BCSCTL3-基本时钟控制寄存器3XT2Sx不用管LFXT1Sx00 LFXT1选为32.768KHz晶振01 保留10 VLOCLK11 外部数字时钟源XCAPxLFXT1晶振谐振电容选择00 1pF01 6pF10 10pF11 12.5pFmsp430g2553.h中基本时钟系统的内容/************************************************************* Basic Clock Module************************************************************/#define __MSP430_HAS_BC2__ /* Definition to show that Module is available */SFR_8BIT(DCOCTL); /* DCO Clock Frequency Control */SFR_8BIT(BCSCTL1); /* Basic Clock System Control 1 */SFR_8BIT(BCSCTL2); /* Basic Clock System Control 2 */SFR_8BIT(BCSCTL3); /* Basic Clock System Control 3 */#define MOD0 (0x01) /* Modulation Bit 0 */#define MOD1 (0x02) /* Modulation Bit 1 */#define MOD2 (0x04) /* Modulation Bit 2 */#define MOD3 (0x08) /* Modulation Bit 3 */#define MOD4 (0x10) /* Modulation Bit 4 */#define DCO0 (0x20) /* DCO Select Bit 0 */#define DCO1 (0x40) /* DCO Select Bit 1 */#define DCO2 (0x80) /* DCO Select Bit 2 */#define RSEL0 (0x01) /* Range Select Bit 0 */#define RSEL1 (0x02) /* Range Select Bit 1 */#define RSEL2 (0x04) /* Range Select Bit 2 */#define RSEL3 (0x08) /* Range Select Bit 3 */#define DIVA0 (0x10) /* ACLK Divider 0 */#define DIVA1 (0x20) /* ACLK Divider 1 */#define XTS (0x40) /* LFXTCLK 0:Low Freq. / 1: High Freq. */ #define XT2OFF (0x80) /* Enable XT2CLK */#define DIVA_0 (0x00) /* ACLK Divider 0: /1 */#define DIVA_1 (0x10) /* ACLK Divider 1: /2 */#define DIVA_2 (0x20) /* ACLK Divider 2: /4 */#define DIVA_3 (0x30) /* ACLK Divider 3: /8 */#define DIVS0 (0x02) /* SMCLK Divider 0 */#define DIVS1 (0x04) /* SMCLK Divider 1 */#define SELS (0x08) /* SMCLK Source Select 0:DCOCLK /1:XT2CLK/LFXTCLK */#define DIVM0 (0x10) /* MCLK Divider 0 */#define DIVM1 (0x20) /* MCLK Divider 1 */#define SELM0 (0x40) /* MCLK Source Select 0 */#define SELM1 (0x80) /* MCLK Source Select 1 */#define DIVS_0 (0x00) /* SMCLK Divider 0: /1 */#define DIVS_1 (0x02) /* SMCLK Divider 1: /2 */#define DIVS_2 (0x04) /* SMCLK Divider 2: /4 */#define DIVS_3 (0x06) /* SMCLK Divider 3: /8 */#define DIVM_0 (0x00) /* MCLK Divider 0: /1 */#define DIVM_1 (0x10) /* MCLK Divider 1: /2 */#define DIVM_2 (0x20) /* MCLK Divider 2: /4 */#define DIVM_3 (0x30) /* MCLK Divider 3: /8 */#define SELM_0 (0x00) /* MCLK Source Select 0: DCOCLK */#define SELM_1 (0x40) /* MCLK Source Select 1: DCOCLK */#define SELM_2 (0x80) /* MCLK Source Select 2: XT2CLK/LFXTCLK */#define SELM_3 (0xC0) /* MCLK Source Select 3: LFXTCLK */#define LFXT1OF (0x01) /* Low/high Frequency Oscillator Fault Flag */#define XT2OF (0x02) /* High frequency oscillator 2 fault flag */#define XCAP0 (0x04) /* XIN/XOUT Cap 0 */#define XCAP1 (0x08) /* XIN/XOUT Cap 1 */#define LFXT1S0 (0x10) /* Mode 0 for LFXT1 (XTS = 0) */#define LFXT1S1 (0x20) /* Mode 1 for LFXT1 (XTS = 0) */#define XT2S0 (0x40) /* Mode 0 for XT2 */#define XT2S1 (0x80) /* Mode 1 for XT2 */#define XCAP_0 (0x00) /* XIN/XOUT Cap : 0 pF */#define XCAP_1 (0x04) /* XIN/XOUT Cap : 6 pF */#define XCAP_2 (0x08) /* XIN/XOUT Cap : 10 pF */#define XCAP_3 (0x0C) /* XIN/XOUT Cap : 12.5 pF */#define LFXT1S_0 (0x00) /* Mode 0 for LFXT1 : Normal operation */ #define LFXT1S_1 (0x10) /* Mode 1 for LFXT1 : Reserved */#define LFXT1S_2 (0x20) /* Mode 2 for LFXT1 : VLO */#define LFXT1S_3 (0x30) /* Mode 3 for LFXT1 : Digital input signal */#define XT2S_0 (0x00) /* Mode 0 for XT2 : 0.4 - 1 MHz */#define XT2S_1 (0x40) /* Mode 1 for XT2 : 1 - 4 MHz */#define XT2S_2 (0x80) /* Mode 2 for XT2 : 2 - 16 MHz */#define XT2S_3 (0xC0) /* Mode 3 for XT2 : Digital input signal */基本时钟系统例程(DCO)MSP430G2553在上电之后默认CPU执行程序的时钟MCLK来自于DCO时钟。