集成电路版图设计基础第7章:匹配

集成电路的设计基础

13

版图几何设计规则

N阱设计规则示意图

2019/11/13

《集成电路设计基础》

14

版图几何设计规则

P+、N+有源区相关的设计规则列表

编号 描 述

尺

寸

目的与作用

2.1

P+、N+有源区宽度

3.5

保证器件尺寸,减少窄沟道效

应

2.2

P+、N+有源区间距

3.5

减少寄生效应

2019/11/13

《集成电路设计基础》

2019/11/13

《集成电路设计基础》

9

版图几何设计规则

• 有几种方法可以用来描述设计规则。 其中包括:

*以微米分辨率来规定的微米规则 *以特征尺寸为基准的λ规则

2019/11/13

《集成电路设计基础》

10

版图几何设计规则

层次

人们把设计过程抽象成若干易 于处理的概念性版图层次,这些层 次代表线路转换成硅芯片时所必需 的掩模图形。

(4)布线层选择。

2019/11/13

《集成电路设计基础》

38

布线规则

2019/11/13

《集成电路设计基础》

39

5 版图设计及版图验证

版图设计一般包括:

基本元器件版图设计 布局和布线 版图分析与检验

2019/11/13

《集成电路设计基础》

40

版图设计及版图验证

版图的构成

版图由多种基本的几何图形所构成。 常见的几何图形有:

《集成电路设计基础》

49

半定制标准单元示意图

抽象图是把版图中与布局布线有关的图 形信息抽出来而删去其他信息所形成的 图形。 其中包括:单元的边界、电源线、地线、 N阱、硅栅、输入/输出的脚(PIN)等以 及其他必要的信息。

版图的匹配和抗干扰设计

i 1

N

i

s

1 2 i m N 1 i 1

N

匹配设计

• 称均值mδ为系统失配 • 称方差sδ为随机失配 • 失配的分布: • 3δ失配:

| mδ |+3 sδ 概率99.7%

匹配设计

• 失配的原因

– 随机失配:尺寸、掺杂、氧化层厚度等影响元 件值的参量的微观波动(fluctuation)

匹配设计

• 晶体管匹配:主要关心元件之间栅源电压 (差分对)和漏极电流(电流镜)的偏差

– 栅源电压失配为:

k VGS Vt Vgs1 2k 2 – 漏极电流失配为:

2Vt I D 2 k2 1 I D1 k1 Vgs1

ΔVt, Δk为元件间的阈 值电压和跨导之差, Vgs1为第1个元件的有 效栅电压,k1, k2为两 个元件的跨导

• 降低系统失配的例子

– 一维公用重心设计 – 二维公用重心设计

匹配设计

• 降低系统失配的例子

– 单元整数比(R1:R2=1:1.5) – 均匀分布和公用重心 – Dymmy元件

R1 R2 R1 R2 R1

dummy R1 R2

R2 dummy

匹配设计

• 降低系统失配的例子

– 单元整数比(8:1) – 加dummy元件 – 公用重心布局 – 问题:布线困难,布线 寄生电容影响精度

15Ω

4u

匹配设计

• 系统失配例子 ——电容

假设对poly2的刻蚀 工艺偏差是0.1um, 两个电容的面积分 别是(10.1)2和(20.1)2, 则系统失配约为 1.1%

20um 20um

10um 10um

匹配设计

07集成电路版图设计技巧

错误布线

正确布线

引线孔、通孔: 引线孔、通孔:

一般情况下,衬底接触和有源区接触布线 一般情况下, 需要在整个接触区域内,保持一定间距, 需要在整个接触区域内,保持一定间距, 连续制作一排引线孔; 连续制作一排引线孔; 模拟电路部分多晶硅栅引线处, 模拟电路部分多晶硅栅引线处,制作两个 通孔;数字电路部分由于面积限制, 通孔;数字电路部分由于面积限制,多晶 硅栅引线处制作一个引线孔; 硅栅引线处制作一个引线孔; 相邻金属层之间,如果面积允许, 相邻金属层之间,如果面积允许,至少制 作两个接触孔。 作两个接触孔。

二、设计技巧

过桥:布线过程中,如果金属线相互阻挡无法通 过桥:布线过程中, 可以使用下层多晶硅作为导线,称为“ 过,可以使用下层多晶硅作为导线,称为“过 过桥多晶硅电阻要小,且不能对大电流、 桥”。过桥多晶硅电阻要小,且不能对大电流、 大电压线路使用过桥。 大电压线路使用过桥。 电源、地线:注意电流通过能力, 电源、地线:注意电流通过能力,根据工艺要求 与模块内器件数量设置足够的线宽。 与模块内器件数量设置足够的线宽。 栅极连接:模拟电路器件之间 即使相距很近) 器件之间( 栅极连接:模拟电路器件之间(即使相距很近) 的栅极尽量使用金属连接,而不要用多晶硅。 的栅极尽量使用金属连接,而不要用多晶硅。降 低后期修改成本。 低后期修改成本。

集成电路版图基础

光电工程学院

王智鹏

一、版图设计原则

图形对称 将模块设计为矩形 模块内电流流向相同 模块内多晶硅栅相互平行 金属布线尽量不跨越器件

MOS管中心对称布局 管中心对称布局

A B

布局: 布局:

集成电路版图基本布局规则是PMOS管在 管在 集成电路版图基本布局规则是 管在下, 上、NMOS管在下,夹在一条电源线和一 管在下 条地线之间,构成一行。 条地线之间,构成一行。 每一模块中除电源和地线外的左右两侧分 别作为输入和输出信号线的布线位置。 别作为输入和输出信号线的布线位置。 各行依次并列排开, 各行依次并列排开,实现电源线与地线的 共用。 共用。

第七章-MOS管模拟集成电路设计基础

右图所示的是威尔电流 镜的改进结构。由M4构成的 有源电阻“消耗”了一个VGS, 使M2、M3的源漏电压相等。 如果M1和M2的宽长比相同, 从M1、M2的栅极到M2、M3 的源极的压差为2VGS2,如果 M2、M3相同,则M4的栅源 电压就为VGS2,使M3管的源 漏电压和M2的源漏电压相 同,都为VGS2。这样的改进 使参考支路和输出支路电流 以一个几乎不变的比例存在。

图7.3.2 NMOS威尔逊电流镜

M2在电路中相当于一个串联电阻(有源电阻),构成电流串联负反馈。M3 的漏节点提供了M1的偏置电压,如果因为某种原因使输出电流Io增加,这个增 加了的电流同时也将导致M2的VGS2增加,使得M1的栅源电压VGS1减小,从而 使电流减小。反之,如果某种原因使Io减小,同样也会因M2的作用阻止电流变 小。正是因为M2的电流串联负反馈的作用,使Io趋于恒流,提高了交流输出电 阻。

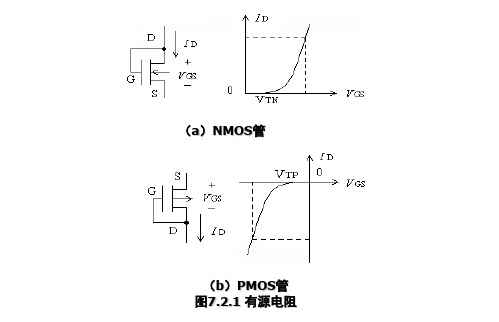

(a)NMOS管

(b)PMOS管 图7.2.1 有源电阻

1、电流偏置电路

在模拟集成电路中,电流偏置电路的基本形式是电流

镜。所谓的电流镜是由两个

或多个并联的相关电流

支路组成,各支路的电

流依据一定的器件比例

关系而成比例。

1) NMOS基本电流镜

NMOS基本电流镜

由两个NMOS晶体管组

成,如图7.3.1所示。

图(a),V1=VGS1,V2=VGS1+VGS2;图(b)是一个CMOS的分压器结构,它的分压原 理与NMOS并没有什么区别,它的Vo也可以用上式计算。

图6点,那就是它们的输出电 压值随着电源电压的变化将发生变化。究其原因是因为电漏电压的 波动直接转变为MOS晶体管的VGS的变化。如果电源电压的波动能够被 某个器件“消化”掉,而不对担当电压输出的VGS产生影响就可以使 输出电压不受电源电压波动的影响。

集成电路模拟版图设计基础

GND

电路图

版图

第一部分:了解版图

2. 版图的意义: 3. 1)集成电路掩膜版图设计师实现集成电路制造

所必不可少的设计环节,它不仅关系到集成电路 的功能是否正确,而且也会极大程度地影响集成 电路的性能、成本与功耗。 4. 2)它需要设计者具有电路系统原理与工艺制造 方面的基本知识,设计出一套符合设计规则的 “正确”版图也许并不困难,但是设计出最大程 度体现高性能、低功耗、低成本、能实际可靠工 作的芯片版图缺不是一朝一夕能学会的本事。

第四部分:版图设计艺术

6)保证对称性 6.1 轴对称的布局 6.2 四角交叉布局 6.2.1 缓解热梯度效应和工艺梯度效应的影响 6.2.2 连线时也要注意对称性 同一层金属 同样多的瞳孔 同样长的金属线 6.3 器件之间、模块之间,尽量让所有东西布局对称 7)信号线匹配 7.1 差分信号线,彼此靠近,相同长度 7.2 寄生效应相同,延迟时间常数相同,信号上升下降时间相同 8)器件尺寸的选择 8.1 相同的宽度 8.2 尺寸大些 8.2.1 工艺刻蚀偏差所占的比例小些

2.1器件 2.1.2 电阻 选择合适的类型,由电阻阻值、方块电

阻值,确定 W、L;R=L/W*R0

电阻类型

电阻版图

第二部分:版图设计基础

2.1器件 2.1.3 电容

1) 电容值计算C=L*W*C0 2) 电容分类:

poly电容 MIM电容 基于单位面积电容值 MOS电容 源漏接地,基于栅电容, C=W*L*Cox

IC模拟版图设计

第三部分:版图的准备 必要文件 设计规则 DRC文件 LVS文件

第三部分:版图的准备

1. 必要文件 PDK *.tf display.drf DRC LVS cds.lib .cdsenv .cdsinit

集成电路版图设计基础电阻电容匹配

设长度为20um 和40um的电阻

若多晶硅刻蚀造成ΔL=0.2um,

则实际长度比为(20.2)/(40.2)=0.503,造成0.5%的失 配。因此,

把匹配电阻分成相同尺寸的电阻段消除工艺误差

分成2段,则实际长度比为 (20.2)/(20.2+20.2)=0.5

6

3 互联寄生

2021/3/11

如果方块电阻小, 导线电阻、通孔电阻不可忽略

若金属走线在电阻上方跨过,各电阻段上的金 属覆盖量不同会导致金属化诱发失配。

需要精确匹配的器件之间的缝隙不应该用来走线

14

8、机械应力和封装偏移

2021/3/11

应力会引起硅电阻率变化,金属和陶瓷封 装应力最小,但成本高

硅和环氧树脂的热膨胀系数相差10倍,随 着器件冷却产生应力

15

8、机械应力和封装偏移

26

热梯度

2021/3/11

热分布的对称轴取决于功率器件的位置和方向

器件应该置于芯片的的轴上产生对称的热分布 ,尽可能远离匹配器件,倾向于中央,

27

电阻布局 热匹配

2021/3/11

28

热电效应

2021/3/11

只要两种材料接触,就会形成接触电势差,半导 体金属的接触电势差受温度强烈影响,如果接触 发生在不同的温度,电阻两端表现为电势差。

每个单位电容最小宽度的导线连接上极板,保持每个 电容的导线电容相等。

11.不要在没有进行静电屏蔽的电容上走 线

导线和极板间的电容将引起匹配电容失配

12.优先使用厚氧化层电容

厚氧化层电介厚度失配比例小。

48

2021/3/11

13.电容放在低应力区域

避免放在四个角,中央应力最小,从中央到边缘的一 般的距离内应力小

第7章 PCB设计基础

• 4. 元件的图形符号 • 元件的图形符号反映了元件外形轮廓的形状及尺寸,与元件的引脚布

局一起构成元件的封装形式。印制元件图形符号的目的是显示元件在 PCB上的布局信息,为装配、调试及检修提供方便。在Protel 2004中, 元件的图形符号被设置在丝印层。

7.1.2 PCB的基本元素

• 5. 其他辅助性说明信息 • 为了阅读PCB或装配、调试等需要,可以加入一些辅助信息,包括图形或文字。

图7.3 【板层和颜色】对话框

7.1.3 PCB工作层与管理

• 在【板层和颜色】对话框中,有六个区域分别设置在PCB编辑区要显示的工作层

•

及其颜色。在每个区域中有一个【表示】复选框,选中工作层,在PCB编辑区中 将显示该层标签页;单击【颜色】下的颜色,弹出【颜色】对话框,在该对话框 中可以对电路板层的颜色进行编辑。 在系统颜色栏中,可以对网络连接预拉线(Connections and From Tos)、DRC错 误标记(DRC Error Markers)、选择目标后的颜色(Selections)、可视栅格(Visible Grid)、焊盘内孔(Pad Holes)、过孔内孔(Via Holes)、PCB边框颜色(Board Line Color)、PCB区域颜色(Board Area Color)、图纸边框颜色(Sheet Line Color)、图 纸区域颜色(Sheet Area Color)、工作窗口起始颜色(Workspace Start Color)及工 作窗口结束颜色(Workspace End Color)等内容进行颜色设置和是否显示设置。 3. 工作层的管理 按快捷键D|K弹出【图层堆栈管理器】对话框,如图7.4所示。在该对话框中, 可以为顶部或底部添加绝缘层(【顶部绝缘体】)、(【底部绝缘体】);可以追加 层(【追加层】)、添加内部电源/接地层(【加内电层】)、将选中的工作层上移 (【向上移动】)或下移(【向下移动】)、删除当前层(【删除】)、设置属性参数 (【属性】)和配置钻孔对,单击【菜单】按钮弹出的菜单,和面板上的命令按钮 相同。

集成电路版图基础

DRC文件

第三部分:版图的准备

4. LVS文件

4.1 LVS: layout versus schematic, 用来进行版图与电路 图对比。 4.2 我们通常使用calibre 这个 工具来进行lvs 检查, 根据run 出来的错误提 示去改正版图,最后 清掉所有的lvs错误。

第三部分:版图的准备

第四部分:版图设计艺术

1.

模拟电路和数字电路的首要目标

模拟电路关注的是功能 1) 电路性能、匹配、速度等 2) 没有EDA软件能全自动实现,所以需要手工处理 数字电路关注的是面积 1) 什么都是最小化 2) Astro、appollo等自动布局布线工具

PMOS版图

第二部分:版图设计基础

以TSMC ,CMOS ,P型衬底单 Nwell工艺为例:NMOS的版 图包括以下层次的图形: NIMP (N+注入) DIFF(有源区) Poly (栅) CONT(过孔) Metal1 (金属) 以TSMC ,CMOS ,P型衬底单 Nwell工艺为例:PMOS的版 图包括以下层次的图形: Nwell (N阱) PIMP (P+注入) DIFF(有源区) Poly (栅) CONT(过孔) Metal1 (金属)

4.3 lvs command file 的设定: 1) 根据你的工艺以及需 求选择你所需要的验 证检查。 2) 选择用命令界面运行 LVS,定义查看LVS报 告文件及LVS报错个 数。

定义金 属层数 关闭ERC 检查

用命令跑 LVS的方式

LVS COMPARE CASE NAMES SOURCE CASE YES LAYOUT CASE YES

IC模拟版图设计

目录

第一部分:了解版图

第七章 MOS管模拟集成电路设计基础

2. 以多晶硅作为下极板的MOS电容器 以多晶硅作电容器下极板所构造的MOS电容器是无极性电

容器,如下图所示。这种电容器通常位于场区,多晶硅下极板 与衬底之间的寄生电容比较小。

(a)金属做上极板 (b)多晶硅做上极板 图7.2.3 多晶硅为下极板的MOS电容器结构

3.薄膜电容器 在某些电路中,需用较大的电容或对电容有某些特殊要求,

7.2 MOS模拟集成电路中的基本元器件

7.2.1 模拟集成电路中电阻器----无源电阻和有源电阻

1. 掺杂半导体电阻 (1)扩散电阻

所谓扩散电阻是指采用热扩散掺杂的方式构造而成的电阻。 这是最常用的电阻之一,工艺简单且兼容性好,缺点是精度稍 差。 (2)离子注入电阻

同样是掺杂工艺,由于离子注入工艺可以精确地控制掺杂 浓度和注入的深度,并且横向扩散小,因此,采用离子注入方 式形成的电阻的阻值容易控制,精度较高。

社,2004年5月(21世纪高等学校电子信息类教材).

第七章 MOS管模拟集成电路设计基础 7.1 引言

1、采用数字系统实现模拟信号处理 现实世界中的各种信号量通常都是以模拟信号的形式出现

的,设计一个电路系统的基本要求,就是采集与实现系统功能 相关的模拟信号,按系统的功能要求对采集的信号进行处理, 并输出需要的信号(通常也是模拟量)。

1、电流偏置电路

在模拟集成电路中,电流偏置电路的基本形式是电流

镜。所谓的电流镜是由两个

或多个并联的相关电流

支路组成,各支路的电

流依据一定的器件比例

关系而成比例。

Hale Waihona Puke 1) NMOS基本电流镜NMOS基本电流镜

由两个NMOS晶体管组 成,如图7.3.1所示。

图7.3.1 NMOS基本电流镜

版图的匹配和抗干扰设计

偏置

参考

抗干扰设计

• 加滤波电容

– 电源线上和版图空余地 方可填加MOS电容进行 电源滤波 – 对模拟电路中的偏置电 压和参考电压加多晶电 容进行滤波 MOS CAP

P-P CAP

• 刻蚀速率与刻蚀窗的大小有关,导致隔离大的多 晶宽度小于隔离小的多晶宽度 均与周围环境有关 • 同类型扩散区相邻则相互增强,异类型相邻则相 互减弱

匹配设计

• 系统失配

– 梯度效应

• 压力、温度、氧化层厚度的梯度问题,元件间的 差异取决于梯度和距离

匹配设计

• 系统失配例子 ——电阻

– 电阻设计值之为2:1 – 由于poly2刻蚀速度的偏差, 假设其宽度偏差为0.1u,则会 带来约2.4%的失配 – 接触孔和接头处的poly电阻, 将会带来约1.2%的失配;对 于小电阻,失配会变大 R=R□•(Leff)/(Weff) R□=996欧姆 Wp = 0.1u 5u 2u

• 随机失配可通过选择合适的元件值和尺寸来减小

– 系统失配:工艺偏差,接触孔电阻,扩散区相 互影响,机械压力,温度梯度等

• 系统失配可通过版图设计技术来降低

匹配设计

• 随机统计波动 (Fluctuations)

– 周围波动(peripheral fluctuations)

• 发生在元件的边沿 • 失配随周长的增大而减小

Analog Power Digital Analog Digital Power

抗干扰设计

• 电容的屏蔽

电路中的高阻接 点接上极板,以 减小寄生和屏蔽 干扰;电容下面 用接地的阱来屏 蔽衬底噪声 此地应为“干净” 地!可独立接出, 不与其他电路共享

CAP

抗干扰设计

• 敏感信号线的屏蔽

《集成电路设计导论》课件

IC设计的测试和验证

探讨IC设计的测试和验证技术, 以确保设计的正确性和可靠性。

总结与展望

集成电路设计的现状与未来趋势

总结集成电路设计的现状并展望未来的发展趋 势,如人工智能芯片和物联网应用。

集成电路设计中的挑战与机遇

探讨集成电路设计中面临的挑战和机遇,如功 耗优化和设计验证等。

《集成电路设计导论》 PPT课件

这是一套《集成电路设计导论》的PPT课件,针对集成电路的概念、分类和历 史发展等主题进行介绍,通过丰富的内容和精美的图片,让学习更加生动有 趣。

第一章:集成电路概述

集成电路的定义

介绍集成电路的基本概念和定义,以及其在电子领域中的重要作用。

集成电路的分类

分析不同类型的集成电路,包括数字集成电路、模拟集成电路和混合集成电路。

探讨集成电路设计中常用的仿真 技术,如时序仿真、噪声仿真和 功耗仿真等。

CMOS工艺的基本原理和特点,以及其在集成电路设计中的应用。

2

CMOS电路设计基础

讨论CMOS电路设计的基本原则和技巧,包括逻辑门设计和布局。

3

CMOS电路的布局与布线

解释CMOS电路布局与布线的重要性,以及如何进行最佳布局和布线。

第五章:模拟电路设计

模拟电路设计基础

介绍模拟电路设计的基本原理和 技术,包括信号放大、滤波和稳 压等。

模拟电路的建模与仿真

讨论模拟电路的建模方法和仿真 技术,以验证电路设计的准确性 和性能。

模拟电路的测试和调试

探讨模拟电路的测试和调试方法, 以保证电路的可靠性和稳定性。

第六章:数字电路设计

1

数字电路的逻辑设计

第四章:数模转换电路设计

数模转换电路的种类

集成电路版图基础.pdf

由一个NMOS,一个PMOS组成, 先画出两个正确尺寸的mos版图, 然后对mos的四端进行连线。

第二部分:版图设计基础

2.1.2 电阻

根据电路选择的电阻类型(ppolyf_s)、电阻的W/L值来画版图,相对应的电 阻类型应当由哪些层的图形组成,这个参照厂家提供的design rule。

1)集成电路掩膜版图设计是实现集成电路制造所必不 可少的设计环节,它不仅关系到集成电路的功能是 否正确,而且也会极大程度地影响集成电路的性能、 成本与功耗。

2)它需要设计者具有电路系统原理与工艺制造方面的 基本知识,设计出一套符合设计规则的“正确”版 图也许并不困难,但是设计出最大程度体现高性能、 低功耗、低成本、能实际可靠工作的芯片版图缺不 是一朝一夕能学会的本事。

第二部分:版图设计基础

4) 打开cell a--工作区和层次显示器

电路转换为选定工艺的版图,版图设计完成后,将版图的数据发 给foundry,foundry收到数据后按照数据制作掩膜版(mask), mask上的图形就代表了最终在芯片加工上需要保留或者需要刻蚀 掉的位置。

VDD

3u/0.18u

IN

OUT

1u/0.18u

GND

电路图

版图

第一部分:了解版图

3. 版图的意义:

第四部分:版图的艺术(这个作为后期目标,暂作了解)

1. 模拟版图和数字版图的首要目标 2. 匹配 3. 寄生效应 4. 噪声 5. 布局规划 6. ESD 7. 封装

IC模拟版图设计

第一部分:了解版图

1. 芯片是怎么来的 2. 版图的定义 3. 版图的意义 4. 版图的工具 5. 版图的设计流程

1) 启动软件

使用Xmanager登陆linux服务器

半导体集成电路课程教学大纲

《半导体集成电路》课程教学大纲(包括《集成电路制造基础》和《集成电路原理及设计》两门课程)集成电路制造基础课程教学大纲课程名称:集成电路制造基础英文名称:The Foundation of Intergrate Circuit Fabrication课程类别:专业必修课总学时:32 学分:2适应对象:电子科学与技术本科学生一、课程性质、目的与任务:本课程为高等学校电子科学与技术专业本科生必修的一门工程技术专业课。

半导体科学是一门近几十年迅猛发展起来的重要新兴学科,是计算机、雷达、通讯、电子技术、自动化技术等信息科学的基础,而半导体工艺主要讨论集成电路的制造、加工技术以及制造中涉及的原材料的制备,是现今超大规模集成电路得以实现的技术基础,与现代信息科学有着密切的联系。

本课程的目的和任务:通过半导体工艺的学习,使学生掌握半导体集成电路制造技术的基本理论、基本知识、基本方法和技能,对半导体器件和半导体集成电路制造工艺及原理有一个较为完整和系统的概念,了解集成电路制造相关领域的新技术、新设备、新工艺,使学生具有一定工艺分析和设计以及解决工艺问题和提高产品质量的能力。

并为后续相关课程奠定必要的理论基础,为学生今后从事半导体集成电路的生产、制造和设计打下坚实基础。

二、教学基本要求:1、掌握硅的晶体结构特点,了解缺陷和非掺杂杂质的概念及对衬底材料的影响;了解晶体生长技术(直拉法、区熔法),在芯片加工环节中,对环境、水、气体、试剂等方面的要求;掌握硅圆片制备及规格,晶体缺陷,晶体定向、晶体研磨、抛光的概念、原理和方法及控制技术。

2、掌握SiO2结构及性质,硅的热氧化,影响氧化速率的因素,氧化缺陷,掩蔽扩散所需最小SiO2层厚度的估算;了解SiO2薄膜厚度的测量方法。

3、掌握杂质扩散机理,扩散系数和扩散方程,扩散杂质分布;了解常用扩散工艺及系统设备。

4、掌握离子注入原理、特点及应用;了解离子注入系统组成,浓度分布,注入损伤和退火。

第七章集成电路版图设计

Electrode

Metal1 Via1 Metal2 Via2 Metal3 Glass

56

49 50 51 61 62 52

CEL

CMF CVA CMS CVS CMT COG

第二层多晶硅

第一层金属 连接第一与第二层金属的接触孔 第二层金属 连接第二与第三层金属的接触孔 第三层金属 钝化玻璃

新加坡Chartered 0.35mCMOS工艺定义的全部工艺层

(extension)

Y

X

(a)

(b)

TSMC_0.35m CMOS工艺版图各层图形之间最小交叠

P_l\plus_sele ct/N_plu s_select

X

Electrode

Contact

Metal1

Metal2

Metal3

N_well

Active

Via1

Via2

Poly

Y

N_well Active

18

6 3 1 3 3 2 2 2 2 15 15 2 2 2 3 3 2 3 2 15 15 3 4 3 3 3

3. 最小交叠(min Overlap)

交迭有两种形式:

a) 一 几 何 图 形 内 边 界 到 另 一 图 形 的 内 边 界 长 度

(overlap)

b) 一 几 何 图 形 外 边 界 到 另 一 图 形 的 内 边 界 长 度

TSMC_0.35m CMOS工艺中各版图层的线条最小宽度

层 (layer) N阱(N_well) 扩散层(P_plus_select/N_plus_select) 最小宽度(minWidth) 单位:lambda=0.2m 12 2

多晶硅(Poly) 有源层(Active)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

需要匹配的器件彼此靠近 注意周围器件 保持匹配器件方向一致

遵守这 3条基本原则, 就可以很好的实现匹配.

school of phye

basics of ic layout design

12

匹配方法 之一:根器件方法 root device method 之一:

根部件,在这里指这样一个电阻,可以根据这一个电阻设计出所 有其他的电阻. 我们经常在选择根器件的时侯, 用最小的电阻作为根器件,这样的 选择当然也可以实现我们需要的匹配, 但同时我们却忽略了另外 一个问题,那就是像 2 K 这样的电阻如果用 2 5 0 做根器件, 那么就需要 8个根器件串联起来实现, 这就导致了这 8个电阻之 间接触电阻也同时加大了,这是我们不希望看到的. 采用根部件的最好方法是找出一个中间值,例如用 1 K 的电阻 作为值将电阻串联和并联起来.这种方法节省了接触电阻的总数 接触电阻的总数 使其所占的比例减少 面积 减少, 减少,因为电阻之间的间隙数 减少 面积也许会减少 减少 薄层电阻,而非接触 少了,现在占主导地位 主导地位的是电阻器件本身的薄层电阻 而非接触 主导地位 薄层电阻 电阻. 电阻 利用根部件时, 如果所有的电阻尺寸一样, 形状一样, 方向一致而 且相互靠近, 那么就可以得到一个很好的匹配.

2

匹配规则

之一:把匹配器件相互靠近放置. 把匹配器件相互靠近放置.

place matched devices close to each other.

之二:使器件保持同一方向. 使器件保持同一方向.

keep devices in the same orientation.

之三:选择一个中间值作为根部件. 选择一个中间值作为根部件. choose a middle value for a root component.

regular (rectangular shape)

parallel elements

Possibly, the current flowing in the same direction.

school of phye

basics of ic layout design

8

简单匹配 - asymmetry due to fabrication

cross-guad your device pairs.

school of phye

basics of ic layout design

4

匹配规则

之七:使布线上的寄生参数匹配. 使布线上的寄生参数匹配.

match the parasitics on your wiring.

之八:使每一样东西都对称. 使每一样东西都对称.

school of phye basics of ic layout design 13

匹配方法 之一:根器件方法 root device method 之一:

1k

2k

2k

500

250

1k

2k

2k

500

250

school of phye

basics of ic layout design

14

匹配方法 之二:交叉法 interdigitating device 之二:

河

南

大

学

Henan

University

集成电路版图设计基础

basics of IC layout design

instructor: Zhang Qihui e-mail:qhzhang07@

第六章 寄生参数

匹配规则 简单匹配 匹配方法

school of phye

basics of ic layout design

20 19.8 20 20.5

basics of ic layout design

2 1.8

2 2.5

school of phye

11

匹配方法

当集成电路产业刚刚起步的时候,制造工业仍然相对落 后.即使你将两个需要匹配的器件放的很近, 我们也仍 然无法保证它们的一致性. 现在虽然制造工艺越来越 精确,但是匹配问题的研究从来就没有停止过, 相反地, 匹配问题显得日益突出和重要. 匹配分为横向匹配, 纵向匹配和中心匹配.实现匹配 有三个要点需要考虑:

school of phye

basics of ic layout design

18

匹配方法 之二:交叉法 interdigitating device 之二:

1

2

3

AABBAABB pattern

ABBAABBA pattern

school of phye

basics of ic layout design

大角度离子注入( 离子注入工艺) 大角度离子注入(100nm离子注入工艺) 离子注入工艺 随着器件特征尺寸的不断缩小,工艺制造进入0.100.13m技术代,此时短沟道效应的现象最为突出即: 当FET源极和漏极之间的距离变小时MOSFET的阈电 压下降. 100nm器件工艺必须用到大角度离子注入工艺,即 Halo的注入工艺.主要是防止漏源相通,降低延伸区 的结深以及缩短沟道长度,使载流子分布更陡,提高 芯片的性能.

19

匹配方法 之二:交叉法 interdigitating device 之二:

Axis of Symmetries:

school of phye

basics of ic layout design

20

匹配方法 之二:交叉法 interdigitating device 之二:

Interdigitation Patterns:

school of phye

basics of ic layout design

9

简单匹配 - asymmetry due to fabrication

an MOS transistor is not a symmetrical device. to avoid channeling of implanted ions the wafer is tilted by about 7 degrees.

之十一:采用尺寸较大的器件. 采用尺寸较大的器件.

go large.

之十二:总是与电路设计者交流. 总是与电路设计者交流.

always communicate with your circuit designer.

school of phye

basics of ic layout design

6

匹配规则

school of phye

basics of ic layout design

3

匹配规则

之四:采用指状交叉方式. 采用指状交叉方式.

interdigitate.

之五:用虚设器件包围起来. 用虚设器件包围起来.

surround yourself with dummies.

之六:四方交叉成对器件. 四方交叉成对器件.

analog transistors often have a large W/L ratio. Interdigitization can be used in a multiple transistor circuit layout to distribute process gradients across the circuit. This improves matching. two matched transistors with one node in common: ★ split them in an equal part of fingers (for example 4) ★ interdigitate the 8 elements: AABBAABB or ABBAABBA

通常在电路中有些大堆部件都必须与一个给定的器件匹配,这个 器件称为定义部件 定义部件(图5-5,P104). 定义部件

两组电阻指状交叉排列

将其指状交叉匹配 指状交叉部件的布线

school of phye basics of ic layout design 15

匹配方法 之二:交叉法 interdigitating device 之二:

school of phye

basics of ic layout design

16

匹配方法 之二:交叉法 interdigitating device 之二:

school of phye

basics of ic layout design

17

匹配方法 之二:交叉法 interdigitating device 之二:

keep everything in symmetry.

之九:使差分布线一致. 使差分布线一致.

make differential logic identical.

school of phye

basics of ic layout design

5

匹配规则

之 十:使器件宽度一致. 使器件宽度一致.

match device widths.

之十三:掩模设计者不会心灵感应. 掩模设计者不会心灵感应.

mask designer are not phychic.

之十四:注意临近的器件. 注意临近的器件.

watch the neighbors.

school of phye

basics of ic layout design

7

简单匹配 - matching single transistor

Interdigitize large aspect ratio devices to reduce source/drain depletion capacitance Using an even capacitance. number (n) of gate fingers can reduce Cdb, Csb to oneonehalf or (n+2)/2n depending on source/drain designation. Typically it is preferred to reduce drain capacitance more so than source capacitance. Also use dummy poly strips to minimize mismatch induced by etch undercutting during fab. And these widths of dummy gates can be shorter than the actual gates gates.