spi 及其接口设计(可打印修改)

SPI及其接口介绍

一、SPI接口简介SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

SPI有三个寄存器分别为:控制寄存器SPCR,状态寄存器SPSR,数据寄存器SPDR。

外围设备FLASHRAM、网络控制器、LCD显示驱动器、A/D 转换器(如图一所示)和MCU等。

图一、ADC中的SPI二、SPI接口一个典型的SPI模块的核心部件是一个8位的移位寄存器和一个8位的数据寄存器SPIDR。

通过SPI进行数据传送的设备有主SPI和从SPI之分,即SPI传送在一个主SPI和一个从SPI之间进行。

图二给出了两个SPI模块相互连接、进行SPI传送的示意图,图左边是一个主SPI,图右边为一个从SPI。

图二、典型SPI示意图在AN-877应用笔记中,对spi的接口定义与典型spi接口有所不同,AN-877使用一根线SDIO代替了典型SPI的MISO和MOSI,SS接口用CSB代替。

图三和图四分别是双线模式下单器件控制(主从一对一)和双线模式下多器件控制(主从一对多)。

图三:主从一对一控制图四:主从一对多控制但是原理都一样。

主从机之间一般由3个引脚组成:串行时钟引脚(SCLK)、串行数据输入/输出引脚(SDIO)、片选引脚(CSB)。

1、引脚数据输入/输出(SDIO):该引脚用作数据的输入/输出,用作输入还是用作输出具体取决于所发送的指令(读或写)以及时序帧中的相对位置(指令周期或数据周期)。

在读或写的第一个阶段,该引脚用作输入,将信息传递到内部状态机。

如果该命令为读命令,状态机把该引脚(SDIO)变为输出,然后该引脚将数据回传给外部控制器。

如果该命令为写命令,该引脚始终用作输入。

串行时钟(SCLK):SCLK由外部控制器提供,时钟频率最高为25MHZ。

所有数据的输入输出都是与SCLK同步的。

输入数据在SCLK的上升沿有效,输出数据在SCLK的下降沿有效。

SPI及USB双通信接口的设计与实现

传感 器

前需要 。作 为记 录仪 与计算机或外 围设备 的信息交

换通道 , 通信接 口具 有重要 的 意义。但是针 对数 据快 速读取和通信接 口更 加灵活 方 面的研究 , 目前还 不够

模 拟调 理 电路

图 1 示。 所

计 算机 具有 S I 口 P接 的外 围设 备

二 片

测试的一个组成部分 , 它与其他测试组件 、 无线通信控制 组件以及主机之间的通信更加复杂 , 这就对记 录仪提 出

了许多新的要求 , 包括多种频率采样 、 多次触发 、 海量数据

存储 、 陕速读取和通信接口更加灵活等 。 数据 针 对多种 频率采样 、 多次触发 的要求 , 设计 了一个 由复杂 可编程 逻 辑器 件 C L (o p xpor m be P D cm l r a al e gm lg ei ) oi dv e 和单片 机构 成 的控制 电路 。随着 大容 c c

编程 逻辑 器件 ( P D 控 制 了信号 的有效 采集存 储 , 片机 与 U B接 口芯片 配合则 实 现 了与 外 围器 件 的有效 通 信 。实 验证 明 ,S CL ) 而单 S UB

接 口可实 现数据 的快 速传 输 ;P 接 口可更方 便地 与 无线控 制及 多种 智能仪 器实 现对 接 。接 口兼 容将 是记 录仪 未来 的发 展方 向 。 SI 关键 词 :存 储测 试 记 录仪 接 口通 信 单 片机 U B SI S P

cmpe rga o lxpormma l l i dvc C L ; n f ciec mmu iainwt eih rl e ie lme tdb o iaino igec i be o c eie( P D) a def t o g e v nct i p r ea d vcsi i e ne ycmbn t fs l hp o h p s mp o n

单片机与外部设备的SPI接口设计与实现

单片机与外部设备的SPI接口设计与实现1.引言单片机与外部设备的通信是嵌入式系统设计中的重要环节。

SPI(Serial Peripheral Interface)是一种常用的串行通信协议,用于实现单片机与外设之间的数据传输。

本文将探讨单片机与外部设备之间的SPI接口设计与实现。

2.SPI接口简介SPI接口是一种同步的数据总线协议,通常由一个主设备和一个或多个从设备组成。

SPI接口包含四个信号线:时钟线(SCK)、主输出从输入线(MISO)、主输入从输出线(MOSI)和片选线(SS)。

通过时钟线的同步操作,主设备可以与从设备进行双向数据传输。

3.SPI接口的工作原理SPI接口的工作原理如下:首先,主设备通过片选线选择从设备,并将数据发送到MOSI线上;随后,主设备通过时钟线提供时钟信号,从而同步数据的传输;同时,从设备将数据通过MISO线发送给主设备;最后,主设备将片选线置高,表示数据传输结束。

4.SPI接口的硬件设计在实现SPI接口的硬件设计时,需要考虑以下几个方面:4.1 片选线的设计片选线的数量由从设备的数量决定。

如果只有一个从设备,可以直接连接到片选线上。

如果有多个从设备,需要使用多个片选线,并通过逻辑门进行选择。

4.2 时钟线的设计时钟线的频率由主设备的时钟频率决定。

需要根据从设备的要求,选择适当的时钟频率。

时钟频率过高可能导致数据传输出错,过低可能导致传输速度较慢。

4.3 数据线的设计数据线包括主输出从输入线(MISO)和主输入从输出线(MOSI)。

需要根据从设备的要求,确定数据线的数量和宽度。

通常,每个从设备都需要一个MISO线和一个MOSI线。

5.SPI接口的软件实现在单片机中实现SPI接口的软件需要编写相应的驱动程序。

以下是SPI接口软件实现的基本步骤:5.1 硬件初始化首先,需要初始化单片机的IO口,并设置片选线等相应的引脚。

5.2 时钟设置根据从设备的时钟要求,设置单片机相应的时钟频率。

SPI的接口及其应用

SPI的接口及其应用2010-09-01 00:10:29| 分类:ARM及程序设计| 标签:|字号大中小订阅1 SPI接口的特点目前很多单片机都配置有SPI、I2C或UART等串行接口。

在SPI、I2C及UART三种串行接口一般情况下速度最快的是SPI。

I2C接口由于是二线协议速度很难超过1MHz/ Bit,而UART工作在方式0(8位移位寄存器)时时钟速度为系统时钟的十二分之一(Fosc/12),而SPI接口时钟速度一般为系统时钟的四分之一(Fosc/4)。

典型SPI接口结构如图1所示。

串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口,Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

SPI 用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI可以同时发出和接收串行数据。

它只需四条线就可以完成MCU与各种外围器件的通讯,这四条线是:串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。

这些外围器件可以是简单的TTL移位寄存器,复杂的LCD显示驱动器,A/D、D/A转换子系统或其他的MCU。

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚(MISO)接收的数据逐位移到移位寄存器(高位在前)。

发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。

主SPI的时钟信号(SCK)使传输同步。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

图2和图3中还给出了SPI总线工作的四种方式及SPI总线接口的时序。

SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

SPI接口的FLASH+ROM与C8051F340的接口设计

利用交义开戈分配引脚,将引脚P0 0配置为

SCK(SPl01数字推挽.引脚P01配置为 MISO(SPl0)数字开漏,引脚P0 2配置为

一

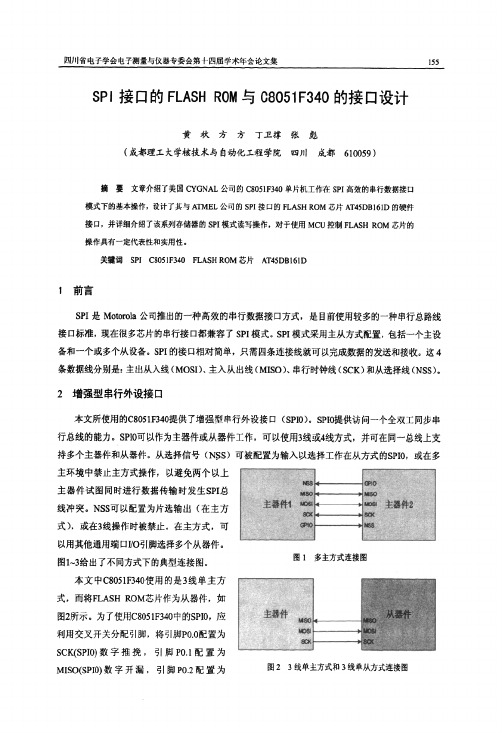

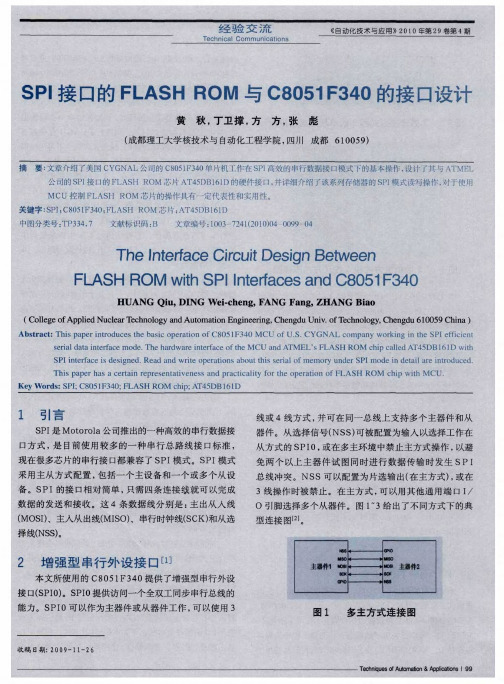

圈】多主方式硅接圈 圈2 3线单土^式和3线单从方式连接圈

SP]接口的FLASH

ROM。j

C805IF340的接u设计

MOSI(SPIO)数字推挽。为r将C8051F340中的SPl0 设置为3线蕾十方式,麻对C8051F340中的SPI特殊 功能寄存器进行配置,具体的配置函数如r:

3

FLASH

ROM芯片

本文所用的FI,ASH ROM芯片蛙美国Atmel公司推出的人容母SPI接u Flash存储器产品 AT45DBl61D。AT45DBl61D是串行接口的闪存芯片,可]忭庄2

5V一2

7V,可J泛应用于数据语

音、图像、程序代码叛据存储中。AT45DBl61D支持Rapids串行接13,适用于高速场台。RapidS

C805 1 F34X Data Sheet.pdf.2006。

AT45DBl61D Data

2 3

Sheet.pdf.2002.

2增强型串行外设接口 本文所使用的C8051F340提供了增强型串行外设接口(SPIO)。SPIO提供访问n.个全般『垌步串

行总线的能力。SPl0可以作为主器件或从器件I作,可以使用3线或4线方式,并可在同一总线上支 持多个主器件和从器件。从选择信号(NSS)可坎配置为输^以选择工作在从方式的SPIO,或在多 土环境中禁lP主方式操作,以避免两个以上

6V或2

7V-3

6V单电源供电,进行编鞲与读取操作。它可以通过CS引

脚米进行使能.并通过二线接口(SI、SO、SCK)进行数据通信。其;r却及功能为 /cs片选信呼:用以选中芯片。当忙s被设置为无效状志时,芯片则不被选中,并且蛀丁闲置

MAX7219及单片机的SPI接口设计

串行显示驱动器PS7219及单片机的SPI接口设计在单片机的应用系统中,为了便于人们观察和监视单片机的运行情况,常常需要用显示器显示运行的中间结果及状态等等。

因此显示器往往是单片机系统必不可少的外部设备之一。

常用的显示器有很多种,其中LED(发光二极管显示器)是应用较多的一种,它特别适用于强光和光线极弱的场合。

要使LED显示,必须提供段选码和位选码。

传统的硬件译码显示接口广泛采用由中央处理器CPU(如:Intel 8031)扩展I/O口(如:8255),然后再使用逻辑门驱动芯片(如7407等)驱动相应的位码和段码。

这种设计,芯片间连线十分复杂,系统工作可靠性不高,已越来越不适应单片机系统集成化、小型化的发展要求。

特别是系统并行扩展I/O,其缺点十分明显(1)连线太多,系统连线复杂,印制板布线不方便;(2)并行总线上挂靠的器件太多,系统工作的稳定性和可靠性低;(3)体积较大,集成度不高。

正是由于上述原因,近年来,各厂家相继开发出了集成度较高、驱动能力较强、驱动位数较多、功能齐全的LED显示驱动器。

本文介绍一种低价位、高性能的多位LED显示驱动器PS7219芯片,以及它与单片机89C51具体的SPI接口设计与应用软件。

1PS7219简介PS7219是一种新型的串行接口的8位数字静态显示芯片。

它是由武汉力源公司新推出的24脚双列直插式芯片,采用流行的同步串行外设接口(SPI),可与任何一种单片机方便接口,并可同时驱动8位LED (或64只独立LED),其引脚图如图1所示。

PS7219内部具有15×8RAM功能控制寄存器,可方便选址,对每位数字可单独控制、刷新、不需重写整个显示器。

显示数字亮度可由数字进行控制,每位具有闪烁使能控制位。

当引脚CON(13脚)置高电平,可禁止所有显示,达到降低功耗的效果,但同时并不影响对控制寄存器的修改。

PS7219还有一个掉电模式、一个允许用户从1位数显示到8位数显示选择的扫描界限寄存器和一个强迫所有LED接通的测试模式。

spi 及其接口设计

SPI 接口的设计第二章介绍了模数转换器的可编程控制架构,其中可编程控制功能的实现需要分成两部分:一部分为SPI 接口电路,以及其根据内部寄存器存储的数据产生的控制信号;另一部分是具体的电路受控模块。

本章将介绍接口与数字逻辑电路的设计,包括应用于本模数转换器的SPI 接口与数字逻辑电路的设计、综合以及仿真验证。

3.1 数据通信接口 3.1.1 串行通信基本的通信方式有两种:并行通信和串行通信。

并行通信是指数据以成组的方式,在多条并行信道上同时进行传输。

串行通信指要传送的数据或信息按一定的格式编码,然后在单根线上,按位的先后顺序进行传送。

接收数据时,每次从单根线上按位接收信息,再把它们拼成一个字符,送给CPU (Central Processing Unit )做进一步的处理。

收发双方必须保持字符同步,以使接收方能从接收的数据比特流中正确区分出与发送方相同的一个一个字符。

串行通信只需要一条传输信道,易于实现,是目前主要采用的一种通信方式,它具有通信线少以及传送距离远等优点。

串行通信时,按数据的传送的方向可以分为单工、半双工和全双工等三种方式。

(1)单工(Simplex ):数据线仅能向一个方向传输数据,两个设备进行通信时,一边只能发送数据,另一边只能接收数据。

(2)半双工(Half Duplex ):数据可在两个设备间向任一个方向传输,但因为只有一根传输线,故同一时间内只能向一个方向传输数据,不能同时收发。

(3)全双工(Full Duplex ):对数据的两个传输方向采用不同的通路,可以同时发送和接收数据,串行通信有两种基本工作方式:异步方式和同步方式。

采用异步方式(Asynchronous )时,数据发送的格式如图3-1所示。

不发送数据时,数据信号线呈现高电平,处于空闲状态。

当有数据要发送时,数据信号线变成低电平,并持续一位的时间,用于表示字符的开始,称为起始位。

起始位之后,在信号线上依次出现待发送的每一位字符数据,最低有效位0D 最先出现。

多媒体处理器中的SPI接口设计

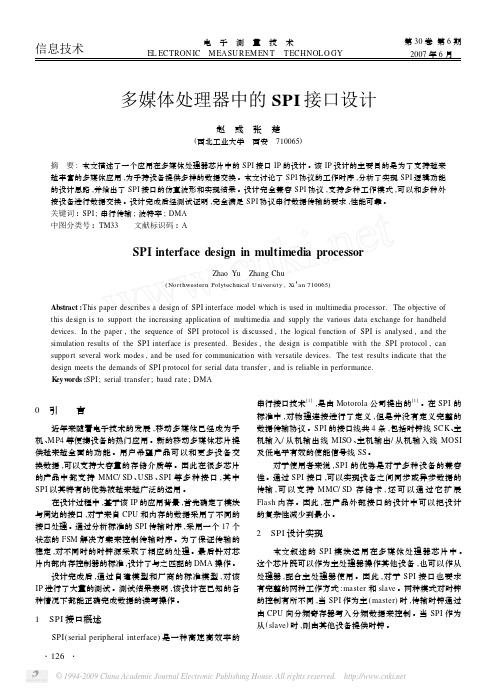

信息技术 电 子 测 量 技 术 EL ECTRON IC M EASU REM EN T TEC HNOLO GY 第30卷第6期2007年6月 多媒体处理器中的SPI接口设计赵 彧 张 楚(西北工业大学 西安 710065)摘 要:本文描述了一个应用在多媒体处理器芯片中的SPI接口IP的设计。

该IP设计的主要目的是为了支持越来越丰富的多媒体应用,为手持设备提供多样的数据交换。

本文讨论了SPI协议的工作时序,分析了实现SPI逻辑功能的设计思路,并给出了SPI接口的仿真波形和实现结果。

设计完全兼容SPI协议,支持多种工作模式,可以和多种外接设备进行数据交换。

设计完成后经测试证明,完全满足SPI协议串行数据传输的要求,性能可靠。

关键词:SPI;串行传输;波特率;DMA中图分类号:TM33 文献标识码:ASPI interface design in multimedia processorZhao Yu Zhang Chu(Nort hwestern Polytechnical University,Xi’an710065)Abstract:This paper describes a design of SPI interface model which is used in multimedia processor.The objective of this design is to support the increasing application of multimedia and supply the various data exchange for handheld devices.In the paper,the sequence of SPI protocol is discussed,the logical f unction of SPI is analysed,and the simulation results of the SPI interface is presented.Besides,the design is compatible with the SPI protocol,can support several work modes,and be used for communication with versatile devices.The test results indicate that the design meets the demands of SPI protocol for serial data transfer,and is reliable in performance.K eyw ords:SPI;serial transfer;baud rate;DMA0 引 言近年来随着电子技术的发展,移动多媒体已经成为手机、MP4等便携设备的热门应用。

SPI及其接口介绍

一、SPI接口简介SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

SPI有三个寄存器分别为:控制寄存器SPCR,状态寄存器SPSR,数据寄存器SPDR。

外围设备FLASHRAM、网络控制器、LCD显示驱动器、A/D 转换器(如图一所示)和MCU等。

图一、ADC中的SPI二、SPI接口一个典型的SPI模块的核心部件是一个8位的移位寄存器和一个8位的数据寄存器SPIDR。

通过SPI进行数据传送的设备有主SPI和从SPI之分,即SPI传送在一个主SPI和一个从SPI之间进行。

图二给出了两个SPI模块相互连接、进行SPI传送的示意图,图左边是一个主SPI,图右边为一个从SPI。

图二、典型SPI示意图在AN-877应用笔记中,对spi的接口定义与典型spi接口有所不同,AN-877使用一根线SDIO代替了典型SPI的MISO和MOSI,SS接口用CSB代替。

图三和图四分别是双线模式下单器件控制(主从一对一)和双线模式下多器件控制(主从一对多)。

图三:主从一对一控制图四:主从一对多控制但是原理都一样。

主从机之间一般由3个引脚组成:串行时钟引脚(SCLK)、串行数据输入/输出引脚(SDIO)、片选引脚(CSB)。

1、引脚数据输入/输出(SDIO):该引脚用作数据的输入/输出,用作输入还是用作输出具体取决于所发送的指令(读或写)以及时序帧中的相对位置(指令周期或数据周期)。

在读或写的第一个阶段,该引脚用作输入,将信息传递到内部状态机。

如果该命令为读命令,状态机把该引脚(SDIO)变为输出,然后该引脚将数据回传给外部控制器。

如果该命令为写命令,该引脚始终用作输入。

串行时钟(SCLK):SCLK由外部控制器提供,时钟频率最高为25MHZ。

所有数据的输入输出都是与SCLK同步的。

输入数据在SCLK的上升沿有效,输出数据在SCLK的下降沿有效。

SPI接口的FLASHROM与C8051F340的接口设计

{

SPI CFG= 0 O x47;

的数 据在 时钟 的上升 沿 写入芯 片 。 s 串行输出 : O 引脚用来 从芯 片以移位方式输 出 O S 数据 。sI 上的数据 在时钟 的下降沿变化 。 /WP写保护 : / P被设置为有效时芯片的扇区 当 w

将被 保护起 来 , 以防止编程 与擦除对数据 的破 坏 。但是

扇 区保 护 使 能 与 扇 区 死 锁 命 令 仍 然 可 以被 芯 片识 别 。 /

/ /主模 式 , SCK 在第一个边沿采样 , 空闲时为低 , 复位值 0 0 x7 S 1C 0(l/ 3 P 0 N: ) ;/ 线单主方式, S 不分配引脚 , 0 N S 使

能SI P

S IC R= x 1/ S K选系统时钟 1 PO K 0 0 ; / C 分频 , 可改变

自 化 术 应 21 年 第4 动 技 与 用》 00 第2 卷 期 9

经 验 交 流

、 I 、 , }C( T 【 _ af ns tI l t 』 I 旧 f m rC

高速场合。Ra iS串行接 口是与 S I pd P 相兼容的 , 速度可 达到 6 MHz 6 。它包含有 l ,0 ,0 个位 , 7 3 15 4 被组织为 4 9 06 个页, 每个页 52 58 或 2 个字节。除了主存储器,T 5 B 6D 1 A 4D ll 还包括两个 S M 数据缓冲 区, RA 每个缓冲区 5 2 5 8 1 / 2 个

本文所用的 F AS L H ROM 芯片是美国 At l me 公司

引脚上 的低电平 会使芯 片一直处于复位状态 。当 / — RE

S ET上转为高 电平后 , 才能进行正常 的操作 。

一种3线制半双工SPI接口设计

一种3线制半双工SPI接口设计

串行外围设备接口SPI(serial peripheralinterface)技术是Motorola 公司推出的一种微处理器、微控制器及其外设间的一种全/半双工同步串行数据接口标准,具有衔接线少、传输效率高等特点,因其硬件功能很强,与SPI有关的软件就相当容易,使CPU有更多的时光处理其他事务。

SPI接口普通采纳4条衔接线:串行时钟线(SCK)、主机输出/从机输入数据线(MOSI)、主机输入/从机输出数据线(MISO)和低电平使能的从机挑选线(SS),有的还带有中断信号线(INT),半双工或单向模式则不需要主机输出/从机输入数据线(MOSI)。

为了在削减引脚的基础上完成主从机的双向通讯,本文采纳半双工机制实现了一种3线制双向SPI 总线模块,即通过使能信号实现数据传输的方向控制,因此将主机输出/从机输入(MOSI)线和主机输入/从机输出线(MISO)线合并为一条双向信号线。

该模块是某芯片中的接口模块,其作用是实现基带芯片对射频芯片的控制以及数据交换,而且为了便于和射频集成,该模块终于以硬IP形式实现。

1 SPI总线协议

射频芯片的SPI接口具有两个主要特征:Slave工作模式和半双工方式通讯。

SPI接口信号描述如表1。

接口时序要求如下:

1)输出时序

当SEN为高电平常,SPI接口处于输出状态。

每次数据传输开头于SCK 信号的升高沿。

数据传输过程中,数据由SCK信号控制,并遵循下列规章:数据传输时,低位在前,高位在后;每个输出数据位在SCK下降沿采样;当本帧数据输出达到24 bit时,结束数据输出;当本帧数

第1页共4页。

基于智能采集模块的SPI总线接口的设计

,

Key wor s LP d: C2t 9 ;SP B s e a mmu iain 1 I u ;S r lCo i nc t ;Daa Ac ust n o t q iio i

S ao H e hu i h s a

Abs r c : T a e sa ls e h ein o P usi tra e bae n ta t he p p re tb ih ste d sg f S 1b nefc sd o AD7 1 a d e e d d rc so PC 9 t e e _ 7 4 n mb d e po e sr L 21 1 h s r

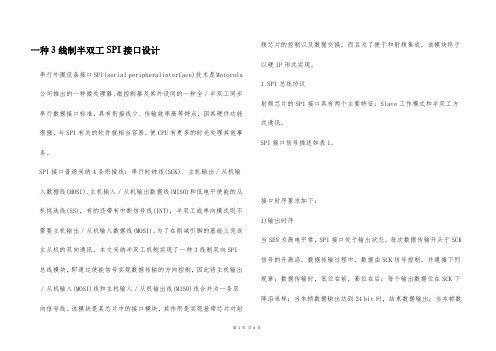

M OS CP { I( I A=1 ) M I O ( PH A=1 S C )

) 兰 旦 !× i < X 旦 墨

帮 丽 瓦Ⅺ 莳 姆

图 3 S I 据 传 输格 式 P数

L C 19 同 A 7 1 的 通 信 中 , P 2 1 P21 D 74 L C 1 9始 终 作 为 主

L .- — -. . .一 —. - -- . . — ■- — - - - - — ———— - - — - -・ - — - - — -- - 一 — - — — - -— — - —- — — - - -- - — - -- ・ - — — - - - —— - — -- u — — - - -- — - -- - + 一

.

i cmmu iain p icpe o P u s d s rb d h o fg r t n o ad r ic i i A D o v rin c is l a o n c t rn il fS I b s i ec ie ,te c n aai f h r wae crut n I o i o C n eso hp

基于SPI的USB控制器接口设计

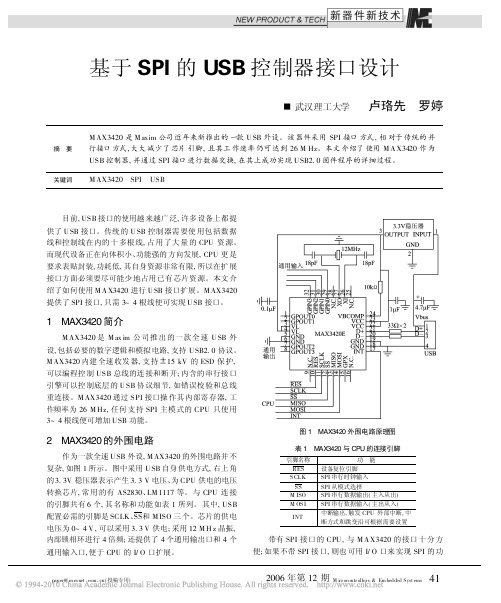

图 3 全双工方式下读/ 写时序图

实 现了 这 两 个 函 数, 本文以 PIC18F2520 和 M AX3420 为例, 在 全双 工方 式

3. 2 半双工方式

半双工方式下 M ISO 为高阻态, M OSI 为双向。由 于 只有一根线, 因 此 半双 工 方式 下 U SB 状态 位 不再 有 效。 半双工方式下的读/ 写操作: ! SS 为高, M AX3420 未选中, M OS I 可以为任意值。

关键词

M AX3420

SPI

US B

目前, US B 接口的使用越 来越广 泛, 许多 设备上都 提 供了 U SB 接口。传统 的 U SB 控制 器需 要使 用包 括数 据 线和控制线在 内的 十 多根 线, 占 用 了大 量 的 CPU 资 源。 而现代设备正在向体积小、 功能强的 方向发展, CPU 更 是 要求表贴封装, 功耗低, 其自身资源非常有限, 所以在扩 展 接口方面必须要尽可能少 地占用 已有 芯片资 源。本文 介 绍了如何使用 M A X3420 进行 U SB 接口扩展。M AX3420 提供了 SPI 接口, 只需 3~ 4 根线便可实现 U SB 接口。

基于 SPI 的 USB 控制器接口设计

武汉理工大学

卢珞先

罗婷

M AX3420 是 M axim 公司近年来新推出的一款 U SB 外设。该 器件采 用 SPI 接口 方式, 相 对于 传统的 并

摘 要

行接口方式, 大大减少 了芯片 引脚, 且其工 作速率 仍可 达到 26 M Hz。本文 介绍了 使用 M A X3420 作 为 US B 控制器, 并通过 SPI 接口进行数据交换, 在其上成功实现 U SB2. 0 固件程序的详细过程。

(完整word版)基于FPGA的SPI接口设计-徐慧军

基于ISE的SPI接口的仿真设计一、SPI介绍SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK (时钟),CS(片选)。

(1)MOSI –主设备数据输出,从设备数据输入(2)MISO –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

数据输出通过SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。

完成一位数据传输,输入也使用同样原理。

这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。

要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。

同样,在一个基于SPI的设备中,至少有一个主控设备。

SPI主机接口设计

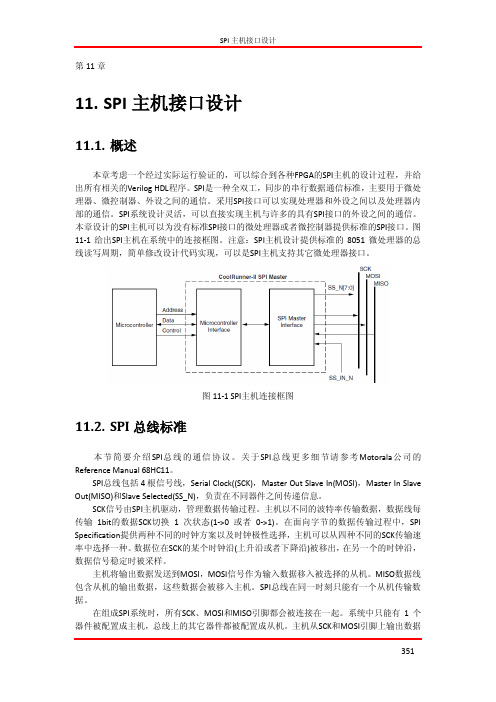

第11章11.SPI主机接口设计11.1.概述本章考虑一个经过实际运行验证的,可以综合到各种FPGA的SPI主机的设计过程,并给出所有相关的Verilog HDL程序。

SPI是一种全双工,同步的串行数据通信标准,主要用于微处理器、微控制器、外设之间的通信。

采用SPI接口可以实现处理器和外设之间以及处理器内部的通信。

SPI系统设计灵活,可以直接实现主机与许多的具有SPI接口的外设之间的通信。

本章设计的SPI主机可以为没有标准SPI接口的微处理器或者微控制器提供标准的SPI接口。

图11-1给出SPI主机在系统中的连接框图。

注意:SPI主机设计提供标准的8051微处理器的总线读写周期,简单修改设计代码实现,可以是SPI主机支持其它微处理器接口。

图11-1 SPI主机连接框图11.2.SPI总线标准本节简要介绍SPI总线的通信协议。

关于SPI总线更多细节请参考Motorala公司的Reference Manual 68HC11。

SPI总线包括4根信号线,Serial Clock((SCK),Master Out Slave In(MOSI),Master In Slave Out(MISO)和Slave Selected(SS_N),负责在不同器件之间传递信息。

SCK信号由SPI主机驱动,管理数据传输过程。

主机以不同的波特率传输数据,数据线每传输1bit的数据SCK切换1次状态(1->0或者0->1)。

在面向字节的数据传输过程中,SPI Specification提供两种不同的时钟方案以及时钟极性选择,主机可以从四种不同的SCK传输速率中选择一种。

数据位在SCK的某个时钟沿(上升沿或者下降沿)被移出,在另一个的时钟沿,数据信号稳定时被采样。

主机将输出数据发送到MOSI,MOSI信号作为输入数据移入被选择的从机。

MISO数据线包含从机的输出数据,这些数据会被移入主机。

SPI总线在同一时刻只能有一个从机传输数据。

实验四单片机原理及应用实验报告——SPI按键显示接口设计

if(ms==0)

ZLG7289_Flash(0xe0); //当计时完成后数码管闪烁

}

}

/*

定义函数jian(),处理定时计时

*/

void jian()

{

if(ms==0)

{

TR0=0;

}

else

{

ms--;

}

min=ms/6000;

s=ms%6000/100;

}

/*

当输入按键为5时,表示输入定时初值的秒部分

*/

else if(j==5)

{

if(s>=59)

{

s=0;

}

else

{

s++;

}

/*

调用jiafa()函数,将输入的按键值计算加入总的10ms的值

*/

jiafa();

ZLG7289_Download(1,3,0,s/10);

ZLG7289_Download(1,4,0,s%10);

*/

if(j==3)

{

q=!q;

while(!ZLG7289_pinINT);//等待按键释放

}

/*

当按下按键0而且T0未开启,表示计数开始,开启T0

*/

if(j==0&&TR0==0)

{

TR0=1;

while(!ZLG7289_pinINT);//等待按键释放

}

/*

当按下按键1,表示暂停计时,定时器T0停止计数

{

min=0;

}

else

{

min++;

}

/*

SPI接口设计与实现

SPI接口设计与实现SPI(SerialPeripheralInterface)总线是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

SPI总线应用广泛,已经成为很多器件的标准配置,可以直接和各个厂家生产的多种标准外围器件直接接口。

其它常用的串行接口还有I2C、UART这两种接口,这三种接口互有优缺点。

与I2C接口相比,SPI接口速度更快、协议更简单、并且是全双工的,但连线也相对多一些。

与UART接口相比,SPI更灵活,因为其使用主设备的时钟进行同步,所以两个比特之间的时间间隔可以是任意的。

在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。

1SPI总线工作原理SPI总线一般以主/从模式工作,通常有一个主设备和一个或多个从设备,数据传输由主机控制,典型SPI结构框图如图1所示。

SPI总线包含四条信号线,分别是sclk、miso、mosi和cs,其中,sclk为数据传输时钟,由主机产生;miso是从机输出,主机输入数据线;mosi是主机输出,从机输入数据线;cs是从设备片选信号,由主机控制,当连接多个从设备时,通过该信号选择不同的从设备。

SPI总线是按字节发送数据的,主机和从机内部都包含一个8位串行移位寄存器,在时钟信号控制下,寄存器内的数据由高到低输出至各自的数据线,8个时钟后,两个寄存器内的数据就被交换了。

如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机的传输。

当主机发送一个连续的数据流时,可以进行多字节传输,在这种传输方式下,从机的片选端必须在整个传输过程中保持低电平。

根据串行同步时钟极性和相位不同,SPI有四种工作方式。

时钟极性(CPOL)为0时,同步时钟的空闲状态为低电平,为1时,同步时钟的空闲状态为高电平。

时钟相位(CPHA)为0时,在同步时钟的第一个跳变沿采样数据,为1时,在同步时钟的第二个跳变沿采样数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二章介绍了模数转换器的可编程控制架构,其中可编程控制功能的实现需 要分成两部分:一部分为 SPI 接口电路,以及其根据内部寄存器存储的数据产生 的控制信号;另一部分是具体的电路受控模块。本章将介绍接口与数字逻辑电路 的设计,包括应用于本模数转换器的 SPI 接口与数字逻辑电路的设计、综合以及 仿真验证。

一个典型的 SPI 模块的核心部件是一个 8 位的移位寄存器和一个 8 位的数据 寄存器 SPIDR。通过 SPI 进行数据传送的设备有主 SPI 和从 SPI 之分,即 SPI 传 送在一个主 SPI 和一个从 SPI 之间进行。图 3-3 给出了两个 SPI 模块相互连接、 进行 SPI 传送的示意图,图左边是一个主 SPI,图右边为一个从 SPI。

把源代码转换为网表的过程叫做综合。网表是使用 Verilog 语言对门级电路

的结构性描述,它是最底层文件。网表是原理图的语言描述,对应着门级电路原

理图。网表中所有的器件都包含有必须的工业参数,如温度特性、电压特性、固

有门延时、输入阻抗、上升时间、下降时间、驱动能力、面积等[31][32]。由于这

些工业参数的存在,使得门级仿真(Gate Level Simulation)十分接近于真实芯

SPI 接口的端口引脚包括:CSB、SCLK、SDIO。 (1)CSB 片选引脚 CSB 是一种低电平有效控制,用来选通读写周期。CSB 可以在多种模式下工 作,如果控制器具有芯片选择输出或其他多器件选择方法,则该引脚可以与 CSB 线相连。当该线为低电平时,器件被选择,SCLK 和 SDIO 线路上的信息便会得 到处理。当该引脚为高电平时,器件会忽略 SCLK 和 SDIO 线路上的所有信息。 这样,多个器件便可以与 SPI 端口相连。在只连接一个器件的情况下,可以将 CSB 线路与低电平相连,使器件始终处于使能状态,但是此时如果端口发生错误, 将无法使器件复位,因为复位信号要在 CSB 的上升沿才起作用。 (2)SCLK 串行时钟 SCLK 引脚为串行移位时钟输入引脚,用来使串行接口的操作同步。输入数 据在该时钟上升沿有效,输出数据在下降沿有效。因为本文中 SPI 接口仅仅用来 为配置寄存器传送数据,所以对数据传输的速率要求不高。为降低该引脚对时钟 线路上噪声的敏感度,它采用施密特触发器实现。 (3)SDIO 串行数据输入/输出 SDIO 引脚用作输入或输出,取决于所发送的指令(读或写)以及时序帧中 的相对位置(指令周期或者数据周期)。在写或读操作的第一阶段,该引脚用作 输入,将信息传递到内部状态机。如果该命令被确定为写命令,则在指令周期内, SDIO 引脚始终用作串行输入,将数据传送给内部移位寄存器。如果该命令被确 定为读命令,状态机将把 SDIO 引脚变为输出,然后该引脚将数据回传给控制器。 在本文设计的 SPI 接口中,该引脚目前只实现向寄存器中写入数据的功能。

表 3-1 典型 SPI 接口引脚

引脚名 MISO(master in slave out) MOSI(master out slave in)

SCLK(serial clock)

描述 钟线。由 SPI 主模块产生,在主从 交换数据时使用,确保数据交换的同步性。

I

来发送的话,就意味着发送过程中将会浪费 30%的传输时间。为了提高串行数据 传输的速率,可以采用同步传送方式。

一帧 第n个字符

D0 D1

起始位

数据位(5-8)

DX

D0

(1-2位)

校验位 停止位 空闲位 起始位

图 3-1 异步串行数据发送格式

同步方式(Synchronous)中串行同步字符的格式如图 3-2 所示。没有数据发 送时,传输线处于空闲状态。为了表示数据传输的开始,发送方先发送一个或两 个特殊字符,称该字符为同步字符。当发送方和接收方达到同步后,就可以连续 地发送数据,不需要起始位和停止位了,可以显著的提高数据的传输速率。采用 同步方式传送的发送过程中,收发双方须由同一个时钟来协调,用来确定串行传 输每一位的位置。在接收数据时,接收方可利用同步字符将内部时钟与发送方保 持同步,然后将同步字符后面的数据逐位移入,并转换成并行格式,直至收到结 束符为止。

核[27](CoolRunner Serial Peripheral Interface Master IP Core),是通过有限状态

机来控制 SPI 主机与从机以及微控制器之间的通信。Motorola 公司的 SPI 核[28]

是一个主从共用的 IP 软核,具有很高的可重用性和通用性。

3.2 SPI 接口的设计与综合

片的物理测试。经过门级仿真后再经过自动布局布线(Auto Place and Route),

从而生成版图(Layout),经过物理验证和后仿真,就可以制版流片,并交付封

装测试。整个流程如图 3-4 所示。

系统要求

综合

单元库IP

可编程逻辑器件

综合

系统级设计

系统实现

系统划分 和

功能设计

系统仿真

行为级/寄存器传 输级(RTL)设计

3.2.2.2 SPI 接口的数据基本传送规则 (1)格式 SDIO 数据传输的第一阶段是指令阶段,指令由 16 位组成,之后是数据,数

V

据由一个或多个 8 位构成,长度由前面的指令字长位确定。CSB 的下降沿与 SCLK 的上升沿一起决定帧何时开始。如果器件的 CSB 与低电平相连,则帧开始 于 SCLK 的第一个上升沿,如图 3-6。

3.1 数据通信接口 3.1.1 串行通信

基本的通信方式有两种:并行通信和串行通信。并行通信是指数据以成组的 方式,在多条并行信道上同时进行传输。

串行通信指要传送的数据或信息按一定的格式编码,然后在单根线上,按位 的先后顺序进行传送。接收数据时,每次从单根线上按位接收信息,再把它们拼 成一个字符,送给 CPU(Central Processing Unit)做进一步的处理。收发双方必 须保持字符同步,以使接收方能从接收的数据比特流中正确区分出与发送方相同 的一个一个字符。串行通信只需要一条传输信道,易于实现,是目前主要采用的 一种通信方式,它具有通信线少以及传送距离远等优点。

一起进行系统仿真(System Simulation)来验证系统设计的正确性。RTL 级设计

按照系统要求编写程序,一般使用 Verilog HDL 或 VHDL 语言进行编程,使之

符合系统设计规定的外特性。RTL 级设计的结果须经行为仿真(Behavior

simulation),保证源代码(Source Code)的逻辑功能正确。

首先,对所要设计的从 SPI 做整体规划,建立架构,并对系统进行层次划分。 根据实际需要,将主 SPI 与从 SPI 之间的连接架构简单的归结为图 3-5 所示。

IV

主SPI

CSB SCLK SDIO

CSB SCLK SDIO

从SPI

图 3-5 主从 SPI 之间连接架构

主 SPI 与从 SPI 之间通过 CSB、SCLK、SDIO 三个引脚进行相连,它们分 别是片选引脚、串行时钟引脚、串行数据输入\输出引脚。此架构比典型的 SPI 接 口引脚少了一个串行数据输出引脚,为了使芯片引脚数量最少,所以将这一引脚 省略。 3.2.2 SPI 接口外特性 3.2.2.1 SPI 接口的端口引脚

同步字符1 同步字符2

数据字符

图 3-2 同步串行数据发送格式

3.1.2 SPI 接口简介 SPI(Serial Peripheral Interface)是由 Motorola 公司提出的一种工业标准,后

来交给 Opencores 组织进行维护。SPI 模块是在 MCU 与 MCU 之间,或 MCU 与 外围设备之间实现近距离、全双工、同步串行传送的接口。与其它串行接口相比, 具有电路结构简单、速度快、通信可靠等优点。通过 SPI 接口,MCU 可以很方 便的与外围芯片直接相连,用以传送控制/状态信息和输入/输出数据。

传送完成标志置 1,完成一次传送。仅从传送路径上看,无所谓发送方和接收方。

在一次传送开始之前发送方应将发送数据写入自己的 SPIDR,该数据自动装载入

移位寄存器。在一次传送完成后,接收方从 SPIDR 中读取接收数据[26]。

目前已有的 SPI 接口 IP 软核,XILINX 公司的 CoolRunner 系列 SPI 主机 IP

III

3.2.1 设计方法、目标及流程

本文 SPI 接口采用自顶向下设计方法。自顶向下设计[29][30]是一种逐级分解、

变换,将系统要求转变为电路或者版图的过程。从系统级(System

Level

Design)开始考虑系统的行为、功能、性能以及允许的芯片面积和成本要求,进

行系统划分和功能设计。用行为语言描述每个方框的外特性,并将全部方框连在

II

SPIDR

SPIDR

移位寄存器

波特率 发生器

MISO

MOSI

SCLK

__

SS

VDD

MISO

MOSI

SCLK

__

SS

移位寄存器

主SPI

从SPI

图 3-3 典型 SPI 模块

典型的 SPI 接口有四个引脚:MISO(主入从出)、MOSI(主出从入)、 SCLK(串行时钟)和 SS(从选择)。具体功能如表 3-1。

SS(slave select)

从机选择线。由主机发送至从机,当输入 时表示该从机被选中,与主机进行通信, 否则未选中,从机不与主机进行通信。

传送时双方的 MISO(主入从出)、MOSI(主出从入)、SCLK(串行时钟)

同名引脚相连。SS 引脚的定义有几种选择,因而有不同的连法。可以看到,主

SPI 和从 SPI 的移位寄存器通过 MISO 和 MOSI 引脚连接为一个 16 位的移位寄

串行通信时,按数据的传送的方向可以分为单工、半双工和全双工等三种方 式。