PCI总线标准协议(中文版)

pcie物理层协议译文

PCie物理层协议译文

PCle的物理层协议是实现PCIe设备之间物理连接的部分,它负责传输数据比特流,并处理与物理连接相关的各种问题。

以下是PCIe物理层协议的译文:

PCle的物理层协议包括物理层传输(PHY) 和物理层配置(PCS)。

1.物理层传输(PHY) :负责在连接的两端之间传输数据。

它包括-一个发送器和一个接收器,以及与这些发送器和接收器相关联的配置和控制逻辑。

发送器将数据从协议层传输到物理媒体上,而接收器从物理媒体接收数据并将其传输到协议层。

2.物理层配置(PCS) :负责管理和配置物理层的行为。

它包括-些客存器和配置寄存器,这些寄存器和配置寄存器可以用于设置物理层的各种参数和特性。

此外,PCle的物理层协议还包括一些其他的组件和功能,如时钟管理和电源管理。

这些组件和功能对于确保PCle设备之间的可靠和高效的连接至关重要。

以上是PCle物理层协议的译文,希望对您有所帮助。

pcie处理层协议中文详解

pcie(PCI-Express)处理层协议中文详解处理层协议(transaction Layer specification)◆TLP概况。

◆寻址定位和路由导向。

◆i/o,memory,configuration,message request、completion详解。

◆请求和响应处理机制。

◆virtual channel(vc)Mechanism虚拟通道机制。

◆data integrity数据完整性。

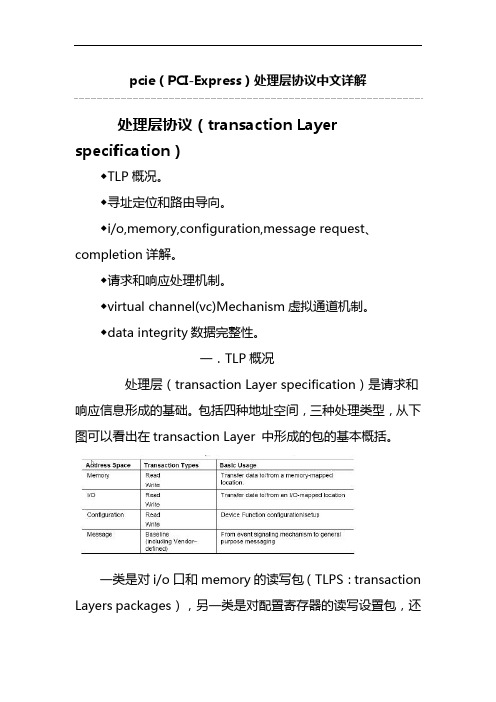

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

一类是对i/o口和memory的读写包(TLPS:transaction Layers packages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory 的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-non posted ,即请求需要返回completion的响应包;还有一种就是;poste,即不需要completion 返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp开销块(Tlp Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。

PCIe协议相关资料要点

PCIe协议相关资料要点PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,用于连接计算机系统的外部设备。

它在现代计算机中广泛应用于图形卡、存储卡和扩展卡等设备的连接。

下面是PCIe协议的相关资料要点。

一、PCIe协议概述PCIe协议是一种高速串行通信协议,用于在计算机系统中传输数据。

它取代了传统的PCI总线,提供更高的带宽和更可靠的性能。

PCIe协议具有以下特点:1. 高速性能:PCIe协议支持多个通道和多个数据传输通路,并且每个通道都可以达到多Gbps的传输速度。

2. 点对点连接:PCIe协议采用点对点连接方式,每个设备都直接连接到主机,并且不会与其他设备共享带宽。

3. 热插拔支持:PCIe协议支持热插拔功能,可以在计算机运行时插入或拔出设备,而无需重新启动系统。

4. 多功率状态支持:PCIe协议支持多功率状态,可以有效地管理设备的能耗。

二、PCIe协议架构PCIe协议的架构包括物理层、数据链路层和传输层。

每个层级都有不同的功能和责任。

1. 物理层(Physical Layer):物理层负责在发送和接收设备之间传输数据。

它定义了数据传输的电气特性、传输速度和功耗等参数。

2. 数据链路层(Data Link Layer):数据链路层负责在发送和接收设备之间建立可靠的数据传输连接。

它通过发送和接收数据包来确保数据的完整性和可靠性。

3. 传输层(Transport Layer):传输层负责数据的路由和传输。

它根据设备的地址和标识符来确定数据的发送和接收。

三、PCIe协议数据传输PCIe协议的数据传输分为读取和写入两种方式。

1. 读取(Read):读取是指从PCIe设备读取数据到主机内存。

读取传输由主机启动,并且主机提供要读取的目标地址。

读取过程中,设备将数据传输到主机内存中的指定地址。

2. 写入(Write):写入是指将数据从主机内存写入到PCIe设备。

pcie协议

pcie协议第一篇:PCIe协议概述PCIe是Peripheral Component Interconnect Express 的缩写,是一种计算机总线标准,用于连接计算机内部各种组件和外部设备。

PCIe可以用于连接图形卡、网卡、声卡、存储设备、专用加速器等各种设备,是现代计算机系统中最常用的总线标准之一。

PCIe协议是为了解决传统PCI总线面临的瓶颈问题而提出的。

传统的PCI总线由于采用并行数据传输技术,在传输数据时存在严重的时序问题和信号完整性问题,随着计算机系统的发展,越来越难以满足高速数据传输的需求。

为了解决这些问题,PCI-SIG(Peripheral Component Interconnect Special Interest Group)组织推出了PCIe协议,这种协议采用串行数据传输技术,在数据传输速度、可扩展性、信号完整性等方面都有较大的优势。

PCIe协议定义了物理层、数据链路层、传输层和应用层等四个层次,每个层次都有相应的协议规范。

其中,物理层规范定义了PCIe总线的物理连线方式、电气特性和传输速率等信息;数据链路层规范定义了数据的帧格式、编码方式和错误检测等信息;传输层规范定义了总线控制、数据流控制和仲裁协议等信息;应用层规范定义了各种设备和驱动程序在PCIe 总线上的交互方式。

PCIe协议的优势在于可以实现高速、可靠的数据传输,同时还具有可扩展性和灵活性等优点。

随着计算机应用场景的不断拓展和计算能力的不断提升,PCIe协议在现代计算机系统中发挥着越来越重要的作用。

第二篇:PCIe协议的物理层PCIe协议的物理层是指PCIe总线物理层协议规范,在PCIe总线系统中,物理层主要是用来定义总线的物理连线方式、电气特性和传输速率等信息。

PCIe协议中规定了四种不同的物理层规范,分别是PCIe 1.0、PCIe 2.0、PCIe 3.0和PCIe 4.0。

PCIe 1.0是最初的版本,采用8b/10b编码方式,传输速率最高可达250MB/s。

pcie,协议,中文

竭诚为您提供优质文档/双击可除pcie,协议,中文篇一:pcie学习资料whitepaper了解pciexpress的基本工作原理synopsys产品市场营销经理scottknowlton20xx年9月从并行转向串行pciexpress(或称pcie),是一项高性能、高带宽,此标准由互连外围设备专业组(pci-sig)制订,用于替代pci、pciextended(pci-x)等基于总线的通讯体系架构以及图形加速端口(agp)。

转向pcie主要是为了实现显著增强系统吞吐量、扩容性和灵活性的目标,同时还要降低制造成本,而这些都是基于总线的传统互连标准所达不到的。

pciexpress标准在设计时着眼于未来,并且能够继续演进,从而为系统提供更大的吞吐量。

第一代pcie规定的吞吐量是每秒2.5千兆比特(gbps),第二代规定的吞吐量是5.0gbps,而最近公布pcie3.0标准已经支持8.0gbps的吞吐量。

在pcie标准继续充分利用最新技术来提供不断加大的吞吐量的同时,采用分层协议也便于pci向pcie的演进,并保持了与现有pci应用的驱动程序软件兼容性。

虽然最初的目标是计算机扩展卡以及图形卡,但pcie目前也广泛适用于涵盖更广的应用门类,包括网络组建、通信、存储、工业电子设备和消费类电子产品。

本白皮书的目的在于帮助读者进一步了解pciexpress以及成功pcie成功应用。

pciexpress基本工作原理拓扑结构本节介绍了pcie协议的基本工作原理以及当今系统中实现和支持pcie协议所需要的各个组成部分。

本节的目标在于提供pcie的相关工作知识,并未涉及到pcie协议的具体复杂性。

pcie的优势就在于降低了复杂度所带来的成本。

pcie属于一种基于数据包的串行连接协议,它的复杂度估计在pci并行总线的10倍以上。

之所以有这样的复杂度,部分是由于对以千兆级的速度进行并行至串行的数据转换的需要,部分是由于向基于数据包实现方案的转移。

(完整版)PCIe协议相关资料

1.PCIe简介PCI-Express是最新的总线和接口标准,它原来的名称为“3GIO”,是由英特尔提出的,很明显英特尔的意思是它代表着下一代I/O接口标准。

交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。

这个新标准将全面取代现行的PCI和AGP,最终实现总线标准的统一。

它的主要优势就是数据传输速率高,目前最高可达到10GB/s以上,而且还有相当大的发展潜力。

PCI Express也有多种规格,从PCI Express 1X到PCI Express 16X,能满足现在和将来一定时间内出现的低速设备和高速设备的需求。

能支持PCI Express的主要是英特尔的i915和i925系列芯片组。

PCI Express(以下简称PCI-E)采用了目前业内流行的点对点串行连接,比起PCI以及更早期的计算机总线的共享并行架构,每个设备都有自己的专用连接,不需要向整个总线请求带宽,而且可以把数据传输率提高到一个很高的频率,达到PCI所不能提供的高带宽。

相对于传统PCI总线在单一时间周期内只能实现单向传输,PCI-E的双单工连接能提供更高的传输速率和质量,它们之间的差异跟半双工和全双工类似。

PCI-E的接口根据总线位宽不同而有所差异,包括X1、X4、X8以及X16,而X2模式将用于内部接口而非插槽模式。

PCI-E规格从1条通道连接到32条通道连接,有非常强的伸缩性,以满足不同系统设备对数据传输带宽不同的需求。

此外,较短的PCI-E卡可以插入较长的PCI-E插槽中使用,PCI-E接口还能够支持热拔插,这也是个不小的飞跃。

PCI-E X1的250MB/秒传输速度已经可以满足主流声效芯片、网卡芯片和存储设备对数据传输带宽的需求,但是远远无法满足图形芯片对数据传输带宽的需求。

因此,用于取代AGP接口的PCI-E 接口位宽为X16,能够提供5GB/s的带宽,即便有编码上的损耗但仍能够提供约为4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

PCI 中文资料

1.1外围的目的DM646x PCI模块允许通信的设备兼容的PCI本地总线规范通过一个32位的地址/数据总线速度高达33 MHz至66 MHz (2.3版本)(为DM6467T器件)。

1.2 产品特点➢PCI本地总线规范(修订版2.3)兼容;➢单功能PCI接口➢32比特地址数据总线宽度➢操作高达33兆赫和高达66 MHz的(为DM6467T设备只)➢优化的爆破行为支持系统的高速缓存行的大小为16 ,32 ,64和128字节➢PCI是只能访问ARMPCI作为一个PCI从设备的配置周期和内存周期。

它也可以作为一个PCI主设备的配置周期,IO周期,和内存访问到其他设备。

作为一个从设备,PCI包括以下功能:➢响应为32位代理中DEVSEL时序(单个等待状态的访问)➢直接支持的内存读取,内存读取多个,内存读线,存储器写,配置读和配置写交易➢别名存储器写和无效的内存写入命令➢支持可变长度的突发传输到高速缓存线存储器读线交易➢支持无限长度的突发传输内存读取多个和存储器写交易➢支持单数据阶段的传输断开存储器读,配置阅读配置写交易➢支持都直接或超时被迫延迟交易的存储器读,存储器读线,和内存读取多个交易➢支持的内存张贴写交易➢支持最多到6基地址寄存器(PCIBAR0 - PCIBAR5的)➢支持可编程的高速缓存行的大小为4 ,8 ,16 ,32 ,64 ,或128字节➢端口设置配置空间寄存器为特定的值后复位作为主设备,PCI包括以下功能:➢作为32位代理的交易开始➢配置读,写,读,写IO ,IO配置内存读取,内存支持读线,内存读取多个,存储器写,存储器写和无效PCI总线命令➢支持的突发传输阶段有256个数据存储器读线,内存读取多个,和内存写入交易➢内存,支持单数据阶段的传输读取交易➢自动选择存储器读,存储器读线,和内存读取多个基于请求的事务的长度和高速缓存行的大小➢PCI_IRDY信号一个时钟周期后PCI_FRAME信号被释放。

pci总线标准协议

pci总线标准协议PCI总线标准协议。

PCI(Peripheral Component Interconnect)总线是一种用于连接外部设备和主板的总线标准,它是一种高速、并行的总线结构,可以支持多种设备的连接。

PCI总线标准协议是为了规范PCI总线的通信协议而制定的,它规定了PCI设备之间的通信方式、数据传输规范和电气特性等,对于PCI设备的互操作性和兼容性起到了重要的作用。

首先,PCI总线标准协议规定了PCI设备之间的通信方式。

PCI设备之间的通信是通过地址、数据和控制信号进行的,协议规定了这些信号的传输方式和时序要求,确保了设备之间的正常通信。

同时,协议还规定了总线仲裁、数据传输和中断请求等机制,保证了多个设备之间的协调工作。

其次,PCI总线标准协议规定了数据传输的规范。

在PCI总线上,数据传输是通过读写操作进行的,协议规定了数据传输的时序、速率和错误检测等要求,保证了数据的可靠传输。

此外,协议还规定了总线的带宽分配和数据缓冲机制,以提高数据传输的效率和可靠性。

另外,PCI总线标准协议还规定了PCI设备的电气特性。

由于PCI总线是一种并行总线,对于信号的电平和时序要求非常严格,协议规定了总线上信号的电气特性,包括电压、电流和信号波形等,以确保设备能够正常工作并且不会对其他设备造成干扰。

总的来说,PCI总线标准协议是对PCI总线通信协议的规范,它规定了PCI设备之间的通信方式、数据传输规范和电气特性等,保证了设备之间的互操作性和兼容性。

在实际应用中,遵循PCI总线标准协议可以有效地提高系统的稳定性和可靠性,同时也为设备的设计和开发提供了统一的标准,促进了整个行业的发展。

总的来说,PCI总线标准协议是一项非常重要的技术规范,它为PCI设备的设计、开发和应用提供了统一的标准,保证了设备之间的互操作性和兼容性。

在实际应用中,遵循PCI总线标准协议可以有效地提高系统的稳定性和可靠性,同时也为设备的设计和开发提供了统一的标准,促进了整个行业的发展。

pcie协议完整版中文版

pcie协议完整版中文版PCIE协议完整版中文版协议双方:甲方:(公司名称/个人名称及注册地址)地址:联系人:联系方式:乙方:(公司名称/个人名称及注册地址)地址:联系人:联系方式:一、约定事项1.1 协议生效时间:本协议自双方签字盖章或电子签约生效之日起执行,有效期为_______年。

1.2 协议目的:本协议旨在明确双方在PCI Express架构标准(以下简称“PCIE”)应用上的权利、义务、履行方式及违约责任,保障双方的权益。

1.3 协议范围:本协议适用于双方在PCIE应用中的合作,包括但不限于硬件设备开发、软件开发、技术支持、销售与推广等方面。

1.4 其他约定:(若有其他约定需在此列明)二、各方身份2.1 甲方身份:(列明甲方的主要业务、经营范围等)2.2 乙方身份:(列明乙方的主要业务、经营范围等)三、权利与义务3.1 甲方的权利与义务(1)提供相关技术、产品等的支持和服务。

(2)需要乙方提供的技术、信息等必须由乙方及时提供。

(3)严格遵守PCIE的应用规范和中国法律相关法规。

(4)尊重乙方的商业秘密及其他权益,不泄露给第三方。

(5)经乙方书面同意,可将签约信息用于宣传及推广。

(6)应保证所提供的技术、产品等不存在侵犯乙方专利权利等情形,如存在侵权,甲方应承担全部赔偿责任。

3.2 乙方的权利与义务(1)提供所需的技术、信息等支持和服务。

(2)严格遵守PCIE的应用规范和中国法律相关法规。

(3)尊重甲方的商业秘密及其他权益,不泄露给第三方。

(4)保证所提供的技术、信息等不存在侵犯甲方专利权利等情形,如存在侵权,乙方应承担全部赔偿责任。

(5)甲方在推广乙方产品时,乙方应及时提供所需的技术支持和相关文件。

(6)双方应互相配合进行技术交流与推广。

四、履行方式4.1 双方应在签约之日起开始共同开发PCIE相关技术、产品等,并根据项目计划书或协议约定的时间节点按时提交开发进展、质量保证及验收等相关信息。

pci e总线标准

pci e总线标准PCI Express(Peripheral Component Interconnect Express)是一种计算机总线标准,用于连接外部设备到计算机。

它是一种高速串行通信接口,用于连接内部硬件设备,如图形卡、网络适配器和存储设备。

PCIe总线标准已经成为现代计算机系统中最常见的总线标准之一,其高速、可靠和灵活的特性使其成为了许多计算机硬件设备的首选接口。

PCIe总线标准最初由英特尔公司于2004年引入,并在随后的几年内不断发展和演进。

它取代了旧的PCI和AGP总线标准,为计算机系统提供了更高的带宽和更低的延迟。

PCIe总线标准采用了不同的版本,包括PCIe 1.0、PCIe 2.0、PCIe 3.0和PCIe 4.0,每个版本都提供了不同的数据传输速率和带宽。

PCIe总线标准的设计采用了一种点对点连接的架构,这意味着每个设备都直接连接到主板上的PCIe插槽,而不需要共享带宽或资源。

这种架构使得PCIe总线标准能够支持高性能的设备,并且在多设备同时工作时不会出现性能瓶颈。

PCIe总线标准还支持热插拔功能,这意味着用户可以在计算机运行的情况下插入或拔出PCIe设备,而不会影响系统的稳定性或性能。

这为用户提供了更大的灵活性和便利性,使他们能够随时升级或更换硬件设备。

除了传统的PCIe插槽,PCIe总线标准还引入了M.2接口,这是一种更小、更紧凑的接口,用于连接固态硬盘和无线网卡等设备。

M.2接口可以通过PCIe总线标准提供更高的带宽和更快的数据传输速率,使得这些设备能够更好地发挥性能。

总的来说,PCIe总线标准是一种高速、可靠和灵活的计算机总线标准,它已经成为了现代计算机系统中最常见的接口之一。

它的设计和特性使得它能够支持高性能的设备,并且为用户提供了更大的灵活性和便利性。

随着技术的不断发展,PCIe 总线标准将继续演进和改进,为计算机硬件设备的发展提供更好的支持和基础。

PCI 配置空间(中文)

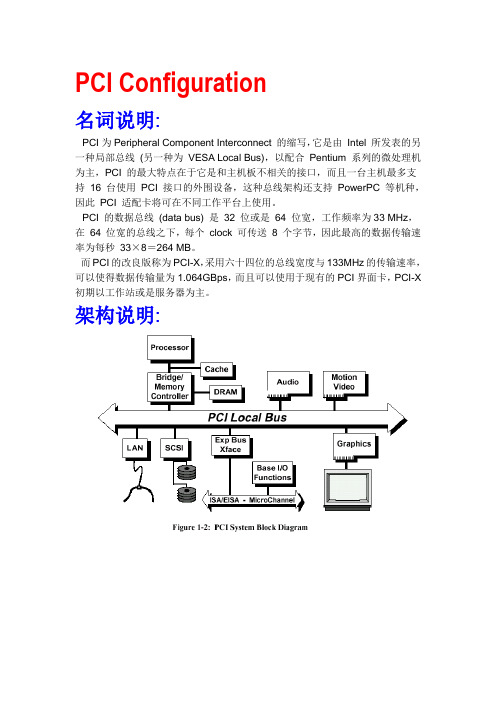

PCI Configuration名词说明:PCI为Peripheral Component Interconnect 的缩写,它是由Intel 所发表的另一种局部总线(另一种为VESA Local Bus),以配合Pentium 系列的微处理机为主,PCI 的最大特点在于它是和主机板不相关的接口,而且一台主机最多支持16 台使用PCI 接口的外围设备,这种总线架构还支持PowerPC 等机种,因此PCI 适配卡将可在不同工作平台上使用。

PCI 的数据总线(data bus) 是32 位或是64 位宽,工作频率为33 MHz,在64 位宽的总线之下,每个clock 可传送8 个字节,因此最高的数据传输速率为每秒33×8=264 MB。

而PCI的改良版称为PCI-X,采用六十四位的总线宽度与133MHz的传输速率,可以使得数据传输量为1.064GBps,而且可以使用于现有的PCI界面卡,PCI-X 初期以工作站或是服务器为主。

架构说明:System(系统讯号):CLK:CLK讯号为一个输入讯号,其提供所有交易,包括总线仲裁等的时序,PCI装置的所有输入都是在CLK讯号的上升边缘被取样的.PCI总线上的所有动作都与PCI CLK讯号同步,其讯号频率的范围在0Mhz~33Mhz.RST(Reset Signal)当重置讯号被驱动成低态时,它会强迫所有PCI组态缓存器,master及target 状态机器与输出驱动器回到初始化状态.Device IdentificationVendor ID(Offset 00h~01h)记录PCI厂商识别码,如Intel ID是8086, VIA ID是1106,Ali ID是10B8. Device ID(Offset 02h~03h)记录PCI装置识别码.以BIOS观点来看,通常为了避掉某些装置与系统的兼容性常藉由判断Vendor ID 与Device ID 做不同的处理.Device ControlCommand Register(Offset 04h~05h)指令缓存器它是一个16位缓存器,提供基本装置响应或进行PCI存取能力的控制.位功能0IO空间(IO Space).当此位被设定为1时,显示该装置需求IO地址.1内存空间(Memory Space).当此位被设定为1时,显示该装置需求内存地址.2Bus Master.当被设定为1时,此装置能当作bus master来用,组态软件用此位来决定装置是否具有bus master能力.3特殊周期(Special Cycle). 当被设定为1时,装置可以监视PCI特殊周期. 4Memory Write and Invalidate Enable. 当被设定为1时,装置可以产生Memory Write-and-Invalidate指令, 当设定为0时,装置使用MemoryWrite指令来取代,软件不应该致能此位,直到装置的快取线大小组态缓存器以系统快取线大小来初始化,组态软件可以用它及位2,Bus Master一起来侦测master是否能够使用Memory Write-and-Invalidate指令,假设它可以的话,则快取线大小将会被写入到master的快取线大小组态缓存器.5VGA调色盘监管(VGA Pallete Snoop). 当此位被设定为1时,此位指示其与VGA兼容的装置去监管对VGA Color Pallete(调色盘)缓存器的IO写入,在非VGA图形装置,重置会将此位设定为1,开启调色盘监管功能. 6同位错误响应(Parity Error Response). 当此位被设定为1时,装置可以报告同位错误(以驱动PERR#到低组态的方式),当清除为0时,装置不会在发生同位错误事件时,驱动PERR#到低组态,不过,它仍必须设定在其状态缓存器里的侦测到同位错误状态位.7逐步驱动控制(Stepping Control).控制装置是否可以进行地址/数据逐步驱动,从不使用逐步驱动的装置必须将此位以硬件接线设定为0,一定要使用逐步驱动的装置必须将此位以硬件接线设定为1,能够使用这两种方式的装置必须将此位实做成一个可读/可写的位,并且在重置后初始化为1.8SERR# Enable.当设定为1时,装置可以驱动SERR#线,设定为0会关闭装置的SERR#输出驱动器,此位与位6(同位错误报告)必须被设定,以便报告地址同位错误9Fast Back-to-Back Enable.假如Bus Master可以在第一次和第二次交易中,与不同的Target进行Fast Back-to-Back交易的话,此位可用来启动或关闭这功能,假如所有在Bus Master所在之PCI总线上的Target是可以进行Fast Back-to-Back交易的话,组态软件可以设定此位来致能此Master进行Fast Back-to-Back交易的能力,无需担心在第一次和第二次交易里是否寻址相同的Target..15:10 保留Status Register状态缓存器(Offset 06h~07h)位R/W 功能3:0 R 保留4 R 能力串行(Capabilities List).它是一个硬件接线,只读位,假如设定为1的话,则表示新能力串行指针缓存器必须在装置组态空间的Offset 34h里实作,在这种情况,组态程序执行装置应该去读取指针缓存器,以决定装置是否支持额外的能力(AGP,VPD等等),并且使用它们各自的组态缓存器,去组态它们.5 R 66Mhz能力(66Mhz Capable).1=装置能够在66Mhz速度下执行.0=只能在33Mhz速度下执行.6 R 保留7 R Fast Back-to-Back能力(Fast Back-to-Back Capable).此只读位元表示Target装置是否支持不同Target的Fast Back-to-Back交易,1=装置支持0=装置不支持.8 R/W Master数据同位错误(Master Data Parity Error).此位只在Bus Master里实作,并且只有在下列条件时才会被设定:●报告的Bus Master是交易的initiator.●(在读取过程中)它自己设定PERR#,或(在写入过程中)侦测到它被Target驱动到低态.●在Master的指令缓存器里的同位错误响应位被设定为1. 10:9 R 装置选择时序(Device Select (DEVSEL#)Timing).它定义了Target装置最慢的DEVSEL#时序.00b=Fast(快速的)01b=Medium(中速的)10b=Slow(慢速的)11b=Reserved(保留)11 R/W 发出Target Abort讯号(Signaled Target Abort).每当Target装置以Target Abort终止交易时,Target就会设定此位,不能发出Target Abort讯号的装置不需要实作此位.12 R/W 接收到Target Abort讯号(Received Target Abort).每当BusMaster的交易是以目前寻址的Target发出的Target Abort终止的时候,它就会设定此位.13 R/W 接收到Master Abort讯号(Received Target Abort).每当BusMaster的交易是因Master Abort而终止(特殊周期除外)的时候,它就会设定此位.14 R/W 发出系统错误讯号(Signaled System Error).每当装置在SERR#在线产生一个错误讯息(System Error)时,它应该设定此位. 15 R/W 侦测到同位错误(Detected Parity Error).每当装置侦测到一个同位错误时, 它应该设定此位(实时同位错误报告功能指令缓存器里的同位错误响应位关闭).Revision ID(Offset 08h)版本识别码缓存器记录PCI装置版本序号,由装置制造商指派,假如制造商提供版本特定的驱动程序,这可确保OS加载正确的驱动程序.Class Code类别码(Offset 09h~0Bh)它是一个24位只读的缓存器,它被分成三个字段:基本类别(Base Class)子类别(Sub Class)及程序界面(Programming Interface),●较高的字节定义功能的基本类别.●中间的字节定义在基本类别里的子类别.●较低的字节定义程序界面.当OS尝试找出一个可以配合类别驱动程序(Class Driver)一起工作的装置时,此暂存器是很有用的,如OS找到一个具有类别码03h,以及子类别码为01h的装置(XGA),则它必须提供与其兼容的显示配接卡驱动程序和该装置一起工作.Base Class 00h在类别码定义之前建立的装置.00h 00h 所有非VGA装置.00h 01h 与VGA兼容的装置.大量储存媒体控制器.子类别程序界面描述00h 00h SCSI控制器01h xxh IDE控制器02h 00h 软式磁盘驱动器控制器03h 00h IPI 控制器04h 00h RAID 控制器05h 00h 其它大量储存媒体控制器Base Class 02h网络控制器.子类别程序界面描述00h 00h Ethernet 控制器01h 00h Token Ring 控制器02h 00h FDDI 控制器03h 00h ATM 控制器04h 00h ISDN 控制器80h 00h 其它网络控制器显示控制器.子类别程序界面描述00h 00h 与VGA兼容的控制器,响应内存地址000A0000h到000BFFFh(Video Frame Buffer,视讯画面缓冲区),以及IO地址03B0h到03BBh,及03C0h到03DFh,还有这些地址的所有别名(alias).01h 与8514兼容的控制器,响应IO地址02E8h以及它的别名,02EAh和02EFH.01h 00h XGA控制器.02h 00h 3D控制器.80h 00h 其它显示控制器.Base Class 04h多媒体控制器.子类别程序界面描述00h 00h 视讯装置.01h 00h 音效装置.02h 00h 计算机电话装置.80h 00h 其它多媒体装置.Base Class 05h内存控制器.子类别程序界面描述00h 00h RAM内存控制器.01h 00h Flash(快闪)内存控制器.80h 00h 其它内存控制器.Base Class 06h桥接器装置子类别程序界面描述00h 00h Host / PCI 桥接器01h 00h PCI / ISA 桥接器02h 00h PCI / EISA 桥接器03h 00h PCI / Micro Channel 桥接器04h 00h PCI / PCI 桥接器01h 相减解碼PCI-to-PCI 桥接器,支持除正常PCI-to-PCI功能之外的相减译码.05h 00h PCI / PCMCIA 桥接器06h 00h PCI / NuBus 桥接器07h 00h PCI / CardBus 桥接器08h xxh RACEway 桥接器,RACEway是一个ANSI标准(ANSI / VITA 5-1994)的交换架构(Switching Fabric)界面位7:1是保留,位0值为0表示桥接器是在通透模式(Transparent Mode),值为1表示它是再端点模式(End-Point Mode).80h 00h 其它桥接器型态.Base Class 07h简单的通讯控制器子类别程序界面描述00h 00h 通用的XT兼容序列控制器.01h 与16450兼容的序列控制器.02h 与16550兼容的序列控制器.03h 与16650兼容的序列控制器.04h 与16750兼容的序列控制器.05h 与16850兼容的序列控制器.06h 与16950兼容的序列控制器.01h 00h 平行阜.01h 双向平行阜.02h 遵循ECP 1.X规格的平行阜.03h IEEE 1284控制器.Feh IEEE 1284 Target装置(非控制器).02h 00h 多阜序列控制器.03h 00h 通用调制解调器.01h 与Hayes兼容的调制解调器,与16450兼容的界面,BAR0映像或IO映像(如BAR型态所指示).02h 与Hayes兼容的调制解调器,与16550兼容的界面,BAR0映像或IO映像(如BAR型态所指示).03h 与Hayes兼容的调制解调器,与16650兼容的界面,BAR0映像或IO映像(如BAR型态所指示).04h 与Hayes兼容的调制解调器,与16750兼容的界面,BAR0映像或IO映像(如BAR型态所指示).80h 00h 其它通讯装置.Base Class 08h基本的系统周边装置.子类别程序界面描述00h 00h 通用8259可程序中断控制器(ProgrammableInterrupt Controller, PIC).01h ISA PIC.02h EISA PIC.10h IO PIC.20h IO(x)APIC中断控制器.01h 00h 通用8237DMA控制器.01h ISA DMA控制器.02h EISA DMA控制器.02h 00h 通用8254定时器.01h ISA系统定时器.02h EISA系统定时器.03h 00h 通用RTC控制器.01h ISA RTC控制器.04h 00h 通用热插拔(PCI Hot-Plug).80h ooh 其它系统外围装置.Base Class 09h输入装置.子类别程序界面描述00h 00h 键盘控制器.01h 00h Diditizer(pen).02h 00h 鼠标控制器.03h 00h 扫瞄器控制器.04h 00h 通用游戏连接阜控制器.10h 游戏连接阜控制器.具有程序界面=10h的游戏连接阜控制器表示任何在这请求/指定IO地址空间之功能里的基地址缓存器,在该IO空间的缓存器符合标准的”传统” 游戏连接阜,在IO区域里位移为00h的字节其行为与传统游戏连接阜界面相同,当读取此字节时,会传回游戏杆/手把(Joystick/Gamepad)的信息,在写入此字节时会启动RC定时器,位移为01h的字节是位移为00h字节的别名,所有在IO区域里的其它字节是未指定的,且可以给制造商以自己特有的方式来使用. 80h 00h 其它输入控制器.Base Class 0Ah船屋系统.子类别程序界面描述00h 00h 通用的船乌系统.80h 00h 其它型态的船乌系统.Base Class 0Bh处理器Base Class 0Ch序列总线控制器.子类别程序界面描述00h 00h Firewire(IEEE 1394).10h 使用1394 OpenHCI规格的IEEE 1394.01h 00h ACCESS.bus02h 00h SSA(Serial Storage Architecture,序列储存架构).03h 00h 使用Universal Host Controller规格的USB(Universal Serial Bus,通用序列阜)控制器.10h 使用Open Host Controller规格的USB(Universal Serial Bus,通用序列阜)控制器.80h 无特定程序界面的USB控制器.FEh USB装置(非主控器(Host Controller))04h 00h Fiber(光纤)Channel.05h 00h SMBus(System Management bus,系统管理汇流排).Base Class 0Dh无线控制器子类别程序界面描述00h 00h 与iRDA兼容的控制器.01h 00h 消费型IR控制器.02h 00h RF控制器.80h 00h 其它型态无线控制器.Base Class 0Eh智能型IO控制器子类别程序界面描述00h xxh 遵循I20架构规格的智能型IO控制器.00h 在相对地址(Offsset)40h的讯息FIFO. Base Class 0Fh卫星通讯控制器子类别程序界面描述01h 00h TV(电视).02h 00h Audio(音效).03h 00h Voice(语音).04h 00h Data(资料).Base Class 10h加密/解密(Encryption/Decryption)子类别程序界面描述00h 00h 网络与运算加密/解密.10h 00h 娱乐加密/解密.80h 00h 其它加密/解密.Base Class 11h数据撷取与讯号处理控制器子类别程序界面描述00h 00h DPIO模块80h 00h 其它数据撷取与讯号处理控制器.Cache Line Size Register快取线大小缓存器(Offset 0Ch)此读/写组态缓存器指定了以dword为单位的系统快取线大小(例如:在P6的系统里此缓存器的值为08h,表示其快取线大小为8个dword,或32个字节),实作了Memory Write-and-Invalidate指令的Bus Master必须实作此缓存器,因为它必须知道快取线大小,以便确保它从快取线边界起始交易,并遵守它将整条线写入内存的约定,所以当这缓存器被设定为0(表示组态软件尚未把快取线大小告诉它)时, Bus Master不可以使用Memory Write-and-Invalidate指令,在这种情况,Master 只能够使用Memory Write(内存写入)指令来更新内存.装置可以限制它所支持的快取线大小数目,假如组态软件写入一个未支持的数值, 则装置会将此数值当作0来动作.Latency Timer等待时间(Offset 0Dh)等待时间以PCI频率周期为单位,定义了在bus master起始新交易时,它可保留总线有权的最小时间量,最理想的是,每一个bus master都应该将此缓存器实作为可读/写的缓存器,藉此给予组态软件在bus master群组间分配可用的总线时间上有最大的弹性,组态软件以读取功能的Min_Gnt(Minimum Grant最小授权)缓存器,决定bus master想要的时间片段.Header Type表头型态缓存器(Offset 0Eh)每一个PCI功能拥有保留给实作其组态缓存器用的64个组态dword区块,前16个dword的格式(Offset 00h~3Fh)与使用是由PCI规格预先定义的,这区域被称为装置的组态表头区域(或表头空间(Header Space)),规格目前定义了三种表头格式,称为Header Type Zero,One与Two:Header Type One是为PCI-to-PCI桥接器定义的(01h).●Header Type Two是为PCI-to-CardBus桥接器定义的(02h).●Header Type Zero是给所有除了PCI-to-PCI与CardBus桥接器以外的装置使用的(00h).Header Type位7是用来表示此装置含有除了桥接器功能以外的其它功能,固位7=1表示为多功能,0=表示为单功能.Built-in Self TestBIST内建自我测试(Offset 0Fh)非必要的,假如装置不支持BIST的话,在读取此缓存器时,它必须要传回为0,装置的BIST是以设定位6为1的方式来请求,在完成BIST后,装置会将位6重置,但必须在二秒钟内完成重置,位0~3为0则表示成功,非零值代表装置特定的错误码.Bass Address基地址缓存器(Offset 10h~27h)在开机时,系统必须自动地组态,以便让所有IO与内存能占用户不相干的地址范围,为了达到此目标,系统必须有能力侦测到装置需要多少个内存与IO地址范围,以及每一个大小.当位0传回1则表示这是一个IO译码器,不是内存译码器,位[31:2]是基地址字段,并且用来IO区块所需的大小以及设定它的起始地址.区块大小的决定与地址范围的指定:●是否实作基地址缓存器?●它是一个内存,还是IO地址译码器?●假如它是内存译码器,它是一个32位还是64位的基地址缓存器?●假如它是内存译码器,与此缓存器相关的内存是可预读的还是不可预读的?●它需要多少内存或地址空间,并且是以什么单位来排列?这所有信息可以很简单的用写入一个全部为1的值到基地址缓存器里,然后读取它来确认,传回值为0表是没有实作基地址缓存器,假设所读取的值不为0,程序执行装置可从基地址栏的最低有效位向上扫瞄传回值,以找出第一个被设定为1的位来决定所需的内存或IO空间的大小.内存范例:假设FFFFFFFFh被写入在组态13h~10h的基地址缓存器里,然后再读取时,所得的值为FFF00000h,由此可知有任何位可以被更改成1表示实作了基地址缓存器,●位0 = 0 表示这是一个内存地址译码器.●位[2:1] = 00b表示它是一个32位内存地址译码器.●位3 = 0 表示它不是可预读的内存.●位20是在基地址字段里所找到的第一个1,此位的二进制权值为1,048,576,表示这是一个1MB大小的内存地址译码器.接下来,程序执行装置写入32位基地址到缓存器里,不过只有位[31:20]是可写入的,译码器接荍位[31:20]并假设所指定的基地址的位[19:0]为0,这表示基地址可以被1MB,既所请求的内存范围大小整除,所指定的起始地址一定会被所请求的内存范围大小整除是PCI译码器的特性.IO范例:假设FFFFFFFFh被写入在组态17h~14h的基地址缓存器里,然后再读取时,所得的值为FFFFFF01h,位0为1,表示这是一个IO地址译码器,从位2(基地址栏的最低有效位向上扫瞄)开始向上扫瞄,找到位8是第一个被成功地改成1的位,此二进权值为256,表示此IO地址译码器大小为256B,或将所得的值作一补码运算后再加1,易可得相同的值.CardBus CIS PointerCardBus与PCI共享的装置实作此非必要的缓存器,此字段指向CardBus卡的借面卡信息结构(CardBus Information Structure,CIS),此缓存器是只读的,并且包含在下列其中一个地方的CIS相对地址(offset):●在功能的装置特定组态空间里(在功能的组态空间的Offset 40h之后)的相对地址(Offset).●与其中一个装置内存基地址缓存器所指示的起始地址间之相对地址(offset).●在装置扩充ROM程序代码影像(Code Image)里的相对地址(offset).CIS的详细说明请参考”CardBus System Architecture”.Subsystem Vendor ID and Subsystem IDSubsystem Vendor ID子系统制造商识别码(Offset 2Ch~2Dh)Subsystem ID子系统识别码(Offset 2Eh~2Fh)PCI功能可以位于界面卡上或内建装置里,使用相同PCI核心逻辑(由third-party(其它厂商)生厂)的两个界面卡或子系统可能会有相同制造商识别码与装置识别码(假如核心逻辑制造商以硬件接线将它们自己的识别码设定在这些缓存器里),假如在这种情况下,在OS辨识要加载到内存的真正装置驱动程序上,可能会有问题.这两个强制性的缓存器被用来确认装置所在的附加卡或子系统,使用这两个缓存器,OS可以分辨在由不同制造商制造,但使用相同third-party核心逻辑的界面卡或子系统之间的差异,这使得随插即用(Plug-and-Play)OS有能力去寻找要加载到内存的正确驱动程序.Expansion ROM Base Address扩充ROM基地址缓存器(Offset 30h~33h)对于含有装置ROM的装置来说是必要的,许多PCI装置都含有一个内含装置的装置驱动程序之装置ROM, 在开机时,系统必须自动地组态,以便让所有IO与内存能占用户不相干的地址范围,为了达到此目标,系统必须有能力侦测到ROM需要多少个内存空间,可以很简单的用写入一个全部为1的值到基地址缓存器里,然后读取它来确认,它必须检查在ROM里的前两个位置是否有扩充ROM的签名,以决定ROM是否真的被安装,假如有安装的话,组态程序必须SHADOW此ROM,并且执行其初始化程序代码.●位0 = 1 致能装置的ROM地址译码器.●位[10:1]保留.●位[31:11]用来指定ROM的起始地址.假设FFFFFFFFh被写入到ROM的基地址缓存器里(位0,既扩充ROM致能位被清除,所以ROM地址译码器不会被致能,直到指定起始内存地址之后),随后再读取此缓存器,所得的值为FFFE0000h,这表示:●位0 = 0 ,表示ROM地址译码器目前被关闭.●位[10:1]保留.●在基地址字段(位[31:11])里,位17为程序执行装置可以设定为1的最低有效位,其二进制权值为128K,表示ROM译码器需要128K的内存地址,然后,程序执行装置写入一个32位的起始地址到此缓存器中,指定128KB的地址边界当作ROM的起始地址.PCI Expansion ROM Header FormatPCI Data Structure FormatROM Header ExtensionsInterrupt Line中断讯号线(Offset 3Ch)PCI装置的中断号码配置与绕线设定处理和此字段密不可分.PCI装置对于中断讯号的定义中,设计了以下四组中断讯号线.INT A# , INT B#, INT C#, INT D#在今的许多PC系统里,内崁在PCI/ISA桥接器内的可程序化路由器都具有四个输入端,用来连接PCI中断线路,目前大多数的PCI装置是单功能装置, 单功能PCI装置只能用INT A#(不得使用INT B#,INT C#,INT D#)来产生中断请求,在多功能PCI装置上,装置设计者可以实作最多四支中断接脚,INT A#,INT B#,INT C#,INT D#,因其是内含二到八个功能的实体套件,ISA中断请求线是正缘触发(Positive edge-triggered),且不可共享,但PCI中断请求线是低态动作的(Active low),准位触发的(Level-sensitive),可共享的(Shareable)请求线,PCI中断只能连接到未被ISA 装置占用的ISA中断请求在线.在系统内存F0000到FFFFF搜寻表格的签名(Signature)($PIR),便可侦测到PCI中断路由表格.格式如下:从表格起点算起的相对字节大小说明0 4 Signature4 2 Version6 2 Table Size8 1 PCI Interrupt R outer’s Bus9 1 PCI Interrupt Router’s DevFunc10 2 PCI Exclusive IRQs12 4 Compatible PCI Interrupt Router16 4 Miniport Data20 11 Reserved31 1 Checksum32 16 First Slot Entry48 16 Second Slot Entry(N+1)*16 16 nth Slot Entryalign 16public ms_irq_route_table_signms_irq_route_table_sign label bytedb "$PIR"ms_irq_route_table_ver dw 0100hms_irq_route_table_size dw 32+(5*16)ms_irq_route_table_bus db 00hms_irq_route_table_dev db VT586_P2I_DEV_FUNCms_irq_route_table_irq dw 0hms_irq_route_table_id dd 05861106h ; VIA 82C586;ms_irq_route_table_id dd 05961106h ; VIA 82C596ms_irq_route_table_mini dd 0hms_irq_route_table_resd db 11 dup(0)ms_irq_route_table_cksm db 0紧接着是16字节的插槽项目格式,依系统主机板所使用的芯片组,内建装置与插槽数而有所不同. 格式如下:从表格起点算起的相对字节大小说明0 1 PCI Bus Number1 1 PCI Device Number2 1 Link Value for INT A#3 2 IRQ Bitmap for INT A#5 1 Link Value for INT B#6 2 IRQ Bitmap for INT B#8 1 Link Value for INT C#9 2 IRQ Bitmap for INT C#11 1 Link Value for INT D#12 2 IRQ Bitmap for INT D#14 1 Slot Number15 1 ReservedInterrupt Pin中断讯号脚(Offset 3Dh)中断讯号线记录器其记录该PCI 装置使用何者INT#讯号,BIOS则依其所提供的信息告知CHIPSET并给予正确中断绕线设定.值为1表示其使用INT A,2则为INT B,3则为INT C,4则为INT D.此记录器是只读并无法写入.MIN_GNT and MAX_LATMIN_GNT(Minimum Grant 最小授权)(Offset 3Eh)此为只读的组态缓存器,其值为0,代表此Bus Master对于指派给予的LT的设定值并没有特定的要求,若非为0则表示master需要多长的时间片段以得到适当的效能,以250ns为单位.Max_LAT:Max_Lat(Offset 3Fh)缓存器的值表示master多久会想要存取总线一次, 此为只读的组态缓存器,对于bus master来说是非必要的.Device StatusPCI 2.2 新增新能力(New Capabilities)组态缓存器offset 06h~07h为装置状态缓存器,其位4=1表示支持新能力,新能力指针缓存器在组态缓存器offset 34h,其细节如下:位0~7为能力识别码位8~15为指向下一个新能力的指标.识别码: 说明00h 保留01h PCI Power Management Interface02h AGP03h VDP(Vital Product Data)04h Slot Identification05h MSI(Message Signaled Interrupt)06h CompactPCI Host Swap7~255d 保留PMC Register:位说明15:11 PME支持(PME_Support)字段,表示功能可以在该状态下,驱动PME#到低态(电源管理事件PM Event)的PM状态,位为0表示在这个PM状态下不支持PME#产生.位对应的PM状态11 D012D113D214D3 hot15D3 cold(功能需要辅助电源来供应PME逻辑电力)10 D2支持位9 D2支持位8:6 辅助电流(Aux_Current)字段.5装置特定的初始化(Device-Specific Initialization,简称DSI)位.4保留3PME频率(PME Clock)位,此位为1表示功能需要有PCI频率存在,才能产生PME#,不需要频率或不产生PME#的功能会以硬件接线将本位元设定为0.2:0 版本字段(Version).位遵循的规格版本210001 1.010 1.1PM控制/状态(PMCSR)缓存器●假如功能实作PME能力的话,则此缓存器含有一个用来反应先前致能之PME是否发生的PME状态(PME Status)位.●假如功能实作PME能力的话, 则此缓存器含有一个PME致能(PME Enable)位,它允许软件去致能或关闭功能驱动PME#讯号到低态的能力.●假如实作了非必要的数据缓存器的话,则此缓存器含有两个字段:●允许软件选择可以透过数据缓存器来读取的信息.●并提供数据缓存器数值必须相乘的比例因子.●软件使用此缓存器的电源状态(Power State)字段,来决定功能目前的PM状态,以及把功能转移到新PM状态.位读/写(R/W) 说明15 读/写,想要将PME状态(PME Status)位,假如功能支持PME1清除为0的话, 的话,此位会反应功能是否遇到PME(即使在把1写入其中此缓存器里的PME_En位将功能在发生PME事件时,驱动PME#到低态的能力关闭),假如设定为1,则功能遇到PME,而软件可以用写入1到其中的方式将它清除.14:13 只读数据比例(Data Scale)字段.12:9 读/写数据选择(Data Select)字段.8 读/写PME致能(PME_En)位.1=致能功能在发生PME事件时,驱动PME#到低态的能力.0=关闭.7:2 只读保留.1:0 读/写电源状态(Power State)字段,软件用此字段来居决定功能目前的PM状态(以读取此字段的方式)或是将它放入到一个新的PM状态(以写入此字段的方式),假如软件选择功能不支持的PM状态,则写入必须正常地完成,但是写入的数据会被丢弃,且状态不变.10 PM状态00b D001b D110b D211b D3hot相关信息与实例当客户要求支持S5 PME Wake up功能但PCI装置不支持时,BIOS 可利用下列程序来做到:STR_SAVE_PCI_DEVICE LABEL BYTEdw MKF_PCI_SLOT1_DEV_FUNC ;(25-11)shl 3dw MKF_PCI_SLOT2_DEV_FUNC ;(26-11)shl 3dw MKF_PCI_SLOT3_DEV_FUNC ;(27-11)shl 3dw MKF_PCI_SLOT4_DEV_FUNC ;(28-11)shl 3dw MKF_PCI_SLOT5_DEV_FUNC ;(29-11)shl 3NO_OF_STR_PCI_TABLE e qu ($ - offsetcgroup:STR_SAVE_PCI_DEVICE)/2mov si,offset cgroup:STR_SAVE_PCI_DEVICEmov cx,NO_OF_STR_PCI_TABLEloop_for_pme_d3:push cxmov dx, word ptr cs:[si]mov ah,00h ; 00hcall read_pcicmp al,0ffhjz next_for_pme_d3mov ah,PCI_REG_STATUS ; 06hcall read_pcitest al, CAPABILITIES_BIT ; 10hjz next_for_pme_d3mov ah,PCI_CAP_PTR ; 34hread_cap_id:call read_pcicmp al, 00jz next_for_pme_d3mov ah,alcall read_pcicmp al, PME_CAP_ID ; 01hjz found_for_pme_idinc ahjmp read_cap_idfound_for_pme_id:add ah,PMECS_REG+1 ; 05hcall read_pciand al,0feh ; Clear & Disable PME call write_pcidec ahcall read_pciand bl,0fch ; set power on statecall write_pciinc ahcall read_pcior al,01h ; Enable PMEcall write_pcinext_for_pme_d3:inc siinc sipop cxloop loop_for_pme_d3mov cx,3333call pm_fixed_delaypopafor_pme_disable:ret;----------------------------------------------------------- -----------;; STACK REQUIRED ;; ;; Input : (AL) Mask of PCI register bits to test. ;; (optional) ;; (AH) Index of PCI register to access. ;; (DL) 7:3 PCI device # ;; 2:0 PCI function # on device ;; (DH) 7:0 PCI bus # of device ;; ;; Output: (AL) Value read from chip set register. ;; (ZF) ZR Corresponding bits in chip set ;; register to mask are all zero. ;; NZ Corresponding bits in chip set ;; register to mask has at least ;; one bit set. ;; ;; Register destroyed : (AL) ;; NOTE : ;; * Do not invoke with "ret_sp". Invoke with "call" only. ;; * Do not change IF status. ;;----------------------------------------------------------------------- ;read_pci PROC NEARpush edxpush eaxpushfxchg ax,dxmovzx eax,ax ; (eax) = device & func #shl eax,8 ; (eax) = dev & func # in; proper position.bts eax,31mov al,dh ; (al) = reg # to access.and al,0fch ; (eax) = proper config enb.shl edx,16mov dx,00cf8h ; (dx) = CONFIG_ADDRESS cliout dx,eaxjcxz short $+2jcxz short $+2shr edx,24 ; (dl) = reg # to access.and dl,003h ; (dl) = byte to access of regor dx,00cfch ; (dx) = CONFIG_DATAin al,dx ; (al) = data read from regjcxz short $+2jcxz short $+2mov dl,alpopfpop eaxtest al,dl ; For returning proper flag info.mov al,dlpop edxretread_pci ENDP●Host/PCI Bridge:通常被称为北桥(North Bridge),它连接主处理器总线与root PCI 总线.●PCI-to-ISA Bridge:通常被称为南桥(South Bridge),它连接root PCI总线与ISA(或EISA) 总线,南桥通常还整合中断控制器(Interrupt Controller),IDE控制器(IDEController),USB Host控制器(USB Controller)与DMA控制器(DMAController).●PCI-to-PCI Bridge:它连接root PCI总线与PCI总线。

pci总线协议书

pci总线协议书甲方(以下简称“甲方”):____________________乙方(以下简称“乙方”):____________________鉴于甲方是一家专业从事计算机硬件研发和生产的公司,乙方是一家专业从事计算机软件研发的公司。

双方本着互惠互利、共同发展的原则,就PCI总线技术合作事宜达成如下协议:第一条定义1.1 “PCI总线”指Peripheral Component Interconnect总线,是一种计算机硬件总线标准,用于计算机硬件之间的数据传输。

1.2 “协议书”指本文档,规定了双方基于PCI总线技术合作的条款和条件。

第二条合作内容2.1 甲方同意向乙方提供PCI总线相关的硬件技术支持和咨询服务。

2.2 乙方同意利用其软件开发能力,开发与PCI总线兼容的软件产品。

第三条技术支持与服务3.1 甲方应根据乙方的需求,提供必要的PCI总线硬件技术支持,包括但不限于硬件设计、接口规范、性能测试等。

3.2 甲方应保证所提供的技术支持和服务符合行业标准和质量要求。

第四条软件开发与兼容性4.1 乙方应保证所开发的软件产品与甲方提供的PCI总线硬件兼容。

4.2 乙方应负责软件产品的开发、测试、维护和升级。

第五条知识产权5.1 双方各自拥有其在合作前已有的知识产权。

5.2 在合作过程中产生的新的知识产权,双方应根据实际贡献协商确定归属。

第六条保密条款6.1 双方应对在合作过程中知悉的对方商业秘密和技术秘密负有保密义务。

6.2 未经对方书面同意,任何一方不得向第三方披露、泄露或允许第三方使用上述秘密。

第七条违约责任7.1 如任何一方违反本协议的任何条款,违约方应承担违约责任,并赔偿守约方因此遭受的所有损失。

第八条协议的变更和终止8.1 本协议的任何变更或补充,必须经双方协商一致,并以书面形式确认。

8.2 如遇不可抗力或其他不可预见因素导致本协议无法继续履行,双方可协商终止本协议。

第九条争议解决9.1 本协议在履行过程中如发生争议,双方应首先通过友好协商解决。

PCI_DSSV3.2 中文版

以下是对12pcidss要求的主要概pci数据安全标准主要概述建立并维护安全的网络和系统不要使用供应商提供的默认系统密码和其他安全参数保护持卡人数据加密持卡人数据在开放式公共网络中的传输维护漏洞管理计划开发并维护安全的系统和应用程序实施强效访问控制措施限制对持卡人数据的物理访问定期监控并测试网络10

网络分段 无线

............................................................................................................................................................................................................ 12 ............................................................................................................................................................................................................ 12

PCI总线标准协议(中文版)

PCI总线标准协议(中⽂版)8.4.2 PCI总线信号定义在⼀个PCI应⽤系统中,如果某设备取得了总线控制权,就称其为"主设备";⽽被主设备选中以进⾏通信的设备称为"从设备"或"⽬标节点''。

对于相应的接⼝信号线,通常分为必备的和可选的两⼤类,为了进⾏数据处理、寻址、接⼝控制、仲裁等系统功能, PCI接⼝要求作为⽬标的设备⾄少需要47条引脚,若作为主设备则需要49条引脚。

下⾯对主设备与⽬标设备综合考虑,并按功能分组将这些信号表⽰在图8.19中。

其中,必要的引脚在左边,任选的引脚在右边。

⼀.信号类型说明图8.19 PCI引脚⽰图为了叙述⽅便,将PCI信号按数传⽅向及驱动特性划分为五种类型,各种类型的规定如下:in:输⼊信号。

out:输出驱动信号。

t/s:表⽰双向三态输⼊/输出驱动信号。

s/t/s:持续三态(Sustained Tri-State),表⽰持续的并且低电平有效的三态信号。

在某⼀时刻只能属于⼀个主设备并被其驱动。

这种信号从有效变为浮空(⾼阻状态)之前必须保证使其具有⾄少⼀个时钟周期的⾼电平状态。

另⼀主设备要想驱动它,⾄少要等到该信号的原有驱动者将其释放(变为三态)⼀个时钟周期之后才能开始。

同时,如果此信号处于持续的⾮驱动状态时,在有新的主设备驱动它之前应采取上拉措施,并且该措施必须由中央资源提供。

o/d:漏极开路(Open Drain)可作线或形势允许多个设备共同使⽤,⼆. PCI总线信号定义PCI总线的信号线共有100根,下⾯按功能分组进⾏说明。

1.系统引线CLK in:时钟输⼊,为所有PCI上的接⼝传送提供时序。

其最⾼频率可达66MHz,最低频率⼀般为0(DC),这⼀频率也称为PCI的⼯作频率。

对于PCI的其他信号,除、、、之外,其余信号都在CLK的上升沿有效(或采样)。

in:复位,⽤来使PCI专⽤的特性寄存器和定时器相关的信号恢复规定的初始状况。

(完整版)PCIe协议相关资料

(完整版)PCIe协议相关资料1.PCIe简介PCI-Express是最新的总线和接⼝标准,它原来的名称为“3GIO”,是由英特尔提出的,很明显英特尔的意思是它代表着下⼀代I/O接⼝标准。

交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。

这个新标准将全⾯取代现⾏的PCI和AGP,最终实现总线标准的统⼀。

它的主要优势就是数据传输速率⾼,⽬前最⾼可达到10GB/s以上,⽽且还有相当⼤的发展潜⼒。

PCI Express也有多种规格,从PCI Express 1X到PCI Express 16X,能满⾜现在和将来⼀定时间内出现的低速设备和⾼速设备的需求。

能⽀持PCI Express的主要是英特尔的i915和i925系列芯⽚组。

PCI Express(以下简称PCI-E)采⽤了⽬前业内流⾏的点对点串⾏连接,⽐起PCI以及更早期的计算机总线的共享并⾏架构,每个设备都有⾃⼰的专⽤连接,不需要向整个总线请求带宽,⽽且可以把数据传输率提⾼到⼀个很⾼的频率,达到PCI所不能提供的⾼带宽。

相对于传统PCI总线在单⼀时间周期内只能实现单向传输,PCI-E的双单⼯连接能提供更⾼的传输速率和质量,它们之间的差异跟半双⼯和全双⼯类似。

PCI-E的接⼝根据总线位宽不同⽽有所差异,包括X1、X4、X8以及X16,⽽X2模式将⽤于内部接⼝⽽⾮插槽模式。

PCI-E规格从1条通道连接到32条通道连接,有⾮常强的伸缩性,以满⾜不同系统设备对数据传输带宽不同的需求。

此外,较短的PCI-E卡可以插⼊较长的PCI-E插槽中使⽤,PCI-E接⼝还能够⽀持热拔插,这也是个不⼩的飞跃。

PCI-E X1的250MB/秒传输速度已经可以满⾜主流声效芯⽚、⽹卡芯⽚和存储设备对数据传输带宽的需求,但是远远⽆法满⾜图形芯⽚对数据传输带宽的需求。

因此,⽤于取代AGP接⼝的PCI-E 接⼝位宽为X16,能够提供5GB/s的带宽,即便有编码上的损耗但仍能够提供约为4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

pcie协议详解中文

pcie协议详解中文PCIe协议详解中文。

PCIe(Peripheral Component Interconnect Express)是一种高速串行接口总线标准,用于连接计算机内部的外部设备。

它是PCI的后继者,提供了更高的带宽和性能,成为了现代计算机系统中最常用的接口之一。

首先,让我们来了解一下PCIe协议的基本特点。

PCIe采用了串行传输技术,相比于PCI的并行传输方式,大大提高了数据传输速度。

它采用了差分信号传输和8b/10b编码技术,能够在较短的时钟周期内传输更多的数据,从而提高了带宽和性能。

PCIe协议支持多种不同的连接方式和速度等级。

常见的连接方式包括x1、x4、x8和x16,分别对应着1条、4条、8条和16条通道,能够满足不同设备对带宽的需求。

而速度等级则包括了不同的代数,如PCIe 1.0、PCIe 2.0、PCIe 3.0和PCIe 4.0等,每一代都在前一代的基础上提高了数据传输速度。

此外,PCIe协议还引入了可扩展性和兼容性的设计理念。

通过支持热插拔和热插拔功能,PCIe设备可以在计算机运行的情况下进行安全连接和断开,而不会对系统造成影响。

同时,PCIe协议还保持了与之前PCI标准的兼容性,使得旧设备可以与新系统兼容,新设备也可以与旧系统兼容,为用户提供了更大的灵活性和选择空间。

在实际应用中,PCIe协议被广泛应用于各种设备之间的连接,如显卡、网卡、存储控制器、扩展卡等。

它不仅能够满足高带宽、低延迟的需求,还能够支持多设备同时连接,为计算机系统的性能提升提供了重要支持。

总的来说,PCIe协议作为一种高速串行接口总线标准,具有高带宽、高性能、可扩展性和兼容性等特点,已经成为了现代计算机系统中不可或缺的一部分。

它的出现和发展,极大地推动了计算机系统的性能提升和外部设备的发展,为用户提供了更加便利和高效的使用体验。

以上就是对PCIe协议的详细解析,希望能够帮助大家更好地理解和应用PCIe 协议。

第8章 PCI总线标准

➢ IRDY# S/T/S:主设备准备好信号(Initiator Ready) ➢ TRDY# S/T/S:从设备准备好信号(Target Ready)

注: IRDY#, TRDY#同时有效,才能从主设备传送数据

从设备. ➢ STOP# S/T/S:从设备发出的要求主设备终止

(zhōngzhǐ)当前的数据传送的信号。 ➢ LOCK # S/T/S:锁定信号 ➢ IDSEL IN:初始化设备选择信号 ➢ DEVSEL# S/T/S:设备选择信号

PCI-Express(中文)

基础篇 (2)一、PCI标准的发展历史 (2)二、PCI Express总线的提出 (3)三、PCI Express技术优势 (5)四、PCI Express总线的前景 (6)系统架构篇 (7)一、总体系统架构 (7)二、PCI Express的体系结构 (10)物理层(Physical Layer) (10)2. 数据链路层(Link Layer) (12)3. 处理层(Transaction Layer) (13)4. 软件层(Software Layer) (15)物理结构篇 (15)一、物理结构外观 (16)二、台式机PCI Express物理接口设计规范 (18)基础篇随着Intel 800MHz FSB芯片组i875P的推出,Intel同时也向世人显示一个全新的总线技术即将推出,那就是由Intel首先提出并开发的3GIO总线。

后来这一技术提交PCI-SIG(PCI 特殊兴趣组织),由PCI-SIG改名为"PCI Express",以标准的形式正式推出,目前的最新版本为v1.0。

本连载就要带大家深入了解这一即将改变整个计算机系统结构、成为下一代总线标准的总线技术。

首先本文要向大家介绍的是一些基础知识。

一、PCI标准的发展历史要了解PCI Express总线技术的提出原因,我们先来简要回顾一下PCI总线的发展历史目前应用的计算机内部总线技术为PCI,即"Peripheral Component Interconnect",中文名为"外围组件互连",它是由Intel于1991年提出的(与本文要介绍的PCI-Express总线技术属同一个公司开发的)。

后来,PCI-SIG小组接替了Intel的PCI规范的发展,在1993年5月发布了PCI 2.0。

那时,PCI的竞争对手是VESA本地总线(VL-bus或VLB),它是由视频电子标准协会提出的32bit总线,在标准的ISA插槽之后提供附加的第三和第四接口,额定频率33MHz,并且能够提供超过ISA。

pcie处理层协议中文详解

pcie(PCI-Express)处理层协议中文详解处理层协议(transaction Layer specification)◆TLP概况。

◆寻址定位和路由导向。

◆i/o,memory,configuration,message request、completion详解。

◆请求和响应处理机制。

◆virtual channel(vc)Mechanism虚拟通道机制。

◆data integrity数据完整性。

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

一类是对i/o口和memory的读写包(TLPS:transaction Layers packages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-non posted ,即请求需要返回completion的响应包;还有一种就是;poste,即不需要completion返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp 开销块(Tlp Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8.4.2 PCI总线信号定义在一个PCI应用系统中,如果某设备取得了总线控制权,就称其为"主设备";而被主设备选中以进行通信的设备称为"从设备"或"目标节点''。

对于相应的接口信号线,通常分为必备的和可选的两大类,为了进行数据处理、寻址、接口控制、仲裁等系统功能, PCI接口要求作为目标的设备至少需要47条引脚,若作为主设备则需要49条引脚。

下面对主设备与目标设备综合考虑,并按功能分组将这些信号表示在图8.19中。

其中,必要的引脚在左边,任选的引脚在右边。

一.信号类型说明图8.19 PCI引脚示图为了叙述方便,将PCI信号按数传方向及驱动特性划分为五种类型,各种类型的规定 如下:in:输入信号。

out:输出驱动信号。

t/s:表示双向三态输入/输出驱动信号。

s/t/s:持续三态(Sustained Tri-State),表示持续的并且低电平有效的三态信号。

在某一时刻只能属于一个主设备并被其驱动。

这种信号从有效变为浮空(高阻状态)之前必须保证使其具有至少一个时钟周期的高电平状态。

另一主设备要想驱动它,至少要等到该信号的原有驱动者将其释放(变为三态)一个时钟周期之后才能开始。

同时,如果此信号处于持续的非驱动状态时,在有新的主设备驱动它之前应采取上拉措施,并且该措施必须由中央资源提供。

o/d:漏极开路(Open Drain)可作线或形势允许多个设备共同使用,二. PCI总线信号定义PCI总线的信号线共有100根,下面按功能分组进行说明。

1.系统引线CLK in:时钟输入,为所有PCI上的接口传送提供时序。

其最高频率可达66MHz,最低频率一般为0(DC),这一频率也称为PCI的工作频率。

对于PCI的其他信号,除、、、之外,其余信号都在CLK的上升沿有效(或采样)。

in:复位,用来使PCI专用的特性寄存器和定时器相关的信号恢复规定的初始状况。

每当复位时, PCI的全部输出信号一般都应驱动到第三态。

2.地址和数据引线AD0~AD31 t/s:地址、数据多路复用的输入/输出信号。

在有效时,是地址周期;在和同时有效时,是数据周期。

一个PCI总线的传输中包含了一个地址信号周期和一个(或多个)数据周期。

PCI总线支持突发方式的读写功能。

地址周期为一个时钟周期,在该周期中AD0~AD31线上含有一个32位的物理地址。

对于I/O操作,它是一个字节地址;若是存储器操作和配置操作,则是双字地址。

在数据周期, AD0~AD7为最低字节, AD24~AD31为最高字节。

当有效时,表示写数据稳定有效,有效表示读数据稳定有效。

~3 t/s:总线命令和字节使能多路复用信号线。

在地址周期内,这四条线上传输的是总线命令;在数据周期内,传输的是字节使能信号,用来表示在整个数据期中, AD0~AD31上哪些字节为有效数据。

3.接口控制信号s/t / s:帧周期信号。

由当前主设备驱动,表示一次访问的开始和持续时间。

无效时,是传输的最后一个数据周期。

s / t / s:主设备准备好信号。

该信号有效表明发起本次传输的设备(主设备)能够完成一个数据期。

它要与配合使用,当这两者同时有效时,才能进行完整的数据传输,否则即为等待周期。

在写周期,该信号有效时,表示有效的数据信号已在AD0~AD31中建立;在读周期,该信号有效时,表示主设备已做好接收数据的准备。

s/t/s:从设备准备好信号。

该信号有效表示从设备已做好完成当前数据传输的准备工作,此时可进行相应的数据传输。

同样,该信号要与配合使用,这两者同时有效数据才能进行完整传输。

在写周期内该信号有效表示从设备已做好了接收数据的准备。

在读周期内,该信号有效表示有效数据已被送入AD0~AD31中,同理, 和的任何一个无效时都为等待周期。

s / t / s:停止数据传送信号,该信号由从设备发出。

当它有效时,表示从设备请 求主设备终止当前的数据传送。

s / t / s:锁定信号。

是由PCI总线上发起数据传输的设备控制的,如果有几个不同的设备在使用总线,但对信号的控制权只属于一个主设备(由信号标定)。

当信号有效时,表示驱动它的设备所进行的操作可能需要多个传输才能完成,如果对某一设备具有可执行的存储器,那么它必须能实现锁定,以便实现主设备对该存储器的完全独占性访问。

对于支持 锁定的目标设备,必须能提供一个互斥访问块,且该块不能小于16 个字节。

连接系统存储器的主桥路也必须使用。

IDSEL in:初始化设备选择信号。

在参数配置读写传输期间,用作片选信号。

s/t/s:设备选择信号,由从设备驱动,该信号有效时,表示驱动它的设备已成为当前访问的从设备。

它有效表明总线上的某一设备已被选中。

4.仲裁信号t/s:总线请求信号。

该信号一旦有效即表示驱动它的设备要求使用总线。

它是一个点到点的信号线,任何主设备都应有自己的信号。

t /s:总线允许信号。

用来向申请占用总线的设备表示其请求已获批准。

这也是一 个点到点的信号线,任何主设备都应有自己的信号。

5.错误报告信号为了能使数据可靠、完整地传输,PCI局部总线标准要求所有挂于其上的设备都应具有错误报告线。

s / t / s:数据奇偶校验错误报告信号,但是该信号不报告特殊周期中的数据奇偶 错。

一个设备只有在响应设备选择信号和完成数据期之后,才能报告一个。

对于每个数据接收设备,如果发现数据有错误,就应在数据收到后的两个时钟周期将 激活。

该信号的持续时间与数据期的多少有关,如果是一个数据期,则最小持续时间为一 个时钟周期;若是一连串的数据期并且每个数据期都有错,那么的持续时间将多于一个时钟周期。

由于该信号是持续的三态信号,所以该信号在释放前必须先驱动为高电平。

另外,对数据奇偶错的报告不能丢失也不能推迟。

o/d:系统错误报告信号。

该信号用于报告地址奇偶错,特殊命令序列中的数据奇偶错,以及其他可能引起灾难性后果的系统错误。

是漏极开路信号,由返遣错误的单元驱动,在一个PCI时钟内有效。

信号的发出和时钟同步,因而满足总线上所有其他信号的建立时间和保持时间的要求。

6.中断信号中断在PCI总线上是可选用的,低电平有效,用漏极开路方式驱动。

同时,此类信号的建立和撤销是与时钟不同步的。

PCI为每一个单功能设备定义一根中断线。

对于多功能设备或连接器,最多可有4条中断线。

对于单功能设备,只能使用,其余3条中断线无意义。

PCI局部总线有四条中断线,定义如下:o/d:中断A,用于请求一次中断。

o/d:中断B,用于请求一次中断并只在多功能设备上有意义。

o/d:中断C,功能同中断B。

o/d:中断D,功能同中断B。

多功能设备上的任何一种功能都能连到任何一条中断线上。

中断寄存器决定该功能用哪一条中断线去请求中断。

如果一个设备只用一条中断线,则这条中断线就称为INTA,如果该设备用了两条中断线,那么它们就称为INTA和INTB,依此类推。

对于多功能设备,可以是所有功能用一条中断线,也可以是每种功能有自己的一条中断线,还可以是上两种情况的综合,一个单功能设备不能用一条以上的中断线去申请中断。

系统供应商在对PCI连接器的各个中断信号和中断控制器进行连接时,其方法是随意的,可以是线或方式、程控电子开关方式,或者是二者的组合,这就是说,设备驱动程序对于中断共享事先无法作出任何假定,即它必须能够给任何逻辑设备提供中断。

7.高速缓存(Cache)支持信号为了使具有可缓存功能的PCI存储器能够和贯穿写(Write-Through)或回写(Write- Back)的Cache相配合工作,可缓存的PCI存储器应该能实现两条高速缓存支持信号作为 输入。

如果可缓存的存储器位于PCI总线上,那么连接回写式Cache和PCI的桥路必须要利用两条引脚,且作为输出,而连接贯穿写式Cache的桥只需要实现一个信号。

上述两个信号的定义如下:in/out:双向试探返回信号(Snoop Backoff)。

当其有效时,说明对某修改行的一次命中,所访问的数据为无效数据。

当无效而SDONE有效时,说明PCI发起方正在访问存储器的有效行并可进行高速缓存的操作。

SDONE in/out:监听完成信号(Snoop Done),表明对处理器Cache对主存的监听状态。

当其无效时,说明监听仍在进行,否则表示监听已经完成。

8. 64位总线扩展信号如果要进行64位扩展,以下信号都要使用。

AD32~AD63 t / s:扩展的32位地址和数据多路复用线,在地址周期(如果使用了双地址周期DAC 命令且有效时)这32条线上含有64位地址的高32位,否则它们是保留的;在数据周期,当和同时有效时,这32条线上含有高32位数据。

~7 t/s:总线命令和字节使能多路复用信号线。

在数据周期,若和同时有效时,该4条线上传输的是表示数据线上哪些字节是有意义的字节使能信号。

如对应第4个字节,对应第5个字节。

在地址周期内,如果使用了DAC命令且信号有效,则表明~7上传输的是总线命令,否则这些位是保留的且不确定。

s / t/s: 64位传输请求。

该信号由当前主设备驱动,表示本设备要求采用64位通路传输数据。

它与有相同的时序。

s / t / s: 64位传输认可。

表明从设备将用64位传输。

此信号由从设备驱动,并且和具有相同的时序。

PAR64 t/s:奇偶双字节校验。

是AD32~AD63和~7的校验位。

当有效且~3上是DAC命令时, PAR64将在初始地址周期之后一个时钟周期有效,并在DAC命令的第二个地址周期后的一个时钟周期失效。

当和同时有效时,PAR64在备数据期内稳定有效,并且在或发出后的第一个时钟处失效。

PAR64信号一旦有效,将保持到数据周期完成之后的一个时钟周期。

该信号与AD32~AD63的时序相同,但延迟一个时钟周期。

该信号线在任何给定的总线周期内应保证连同AD32~AD63和~7在内的所有信号线上的“1”的个数为偶数(偶校验)或者为奇数(奇校验)。

在发送时产生而在接收时进行校验。

8.4.3 PCI总线的操作※总线命令※命令使用规则※ PCI总线协议※ PCI总线的数据传输过程一.总线命令总线命令是由主设备发向从设备,其作用是规定主、从设备之间的传输类型,它出现 于地址周期的3上。

这里的主设备是指通过仲裁而获得总线控制权的设备;从设备是指由:~3上命令及AD0~A 上的地址所选中的目标设备。

表8.1给出了总线编码及类型说明。

其中,命令编码中的1表示高电平,0表示低电平。

1.中断应答命令中断应答命令是一个读命令,执行主设备从申请中断的从设备中读回中断矢量的操作。

2.特殊周期命令该命令为PCI总线提供了一个简单的信息广播机制,通报处理器的状态或在各个从设备之间传递信息。

表8.1 总线命令表3.I/O读命令该命令用来从一个映射到I/O地址空间的设备中读取数据。