交通灯控制系统的VHDL代码

交通灯vhdl设计

LIBRARY IEEE;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity jiaotong isport( clk,jin,rest:in std_logic;ra,ya,ga,la:out std_logic;rb,yb,gb,lb:out std_logic;seg7ah: out std_logic_vector(6 downto 0); ---A路十位显示seg7al: out std_logic_vector(6 downto 0); ----A路个位显示seg7bh: out std_logic_vector(6 downto 0); ----B十位显示seg7bl: out std_logic_vector(6 downto 0) ----B个位显示);end jiaotong;architecture lights of jiaotong issignal clk1hz:std_logic;signal one,ten:std_logic_vector(3 downto 0);signal one1,ten1:std_logic_vector(3 downto 0);signal cnt:std_logic_vector(1 downto 0);signal seg7_b: std_logic_vector(6 downto 0); ---用于B道红灯计时signal seg7_h: std_logic_vector(6 downto 0); ---十位显示信号signal seg7_l: std_logic_vector(6 downto 0); ---个位显示信号signal seg7: std_logic_vector(6 downto 0); ---用于闪烁状态signal seg7_a: std_logic_vector(6 downto 0); ----用于A道红灯计时signal r1,y1,g1,l1,r2,y2,g2,l2:std_logic;type states is(s1,s2,s3,s4,s5,s6,s7,s8);beginp2:process(clk) --得到1HZ时钟信号variable num:integer range 0 to 499;beginif(clk'event and clk='1') thenif(num=499) then clk1hz<=(not clk1hz);num:=0;else num:=num+1;end if;end if;end process p2;p3:process(clk,rest,clk1hz) --状态改变电路variable qh,ql:std_logic_vector(3 downto 0); --计数器的十位,与个位变量variable a:std_logic;variable st :states;beginif(clk1hz'event and clk1hz='1') thenif(rest='1') then st:=s1; a:='0';elsecase st iswhen s1=>if(jin='0') then if(a='0')then qh:="0001";ql:="0100";a:='1';r1<='1';y1<='1';g1<='1';l1<='0';r2<='0';y2<='1';g2<='1';l2<='1';elsif(qh=0 and ql=1) then --实现状态转换st:=s2;a:='0';qh:="0000";ql:="0000";elsif(ql=0) then --实现15S计时ql:="1001";qh:=qh-1;else ql:=ql-1;end if;end if;when s2=>if(jin='0') thenif(a='0') then --实现A通道黄灯qh:="0000";ql:="0100";a:='1';r1<='1';y1<='0';g1<='1';l1<='1';r2<='0';y2<='1';g2<='1';l2<='1';elseif(ql=1) thenst:=s3;a:='0';qh:="0000";ql:="0000";else ql:=ql-1;end if;end if;end if;when s3=>if(jin='0') thenif(a='0') then --实现A通道通行绿灯qh:="0011";ql:="1001";a:='1';r1<='1';y1<='1';g1<='0';l1<='1';r2<='0';y2<='1';g2<='1';l2<='1';elseif(qh=0 and ql=1) thenst:=s4;a:='0';qh:="0000";ql:="0000";elsif(ql=0) thenql:="1001";qh:=qh-1;else ql:=ql-1;end if;end if;end if;when s4=>if(jin='0') thenif(a='0') then --实现A通道黄灯qh:="0000";ql:="0100";a:='1';r1<='1';y1<='0';g1<='1';l1<='1';r2<='0';y2<='1';g2<='1';l2<='1';elseif(ql=1) thenst:=s5;a:='0';qh:="0000";ql:="0000";else ql:=ql-1;end if;end if;end if;when s5=>if(jin='0') thenif(a='0') then --实现B道左转弯qh:="0001";ql:="0100";a:='1';r1<='0';y1<='1';g1<='1';l1<='1';r2<='1';y2<='1';g2<='1';l2<='0';elseif(qh=0 and ql=1) thenst:=s6;a:='0';qh:="0000";ql:="0000";elsif(ql=0) thenql:="1001";qh:=qh-1;else ql:=ql-1;end if;end if;end if;when s6=>if(jin='0') thenif(a='0') then --实现B道黄灯qh:="0000";ql:="0100";a:='1';r1<='0';y1<='1';g1<='1';l1<='1';r2<='1';y2<='0';g2<='1';l2<='1';elseif(ql=1) thenst:=s7;a:='0';qh:="0000";ql:="0000";else ql:=ql-1;end if;end if;end if;when s7=>if(jin='0') thenif(a='0') then --实现B道通行绿灯qh:="0010";ql:="1001";a:='1';r1<='0';y1<='1';g1<='1';l1<='1';r2<='1';y2<='1';g2<='0';l2<='1';elseif(qh=0 and ql=1) thenst:=s8;a:='0';qh:="0000";ql:="0000";elsif(ql=0) thenql:="1001";qh:=qh-1; else ql:=ql-1;end if;end if;end if;when s8=>if(jin='0') thenif(a='0') then --实现B道黄灯qh:="0000";ql:="0100";a:='1';r1<='0';y1<='1';g1<='1';l1<='1';r2<='1';y2<='0';g2<='1';l2<='1';elseif(ql=1) thenst:=s1;a:='0';qh:="0000";ql:="0000";else ql:=ql-1;end if;end if;end if;end case;end if;end if;one<=ql;ten<=qh;end process p3;p5: process(jin,clk) --紧急情况控制variable seg7_t:std_logic_vector(6 downto 0);beginif (jin='1') thenra<=r1 and (not jin); --A道红灯亮rb<=r2 and (not jin); --B到红灯亮ga<=g1 or jin;gb<=g2 or jin;ya<=y1 or jin;yb<=y2 or jin;la<=l1 or jin;lb<=l2 or jin;seg7_t:="1111111";seg7(0)<=seg7_t(0) and clk; ---实现数码管闪烁显示seg7(1)<=seg7_t(1) and clk;seg7(2)<=seg7_t(2) and clk;seg7(3)<=seg7_t(3) and clk;seg7(4)<=seg7_t(4) and clk;seg7(5)<=seg7_t(5) and clk;seg7(6)<=seg7_t(6) and clk;elsera<=r1;rb<=r2;ga<=g1 ;gb<=g2 ;ya<=y1 ;yb<=y2 ;la<=l1;lb<=l2;end if;end process p5;p6:process(clk,one,ten,one1,ten1) --------------7段译码--- beginc1:case one iswhen "0000" =>seg7_l<="0111111"; --0when "0001" =>seg7_l<="0000110"; --1when "0010" =>seg7_l<="1011011"; --2when "0011" =>seg7_l<="1001111"; --3when "0100" =>seg7_l<="1100110"; --4when "0101" =>seg7_l<="1101101"; --5when "0110" =>seg7_l<="1111101"; --6when "0111" =>seg7_l<="0000111"; --7when "1000" =>seg7_l<="1111111"; --8when "1001" =>seg7_l<="1100111"; --9when others=>seg7_l<="1110111";end case c1;c2:case ten iswhen "0000" =>seg7_h<="0111111"; --0when "0001" =>seg7_h<="0000110"; --1when "0010" =>seg7_h<="1011011"; --2when "0011" =>seg7_h<="1001111"; --3when "0100" =>seg7_h<="1100110"; --4when "0101" =>seg7_h<="1101101"; --5when "0110" =>seg7_h<="1111101"; --6when "0111" =>seg7_h<="0000111"; --7when "1000" =>seg7_h<="1111111"; --8when "1001" =>seg7_h<="1100111"; --9when others=>seg7_h<="1110111";end case c2;c3:case ten1 iswhen "0000" =>seg7_a<="0111111"; --0when "0001" =>seg7_a<="0000110"; --1when "0010" =>seg7_a<="1011011"; --2when "0011" =>seg7_a<="1001111"; --3when "0100" =>seg7_a<="1100110"; --4when "0101" =>seg7_a<="1101101"; --5when "0110" =>seg7_a<="1111101"; --6when "0111" =>seg7_a<="0000111"; --7when "1000" =>seg7_a<="1111111"; --8when "1001" =>seg7_a<="1100111"; --9when others=>seg7_a<="1110111";end case c3;c4:case one1 iswhen "0000" =>seg7_b<="0111111"; --0when "0001" =>seg7_b<="0000110"; --1when "0010" =>seg7_b<="1011011"; --2when "0011" =>seg7_b<="1001111"; --3when "0100" =>seg7_b<="1100110"; --4when "0101" =>seg7_b<="1101101"; --5when "0110" =>seg7_b<="1111101"; --6when "0111" =>seg7_b<="0000111"; --7when "1000" =>seg7_b<="1111111"; --8when "1001" =>seg7_b<="1100111"; --9when others=>seg7_b<="1110111";end case c4;end process p6;p7:process(jin,clk,clk1hz,r1,r2) --------------显示模块--- beginif(jin='0') thenelsif(r1='0') thenseg7bh<=seg7_h; seg7bl<=seg7_l;seg7ah<=seg7_a; seg7al<=seg7_b;elsif(r2='0') thenseg7bh<=seg7_a; seg7bl<=seg7_b;seg7ah<=seg7_h; seg7al<=seg7_l;elseseg7ah<=seg7; seg7al<=seg7;seg7bh<=seg7; seg7bl<=seg7;end if;end process p7;p8:process(r1,r2,clk) ---红灯计时模块variable kh,kl:std_logic_vector(3 downto 0);variable b:std_logic;beginif(rest='1') then b:='0';end if;if(r1='0' and jin='0') then ---A路红灯时间计时if(b='0') thenkh:="0101";kl:="0100";b:='1';elseif(kh=0 and kl=1) thenkh:="0000"; kl:="0000"; b:='0';elsif(kl=0) then kl:="1001"; kh:=kh-1;elsekl:=kl-1;end if;end if;end if;if(r2='0' and jin='0') then --B路红灯时间计时if(b='0') thenkh:="0110";kl:="0100";b:='1';elseif(kh=0 and kl=1) thenkh:="0000"; kl:="0000"; b:='0';elsif(kl=0) then kl:="1001"; kh:=kh-1;elsekl:=kl-1;end if;end if;end if;ten1<=kh; one1<=kl;end process p8;end lights;。

vhdl交通灯说明

一:十字路口交通灯实现程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY traffic ISPORT ( clk,urgency:IN STD_LOGIC;led:BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0);East_West,South_North:BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0));END traffic;ARCHITECTURE A OF traffic ISBEGINPROCESS(clk)BEGINIF urgency='0' THEN --紧急情况两方向都禁止led<="10000001";--全红灯East_West<="00000000";South_North<="00000000";ELSIF clk'event AND clk='1' THENIF East_West>"01000110"OR South_North>"01000110" THENEast_West<="01000101";--45sSouth_North<="01000000";--40Sled<="10000100";--东西红灯南北绿灯(红黄绿--绿黄红)ELSIF East_West="00000110"AND South_North="00000001" THENEast_West<="00000101";--5SSouth_North<="00000101";--5Sled<="10000010";--东西红灯南北黄灯ELSIF East_West="00000001"AND South_North="00000001"andled="10000010" THEN--East_West<="01000000";--40SSouth_North<="01000101";--45Sled<="00100001";--东西绿灯南北红灯ELSIF East_West="00000001"AND South_North="00000110" THENEast_West<="00000101";South_North<="00000101";led<="01000001";--东西黄灯南北红灯ELSIF East_West<="00000001"AND South_North="00000001"AND LED="01000001" THEN East_West<="01000101";South_North<="01000000";led<="10000100";--东西红灯南北绿灯ELSIF East_West(3 DOWNTO 0)=0 THENEast_West<=East_West-7;--计数超出范围则减7South_North<=South_North-1;ELSIF South_North(3 DOWNTO 0)=0 THENEast_West<=East_West-1;South_North<=South_North-7;ELSEEast_West<=East_West-1;--正常情况下东西南北各计数值减1(上升沿触发)South_North<=South_North-1;END IF;END IF;END PROCESS;END A;二:模式选择与引脚定义如下:1:选择模式52:引脚定义如下:三:硬件说明:数码管2和数码管1作为东西方向灯的时间显示,数码管4和数码管3作为南北方向灯的时间显示。

vhdl交通灯程序

IF(countnum=80) THEN

next_state:=s3; seconds<="0000";

ELSIF(countnum>=60 AND countnum<80) THEN

(countnum>=139 AND countnum<141) OR

(countnum>=143 AND countnum<145) OR

(countnum>=147 AND countnum<149)) THEN

next_state:=s2;

IF((countnum>=61 AND countnum<63) OR

(countnum>=65 AND countnum<67) OR

next_state:=s4;

IF((countnum>=131 AND countnum<133) OR

(countnum>=135 AND countnum<137) OR

VARIABLE next_state:states; --状态变量

BEGIN

IF(reset='0') THEN --复位

countnum:=0; seconds<="0000"; next_state:=s0;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

VHDL交通灯程序

该程序基于VHDL语言使用spartan6芯片实现的建议交通灯的变化红灯---25秒黄灯闪烁---5秒绿灯---20秒在LED灯亮的时候伴有没有灯亮的时候数码管的倒计时library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating-- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entitytrafficlight isport( clk:instd_logic;rst:instd_logic;led: out std_logic_vector(9 downto 0);ledout: out std_logic_vector(3 downto 0)); endtrafficlight;architecture Behavioral of trafficlight issignalcount:integer range 1 to 50 ;signalclkcount:integer range 0 to 20000000;signaldivclk:std_logic;signal clkcount1:integer range 0 to 200000;signal clkcount2:integer range 0 to 600000;signalshi:std_logic_vector(3 downto 0);signalge:std_logic_vector(3 downto 0);signalsel:std_logic_vector(1 downto 0);beginprocess(clk,rst) --秒脉冲分频beginifrst='0' thenclkcount<=0;elsifclk'event and clk='1' thenifclkcount=20000000 thenclkcount<=0;divclk<=not divclk;elseclkcount<=clkcount+1;end if;end if;end process;process(clk,clkcount2,sel,rst) --数码管扫描分频beginifrst='0' thenclkcount2<=0;elsifclk'event and clk='1' thenif clkcount2=600000 thenclkcount2<=0;else clkcount2<=clkcount2+1;end if;end if;if (clkcount2<300000) thensel<="01";elsesel<="10";end if;end process;process(divclk,rst)beginifrst='0' thencount<=1;elsifdivclk'event and divclk='1' thenif count=50 thencount<=1;elsecount<=count+1;end if;end if;end process;process(divclk,rst)beginif (rst='0' ) thenge<="0101";shi<="0010";elsif(divclk'event and divclk='1')thenif(count<=25)thenif(ge="0001"and shi="0000")thenge<="0101";shi<="0000";elsif(ge="0000")thenshi<=shi-1;ge<="1001";elsege<=ge-1;end if;elsif(count<=30)thenif(ge="0001"and shi="0000")thenge<="0000";shi<="0010";elsege<=ge-1;end if;elsif(count<=50)thenif(ge="0001"and shi="0000")thenge<="0101";shi<="0010";elsif(ge="0000")thenshi<=shi-1;ge<="1001";elsege<=ge-1;end if;end if;end if;end process;process(count,divclk,rst)beginifrst='0' thenledout<="0000";elsifdivclk'event and divclk='1' thenif(count=50)thenledout<="0001";elsif(count<=24)thenledout<="0001";elsif(count<=29)thencase count iswhen 25=>ledout<="0100";when 26=>ledout<="0000";when 27=>ledout<="0100";when 28=>ledout<="0000";when 29=>ledout<="0100";when others=>ledout<="0100";end case;elseledout<="0010";end if;end if;end process;process(ge,shi,sel)beginif(sel="01")thencasege iswhen"0000"=> led <="010*******";when"0001"=> led <="010*******";when"0010"=> led <="010*******";when"0011"=> led <="010*******";when"0100"=> led <="010*******";when"0101"=> led <="010*******";when"0110"=> led <="010*******";when"0111"=> led <="010*******";when"1000"=> led <="010*******";when"1001"=> led <="010*******";when others=> led <="010*******";end case;elsecaseshi iswhen"0000"=> led <="1000111111";when"0001"=> led <="1000000110";when"0010"=> led <="1001011011";when others => led <="1001111111";end case;end if;end process;end Behavioral;。

交通灯控制器-VHDL语言编写代码

---------------------------------------Title:交通灯控制器----Author:Pan Hongtao ----Data: 2006-10-1 ---------------------------------------library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--------------------------------------------------------------------entity exp18 isport( Clk : in std_logic; --时钟输入Rst : in std_logic; --复位输入R1,R2 : out std_logic; --红灯输出Y1,Y2 : out std_logic; --黄灯输出G1,G2 : out std_logic; --绿灯输出Display : out std_logic_vector(6 downto 0); --七段码管显示输出SEG_SEL : buffer std_logic_vector(2 downto 0) --七段码管扫描驱动);end exp18;--------------------------------------------------------------------architecture behave of exp18 issignal Disp_Temp : integer range 0 to 15;signal Disp_Decode : std_logic_vector(6 downto 0);signal SEC1,SEC10 : integer range 0 to 9;signal Direction : integer range 0 to 15;signal Clk_Count1 : std_logic_vector(9 downto 0); --产生0.5Hz时钟的分频计数器signal Clk1Hz : std_logic;signal Dir_Flag : std_logic; --方向标志beginprocess(Clk)beginif(Clk'event and Clk='1') thenif(Clk_Count1<1000) thenClk_Count1<=Clk_Count1+1;elseClk_Count1<="0000000001";end if;end if;end process;Clk1Hz<=Clk_Count1(9);process(Clk1Hz,Rst)beginif(Rst='0') thenSEC1<=0;SEC10<=2;Dir_Flag<='0';elsif(Clk1Hz'event and Clk1Hz='1') thenif(SEC1=0) thenSEC1<=9;if(SEC10=0) thenSEC10<=1;elseSEC10<=SEC10-1;end if;elseSEC1<=SEC1-1;end if;if(SEC1=0 and SEC10=0) thenDir_Flag<=not Dir_Flag;end if;end if;end process;process(Clk1Hz,Rst)beginif(Rst='0') thenR1<='1';G1<='0';R2<='1';G2<='0';else --正常运行if(SEC10>0 or SEC1>3) thenif(Dir_Flag='0') then --横向通行R1<='0';G1<='1';R2<='1';G2<='0';elseR1<='1';G1<='0';R2<='0';G2<='1';end if;elseif(Dir_Flag='0') then --横向通行R1<='0';G1<='0';R2<='1';G2<='0';elseR1<='1';G1<='0';R2<='0';G2<='0';end if;end if;end if;end process;process(Clk1Hz)beginif(SEC10>0 or SEC1>3) thenY1<='0';Y2<='0';elsif(Dir_Flag='0') thenY1<=Clk1Hz;Y2<='0';elseY1<='0';Y2<=Clk1Hz;end if;end process;process(Dir_Flag)beginif(Dir_Flag='0') then --横向Direction<=10;else --纵向Direction<=11;end if;end process;process(SEG_SEL)begincase (SEG_SEL+1) iswhen "000"=>Disp_Temp<=Direction;when "001"=>Disp_Temp<=Direction;when "010"=>Disp_Temp<=SEC10;when "011"=>Disp_Temp<=SEC1;when "100"=>Disp_Temp<=Direction;when "101"=>Disp_Temp<=Direction;when "110"=>Disp_Temp<=SEC10;when "111"=>Disp_Temp<=SEC1;end case;end process;process(Clk)beginif(Clk'event and Clk='1') then --扫描累加SEG_SEL<=SEG_SEL+1;Display<=Disp_Decode;end if;end process;process(Disp_Temp) --显示转换begincase Disp_Temp iswhen 0=>Disp_Decode<="0111111"; --'0'when 1=>Disp_Decode<="0000110"; --'1'when 2=>Disp_Decode<="1011011"; --'2'when 3=>Disp_Decode<="1001111"; --'3'when 4=>Disp_Decode<="1100110"; --'4'when 5=>Disp_Decode<="1101101"; --'5'when 6=>Disp_Decode<="1111101"; --'6'when 7=>Disp_Decode<="0000111"; --'7'when 8=>Disp_Decode<="1111111"; --'8'when 9=>Disp_Decode<="1101111"; --'9'when 10=>Disp_Decode<="1001000"; --'='when 11=>Disp_Decode<="0010100"; --'||'when others=>Disp_Decode<="0000000"; --全灭end case;end process;end behave;。

交通灯VHDL语言程序源代码

交通灯控制器的设计智能交通灯控制器的源程序如下:library ieee;use ieee.std_logic_1164.all;entity traffic_control isport( clk: in std_logic;sense0,sense1: in std_logic; --分别为东西路和南北路车辆指示器counter: out integer range 0 to 44;r0,y0,g0: out std_logic; --r0,y0,g0为南北路的红、黄、绿灯r1,y1,g1:out std_logic); --r1,y1,g1为东西路的红、黄、绿灯end;architecture art of traffic_control2 issignal state:std_logic_vector(1 downto 0);signal cnt:integer range 0 to 44;beginprocess(clk)variable nclr,en:bit; --nclr为倒计时计数器清零端,en为计数器使能端beginif clk'event and clk='1' thenif nclr='0' thencnt<=0; --同步清零elsif en='0'thencnt<=cnt; --计数器停止计数elsecnt<=cnt+1; --计数器值增加end if;case state iswhen "00"=>r0<='1';y0<='0';g0<='0';r1<='0';y1<='0';g1<='1';if(sense0 and sense1)='1' then --东西道和南北道都有车if cnt=44 thenstate<="01";nclr:='0';en:='0';elsestate<="00";nclr:='1';en:='1';end if;elsif(sense0 and (not sense1))='1' then --东西道有车,南北道无车state<="01";nclr:='0';en:='0';elsestate<="00";nclr:='1';en:='1';end if;when "01"=>r0<='1';y0<='0';g0<='0';r1<='0';y1<='1';g1<='0';if cnt=5 thenstate<="10";nclr:='0';en:='0';elsestate<="01";nclr:='1';en:='1';end if;when "10"=>r0<='0';y0<='0';g0<='1';r1<='1';y1<='0';g1<='0';if(sense0 and sense1)='1' then --东西道和南北道都有车if cnt=29 thenstate<="11";nclr:='0';en:='0';elsestate<="10";nclr:='1';en:='1';end if;elsif sense0 ='0' then --东西道有车,南北道无车state<="11";nclr:='0';en:='0';elsestate<="10";nclr:='1';en:='1';end if;when "11"=>r0<='1';y0<='1';g0<='0';r1<='1';y1<='0';g1<='0';if cnt=5 thenstate<="00";nclr:='0';en:='0';elsestate<="11";nclr:='1';en:='1';end if;end case;end if;end process;counter<=cnt;end art;。

基于VHDL的交通灯控制系统的设计

摘要摘要EDA技术的一个重要特征就是使用硬件描述语言(HDL)来完成系统的设计文件,应用VHDL的数字电路实验降低了数字系统的设计难度,这在电子设计领域已得到设计者的广泛采用。

本设计就是针对交通信号灯控制器的设计问题,提出了基于VHDL语言的交通信号灯系统的硬件实现方法。

通过对系统进行结构分析,采用了层次化的设计方法,给出了各个模块的VHDL程序,并且利用Quartus Ⅱ对应用程序进行了仿真,并给出了相应的仿真结果。

通过电路优化设计,可以使用规模更小的可编程逻辑芯片,从而降低系统成本。

关键词:交通信号灯;VHDL;仿真ABSTRACTABSTRACTOne important characteristic of the EDA is that the design documents should be completed by the HDL, the digital circuit experiment utilized very-high-speed integrated circuit hardware description language(VHDL) may reduce the difficulties of digital system designing, and it is widely used by electronic designer now. Aiming at the design problem of traffic light controller, this paper puts forward a hardware realization method of traffic light system with VHDL. By analyzing the architecture of system, it gives the program of each module with VHDL using hierarchical design means. It also gives the simulation results by QuartusⅡ. Optimizes the design through the electric circuit, may use the scale smaller programmable logic chip, thus reduces the system cost.Key word: Street-traffic control lights; VHDL; Simulation目录第1章引言 (1)第2章EDA技术概述 (2)2.1 EDA技术及其发展 (2)2.2 EDA与传统电子设计方法的比较 (2)2.3 EDA的工程设计流程 (2)第3章可编程技术简介 (4)3.1 可编程逻辑器件概述 (4)3.2 FPGA/CPLD概述 (4)3.3 硬件描述语言介绍 (5)3.4 选择VHDL硬件描述语言设计的优势 (6)3.5 软件开发工具Quartus II 简介 (6)第4章交通灯控制系统的设计 (8)4.1 系统功能分析 (8)4.2 系统结构设计 (9)4.3系统程序实现与仿真分析 (10)4.3.1 时钟脉冲发生电路 (10)4.3.2 计数秒数选择电路 (12)4.3.3 倒计时控制电路 (15)4.3.4 红绿灯信号控制电路 (19)4.3.5 建立程序包 (22)4.3.6 连接各个模块 (23)4.3.7 状态机的优势 (24)结束语 (26)参考文献 (27)致谢 (28)附录 (29)1.时钟发生电路程序代码 (29)2.计数秒数选择电路程序代码 (31)3.倒计时控制电路程序代码 (32)4.红绿灯信号控制电路程序代码 (34)5.连接各个模块的程序代码 (38)外文资料原文 ................................................................................... 错误!未定义书签。

VHDL 交通灯

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY JTDKZ ISPORT(CLK,SM,SB:IN STD_LOGIC; MR,MY,MG,BR,BY,BG:OUT STD_LOGIC); END ENTITY JTDKZ;ARCHITECTURE ART OF JTDKZ ISTYPE STATE_TYPE IS(A,B,C,D);SIGNAL STATE:STA TE_TYPE;BEGINCNT:PROCESS(CLK) ISV ARIABLE S:INTEGER RANGE 0 TO 45;V ARIABLE CLR,EN: BIT;BEGINIF (CLK'EVENT AND CLK='1')THENIF CLR='0'THENS:=0;ELSIF EN='0' THENS:=S;ELSES:=S+1;END IF;CASE STATE ISWHEN A=>MR<='0';MY<='0';MG<='1';BR<='1';BY<='0';BG<='0';IF(SB AND SM)='1' THENIF S=45 THENSTATE<=B;CLR:='0';EN:='0';ELSESTATE<=A;CLR:='1';EN:='1';END IF;ELSIF(SB AND (NOT SM))='1' THEN STATE<=B; CLR:='0';EN:='0';ELSESTATE<=A;CLR:='1';EN:='1';END IF;WHEN B=>MR<='0';MY<='1';MG<='0';BR<='1';BY<='0';BG<='0';IF S=5 THENSTATE<=C;CLR:='0';EN:='0';ELSESTATE<=B;CLR:='1'; EN:='1';END IF;WHEN C=>MR<='1';MY<='0';MG<='0';BR<='0';BY<='0';BG<='1';IF(SM AND SB)='1' THENIF S=25 THENSTATE<=D;CLR:='0';EN:='0';ELSESTATE<=C;CLR:='1';EN:='1';END IF;ELSIF SB='0' THENSTATE<=D;CLR:='0';EN:='0';ELSESTATE<=C;CLR:='1';EN:='1';END IF;WHEN D=>MR<='1';MY<='0';MG<='0';BR<='0';BY<='1';BG<='0';IF S=5 THENSTATE<=A;CLR:='0';EN:='0';ELSESTATE<=D;CLR:='1'; EN:='1';END IF;END CASE;END IF;END PROCESS CNT;END ARCHITECTURE ART;-- CNT45S.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT45S ISPORT(SB,CLK,EN45:IN STD_LOGIC;DOUT45M,DOUT45B:OUTSTD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY CNT45S;ARCHITECTURE ART OF CNT45S ISSIGNAL CNT6B: STD_LOGIC_VECTOR(5 DOWNTO 0);BEGINPROCESS(SB,CLK,EN45)ISBEGINIF SB='0'THEN CNT6B<=CNT6B-CNT6B-1;ELSIF(CLK'EVENT AND CLK='1')THENIF EN45='1'THEN CNT6B<=CNT6B+1;ELSIF EN45='0'THEN CNT6B<= CNT6B-CNT6B-1;END IF;END IF;END PROCESS;PROCESS(CNT6B) ISBEGINCASE CNT6B ISWHEN"000000"=>DOUT45M<="01000101";D OUT45B<="01010000";WHEN"000001"=>DOUT45M<="01000100";D OUT45B<="01001001";WHEN"000010"=>DOUT45M<="01000011";D OUT45B<="01001000";WHEN"000011"=>DOUT45M<="01000010";D OUT45B<="01000111";WHEN"000100"=>DOUT45M<="01000001";D OUT45B<="01000110";WHEN"000101"=>DOUT45M<="01000000";D OUT45B<="01000101";WHEN"000110"=>DOUT45M<="00111001";D OUT45B<="01000100";WHEN"000111"=>DOUT45M<="00111000";D OUT45B<="01000011";WHEN"001000"=>DOUT45M<="00110111";D OUT45B<="01000010";WHEN"001001"=>DOUT45M<="00110110";D OUT45B<="01000001";WHEN"001010"=>DOUT45M<="00110100";D OUT45B<="01000000";WHEN"001011"=>DOUT45M<="00110100";D OUT45B<="01101001";WHEN"001100"=>DOUT45M<="00110011";D OUT45B<="00111000";WHEN"001101"=>DOUT45M<="00110010";D OUT45B<="00110111";WHEN"001110"=>DOUT45M<="00110001";D OUT45B<="00110110";WHEN"001111"=>DOUT45M<="00110000";D OUT45B<="00110101";WHEN"010000"=>DOUT45M<="00101001";D OUT45B<="00110100";WHEN"010001"=>DOUT45M<="00101000";D OUT45B<="00110011";WHEN"010010"=>DOUT45M<="00100111";D OUT45B<="00110010";WHEN"010011"=>DOUT45M<="00100110";D OUT45B<="00110001";WHEN"010100"=>DOUT45M<="00100101";D OUT45B<="00110000";WHEN"010101"=>DOUT45M<="00100100";D OUT45B<="00101001";WHEN"010110"=>DOUT45M<="00100011";D OUT45B<="00101000";WHEN"010111"=>DOUT45M<="00100010";D OUT45B<="00100111";WHEN"011000"=>DOUT45M<="00100001";D OUT45B<="00100110";WHEN"011001"=>DOUT45M<="00100000";D OUT45B<="00100101";WHEN"011010"=>DOUT45M<="00011001";D OUT45B<="00100100";WHEN"011011"=>DOUT45M<="00011000";D OUT45B<="00100011";WHEN"011100"=>DOUT45M<="00010111";D OUT45B<="00100010";WHEN"011101"=>DOUT45M<="00010110";D OUT45B<="00100001";WHEN"011110"=>DOUT45M<="00010101";D OUT45B<="00100000";WHEN"011111"=>DOUT45M<="00010100";D OUT45B<="00011001";WHEN"100000"=>DOUT45M<="00010011";D OUT45B<="00011000";WHEN"100001"=>DOUT45M<="00010010";D OUT45B<="00010111";WHEN"100010"=>DOUT45M<="00010001";D OUT45B<="00010110";WHEN"100011"=>DOUT45M<="00010000";D OUT45B<="00010101";WHEN"100100"=>DOUT45M<="00001001";D OUT45B<="00010100";WHEN"100101"=>DOUT45M<="00001000";D OUT45B<="00010011";WHEN"100110"=>DOUT45M<="00000111";D OUT45B<="00010010";WHEN"100111"=>DOUT45M<="00000110";D OUT45B<="00010001";WHEN"101000"=>DOUT45M<="00000101";D OUT45B<="00010000";WHEN"101001"=>DOUT45M<="00000100";D OUT45B<="00001001";WHEN"101010"=>DOUT45M<="00000011";D OUT45B<="00001000";WHEN"101011"=>DOUT45M<="00000010";D OUT45B<="00000111";WHEN"101100"=>DOUT45M<="00000001";D OUT45B<="00000110";WHEN OTHERS=>DOUT45M<="00000000"; DOUT45B<="00000000";END CASE;END PROCESS;END ARCHITECTURE ART;--CNT05S.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT05S ISPORT(CLK,EN05M,EN05B:IN STD_LOGIC; DOUT5:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY CNT05S;ARCHITECTURE ART OF CNT05S ISSIGNAL CNT3B: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINPROCESS(CLK, EN05M,EN05B) ISBEGINIF(CLK'EVENT AND CLK='1')THENIF EN05M='1' OR EN05B='1'THENCNT3B<=CNT3B+1;ELSECNT3B<="000";END IF;END IF;END PROCESS;PROCESS(CNT3B) ISBEGINCASE CNT3B ISWHEN "000"=>DOUT5<="00000101";WHEN "001"=>DOUT5<="00000100";WHEN "010"=>DOUT5<="00000011";WHEN "011"=>DOUT5<="00000010";WHEN "100"=>DOUT5<="00000001";WHEN OTHERS=>DOUT5<="00000000";END CASE;END PROCESS;END ARCHITECTURE ART;--CNT25S.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT25S ISPORT(SB,SM,CLK,EN25:IN STD_LOGIC;DOUT25M,DOUT25B:OUTSTD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY CNT25S;ARCHITECTURE ART OF CNT25S ISSIGNAL CNT5B: STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINPROCESS(SB,SM,CLK,EN25)ISBEGINIF SB='0' OR SM='0' THENCNT5B<=CNT5B-CNT5B-1;ELSIF(CLK'EVENT AND CLK='1')THENIF EN25='1' THENCNT5B<=CNT5B+1;ELSIF EN25='0'THENCNT5B<= CNT5B-CNT5B-1;END IF;END IF;END PROCESS;PROCESS(CNT5B) ISBEGINCASE CNT5B ISWHEN"00000"=>DOUT25B<="00100101";DO UT25M<="00110000";WHEN"00001"=>DOUT25B<="00100100";DO UT25M<="00101001";WHEN"00010"=>DOUT25B<="00100011";DO UT25M<="00101000";WHEN"00011"=>DOUT25B<="00100010";DO UT25M<="00100111";WHEN"00100"=>DOUT25B<="00100001";DO UT25M<="00100110";WHEN"00101"=>DOUT25B<="00100000";DO UT25M<="00100101";WHEN"00110"=>DOUT25B<="00011001";DO UT25M<="00100100";WHEN"00111"=>DOUT25B<="00011000";DO UT25M<="00100011";WHEN"01000"=>DOUT25B<="00010111";DO UT25M<="00100010";WHEN"01001"=>DOUT25B<="00010110";DO UT25M<="00100001";WHEN"01010"=>DOUT25B<="00010101";DOUT25M<="00100000";WHEN"01011"=>DOUT25B<="00010100";DO UT25M<="00011001";WHEN"01100"=>DOUT25B<="00010011";DO UT25M<="00011000";WHEN"01101"=>DOUT25B<="00010010";DO UT25M<="00010111";WHEN"01110"=>DOUT25B<="00010001";DO UT25M<="00010110";WHEN"01111"=>DOUT25B<="00001000";DO UT25M<="00010101";WHEN"10000"=>DOUT25B<="00001001"; DOUT25M<="00010100";WHEN"10001"=>DOUT25B<="00001000"; DOUT25M<="00010011";WHEN"10010"=>DOUT25B<="00000111"; DOUT25M<="00010010";WHEN"10011"=>DOUT25B<="00000101"; DOUT25M<="00010001";WHEN"10100"=>DOUT25B<="00000100"; DOUT25M<="00010000";WHEN"10101"=>DOUT25B<="00000100"; DOUT25M<="00001001";WHEN"10110"=>DOUT25B<="00000011"; DOUT25M<="00001000";WHEN"10111"=>DOUT25B<="00000010"; DOUT25M<="00000111";WHEN"11000"=>DOUT25B<="00001001"; DOUT25M<="00000110";WHEN OTHERS=>DOUT25B<="00000000"; DOUT25M<="00000000";END CASE;END PROCESS;END ARCHITECTURE ART;--XSKZ.VHDLLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY XSKZ ISPORT(EN45,EN25,EN05M,EN05B: IN STD_LOGIC;AIN45M,AIN45B: IN STD_LOGIC_VECTOR(7 DOWNTO 0);AIN25M,AIN25B,AIN05: IN STD_LOGIC_VECTOR(7 DOWNTO 0);DOUTM,DOUTB: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY XSKZ;ARCHITECTURE ART OF XSKZ ISBEGINPROCESS(EN45,EN25,EN05M, EN05B) ISBEGINIF EN45='1' THENDOUTM<=AIN45M(7 DOWNTO 0);DOUTB<=AIN45B(7 DOWNTO 0);ELSIF EN05M='1' THENDOUTM<=AIN05(7 DOWNTO 0); DOUTB<=AIN05(7 DOWNTO 0);ELSIF EN25='1' THENDOUTM<=AIN25B(7 DOWNTO 0); DOUTB<=AIN25B(7 DOWNTO 0);ELSIF EN05B='1' THENDOUTM<=AIN05(7 DOWNTO 0); DOUTB<=AIN05(7 DOWNTO 0);END IF;END PROCESS;END ARCHITECTURE ART;。

VHDL实验源码-交通灯控制

library ieee;use ieee.std_logic_1164.all;entity traffic_control isport( clk,reset:in std_logic;light_h,light_v:out std_logic_vector(2 downto 0); count_vh,count_vl,count_hh,count_hl:out std_logic_vector(3 downto 0)); end entity traffic_control;architecture behave of traffic_control issignal temp,temp_h,temp_v:integer range 0 to 100:=0;beginP1:process(reset,clk)beginif(reset='1') thentemp<=0;elsif(reset='0') thenif(clk'event and clk='1') thenif(temp=100) thentemp<=0;else temp<=temp+1;end if;end if;end if;end process p1;p2:process(reset,clk,temp)variable y_h,y_v,x_h,x_v:integer range 0 to 9;beginif(temp<55) thentemp_h<=55-temp;temp_v<=60-temp;light_h<="100";light_v<="001";elsif(temp>=55 and temp<60)thentemp_h<=60-temp;temp_v<=60-temp;light_h<="010";light_v<="001";elsif(temp>=60 and temp<95)thentemp_h<=100-temp;temp_v<=95-temp;light_h<="001";light_v<="100";elsif(temp>=96) thentemp_h<=100-temp;temp_v<=100-temp;light_h<="100";light_v<="010";end if;y_h:=temp_h/10;x_h:=temp_h mod 10;y_v:=temp_v/10;x_v:=temp_v mod 10;c1:case y_h iswhen 0 => count_hh<="0000";when 1 => count_hh<="0001";when 2 => count_hh<="0010";when 3 => count_hh<="0011";when 4 => count_hh<="0100";when 5 => count_hh<="0101";when 6 => count_hh<="0110";when others => count_hh<="0000";end case c1;c2:case x_h iswhen 0 => count_hl<="0000";when 1 => count_hl<="0001";when 2 => count_hl<="0010";when 3 => count_hl<="0011";when 4 => count_hl<="0100";when 5 => count_hl<="0101";when 6 => count_hl<="0110";when 7 => count_hl<="0111";when 8 => count_hl<="1000";when 9 => count_hl<="1001";when others => count_hl<="0000"; end case c2;c3:case y_v iswhen 0 => count_vh<="0000";when 1 => count_vh<="0001";when 2 => count_vh<="0010";when 3 => count_vh<="0011";when 4 => count_vh<="0100";when 5 => count_vh<="0101";when 6 => count_vh<="0110";when others => count_vh<="0000"; end case c3;c4:case x_v iswhen 0 => count_vl<="0000";when 1 => count_vl<="0001";when 2 => count_vl<="0010";when 3 => count_vl<="0011";when 4 => count_vl<="0100";when 5 => count_vl<="0101";when 6 => count_vl<="0110";when 7 => count_vl<="0111";when 8 => count_vl<="1000";when 9 => count_vl<="1001";when others => count_vl<="0000"; end case c4;end process p2;end architecture behave;。

基于FPGA的交通灯控制器设计(VHDl代码全,各个模块均调.

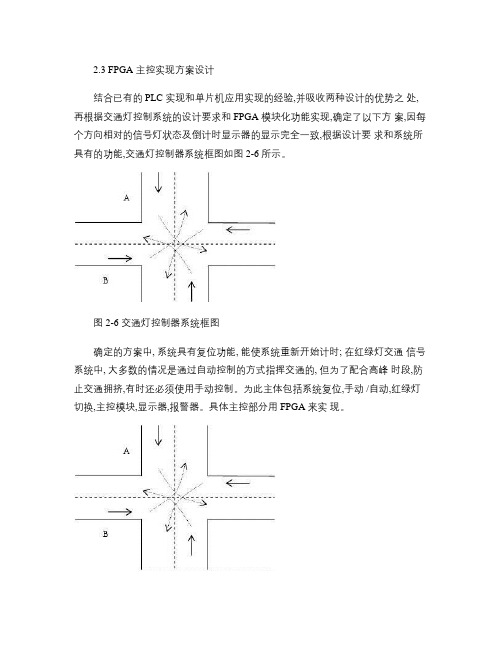

2.3 FPGA 主控实现方案设计结合已有的 PLC 实现和单片机应用实现的经验,并吸收两种设计的优势之处,再根据交通灯控制系统的设计要求和 FPGA 模块化功能实现,确定了以下方案,因每个方向相对的信号灯状态及倒计时显示器的显示完全一致,根据设计要求和系统所具有的功能,交通灯控制器系统框图如图 2-6 所示。

图 2-6 交通灯控制器系统框图确定的方案中, 系统具有复位功能, 能使系统重新开始计时; 在红绿灯交通信号系统中, 大多数的情况是通过自动控制的方式指挥交通的, 但为了配合高峰时段,防止交通拥挤,有时还必须使用手动控制。

为此主体包括系统复位,手动 /自动,红绿灯切换,主控模块,显示器,报警器。

具体主控部分用 FPGA 来实现。

图 2-7 交通灯通行示意图结合实现方案,主要有东西、南北、南北左拐,东西左拐,跟手动控制 5种工作方式,具体由 M2~M0设定,具体如表 2-1。

表2-1 交通灯工作方式表方式 M2(0:自动, 1:手动 M1(0:A向,1:B向M0(O:直行, 1:左拐1 0 0 02 0 0 13 0 1 04 0 1 15 1 * *当出现特殊情况时,可选择方式 1 到方式 4 中的任何一种方式,停止正常运行,进入特殊运行状态。

此时交通灯按工作方式显示,计时电路停止计时,计时时间闪烁显示。

当系统总复位时,控制电路和计时电路复位,信号灯全部熄灭。

3 各功能模块的设计与实现3.1总体设计思路3.1.1系统组成框图结合设计任务要求和确定的实现方案, 假设某个十字路口是由一条主干道和一条次干道回合而成, 在每个方向设置红绿黄 3种信号灯, 红灯亮禁止通行, 绿灯亮允许通行。

黄灯亮允许行驶中车辆有时间停考到禁止线以外。

按照自顶向下的层次化设计方法, 整个系统可分为 4个模块, 系统时序发生电路、红绿灯计数时间选择模块、定时控制电路、红绿灯信号译码电路。

其系统组成方框图如图 3-1所示。

交通灯的VHDL语言设计

when green=>if a='0' then th:="0011"; tl:=“0000"; a:='1'; g<='1'; r<='0'; yy<='0'; else if not(th="0000" and tl="0110") then if tl="0000" then tl:="1001"; th:=th-1; else tl:=tl-1; end if; else th:="0000"; tl:=tl-1; a:='0'; state:=yellow; end if; end if;

when yellow=>if a='0' then th:="0000"; tl:="0101"; a:='1'; g<='0'; r<='0'; yy<='1'; else if not(th="0000" and tl="0001") then tl:=tl-1; else th:="0000"; tl:="0001"; a:='0'; state:=red; end if; end if; end case; end if; timh<=th; timl<=tl; y<=(yy and clk2); end process; end rtl;

VHDL应用 VHDL应用举例

Verilog代码(计数器、交通灯、串并转换)

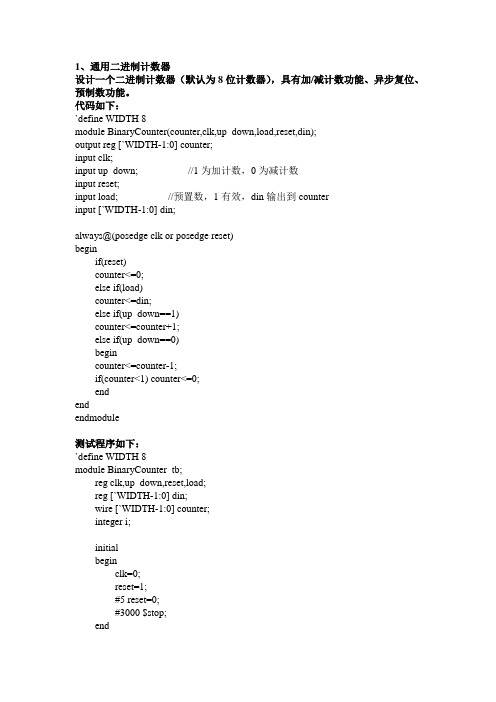

1、通用二进制计数器设计一个二进制计数器(默认为8位计数器),具有加/减计数功能、异步复位、预制数功能。

代码如下:`define WIDTH 8module BinaryCounter(counter,clk,up_down,load,reset,din);output reg [`WIDTH-1:0] counter;input clk;input up_down; //1为加计数,0为减计数input reset;input load; //预置数,1有效,din输出到counterinput [`WIDTH-1:0] din;always@(posedge clk or posedge reset)beginif(reset)counter<=0;else if(load)counter<=din;else if(up_down==1)counter<=counter+1;else if(up_down==0)begincounter<=counter-1;if(counter<1) counter<=0;endendendmodule测试程序如下:`define WIDTH 8module BinaryCounter_tb;reg clk,up_down,reset,load;reg [`WIDTH-1:0] din;wire [`WIDTH-1:0] counter;integer i;initialbeginclk=0;reset=1;#5 reset=0;#3000 $stop;endalways #5 clk=~clk;/*always@(posedge clk)beginup_down={$random}%2;load={$random}%2;din={$random}%256;end*/initialbegin#5;for(i=0;i<256;i=i+3)begindin=i;#10;endendinitialbeginup_down=1;load=1;#20 load=0;#30 load=1;#30 load=0;endalways #200 up_down=~up_down;BinaryCounter bcounter(.counter(counter),.clk(clk),.up_down(up_down),.load(load),.reset(reset),.din(din));endmodule波形图如下:图1 二进制计数器波形图图2 二进制计数器波形图从图像可看出,20s-50s为加计数,50s-80s时load=1,执行置数功能,80s-200s 时up_down=1,为加计数,200s-280s时up_down=0,为减计数。

基于VHDL语言的交通信号灯设计

基于VHDL语言的交通信号灯设计交通信号灯的设计是交通管理中非常重要的一环,通过合理的交通信号灯设计,可以提高道路交通的效率,并保证交通的安全性。

在本文中,将基于VHDL语言设计一个简单的交通信号灯系统,对信号灯进行控制。

首先,我们需要了解交通信号灯的基本原理。

一般情况下,交通信号灯通常分为红灯、黄灯和绿灯三个状态。

每个状态的时间长度可以根据实际情况进行调整。

在设计中,我们将考虑两个十字路口,每个十字路口设置一个交通信号灯。

接下来,我们将使用VHDL语言进行交通信号灯的设计。

首先定义一个信号类型,表示交通灯的三种状态:```vhdltype traffic_light_state is (red, yellow, green);```然后,定义信号灯实体,包括输入信号和输出信号:```vhdlentity traffic_light isportclk: in std_logic;reset: in std_logic;north_south_light: out traffic_light_state;east_west_light: out traffic_light_stateend traffic_light;```在实体中,我们使用了时钟clk和复位信号reset,以确保交通灯的状态按照预期进行转换。

north_south_light和east_west_light是输出信号,表示两个十字路口的交通信号灯状态。

接下来,我们定义信号灯行为。

在时钟上升沿或复位信号为高时,交通灯的状态会发生变化。

我们可以使用一个计数器和状态机来实现交通灯的控制。

当计数器达到一定值时,状态机将更新信号灯的状态。

```vhdlarchitecture behav of traffic_light issignal state: traffic_light_state := red;beginprocess(clk, reset)beginif reset = '1' thencounter <= 0;state <= red;elsif rising_edge(clk) thencounter <= counter + 1;case state iswhen red =>state <= green;counter <= 0;end if;when green =>state <= yellow;counter <= 0;end if;when yellow =>state <= red;counter <= 0;end if;end case;end if;end process;north_south_light <= state; east_west_light <= state; end behav;```最后,我们需要在顶层模块中实例化交通信号灯实体,并提供时钟和复位信号。

交通灯VHDL仿真全代码

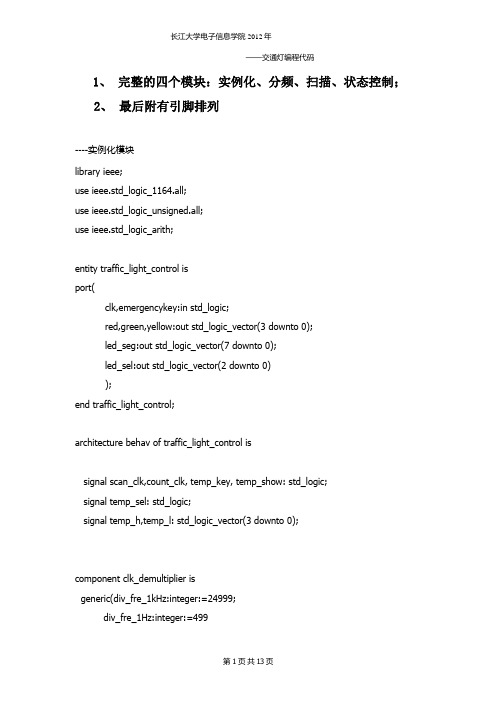

1、完整的四个模块:实例化、分频、扫描、状态控制;2、最后附有引脚排列----实例化模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith;entity traffic_light_control isport(clk,emergencykey:in std_logic;red,green,yellow:out std_logic_vector(3 downto 0);led_seg:out std_logic_vector(7 downto 0);led_sel:out std_logic_vector(2 downto 0));end traffic_light_control;architecture behav of traffic_light_control issignal scan_clk,count_clk, temp_key, temp_show: std_logic;signal temp_sel: std_logic;signal temp_h,temp_l: std_logic_vector(3 downto 0);component clk_demultiplier isgeneric(div_fre_1kHz:integer:=24999;div_fre_1Hz:integer:=499);port(clk:in std_logic;clk_1kHz,clk_1Hz:out std_logic);end component;component scandisplay isport(clk:in std_logic;led_sel:out std_logic_vector(2 downto 0);time_h,time_l:in std_logic_vector(3 downto 0);led_segcode:out std_logic_vector(7 downto 0));end component;component StageControl isport(clk:in std_logic;emergencykey:in std_logic;time_h,time_l:out std_logic_vector(3 downto 0);redlight,greenlight,yellowlight:out std_logic_vector(3 downto 0));end component;beginu0:clk_demultiplier port map(clk=>clk, clk_1kHz=>scan_clk,clk_1Hz=>count_clk);u1:scandisplay port map(clk=>scan_clk,time_h=>temp_h,time_l=>temp_l, led_segcode=>led_seg,led_sel=>led_sel);u2:StageControl port map(clk=>count_clk, emergencykey=>emergencykey, redlight=>red,greenlight=>green,yellowlight=>yellow,time_h=>temp_h, time_l=>temp_l);end behav;-- 分频模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith;entity clk_demultiplier isgeneric(div_fre_1kHz:integer:=24999;--=2;div_fre_1Hz:integer:=999 --=4);port(clk:in std_logic;clk_1kHz,clk_1Hz:buffer std_logic);end entity;architecture behav of clk_demultiplier issignal fre_1kHz:integer range 0 to div_fre_1kHz;signal fre_1Hz:integer range 0 to div_fre_1Hz;beginprocess(clk) --将clk_1kHz =clk/50000 beginif rising_edge(clk) thenif(fre_1kHz>=div_fre_1kHz) then fre_1kHz<=0;clk_1kHz<=not clk_1kHz;elsefre_1kHz<=fre_1kHz+1;end if;end if;end process;process(clk_1kHz)--将clk_1Hz =clk_1kHz/1000 beginif rising_edge(clk_1kHz) thenif(fre_1Hz>=div_fre_1Hz) then fre_1Hz<=0;clk_1Hz<=not clk_1Hz;elsefre_1Hz<=fre_1Hz+1;end if;end if;end process;end behav;--扫描显示模块scandisplaylibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith;entity scandisplay isport(clk:in std_logic;led_sel:out std_logic_vector(2 downto 0); time_h,time_l:in std_logic_vector(3 downto 0); led_segcode:out std_logic_vector(7 downto 0));end scandisplay;architecture behav of scandisplay issignal num_in: std_logic_vector(3 downto 0);signal counter:integer range 0 to 1;-- signal led_chioce:std_logic;-- signal led_sel2:std_logic_vector(2 downto 0);--signal led_sel:std_logic;Beginprocess(clk) --数码管扫描beginif(clk'event and clk='1')thencounter<=counter+1;end if;if counter=1 thennum_in<=time_h;led_sel<="001";elsenum_in<=time_l;led_sel<="000";end if;end process;process(num_in) --显示译码(共阴?共阳)begincase num_in iswhen "0000"=>led_segcode<="00111111";when "0001"=>led_segcode<="00000110";when "0010"=>led_segcode<="01011011";when "0011"=>led_segcode<="01001111";when "0100"=>led_segcode<="01100110";when "0101"=>led_segcode<="01101101";when "0110"=>led_segcode<="01111101";when "0111"=>led_segcode<="00000111";when "1000"=>led_segcode<="01111111";when "1001"=>led_segcode<="01101111";when others=>led_segcode<="00000000";end case;end process;end behav;--StageControl控制模块library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;use ieee.std_logic_arith;entity StageControl isport(clk:in std_logic; --时钟emergencykey:in std_logic; --紧急开关time_h,time_l:out std_logic_vector(3 downto 0); --定时redlight,greenlight,yellowlight:out std_logic_vector(3 downto 0) --红黄绿灯);end StageControl;architecture behav of StageControl istype color is(greenred,yellowred,redgreen,redyellow); --四种状态signal stagechange:std_logic:='0';signal tempr,tempg,tempy:std_logic_vector(3 downto 0);signal temp_h,temp_l:std_logic_vector(3 downto 0);signal temp_color:color:=greenred;beginprocess(clk,emergencykey)variable temp_r,temp_g,temp_y:std_logic_vector(3 downto 0); --三组灯的中间变量variable temph,templ:std_logic_vector(3 downto 0); --定时的中间变量variable tempcolor:color:=greenred; --initial stage --当前状态的中间变量beginif(clk'event and clk='1')thencase emergencykey iswhen '1'=> --the normal stagecase temp_color iswhen greenred=> --initial stagetempr<="1100";tempg<="0011";tempy<="1111";case stagechange iswhen '0' =>temp_h<="0010";temp_l<="0101";stagechange<='1';when others =>case temp_l iswhen "0000"=>temp_l<="1001";temp_h<=temp_h-1;when "0001"=>case temp_h iswhen "0000" =>temp_h<="0000";temp_l<="0000";stagechange<='0';temp_color<=yellowred;when others =>temp_l<="0000";end case;when others=>temp_l<=temp_l-1;end case;end case;when yellowred=> --- Second stagetempr<="1100";tempg<="1111"; --quanmietempy<="0011";case stagechange iswhen '0' =>temp_h<="0000";temp_l<="0101";stagechange<='1';when others =>case temp_l iswhen "0000"=>temp_l<="1001";temp_h<=temp_h-1;when "0001"=>case temp_h iswhen "0000" =>temp_h<="0000";temp_l<="0000";stagechange<='0';temp_color<=redgreen;when others =>temp_l<="0000";end case;when others=>temp_l<=temp_l-1;end case;end case;when redgreen=> --Third stagetempr<="0011";tempg<="1100";tempy<="1111";case stagechange iswhen '0' =>temp_h<="0011";temp_l<="0101";stagechange<='1';when others =>case temp_l iswhen "0000"=>temp_l<="1001";temp_h<=temp_h-1;when "0001"=>case temp_h iswhen "0000" =>temp_h<="0000";temp_l<="0000";stagechange<='0';temp_color<=redyellow;when others =>temp_l<="0000";end case;when others=>temp_l<=temp_l-1;end case;end case;when redyellow=> --Forth stagetempr<="0011";tempg<="1111";tempy<="1100";case stagechange iswhen '0' =>temp_h<="0000";temp_l<="0101";stagechange<='1';when others =>case temp_l iswhen "0000"=>temp_l<="1001";temp_h<=temp_h-1;when "0001"=>case temp_h iswhen "0000" =>temp_h<="0000";temp_l<="0000";stagechange<='0';temp_color<=greenred;when others =>temp_l<="0000";end case;when others=>temp_l<=temp_l-1;end case;end case;end case;when others=> --emergency statetempr<="0000";tempg<="1111";tempy<="1111";--- time_h<=temp_h;-- time_l<=temp_l;--temp_color<=tempcolor;end case;redlight<=tempr;greenlight<=tempg;yellowlight<=tempy;time_h<=temp_h;time_l<=temp_l;end if;end process;end behav;引脚排列图:。

基于VHDL语言的交通灯

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY traffic ISPORT (CLK,R,SP,fault: IN STD_LOGIC;eLIGHT : BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0);--东:绿,黄,红sLIGHT : BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0);--南:绿,黄,红wLIGHT : BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0);--西:绿,黄,红nLIGHT : BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0);--北:绿,黄,红SEL : BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0);Q1,Q2 : OUT INTEGER RANGE 0 TO 24;---------倒计时SMG :OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END traffic ;ARCHITECTURE RT1 OF traffic ISTYPE STATES IS (S0,S1,S2,S3);SIGNAL STATE : STATES ;SIGNAL CLK1HZ:STD_LOGIC;SIGNAL T:INTEGER RANGE 0 TO 10;SIGNAL T1,T2: INTEGER RANGE 0 TO 24;SIGNAL L1,L2,L3,L4 : INTEGER RANGE 0 TO 10;BEGINP1:PROCESS(CLK) ------产生1Hz时钟的分频计数器V ARIABLE cnt : INTEGER RANGE 0 TO 512;BEGINIF CLK='1' AND CLK'EVENT THENIF cnt=511 THEN cnt:=0;ELSEIF cnt<256 THEN CLK1HZ<='1';ELSE CLK1HZ<='0';END IF;cnt:=cnt+1;END IF;END IF;END PROCESS;----------------------------------------------------P2: PROCESS (CLK1HZ,fault,T1,T2,SP,R,eLIGHT(1),sLIGHT(1),wLIGHT(1),nLIGHT(1)) BEGINIF R='1' THEN STA TE<=S0;T1<=16;T2<=19;--初始状态ELSIF SP='1' THEN -------------------紧急状态eLIGHT<="001";sLIGHT<="001";wLIGHT<="001";nLIGHT<="001";STATE<=S0;T1<=16;T2<=19;ELSIF fault='1' THEN-----------------系统出现故障eLIGHT<="010";sLIGHT<="010";wLIGHT<="010";nLIGHT<="010";eLIGHT(1)<=CLK1HZ;sLIGHT(1)<=CLK1HZ;wLIGHT(1)<=CLK1HZ;nLIGHT(1)<=CLK1HZ;STATE<=S0;T1<=16;T2<=19;ELSIF (CLK1HZ'EVENT AND CLK1HZ='1') THEN------正常运行CASE STATE IS--------------------------------------------------------------WHEN S0=> eLIGHT<="001";wLIGHT<="001";--禁东西干道sLIGHT<="100";nLIGHT<="100";--通南北干道T1<=T1-1;T2<=T2-1;Q1<=T1;Q2<=T2;IF T1=0 THENSTATE<=S1;T1<=2;T2<=2;END IF;WHEN S1=> eLIGHT<="001";wLIGHT<="001";sLIGHT<="010";nLIGHT<="010";--南北黄灯T1<=T1-1;T2<=T2-1;Q1<=T1;Q2<=T2;IF T1=0 THENSTATE<=S2;T1<=24;T2<=19;END IF;---------------------------------------------------------------WHEN S2=> eLIGHT<="100";wLIGHT<="100";--通东西干道sLIGHT<="001";nLIGHT<="001";--禁南北干道T1<=T1-1;T2<=T2-1;Q1<=T1;Q2<=T2;IF T2=0 THENSTATE<=S3;T1<=4;T2<=4;END IF;WHEN S3=> eLIGHT<="010";wLIGHT<="010";--东西黄灯sLIGHT<="001";nLIGHT<="001";T1<=T1-1;T2<=T2-1;Q1<=T1;Q2<=T2;IF T1=0 THENSTATE<=S0;T1<=17;T2<=19;END IF;WHEN OTHERS=>STA TE<=S0;T1<=16;T2<=19;END CASE;END IF;L1<=T1/10;L2<=T1 REM 10;--求A干道,十位,个位L3<=T2/10;L4<=T2 REM 10;--求B干道,十位,个位END PROCESS;---------------------------------------------------------------------- P3:PROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1' THENSEL<=SEL+1;END IF;END PROCESS;--------------------------------------------------------P4:PROCESS(SEL,T,STATE,L1,L2,L3,L4)BEGINif (STATE=S0 OR STA TE=S1) THENCASE SEL ISWHEN "000" => T<=L2;WHEN "001" => T<=L1;WHEN OTHERS =>T<=10;END CASE;END IF;IF (STATE=S2 OR STA TE=S3) THENCASE SEL ISWHEN "010" => T<=L4;WHEN "011" => T<=L3;WHEN OTHERS =>T<=10;END CASE;END IF;END PROCESS;--------------------------------------------------------P5:PROCESS(T)BEGINCASE T ISWHEN 0=>SMG<="01111110";WHEN 1=>SMG<="00110000";WHEN 2=>SMG<="01101101";WHEN 3=>SMG<="01111001";WHEN 4=>SMG<="00110011";WHEN 5=>SMG<="01011011";WHEN 6=>SMG<="00011111";WHEN 7=>SMG<="01110000";WHEN 8=>SMG<="01111111";WHEN 9=>SMG<="01110011";WHEN OTHERS=> SMG<="00000000";END CASE;END PROCESS;END RT1;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

--希望大家把有用的代码上传,共同学习交流--traffic_control,红绿灯交通控制library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity traffic_control isport( clk,rst: in std_logic;seg_bit:out std_logic_vector(1 downto 0);decode:out std_logic_vector(7 downto 0);ledcol:out std_logic_vector(2 downto 0); --南北方向控制ledrow:out std_logic_vector(2 downto 0) --东西方向控制);end entity traffic_control;architecture fms of traffic_control istype traffic_state is (s0,s1,s2,s3);type seg_state is(seg_s0,seg_s1);signal cs,ns:seg_state;signal current_state,next_state:traffic_state;signal fdiv:std_logic;signal seg_fdiv:std_logic;signal code:integer range 0 to 30;signal seg_in:integer range 0 to 30;signal countout:integer range 0 to 50;signal longcount1,longcount2,shortcount1,shortcount2:std_logic; begin--50M时钟分频为1Hz,即1s--50,000,000process(clk)variable aa: integer range 0 to 50000000;beginif clk'event and clk='1' then--if aa=49999999 then aa:=0;------需要的赋值if aa=4 then aa:=0;----测试仿真测试值else aa:=aa+1;end if;end if;--if aa<25000000 then fdiv <= '1';----真实值if aa<2 then fdiv <= '1';----------仿真值else fdiv <='0';end if;end process;--分频模块,产生5ms脉冲:250,000/50,000,000 =0.005S process(clk)variable bb: integer range 0 to 250000;beginif clk'event and clk='1' then--if bb=249999 then bb:=0;------需要的赋值if bb=4 then bb:=0;----测试仿真测试值else bb:=bb+1;end if;end if;--if bb<125000 then fdiv <= '1';----真实值if bb<2 then seg_fdiv <= '1';----------仿真值else seg_fdiv <='0';end if;end process;--计数输出后用于数码管显示process(countout)beginif countout>30 then seg_in<=(countout-30);elsif countout>0 then seg_in<=countout;else seg_in<=0;end if;end process;--状态机实现数码管显示十位与各位process(seg_fdiv,rst)beginif rst='0' then cs <=seg_s0;elsif seg_fdiv'event and seg_fdiv='1'thencs<=ns;end if;end process;--根据计数值显示在数码管process(cs,seg_in)begincase cs iswhen seg_s0 => seg_bit(0)<='0';seg_bit(1)<='1'; code<=(seg_in / 10);if cs= seg_s0 then ns<=seg_s1;else ns<=seg_s0;end if;when seg_s1 => seg_bit(0)<='1';seg_bit(1)<='0'; code<=(seg_in rem 10);if cs= seg_s1 then ns<=seg_s0;else ns<=seg_s1;end if;when others=> cs<=seg_s0;end case;end process;--七段码段译码process(code,rst)beginif rst='0' then decode<="10010000";elsecase code is------------------------------ 共阳极共阴极when 0 => decode <= "10010000";-- 0x90;0 0110 1111 -- 0x6fwhen 1 => decode <= "10011111";-- 0x9f;1 0110 0000 -- 0x60when 2 => decode <= "01011000";-- 0x58 2 1010 0111 -- 0xa7when 3 => decode <= "00011001";-- 0x19 3 1110 0110 -- 0xe6when 4 => decode <= "00010111";-- 0x17;4 1110 1000 -- 0xe8when 5 => decode <= "00110001";-- ox31;5 1100 1110 -- 0xcewhen 6 => decode <= "00110000";-- 0x30;6 1100 1111 -- 0xcfwhen 7 => decode <= "10011101";-- 0x9d;7 0110 0010 -- 0x62when 8 => decode <= "00010000";-- 0x10;8 1110 1111 -- 0xefwhen 9 => decode <= "00010001";-- 0x11;9 1110 1110 -- 0xee-- when "1010" => decode <= "00010100";-- 0x14;a-- when "1011" => decode <= "00110010";-- ox32;b-- when "1100" => decode <= "11110000";-- 0xf0;c-- when "1101" => decode <= "00011010";-- 0x1a;d-- when "1110" => decode <= "01110000";-- 0x70;e-- when "1111" => decode <= "01110100";-- 0x74;fwhen others =>null;end case;end if;end process;--40进制计数process (fdiv)variable cc:std_logic_vector(1 downto 0) ;variable count:integer range 0 to 50 ;beginif fdiv'event and fdiv='1' then--if count=0 then count:=50;--else count:=count-1; --计时50sif count=0 then count:=8 ;else count:=count-1;end if;countout<=count; --变量输出进程--if count<20 then longcount1<='1';if count>5 then longcount1<='1';--测试else longcount1<='0';end if;--if count>19 and count<23 then shortcount1<='1';if count>4 and count<6 then shortcount1<='1';--测试else shortcount1<='0';end if;--if count>22 and count<53 then longcount2<='1';if count>2 and count<5 then longcount2<='1';--测试else longcount2<='0';end if;--if count>52 then shortcount2<='1';--测试if count<2 then shortcount2<='1';else shortcount2<='0';end if;end if;end process;--状态机时序进程process(clk,rst)beginif rst='0' then current_state <=s0;elsif clk'event and clk='1'thencurrent_state<=next_state;end if;end process;--1.*绿* 红** 24;2.**黄红*黄15;3. 红** *绿* 42;4. 红*黄**黄;51--状态机控制四种状态装换,通过current_state与计时信号同时决定---默认状态编码process(current_state,next_state,longcount1,longcount2,shortcount1,shortcount2) begincase current_state iswhen s0 => ledcol<="010";ledrow<="100";if current_state=s0 and longcount1='1' then next_state<=s1;else next_state<=s0;end if;when s1 => ledcol<="001";ledrow<="101";if current_state=s1 and shortcount1='1' then next_state<=s2;else next_state<=s1;end if;when s2 => ledcol<="100";ledrow<="010";if current_state=s2 and longcount2='1' then next_state<=s3;else next_state<=s2;end if;when s3 => ledcol<="101";ledrow<="001";if current_state=s3 and shortcount2='1' then next_state<=s0;else next_state<=s3;end if;when others => next_state<=s0;end case;end process;end architecture fms;。