串口JTAG使用说明

AVR单片机JTAG接口的使用方法

AVR单片机JTAG接口的使用方法AVR单片机JTAG(Joint Test Action Group)接口是一种用于单片机的调试和编程工具。

它提供了一种高效的方式来进行硬件调试、固件编程和软件调试。

在本文中,我将详细介绍AVR单片机JTAG接口的使用方法。

1.JTAG接口简介JTAG接口由四条线组成,分别是TCK(时钟线)、TMS(状态线)、TDI(数据输入线)和TDO(数据输出线)。

它是一种串行接口,用于与其他外设进行通信。

JTAG接口能够通过硬件调试、固件编程和软件调试来提高系统调试的效率。

2.JTAG接口的初始化在使用JTAG接口之前,需要对其进行初始化。

首先,需要确定使用的JTAG接口类型,然后根据类型选择与之匹配的调试工具和软件。

接下来,需要连接JTAG接口的四个引脚到单片机的相应引脚上。

通常,这些引脚在单片机的数据手册中有详细的说明。

3.JTAG接口的连接连接JTAG接口的四个引脚到单片机的相应引脚上,确保连接正确无误。

通常,TCK(时钟线)和TMS(状态线)引脚是共享的,它们分别连接到单片机的相应引脚上。

TDI(数据输入线)和TDO(数据输出线)引脚则是分别连接到单片机的相应引脚上。

请务必根据单片机的数据手册正确连接JTAG接口引脚。

4.JTAG接口的编程在使用JTAG接口进行编程之前,需要确保已经安装了合适的调试工具和软件。

这些工具和软件可以帮助我们完成对单片机的编程操作。

通常,这些工具和软件提供了一些简单的命令和接口,用于与单片机进行通信。

通过这些命令和接口,我们可以读取和写入单片机的内部寄存器,从而实现对单片机的编程操作。

5.JTAG接口的调试使用JTAG接口进行调试可以帮助我们找到系统中的错误和问题。

通过读取和写入单片机的内部寄存器,我们可以查看程序的执行状态、输入和输出数据、栈的使用情况等信息。

通过这些信息,我们可以判断程序中的错误和问题,并进行调试操作。

6.JTAG接口的注意事项在使用JTAG接口之前-确保JTAG接口的引脚连接正确无误,避免引脚连接错误导致的通信问题。

JTAG仿真器使用方法图文教程

JTAG仿真器使⽤⽅法图⽂教程本⽂主要介绍USBJTAG的使⽤⽅法,该仿真器既可以⽤做JTAG放着器给AVR芯⽚下载程序以及仿真,也可以⽤来给STC89C系列的芯⽚下载程序。

本⽂主要分为以下⼏个部分:JTAG简介、AVRJTAG仿真器⼯作原理、JTAG仿真器上的跳线设置、JTAG驱动安装、JTAG仿真器的验证。

1、什么是JTAG仿真器JTAG仿真器,也叫JTAG调试器,即⼀种采⽤JTAG协议进⾏调试和下载的器件。

JTAG也是⼀种国际标准测试协议(IEEE 1149.1兼容),主要⽤于芯⽚内部测试。

现在多数的⾼级器件都⽀持JTAG协议,如DSP、FPGA器件等。

标准的JTAG接⼝是4线:TMS(模式选择)、TCK(时钟)、TDI(数据输⼊)、TDO(数据输出)。

相关JTAG引脚的定义为:TCK为测试时钟输⼊;TDI为测试数据输⼊,数据通过TDI引脚输⼊JTAG接⼝;TDO为测试数据输出,数据通过TDO引脚从JTAG 接⼝输出;TMS为测试模式选择,TMS⽤来设置JTAG接⼝处于某种特定的测试模式;TRST为测试复位,输⼊引脚,低电平有效。

这⾥主要介绍的是AVR的JTAG仿真器,由于每个器件对应的上位机软件(PC上运⾏的软件)实现⽅式不同,所以不同器件的JTAG仿真器是不能够通⽤的。

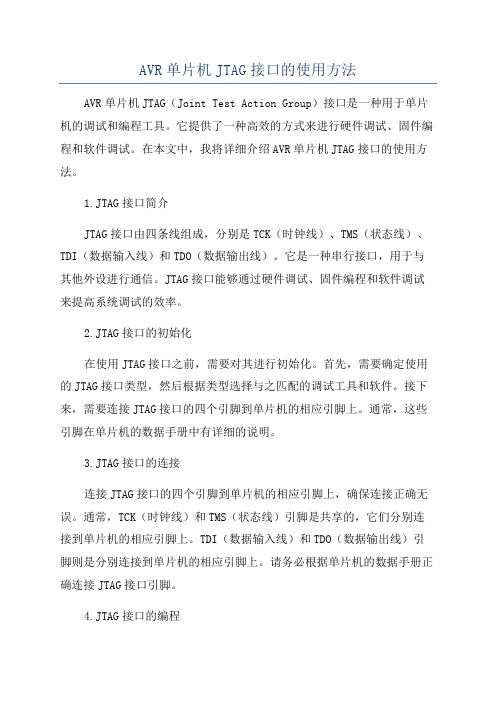

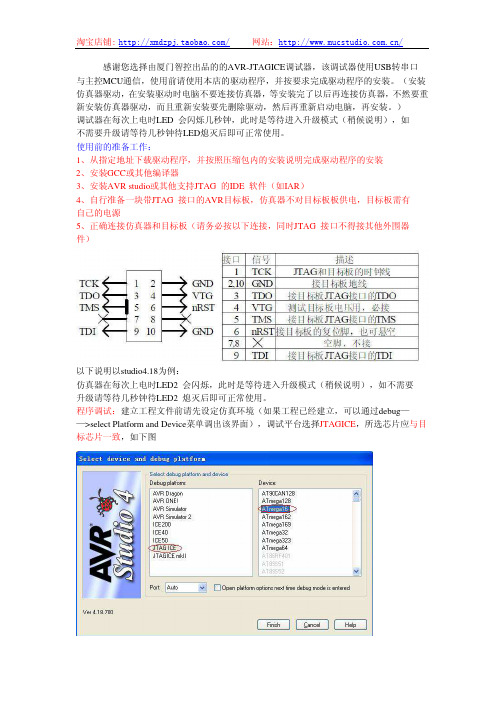

AVR使⽤的JTAG接⼝是4线接⼝,但是现在⽹上普遍流⾏的做法是,在JTAG接⼝中加⼊AVR器件的复位(RST)引脚,2个电源引脚(VCC)、2个地引脚(GND)、⼀个空引脚(NC)⼀共是10个引脚,并且这10个引脚有固定的引脚排序。

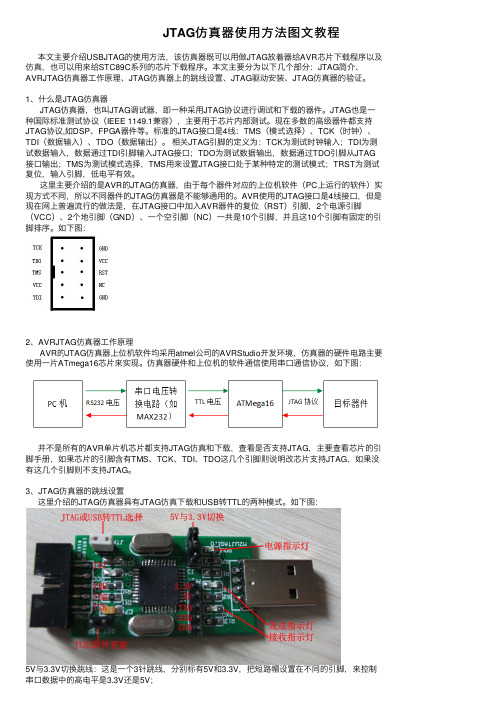

如下图:2、AVRJTAG仿真器⼯作原理AVR的JTAG仿真器上位机软件均采⽤atmel公司的AVRStudio开发环境,仿真器的硬件电路主要使⽤⼀⽚ATmega16芯⽚来实现。

仿真器硬件和上位机的软件通信使⽤串⼝通信协议,如下图:并不是所有的AVR单⽚机芯⽚都⽀持JTAG仿真和下载,查看是否⽀持JTAG,主要查看芯⽚的引脚⼿册,如果芯⽚的引脚含有TMS、TCK、TDI、TDO这⼏个引脚则说明改芯⽚⽀持JTAG,如果没有这⼏个引脚则不⽀持JTAG。

jtag工作原理详解

jtag工作原理详解JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它提供了一种通用的、标准化的方法来访问集成电路内部的信号和寄存器,以便进行测试、调试和编程操作。

本文将详细介绍JTAG工作原理,包括JTAG的基本原理、信号传输方式、测试模式和操作流程等。

一、JTAG的基本原理JTAG是一种串行接口,它使用了四根信号线(TCK、TMS、TDI、TDO)来实现与目标芯片的通信。

其中,TCK(Test Clock)是测试时钟信号,用于同步数据传输;TMS(Test Mode Select)是测试模式选择信号,用于控制JTAG状态机的状态转换;TDI(Test Data Input)是测试数据输入信号,用于向目标芯片发送测试数据;TDO(Test Data Output)是测试数据输出信号,用于从目标芯片读取测试结果。

二、信号传输方式JTAG使用的是一种称为“链式扫描”(Scan Chain)的方式来传输数据。

在链式扫描中,所有的目标芯片连接成一个长链,每个芯片都有一个扫描链(Scan Chain)用于传输数据。

通过控制TMS信号,可以选择要操作的芯片,并将数据从一个芯片传递到下一个芯片。

三、测试模式JTAG定义了多种测试模式,包括测试、调试和编程模式等。

其中,测试模式用于对芯片进行功能测试和故障诊断;调试模式用于对芯片进行调试和性能分析;编程模式用于对芯片进行编程操作。

在测试模式下,可以通过JTAG接口对芯片内部的寄存器进行读写操作,以验证芯片的功能是否正常。

通过设置不同的测试模式,可以选择要测试的功能模块,并将测试数据传递到目标芯片进行测试。

四、操作流程JTAG的操作流程通常包括以下几个步骤:1. 初始化:将JTAG状态机设置为测试模式,并将目标芯片复位到初始状态。

2. 选择目标芯片:通过控制TMS信号,选择要操作的目标芯片。

3. 设置测试模式:通过控制TMS和TDI信号,设置目标芯片的测试模式。

什么是JTAG及其使用方法

什么是JTAG及其使用方法JTAG(Joint Test Action Group)是一种用于测试和调试电子设备的接口和协议标准。

它最初是由一组芯片制造商于1985年共同开发的,并被广泛应用于各种数字电路和嵌入式系统中。

JTAG可以通过一组标准的测试和调试功能,提供对目标设备内部电路的控制和观察。

JTAG的使用方法包括以下几个方面:1.设备连接:使用JTAG接口连接目标设备和测试设备。

JTAG接口通常由四个线路组成,即TCK(时钟)、TMS(状态机控制)、TDI(数据输入)和TDO(数据输出)。

这些线路通过专门的JTAG连接器或引脚与目标设备连接。

2.设备识别:测试设备通过JTAG接口与目标设备通信,并识别目标设备的类型和功能。

这通常是通过发送一系列特定的指令和信号来实现的。

目标设备需要支持JTAG协议,并在芯片内部集成了JTAG控制逻辑。

3.测试模式:JTAG可以让我们在目标设备的测试模式下运行和测试其内部电路。

在测试模式下,我们可以检查和修改目标设备内部各个电路的状态和数据。

测试模式通常使用状态机来控制目标设备的测试流程。

4.调试功能:JTAG还提供了强大的调试功能,允许工程师监视和控制目标设备的执行过程。

通过JTAG接口,我们可以在目标设备运行的任何时候停止执行,并检查寄存器、内存和其他关键数据。

同时,我们还可以通过JTAG接口修改寄存器和内存中的数据,以调试软件和硬件问题。

5.效能测试:除了测试和调试功能之外,JTAG还可以用于测试目标设备的性能和效能。

通过发送特定的信号和指令,我们可以控制目标设备的工作频率、电压和其他工作参数,以评估其在不同工作条件下的性能。

需要注意的是,JTAG只是一个接口标准和协议,而实现JTAG功能的具体硬件和软件可能因厂商和设备类型而有所差异。

因此,在实际使用JTAG之前,我们需要了解目标设备的JTAG接口规格和支持的JTAG功能。

总之,JTAG是一种强大而灵活的测试和调试接口,它能够帮助我们识别和解决各种硬件和软件问题。

jtagapb用法

jtagapb用法摘要:1.JTAG简介2.APB简介3.JTAG与APB的结合:JTAG-APB4.JTAG-APB的使用方法5.实例演示6.注意事项正文:JTAG(Joint Test Action Group,联合测试行动组)和APB(Advanced Peripheral Bus,高级外围总线)是两种硬件调试和编程接口,它们在嵌入式系统开发中广泛应用。

JTAG主要用于芯片内部测试,而APB则用于芯片内部各个模块之间的通信。

当这两者结合时,它们为开发者提供了一种强大的硬件调试和编程解决方案。

本文将详细介绍JTAG-APB的使用方法。

1.JTAG简介JTAG是一种用于测试和调试硬件的标准接口,它最初由英国公司Philips Semiconductors于1990年代研发。

JTAG接口主要有四根线:TMS(Test Mode Select,测试模式选择)、TDI(Test Data In,测试数据输入)、TDO (Test Data Out,测试数据输出)和TCK(Test Clock,测试时钟)。

通过这些线路,JTAG提供了一种可靠的方法来访问和控制芯片内部的各种寄存器和逻辑。

2.APB简介APB是一种高性能、低延迟的总线接口,用于芯片内部各个模块之间的通信。

它由两根数据线(A和B)和一根时钟线(CLK)组成。

APB支持同步和异步传输,数据传输速率较高,可满足大多数嵌入式系统的需求。

3.JTAG与APB的结合:JTAG-APB当JTAG和APB结合时,开发者可以利用JTAG接口进行硬件调试,同时通过APB接口实现芯片内部模块之间的通信。

这为开发者提供了一种便捷的方式,可以在调试过程中实时观察和控制芯片的运行状态。

4.JTAG-APB的使用方法要使用JTAG-APB,首先需要配置相应的硬件和软件环境。

这包括:- 硬件:具有JTAG和APB接口的芯片- 软件:支持JTAG-APB的调试工具和驱动程序使用JTAG-APB时,可分为以下几个步骤:1)连接硬件:将JTAG和APB接口连接到开发板上。

串口JTAG使用说明

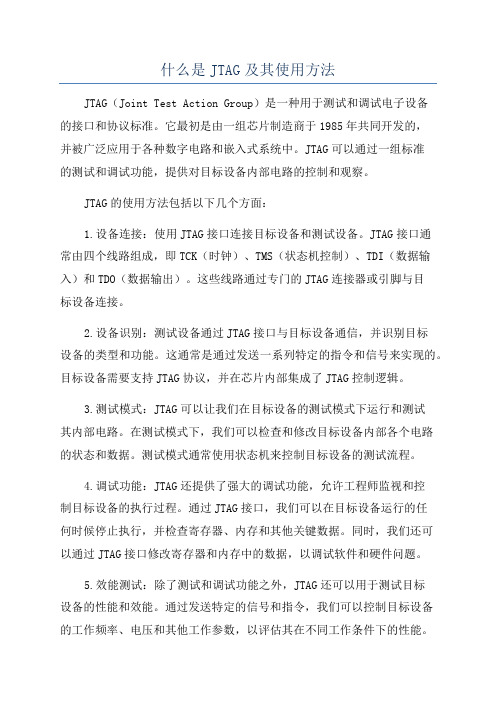

AVR JTAG下载HEX文件使用说明本文只介绍AVR JTAG下载HEX文件在AVR Studio环境下的下载方法,推荐使用。

并口下载线主要优点是电路简单,缺点主要有下载速度慢、不能在AVR Studio环境下使用。

具体差别在用了AVR JTAG 之后就知道了,现在一个标准的下载线也只要几十块钱和并口下载线没什么差别了。

此处所说的STK500下载线和AVR ISP下载线同属一类,它们使用相同的通信协议,STK500确切的说是一个学习板,AVR JTAG才是真正意义上的下载线。

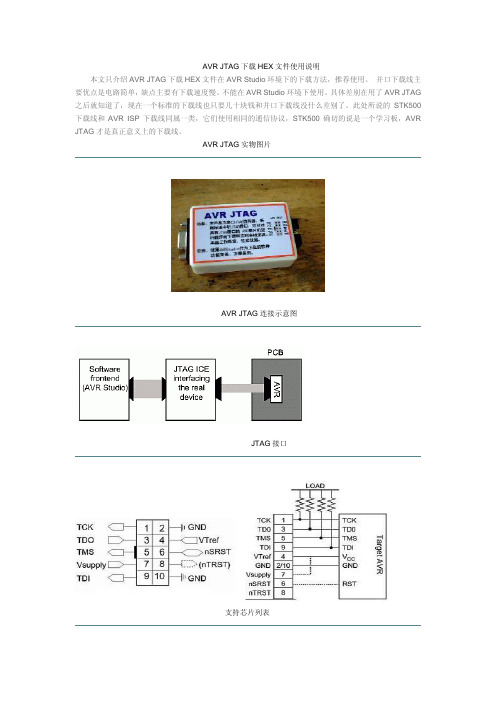

AVR JTAG实物图片AVR JTAG连接示意图JTAG接口支持芯片列表AVR JTAG下载线支持芯片型号非常多,这里就不一一列出了,只要AVR芯片支持ISP下载的都可以。

AVR JTAG下载HEX文件-操作方法:1、打开AVR Studio 软件,按下图操作。

2、在这里选择所用器件及连接端口,选择JTAG ICE,自动检测端口,点击Connect进入下一步。

3、下面窗口提示所用AVR ISP下载线固件版本与当前所用软件不同,提示要求升级AVR ISP下载线固件,如版本相同就不会出现下面的提示。

如你所用的AVR ISP下载线不支持在线升级功能的话,不要点确定要不AVR ISP下载线会死在那里不动了,直接点击取消跳过此步既可。

4、正常会进入下面编程(Program)界面。

主要包括有器件(Device)、编程模式(Programming mode)、Flash下载、EEPROM下载几个部分,最下面部分是信息窗口。

器件:用于选择器件和手工擦除器件。

编程模式:用于选择ISP和并口下载模式,由于此处用的是AVR JTAG下载线只支持ISP方式下载。

Erase Device Before擦除器件,选中此项在每次下载前会对将器件擦除。

需要同时烧写用户程序和引导程序时需要注意此处,正常情况下需选中此项。

Verify Devic写入校验,默认为选中。

fpga jtag手册

fpga jtag手册

FPGA JTAG接口是一种串行接口,用于对FPGA内部逻辑进行调试、配置和测试等功能。

以下是FPGA JTAG接口的基本使用手册:

连接方式:将JTAG电缆的一端连接到FPGA开发板上的JTAG接口,另一端连接到PC上的JTAG调试器。

确保连接稳定,避免在调试过程中出现断线或接触不良的情况。

配置JTAG接口:在开始调试之前,需要配置JTAG接口的参数,例如波特率、数据位、停止位等。

这些参数需要根据目标FPGA设备和JTAG调试器的要求进行设置。

启动调试:打开JTAG调试器软件,选择正确的设备型号和连接方式,然后点击“开始调试”按钮。

此时,调试器将与目标FPGA建立通信连接,并进入调试状态。

加载配置文件:在调试过程中,可能需要将配置文件加载到目标FPGA中。

可以通过JTAG接口将配置文件传输到目标FPGA中,或者在调试器软件中选择相应的配置文件进行加载。

运行和停止调试:在调试过程中,可以通过调试器软件控制目标FPGA的运行和停止。

可以单步执行、步进执行或全速运行目标FPGA的程序。

同时,还可以在调试过程中设置断点、观察寄存器和内存等操作。

结束调试:当调试完成后,可以通过调试器软件结束调试会话,并关闭JTAG接口的连接。

需要注意的是,使用FPGA JTAG接口进行调试需要一定的技术背景和经验。

在调试过程中,需要仔细检查连接线和设备参数设置,避免出现通信错误或配置错误等问题。

同时,也需要遵守相关的安全操作规程,确保不会损坏目标FPGA 或造成其他安全问题。

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM (OCM)和使用DDR3两种情况。

JTAG方式JTAG方式是调试中最常用的方式,在SDK中在Project Explorer窗口工程上右键-Debug As-Debug ConfiguraTIons可以看到以下窗口首次打开左边窗口中Xilinx C/C++ applicaTIon(GDB)下没有子项,这时双击Xilinx C/C++ applicaTIon(GDB)即可新建一个调试;这时右边窗口会自动填充如上图,若没有则手动填入;在右边ApplicaTIon窗口指定要下载调试的.elf文件;在右边STDIO Connection可以指定标准输入输出串口,即printf打印串口,若这里选择开发板上uart的com口,则调试时printf的信息打印到调试时Console窗口,同时也可从Console窗口输入数据,以此将数据通过串口发送到开发板上以上设置完成后点击Debug即可开始调试;若以上在Project Explorer窗口工程上右键-Run As-Run Configurations;配置与此类似,最后点击run即可开始运行,只是不是调试而是直接上板运行。

只用OCM只用OCM指不使用DDR3的方式,与使用DDR3的方式略有不同。

这里不用FSBL来加载PL部分的.bit文件和第二阶段启动程序(裸机程序),而直接用BootROM加载裸机程序到OCM,即将裸机程序当做FSBL来运行,当然还要以下处理才可以:包含进头文件:#include ps7_init.h在裸机程序main函数开始处调用:ps7_init()从design_1_wrapper_hw_platform_1目录复制ps7_init.c和ps7_init.h文件到裸机程序所在的src目录中注意:这里样调用ps7_init()只适用于只用OCM的情况,经测试打开DDR3后再这样调用会在ps7_init()中初始化失败,调试发现在初始化PLL时失败(原因未知)。

JTAG使用说明

JTAG使用说明遵循JTAG的器件包含以下几个管脚TCK 测试时钟输入,它和系统时钟不同TDI测试数据输入,通过它数据移位进入器件TDO测试数据输出,通过它数据从器件移出TMS测试模式选择,在JTAG规范中TMS命令选择测试模式TRST测试复位输入,它为TAP控制器提供异步初始化器件的测试支持功能是通过TAP控制器来实现的。

TAP是一个状态机,它控制控制所有相关操作,每种遵循JTAG的器件都有自己的TAP控制器,通过TCK和TMS可以使状态机内部的状态发生变化,从而支持诸如断点、单步、内部观察等调试工作。

本章针对ARM7TDMI介绍调试结构。

ARM的调试体系采用协议转换器来使调试器通过JTAG与ARM核直接通信。

前面JTAG标准中提到的扫描链功能是测试用,这里把它作为调试用:捕获数据总线上的信号并向内核或存储器插入新的信息。

ARM7TDMI-S核内具有EmbeddedICE逻辑,EmbeddedICE逻辑提供对片内调试的支持。

调试指令直接通过扫描链插入ARM内核并执行。

根据插入调试指令的不同,内核可以处于观察、保存或改变状态。

ARM的调试体系可以使程序指令执行速度处于调试速度或全速运行。

在ARM中采用JTAG的特点是:通过JTAG接口可以观察ARM内核状态和系统状态(注意:系统状态包括片内外设,不同于内核状态);不占用额外的目标系统资源;提供传统的断点访问和观察点访问;不再需要另外的UART端口来和监控程序通信。

围绕ARM内核有两个扫描链:围绕整个内核外围的一个扫描链以及仅仅覆盖数据总线和断点的扫描链。

由于后者的链比较短,从而使调试指令和数据可以快速插入内核,避免了额外的时间ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

jtagulator使用方法

jtagulator使用方法

JTAGulator是一种用于识别和定位JTAG接口的工具,它可以

帮助工程师和安全研究人员在硬件设备上找到JTAG接口,并进行进

一步的分析和破解。

以下是关于JTAGulator的使用方法的详细介绍:

1. 连接硬件设备,首先,将JTAGulator通过USB线缆连接到

计算机上。

然后,使用导线将JTAGulator的引脚连接到目标设备上

的JTAG接口。

2. 配置JTAGulator,打开JTAGulator的控制软件,并根据目

标设备的JTAG接口类型和引脚布局进行相应的配置。

这通常需要参

考目标设备的硬件手册或相关资料。

3. 执行扫描,在软件界面上设置扫描参数,然后启动扫描。

JTAGulator将尝试不同的引脚组合,以确定目标设备上JTAG接口

的位置和布局。

4. 分析扫描结果,一旦扫描完成,软件将显示找到的JTAG接

口信息,包括引脚布局、电压和信号强度等。

分析这些信息可以帮

助确定正确的JTAG接口连接方式。

5. 进行进一步的研究,一旦JTAG接口被确定,可以使用JTAGulator或其他工具进行后续的JTAG调试、固件破解或安全分析工作。

除了上述步骤,使用JTAGulator还需要对硬件设备和JTAG接口有一定的了解,以便正确地配置和解释扫描结果。

此外,还需要谨慎操作,以避免对目标设备造成损坏。

总而言之,JTAGulator是一款强大的工具,可以帮助用户快速而准确地定位JTAG接口,但使用时需要谨慎并且需要一定的硬件和JTAG知识作为基础。

AVR-JTGAICE使用说明

感谢您选择由厦门智控出品的的AVR-JTAGICE调试器,该调试器使用USB转串口 与主控MCU通信,使用前请使用本店的驱动程序,并按要求完成驱动程序的安装。

(安装仿真器驱动,在安装驱动时电脑不要连接仿真器,等安装完了以后再连接仿真器,不然要重新安装仿真器驱动,而且重新安装要先删除驱动,然后再重新启动电脑,再安装。

)调试器在每次上电时LED 会闪烁几秒钟,此时是等待进入升级模式(稍候说明),如不需要升级请等待几秒钟待LED熄灭后即可正常使用。

使用前的准备工作:1、从指定地址下载驱动程序,并按照压缩包内的安装说明完成驱动程序的安装2、安装GCC或其他编译器3、安装AVR studio或其他支持JTAG 的IDE 软件(如IAR)4、自行准备一块带JTAG 接口的AVR目标板,仿真器不对目标板板供电,目标板需有自己的电源5、正确连接仿真器和目标板(请务必按以下连接,同时JTAG 接口不得接其他外围器 件)以下说明以studio4.18为例:仿真器在每次上电时LED2 会闪烁,此时是等待进入升级模式(稍候说明),如不需要升级请等待几秒钟待LED2 熄灭后即可正常使用。

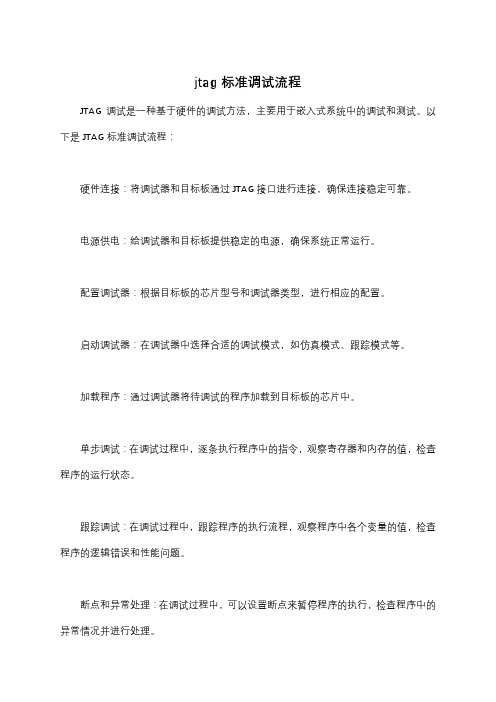

程序调试:建立工程文件前请先设定仿真环境(如果工程已经建立,可以通过debug— —>select Platform and Device菜单调出该界面),调试平台选择JTAGICE,所选芯片应与目 标芯片一致,如下图程序调试:程序编译完后选择Debug菜单下的Start Debugging 进入调试,调试器将把编译好的程序下载到目标芯片中进行仿真,该过程视实际程序的大小需要不同的时间。

以下是debug菜单的简要说明(摘自OURAVR)Auto Step 自动执行它能重复执行指令。

如果当前处于source 方式时(即C 语言窗口显示方式),一条的指令会被执行。

如果处理disassembly 方式 (即显示为汇编指令方式),一条汇编指令会被执 行。

jtag标准调试流程

jtag标准调试流程

JTAG调试是一种基于硬件的调试方法,主要用于嵌入式系统中的调试和测试。

以下是JTAG标准调试流程:

硬件连接:将调试器和目标板通过JTAG接口进行连接,确保连接稳定可靠。

电源供电:给调试器和目标板提供稳定的电源,确保系统正常运行。

配置调试器:根据目标板的芯片型号和调试器类型,进行相应的配置。

启动调试器:在调试器中选择合适的调试模式,如仿真模式、跟踪模式等。

加载程序:通过调试器将待调试的程序加载到目标板的芯片中。

单步调试:在调试过程中,逐条执行程序中的指令,观察寄存器和内存的值,检查程序的运行状态。

跟踪调试:在调试过程中,跟踪程序的执行流程,观察程序中各个变量的值,检查程序的逻辑错误和性能问题。

断点和异常处理:在调试过程中,可以设置断点来暂停程序的执行,检查程序中的异常情况并进行处理。

结束调试:当调试完成后,断开调试器和目标板的连接,关闭电源。

需要注意的是,JTAG调试需要对硬件和软件都有一定的了解,需要熟悉目标板的芯片型号、电路原理和程序代码。

同时,调试过程中需要耐心和细心,逐一排查问题并解决问题。

以上是JTAG标准调试流程的简要介绍,具体的调试方法和步骤可能因不同的工具和场景而有所不同。

JTAG ICE 使用说明书

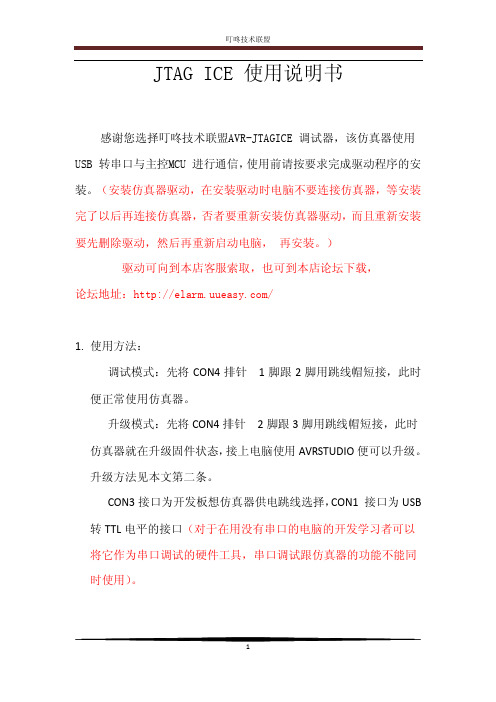

JTAG ICE 使用说明书感谢您选择叮咚技术联盟AVR-JTAGICE 调试器,该仿真器使用USB 转串口与主控MCU 进行通信,使用前请按要求完成驱动程序的安装。

(安装仿真器驱动,在安装驱动时电脑不要连接仿真器,等安装完了以后再连接仿真器,否者要重新安装仿真器驱动,而且重新安装要先删除驱动,然后再重新启动电脑,再安装。

)驱动可向到本店客服索取,也可到本店论坛下载,论坛地址:/1.使用方法:调试模式:先将CON4排针1脚跟2脚用跳线帽短接,此时便正常使用仿真器。

升级模式:先将CON4排针2脚跟3脚用跳线帽短接,此时仿真器就在升级固件状态,接上电脑使用AVRSTUDIO便可以升级。

升级方法见本文第二条。

CON3接口为开发板想仿真器供电跳线选择,CON1 接口为USB 转TTL电平的接口(对于在用没有串口的电脑的开发学习者可以将它作为串口调试的硬件工具,串口调试跟仿真器的功能不能同时使用)。

2.升级方法该JTAG 使用studio 本身的固件(版本4.17),与studio 有最大的兼容性,支持AVRstudio 固件升级。

(AVRstudio 4.17 可向我们客服索取也可到网上下载)将CON3排针的 2脚跟3脚用跳线帽短接,点击Tools->AVR Prog…如下图:打开AVRprog 后点击Browse…,找到studio 安装目录下JTAGICE 文件夹内的Upgrade.ebn 文件,然后选中flash 项的program 就把新的固件下载到JTAGICE 本身的芯片中了。

如下图:待固件升级完毕,对JTAGICE 从新上电,到此固件升级完毕,便可以用新固件进行调试。

3.支持芯片清单为:(不同版本可能支持不同芯片)Atmega16,Atmega162,Atmega169,Atmega32,Atmega323,Atmega64 ,Atmega128,AT90CAN128.3.AVRstudio配合JTAG ICE 的调试仿真使用说明,见AVRstudio使用说明书。

JTAG与MAX232的说明

MAX232max232是一种把电脑的串行口rs232信号电平(-10 ,+10v)转换为单片机所用到的TTL 信号点平(0 ,+5)的芯片,下面我来介绍一下max232引脚图以及max232和电脑串口的连接电路,RS232引脚定义。

max232《RS232引脚定义》引脚定义符号1 载波检测DCD2 接收数据RXD3 发送数据TXD4 数据终端准备好DTR5 信号地SG6 数据准备好DSR7 请求发送RTS8 清除发送CTS9 振铃提示RIMAX232获得正负电源的另一种方法在单片机控制系统中,我们时常要用到数/模(D/A)或者模/数(A/D)变换以及其它的模拟接口电路,这里面要经常用到正负电源,例如:9V,-9V; 12V,-12V.这些电源仅仅作为数字和模拟控制转换接口部件的小功率电源。

在控制板上,我们有的只是5V电源,可又有很多方法获得非5V电源。

1.外接;2.DC-DC变换......在这里我介绍一块大家常用的芯片:MAX232. MAX232是TTL--RS232电平转换的典型芯片,按照芯片的推荐电路,取振荡电容为uF的时候,若输入为5V,输出可以达到-14V左右,输入为0V ,输出可以达到14V,在扇出电流为20mA的时候,处处电压可以稳定在12V和-12V.因此,在功耗不是很大的情况下,可以将MAX232的输出信号经稳压块后作电源使用。

我在网上搜索了一些232的例程,但用单片机向PC发数据的程序较少,所有自己无耐,写了该程序用于测试芯片有没有正常工作,希望能给有需要的朋友带来点方便!#include<pic.h> //包含单片机内部资源预定义__CONFIG(0x3F52); //4M晶体HS振荡/*********************************************************************** ********延时1MS 带参数(int)子程序************************************************************************ *******/void delay (unsigned int time){unsigned int a,b;for(a=0;a<time;a++){for(b=0;b<88;b++);}}//主程序void main(){unsigned charstring[]={0xBB,0xB6,0xD3,0xAD,0xB9,0xE2,0xC1,0xD9,0xC1,0xD6,0xBE,0xA9,0xBF,0xC6 ,0xBC,0xBC,0xD3,0xD0,0xCF,0xDE,0xB9,0xAB,0xCB,0xBE,0x0D,0x0A,0xB3,0xCC,0xD0,0x F2,0xA3,0xBA,0xD6,0xD0,0xB9,0xFA,0x20,0x51,0x51,0x3A,0x35,0x37,0x33,0x31,0x39,0x 32,0x39,0x35,0x34,0x0D,0x0A};unsigned char i;TRISC7=1;TRISC6=0;SPBRG=25; //设置波特率为9600BPSTXSTA=0X24; //使能串口发送,选择高速波特率RCSTA=0X80; //使能串口工作,禁止接收INTCON=0X00;while(1){for(i=0;i<51;i++){while(!TRMT){;}TXREG=string[i];}delay(2000);}}有一种hin232芯片,与max232芯片比较的话,价格相对要便宜很多。

JTAG仿真器使用方法_gz

JTAG仿真器使用方法

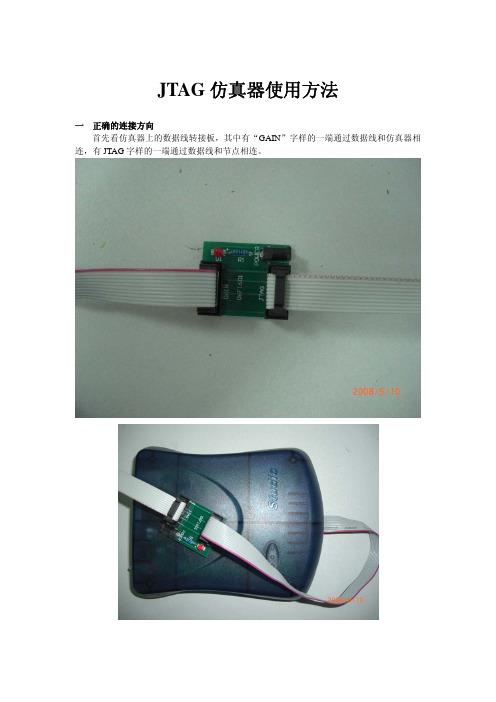

一正确的连接方向

首先看仿真器上的数据线转接板,其中有“GAIN”字样的一端通过数据线和仿真器相连,有JTAG字样的一端通过数据线和节点相连。

二通过串口线把PC和仿真器连接起来

三连接电源,电源要插在转接板上注意:当使用外接电源时,节点的开关不要打开。

四连接节点

注意细节,数据线和节点连接时,凸起的部分朝向节点内部,如下图。

因为数据线的原因,如果仿真器找不到节点,可以把突起部分朝外,再连接。

五烧写程序

当节点正确连接后,打开avrstudio烧写程序。

步骤如下:

1 打开avrstudio,这里推荐avrstudio4.12,会弹出一个对话框,点击“cancel”

2 在如下界面上点击“CON”图标

3 点击“CON”图标后,在弹出的对话框中做如下选择

选择完毕,点击“connect”按钮。

4 正确连接后会弹出如下界面

图片中最下面的提示信息“JTAG ICE found on COM1”表示,仿真器找到了节点。

图片最上方“NO device selected”表示没有选中设备。

5 在NO device selected”中选择128芯片

6 选择好设备型号后就可以进行编程了,点击下面图片的按钮,选择要烧写的程序。

7 点击“Program”按钮即可把程序烧写到节点里了。

AVR JTAG ICE使用说明

AVR JTAG ICE使用说明

----------中科院精英团队

1、首先用USB线将仿真器与电脑连接,电脑右下角会提醒找到

硬件,如下图:

随后,电脑会跳出安装驱动程序的对话框,点击取消。

2、安装USB-serial驱动点击驱动程序安装文件:

一直点击确定,最后程序安装成功;

3、查看串口,在“我的电脑---系统信息---硬件”中查找:

如果串口号不是COM3\COM4 请改之!

3、用5X2连接线将仿真器和目标板链接,目标板上电,此时,

三个灯都会亮。

4、打开A VR STUDIO,点击CON按钮:

5、如果顺利,将出现下面对话框:

选择你要下载的程序,点击PROGRAM即可。

6、点击取消,在PROJECT-----PROJECT WIZARD 选项中选择你

要仿真的文件,或者建立自己需要的工程。

7、点击编译,进入仿真调试坏接。

8、其他靠自己啦!。

C2000串口烧录程序应用手册说明书

Application Notes ZHCA806 – June 20181C2000串口烧录程序 应用手册Howard Zou摘要JTAG 是最常见的MCU 代码下载接口,但是很多时候MCU 无法通过JTAG 下载代码,为此,C2000在ROM 中集成了多种方式的代码下载引导程序,可以通过SCI, SPI, CAN 等接口把代码下载到RAM 中。

很多用户要求把程序下载到片上flash 中,为此,TI 开发了一套SCI flash kernel 程序。

我们可以通过引导程序将SCI flash kernel 下载到RAM 中,然后通过SCI flash kernel 再将需要的应用程序下载到片上flash 。

本文主要介绍了如何通过SCI flash kernel 将应用代码下载到片上flash ,并详细介绍了在芯片被密码保护的时候如何下载程序,对于双核芯片又该如何下载程序,最后介绍了通过批处理实现烧录的方式,适合于工厂在不知道芯片密码的情况下大批量烧录。

目录1 引言 (2)2 通过SCI 导入应用程序流程 ............................................................................................................3 3 待导入文件生成 ................................................................................... E rror! Bookmark not defined.3.1 kernel.txt 文件生成 (4)3.2 应用程序App.txt 待导入文件生成 ............................................................................................ 5 4 通过serial_flash_programmer.exe 下载程序 .................................... Error! Bookmark not defined.4.1 flash kernel A 芯片程序下载,以F28027为例 (6)4.2 flash kernel B 芯片程序下载,以F28379D 为例 (7)4.3 芯片加密时的应用程序升级 (11)4.4 通过批处理命令烧录程序 ...................................................................................................... 12 5 其他 . (14)参考文献 (14)图图 1.通过SCI 导入应用程序流程 .................................................... Error! Bookmark not defined. 图2.引导程序流程 .......................................................................... Error! Bookmark not defined. 图 3.CCS 添加编译步骤 .................................................................. Error! Bookmark not defined. 图 4.通过hex2000工具转换出hex 文件 ................................................................................... 5 图 5.命令窗的调用方法 .............................................................................................................. 6 图 6.F28027下载应用程序界面 ................................................................................................. 7 图 7.F28379D 下载flash kernel cpu1界面 .............................................................................. 8 图 8.F28379D 下载应用程序界面 ............................................................................................... 9 图9.F28379D 下载应用程序到CPU1成功后界面 ................................................................... 10 图10. F28379D 下载应用程序到CPU2成功后界面 . (11)图11.F28379D解密成功界面 (12)图12.新建批处理文件 (12)图13.批处理文件内容 (13)图14.等待输入串口号 (13)1 引言随着应用程序的功能不断增强,终端客户经常需要对嵌入式软件进行程序升级,这些通过引导程序就可以实现。

jtag标准调试流程

jtag标准调试流程JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

下面是JTAG标准调试流程的详细步骤:1. 硬件连接:将JTAG调试器与目标设备连接起来。

通常使用JTAG调试器的JTAG接口连接到目标设备的JTAG接口上,确保连接正确无误。

2. 软件设置:打开调试软件,并选择正确的目标设备和调试器。

根据实际情况,可能需要设置一些调试选项,如时钟频率、通信速率等。

3. 初始化:调试软件会发送一些初始化命令到目标设备,以确保设备处于正确的状态。

这些命令可能包括复位设备、加载调试固件等。

4. 读取设备信息:调试软件会读取目标设备的一些基本信息,如设备ID、版本号等。

这些信息可以用于确认目标设备是否正确连接,并且与调试软件兼容。

5. 设置断点:调试软件可以设置断点,以便在程序执行到指定位置时暂停执行。

断点可以设置在特定的代码行、函数调用或内存地址上。

6. 单步执行:调试软件可以逐步执行程序,以便检查每一步的执行情况。

可以使用单步执行命令,逐条执行指令,或者逐个时钟周期执行。

7. 查看寄存器状态:调试软件可以读取和修改目标设备的寄存器状态。

这些寄存器包括通用寄存器、特殊功能寄存器等,用于存储和控制设备的状态信息。

8. 查看内存内容:调试软件可以读取和修改目标设备的内存内容。

可以查看程序代码、数据等存储在内存中的信息,以便分析和调试程序。

9. 跟踪程序执行:调试软件可以跟踪程序的执行流程,记录程序运行时的各个环节。

可以查看函数调用栈、程序计数器值等,以便分析程序的执行路径。

10. 分析错误:如果程序发生错误或异常,调试软件可以捕获并显示错误信息。

可以查看错误代码、错误位置等,以便定位和修复问题。

11. 退出调试模式:调试完成后,可以选择退出调试模式。

调试软件会发送相应的命令到目标设备,使其恢复正常工作状态。

以上是JTAG标准调试流程的一般步骤,具体的流程可能会根据不同的调试工具和目标设备而有所差异。

USB-UART-JTAG模块说明文档

USB ,UART ,JTAG 模块设计说明文档制作人:硬件平台部 陈定一, USB 模块USB(Universal serial bus)的中文含义是通用串行总线。

USB 接口的特点是速度快、兼容性好、不占中断、可以串接、支持热插拔等。

目前USB 接口有四种标准,分别为USB1.0(1.5Mbps),USB1.1(12Mbps ),和USB2.0(480Mbps )以及最新的标准USB3.0(5Gbps)。

USB 线缆由四根线组成:VBUS,GND,D+,D-,VBUS 在理想状态下的供电电压是5V ,但在设计当中应当注意的是USB Hub 从供电能力分为High Power 和Low Power 。

High Power 能提供最大500mA 的电流,电压范围(4. 75--5.25V ),Low Power 能提供最大电流只有100mA ,输出电压范围(4.4--5.25V )。

USB 充电接口电路模块设计原理图:GNDUSB 口VDD51.外围元器件的选择:a. USB 充电接口选用USB 口-7.5*3.7*9.3mm-屏蔽壳0.4mm 铜合金-基座黑色LCP 料。

b. 电源线和地线之间分别串联一个阻抗为100欧姆、100MHZ,额定电流为2A 的磁珠。

(用磁珠来抑制高频噪声和尖峰干扰,还具有吸收静电脉冲)c. 电容的选择注意用大电容(10UF 以上)与小电容(0.1UF )配合使用(大小电容配合使用频率特性比较好,并可减小电源对地阻抗)。

2.使用注意事项:a.具体的USB 封装,磁珠,电容大小可以调节,以达到最佳电路效果。

b.电路原理图可根据实际电路需要进行修改。

USB 有不同的速度模式,每个USB 设备必须支持低速或全速的一种,上位机端通过检测两根信号线上的电平来判断外接的是一个支持低速还是全速的的外设。

在上位机端的两根信号线D+和D-上分别都下拉了一个15K 的电阻到地,作为新接入的外设端设备则应该在D+或者D-线上上拉一个1.5K 电阻到3.3V 电源,分别代表全速设备或低速设备。

JTAG使用说明

7 TMS Output Test Mode Select

8 GND -- 接地

9 TCK Output Test Clock output from Dragon-ICE to the target

11 RTCK 测试时钟返回信号

13 TDO 测试数据串行输出

15 nRESET 目标系统复位信号

17 、 19 NC 未连接

下面以S3C4510B开发板为例说明JTAG接口:

在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG 接口调试S3C4510B,在系统上电前,首先应检测JTAG 接口的 TMS 、 TCK 、 TDI 、 TDO 信号是否已与 S3C4510B 的对应引脚相连,其次应检测 S3C4510B 的 nEWAIT 引脚( Pin71 )是否已上拉, ExtMREQ 引脚( Pin108 )是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B 不能正常工作或无法与JTAG 接口通信,均与没有正确处理这两只引脚有关。

10 GND -- 接地

11 RTCK Input (可选项) Return Test Clock。由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。不使用时可以直接接地。

12 GND -- 接地

本章针对ARM7TDMI介绍调试结构。ARM的调试体系采用协议转换器来使调试器通过JTAG与ARM核直接通信。前面JTAG标准中提到的扫描链功能是测试用,这里把它作为调试用:捕获数据总线上的信号并向内核或存储器插入新的信息。ARM7TDMI-S核内具有EmbeddedICE逻辑,EmbeddedICE逻辑提供对片内调试的支持。调试指令直接通过扫描链插入ARM内核并执行。根据插入调试指令的不同,内核可以处于观察、保存或改变状态。ARM的调试体系可以使程序指令执行速度处于调试速度或全速运行。在ARM中采用JTAG的特点是:通过JTAG接口可以观察ARM内核状态和系统状态(注意:系统状态包括片内外设,不同于内核状态);不占用额外的目标系统资源;提供传统的断点访问和观察点访问;不再需要另外的UART端口来和监控程序通信。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AVR JTAG下载HEX文件使用说明

本文只介绍AVR JTAG下载HEX文件在AVR Studio环境下的下载方法,推荐使用。

并口下载线主要优点是电路简单,缺点主要有下载速度慢、不能在AVR Studio环境下使用。

具体差别在用了AVR JTAG 之后就知道了,现在一个标准的下载线也只要几十块钱和并口下载线没什么差别了。

此处所说的STK500下载线和AVR ISP下载线同属一类,它们使用相同的通信协议,STK500确切的说是一个学习板,AVR JTAG才是真正意义上的下载线。

AVR JTAG实物图片

AVR JTAG连接示意图

JTAG接口

支持芯片列表

AVR JTAG下载线支持芯片型号非常多,这里就不一一列出了,只要AVR芯片支持ISP下载的都可以。

AVR JTAG下载HEX文件-操作方法:

1、打开AVR Studio 软件,按下图操作。

2、在这里选择所用器件及连接端口,选择JTAG ICE,自动检测端口,点击Connect进入下一步。

3、下面窗口提示所用AVR ISP下载线固件版本与当前所用软件不同,提示要求升级AVR ISP下载线固件,如版本相同就不会出现下面的提示。

如你所用的AVR ISP下载线不支持在线升级功能的话,不要点确定要不AVR ISP下载线会死在那里不动了,直接点击取消跳过此步既可。

4、正常会进入下面编程(Program)界面。

主要包括有器件(Device)、编程模式(Programming mode)、Flash下载、EEPROM下载几个部分,最下面部分是信息窗口。

器件:用于选择器件和手工擦除器件。

编程模式:用于选择ISP和并口下载模式,由于此处用的是AVR JTAG下载线只支持ISP方式下载。

Erase Device Before擦除器件,选中此项在每次下载前会对将器件擦除。

需要同时烧写用户程序和引导程序时需要注意此处,正常情况下需选中此项。

Verify Devic写入校验,默认为选中。

Flash:下载Flash文件,有选择文件(Input HEX File)、编程(Program)、校验(Verify)、读取(Read)。

EEPROM:下载EEPROM文件,包含内容与上面相同。

如果你是初学者,并不要求对器件进行熔丝等复杂配置,由此窗口将HEX文件写入器件就可以实验了。

其它系统时钟及看门狗等可先使用器件默认配置。

5、下图为熔丝配置(Fuses)界面,具体配置请参照熔丝配置部分。

6、下图为器件锁定配置(LockBits)界面,主要为设置对用户代码、程序区及引导区的保护等级。

7、下图为高级配置(Advanced)界面。

8、下图为AVR ISP下载线配置(Board)界面,主要对下载线进行相关设置。

由于工作在AVRISP模式,只ISP下载波特率可以使用,通常情况下设置为230.4kHz均可使用,如目标板装有晶振主频较高时可以提高此处下波特率,可以提高下载速度。

注:更改后需要点后面的写入(Write)才有效。

9、下图为自动编程(Auto)界面,可以在这里选择要操作的项目,然后按启动(Start)既可一次完成。

AVR ISP下载线-连接错误:

1、AVR ISP下载线,重复出现下面窗口。

问题原因:PC机与AVR ISP下载线连接不成功。

问题出在PC与AVR下载线之间,查看串口连接是否正确、AVR下载线是否上电。

3、AVR ISP下载线窗口弱出如下窗口。

问题原因:AVR ISP下载线与目标芯片连接不成功。

问题出在AVR ISP下载线与目标芯片之间,查看ISP接口是否正确、是不是芯片时钟被锁住了。

AVR JTAG仿真器-仿真模式:

1、打开AVR Studio 软件,按下图操作。

2、在打开图口中选择需要仿真程序的.cof仿真文件,注意编译环境也需要设置生成目标文件为cof文件。

这

个文件包含调试信息,可以在C源程序的环境下调试,如果打开的是hex,则只能在编译器生成的汇编语言下调试了。

点击“打开”进入下一步。

3、下面窗口提示工程文件保存位置,使用默认位置就行了,点击“保存”进入下一步。

4、软件弹出设置器件及仿真模式窗口,此处是AVR JTAG硬件仿真所以下面分别选择:调试模式为JTAG ICE、芯片型号为mega16、端口用自动就可以了。

点击“完成”进入下一步。

5、经过上面步骤如硬件连接没有问题,那么会进入正式仿真界面,界面如下图。

6、到这一步就可以进行程序调试了,再后面的详细操作方法可以参照书本或者查看AVR STUDIO技术手册:AVR Studio 中文使用说明。

AVR JTAG仿真器-连接错误:

1、AVR JTAG仿真器工作在下载模式,重复出现下面窗口。

问题原因:PC机与AVR JTAG仿真器连接不成功。

问题出在PC与AVR仿真器之间,查看串口连接是否正确、AVR仿真器是否上电。

2、AVR JTAG仿真器工作在仿真模式,重复出现下面窗口。

PC机与AVR JTAG仿真器连接不成功。

问题原因:PC机与AVR JTAG仿真器连接不成功。

问题出在PC与AVR仿真器之间,查看串口连接是否正确、AVR仿真器是否上电。

3、AVR JTAG仿真器工作在仿真模式,重复出现下面窗口。

问题原因:AVR JTAG仿真器与目标芯片连接不成功。

问题出在AVR JTAG仿真器与目标芯片之间,查看JTAG接口是否正确、AVR芯片是否打开JTAGEN熔丝位。