基于FPGA的图像差分处理

fpga差分信号电平

FPGA差分信号电平1. 介绍在数字电路设计中,差分信号电平的处理是一个重要的环节。

差分信号是指在两个信号线上传输的信号,其中一条线传输的信号与另一条线传输的信号是相互补充的。

FPGA(现场可编程门阵列)是一种灵活可编程的硬件平台,通过控制差分信号电平可以实现各种不同的功能。

本文将详细探讨FPGA差分信号电平的相关知识,包括差分信号的定义、差分信号电平的特点、FPGA中处理差分信号电平的方法等。

2. 差分信号的定义差分信号是指在两条互补的信号线上传输的信号。

一条信号线上的信号是另一条信号线上信号的反相。

差分信号的传输具有以下特点: - 抗干扰能力强:由于两条信号线上的信号是相互补充的,外界噪声对两条信号线的影响是相互抵消的,因此差分信号的抗干扰能力强。

- 传输距离远:差分信号的传输距离相对较远,可以降低传输损耗和干扰。

- 传输速率高:差分信号的传输速率相对较高,可以实现更高的数据传输效率。

3. 差分信号电平的特点差分信号电平的特点主要体现在以下几个方面: - 信号范围:差分信号的电平范围一般为正负方向的电压差值,例如0V和3.3V之间的差分信号电平范围为-1.65V 到1.65V。

- 电平波形:差分信号的波形由正信号和负信号组成,正信号和负信号之间存在特定的时间关系。

- 传输方式:差分信号一般通过两根平衡的信号线传输,两根信号线的电压信号是相互补充的。

4. FPGA中处理差分信号电平的方法FPGA中处理差分信号电平的方法有多种,以下是常用的几种方法:4.1 逻辑电平转换逻辑电平转换是将差分信号电平转换为FPGA可接受的电平范围。

常见的逻辑电平转换方法有电阻分压器、差分放大器等。

电阻分压器可以将差分信号电平降低到FPGA可接受的范围,差分放大器可以将差分信号电平放大到FPGA可接受的范围。

4.2 信号调整在差分信号传输中,可能会出现信号失真的情况。

为了保证差分信号的有效传输,需要对信号进行调整。

fpga差分输入原理

fpga差分输入原理FPGA差分输入原理概述在现代电子系统中,FPGA(现场可编程门阵列)作为可编程逻辑器件的一种,广泛应用于数字电路设计和嵌入式系统中。

FPGA具有可编程性和灵活性的特点,使得它成为了数字电路设计的首选。

而在FPGA设计中,差分输入是一种常见的输入方式。

本文将介绍FPGA差分输入的原理和工作方式。

差分输入是一种通过将输入信号分为正负两路进行传输和处理的方式。

在FPGA中,差分输入通常由两个引脚组成,分别为正差分输入和负差分输入。

差分输入通过使正差分输入和负差分输入之间的电压差保持恒定,从而提高了系统的抗干扰性能和信号传输质量。

差分输入的工作原理可以通过以下步骤进行解释:1. 差分输入电路FPGA差分输入电路通常由差分对(Differential Pair)和电流源(Current Source)组成。

差分对由两个互补的MOSFET(金属-氧化物半导体场效应晶体管)组成,其中一个导通时另一个截止,通过调节两个MOSFET的工作状态,可以实现对输入信号的放大和处理。

2. 差分信号传输差分输入信号通常是通过差分对的输出电压差来表示的。

当输入信号为高电平时,正差分输入的电压上升,负差分输入的电压下降;当输入信号为低电平时,正差分输入的电压下降,负差分输入的电压上升。

通过这种方式,FPGA可以通过比较差分输入的电压差来检测输入信号的变化。

3. 差分输入的优势差分输入具有以下优势:- 抗干扰性强:差分输入将信号分为正负两路传输,可以使系统更好地抵抗来自外部的电磁干扰和噪声。

- 传输距离较长:差分输入可以通过增加差分对的增益来放大信号,从而提高信号传输的距离和质量。

- 电压共模抑制比高:差分输入可以通过设计差分对的工作状态来提高电压共模抑制比,从而减小共模干扰。

差分输入的应用差分输入在FPGA设计中有广泛的应用,包括但不限于以下几个方面:- 数据通信:差分输入可以用于串行通信接口(如LVDS、USB、HDMI等),提高信号传输的稳定性和可靠性。

基于MATLAB与FPGA的图像处理教程

这本书的作者韩彬、林海全和姜宇奇都是电子工业社的专家,他们深入浅出地 讲解了基于MATLAB和FPGA的图像处理原理和应用。其中,MATLAB作为一种强 大的数学计算和算法开发工具,被广泛用于算法设计和验证。而FPGA(现场可 编程门阵列)则是一种灵活的硬件加速引擎,可以用于实现高性能的并行处理 和计算。

当谈到MATLAB在图像处理中的应用时,作者强调:“MATLAB是一个强大的科 学计算工具,它提供了丰富的图像处理工具箱,使得用户可以轻松地实现各种 复杂的图像处理算法。”

对于如何结合MATLAB和FPGA进行图像处理,作者解释道:“通过将MATLAB算 法部署到FPGA上,我们可以实现高速、实时的图像处理。这是因为FPGA具有 高并行性和高效率的特点,可以大大提高算法的执行速度。”

在理解了图像处理算法的理论基础之后,本书通过MATLAB软件将这些算法进 行实现和验证。这部分内容详细介绍了如何使用MATLAB进行图像处理的各种 操作,包括图像的读取、处理和显示等。通过这部分内容,读者可以深入理解 图像处理算法在软件层面的实现方法。

这一部分是本书的核心内容,它详细介绍了如何将前面所学的图像处理算法通 过FPGA进行并行硬件加速。这部分内容涉及到了FPGA的基本知识、硬件设计 流程以及具体的实现案例。通过这部分内容,读者可以了解到FPGA在图像处理 领域的应用以及如何将算法移植到FPGA上进行硬件加速。

内容摘要

这些实例涵盖了多种图像处理算法,包括图像滤波、边缘检测、形态学操作等。通过这些实例, 读者可以深入了解FPGA图像处理的实现细节。 《基于MATLAB与FPGA的图像处理教程》是一本理论与实践相结合的教程,适合对图像处理和嵌 入式系统开发感兴趣的读者阅读。通过本书的学习,读者可以掌握使用MATLAB和FPGA进行图像 处理的核心技能,为实际项目的开发提供有力的支持。

基于FPGA的数字图像处理

数 字 图 像处 理 的 特 点 是处 理 的 数 据 量 集 成 度 、 量 和 速 度 方 面 都 达 到 了 较 高 的 容

大 , 理 非 常 耗 时 , 文 研究 了 在FPGA上 处 本

像 采 集 模 块 , 像 处 理 模 块 和 图 像 显 示模 图 块。 图像 采 集 模 块 实 现 的功 能是 捕获 图像 ,

用。

实现 , 样 能 同 时 兼 顾 速 度 及 灵活 性 。 这 F GA结构 的 最 大特 点是 结 构 灵活 , P 有较计 , 而 能够 提 高 从

第 一 阶 段 大 体 上 是2 世 纪 6 年 代 末到 0 0

2 0世纪 8 年 代 中 期 , 时 的 代 表 产 品 是 美 0 当

数据 需 多次 重 复 使 用 , 因此 , 图像 处 理 往 往

( ) 辑 功 能块 的 局 部 布 线和 相 互 间的 6逻 ( ) /O功 能 块 有 快 速 的 I 7I /0驱 动 、 寄

阶 段 的 产 品 出 现 两 大 类 , 种 仍 是 采 用插 通 用 布 线 , 以 精 确 的预 测 网 线 的 延 时 。 一 可

水平 , 己经 能 够 完成 复 杂 的 逻 辑 运 算 。 目前 , P F GA芯 片 己 经 具 备 了 许 多功

用 硬 件描 述 语 言 实 现 图像 处 理 算 法 , 过 通

由S AA7 1 解码 完 成 ; l3 图像 处 理 模块 进 行 图像 的 处 理 , 要 由F GA进 行 ; 主 P 图像 显示 部 分 则 由s AA7 2 编 码模 块 完 成 。 11 图 像 处 理 系 统 中 , 层 的 图 像 预 处 理 底

是 图 像 处 理 系 统 中 最 为 耗 时 的 环 节 , 整 对

基于 FPGA 的图像识别及处理技术研究

基于 FPGA 的图像识别及处理技术研究随着科技的日益发展,计算机视觉技术成为一项越来越热门的领域。

其中,图像识别与处理技术是计算机视觉中的重要内容。

本文将探讨基于 FPGA 的图像识别与处理技术,介绍它的原理、应用场景以及未来发展方向。

一、基础原理FPGA(Field Programmable Gate Array),中文名为现场可编程门阵列,是由一系列的可编程逻辑单元、输入输出块(IOB)、时钟管理单元、片上RAM等组成的可编程芯片。

图像识别与处理的基本流程是:图像采集 -> 图像预处理 -> 特征提取 -> 分类识别。

其中,图像预处理的任务是将原始图像进行去噪、增强、边缘检测等处理,特征提取的任务是将处理后的图像进行特征提取,分类识别的任务是将提取得到的特征进行分类,从而识别出图像中的目标物体。

FPGA 可以根据需要进行编程,实现不同的逻辑功能。

对于图像处理,可以采用 VHDL 或 Verilog 语言进行编程,将图像预处理、特征提取和分类识别等功能独立实现在FPGA 中。

由于FPGA 的并行计算能力很强,能够同时处理多个像素点,因此在图像识别与处理中表现出色。

二、应用场景基于 FPGA 的图像识别与处理技术在许多领域都有广泛应用。

下面简单介绍几个典型的应用场景。

1. 智能监控安防领域是 FPGA 图像识别与处理技术的典型应用之一。

以智能监控系统为例,该系统需要对摄像头拍摄的图像进行实时分析和处理,识别出异常行为(如人员进出、奔跑等)并及时采取措施。

使用 FPGA 技术可以有效提升系统的实时性和准确性。

2. 无人驾驶无人驾驶领域同样是 FPGA 图像识别与处理技术的重要应用之一。

无人驾驶车辆需要通过摄像头获取道路信息、交通信号灯等,然后根据识别结果确定行驶方向、速度等。

基于 FPGA 的图像识别处理可以大幅提高无人驾驶车辆的实时性和关键信息的准确性。

3. 机器视觉机器视觉是一项广泛应用于工业自动化、农业、医疗等领域的技术。

基于FPGA的数值计算在实时图像处理中的应用

2 视 频处 理 结构 及 原理

2 1 硬件 结构 .

如 图 1所 示 , 计 的 基 本 流程 为 : VIDii 设 D ( g — tl s a Itrae 信 号 经 过 解 码 器 解 码 后 , a Vi l nefc) u 进 入 F GA 计 算 , 算 结 果 送 入 编 码 器 编 码 , 经 P 计 再 过 D 接 口接 入显 示器 , VI 实现 实 时 图像 处 理 。下 面 简单介 绍 各部 分 的功能 结 构 。 ( ) VI 口。D L 是 基 于 TMDS Trn 1D 接 VI] 5 ( a— s inMii zdDi ee t l in 1通 讯 协议 的 io nmie f rni g a) t f aS 接 口技术 , 主要用 于计 算 机 和 显 示 设 备 之 间 的 连

以上 , 其 中 内嵌 的 I 且 P核 最 快 可 以在 1个 时钟

( 0n 左右 ) 1 s 内完成 多 位乘 法 运 算 , 文采 用 Al 本 —

tr 公 司 的 C co e系列 芯 片 , 充 分 考 虑 视 频 ea y ln 并 信号 的行 间特 性 , 用 逐 位 比较 完 成 数 据 的 开平 利 方运算 , 终 可 以实 现 对 具 有 二 次 曲线 边 界 的 图 最 像 进行 物 理分 割 。

图像分 割是 将 图像 中有 意义 的 特征部 分 提取 出来 , 这是 进一 步进 行 图像识 别 、 析 和理解 的基 分 础 。基 于 图 像 边 界 的 分 割 是 图像 分 割 的 重 要 方 式 , 中往 往会 涉 及 到 图像 边 界 是 二 次 曲线 的情 其 况 。在 实 时视频 图像 处 理 中 , 难 点 在 于 必 须 高 其 速 完成 大量 的数 据处 理 , 例如 对 刷新 率 为 7 、 5Hz 分 辨率 为 10 4 6 2 ×7 8的图像 显示 , 传输 像 素 时钟 频 率为 8 0MHz 左右 , 了保 持显 示 的连续 性 , 为 数 据处 理速 度 至少不 能低 于这 个 频率 。如 果此 时要 实 时地 进行 图像 分割就 必 须实 时地 完成 图像 边 界 的计 算 。 例如 用在 某些 显示 系 统 中的大 屏幕 全景 显示 器 , 果 需要提 取 其 中 圆形 区 域 部 分 的 图 像 信 息 如 来进 行处 理就 必须 首先 完成 图像 的实 时分割 。 由 于该 显示 区域具 有 二 次 曲线 的边 界 , 因此 如何 实 时确定 图像 边 界就成 了首要 任务 。 在硬 件 电路上 对 数 据 做 复 杂 计 算 , 如 开 方 例

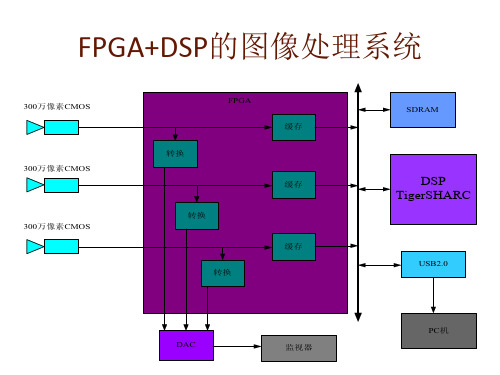

FPGA+DSP的图像处理系统

DSP的发展和趋势

– ADI的DSP具有出色的浮点处理能力,多用于雷

达/声纳等信号处理;独特的多DSP互联能力被

称为“多DSP系统的实现标准”

– TI公司的DSP则更注重单片的处理能力,在民用

高端DSP市场占有很大份额

DAC器件技术发展趋势

①高速、高精度、低功耗;

②多功能集成,如增加滤波器;

③接口电平采用高速协议:LVDS、DDR等技术。

RAM、FIFO技术

• 同步技术、双沿和多沿传输技术应用广泛

• 静态存储器:

– SBSRAM、ZBTSRAM等同步SRAM,时钟频率可 以高达200 MHz以上。 – QDR SRAM,在一个时钟周期内传输4个数据

TigerSHARC DMA Controller

I/O Processor INTERNAL BUS

128-bit DATA 32-bit ADDR

Bus Interface Unit IFIFO OBUF OFIFO DMA Controller

Data Address

Control

DMAR

SOC Bus Interface

USB特点:

• 连接灵活

等;

②缓冲和存储电路,RAM、FIFO等;

③逻辑控制和协处理器,CPLD和FPGA; ④通信接口电路,高速串行通信(光纤/LVDS)

模拟信号数字信号的转换电路

• ADC – Analog Digital Convertor

• DAC – Digital Analog Convertor

ADC器件

ADC器件发展趋势

FPGA使用LVDS差分信号的一些注意事项

FPGA使⽤LVDS差分信号的⼀些注意事项最近在调试⼀个LVDS的屏显功能,涉及到了⼀些LVDS的东东,简单地整理如下,后续会再补充。

(1)对于altera FPGA(CYCLONE III)1、对于作为LVDS传输的BANK必须接2.5V的VCCIO;2、左右BANK(即1/2/5/6 BANK)的LVDS发送差分对信号⽆需外接匹配电阻,⽽上下BANK(即3/4/7/8 BANK)则需要,如果硬件⼯程师忘了,还可以在FPGA的IO引脚分配时⾥加端接电阻设置;3、分配管脚时,左右BANK的LVDS差分信号脚在IO分配时选择的IO电平标准是LVDS,⽽上下BANK的LVDS差分信号脚在IO分配时选择的IO电平标准是LVDS_E_3R;4、分配管脚时,只要指定LVDS信号的p端(+),则n端(-)会⾃动分配。

在verilog代码中只要⼀个信号接⼝即可,⽆需在代码中定义⼀个差分对接⼝;5、在altera FPGA内使⽤的LVDS收发IP核是altlvds_rx和altlvds_tx,相应的IP使⽤说明在megawizard⾥有。

(2)对于xilinx FPGA区别altera的地⽅在于⾸先在Verilog的代码⾥,xilinx的LVDS信号需要定义⼀对差分对信号,通过xilinx的原语进⾏差分对转单端或者单端转成差分对信号。

另外在IO引脚分配时,xilinx的电平标准都是⼀样的,⽐如都是LVDS_33。

下图1是altera下的LVDS信号引脚分配,可见⽤户只需要分配p端(+)引脚即可。

图1 altera LVDS引脚分配情况下图2是xilinx的LVDS信号引脚分配,xilinx的LVDS引脚区分p端和n端。

当然在vivado下引脚分配可以只分配P端脚号,N端脚号会⾃动分配。

⽽在代码⾥都需要写明差分对信号,再通过原语转成单端信号。

图2 xilinx下LVDS的引脚分配情况By 我有风⾐~~。

一种基于FPGA的图像格式转换设计

常用的色彩编码方案是 Y b r C C ,其 中 Y是亮度分量 , C b是蓝 色色度分量 ,而 Cr 是指红 色色度分量。人的 肉眼对视频 的 Y分量更敏感 ,因此 ,通过对色度分量 进行子采样来减少分量后 ,肉眼将 觉察不到 图像质量

V rIgH 语 言 设 计 出相 应 的硬 件 模 块 , 后 结 合 M T A e _ DL o 最 A L B工具 对 硬 件模 块 处 理 后 的 数 据做 了相 应

的仿真。仿 真结果表 明,该设计对分辨率低 于 6 0 4 0的 图像数据能够很好的满足其 实时性要 求, 4x 8

( ol e f lcr a a dIfr t nE gn eig Hu a iesy C a gh 0 2 C ia C l g e t c l n omai n ier , n nUnv ri , h n sa4 8 , hn ) e oE i n o n t 1 0

计 算 机 系 统 应 用

2 01 0年 第 1转换设计 P

朱 喜 ( 南 大 学 电气 与信 息工 程 学 院 长 沙 41 0 2 湖 0 8)

杨 小 宁 郑 善 贤 王 炼 红

摘

要: 为 了实现 图像的 实时处理 ,常采用现场可编程 门阵列(P A 对采集到 的图像数据 首先进行格式转换处 FG ) 理 。本文 以对 Mir n MT V 1 传感器的三种 图像 格式输 出的处理为例 ,首先就 Y C 4 22 转 co 9 1 2 Cb r :: Y C 4 44,R 5 5 转 R 8 8 a e Cb r :: GB 6 GB 8 ,B y r格式转 R B 8 G 8 8及 降噪的原理进行 了介绍 ,然后应用

基于FPGA的图像处理系统

基于FPGA的图像处理系统一、引言在当代社会中,图像处理技术已广泛应用于各个领域,如医学影像、自动驾驶、安防监控等。

图像处理系统的实现要求高效、实时、稳定,而传统的软件实现方式在处理速度和实时性方面存在局限性。

因此,基于可编程逻辑器件(Field Programmable Gate Array,简称FPGA)的图像处理系统应运而生。

本文将介绍的原理、设计和应用。

二、原理FPGA是一种可编程的硬件设备,具有可重构性的特点,用户可以通过编程对FPGA进行逻辑电路的配置。

将图像处理任务转化为逻辑电路的实现,通过并行计算和密集的硬件资源,提供了高性能和高速度的图像处理能力。

1. FPGA的工作原理FPGA由一系列可编程的逻辑单元(Logic Cell)和可编程的可输入/输出块(Input/Output block)组成。

用户可以通过硬件描述语言(HDL)对FPGA进行编程,从而实现所需的逻辑功能。

2. 基于FPGA的图像处理流程的核心是使用FPGA对图像进行分析和处理。

其处理流程包括图像输入、预处理、特征提取、特征分析和图像输出等基本步骤。

(1)图像输入:将需要处理的图像输入到FPGA,通常使用摄像头或者传感器得到实时图像。

(2)预处理:对输入的图像进行预处理,例如去噪、灰度化、增强对比度等操作。

这些预处理操作旨在缩减噪声和提高图像质量,为后续的特征提取和分析提供更好的数据基础。

(3)特征提取:通过对图像进行边缘检测、角点检测、纹理分析等操作,提取图像中的重要特征。

特征提取是图像处理中的关键步骤,其结果能够反映出图像的本质信息。

(4)特征分析:依据提取的特征,对图像进行分析和处理。

可以进行目标检测、物体识别、人脸识别等任务。

(5)图像输出:将经过处理后的图像输出,通常通过显示器、视频录制设备等方式展示结果。

三、设计的设计包括硬件设计和软件设计。

硬件设计的关键是选择和配置适当的FPGA芯片,确定需要的逻辑电路和资源,并将其编程在FPGA中。

基于FPGA的图像处理探究

隹Isl^iSls V12021年第03期(总第219期)基于FPGA的图像处理探究王建,赵红霞(运城职业技术学院,山西运城044000)摘要:随着图像处理的数量的增大和图形处理算法复杂度变高,图像处理实时性就变得十分重要。

为了解决图像处理中数据实时性问题,文章基于FPGA的图像处理进行分析,文章基于边缘检测算法和滤波算法,选择以Sobel算子对图像进行预处理,并选择Matlab软件对算法进行仿真,研究算法的可行性。

实验表明文章提出的基于FPGA的图像处理系统具有良好的边缘检测效果,能够实现数据处理实时要求。

关键词:图像处理;FPGA;边缘检测;中值滤波中图分类号:TP391文献标识码:B文章编号:2096-9759(2021)03-0079-03在图像处理的数量的增多,以及图形处理算法复杂度日益变高的背景下,针对图像处理实时处理难度将越来越高。

结合国内外学者研究的文献,主要集中了图像处理算法的研究层面上,关于选择具体的处理器和仿真软件两者融合进行研究的文献较少。

因此,本文基于FPGA对图像进行处理,釆用边缘检测和滤波算法,以Sobel算子对图像进行实时处理,从而满足图像处理时间和速度的要求,结合仿真结果验证本次设计的实用性,从而说明本研究实际意义。

1边缘检测和Sobel算法、中值滤波理论分析在实际生活中,边缘是指两个灰度值在相差较大的相邻区域当中,具体表现为特征不连续性。

通常用导数函数变化收稿日期:2020-12-29图2两种过滤方法实验结果对比图由图2中的四组曲线对两种过滤方法的拟合优度和误判率分别进行分析。

首先,针对拟合度优度指数分析得出,本文过滤方法的拟合度和传统过滤方法的拟合度在整体上註的差异性较小,数值基本接近,但仍然能够看出本文过滤方法的拟合优度指数更高,由本文上述计算可知,拟合优度指数数值越高,则说明过滤的精度越高。

因此,证明本文提出的异常信息流过滤方法与传统过滤方法相比,在实际应用中的过滤精度更高。

基于FPGA的低照度CMOS的图像处理与检测技术研究

基于FPGA的低照度CMOS的图像处理与检测技术研究摘要随着时代的不断发展,人们对图像处理和检测技术的需求量不断的增大,基于FPGA的运动目标检测技术是其重要的组成部分,成为研究的热点。

本课题设计了一种基于FPGA的低照度CMOS运动目标检测系统。

30639本文首先阐述了运动目标检测的几种方法,低照度CMOS的研究意义及其研究现状,本文研究的背景和研究的内容。

接着详细介绍了本课题所用到的软硬件平台,主要包括低照度CMOS摄像头,FPGA开发板,显示器,电源以及所用到的软件平台。

最后在搭建好的的运动目标检测的硬件平台的基础上进行视频信号的AD和DA转化并且运用背景相减法进行目标检测。

具体工作如下:首先,通过对图像格式进行分析,运用verilog编程并运用signaltap进行调试,并成功视频信号的接收和发送。

接着,对SRAM的读写进行编程和调试,实现存储背景信息;最后,运用背景相减法,进行图像检测和处理。

关键词运动目标检测 Quartus II 数模转换模数转换低照度CMOS 背景相减法毕业设计说明书(毕业论文)外文摘要Title Based on the FPGA low illumination CMOS imageprocessing and detection technology research AbstractIt is constantly increasing of image processing and detecting technology with the development of the time. The night moving targets detection based on FPGA technology is an important part of this technology and become research hot spot.And the moving target detection technology has been widely used in military, traffic, security monitoring,etc.Therefore, research on moving target detection invested a lot of manpower and material resources at home and abroad.This topic has designed a kind of low illumination CMOS motion target detection system based on FPGA.源自First ,this article expounds the moving target detection and low illumination CMOS research significance and research status.Second then this topic by using the software and hardware platform is introduced, mainly including low illumination CMOS camera, the FPGA development board, display, power supply, etc.It achieves the goal of frame differential method detection method on the basis of the existingmotion target detection.Finally, through the analysis of the moving object, and using verilog programming, realizing the collection of the signal, processing and output.the video acquisition based on FPGA, display and the goal of sports into the alarm function.Keywords moving object detection Quartus IIdigital-to-analogue conversion Frame Difference analog-digital conversion low-light-level CMOS 目次1 绪论 11.1 运动目标检测的研究意义以及研究现状 11.2 低照度CMOS的研究意义及研究现状 11.2.1 国外低照度CMOS发展现状 21.2.2 国内低照度CMOS发展现状 31.2.3 低照度CMOS的发展条件及趋势 41.3 本课题的研究背景 51.4 本课题的工作内容 52 低照度CMOS图像处理软硬件平台 62.1 低照度CMOS图像处理硬件平台主要构成 62.1.1 FPGA开发板系统组成 6 :2.1.2 低照度CMOS的技术指标 82.1.3 PAL制信号 92.1.4 显示器 122.1.5 6V稳压电源 122.2 低照度CMOS图像处理软件平台 122.2.1 Quartus II 122.2.2 verilog硬件描述语言 132.3本章小结 133 算法设计与实现 143.1 图像检测系统设计及编程实现 143.1.1 TVP5150进行图像视频的采集 143.1.2 SRAM的读写控制 173.1.3 信号的处理和报警控制 203.1.4 ADV7123进行图像的输出显示 233.1.5 各模块的连接与总程序编写 263.2 实验的步骤和功能的实现 273.2.1 各部分之间的连接 273.2.2 CMOS相机的检测 283.2.3 实现接收和发送模块 283.2.4 实现SRAM的接收存储 293.2.5 实现SRAM读出和监控报警的功能 29 3.3 本章小结 29结论 30致谢 31参考文献321 绪论1.1 运动目标检测的研究意义以及研究现状1.2 低照度CMOS的研究意义及研究现状1.2.1 国外低照度CMOS发展现状1.2.2 国内低照度CMOS发展现状1.2.3 低照度CMOS的发展条件及趋势由于CMOS具有体积小,速度快等优势,才使得它可以随着安防行业网络化的浪潮成为高清IPC的首选方案,打破了CCD在模拟时代的垄断地位。

FPGA中差分信号的定义和使用

FPGA中差分信号的定义和使用FPGA中差分信号的定义和使用做数字电路设计的朋友对差分信号的定义应该都不会太陌生,在当前比较流行的高速串行总线上,基本都是使用的差分信号。

比如USB,PCIE,SATA等等。

大多数的FPGA也都支持差分信号,甚至某些新型号的CPLD也开始支持差分信号了。

那么在FPGA中如何正确定义和使用差分信号呢?在这篇文章里,我们基于ALTERA公司的CYCLONE III系列的FPGA芯片,做一些讨论。

一,差分信号输出我们先在设计中定义一个名字为DIF_OUT的输出信号。

并将UART_CLK时钟赋给它(UART_CLK为串口时钟,大概为115.2kHz)。

(该实验是在一个FPGA的项目上添加部分差分信号的设计来做的,会引用到原设计里的一些信号,但在介绍中,只会给出与差分信号实验相关的部分)如下面所示:module FPGA_TOP(……DIF_OUT,……);……output DIF_OUT;……assign DIF_OUT = UART_CLK;endmodule在设计里,DIF_OUT和其他变量的定义和赋值方式是一样的,没有任何的区别。

如果需要将DIF_OUT当做差分信号输出的话,就必须在Pin Planner中对其I/O Standard进行定义。

如下图所示,我们可以把I/O Standard定义为1.2V的单端输出信号。

我们也可以把I/O Standard定义为BUS_LVDS类型的信号,这个时候会出现什么情况呢?从下面的图可以看到,系统会在将DIF_OUT定义为Bus LVDS类型的同时,多添加一个DIF_OUT(n)的信号,并且根据DIF_OUT的location自动选定DIF_OUT(n)的location。

在Differential Pair里,会显示这两个信号互为差分信号对,也就是说,这是一组差分信号。

我们再通过实例讨论一下CYCLONE III中定义差分信号时的注意事项。

基于FPGA视频和图像处理系统的FIFO缓存技术

【 关键词 】F G ; P A 图像处理 ; 帧差法 ;IO 动 态 目标检测 ;h Soe FF ; C i cp p 【 中图分类号】T 9 11 N 4. 【 文献标识码】A

FI FO c c no o y i Vi e n mag oc s i g Sy tm s d on FPGA Ca he Te h l g n d o a d I e Pr e sn se Ba e

o j

图 3 IE S h mai S mb lFF 部 分 原 理 图 S c e t y o I O c

敏感的图像数据, 通常图像处理的也是图像灰度值 。

是第一帧的奇数场或是偶数场的 y 值信号。y值信号进入 了计算能力上 的支持 。D M模块为 内部例化器件提供系 bFF C IO缓存 , 相当于将 y 值信号做 了延迟 , 读使能开启输出 统 时钟信号。另外 , C D M具有将信号差分 、 相移 、 倍频 、 分 Y信号 。在系统时钟下 , 两个 FF IO输 出的 a ,y yb 则是 V I PN

都非常重要 。

频 图像信号 , 经图像缓存 模块缓 冲, 一路 传输 给检 测模块 路直接还原为视频数据流信号 , 完善 的系统显示模块还

经 A 7 2 编码芯片转换输 出 L D显示 , C 视频 图像处 理 系 统设 计 中, 频 信 号 经过 采 集 、 视 缓 进行算法处理 , S A 11 存、 处理 、 出( 输 显示或存 储 ) 。而缓存模块 的设计取决 于

X A G H uh n Z A G Z ie WA G P n I N o ze , H N hj , N e g i

基于FPGA的高速图像数据处理技术研究

基于FPGA的高速图像数据处理技术研究随着科技的不断进步和发展,图像处理技术已经成为了现代社会不可或缺的重要组成部分。

随着图像数据量的不断增大和复杂度的不断提高,如何进行高速、高效、精准的图像数据处理成为了人们关注的焦点。

FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,具有高速并行计算、灵活可编程的特点,已经成为了高速图像数据处理领域的热门技术之一。

一、FPGA在高速图像数据处理中的应用FPGA是一种由大量可编程逻辑单元、数据存储单元和输入输出单元组成的可编程逻辑器件。

因此,相对于传统的通用处理器,FPGA具有高速并行计算和适应性强等特点,可以更好地适应实时性要求较高的高速图像数据处理任务。

在高速图像处理中,FPGA主要应用于以下几个方面:1. 图像采集与传输。

FPGA可以直接通过数据总线实现与图像采集设备之间的数据传输,减少了传输数据时的中间环节,从而提高了传输速度和稳定性。

2. 图像滤波。

FPGA可以实现各种基于滑动窗口的滤波算法,如均值滤波、中值滤波、Sobel算子等,能够快速、高效地过滤掉图像中的噪声,提高图像的质量和清晰度。

3. 图像分割与识别。

FPGA可以实现各种基于模板匹配和神经网络的图像分割和识别算法,如Canny边缘检测、Hough变换、BP神经网络等,可以高速且准确地分割出目标区域和识别出目标特征,实现图像智能化处理。

4. 视频编码压缩。

FPGA可以实现实时的视频压缩编码器,如H.264、MPEG-2等,可以将高分辨率、高帧率的视频信号进行高效地压缩,从而减少数据带宽和存储空间,实现更高级别的视频处理和传输。

二、FPGA在高速图像数据处理中的优势相对于传统的通用处理器,FPGA在高速图像数据处理领域具有以下优势:1. 实时性好。

FPGA的可编程逻辑单元可以并行计算,与CPU相比,其在对图像进行处理时的响应速度更快,更符合高速图像处理要求。

基于FPGA的图像处理加速算法实现

基于FPGA的图像处理加速算法实现图像处理是一门研究如何对数字图像进行分析、处理和修改的领域。

它在计算机视觉、图像识别和模式识别等众多领域中有着广泛的应用。

随着计算机技术的不断发展和进步,图像处理算法的实现和优化成为了一个重要的研究方向。

本文将介绍基于FPGA的图像处理加速算法实现。

FPGA即“现场可编程门阵列”(Field-Programmable Gate Array),是一种广泛应用于数字电路设计和实现的技术。

相比于传统的基于CPU的图像处理算法,基于FPGA的图像处理加速算法能够提供更高的运算速度和更低的功耗。

在基于FPGA的图像处理加速算法实现中,首先需要选择合适的FPGA平台。

目前市面上有多种FPGA平台可供选择,如Xilinx的Zynq系列和Altera的Cyclone系列。

选择FPGA平台时需要考虑其可编程性、处理性能和资源利用率等因素。

接下来,需要设计和实现图像处理算法。

常见的图像处理算法包括图像滤波、边缘检测、图像增强等。

这些算法通过对图像像素进行计算和处理,实现对图像的改变和优化。

在设计算法时,需要考虑算法的复杂度和实现的可行性。

FPGA可以通过并行计算和硬件加速的方式提高图像处理算法的执行效率。

在算法设计完成后,需要将算法转化为硬件描述语言(HDL)并进行综合和布局布线。

HDL是一种专门用于描述硬件电路的语言,如VHDL和Verilog。

综合和布局布线是将HDL代码翻译为硬件的过程,可以通过专门的综合工具和布局布线工具完成。

这一步骤是将算法转化为可在FPGA平台上运行的电路的关键步骤。

在综合和布局布线完成后,需要进行验证和调试。

验证工作主要包括功能验证和性能验证。

功能验证是确保算法在硬件上的实现和预期的功能一致,可以通过仿真和测试来进行。

性能验证是评估算法在FPGA平台上的运行速度和资源利用率,可以通过性能分析工具和基准测试来进行。

最后,将验证通过的算法加载到FPGA平台上,进行实时图像处理。

基于FPGA的数字图像处理

基于FPGA的数字图像处理摘要:随着数字多媒体技术的不断发展,数字图像处理技术被广泛应用于航空航天、通信、医学及工业生产等领域中。

图像处理系统一般包括两个部分:图像采集部分和图像处理部分。

图像采集部分由专用的视频处理器、图像缓存和控制接口电路组成。

图像处理部分可以是计算机,也可以是专用图像处理器件,或者是两者的结合。

由于底层图像处理的数据量很大,要求处理速度快,但运算结果相对比较简单,以FPGA作为主要处理芯片的图像处理系统非常适合于对图像进行处理。

关键词:FPGA 数字图像数据处理数字图像处理的特点是处理的数据量大,处理非常耗时,本文研究了在FPGA上用硬件描述语言实现图像处理算法,通过功能模块的硬件化,解决了视频图像处理的速度问题。

随着微电子技术的高速发展,FPGA为数字图像信号处理在算法、系统结构上带来了新的方法和思路。

图像处理系统的发展大致分为三个阶段。

第一阶段大体上是20世纪60年代末到20世纪80年代中期,当时的代表产品是美国和英国的一些公司推出的各种图像计算机以及图像分析系统。

第二阶段是从20世纪80年代中期到20世纪90年代初期,该阶段的特点是小型化,外部结构不再是机箱式而是插卡式。

第三阶段是从20世纪90年代初开始,这阶段的产品出现两大类,一种仍是采用插卡式,随着PCI总线技术的成熟,采用PCI总线的产品逐步取代采用ISA总线接口的产品。

随着近些年来多媒体技术的发展,人们对视频信息的需求愈来愈强烈,图像采集与处理显得越来越重要。

依托计算机技术、通信技术和网络条件的发展以及数字信号处理的快速发展,图像处理系统出现以下发展趋势。

(1)随着硬件的发展,图像处理系统的性能会越来越高,价格会逐步降低。

(2)图像处理系统的功能都会集成在一个便于携带使用方便的电子设备上,不需要PC和各种辅助设备。

(3)由于网络的普及,图像处理系统将和网络结合,实现远程的图像采集和传输。

(4)图像处理系统内部将集成开发软件,使得用户更加容易根据自己的需要开发相应的图像处理算法,系统的效率更高。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的图像差分处理

1背景知识

差分图像在许多领域得到了广泛的应用,比如:视频压缩,生物医学诊断,天文学,遥感,人脸识别等。

2 matlab仿真MATLAB源码:Main.mI = imread(flower.bmp); figure, imshow(I);I_gray = rgb2gray(I);figure,imshow(I_gray);Id = mipcentraldiff(I_gray,dx); figure, imshow(Id);Mipcentraldiff.mfunction dimg = mipcentraldiff(img,direction)% MIPCENTRALDIFF Finite difference calculations %% DIMG = MIPCENTRALDIFF(IMG,DIRECTION)%% Calculates the central-difference for?a given direction% IMG : input image% DIRECTION : dx?or dy% DIMG : resultant image%% See also MIPFORWARDDIFF MIPBACKWARDDIFF MIPSECONDDERIV% MIPSECONDPARTIALDERIV% Omer Demirkaya, Musa Asyali, Prasana Shaoo, ... % Medical Image Processing Toolboximg = padarray(img,[1 1],symmetric,both);[row,col] = size(img);dimg = zeros(row,col);switch(direction)casedx,dimg(:,2:col-1) = (img(:,3:col)-img(:,1:col-2))/2;casedy,dimg(2:row-1,:) = (img(3:row,:)-img(1:row-2,:))/2;otherwise,disp(Direction is unknown);enddimg = dimg(2:end-1,2:end-1);仿真结果:

图1 RGB原图

图2 gray

图3 central_diff

3 FPGA设计

图4 基于串口传图的中心差分

如图4所示,我们将RGB565格式转化为Ycbcr格式,Y通道进入中心差分模块,完成中心差分算法。