Calibre LVS的使用方法

Calibre LVS 介绍

Calibre LVS 介绍本篇就讲解有关LVS方面的内容。

具体实例可以参照 ”dracula LVS介绍”中的说明。

一、具体操作:%drac_cvt %caliber –lvs | tee mlvs.logopen cell view “lvs_test”%calibre –rveLoad LVS result databasemodify layoutuse query tools to highlight errors (举例)*注:当然还有其他一些工具来帮助查找错误所在,点击就可以,不至于要想半天来判断错在source端还是drain 端等扼杀脑细胞的问题了。

有一大特点就是很人性化的点击,就到显示到相应的位置,无法是layout还是schematic或者是source net list。

二、相关文件内容1, netlist***** lvs_test NETLIST ******.BIPOLAR.GLOBAL VSS VDD************************************************************************************.SUBCKT lvs_test OUT INRI6 net2 IN 1kCI4 OUT VSS 0.2pMI1 VSS net2 OUT VSS PMI0 VDD net2 OUT VDD N.ENDS可以用 caliber –lv –cs 对netlist进行转换和语法分析。

*建议:subckt name最好与cell name一致。

2,由dracula 转换过来作了些小的修改,只是保证了语法没有错,并且能达到基本的要求为目的,所以大家可以对比上次 dracula 来看。

Caliber ERC 一般与 LVS 一起验证,要产生 LVS 可RVE 的database,需要加入 MASK SVDB DIRECTORY "svdb" QUERY 会产生 svdb目录,要产生ERC database 要使用 ERC SELECT CHECK 。

calibre使用帮助

calibre使用帮助Calibre是一款功能强大的电子书管理软件,它可以帮助用户管理、转换和阅读电子书。

以下是关于Calibre使用的详细指南。

-运行安装程序,按照提示完成安装过程。

2. 添加电子书到Calibre库:- 打开Calibre软件,点击“添加图书”按钮或拖放图书到Calibre 界面。

-选择您要添加的电子书文件,并点击“打开”按钮。

- Calibre会自动将电子书添加到您的图书库中。

3.转换电子书格式:-选择您想要转换的电子书。

-点击“转换图书”按钮。

-在转换选项中,选择您想要的输出格式和其他设置。

-点击“确定”开始转换。

- 转换完成后,您可以在Calibre库中找到转换后的电子书。

-点击“保存”按钮保存修改。

5. 在Calibre中阅读电子书:-选择您想要阅读的电子书。

-点击“阅读图书”按钮。

- Calibre内置阅读器会打开,并显示您选择的电子书。

6.同步电子书到设备:-连接您的设备到计算机。

- 在Calibre中选择您想要同步到设备的电子书。

-点击“发送到设备”按钮。

- Calibre会自动将选中的电子书同步到您的设备上。

7. 在Calibre中和排序电子书:- 使用栏在Calibre库中电子书。

8. 自定义Calibre界面:-点击“首选项”按钮。

- 在“界面”选项中,您可以自定义Calibre的外观和行为。

-点击“保存”按钮保存修改。

9. 使用插件扩展Calibre功能:-点击“首选项”按钮。

- 在“插件”选项中,您可以安装和管理各种插件,以扩展Calibre 的功能。

10. 备份和恢复Calibre库:-点击“首选项”按钮。

-在“高级”选项中,选择“备份/还原”。

- 按照提示选择您要备份或恢复的Calibre库文件。

希望上述信息对您使用Calibre有所帮助。

Calibre是一款强大的电子书管理工具,它提供了多种功能来满足您对电子书的各种需求。

无论是转换、管理、阅读还是备份,Calibre都能帮助您完成这些任务。

Calibre user manual

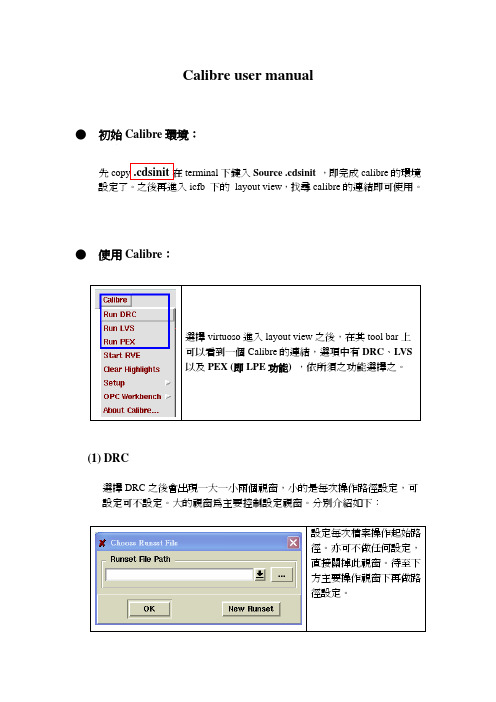

Calibre user manual● 初始Calibre 環境:先copy .cdsinit 在terminal 下鍵入Source .cdsinit ,即完成calibre 的環境設定了。

之後再進入icfb 下的 layout view ,找尋calibre 的連結即可使用。

● 使用Calibre :選擇virtuoso 進入layout view 之後,在其tool bar 上可以看到一個Calibre 的連結,選項中有DRC 、LVS 以及PEX (即LPE 功能) ,依所須之功能選擇之。

(1) DRC選擇DRC 之後會出現一大一小兩個視窗,小的是每次操作路徑設定,可設定可不設定。

大的視窗為主要控制設定視窗。

分別介紹如下:設定每次檔案操作起始路徑。

亦可不做任何設定,直接關掉此視窗。

待至下方主要操作視窗下再做路徑設定。

Main Window設定以Rule、Inputs、Outputs為主,通常皆以預設執行即可設定完成後,選Run DRC即可操作。

Rules:Kick ”…” to browser Rules file & Run DirectoryKick “View” to view & edit rules fileInput:由layout 連結過來,點選import from layout,calibre將會自動將layout 檔成gds檔。

此外Calibre 有預設的file name,以cellname.calibre.gds命名。

原則上不須更改任何設定,以其預設操作即可。

亦可自已命名。

Outputs:預設輸出為cell name.drc.summary即為dracula的.sum檔圖中選項皆以預設操作即可。

執行Run DRC後會出現兩個視窗,一個是summary report,一個是RVE視窗summary report即相當於.sum檔之結果,而利用RVE的highlight功能,可加速DRC驗証以及偵錯能力。

Calibre DRC、LVS的详细教程

//

rule_4a { @ res minimum enclosure of oxide is 7

enclosure oxide res < 7 }

// oxide 的内外边的间距 ,enclosure 具体的介绍见下一节

rule_4b { @ oxide minimum enclosure of res is 6

Begin Cell Definition Cell Name : VG, View Name : layout Rectangle - Layer : 7 Data Type : 0 BBOX : (5000,-10500) (16000,-8100) Rectangle - Layer : 7 Data Type : 0 BBOX : (5000,5900) (16000,8300) Rectangle - Layer : 1 Data Type : 0 BBOX : (5000,0) (16000,10200) End Cell Definition

T8.4 Internal operation 理解 Internal 指令的关键是 Internal 指令是 polygon 的内边(interior edge)的相对关系, 只有 interior edge 之间才能检查。T8.4 的左边是在同一个 polygon 的 internal 检查,请注意左 边凹进去的相对两边不作检查,这是因为这两边是 exterior edge。同一 layer 的 polygon 的

8.2 DRC Rule File

T8.2 DRC flow 如图 T8.2 所示,DRC 的输入有两项,一个是 layout,就是手工或 APR 生成的版图,一 般是 GDSII 格式。另一个是 Rule File,Rule File 告诉 DRC 工具怎样做 DRC,这个文件十分 重要,一般,由流片厂家提供,或者由 designer 根据流片厂家提供的版图几何规范自己写。 Calibre 读入 GDS(版图)和 Rule File,进行处理,输出结果,输出结果是 calibre 自己定义 的格式,designer 可以通过一个 Viewer 来看,一般用 cadence 的 virtuoso 来分析输出结果和 修改版图。

calibre_LVS入门

Calibre环境做LVS步骤及注意事项1、LVS数据准备在Astro中完成芯片后提取.fv文件及.gds文件,这两个文件是做LVS必备的。

.v文件用来生成在LVS过程中用来和Layout进行比对的.spi文件,而.gds 文件用来读入calibre得到Layout。

2、将.gds文件读入calibre具体步骤省略。

3、生成.spi文件.spi文件是由.v和一些.cdl、.spi文件一同生成的。

生成.spi文件有一个脚本,以SMIC18 工艺xxx目录为例:v2lvs \-lsp xxx/smic18.cdl \-lsp xxx/POR.cdl \-lsp xxx/RAM256X8.cdl \-lsp xxx/SP018W.sp \-s xxx/smic18.cdl \-s xxx/POR.cdl \-s xxx/RAM256X8.cdl \-s xxx/SP018W.sp \-s0 VSS \-s1 VDD \-v $topCell.v \-o $topCell.spi格式是固定的,-lsp后面列出你所要做LVS的芯片用到的IP的.spi(.sp)文件,rom、ram、stdcell是.cdl文件。

-s后面再把-lsp列出的文件重复一遍。

-s0和-s1不变,-v后面写你要进行转换的.fv文件,-o后面写你要输出的.spi文件。

文件写好后,在文件所在目录直接键入文件名,文件即开始自动执行。

执行后若无warning和error即可。

icc中提取出来的.v文件需要有phsical only的器件,但是不需要corner和filler pad,pcut和power IO必须加进去。

还有一些格式要求,需要使用如下选项:wirte_verilog –diode_ports –split_bus –no_pad_filler –no_corner_filler_cells -pg 这些信息加好后,再进行上面转换.spi文件的步骤。

Calibre 中文教程

Lab-4.Calibre –DRC與LVSI•目的:實習六是介紹一個大部分業界所使用的一套佈局驗證的軟體―Calibre(為Mentor公司之產品),Calibre是被世界上大多數的IC設計公司做為sign-off的憑據,適合做大型電路的驗證。

Calibre和Dracula、Diva有許多不同之處。

Calibre是一套類似Diva的驗證軟體,但其嚴謹度與考靠性遠優於Diva,這也是大家為何要使用Dracula的原因,但Dracula的操作不易,且無法做on-line的驗證。

但Calibre改進了這些缺點,不但操作簡易,更可搭配Virtuoso或其他layout軟體做線上的驗證,由於Calibre的已被大多數的公司所採用,因此CIC也將轉向支援Calibre的技術而漸漸取代Dracula。

本實習的目的是要將前一實習的電路,經過Calibre的佈局驗證後,以便能將此Layout送去製造。

而本實習將延續實習四的Layout為實例,藉此介紹整個Dracula的操作流程。

II•DRC(Design Rule Check):1•建立子目錄、拷貝calibre_035.drc檔及撰寫DRC的主要檔案:<i>因為作DRC佈局驗證時會造出非常多檔案,因此在此強烈建議建立一個屬於此Layout作DRC時之新目錄夾,也就是說在你的根目錄下鍵入mkdir 0.35然後再進入0.35的資料夾內,即鍵入cd0.35,再鍵入mkdirdrcnand3,建立一個名為drcnand3的子目錄 。

..<ii>先進入/avanti/Lab610/avanti/Lab/610/test/lab/drc/目錄下再利用filemgr &或拷貝指令cp ,將calibre_035.drc 拷貝至你的工作目錄底下。

<iii>為配合Layout ,因此在作DRC 驗證時必須利用編輯軟體(ex Vi 、textedit….),編輯下面的檔案並存為drc_rules的檔。

calibre用法

calibre是一个强大的电子书管理工具,使用方法如下:

1.安装完成后进入设置向导,首先为你的图书选择一个合适的存储文件夹,你

转换后的图书都会保存在这里面。

2.再选择你合适的设备,如果你是kindle的用户那么,选择Amazon---kindle,

如果您买到的的是新款kindle也可以选择kindle paperwhite。

3.紧接着进行下一步,这里是进行推送邮箱的配置,对于只有格式转换需求的

同学,此步可以跳过,直接点击“下一步”。

4.设置完成后,开始转换图书,首先添加图书。

5.添加完成后,在列表中找到自己刚刚添加的图书,点击右键,选择“转换书

籍”“逐个转换”。

6.找到你的书籍。

7.选择输出格式。

8.点击界面右侧的调试选项进行调试,点击界面中的文件夹图标来选择文件夹

放置调试输出。

需要注意的是在调试过程中会输出转换各个阶段中生成的中

转html,这个html可作为手动编辑转换的起点。

9.调试完成没有什么问题后就可以点击界面右侧的PDF输出选项,进入该界面,

可以设置一些智障的大小、字体大小、颜色等选项,选择完成后就点击确定

进行转换了。

按照以上步骤操作后,您就可以成功使用calibre进行电子书转换了。

Calibre_使用

Calibre_使⽤如何在Cadence 环境⾥简单的使⽤Calibre⼀、在Cadence 环境⾥调⽤Calibre1、在.cdsinit ⾥加上 load(“/usr/calibre/mgc_skl.skl”),这个.skl ⽂件就是Mentor 公司提供的skill ⽂件。

2、在启动icfb &的路径下 module add calibre3、启动icfb &后,打开⼀个版图检查⼀下顶端的Menu ⾥有没⼀个Calibre 的菜单。

如果有则表⽰可以在当前环境下使⽤Calibre 了,这个菜单⾥有DRC 、LVS 、XRC 、RVE 等命令。

4、看书可以⽤mgcdocs &命令,下⾯有Clibre 的参考⼿册。

⼆、⼏个有⽤的缩写1、 SVRF---Standard Verification Rule Format (标准的检查⽂件)2、 RVE---Results Viewing Environment(显⽰结果⽤的环境窗⼝)3、 SVDB---Standard Verification Database (LVS results)4、 DRC---Design Rule Checking5、 LVS---Layout Versus Schematic6、 ERC---Electrical Rule Checking 三、⼀个简单的DRC 流程2、⼀个DRC 实例(1)打开⼀个版图,在Calibre 菜单下点出 RUN DRC 命令。

(2)Cancel 掉Load Runset File 命令窗⼝,Runset File是RUN DRC时需要填⼊的⼀些设置,⽅便于下次RUN。

第⼀次由于没有,所以就Cancel。

等第⼀次RUN完后,可以将填⼊的设置存成⼀个Runset File。

再RUN DRC时,可以将这个Runset File Load 进来。

(3)上⾯的窗⼝中,可以看到 Rules 与 Inputs 两个命令是红⾊的,表⽰RUN DRCDRC-可以帮(4)点击Inputs 命令,在Layout命令⾏⾥输⼊你要检查的版图的GDS,假如你已经把当前版图输出GDS了,可以输⼊已经⽣成的GDS。

Calibre使用简介

© 2006 微电子中心

2020年2月

8

因为做DRC 会产生很多文件,建议建立一个专属于此Layout 做DRC 时的 新文件夹。然后拷贝Rule File 至此工作目录下。

从版图中导出GDS文件至此工作目录下,亦可在Calibre DRC 图形界面中 选择从当前版图中导出GDS文件。

© 2006 微电子中心

Commercial Verification Tools

Cadence

Dracula

Synopsys

Hercules������

Mentor

Calibre

© 2006 微电子中心

2020年2月

5

What are I/Os for DRC and LVS?

Inputs Layout <GDSII> Schematic or Netlist <SPICE> (LVS only) Rule Files <ASCII>

© 2006 微电子中心

2020年2月

12

DRC Rule File

Calibre 是一个基于边(edge)的DRC/LVS 工具,所有的运算都 是基于“边”来进行的。边有内边和外边之分。

如上图所示,任一个polygon 的边都分为两部分,polygon 内部 那一面的称为内边(interior side edge),外部的称为外边 (exterior side edge)。理解这个定义对于理解calibre 复杂的指 令是十分有用的。

上面介绍了Internal、External、Enclosure 三条指令,剩余的指 令请参阅calibre 的文档。

calibre 的指令集十分复杂,足以完成各种规则的DRC 检查, designer 要理解所有的指令才可以用好calibre。

calibre_v2lvs

calibre自带v2lvs命令使用指南发表于13 天前⁄系统工具⁄暂无评论⁄被围观208 views+做为现今流行的深亚微米集成电路物理验证工具,calibre 有其强大的功能,其v2lvs命令能够方便的把verilog格式网表转为spice格式网表,对于IC后端的工程师来说是非常有用,且有必要掌握的。

命令:v2lvs可用参数:[-l verilog_lib_file] [-lsp spice_library_file] [-lsr spice_library_file] [-s spice_library_file] [-s0 groundnet] [-s1 powernet] [-sk] [-p prefix] [-w warning_level] [-a array_delimiters] [-c char1[char2]] [-u unnamed_pin_prefix] [-t svdb_dir] [-addpin pin_name] [-b] [-n] [-i] [-e] [-h] [-cb][-ictrace] 参数介绍:··-v verilog_design_fileSpecifies the filename of the input Verilog structural netlist.·-o output_spice_fileSpecifies where to place the output LVS SPICE netlist. Default is standard out. ·-l verilog_lib_fileSpecifies the location of the Verilog primitive library file. It is not translated. ·-lsp spice_library_fileSpecifies SPICE library file name using pin mode. The SPICE file is parsed for interface configurations. Pins with pin select ([ ]) annotation are kept as individual pins using escaped identifiers.·-lsr spice_library_fileSpecifies SPICE library file name using range mode. The SPICE file is parsed for interface configurations. Pins with pin select ([ ]) annotation are assembled into Verilog ranges.·-s spice_library_fileSpecifies that the -o output file have a .INCLUDE statement placed at the beginning that points to the SPICE library file.·-s0 groundnetSpecifies the default net name for mapping to pin connections with a value of zero (0). Outputs the specified names in place of Verilog supply0 nets and generates .GLOBAL declarations in the output netlist.·-s1 powernetSpecifies the default net name for mapping to pin connections with a value of one (1). Outputs the specified names in place of Verilog supply1 nets and generates .GLOBAL declarations in the output netlist.·-skSpecifies that Verilog supply0 and supply1 nets are not connected to the global power and ground nets.·-p prefixAdds prefix to Verilog gate level primitive cells.·-w warning_levelControls the amount of warning message output. Possible level choices are:0 Selects to output no warning messages.1 Selects to output warning messages for skipped blocks and modules only.2 Selects to output level 1 and calls to undeclared modules and pin arrays with widths wider than ports. This is the default.3 Selects to output level 2 and called port array mismatches and unsupported compiler directives.4 Selects output level 3 plus all ignored constructs.·-a array_delimitersChanges the array delimiter characters. The default is [ ].·-c char1[char2]Sets the substitution characters for escaped identifier characters illegal in SPICE. char1 replaces $, comma, (, ), and =. char2 replaces /. No space is needed between the two user-supplied arguments.·-u unnamed_pin_prefixSpecifies a prefix to add to unnamed pin connections in module instantiations. ·-t svdb_dirAdds source netlist pin direction information to the SVDB. This is used in Calibre xRC.·-addpin pin_name。

calibre使用帮助

◦ 各器件及PIN已生成 ◦ 黄线提示各节点连接关系 ◦ 可相应补充连线等图形

环境设置 版图设计 版图验证

◦ DRC ◦ LVS ◦ PEX

导出文件

◦ 导出CDL文件 ◦ 导出GDSII文件

总结

calibre功能列表

DRC -- Design Rule Checking ERC -- Electrical Rule Checking LVS -- Layout Versus Schematic PEX -- Post-layout Extraction RVE -- Results Viewing Environment 显示结果用的环境窗口 ◦ SVDB -- Standard Verification Database 显示LVS结果 ◦ ◦ ◦ ◦ ◦

◦ 双击错误可定位,图中高亮部分

◦ 也可在lvs.rpt中找到对应信息

◦ 正确提示

环境设置 版图设计 版图验证

◦ DRC ◦ LVS ◦ PEX

导出文件

◦ 导出CDL文件 ◦ 导出GDSII文件

总结

◦ 选择pex rule ◦ 为PEX设定专门的目录

◦ 做PEX之前都会做一次LVS ◦ 因此输入需要选择网表文件

环境设置 版图设计 版图验证

◦ DRC ◦ LVS ◦ PEX

导出文件

◦ 导出CDL文件 ◦ 导出GDSII文件

总结

◦ 选择lvs rule ◦ 为LVS设定专门的目录

◦ 设定输入 ◦ 选中复选框,让工具自动生成网表

◦ 设定输入 ◦ 选择已经生成的网表(通常是CDL文件)

calibre使用介绍

设定inputs

• Rule载入后,calibre自动跳转到inputs,同 时file自动指到当前的layout cell name 。在 鼠标点选的地方有个export from layout viewer选项,这个是由calibre直接从layout 抽取GDS,从而不需要layout designer在进行 DRC验证前单独stream out gds file.

Run DRC

• 当设置完成后,点击Run DRC的选项, calibre工具开始按照载入的rule进行DRC验 证。

• 另外,calibre DRC可以对有特殊要求的 layout进行其他设置,如果有需要可以在 DRC options里面进行设置,但是一般情况 下不需要做改动。

DRC result

CALIBRE 使用介绍

Calibre 简介

• Calibre是一套类似于Diva的验证软件,其操 作简单,可以做on-line 的验证,更可以搭 配virtuoso或其他layout软件,因此calibre已 经被大多数公司采用。

Calibre 主要用途

• Calibre主要用于以下2个方面的验证: • DRC (Design Rule Check) • LVS (Layout Versus Schematic)

Comparison result

• 这个result里面包含了: 1.Incorrect nets 2.Incorrect ports 3.Incorrect instances 4.Property Errors 一般我们clean的顺序是从2开始然后是1,基 本上前两项clean后,后面的2项就OK了。

LVS(layout versus schematic)

Calibre验证工具使用指南

Calibre DRC/LVS使用指南单元库设计B组:吴亮马艳目录1.Calibre验证工具简介 (3)1.1Calibre DRC (3)1.2Calibre LVS (3)2.DRC可视化界面的使用 (3)2.1.运行步骤 (3)2.2.如何选择规则 (7)2.3.如何使用Group语句 (7)2.4.如何检查版图的被选区域 (7)3.LVS可视化界面的使用 (7)3.1.运行步骤 (7)3.2.Hcell的使用 (11)3.3.如何使用LVS BOX (11)3.4.短路和开路 (11)4.常见问题 (11)4.1 DRC使用中的常见问题 (11)4.2 LVS使用中所发生的问题 (12)5.rulefile文件的语法 (12)5.1基本的规则语法 (12)5.2 Rule file文件对大小写的区分 (12)5.3 Rule file文件的顺序 (13)5.4 INCLUDE语句 (13)5.5 如何使用条件语句 (13)5.6典型的LVS规则语法 (13)5.7 TEXT的语法 (14)5.8 如何将TEXT连接到目标层 (14)5.9 连接的建立 (14)5.10 软连接 (15)5.11 Property Tracing 语句 (15)5.12 REDUCE语句 (15)5.13 Antenna天线效应 (15)5.14 通过Calibre产生GDSII格式的输出 (16)5.15 LVL的使用 (16)6.用命令行执行Calibre (16)7.帮助文档 (17)1.Calibre验证工具简介Calibre是Mentor公司的一个版图验证工具,其主要包括DRC(Design Rule Checking设计规则验证),LVS(Layout Versus Schematic版图与原理图对照验证)和RVE(Result Verification Environment 验证结果环境).它可以进行Hierarchical(层次化)的验证,是一套支持多种格式的功能十分强大的验证工具。

calibre版图drc,lvs,pex和后仿真smic65

生成版图以及calibre的DRC、LVS、PEX和后仿真在schematic界面:Tools--design synthesis--layout XL;在layout界面:Design--generate from source,出现下图,按照下图所示进行选择:注意,在I/O pins,一列中,修改完后一定要单击Apply;Pin type一列,一定要单击undate;pin Label shape一列,单机呢Pin label options,出现右图,layer name改为选择same as pin。

然后单击ok,ok。

接下来,自动生成了mos管的版图,我们需要做的是进行连线。

首先按键盘F键,使图居中;然后按shift+ F键,出现详细的mos管内部结构图;之后,在菜单栏单击options—display,出现下图:X snap spacing和Ysnap spacing调的越小,画线时的精度就越大。

Display levels里的stop,一般写20,表示显示的层数。

开始连线,画版图。

、、、、、///画完以后,进行DRC检查:在layout界面:calibre--run drc,出现下图:第一次进行drc时,在load runset file对话框里,单击cancel。

单击Rules标签,在DRC rules file里,单击“…”,选择DRC文件,DRC Run directory里选择运行的目录,最好自己新建一个文件夹。

单击input标签,出现下图:选中export from layout viewer,单击output标签,出现下图:不用改其他都不用改,单击run DRC标签,开始检查设计规则。

界面如下图:将show all 改为show not waived,变成下图:红色的就是不满足设计规程的,需要改版图。

右击下图右边的数字,如“19,20,21,22”,选择highlight,就会在版图界面放大并标出出错的地方。

Calibre经典教程和看LVS的错误报告的方法

Calibre经典教程和看LVS的错误报告的方法看calibre lvs 错误报告的方法1.Report开头部分的Warning和Error信息(因为出现Warning和Error的情况很多,这里主要举一些常见的例子):∙Error部分:只要report的开头部分有Error信息出现,lvs就肯定没有运行成功。

Error一般由lvs命令文件或netlist文件中的参数定义引起,这时候需要修改lvs文件或者netlist。

Error信息都很直观,比较容易查出产生Error的地方。

o Example1 (参见文件“lvs_test1.rep”) :在”lan_yang_dig.cir”的2191和2192行调用到了两个标准单元”INLX1”和”LOGICOL”,但是netlist中找不到对这两个标准单元的描述。

这个错误需要检查netlist,添加上对这些标准单元的描述部分。

通常标准单元的netlist由foundry提供,是一个单独的cdl或者spice文件;Example1:LVS Netlist Compiler - Errors and Warnings for "LANYANG_FULLCHIP_V11_20060427.CIR"-------------------------------------------------------------Error: No matching ".SUBCKT" statement for "INLX1" at line 2191 in file "lan_yang_dig.cir"Error: No matching ".SUBCKT" statement for "LOGIC0L" at line2192 in file "lan_yang_dig.cir"..................Warning部分:warning不会影响lvs的运行,但是经常会导致结∙果的不正确。

928142-集成电路-calibre_lvs

Calibre物理验证之--- LVS

第八步

Run完后, 会弹出两 个窗口, 一个是 report,一 个是lvs RVE的, 如右图, 有笑脸的 为lvs ok 的。

Calibre物理验证之--- LVS

第九步

下面我们 来看一下 有错的时 候,报告 会是怎么 样的。

首先看一 下lvs report文件, 有一个叉 号,说明 此cell有误。

Calibre物理验证之--- LVS

第二步

在相应位置 填入相应的 文件路径及 名称,lvs commandfile 然后load一下。 选择验证路 径。

Calibre物理验证之--- LVS

第三步

点击左侧第二 项inputs,选 择layout项, 如果把 “export from layout viewer” 选项选中,则 默认为系统 Stream out GDS。如果此 选项关闭,则 需要自己选择 验证所需GDS。

CALIBRE物理验证之-LVS

张侠

Calibre物理验证之--- LVS

下面我们来学习利用calibre进行lvs验证, 首先我们把需要的文件放到同一个路径下:建 立一个lvs的路径,把lvs commandfile、 netlist等放到lvs路径下。

第一步

打开所要run 的cell,点击 窗口菜单栏 里的calibre, 选择run lvs, 会弹出如右 图窗口。

Calibre物理验证之--- LVS

第四步

点击Netlist选 项,在Files 栏里填入 netlist的路径 和名字(可 以浏览选 择),在Top cell栏里填入 要验证 的cell 在netlist中的 名称。

Calibre物理验证之--- LVS

calibredrv常用指令

calibredrv常用指令1. 简介calibredrv是一个用于管理电子书库的命令行工具。

它基于Calibre电子书管理软件,并提供了一些常用的指令,用于管理和操作电子书库。

在本文中,我们将介绍calibredrv的常用指令,包括安装和配置calibredrv,创建和管理电子书库,导入和导出电子书,以及其他一些有用的功能。

2. 安装和配置安装calibredrv要安装calibredrv,可以使用pip命令进行安装。

打开终端,并执行以下命令:pip install calibredrv配置calibredrv安装完成后,需要进行一些配置,以便连接到Calibre电子书库。

首先,需要知道Calibre的电子书库位置。

可以通过在终端中执行以下命令来查找:calibre-debug -c "import calibre.utils.config; print(calibre.utils.config.pref erences_dir)"然后,将找到的路径添加到配置文件中。

配置文件位于用户的主目录下的.calibredrv文件夹中。

在此文件夹中,可以找到一个名为config.yml的文件。

将以下内容添加到config.yml文件中:calibre_db: /path/to/calibre/library/metadata.db3. 创建和管理电子书库创建电子书库要创建一个新的电子书库,可以使用以下命令:calibredrv create-library /path/to/library这将在指定的路径下创建一个新的电子书库。

删除电子书库要删除一个电子书库,可以使用以下命令:calibredrv delete-library /path/to/library这将删除指定路径下的电子书库。

列出电子书库要列出当前所有的电子书库,可以使用以下命令:calibredrv list-libraries这将列出所有已创建的电子书库的路径。

CalibreLVSBOX的详细用法

CalibreLVSBOX的详细用法例如下面的buf包含两个inv单元:

对应的buf版图,inv单元版图只预留PIN:

勾选Calibre LVS中的LVS Options选项。

然后在LVS Options→include中勾选Include Rule Statements,并输入:

LVS BOX inv

Run LVS结果会有BOX单元提示。

2、匹配版图和电路不同名。

例如如版图的名称是inv_box,但电路依然为inv,这种情况需要使用到H-cells。

首先需要创建一个hcell文件,按照格式:[版图名][空格][电路名]的格式输入信息。

然后在Inputs→H-Cells中勾选Use H-Cells file,并选择上述的hcell文件。

同时也需要修改LVS Options→include→Include Rule Statements信息。

最后Run LVS。

3、匹配多个不同名的版图和同一个电路。

同一个inv可能由于版图的形状不同等原因存在不同名的单元,假设电路inv,版图有inv_box和inv_ip。

在上一种情况的基础上修改hcell文件。

inv_box inv

inv_ip inv

修改LVS Options→include→Include Rule Statements信息。

最后Run LVS。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

•

了重要的数据文件和子目录,并且在用

RVE反标及xCalibre

• 的数据;

进行寄生参数提取时需要用到该目录下

• TOPCELL.rep Calibre LVS Report File,所有 的错误信息均在该文件中,

•

查错过程主要就是基于此文件;

• TOPCELL.rep.ext Calibre LVS Extraction Report

Calibre LVS的使用方法

3.3 Calibre LVS的执行命令:

cd ~/check/calilvs (进入LVS的运一次LVS产生的数据目录,以免影响本次执行结果)

calibre –lvs -hier -spice ./svdb/TOPCELL.sp –hcell hcells -auto ../rule/CLVS.ru |tee TOPCELL.log

File;

• CLVS.ru Calibre LVS规则文件。

Calibre LVS is OK !

Calibre LVS Report File

Circuit Extraction Report File

Connectivity Errors Calibre LVS

Failed !

Calibre LVS Report File

Circuit Extraction Report File

(5) –hcell hcells表示额外得将hcells文件中指定的Layout和电路网表单元进行 比较并在最后的报告中给出相应的比较结果。hcells也可以用其它的文件名

• 3.4 Calibre LVS所用到和产生的文件列表及说明:

• svdb/

这是Calibre LVS在执行过程中

自动产生的目录,里面存放

可以任意指定TOPCELL.sp和TOPCELL.log文件名,这里用同样的前缀也是为了 保证同一次验证结果数据文件的一致性;

该命令可以最简单的用 calibre –lvs ../rule/CLVS.ru 代替,其它选项可根据需要部分或 全部选择使用:

(1) |tee TOPCELL.log 表示屏幕显示信息输出到TOPCELL.log文件中; (2) –spice ./svdb/TOPCELL.sp表示将Layout提取后生成TOPCELL.sp文件; (3) -hier表示层次式校验,不是将整个版图 Flatten 后进行校验; (4) –auto表示额外得将Layout和电路网表中名字相同的单元进行自动比较并在 最后的报告中给出相应的比较结果