Formality_Debugging_FailingVerificationsLabInstructions

Synopsys Formality EC Solution说明书

DATASHEETOverview Formality ® is an equivalence-checking (EC) solution that uses formal, static techniques to determine if two versions of a design are functionally equivalent.Formality delivers capabilities for ECO assistance and advanced debugging to help guide the user in implementing and verifying ECOs. These capabilities significantly shorten the ECO implementation cycle.The size and complexity of today’s designs, coupled with the challenges of meeting timing, area, power and schedule, requires that the newest, most advanced synthesis optimizations be fully verifiable.Formality supports all of the out-of- the-box Design Compiler ® and Fusion Compiler™ optimizations and so provides the highest quality of results that are fully verifiable.Formality supports verification of power-up and power-down states, multi-voltage, multi- supply and clock gated designs.Formality’s easy-to-use, flow-based graphical user interface and auto-setup mode helps even new users successfully complete verification in the shortest possible time.Figure 1: Formality equivalence checking solutionIndependent formalverification of DesignCompiler and FusionCompiler synthesisresults, with built-in intelligencedelivering the highestverifiable QoRFormality Equivalence Checking and Interactive ECOKey Benefits• Perfect companion to Design Compiler and Fusion Compiler—supports all default optimizations• Intuitive flow-based graphical user interface• Verifies low-power designs including power-up and power-down states• ECO implementation assistance, fast verification of the ECO, and advanced debugging• Auto setup mode reduces “false failures” caused by incorrect or missing setup information• Multicore verification boosts performance• Automated guidance boosts completion with Design Compiler and Fusion Compiler• Verifies full-custom and memory designs when including ESP technologyFormalityThe Most Comprehensive Equivalence Checking SolutionFormality delivers superior completion on designs compiled with Design Compiler or Fusion Compiler. Design Compiler is the industry leading family of RTL Synthesis solutions. Fusion Compiler is the next generation RTL-to-GDSII implementation system architected to address the complexities of advanced process node design. Designers no longer need to disable the powerful optimizations available with Design Compiler or Fusion Compiler to get equivalence checking to pass. Design Compiler/Fusion Compiler combined with Formality delivers maximum quality of results (QoR) that are fully verifiable.Easy to Use with Auto-setup modeFormality’s auto-setup mode simplifies verification by reducing false failures caused by incorrect or missing setup information. Auto-setup applies setup information in Formality to match the assumptions made by Design Compiler or Fusion Compiler, including naming styles, unused pins, test inputs and clock gating.Critical files such as RTL, netlists and libraries are automatically located. All auto-setup information is listed in a summary report.Guided SetupFormality can account for synthesis optimizations using a guided setup file automatically generated by Design Compiler or Fusion Compiler. Guided setup includes information about name changes, register optimizations, multiplier architectures and many other transformations that may occur during synthesis. This correct-by-construction information improves performance and first-pass completion by utilizing the most efficient algorithms during matching and verification.Formality-guided setup is a standard, documented format that removes unpredictability found in tools relying on log file parsing.Independent VerificationEvery aspect of a guided setup flow is either implicitly or explicitly verified, and all content is available for inspection in an ASCII file.Figure 2: Automatic cone pruning improves schematic readability when debuggingHier-IQ TechnologyPatented Hier-IQ technology provides the performance benefits of hierarchical verification with flat verification’s out-of- the-box usability.Error-ID TechnologyError-ID identifies the exact logic causing real functional differences between two design representations. Error-ID can isolate and report several logic differences when multiple discrepancies exist. Error-ID will also present alternative logic that can be changed to correct a given functional difference; this flexibility allows the designer to select the change that is easiest to implement.Failing Pattern Display WindowAll failing input patterns can be viewed in a familiar spreadsheet-like format. The failing pattern window is an ideal way to quickly identify trends indicating the cause of a failing verification or improper setup.Figure 3: Problem areas can be easy identified by visual inspection of the Failing Pattern WindowPower-aware VerificationFormality is fully compatible with Power Compiler™ and verifies power-up and power-down states, multi-voltage, multi-supply and clock gated designs.When a reference design block is powered up, Formality verifies functionality. If the implementation design powers up differently, failing points will occur.Formality functionally verifies that the implementation powers down when the reference powers down and will detectfunctional states where the implementation does not power down as expected. The valid power states are defined in the power state table (PST).Power intent is supplied to Formality through IEEE 1801 Unified Power Format (UPF).Figure 4: Power connectivity is easy to see and debug from the schematic viewAccelerated Time to ResultsFormality’s performance is enhanced with multicore verification. This Formality capability allows verification of the design using up to four cores simultaneously to reduce verification time.Other Time-Saving FeaturesFormality’s Hierarchical Scripting provides a method to investigate sub-blocks without additional setup and is ideal for isolating problems and verifying fixes.The Source Browser opens RTL and netlist source files to highlight occurrences of a selected instance. This can help users correlate between the RTL and gate-level design versions.Error Region Correlation provides a quick, visual identification of the logic from one design that correspond to the errors isolated by Error-ID within the other.Command Line Editing allows you to take advantage of history and common text editor commands when working from Formality’s command line.Interactive ECOKey BenefitsProvides GUI-driven ECO implementation assistance, fast ECO verification, and advanced debugging. Formality guides the user through the implementation of ECOs, and then quickly verifies only the changed logic.Formality Interactive ECO FlowFormality uses the ECO RTL and an unmodified netlist. Guided GUI driven changes are made to the netlist. Once the ECO has been implemented, a quick verification is run on only the affected logic cones, eliminating the need for a full verification run on the design to verify that the ECO was implemented correctly.Once all ECO’s are implemented and fully verified, a list of IC Compiler™ commands is generated to assist in implementing the physical changes to the design.ECO GuidanceFormality highlights equivalent nets between the reference and implementation designs, and nets that have lost their equivalence due to the ECO changes in the reference. This helps the designer quickly identify where the change should be made in the implementation.Implementing the ECOEditing commands in Formality are used to modify the netlist in-place using the GUI.Rapid ECO VerificationFormality can identify and verify just the portion of the design affected by the ECO. This ensures that the ECO was implemented correctly. If the ECO verification fails, the ECO can be interactively “undone” and new edits can be made again. Once the partial verification passes, the changes are committed. This partial verification eliminates having to verify the entire design to assure that the ECO was implemented correctly, dramatically reducing the total time required to implement and verify the ECO.Figure 5: Equivalent net is highlighted between Reference design (left) and Implementation design (right)Figure 6: On a completed ECO, the schematic shows the nets affected by ECO in yellow, and the new component and net in orangeFigure 7: Formality transcript shows a successful partial verification of the portion of the design that was affected by the ECOInterface with IC Compiler IIOnce the ECO’s are implemented and verified, a final complete verification run is performed to assure that the ECO RTL and the ECO netlist are functionally equivalent.Formality produces IC Compiler II compatible ECO command file, easing the implementation in the physical design.Advanced DebuggingFormality incorporates advanced debugging capabilities that help the designer identify and debug verifications that do not pass. The designer can find compare points, equivalences (and inverted-equivalences) between reference and implementation designs, perform “what if” analysis by interactively modifying the designs, and verify equivalence between two (or multiple) points.Transistor VerificationESP combines with Formality to offer fast verification of custom circuits, embedded memories and complex I/Os. ESP technology directly reads existing SPICE and behavioral RTL models and does not require restrictive mapping or translation.Input Formats• Synopsys DC, DDC, Milkyway™• IEEE 1800 SystemVerilog• Verilog-95, Verilog-2001• VHDL-87, VHDL-93• IEEE 1801 Unified Power Format (UPF)Guided Setup Formats• Synopsys V-SDC• Formality Guide Files (SVF)Platform Support• Linux Suse, Red Hat and Enterprise• SPARC SolarisFor more information about Synopsys products, support services or training, visit us on the web at: , contact your local sales representative or call 650.584.5000.©2019 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks isavailable at /copyright.html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.。

formality简介

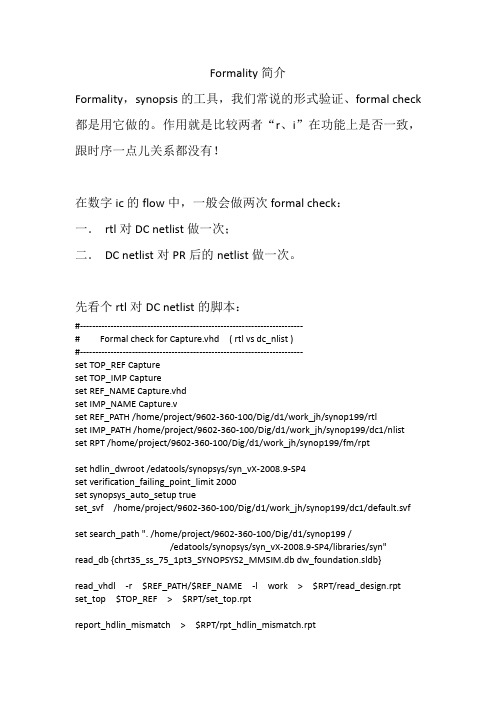

Formality简介Formality,synopsis的工具,我们常说的形式验证、formal check 都是用它做的。

作用就是比较两者“r、i”在功能上是否一致,跟时序一点儿关系都没有!在数字ic的flow中,一般会做两次formal check:一.rtl对DC netlist做一次;二.DC netlist对PR后的netlist做一次。

先看个rtl对DC netlist的脚本:#-------------------------------------------------------------------------# Formal check for Capture.vhd ( rtl vs dc_nlist )#-------------------------------------------------------------------------set TOP_REF Captureset TOP_IMP Captureset REF_NAME Capture.vhdset IMP_NAME Capture.vset REF_PATH /home/project/9602-360-100/Dig/d1/work_jh/synop199/rtlset IMP_PATH /home/project/9602-360-100/Dig/d1/work_jh/synop199/dc1/nlist set RPT /home/project/9602-360-100/Dig/d1/work_jh/synop199/fm/rptset hdlin_dwroot /edatools/synopsys/syn_vX-2008.9-SP4set verification_failing_point_limit 2000set synopsys_auto_setup trueset_svf /home/project/9602-360-100/Dig/d1/work_jh/synop199/dc1/default.svf set search_path ". /home/project/9602-360-100/Dig/d1/synop199 //edatools/synopsys/syn_vX-2008.9-SP4/libraries/syn"read_db {chrt35_ss_75_1pt3_SYNOPSYS2_MMSIM.db dw_foundation.sldb}read_vhdl -r $REF_PATH/$REF_NAME -l work > $RPT/read_design.rptset_top $TOP_REF > $RPT/set_top.rptreport_hdlin_mismatch > $RPT/rpt_hdlin_mismatch.rptread_verilog -i $IMP_PATH/$IMP_NAME -l work >> $RPT/read_design.rpt set_top $TOP_IMP >> $RPT/set_top.rpt#set_constant -type port r:/.../ 0#set_constant -type port i:/.../ 0match > $RPT/match.rptreport_matched_points > $RPT/matched_point.rptreport_unmatched_points > $RPT/unmatched_point.rptreport_loops -limit 0 -unfold > $RPT/loops.rptverify#以上内容可以放在一个文件里作为脚本,调用方法就是在fm_work下$ fm_shell –f ../scripts/fm_rtl2dc.tcl如果成功要看详细信息或者失败要debug的话,再输入start_gui,进入-GUI模式。

Conformal_Verification_Guide_8.1

I N VE N TI V ECONFIDENTIALFormal Verification GuidePrototype | Implement | VerifyAgenda• Equivalence Checking Refresh • Verification Guide– RTL Design – Verifiable Synthesis Flow – Abort Resolution• ECO Automation • Best Practice Recommendation2August 6, 2009Cadence ConfidentialEncounter Conformal Product FamilyVerifies 100% of design functionality without requiring test vectors Provides independent verification for lowest risk silicon Validates CPF LP Equivalence Checking Verifies Low Power design implementation Performs structural and functional checksEquivalence CheckingRTL or Gate RTL or GateDigital Custom Verification including Memories, Data Paths, and IO Orders of magnitude faster than simulationLow Power VerificationFunctional Checksv1v2ISOABFinds bugs earlier in the design cycle Verifies proper CDC synchronization to avoid clock related re-spins Creates safer EC environmentValidation, generation and analysis of constraints Uses industry proven formal engines Shorter design cycle with improved timing constraintsConstraint DesignECO Implementationo1 o2Provides automated RTL2GDS ECO solution Identifies and generates fix to implement ECO Interfaces with physical implementation tool flow3August 6, 2009Cadence ConfidentialEncounter Conformal & FED Product FamilyEquivalence CheckingRTL or Gate RTL or GateConstraint DesignLow Power VerificationFunctional ChecksAValidation, generation & analysis of constraints Shorter design cycles with improved timing constraintsv 1v2ISOB100% Independent vector-less verification of implementation RTL Gate Transistor CDC & Ext ChecksStructural and functional LP checks LP design implementation Verification LP Equivalence CheckingNew Products ECO Implementation RC-Physical Synthesis Chip Planning Systemso 1 o 2Automated RTL2GDS ECO solution Identifies and generates ECO fix Physical Correlation & Predictability with final backend Congestion Analysis & Opto (Congestion Relief) Architectural & Economic Forecasting Lower IC Cost & Expedite TTM4August 6, 2009Cadence ConfidentialI N VE N TI V ECONFIDENTIALCrash Course on Equivalency CheckingPrototype | Implement | VerifyEquivalence Checking FlowGolden Design Standard Library Revised DesignSpecify Constraints and Design ModelingSetup Mode LEC ModeSpecify Compare ParametersCompare DesignsMiscompare?yesDiagnosenoEquivalence Checking Complete6August 6, 2009Cadence ConfidentialMapping! What is that?Pairing corresponding golden and revised key points:G RPI PO DFF DLAT BBOX CUT Z EPI PO DFF DLAT BBOX CUT Z E Key points Combinatorial logicGolden RevisedE UExtra Points Unreachable Points Unmapped Points7August 6, 2009Cadence ConfidentialComparison– Only mapped points can be compared. – Comparison is an iterative process.• Conformal remembers points already compared. • Comparison can be interrupted with Control-c. • Enter compare to continue comparing.set log file logfile.$LEC_VERSION -replace add notranslate module *sram* -library -both read design cpu_rtl.v -verilog -golden read design -file verilog.vc -verilog -revised // Command:pin constraint 0 scan_en -revised add compare ================================================================================ set flatten model -latch_fold Compared points PO DFF DLAT BBOX Total add renaming rule rule0 "abc" "xyz" -map -revised -------------------------------------------------------------------------------Equivalent renaming rule rule1 "xyz" "C" -map -golden 2 146 2 1 151 add -------------------------------------------------------------------------------set system mode lec Non-equivalent 0 2 0 0 2 add compare points -all ================================================================================ compare ...8August 6, 2009Cadence ConfidentialUsing the Mapping Manager to Debug NEQsMain windowUnmapped pointsMapped pointsCompared points9August 6, 2009Cadence ConfidentialCategories of Comparison ResultsEquivalent: Key points proven to be equivalent (green-filledcircle)Inverted-Equivalent: Key points proven to be complementary (divided green-filled circle) Nonequivalent: Key points proven to be different (red-filled circle) Abort: Key points not yet proven equivalent or nonequivalent due to timeout or other system parameters (yellow-filled circle) Not-Compared: Key points not yet compared?10LEC> report compare data -class [...]August 6, 2009Cadence ConfidentialI NVENTIVE CONFIDENTIAL RTL DesignFor Ease of VerificationRTL Design For Ease of Verification•To highlight the impact of RTL design on verification –Useful for RTL designers to understand their impact of coding styles on verification–Useful guidelines for machine/script generated RTL codes •Factors in RTL designs that can affect the ease of verifications are–Don’t care conditions in RTL description–Structuring of logics–Partitioning of designsRTL Design For Ease of VerificationDon’t-Cares Conditions in RTL•Don’t-care conditions are created in RTL by–X assignments–Incomplete case–Out-of-range indexing–Range constraint (VHDL)• A don’t-care condition can be synthesized to– a constant (zero or one)–or any Boolean function•Designs with extensive don’t-care conditions can be difficult to verify •Use LEC “report design data”to report don’t cares•Use LEC “report rule checks”to report out-of-range indexingRTL Rule Checkers•LEC’s RTL rule checker provides an fast and easy way to detect RTL coding styles that can impact verification •For example, index out of range is reported as –// Warning: (RTL7.3) Array index in RHS might be out of range (occurrence:1)•Running LEC RTL rule checker early in the RTL design process can reduce many potential synthesis andverification issues later onRTL Rule CheckersSETUP> read design –golden rtl.vSETUP> read design –revised rtl.vSETUP> set system mode lecSETUP> report rule check –golden –design –verbose > lint.rptSETUP> report message –golden –model –verbose > model.rpt•Consider Synthesis and EC ramifications of design –Multiply-driven and floating nets–Combinational cycles–Assignment size mismatch–Ambiguities leading to simulation mismatches–EtcRTL Design For Ease of VerificationDon’t-Cares Due to Index Out of Range•Don’t care is created when index is out of range –When the index can address more locations thanwhat an array can hold•For examplereg[4:0] q; // q has 5 locationsReg[2:0] A; // A can index 8 locationsBAD -q[A];// (1) out-of-range conditionGOOD -q[(A> 4) ? 0: A)];// (2) No out-of-rangeLogic Structuring•Structural Similarity–How closely does RTL structure match the netlist •Designs with higher structural similarity between RTL and netlist are easier to verify•Synthesis can restructure code. For examples:–Resource sharing–Map unsigned operators to signed operators•Minimize structural differences between RTL and netlist by:–Using Verilog 2K to code signed arithmetics–Using explicit grouping (such as in additions) with parenthesis –Manually code resource sharingDesign Partitioning•Partitioning a complex block breaks it into smaller pieces for ease of verification•Guidelines–Keep high complexity design modules small in size–Avoid excessive logic cone depth–Separate datapath block (especially those requiring retiming) from control block–Partitioning may impact QOR so the tradeoffs should be explored early in the design cycle•Smaller blocks are easier to verify. Well partitioned designs can also make use of more techniques to ease verificationsI NVENTIVE CONFIDENTIAL Verifiable Synthesis FlowModule Data PathArchitecture & Advanced Synthesis Optimizations Create Verification Challenges DatapathArchitectureBoundary OptimizationPhase Inversion Resource Sharing• A synthesis flow with verification considerations can significantly reduce verification challenges–Enable the identification of synthesis bugs more easily–Allow use of more LEC features (e.g., module-based datapath analysis, hierarchical comparisons) to streamline the verification processL E CSynthesis Optimization on Datapath Modules•Synthesis tools like RC and DC can group several datapath operators into asingle datapath unit which called datapath module. These modules can be synthetic or they can be instantiated components such as DW modules•For Design Compiler, these modules are reported in the resource report with string DP_OP as naming convention•These modules boundary are not preserved if ungrouping and boundary optimization are applied, making them difficult to prove Synthesis Flow Needs To Be Verification-Friendly R T L D a t a p a t h D e si g n ungroup/boundary optimizationMulti-Stage Synthesis•The basic principle of ensuring ease of verification is to break difficult to verify synthesis optimizations intostages in the synthesis flow•Recommend synthesis stages–RTL to first mapped netlist•Enable: datapath synthesis•Disable: ungrouping, boundary optimizations, phase inversions –Mapped netlist to optimized mapped•Enable: Ungrouping, Incremental optimizations, boundaryoptimizationsEmbed Verification Requirements in Synthesis •To deploy an easy to verify synthesis flow, embed the verificationsinto the synthesis scripts–Instead of resynthesizing after running into verification challenges •Control synthesis options that impact verification, e.g.,–Range constraint–Datapath synthesis, resource sharing–Ungrouping, boundary optimizations•Allow for a range of verification requirements to allow for trade-offs in verifiability•This is default behavior for Encounter RTL Compiler (RC)LEC Feature Module Based Datapath (MDP) Analysis (DC Synthesis)•Datapath synthesis may cause aborts because of operator optimization.•This is handled in RTL Compiler with Netlist Verification (more later). DC netlists require MDP.•Module-Based Datapath (MDP) Analysis performs datapath abstraction at a module level•This analysis is performed in addition to and prior to the regular operator level analysis•The result goal is to improve the quality of the operator-level analysis•Requires the preservation of synthetic datapath modules during synthesisRTLRTLFinal GateDC Script LE C DC Script Original Flow New Flow RTL FinalGate DC + MDP Script Intermediate Gate L E C LE C •Include MDP Script •Output Intermediate &Final Netlist•Perform RTL2Gate•Perform Gate2Gate Improve Synthesis Script to Ensure Verification Success (MDP) Analysis (DC Synthesis)DC Synthesis Script to Enable MDP Analysis•To enable the successful verification of datapath design using Design Compiler synthesis, LEC provides a script to ensure that LEC’s Module-Based Datapath (MDP) Analysis can be effectively applied•The script can be embedded into the overall synthesis script as followssource <lec_release_path>/share/cfm/lec/scripts/mdp.tcl…compile_ultra_mdp<level> <design_module>compile_ultra……<continue original DC synthesis script commands>…•compile_ultra_mdp command is placed before the first compile_ultra command in the DC script•Design module is the name of the top module that is synthesizedDC Synthesis Script for Datapath Verification •MDP level can be 1, 2, 3, or 4, and affects the synthesis as followsMDP Level Preserve Hierarchy ofBoundaryOptimizationSequentialOutputInversion DP/DW Design1YES NO ALLOW ALLOW 2YES NO DISABLE ALLOW 3YES NO DISABLE DISABLE 4YES YES DISABLE DISABLECollecting DC Synthesis Data•During the synthesis process, the following information should be collected for verification–Datapath Resource File: This is required to ensure that datapath intensive design can be easily verified–Change Name File: This is required to ensure name-based mapping for ease of verification–VSDC File: This file contains information that can help to guide the setup of the verification–Synthesis log file: This can contain information to help guide the setup of the verificationLEC Feature Qualifying Your DC Synthesis Environments •New versions of synthesis tools may introduce new verificationrequirements–New optimization techniques (e.g., sequential constant groups)–New datapath structures (e.g., new multiplier architectures)–New technology mapping techniques (e.g., using multi-bit library cells)–Changes in naming conventions (e.g., in generate statements)–Changes in default synthesis option settings (e.g., having sequential merge optimizations ON by default)•LEC ships with IP-free designs that can be used as testcases in a new synthesis environment or tool–Enable users to provide early feedbacks to the Conformal team to ensure success of verifications in the latest synthesis environment –At $conformal_dir/share/cfm/lec/demo/*How to Determine QoR ImpactRTL RTLFinalGate DC ScriptL E CDCScriptOriginal FlowNew FlowRTLRTLFinalGateDC ScriptDC + MDPScriptIntermediateGate L ECL E CQoR ImpactRC Netlist Verification Flow• RC verification flow– Only one intermediate netlist between RTL code and the final netlist – Two LEC comparisons: RTL-to-Intermediate & Intermediate-toFinal – Better support of advanced (datapath) optimizations – LEC-friendly netlist by 'write_hdl –lec’• additional datapath info (as comments) about architecture changes31August 6, 2009Cadence ConfidentialRC Netlist Verification Flow•Synthesize with no ungrouping •Output Intermediate & Final Netlist •Perform RTL2Gate •Perform Gate2GateNew Flowwrite_hdl -lecRTLFinal GateEC LIntermediate GateEC LIntermediate netlist to Ensure Verification Success32August 6, 2009Cadence ConfidentialRC Netlist Verification Flow for Datapathread_hdl elaborate read_sdcFirst netlist generated with “-lec” optionsynthesize -to_mapped write_hdl -lec > intermediate.v write_do_lec -revised intermediate.v > rtl2map.do [ungroup in any way] <no more datapath architecture change> Do not ungroup before first netlistsynthesize -incr as many times as wished without “-lec” option; write_hdl > final.v write_do_lec -golden intermediate.v -revised final.v > map2final.do exit Every “write_hdl” followed by “write_do_lec”33August 6, 2009Cadence ConfidentialRC Netlist Verification Flow for Datapath• First LEC run (RTL-gate):read design <RTL_code> -golden read design intermediate.v -revised compare – write_do_lec generates a hierarchical dofile script (rtl2map.do) – Conformal dofile script will contain the following commands: analyze datapath –module –verbose analyze datapath -verbose• Second LEC run (gate-gate):read design intermediate.v -golden read design final.v -revised compare – write_do_lec generates a flat dofile script (map2final.do)34August 6, 2009Cadence ConfidentialSummary• When a design is complex and contains many datapath operators, with today’s advance synthesis optimizations, the datapath become structurally different between RTL and netlist, creating challenge to all verification tools • To effectively help Conformal datapath analysis quality and improve verification result, an integrated synthesis & verification flow is needed • DC MDP Analysis and the recommended synthesis script will help close the gap between datapath synthesis and verification • RC Netlist Verification flow reduces the chance of aborts for a more complete verification35August 6, 2009Cadence ConfidentialI N VE N TI V ECONFIDENTIALAbort ResolutionResolving Aborts• Abort is reported when formal (exhaustive) analysis cannot provide a complete proof of equivalence within a resource limit– The design has been partially verified since no input vector resulting in non-equivalence has been found either• Resource limit is adjusted by compare effort– SET COMPARE EFFORT <LOW|MED|HIGH|COMPLETE>• This section describes– Techniques to resolve aborts – Methods to isolate abort to better understand the aborted region and options for further verifications37August 6, 2009Cadence ConfidentialResolving AbortsReview Synthesis Flow• Abort can be avoided by following the guidelines given earlier • For datapath intensive design– Check that MDP level 4 has been used for DC synthesis – Use Netlist Verification Flow for RC synthesis• RTL design for ease of verification– Check for excessive don’t care conditions with LEC’s rule checker and design report• Partition the design well and use LEC’s hierarchical comparison– Check that all complex modules can be hierarchically compared38August 6, 2009Cadence ConfidentialResolving AbortsReview LEC Dofiles• Hierarchical Comparison– Check that hierarchical comparison is used – For module containing abort, check that it has no submodules that can be further hierarchically compared• For datapath intensive design– Check that MDP has been used (Analyze datapath –module) – Check that datapath analysis are successful• Abort Analysis– Check that LEC’s abort analysis has been used (analyze abort)• Multithreading– Check that multithreading is used for abort analysis39August 6, 2009Cadence ConfidentialResolving AbortsAdvanced LEC Techniques• Several advanced techniques are available to resolve aborts • Advanced options for ‘analyze datapath’– – – – -wordlevel -share -effort high -addertree• Advanced commands and techniques– run partition_compare (help run partition_compare –verbose) – add partition points – read design –norangeconstraint –vhdl40August 6, 2009Cadence ConfidentialRe-synthesis and RTL Recoding•Re-synthesis of problem blocks–Adjust effort level–Disable range constraints–Preserve key signals and boundaries •Pros–Makes verification easy for all future runs •Cons–Requires additional efforts, may impact qualityAbort Isolation•When aborts cannot be completely resolved, it is useful to identify the region where aborts occurred–Allow for a more targeted re-synthesis–Allow for a better understanding on the netlist that leads to abort –Allow for additional verification to these smaller regions •Techniques to isolate abort–Ensure that the modules are hierarchically compared•Easier if RTL is partitioned well–In MDP analysis flow, abstracted datapath cluster can be automatically isolatedAbort Isolation for Datapath Module •When using MDP analysis, LEC can isolate the datapathmodule that causes the abort so that the remaining non-aborting netlist can be verified–That is, if the remaining netlist is equivalent and the datapath module is also equivalent, then the entire netlist is equivalent •Provides more visibility into the region of abort –Instead of reporting all fanout keypoints from the datapath module as abort, only the datapath module is reported as abort(See next slide)•The is invoked as–ANALYZE DATAPATH –isolate_abort_module…Abort Isolation for Datapath Module •Results with abort:==============================================================Compared points PO Total--------------------------------------------------------------Abort 67 67==============================================================•Results with abort isolation:==============================================================Compared points PO Total--------------------------------------------------------------Equivalent 67 67==============================================================Compared results of isolated instances in Revised design (top)==============================================================Status Instance (Module)--------------------------------------------------------------Abort i5/add_123_S1_DP_OP_123_456(NV_GR_PE_STRI_core_add_123_S1_DP_OP_123_456) ==============================================================Multi-Threading•For machines with multi-core CPUs–No need to set up the parallel processing environment–Takes advantage of multi-core, multi-CPU machines •Parallel ComparisonLEC> compare –threads #•Best for large gate-to-gate comparisons, where the comparison canbe distributed to multiple comparison threadsLEC> analyze abort –compare –threads #•Best for RTL-to-gate comparison aborts, where a few keypoints canconsume a large portion of the runtime*Obsoletes the previous method of parallel comparisons using the command Run Parallel Compare•Support two new multiplier architectures •Improve divider architecture analysis•Support higher effort analysis for better datapath learning quality.Results from sample testcasesRadix-8Unsigned DividerHigh Effort AnalysisDatapath AnalysisI NVENTIVE CONFIDENTIAL ECO AutomationPrototype | Implement | VerifyECO ChallengesNomenclature•Engineering Change Order (ECO) is the process of making local changes to the design netlist without re-running the entire synthesis and P&R flow•ECO Types–Functional ECO•Changes the functionality of the design–Non-functional ECO•Fix timing, cross talk, DRV, routing violations with minimal effort•ECO Stages–Pre-Mask ( Pre tape-out) ECO•Uses normal logic gates to implement change–Post-Mask (Metal-only ECO)•Uses spare gates only to implement changeECO ChallengesManual Task•Current ECO flows are manual–Process is very time and resource consuming–Error Prone–Limited by ECO size•Very difficult to identify location of needed fix–Easy to modify RTL, yet difficult to transfer fix to gate netlist•Manual ECO changes do not easily incorporate use of –Spare gates, location, timing, routing access–Freed cells (used originally but not used in ECO patch)•Hard to manually optimize the eco patchECO ChallengesManual Flow Targeting Post Mask ECOSynthesisNew RTL (R2)Old RTL (R1)Old Netlist (G1)Final Netlist (New DEF)ECO Route/DRV/SIOld DEFP&RManual EditingTest InsertionNew Netlist(G2)ECECDelete/add connections Map to spare gatesDifficult to identify where to fix!Which logic cones are affected?P&RWhat type/many spare cells are available and how can I optimally map new gates to them?Use limited Metal Layers!How can I get the smallest possible change?Create ECO CmdWill this ECO meet timing, is it DRC clean?ORB a c k -e n d EC Or o n t -e n d E C ORepeat process for each ECO。

Formality使用指南【精选】

5.Verify

点击OK键,完成。现在你已经准备好 ,可以进行 fifo.v和fifo.vg功能是否一致。

选择Verify按钮,点击Verify All,进行形式验证。

验 证 结 束 , 结 果 出 现 “ Verify”fail 的 对话 框 , 提示 两种功能不一致。

6. Debug

2.设置Implementation Design

点击Implement按钮,在Read Design Files 中点击 Verilog,出现Add verilog files对话框,

选择gate目录下的verlog网表文件fifo.vg, 点击Load Files加载网表文件fifo.vg,

由于fifo.v 是源代码,fifo.vg只是综合的源代 码,没有添加SCAN和JTAG链。故可以省略 这一步

检查reference design4和.MImatpclehmention design的比较

点是否匹配 点击Match按钮,选择Run Matching按钮,进行匹

配检查。 出现下图结果:没有不匹配的比较点,可以进入下

2.1加载Technology library

选择Read DB Libraries按钮,点击DB…按钮,出现 Add DB Files对话框

选择lib目录下的lsi_10k.db库文件,(确保Read as share library被选中)点击LOAD Files,加载库文件。

选 择 Set Top Design, 在 Choose a library 中 选 择 WORK (Design Library),

1.1读取源文件

在对话框中选择:Rtl目录下的fifo.v文件, 点击Open按钮,打开fifo.v源代码。如图:

STM32固件库使用手册的中文翻译版

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优 的。对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应 用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

1.3.1 变量 ................................................................................................................................................ 28 1.3.2 布尔型 ............................................................................................................................................ 28 1.3.3 标志位状态类型 ........................................................................................................................... 29 1.3.4 功能状态类型 .............................................................................................................

synopsys_formality指导手册_概述说明

synopsys formality指导手册概述说明1. 引言1.1 概述在硬件设计领域,验证是一个非常重要的环节。

在设计过程中,我们需要确保设计的正确性和可靠性。

为了实现这个目标,Formality工具被广泛应用于电子设计自动化(EDA)过程中的形式验证。

Synopsys Formality是一款强大的形式验证工具,它可以帮助我们验证两个不同层次或版本的设计之间的等效性。

通过使用Formality,我们可以有效地检查逻辑门级网表和原始RTL之间是否存在功能差异或者错误。

本指导手册将介绍Formality工具的基本概念、应用场景以及使用步骤。

你将了解到如何利用Formality进行验证,并掌握其使用方法和技巧。

1.2 文章结构本文将分为以下几个部分:- 引言:对Formality进行概述并介绍文章结构。

- 正文:详细介绍Formality工具及其相关内容。

- Formality基本概念:解释Formality中涉及到的关键概念和术语。

- Formality的应用场景:探讨使用Formality解决哪些问题以及在哪些情况下选择使用该工具。

- 使用Formality进行验证的步骤:分步骤介绍如何使用Formality进行验证。

- 结论:总结本文的主要内容,并指出Formality在硬件验证中的重要性和前景。

1.3 目的本指导手册的目的是为读者提供对于Formality工具的全面理解。

通过阅读本文,读者将能够了解Formality在形式验证中的基本概念、功能和应用场景,从而能够更好地应用该工具来提高硬件设计的准确性和可靠性。

2. 正文Formality是Synopsys公司开发的一款形式验证工具,它旨在为硬件设计工程师提供一种高效且可靠的形式验证解决方案。

Formality通过比较两个逻辑设计的等效性来进行验证,确保电路实现与规范之间不存在功能差异或逻辑错误。

Formality作为一种形式验证工具,在电路设计领域中有着广泛的应用。

第6章 ic design

基于事件的仿真

基于事件的仿真 Event-Based Simulation, EBS Any change in input stimulus is identified as an event. 捕获每个事件,并将该事件传播到整个设计, 捕获每个事件,并将该事件传播到整个设计,直 至达到稳态为止 输入激励的每个变化都视为一个事件 EBS的特点 的特点 高仿真精度 仿真速度依赖于设计的规模 大型设计仿真速度较慢

Verifies the system memory map and the internal interconnect of the design. Verifies design at the system level.

软件学院

SoC

Slide 10/76

基于平台的验证

The verification for such a design involves the interconnect verification between the basic platform and the additional IP blocks.

软件学院 SoC Slide 19/76

基于事务的验证

基于事务的验证 Transaction-Based Verification, TBV Transaction based verification does not require detailed test benches with large vectors. TBV的要素 的要素 被测设计(Design Under Test, DUT) 被测设计 事务(Transaction): 设计与事务处理器 设计与事务处理器(Transactor) 事务 之间通过接口进行的一次数据或控制传输 事务验证模块(Transaction Verification Module, 事务验证模块 TVM): 执行一类特定事务的任务集合 测试(Test): 为系统中每个事务处理器产生任务序 测试 列的程序

verification

VerificationIntroductionVerification is the process of confirming the accuracy and validity of a system or component. It involves checking if a system or component meets the specified requirements and performs as intended. In software development, verification aims to ensure that the software meets the desired quality standards and satisfies the functionality specified in the requirements.The Importance of VerificationVerification is a critical step in the software development life cycle (SDLC). It helps to identify bugs, errors, and inconsistencies early in the development process. By verifying the software, developers can catch and fix issues before they become major problems. This saves time, effort, and resources that would otherwise be wasted on detecting and fixing errors later in the development cycle or during actual usage.Types of VerificationThere are several types of verification methods used in software development. These methods include:1. Code ReviewsCode reviews involve having other developers examine the source code to identify potential issues, bugs, or vulnerabilities. This helps to ensure that the code is of high quality, follows best practices, and is maintainable.2. Unit TestingUnit testing involves writing and executing tests on individual units of code, such as functions or methods. It verifies if the units meet the specified requirements and behave as expected. Unit testing can be automated, making it easier to run tests repeatedly during development.3. Integration TestingIntegration testing ensures that individual units of code work together correctly when combined. It verifies if the interactions between different code modules are functioning as intended. Integration testing identifies interface issues and helps to ensure the correct integration of components.4. System TestingSystem testing involves testing the entire system as a whole. It verifies if the system meets the requirements and behaves as expected in different scenarios. System testing is typically performed in an environment that closely resembles the production environment.5. User Acceptance Testing (UAT)User acceptance testing involves testing the software from the end-user’s perspective. It verifies if the software meets the user’s needs and expectatio ns. UAT is usually conducted by actual end-users or representatives who simulate real-life scenarios to validate the software’s usability.Verification ProcessThe verification process typically follows these steps:1.Planning: Define the verification objectives, including the specificverification methods to be used, and create a verification plan.2.Preparation: Identify the necessary resources, such as testenvironments, test data, and testing tools. Prepare the test cases, test scripts, or test scenarios to be used during the verification process.3.Execution: Execute the verification activities according to theverification plan. This may involve conducting code reviews, running unit tests, performing integration tests, system testing, and user acceptance testing.4.Analysis: Analyze the results obtained from the verification activities.Identify and document any deviations, defects, or discrepancies.5.Resolution: Address and resolve the identified issues. This mayinvolve fixing bugs, modifying code, or enhancing the software to meet thedesired quality standards.6.Reporting: Document the verification process, including the results,findings, and any actions taken. This helps in maintaining a record for future reference.Challenges in VerificationAlthough verification is essential, it can present some challenges:1. Time and Resource ConstraintsVerification requires time and resources. It can be challenging to allocate sufficient time and resources for the different verification activities, especially when facing tight deadlines or limited budgets.2. Requirement ChangesRequirements can change during the development process. These changes can impact the verification process, making it necessary to reassess and update the verification plan and test cases.3. ComplexitySome systems or components may be complex, making verification a challenging task. It requires a deep understanding of the system architecture, dependencies, and interactions to design effective verification strategies.4. Lack of Proper Tools and InfrastructureThe availability of suitable tools and infrastructure is essential for efficient verification. Lack of proper tools and infrastructure can hinder the verification process and make it more time-consuming.ConclusionVerification is a crucial step in software development to ensure that the software meets the desired quality standards and performs as expected. It involves various methods, such as code reviews, unit testing, integration testing, system testing, and user acceptance testing. By following a systematic verification process, developers can identify and resolve issues early, saving time and resources. Despite the challenges involved, proper planning, preparation, and execution of verification activities can greatly enhance the quality and reliability of software products.。

Formality使用指南

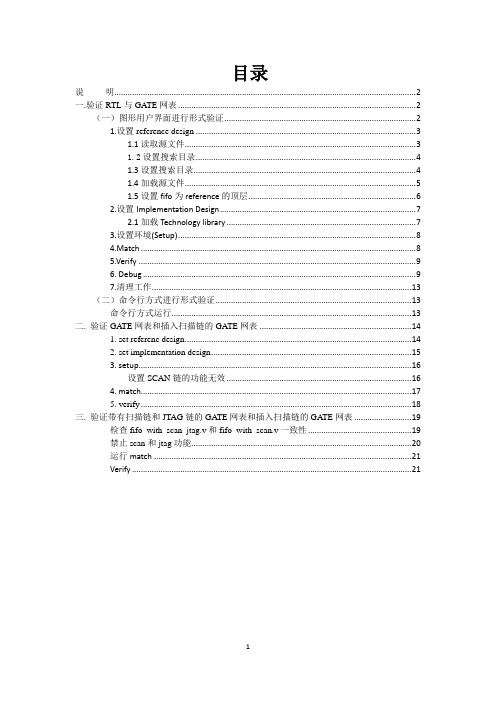

目录说明 (2)一.验证RTL与GATE网表 (2)(一)图形用户界面进行形式验证 (2)1.设置reference design (3)1.1读取源文件 (3)1.2设置搜索目录 (4)1.3设置搜索目录 (4)1.4加载源文件 (5)1.5设置fifo为reference的顶层 (6)2.设置Implementation Design (7)2.1加载Technology library (7)3.设置环境(Setup) (8)4.Match (8)5.Verify (9)6. Debug (9)7.清理工作 (13)(二)命令行方式进行形式验证 (13)命令行方式运行 (13)二. 验证GATE网表和插入扫描链的GATE网表 (14)1. set referenc design (14)2. set implementation design (15)3. setup (16)设置SCAN链的功能无效 (16)4. match (17)5. verify (18)三. 验证带有扫描链和JTAG链的GA TE网表和插入扫描链的GATE网表 (19)检查fifo_with_scan_jtag.v和fifo_with_scan.v一致性 (19)禁止scan和jtag功能 (20)运行match (21)Verify (21)说明FiFo的Tutorial目录下包含以下几个子目录:Rtl:fifo的RTL源代码;包含fifo.v, gray_counter.v, push_ctrl.v, gray2bin.v, pop_ctrl.v, rs_flop.v。

Lib:门级网表需要的技术库;包含lsi_10k.db。

Gate:综合的门级网表;包含fifo.vg 和fifo_mod.vg。

Gate_with_scan:插入扫描链的门级网表;包含fifo_with_scan.v。

Gate_with_scan_jtag:带有扫描链和JTAG链的门级网表;包含fifo_with_scan_jtag.v。

IC验证基础

验证的途径

模拟(simulation) 仿真(emulation) 形式验证(formal verification)

功能验证的方法

白盒法 黑盒法 灰盒法

白盒法

验证人员对内部结构和实现有充分了解的情 况下进行的验证 优点:

快速得到感兴趣的状态和输入,隔离某一特定的

ASIC Verification Introduction

刘蕊

验证的重要性

验证工作量占整个芯片开发周期的50%到 70% 验证工程师的数量超过了设计工程师

验证的概念

验证(verification)就是对设计(design)的进行检 查的过程,它的是目的是保证设计的功能和时序 正确,确保设计符合设计规范(specification)的 要求 只有穷举式的验证才是充分的,我们只能执行有 限的验证,验证是一个证伪的过程,而不是证明 的过程。

验证与测试

验证一般发生在流片(tape-out)前,主要检查设 计的逻辑正确性 测试发生在芯片制造后,主要检查生产出来的芯片 能否达到产品要求

验证的顺序

验证的层次

模块级验证(block level) 子系统级验证(subsystem level) 系统级验证(system level)

asicverificationintroduction验证工作量占整个芯片开发周期的50到70验证工程师的数量超过了设计工程师验证的概念验证verification就是对设计design的进行检查的过程它的是目的是保证设计的功能和时序正确确保设计符合设计规范specification的要求只有穷举式的验证才是充分的我们只能执行有限的验证验证是一个证伪的过程而不是证明的过程

FM_8

Apply the recommended debugging procedure to a failing verification

List the failing points Run Error Diagnosis to isolate setup errors or errors in implementation

2. 3.

4.

Use Pattern Window and Logic Cone Display to investigate failures that are not isolated by Error Diagnosis.

8- 2

Formality 2005.09

Formality Flow Overview (review)

Formality 2005.09

8- 6

Unmatched Points – Clues to Identify Causes

Symptom

Possible Cause

Action

More unmatched points in ref than in imp

FM is ignoring full case DC removed constant registers

Black box in ref Re-encoded FSM More unmatched points in imp than in ref Design transformation created extra logic Black box in ref Re-encoded FSM Insertion of test Same number of unmatched points in ref and imp Names have undergone a transformation

formal验证原理

formal验证原理Formal verification is a process of verifying a system or hardware by using mathematical proof to confirm that the system meets its specifications. It is an enormously powerful tool for verifying the correctness of hardware and software designs, but also very expensive.Formal verification is based on certain premises of mathematical logic, namely that a system contains a set of predefined assumptions and logical statements. Using these assumptions and logical statements, we can then use certain mathematical techniques and tools to prove that the system meets its requirements. Moreover, it is possible to assess the correctness of the results and the results of the proof can be used to understand why a system behaves in a particular manner.In order to form a proof, we need to identify a set of assumptions and logical statements about the system. This is often done by creating a formal specification document that defines the requirements of the system. Once these assumptions and statements are made, we can then use tools like theorem provers, model checkers, and symbolic executors to prove the correctness of the system.Once the proof has been made, we can use verification tools such as testbenches and assertions to test whether the assumptions and statements made in the proof hold true for thesystem. The testbenches are used to simulate the execution of the system and the assertions are used to verify whether the system meets its requirements or not. The results of the testbench and assertion checks are then used to gain confidence in the correctness of the system and to assess any potential problems that may arise.In conclusion, formal verification is a powerful tool that can be used to prove the correctness of hardware and software designs. It is based on certain premises of mathematical logic and uses theorem provers, model checkers, and symbolic executors to prove the correctness of the system. Once the proof has been made, verification tools such as testbenches and assertions can be used to test the system and to assess any potential problems that arise. Thus, formal verification is an effective way to ensure the correctness of a system design.。

IC验证工程师招聘笔试题与参考答案(某大型集团公司)2024年

2024年招聘IC验证工程师笔试题与参考答案(某大型集团公司)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在集成电路(IC)验证过程中,以下哪个阶段通常不会直接涉及硬件描述语言(HDL)的编写?A、功能验证B、时序验证C、代码覆盖率分析D、功耗验证2、在Verilog HDL中,以下哪个关键字用于定义一个无符号整数类型?A、integerB、unsignedC、realD、bit3、以下关于IC(集成电路)验证的描述,正确的是:A. IC验证主要是通过仿真来验证设计的功能正确性。

B. IC验证过程不需要考虑时序问题。

C. IC验证只需要关注设计的顶层模块。

D. IC验证的结果完全取决于验证环境的设置。

4、在IC验证中,以下哪种验证方法主要用于检查设计中的时序问题?A. 动态仿真验证B. 状态机验证C. 功能仿真验证D. 代码覆盖率分析5、在集成电路(IC)验证过程中,以下哪种技术主要用于验证芯片的行为是否与设计规格相符?A. DFT(Design For Test)B. ATPG(Automatic Test Pattern Generation)C. Formal VerificationD. FPGA Prototyping6、以下哪种验证方法可以检测到设计中的时序错误?A. 动态仿真B. 功能仿真C. 硬件加速仿真D. 性能仿真7、在数字电路中,以下哪种触发器是同步时序逻辑电路中最常用的基本触发器?A、D触发器B、JK触发器C、RS触发器D、T触发器8、以下关于Verilog硬件描述语言中模块定义的说法,正确的是?A、模块名称必须以字母开头B、模块名称可以包含下划线、数字等特殊字符C、模块名称可以与标准库中的模块名称相同D、模块名称在定义时可以不指定返回值类型9、以下哪个不是IC验证常用的验证方法?()A. 仿真验证B. 模拟验证C. 代码覆盖率分析D. 逻辑仿真 10、在UVM(Universal Verification Methodology)中,以下哪个组件不是用于创建测试序列的?()A. sequenceB. driverC. monitorD. scoreboard二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是IC(集成电路)验证中常用的验证方法?A. 功能仿真B. 逻辑综合C. 信号完整性分析D. 动态功耗分析2、在IC验证流程中,以下哪些步骤属于验证环境的搭建?A. 设计测试用例B. 创建测试平台C. 编写验证脚本D. 实施验证计划3、以下哪些技术是IC验证工程师在芯片设计过程中常用的验证方法?()A. 仿真验证B. 硬件加速验证C. 现场可编程逻辑阵列(FPGA)验证D. 模拟验证E. 系统级验证4、在IC验证过程中,以下哪些工具是常用的?()A. Verilog/VHDLB. SystemVerilogC. UVM(Universal Verification Methodology)D. ModelSimE. VCS5、以下哪些技术是IC(集成电路)验证工程师在设计中常用的验证方法?()A. 仿真验证B. 仿真加速C. 硬件加速D. 实物测试E. 模拟验证6、在IC验证过程中,以下哪些工具是常用的验证语言和描述工具?()A. VerilogB. VHDLC. SystemVerilogD. C/C++E. Python7、关于集成电路(IC)验证,以下哪些是验证工程师常用的验证方法?()A. 仿真验证B. 代码覆盖率分析C. 动态功耗分析D. 硬件在环(HIL)测试8、以下关于Verilog和SystemVerilog的区别,哪些描述是正确的?()A. Verilog是SystemVerilog的超集B. SystemVerilog增加了对系统级设计的支持C. Verilog不支持面向对象编程,而SystemVerilog支持D. Verilog主要用于数字电路设计,而SystemVerilog适用于系统级和硬件描述9、以下哪些是IC验证工程师在验证过程中常用的验证方法?A. 仿真验证B. 系统测试C. 代码覆盖率分析D. 动态功耗分析E. 断言检查 10、以下关于Verilog HDL的描述,正确的是?A. Verilog HDL支持行为建模和结构建模B. Verilog HDL不支持模拟仿真C. Verilog HDL主要用于硬件描述和仿真D. Verilog HDL不支持时序约束三、判断题(本大题有10小题,每小题2分,共20分)1、在数字电路设计中,同步复位比异步复位更易于时序分析和综合,因此在所有情况下都应当使用同步复位而不是异步复位。

ic开发验证方式

ic开发验证方式IC(集成电路)开发的验证方式可以分为以下几种:1. 仿真验证:通过使用电子设计自动化(EDA)工具进行电路级或系统级仿真,验证电路的功能和性能。

仿真可以帮助检测潜在的设计错误、验证电路的工作状态以及评估性能参数。

常见的仿真工具包括SPICE(模拟电路仿真程序)、Verilog和VHDL(硬件描述语言)等。

2. 逻辑验证:逻辑验证主要用于验证数字电路的功能和正确性。

通过使用逻辑设计自动化工具(如逻辑综合和逻辑仿真工具)来验证电路设计是否满足预期的布尔逻辑行为。

常见的逻辑验证工具包括模型仿真器(如ModelSim、VCS等)和形式验证工具(如FormalProver)等。

3. 物理验证:物理验证主要针对集成电路的版图、布局和物理约束进行验证,以确保电路在物理层面上满足要求。

物理验证包括布局布线验证、时序收敛验证、功耗分析等。

常见的物理验证工具包括Calibre、IC Validator、PrimeTime 等。

4. FPGA/ASIC验证:对于FPGA(现场可编程门阵列)或ASIC(专用集成电路)的开发,通常需要进行硬件验证。

这种验证方式涉及将设计编译到FPGA或ASIC芯片上,然后进行测试和调试以确认其功能和性能。

常见的硬件验证工具包括ModelSim、Xilinx ISE、Cadence Incisive等。

5. 实际验证:在所有虚拟验证完成后,需要将设计制造成实际的芯片,并使用实际的测试设备进行验证。

这包括芯片生产、封装、测试和验证等步骤。

实际验证通常需要借助自动测试设备(ATE)来进行测试和验证。

以上是一些常见的IC开发验证方式,实际使用的验证方法可能会因设计需求和开发流程而有所不同。

验证过程中的重要原则是确保设计在各个层面上都符合预期要求,并最大程度地减少设计错误和风险。

Formality_Basic_Lab_Instruction

Overview of Formality Basic LabsPurpose: These labs are designed for you to become familiar with using Formality.Content: There are four labs using Synopsys training and public-domain RTL source. The netlists were generated using DesignCompiler 2006.06-SP5 software. Be aware that there are additional SVF enhancements created by later versions of DC. (Using newer SVF files with the Auto Setup Mode in Formality will reduce or eliminate the issues in these labs.)Procedure:∙Follow the instructions for each lab.∙There is a “.solution” sub-directory with the correct result.Please compare your result with the correct result as you finish each lab.Invoke Formality in this manner to bring up the GUI:"fm_shell -gui -f runme.fms |tee runme.log" or"formality -f runme.fms |tee runme.log"FM Lab1: Basic Formality FlowObjective: This lab will introduce you to the Formality GUI bymanually reading-in two designs for verification. Then, you will create a Tcl script to perform the same verification.Lab flow:All of the necessary reference and implemention files, and librariesare included in sub-directories.Use the Formality GUI to verify the golden Verilog RTL against thegate-level Verilog netlist produced by DC. Be sure to include the SVF file. Aft erward, modify the resulting “fm_shell_command.log” fileto become a Formality TCL script.a.)Bring up the Formality GUI by us ing the command “formality” or“fm_shell –gui”. Follow the flow buttons on the GUI to read-inSVF, reference designs, implementation design with library, andthen verify.b.)The DC produced SVF file "default.svf" is located under the sub-directory "netlist_w_svf". This file is necessary for correctsetup.c.)The Verilog RTL files are located under the directory "rtl". Thetop-level design name is "mR4000".d.)The Verilog gate-level netlist "mR4000.gates.v" is located underthe directory "netlist_w_svf". The top-level design name is"mR4000".e.)The library file "tc6a_cbacore.db" is located under "lib". Thisis needed for the netlist. There are no Verilog simulationlibraries, just the .db file for this lab.f.)Use the GUI flow buttons: Guidance, Reference, Implementation,Setup (not needed), Match, Verify, Debug (not needed).g.)After completing a successful verification using the GUI, editand transform the "fm_shell_command.log" file into a Formality"runme.fms" Tcl script.h.)Use the script to run verification: "fm_shell -f runme.fms |teerunme.log".i.)Experiment with Formality commands and variables. Try some ofthe following commands:help report*report_passing_pointsman set_topman verifyreport_statusj.)Exit Formality.FM Lab2: Recognizing Simulation/SynthesisMismatch ErrorsObjective: This lab will give you practice in writing a Formality Tcl script. This design is VHDL and contains several potential differences between simulation and synthesis in their code interpretation which Formality will flag. You will need to direct Formality to ignore the differences and continue verification.By default, Formality is conservative in its interpretation of RTL. It will stop processing if it finds a difference between simulation and synthesis. You can direct it to continue by turning these error messages into warning messages. Use the following variable toaccomplish this:set hdlin_warn_on_mismatch_message “FMR_VHDL-1002 …”Use this variable before reading in the RTL into a container.(Note: If you have these types of mismatch issues using your designat work, you need to make sure that these conditions are investigated before taping-out your design.)This lab requires the use of “hdlin_dwroot”. Please edit the runme.fms u nder the …fm_basic/labs/lab2/scripts directory to correctly set the variable “hdlin_dwroot” to the top-level location of the DC software.Lab flow:1.)Use the script ./scripts/runme.fms as a starting point to createyour Formality Tcl script. Copy it to the lab2 workingdirectory.2.)You will need to complete the following:a.Read and link the reference VHDL files from the directorysrc.b.Read and link the Verilog gate-netlist.3.)Run an initial verification. Look at the error message ID.4.)Include the error message ID in the Formality script using thevariable hdlin_warn_on_mismatch_message to turn it into a warning message instead.5.)Continue this until you get a successful verification.6.)There are two other ways to accomplish this conversion ofsim/synth messages to warnings. See the ./.solution/runme.fmsscript.FM Lab3: Missing Part of the Design Objective: This lab shows an example of what happens in verificationif a piece of the reference design is missing while the implementation design remains complete. The point to this lab is to review transcript messages. These messages can provide hints to correct problems. You must change the "runme.fms" FM TCL script to get a successful verification.Lab flow:1.) Run the verification using the existing "runme.fms" script.2.)Find clues to indicate the potential problem.2a) Transcript messages:Formality debugging involves collecting information that may point to the reason why the design fails verification. Always look at the transcript messages first.Note the following warning message in the transcript:Warning: Cannot link cell '/WORK/fifo/memory' to its reference design'DW_ram_r_w_s_lat'. (FE-LINK-2)Status: Implementing inferred operators...Status: Creating black-box designs...Created technology library 'FM_BBOX' in container 'r' for black-box designsCreated black-box design 'DW_ram_r_w_s_lat' in library 'FM_BBOX'Warning: 1 blackbox designs were created for missing references. (FM-064) Formality is creating a black-box to represent a missing piece of the design. The missing piece is the DW part "DW_ram_r_w_s_lat".This is only a warning instead of an error because the customerincluded this variable setting in the FM TCL script:set hdlin_unresolved_modules black_boxOtherwise, Formality would have stopped processing the design.The problem is resolved by setting a variable to point to the top-level of the DesignCompiler tree. Formality can then find the correct DW information to generate the missing part.The Formality variable is hdlin_____________________.The DC location (for Synopsys internal training) is/global/apps/syn_2007.12-SP2.*** It is important to note that if you are paying attention to the transcript, you would stop here and correct the problem with themissing piece of the design. However, since the script continued tofinish the verification, there are some additional clues to see if you skipped the warning message.2b) Messages from matching:If you proceeded through matching, you will see several unmatched,black-box input pins. Since there are no unmatched implementationblack-boxes, this means that the reference design has a black-box that the implementation does not have.Additionally, the implementation seems to have latches that the reference design does not have. You can draw the conclusion that a big design piece is missing in the reference design.Here is a picture of the GUI unmatched points tab:2c) Graphical debugging:After running the verification and getting failing compare points, we normally would run "Diagnose". However, we already know that a large piece of the design is missing.It would be interesting to quickly view the pattern window to see how the missing design piece affected the logic cone of a failing compare point.Notice that several logic cone inputs seem to be missing in the pattern window:3.) Include the missing variable for specifying the DC tree in the FM TCL script and re-run verification. If you do not get a successfulverification, view the .solution directory.FM Lab4: Beginning DebugObjective: This lab will give you practice in using the Diagnose command and in viewing failing logic cones. This is a gate-netlist vs gate-netlist ECO verification. The ECO was done manually, and you are checking the resulting netlist against the original netlist.Lab flow:a.Run Formality script fm.tcl.formality –f fm.tcl |tee fm.logb.Start the GUI.c.Right mouse click on the first failing compare point and selectShow Patterns.d.This brings up the Pattern Viewer. The Pattern Viewer is verifyuseful in quickly identifying obvious differences in inputs to logic cones. We recommend using the Pattern Viewer first whendoing graphical debugging.e.In this case there is nothing obvious that is different betweenthe ref/impl logic cone inputs other than the same patternproduces different results at the compare point. Therefore, there is some difference in the combinational logic in the two cones.f.Close the Pattern Viewer.g.Click Diagnose button. This runs the diagnosis algorithm on allfailing compare points. You should get 1 error detected and 2 error candidates.h.The GUI automatically changes to Error Candidate window. Rightclick on failing cell U4072.i.Select Show Logic Cones.j.Select first failing compare point and click OK. The schematic will highlight the error candidate (implementation) and thematching region (reference).k.Notice that U4072 is a 3-input AND in the reference and a 3-input OR in the implementation. This is the ECO problem. Also noticehighlighted in orange.l.Click on the Error Candidate Pruning button (or F8). The implemenation will be pruned.m.Click on the reference window and click again on the Error Candidate Pruning button (or F8). Now the reference is pruned.The resultant logic cones are easier to deal with. (No action needed in this lab to correct the design.)n.Close the schematic window. Click on the failing points tab. o.Select the first two failing points (bd_au_count_reg_0_ and bd_au_count_reg_1_) and click Diagnose Selected Points button. p.Note that there is still 1 error detected but now there are 6 error candidates.q.Right click on failing cell U4072.r.Select Show Logic Cones. Note that the Select Failing Compare Point window shows the 7 failing points but only 2 have been diagnosed.s.Select first failing compare point and click OK.t.Prune (F8) the reference and implementation schematic windows.Note that there are more possible failures candidates. This is due to selecting a subset of the failing points.。

formality read_sverilog define

formality read_sverilog define在计算机科学和电子工程的领域中,有一种称为Verilog的硬件描述语言,它被广泛应用于设计和验证硬件电路。

在Verilog中,有一些关键字和指令是经常被使用的,包括formality、read_sverilog和define。

下面我们将一步步地讲解这些关键字和指令的含义和用法。

首先,formality是一种验证工具,可用于验证Verilog设计的功能正确性。

它是一种形式验证工具,可以比较两个硬件模块或设计的行为,以便查找问题或错误。

使用formality工具可以提高设计的可靠性和可维护性,同时减少测试和调试的工作量和时间。

其次,read_sverilog是Verilog中的一个重要指令,用于读取和解析Verilog代码。

使用read_sverilog指令可以将Verilog代码转换为内存中的一种内部表示形式,以便进行后续的分析和处理。

这个过程包括预处理、语法分析和建立内部数据结构等步骤,最终生成预期的数据结构和关系。

最后,define是一种预处理指令,用于定义常量、变量和宏指令等。

使用define指令可以简化代码的编写和理解,减少代码中的冗余和错误,提高代码可读性和可维护性。

在Verilog中,使用`define指令可以定义常量、宏、变量和函数等,以达到更高的代码重用和可扩展性。

总之,Verilog中的formality、read_sverilog和define等关键字和指令,是Verilog设计和验证中至关重要的工具和技术。

使用这些工具和技术可以提高设计和验证的效率和质量,减少出错的机会和成本,使Verilog设计和开发更加可靠和可维护。

希望这篇文章能够对想要了解和应用Verilog的读者有所帮助。

formality简介教学文案

Formality简介Formality,synopsis的工具,我们常说的形式验证、formal check 都是用它做的。

作用就是比较两者“r、i”在功能上是否一致,跟时序一点儿关系都没有!在数字ic的flow中,一般会做两次formal check:一.rtl对DC netlist做一次;二.DC netlist对PR后的netlist做一次。

先看个rtl对DC netlist的脚本:#-------------------------------------------------------------------------# Formal check for Capture.vhd ( rtl vs dc_nlist )#-------------------------------------------------------------------------set TOP_REF Captureset TOP_IMP Captureset REF_NAME Capture.vhdset IMP_NAME Capture.vset REF_PATH /home/project/9602-360-100/Dig/d1/work_jh/synop199/rtlset IMP_PATH /home/project/9602-360-100/Dig/d1/work_jh/synop199/dc1/nlist set RPT /home/project/9602-360-100/Dig/d1/work_jh/synop199/fm/rptset hdlin_dwroot /edatools/synopsys/syn_vX-2008.9-SP4set verification_failing_point_limit 2000set synopsys_auto_setup trueset_svf /home/project/9602-360-100/Dig/d1/work_jh/synop199/dc1/default.svf set search_path ". /home/project/9602-360-100/Dig/d1/synop199 //edatools/synopsys/syn_vX-2008.9-SP4/libraries/syn"read_db {chrt35_ss_75_1pt3_SYNOPSYS2_MMSIM.db dw_foundation.sldb}read_vhdl -r $REF_PATH/$REF_NAME -l work > $RPT/read_design.rptset_top $TOP_REF > $RPT/set_top.rptreport_hdlin_mismatch > $RPT/rpt_hdlin_mismatch.rptread_verilog -i $IMP_PATH/$IMP_NAME -l work >> $RPT/read_design.rpt set_top $TOP_IMP >> $RPT/set_top.rpt#set_constant -type port r:/.../ 0#set_constant -type port i:/.../ 0match > $RPT/match.rptreport_matched_points > $RPT/matched_point.rptreport_unmatched_points > $RPT/unmatched_point.rptreport_loops -limit 0 -unfold > $RPT/loops.rptverify#以上内容可以放在一个文件里作为脚本,调用方法就是在fm_work下$ fm_shell –f ../scripts/fm_rtl2dc.tcl如果成功要看详细信息或者失败要debug的话,再输入start_gui,进入-GUI模式。

assert 和verify命令的详细用法

assert,assert_valid,verify,trace用法(转载)2010-08-05 9:10对于开始学vc的人,对于assert,assert_valid,verify,trace的宏感到很奇怪,总是觉得很难掌握似的,其实这些主要是没有理清楚他们各自宏之间深层次的意义。

这些都是我平时的学习笔记,可能有些是网上的资源,如果有重复请大家不要见怪~ASSERT()ASSERT()被测试它的参数,若参数为0,则中断执行并打印一段说明消息。

在Release 版本的程序中它不起任何作用。

ASSERT()使用的时候必须保证参数表达式中不能有函数调用(译者注:ASSERT()宏在 Release 版本中不对表达式求值),因此对于任何有函数调用的参数表达式,应该使用宏 VERIFY(),以保证表达式中的函数调用在 Release 版本中会被正确求值。

断言(assertion)用带断言信息(程序, 模块, assertion行)的对话框执行. 对话框有3个按钮: "Break", "Repeat" ("Debug"), and "Continue" ("Ignore"). "Break" 结束程序, "Continue" 忽略断言, 最有用的是"Repeat"按钮. 按下它在断言的地方打开源代码编辑器. 在这里你可以测试所有的变量值并明白哪里出了问题。

例如:ASSERT(pPointer);ASSERT(n>0 && n<100);ASSERT(0);ASSERT在执行简单验证时很有用,但对于C++对象,特别是由CObject派生的对象,则有更好的方法ASSERT_VALID来实现类似操作。

作为一般规则,我们应在开始使用每一个对象之前检查数据讹误,ASSERT_VALID宏使得对CObject的派生类实现该操作非常简单。

RTL验证工具:VCS简介

案的基石。VCS 是业界领先的仿真器,支持本征断言(native assertion)描述、自动测试平台 生成技术(testbench)、以及代码和断言覆盖引擎,确保智能化验证的实现。VCS 中本征代码 支持 (Native)技术确保了设计验证的效率、性能和质量,并缩短了验证周期。VCS 中的本征 代码技术实现了在单一工具中,支持可验证性设计(DFV),及 覆盖率驱动和约束的随机激励 生成。其本征对断言的支持和所包含的丰富的断言检查工具库保证了设计人员能够方便地采用 DFV 技术来查找错误和提高验证质量。 此外,断言可以作为设计要求重复利用,在 Synopsys 的混合 RTL 规则验证产品 Magellan 中进行形式验证。 VCS 对专用集成电路(ASIC)生产商的建模和仿真签核(Sign-off)提供了支持。 VCS 对统一的设计和验证语言标准 SystemVerilog 提供支持。 SystemVerilog 增强了设计人员的 能力,加快了验证速度并提高了验证的质量。 对于要求在 RTL 环境中使用 SystemC 模型进行验证的设计团队,VCS 提供了支持 OSCI SystemC 的直接内核接口(DKI)和支持 System Studio 的直接内核接口(DKI)。 主要优点:

本征测试平台(testbench)、断言和完备的覆盖率测试技术,为 Verilog 和混合 HDL 验证带 来 2-5 倍的性能提升 为 SystemVerilog 设计和基于断言的验证提供支持,确保更高的设计和验证效率 提供最高的性能和容量,加快产品上市周期 通过集成 NanoSim 实现了具有最高处理能力的混合信号仿真环境 采用单个统一工具,实现 Verilog 和混合 HDL RTL 及 SystemC 的支持 支持所有主要的 UNIX 和 Linux 平台

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。