74HC595D(最新中文版)

移位寄存器74HC595中文资料

移位寄存器74HC595中文资料--------------------------------------------------------------------------------移位寄存器74HC595中文资料74HC595 是一款漏极开路输出的CMOS 移位寄存器,输出端口为可控的三态输出端,亦能串行输出控制下一级级联芯片。

74HC595特点:高速移位时钟频率Fmax>25MHz标准串行(SPI)接口CMOS 串行输出,可用于多个设备的级联低功耗:TA =25℃时,Icc=4μA(MAX)图1 74HC595引脚图74HC595引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH三态输出管脚8GND电源地9SQH串行数据输出管脚10SCLR移位寄存器清零端11SCK数据输入时钟线12RCK输出存储器锁存时钟线13OE输出使能14SI数据线15VCC电源端图2 74HC595逻辑图74HC595真值表:输入管脚输出管脚SISCKSCLRRCKOEXXXXHQA—QH 输出高阻XXXLQA—QH 输出有效值XXLXX移位寄存器清零L上沿HXX移位寄存器存储LH上沿HXX移位寄存器存储HX下沿HXX移位寄存器状态保持XXX上沿X输出存储器锁存移位寄存器中的状态值XXX下沿X输出存储器状态保持74HC595参数:Absolute Maximum Ratings绝对最大额定值参数数值Supply Voltage电源电压(VCC)−0.5 to +7.0VDC Input Voltage 直流输入电压(VIN)−1.5 to VCC +1.5VDC Output V oltage 直流输出电压(VOUT)−0.5 to VCC +0.5VClamp Diode Current 钳位二极管电流(IIK, IOK)±20mADC Output Current直流输出电流,每个引脚(输出)±35mADC VCC or GND Current,per pin (ICC)±70mAStorage Temperature Range 储存温度范围(TSTG)−65℃to +150℃Power Dissipation 功耗(PD)(Note 3)600mWS.O. Package only500mWLead Temperature (TL) (Soldering 10 seconds)260℃Recommended Operating Conditions建议操作条件参数最小最大单位Supply Voltage电源电压(VCC)26vDC Input or Output Voltage(VIN, VOUT)输入输出电压0VCCVOperating Temperature Range工作温度范围(TA)−40+85℃Input Rise or Fall Times 输入上升或下降时间(tr,tf) VCC = 2.0V-1000nsVCC = 4.5V-500nsVCC = 6.0V-400nsDC SPECIFICATIONS直流电气规格Symbol 符号Parameter 参数Conditions 条件VCCTA=25℃TA= −40to85℃TA= −55to125℃UNIT 单位典型Guaranteed Limits保证界限VIHMinimum High Level Input V oltage最大高电平输入电压-2.0V-1.51.51.5V4.5V-3.153.153.156.0V-4.24.24.2VILMaximum LOW Level Input V oltage最大低电平输入电压-2.0V-0.50.50.5V4.5V-1.351.351.356.0V-1.81.81.8VOHMinimum HIGH Level Output V oltage最大高电平输出电压VIN=VIH or VIL|IOUT|≤20μA2.0V2.01.91.91.9V4.5V4.54.44.44.46.0V6.05.95.95.9Q'HVIN = VIH or VILV|IOUT| ≤4.0mA4.5V4.23.983.843.7|IOUT| ≤5.2mA6.0V5.25.485.345.2QA thru QHVIN = VIH or VILV|IOUT| ≤6.0mA4.5V4.23.983.843.7IOUT| ≤7.8mA6.0V5.75.485.345.2VOLMaximum LOW Level Output V oltage最大低电平输出电压VIN=VIH or VIL|IOUT| ≤20μA2.0V0.10.10.1V4.5V0.10.10.16.0V0.10.1Q'HVIN = VIH or VILV|IOUT| ≤4mA4.5V0.20.260.330.4|IOUT| ≤5.2mA6.0V0.20.260.330.4QA thru QHVIN = VIH or VILV|IOUT| ≤6.0mA4.5V0.20.260.330.4|IOUT| ≤7.8mA6.0V0.20.260.330.4IINMaximum Input Current最大输入电流VIN=VCC or GND6.0V±0.1±1.0±1.0μAIOZMaximum 3-STATE Output Leakage最大3态输出泄漏电流VOUT = VCC or GND G = VIH6.0V-±0.5±5.0±10μAICCMaximum Quiescent Supply Current电源电流VIN=VCC or GND IOUT = 0μA6.0V-8.080160μA交流电气特性:Symbol 符号Parameter 参数Conditions 条件典型Guaranteed LimitUNIT 单位fMax最高工作频率-5030MHztPHL, tPLHMaximum Propagation Delay,最大传输延迟SCK to Q’HCL = 45 pF1220nstPHL, tPLHMaximum Propagation Delay, 最大传输延迟RCK to QA thru QHCL = 45 pF1830nstPZH, tPZLMaximum Output Enable Time from G to QA thru QH 最大输出启用时间G to QA thru QH RL=1kΩ CL=45pF1728nstPHZ, tPLZMaximum Output Disable Time from G to QA thru QH最大输出禁用时间G to QA thru QH RL=1kΩ CL=5pF1525nstSMinimum Setup Time from SER to SCK--20nstSMinimum Setup Time from SCLR to SCK--20nstSMinimum Setup Time from SCK to RCK--40nstHMinimum Hold Time from SER to SCK--nstWMinimum Pulse Width of SCK or RCK--16ns本文来自: 原文网址:/info/cmos/0083302.html。

74hc595中文资料

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存

储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C PD决定动态的能耗,

P D=C PD×V CC×f1+∑(C L×V CC2×f0)

F1=输入频率,C L=输出电容f0=输出频率(MHz)Vcc=电源电压

引脚说明

功能表

H=高电平状态L=低电平状态↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效

当MR为高电平,OE为低电平时,数据在SH CP上升沿进入移位寄存器,在ST CP上升沿输出到并行端口。

74HC595完整中文资料

74HC595完整中文资料74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持第二步:目的:将位数据逐位移入74HC595,即数据串入方法:P1.2产生一上升沿,将P1.0上的数据移入74HC595中.从低到高。

74HC595完整中文资料

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有 咼阻、关、断状态。

三态。特点8位串行输入8位串行或并行输出 存储状态寄存 器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能 力 并行输出,总线驱动 串行输出;

标准 中等规模集成电路应用 串行到并行的数据转换Remote c ontrol holding register.描述595是告诉的硅结构的CMO器件,

CPD决 定动态的能耗,PD=CPD< VCC< f1 +刀(CLXVCC2< f0) F 1=输入频率,。1=输出电容f0=输出频率(MHZ Vcc=电源电压 引脚说明符号引脚描述

内部结构

结合引脚说明就能很快理解595的工作情况

功能表:

管脚编号

管脚名

管脚定义功能

1、2、3、4、5、6、

7、15

QA—QH

2)74595的主要优点是具有数据存储寄存器,在移位的过程中,输出 端的数据可以保持不变。这在串行速度慢的场合很有用处,数码管没 有闪烁感。

与164只有数据清零端相比,595还多有输出端时能/禁止控制 端,可以使输出为高阻态。

3)595是串入并出带有锁存功能移位寄存器,它的使用方法很简单, 在正常使用时SCLR为高电平,G为低电平。从SER每输入一位数据, 串行输595是串入并出带有锁存功能移位寄存器,它的使用方法很简 单,如下面的真值表,在正常使用时SCLF为高电平,G为低电平。 从SER每输入一位数据,串行输入时钟SCK上升沿有效一次,直到八 位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被

送到了输出端。入时钟SCK上升沿有效一次,直到八位数据输入完毕, 输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。

74HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74HC595D中文资料_数据手册_参数

74HC595D中⽂资料_数据⼿册_参数74HC595; 74HCT5958-bit serial-in, serial or parallel-out shift register with outputlatches; 3-stateRev. 6 — 12 December 2011Product data sheet1. General descriptionThe 74HC595; 74HCT595 are high-speed Si-gate CMOS devices and are pin compatible with Low-power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard No.7A.The 74HC595; 74HCT595 are 8-stage serial shift registers with a storage register and3-state outputs. The registers have separate clocks.Data is shifted on the positive-going transitions of the shift register clock input (SHCP). The data in each register is transferred to the storage register on a positive-going transition of the storage register clock input (STCP). If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register.The shift register has a serial input (DS) and a serial standard output (Q7S) for cascading. It is also provided with asynchronous reset (active LOW) for all 8 shift register stages. The storage register has 8 parallel 3-state bus driver outputs. Data in the storage register appears at the output whenever the output enable input (OE) is LOW.2. Features and benefits8-bit serial input8-bit serial or parallel outputStorage register with 3-state outputsShift register with direct clear100MHz (typical) shift out frequencyESD protection:◆HBM JESD22-A114F exceeds2000V◆MM JESD22-A115-A exceeds200VMultiple package optionsSpecified from -40C to+85C and from -40C to+125C3. ApplicationsSerial-to-parallel data conversionRemote control holding register3-state4. Ordering information5. Functional diagramTable 1.Ordering informationType numberPackageTemperature rangeName DescriptionVersion 74HC595N -40?C to +125?CDIP16plastic dual in-line package; 16leads (300mil)SOT38-474HCT595N 74HC595D -40?C to +125?CSO16plastic small outline package; 16leads;body width 3.9mmSOT109-174HCT595D 74HC595DB -40?C to +125?CSSOP16plastic shrink small outline package; 16leads; body width 5.3mmSOT338-174HCT595DB 74HC595PW -40?C to +125?CTSSOP16plastic thin shrink small outline package; 16leads; body width 4.4mmSOT403-174HCT595PW 74HC595BQ -40?C to +125?CDHVQFN16plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads; 16terminals; body 2.5 ? 3.5 ? 0.85 mmSOT763-174HCT595BQ3-state3-state 6. Pinning information3-state6.2Pin descriptionTable 2.Pin description Symbol Pin DescriptionQ11parallel data output 1Q22parallel data output 2Q33parallel data output 3Q44parallel data output 4Q55parallel data output 5Q66parallel data output 6Q77parallel data output 7 GND8ground (0 V)Q7S9serial data outputMR10master reset (active LOW)OE13output enable input (active LOW)DS14serial data inputQ015parallel data output 0V CC16supply voltage7. Functional descriptionTable 3.Function table[1]Control Input Output FunctionSHCP STCP OE MR DS Q7S QnX X L L X L NC a LOW-level on MR only affects the shift registersX↑L L X L L empty shift register loaded into storage registerX X H L X L Z shift register clear; parallel outputs in high-impedance OFF-state↑X L H H Q6S NC logic HIGH-level shifted into shift register stage 0. Contents of all shift register stages shifted through, e.g. previous state of stage 6(internal Q6S) appears on the serial output (Q7S).X↑L H X NC QnS contents of shift register stages (internal QnS) are transferred to the storage register and parallel output stages↑↑L H X Q6S QnS contents of shift register shifted through; previous contents of the shift register is transferred to the storage register and the paralleloutput stages[1]H=HIGH voltage state;L=LOW voltage state;↑=LOW-to-HIGH transition;X=don’t care;NC=no change;Z=high-impedance OFF-state.3-state8. Limiting valuesTable 4.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V). Symbol Parameter Conditions Min Max UnitV CC supply voltage-0.5+7VI IK input clamping current V I < -0.5V or V I>V CC+0.5 V-±20mAI OK output clamping current V O<-0.5V or V O > V CC + 0.5 V-±20mAI O output current V O=-0.5V to (V CC+0.5V)pin Q7S-±25mApins Qn-±35mAI CC supply current-70mAI GND ground current-70-mAT stg storage temperature-65+150?CP tot total power dissipationDIP16 package[1]-750mWSO16 package[2]-500mWSSOP16 package[3]-500mWTSSOP16 package[3]-500mWDHVQFN16 package[4]-500mW[1]For DIP16 package: P tot derates linearly with 12mW/K above 70 ?C.[2]For SO16 package: P tot derates linearly with 8mW/K above 70 ?C.[3]For SSOP16 and TSSOP16 packages: P tot derates linearly with 5.5mW/K above 60 ?C.9. Recommended operating conditions10. Static characteristicsTable 5.Recommended operating conditionsSymbol ParameterConditions74HC59574HCT595UnitMinTyp Max Min Typ Max V CC supply voltage 2.0 5.0 6.0 4.5 5.0 5.5V V I input voltage 0-V CC 0-V CC V V O output voltage 0-V CC 0-V CC V ?t/?Vinput transition rise and fall rateV CC = 2.0 V --625---ns/V V CC = 4.5 V - 1.67139- 1.67139ns/V V CC = 6.0 V--83---ns/V T ambambient temperature-40+25+125-40+25+125C Table 6.Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground =0V).Symbol ParameterConditions-40?C to +85?C -40?C to +125?C UnitMinTypMaxMinMax74HC595V IHHIGH-level input voltageV CC =2.0V 1.5 1.2- 1.5-V V CC =4.5V 3.15 2.4- 3.15-V V CC =6.0VV CC =2.0V -0.80.5-0.5V V CC =4.5V - 2.1 1.35- 1.35V V CC =6.0V- 2.81.8- 1.8VV OHHIGH-level output voltageV I =V IH or V IL all outputsI O =-20µA; V CC =2.0V 1.9 2.0- 1.9-V I O =-20µA; V CC =4.5V 4.4 4.5- 4.4-V I O =-20µA; V CC =6.0V 5.96.0- 5.9-VQ7S outputI O =-4mA; V CC =4.5V 3.84 4.32- 3.7-V I O =-5.2mA; V CC =6.0V 5.345.81- 5.2-VQn bus driver outputs I O =-6mA; V CC =4.5V 3.84 4.32- 3.7-V I O =-7.8mA; V CC =6.0V5.345.81- 5.2-V3-stateV OL LOW-leveloutput voltage V I=V IH or V ILall outputsI O=20µA; V CC=2.0V-00.1-0.1V I O=20µA; V CC=4.5V-00.1-0.1V I O=20µA; V CC=6.0V-00.1-0.1V Q7S output I O=4mA;V CC=4.5V-0.150.33-0.4V I O=5.2mA;V CC=6.0V-0.160.33-0.4V Qn bus driver outputsI O=6mA;V CC=4.5V-0.150.33-0.4V I O=7.8mA;V CC=6.0V-0.160.33-0.4VI I input leakagecurrentV I=V CC or GND; V CC=6.0V--±1.0-±1.0µAI OZ OFF-state--80-160µAC I inputcapacitance- 3.5---pF 74HCT595V IH HIGH-levelinput voltageV CC=4.5V to 5.5V 2.0 1.6- 2.0-VV IL LOW-levelinput voltageV CC=4.5V to 5.5V- 1.20.8-0.8VV OH HIGH-leveloutput voltage V I=V IH or V IL; V CC=4.5Vall outputsI O=-20µA 4.4 4.5- 4.4-V Q7S outputI O=-4mA 3.84 4.32- 3.7-V Qn bus driver outputsI O=-6mA 3.7 4.32- 3.7-VV OL LOW-leveloutput voltage V I=V IH or V IL; V CC=4.5Vall outputsI O=20µA-00.1-0.1V Q7S outputI O=4.0mA-0.150.33-0.4V Qn bus driver outputsI O=6.0mA-0.160.33-0.4VI I input leakagecurrent V I=V CC or GND; V CC=5.5V--±1.0-±1.0µATable 6.Static characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground=0V). Symbol Parameter Conditions-40?C to +85?C-40?C to +125?C UnitMin Typ Max Min Max3-stateI OZ OFF-state--80-160µAI CC additionalsupply current per input pin; I O=0A; V I=V CC-2.1V; other inputs at V CC or GND;V CC=4.5V to5.5Vpins MR, SHCP, STCP, OE-150675-735µA pin DS-25113-123µAC I inputcapacitance - 3.5---pFTable 6.Static characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground=0V).Symbol Parameter Conditions-40?C to +85?C-40?C to +125?C UnitMin Typ Max Min Max3-state 11. Dynamic characteristicsTable 7.Dynamic characteristicsVoltages are referenced to GND (ground = 0 V); for test circuit see Figure14.Symbol Parameter Conditions25 ?C-40?C to+85 ?C-40?C to+125 ?C UnitMin Typ[1]Max Min Max Min Max74HC595t pd propagationdelay SHCP to Q7S; see Figure9[2]V CC = 2 V-52160-200-240ns V CC = 4.5 V-1932-40-48ns V CC = 6 V-1527-34-41ns STCP to Qn; see Figure10[2] V CC = 2 V-55175-220-265ns V CC = 4.5 V-2035-44-53ns V CC = 6 V-1630-37-45ns MR to Q7S; see Figure12[3] V CC = 2 V-47175-220-265ns V CC = 4.5 V-1735-44-53ns V CC = 6 V-1430-37-45nst en enable time OE to Qn; see Figure13[4]V CC = 2 V-47150-190-225nsV CC = 4.5 V-1730-38-45nsV CC = 6 V-1426-33-38ns t dis disable time OE to Qn; see Figure13[5]V CC = 2 V-41150-190-225nsV CC = 4.5 V-1530-38-45nsV CC = 6 V-1227-33-38ns t W pulse width SHCP HIGH or LOW;V CC = 4.5 V156-19-22-nsV CC = 6 V135-16-19-nsSTCP HIGH or LOW;see Figure10V CC = 2 V7511-95-110-nsV CC = 4.5 V154-19-22-nsV CC = 6 V133-16-19-nsMR LOW; see Figure12V CC = 2 V7517-95-110-nsV CC = 4.5 V156-19-22-nsV CC = 6 V135-16-19-ns3-statet suset-up timeDS to SHCP; see Figure 10V CC = 2 V 5011-65-75-ns V CC = 4.5 V 104-13-15-ns V CC = 6 V 9 3-11-13-nsSHCP to STCP; see Figure 11V CC = 2 V 7522-95-110-ns V CC = 4.5 V 158-19-22-ns V CC = 6 V 137-16-19-ns t hhold timeDS to SHCP; see Figure 11V CC = 2 V 3-6-3-3-ns V CC = 4.5 V 3-2-3-3-ns V CC = 6 V3-2-3-3-ns t recrecovery timeMR to SHCP; see Figure 12V CC = 2 V 50-19-65-75-ns V CC = 4.5 V 10-7-13-15-ns V CC = 6 V 9-6-11-13f maxmaximum frequencySHCP or STCP; see Figure 9 and 10V CC = 2 V 930- 4.8-4-MHz V CC = 4.5 V 3091-24-20-MHz V CC = 6 V35108-28-24-MHz C PDpower dissipation capacitancef i = 1 MHz; V I =GND to V CC [6][7]-115-----pF74HCT595; V CC = 4.5 V to 5.5 V t pdpropagation delay SHCP to Q7S; see Figure 9[2]-2542-53-63ns STCP to Qn; see Figure 10[2]-2440-50-60ns MR to Q7S; see Figure 12[3]-2340-50-60ns t en enable time OE to Qn; see Figure 13[4]-2135-44-53ns t dis disable time OE to Qn; see Figure 13[5] -1830-38-45ns t Wpulse widthSHCP HIGH or LOW;see Figure 9166-20-24-ns STCP HIGH or LOW; see Figure 10165-20-24-ns MR LOW; see Figure 12208-25-30-ns t suset-up timeDS to SHCP; see Figure 10165-20-24-ns SHCP to STCP; see Figure 11168-20-24-ns t hhold timeDS to SHCP; see Figure 113-2-3-nsTable 7.Dynamic characteristics …continuedVoltages are referenced to GND (ground = 0 V); for test circuit see Figure 14.Symbol Parameter Conditions25 ?C -40?C to +85 ?C -40?C to +125 ?C Unit Min Typ [1]Max Min Max Min Max3-state[1]Typical values are measured at nominal supply voltage.[2]t pd is the same as t PHL and t PLH .[3]t pd is the same as t PHL only.[4]t en is the same as t PZL and t PZH .[5]t dis is the same as t PLZ and t PHZ .[6]C PD is used to determine the dynamic power dissipation (P D in µW).P D =C PD ?V CC 2?f i +∑(C L ?V CC 2?f o )where:f i=input frequency in MHz;f o =output frequency in MHz;∑(C L ?V CC 2?f o )=sum of outputs;C L =output load capacitance in pF;V CC =supply voltage in V.[7]All 9outputs switching.12. Waveformst rec recovery time MR to SHCP; see Figure 1210-7-13-15-ns f max maximum frequencySHCP and STCP; see Figure 9 and 103052-24-20-MHz C PDpower dissipation capacitancef i = 1 MHz; V I =GND to V CC [6] [7]-130-----pFTable 7.Dynamic characteristics …continuedVoltages are referenced to GND (ground = 0 V); for test circuit see Figure 14.Symbol Parameter Conditions25 ?C -40?C to +85 ?C -40?C to +125 ?C Unit Min Typ [1]Max Min Max Min Max3-stateTable 8.Measurement points Type Input OutputV M V M74HC5950.5V CC0.5V CC 74HCT595 1.3V 1.3V3-stateTable 9.Test data74HC595V CC6ns50 pF1kΩopen GND V CC74HCT5953V6ns50 pF1kΩopen GND V CC3-state 13. Package outlineDIP16: plastic dual in-line package; 16 leads (300 mil)SOT38-4Fig 15.Package outline SOT38-4 (DIP16)3-state SO16: plastic small outline package; 16 leads; body width 3.9 mm SOT109-1Fig 16.Package outline SOT109-1 (SO16)3-state SSOP16: plastic shrink small outline package; 16 leads; body width 5.3 mm SOT338-1Fig 17.Package outline SOT338-1 (SSOP16)3-state TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm SOT403-1Fig 18.Package outline SOT403-1 (TSSOP16)。

74HC595D中文资料_数据手册_参数

NXP Semiconductors

74HC595; 74HCT595

8-bit serial-in, serial or parallel-out shift register with output latches; 3-state

11 12

SHCP STCP

14 DS

Q7S 9 15

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 12 December 2011

© NXP B.V. 2011. All rights reserved.

3 of 24

NXP Semiconductors

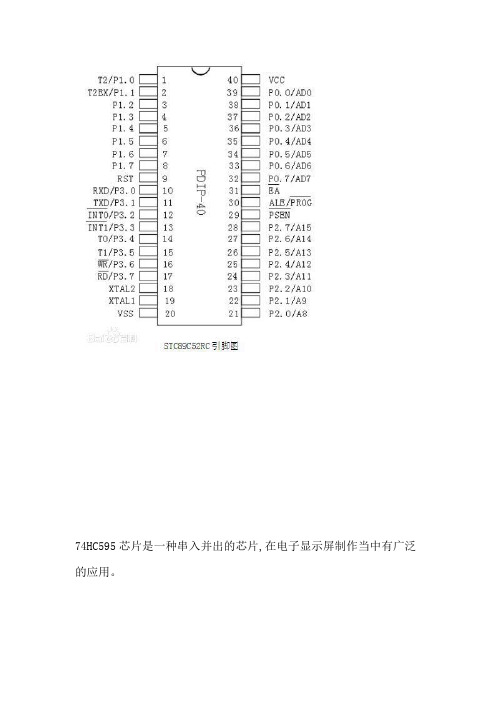

Fig 7. Pin configuration for DHVQFN16

74HC_HCT595

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 12 December 2011

16 VCC 15 Q0 14 DS 13 OE 12 STCP 11 SHCP 10 MR 9 Q7S

001aao241

Fig 5. Pin configuration DIP16, SO16

74HC595 74HCT595

Q1 1 Q2 2 Q3 3 Q4 4 Q5 5 Q6 6 Q7 7 GND 8

5. Functional diagram

14 DS 11 SHCP 10 MR

8-STAGE SHIFT REGISTER

4HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74HC595完整中文资料word资料5页

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

Glzaaa74hc595中文资料

秋风清,秋月明,落叶聚还散,寒鸦栖复惊。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存

储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C PD决定动态的能耗,

P D=C PD×V CC×f1+∑(C L×V CC2×f0)

F1=输入频率,C L=输出电容f0=输出频率(MHz)Vcc=电源电压

引脚说明

功能表

H=高电平状态L=低电平状态↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效

当MR为高电平,OE为低电平时,数据在SH CP上升沿进入移位寄存器,在ST CP上升沿输出到并行端口。

74HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote contr ol holding register. 描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解595的工作情况引脚功能表:真值表:74595的控制端说明:/SRCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

(通常我将RCK置为低电平,) 当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

74HC595D

74hc595d中文资料,74hc595d pdf 74HC595中文资料8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote control holding register.描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

74HC595参考数据CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压74HC595引脚说明74HC595功能表H=高电平状态L=低电平状态↑=上升沿↓=下降沿Z=高阻NC=无变化×=无效当MR为高电平,OE为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口。

74hc595d的生产厂家有NXP Semiconductors和ON Semiconductor最近闲来无事,想想好久没写点什么了。

所以闲余时间就写了个小程序和大家学习交流。

虽然通过仿真器调试过,但是由于没有做硬件,所以难免有疏漏之处,希望各位访客在发现后能指正。

硬件电路及程序原理描述:数码管采用8段共阴数码管。

74HC595中文

74HC595芯片中文资料

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C PD决定动态的能耗,

P D=C PD×V CC×f1+∑(C L×V CC2×f0)

F1=输入频率,C L=输出电容f0=输出频率(MHz)Vcc=电源电压

引脚说明

功能表

H=高电平状态

L=低电平状态

↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效

当MR为高电平,OE为低电平时,数据在SH CP上升沿进入移位寄存器,在ST CP上升沿输出到并行端口。

74HC595完整中文资料

74HC595完整中文资料74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有咼阻、关、断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote c ontrol holding register. 描述595是告诉的硅结构的CMO器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp勺上升沿输入,在S Tcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7 ),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能0E时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗,PD= CPD< VCC< f1 + 刀(CL X VCC2< f0) F 1=输入频率,。

1=输出电容f0 =输出频率(MHZ Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解595的工作情况功能表:真值表:74595的数据端:QA--QH:八位并行输出端,可以直接控制数码管的8个段。

QH':级联输出端。

我将它接下一个595的SI端。

SI:串行数据输入端。

74595的控制端说明:/SRCLR(10脚):低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->…-->QH ;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

74HC595完整中文资料

74HC595完整中文资料74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以挺直清除100MHz的移位频率输出力量并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote c ontrol holding register. 描述595是告知的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

假如两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7J,和—个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD 打算动态的能耗,PD = CPDxVCCxfl+E (CLxVCC2xfO) F 1 二输入频率,CL二输出电容fO :=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解595的工作状况功能表:真值表:74595的数据端:QA-QH:八位并行输出端,可以挺直把握数码管的8个段。

QH':级联输出端。

我将它接下一个595的SI端。

SI:串行数据输入端。

74595的把握端说明:/SRCLR (10脚):低点平常将移位寄存器的数据清零。

通常我将它接VcCo SRCK (11脚):上升沿时数据寄存器的数据移位。

QA->QB->QC->...->QH ;下降沿移位寄存器数据不变。

(脉冲宽度:5V 时,大于几十纳秒就行了。

5、74HC595完整中文资料

74HC59574HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz 的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote control holding register. 描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp 的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VC C2×f0) F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15 QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74hc595中文资料

74HC595芯片资料

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q 7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C PD决定动态的能耗,

P D=C PD×V CC×f1+∑(C L×V CC2×f0)

F1=输入频率,C L=输出电容f0=输出频率(MHz)Vcc=电源电压

引脚说明

功能表

H=高电平状态

L=低电平状态↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74HC595(文件编号:S&CIC0501) 3态8位移位寄存器一、 概述74HC595是一颗高速CMOS 8位3态移位寄存器/输出锁存器芯片,采用CMOS 硅栅工艺。

该器件包含一个8位串行输入与并行界出移位寄存器并提供一个8位D 型存储寄存器,该存储寄存器具有8位3三态输出。

分别提供独立的时钟信号给移位寄存器和存储寄存器,移位寄存器具有直接清零功能和串行输入输出功能以及级联应用.(采用标准引脚。

)移位寄存器和存储寄存器均为使用正边缘时钟触发,如果这两个时钟连接在一起,移位寄存器始终在存储寄存器的前一个时钟脉冲。

所有输入端口均设有防静电及瞬间过压保护电路。

二、 特性➢ 高速率传输, ➢ ➢ 高抗扰度 ➢ 对称输出阻抗 ➢ 传播延迟平衡:➢ ➢ 脚位及功能与74三、 产品应用➢ LED四、74HC595(文件编号:S&CIC0501) 3态8位移位寄存器五、脚位图与逻辑符号图74HC595(文件编号:S&CIC0501) 3态8位移位寄存器七、逻辑方框图74HC595(文件编号:S&CIC0501) 3态8位移位寄存器九、时序图(注:) 此图表示高阻抗时段.十、最大额定值符号特性参数值单位Vcc 工作电压-0.5 ~ +7 V Vl 直流输入电压-0.5 ~Vcc+0.5 V Vo 直流输出电压-0.5 ~Vcc+0.5 V Ilk 直流输正向输入±20 mA Iok 直流正向输出±20 mA Io 直流输出电流±35 mA Icc or I GND VCC或GND电流±70 mA Pd 功耗500(*) mW Tstg 储存温度-65 ~+150 ℃TL 焊接温度(10秒) 300 ℃建议使用值符号特性参数值单位Vcc 工作电压 2 ~ 6 V Vl 输入电压0~ Vcc V Vo 输出电压0 ~Vcc V 到p 工作温度-55 ~125 ℃tr, tf 输入转变时间Vcc=2.0V 0 ~1000 ns Vcc=4.5V 0 ~ 500 ns Vcc=6.0V 0 ~ 400 ns74HC595(文件编号:S&CIC0501) 3态8位移位寄存器十一、直流特性符号特性测试条件测试值单位Vcc(V)T A=25℃-40 ~ 85℃-55 ~ 125℃最小值典型值最大值最小值最大值最小值最大值V IH高电平输入2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.2 4.2 4.2V IL低电平输入2.0 0.5 0.5 0.5V 4.5 1.35 1.35 1.356.0 1.8 1.8 1.8V OH高电平输出(指QH’端的输出)2.0 Io=-20uA 1.9 2.0 1.9 1.9V4.5 Io=-20uA 4.4 4.5 4.4 4.46.0 Io=-20uA 5.9 6.0 5.9 5.94.5 Io=-6.0mA 4.18 4.31 4.13 4.106.0 Io=-7.8mA 5.68 5.8 5.63 5.60V OH高电平输出(指QA到QH端)2.0 Io=-20uA 1.9 2.0 1.9 1.9V4.5 Io=-20uA 4.4 4.5 4.4 4.46.0 Io=-20uA 5.9 6.0 5.9 5.94.5 Io=-6.0mA 4.18 4.31 4.13 4.106.0 Io=-7.8mA 5.68 5.8 5.63 5.60V OL低电平输出(指QH’端的输出)2.0 Io=20uA 0.0 0.1 0.1 0.1V4.5 Io=20uA 0.0 0.1 0.1 0.16.0 Io=20uA 0.0 0.1 0.1 0.14.5 Io=6.0mA 0.17 0.26 0.33 0.406.0 Io=7.8mA 0.18 0.26 0.33 0.40V OL低电平输出(指QA到QH端)2.0 Io=20uA 0.0 0.1 0.1 0.1V4.5 Io=20uA 0.0 0.1 0.1 0.16.0 Io=20uA 0.0 0.1 0.1 0.14.5 Io=6.0mA 0.17 0.26 0.33 0.406.0 Io=7.8mA 0.18 0.26 0.33 0.40I I输入漏电流 6.0 Vl = Vcc orGND±0.1 ±1 ±1 uAI OZ高阻抗输出漏电流 6.0 Vl = V IH orV ILV o = Vcc orGND±0.5 ±5 ±10 uAI CC静态电流 6.0 Vl = Vcc orGND4 40 80 uA74HC595(文件编号:S&CIC0501) 3态8位移位寄存器十二、交流特性(CL = 50pF,输入tt= t f = 6ns)符号限定特性测试条件测试值单位Vcc(V)C L(pF)T A=25℃-40 ~ 85℃-55 ~ 125℃最小典型最大最小最大最小最大t TLH t THL(QA-QH)输出转变时间2.05025 60 75 90ns4.5 7 12 15 186.0 6 10 13 15t TLH t THL(SQH)输出转变时间2.05030 75 95 115ns4.5 8 15 19 236.0 7 13 16 20t PLH t PHL (SCK-QH’)传播延时时间2.05045 125 155 190ns4.5 15 25 31 386.0 13 21 26 32t PLH t PHL(SCLR-QH’)传播延时时间2.05060 175 220 265ns4.5 18 35 44 536.0 15 30 37 45t PLH t PHL (RCK-Qn)传播延时时间2.05060 150 190 225ns4.5 20 30 38 456.0 17 26 32 382.015075 190 240 285ns4.5 25 38 48 576.0 22 32 41 48t PZL t PZH 高阻抗输出开启时间2.050 R L= 1KΩ45 135 170 205ns4.5 15 27 34 416.0 13 23 29 352.0150 R L= 1KΩ60 175 220 265ns4.5 20 35 44 536.0 17 30 37 45t PLZ t PHZ 高阻抗输出关闭时间2.050 R L= 1KΩ30 150 190 225ns4.5 15 30 38 456.0 14 26 32 38f MAX最高时钟频率2.0506.0 17 4.8 4MHz 4.5 30 50 24 206.0 35 59 28 242.01505.2 14 4.2 3.4MHz 4.5 26 40 21 176.0 31 45 25 20t W(H)最小脉宽(SCK, RCK)2.05017 75 95 110ns4.5 6 15 19 2274HC595(文件编号:S&CIC0501) 3态8位移位寄存器6.0 6 13 16 19t W(L)(SCLR)最小脉宽2.05020 75 95 110ns 4.5 6 15 19 226.0 6 13 16 19t S(SI-CCK)最小启动时间2.05025 50 65 75ns4.5 5 10 13 156.0 4 9 11 13t S(SCK-RCK)最小启动时间2.05035 75 95 110ns4.5 8 15 19 226.0 6 13 16 19t S(SCRL-RCK)最小启动时间2.05040 100 125 145ns4.5 10 20 25 296.0 7 17 21 25t h最小维持时间2.0500 0 0ns 4.5 0 0 06.0 0 0 0t REM最小复位时间2.05015 50 65 75ns 4.5 3 10 13 156.0 3 9 11 13十三、输入电容特性符号特性测试条件测试值单位Vcc(V)T A=25℃-40 ~ 85℃-55 ~ 125℃最小典型最大最小最大最小最大CIN 输入电容 5 10 10 10 皮法CPD 功率耗散电容184 皮法74HC595(文件编号:S&CIC0501) 3态8位移位寄存器十四、 测试电路123321DCBAVCCOPEN GNDR1CLD.U.T.VCCRTPULSE GENERATOR测试转换 t PLH t PHL 开路 t PZL t PLZ 接电源正 t PZH t PHZ接地LC=50-150PF 或相当于此值的容量 (包含测试架与探针之分布电容) R1=1KΩ或相当于1KΩ的电阻值. RT=脉冲产生器的Zout. (典型值= 50Ω)波形图1: SCK ~ QH’的传播延时时间以及SCK 的最小脉宽. (频率=1MHz;50%的占空比)74HC595(文件编号:S&CIC0501) 3态8位移位寄存器波形图2: RCK ~ Qn的传播延时时间(频率=1MHz;50%的占空比)波形图3: SI ~ SCK启动时间与持续时间(此启动时间指波形脉冲的启动时间) (频率=1MHz;50%的占空比)74HC595(文件编号:S&CIC0501) 3态8位移位寄存器波形图4: SCK ~ RCK启动时间与持续时间(此启动时间指波形脉冲的启动时间)(频率=1MHz;50%的占空比)波形图5: SCLR最小脉宽与复位时间(频率=1MHz;50%的占空比)74HC595(文件编号:S&CIC0501) 3态8位移位寄存器波形图6: 输出启动与关闭时间(频率=1MHz;50%的占空比)波形图7:输入波形(频率=1MHz;50%的占空比)74HC595(文件编号:S&CIC0501) 3态8位移位寄存器74HC595(文件编号:S&CIC0501) 3态8位移位寄存器74HC595(文件编号:S&CIC0501) 3态8位移位寄存器。