USRP母版和子板性能

usrp介绍

看到一介绍USRP的好文,征得作者同意,现转载如下。

该文转载自:/blog/cns!4878164F2CBA0005!197.entryUSRP硬件平台介绍USRP:Universal Software Radio PeripheralUSRP由母板和子板组成。

一块USRP母板主要包括如下硬件器件[1]:1.4个高速AD转换器,每个AD采样率为64MS/s,12bit,85dB SFD R(无杂散动态范围)(AD9862);2.4个高速DA转换器,每个DA采样率为128MS/s,14bit,83dB SF DR (AD9862);3. 一片FPGA,型号为Altera Cyclone EP1C12Q240C8;4.一片高速USB2.0控制器(接口速率480Mbps),型号为Cypress EZ -USB FX2(注意,USRP不支持USB1.x);5.4个扩展插槽(2发2收),用于连接2-4块子板;6.每个子板上提供16个GPIO引脚,用于外部调试;7.一些胶合逻辑。

USRP2是USRP的增强版,于2008年9月推出,其母板所选用硬件的信号处理能力有很大提高[1]:üFPGA选择Xilinx Spartan 3-2000 FPGA;ü除USB2.0之外,还提供G比特以太网接口;ü两个100MS/s,14bit的AD转换器;ü两个400MS/s,16bit的DA转换器;üSD卡读卡器;ü等等…USRP的子板作为射频前端使用,其作用是将基带信号调制到一个较高的载频上输出,或将输入信号下变频到基带。

子板的类型有三种:接收板(Receiver)、发送板(Transmitter)、收发板(Transceiver)。

接收板只支持接收,并只有一个RX端口,接收板有以下几种[1][2]:üBasicRX,1-250MHz接收,BasicRX板只进行一个简单的接口转换,即将母板上扩展插槽引脚上的模拟信号转换为SMA射频线缆中的模拟信号。

软考嵌入式系统设计师笔记归纳总结

软考嵌入式系统设计师笔记1.嵌入式系统的组成:硬件层、中间层、系统软件层和应用软件层(1)硬件层:嵌入式微处理器、存储器、通用设备接口和I/O 接口。

嵌入式核心模块=微处理器+电源电路+时钟电路+存储器Cache:位于主存和嵌入式微处理器内核之间,存放的是最近一段时间微处理器使用最多的程序代码和数据。

它的主要目标是减小存储器给微处理器内核造成的存储器访问瓶颈,使处理速度更快。

(2)中间层(也称为硬件抽象层HAL或者板级支持包BSP):它将系统上层软件和底层硬件分离开来,使系统上层软件开发人员无需关系底层硬件的具体情况,根据BSP 层提供的接口开发即可。

BSP 有两个特点:硬件相关性和操作系统相关性。

设计一个完整的BSP 需要完成两部分工作:A、嵌入式系统的硬件初始化和BSP 功能。

片级初始化:纯硬件的初始化过程,把嵌入式微处理器从上电的默认状态逐步设置成系统所要求的工作状态。

板级初始化:包含软硬件两部分在内的初始化过程,为随后的系统初始化和应用程序建立硬件和软件的运行环境。

系统级初始化:以软件为主的初始化过程,进行操作系统的初始化。

B、设计硬件相关的设备驱动。

(3)系统软件层:由RTOS、文件系统、GUI、网络系统及通用组件模块组成。

RTOS是嵌入式应用软件的基础和开发平台。

(4)应用软件:由基于实时系统开发的应用程序组成。

2.嵌入式系统的定义(1)定义:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

(2)嵌入式系统发展的4 个阶段:无操作系统阶段、简单操作系统阶段、实时操作系统阶段、面向Internet 阶段。

(3)知识产权核(IP 核):具有知识产权的、功能具体、接口规范、可在多个集成电路设计中重复使用的功能模块,是实现系统芯片(SOC)的基本构件。

(4)IP 核模块有行为、结构和物理3 级不同程度的设计,对应描述功能行为的不同可以分为三类:软核、固核、硬核。

USRP原理

USRP原理1.概述:USRP(universal software radio peripheral通用软件无线电外设)是实现软件无线电的硬件平台,是种非常灵活的USB 设备,用来把计算机接入射频的世界,在无线通信系统中充当数字基带和中频部分。

下图为一个典型的软件无线电处理流程:USRP由Matt Ettus发明,是GNU Radio(开源软件无线电工具包)最重要的硬件“伙伴”。

它的硬件系统也是完全开源的,包括母板和子板两部分,母板的主要功能为中频采样以及中频信号到基带信号之间的互相转换,子板的功能在于射频信号的接收和发送以及到中频的转换。

子板有多种类型,分别覆盖不同的射频频谱范围,且具有不同的收发能力和增益。

而计算机才是真正处理波形、调制解调的部分。

一块母板最多接四块子板。

插着四个子板(两个接收子板两个发射子板)的USRP实物图:USRP的基本结构图:2.母板母板的逻辑功能结构图:2.1AD/DAUSRP母板采用2块AD9862芯片,每块可分别提供两路12bit、采样率是每秒64M符号的ADC和两路14bit、采样率是每秒128M符号的DAC。

那么一块主板可提供4路ADC和4路DAC,也即收发各两路的复采样。

此外DAC单元还集成了数字上变频(DUC)功能。

复采样:和实采样相对,每次采样有两支路输出,记作I:同相支路,Q:正交支路。

AD9862芯片是业界首款适合无线宽带通信应用的高性能混合信号前端(MxFE),上面集成了四个高性能数据转换器(2个ADC和2个DAC)。

发送路径允许接受多种数据格式,包括两个高性能DAC、发送端可编程增益放大器(PGA)、2倍或4倍内插滤波器、一个希尔伯特(Hilbert)数字滤波器和用于复信号或实信号上变频的数字混频器(DUC)。

这些特点使系统结构从本质上减少了重构和抗混叠滤波要求。

接收路径包括用以在基带或低中频(IF)上接收多种数据或正交(I&Q)数据的两个高性能ADC、输入缓冲器、接收端可编程增益放大器和抽取滤波器。

子模板与IO接口设备的软件驱动简介

子模板与IO接口设备的软件驱动简介软件驱动是连接操作系统与硬件设备的一种软件程序,其作用是使操作系统能够正确识别、控制和与硬件设备进行通信。

在这里,我们将简要介绍子模板与IO接口设备的软件驱动。

子模板与IO接口设备的软件驱动是一种特定类型的驱动程序,其作用是实现操作系统与IO接口设备的交互。

IO接口设备包括各种外部设备,如打印机、键盘、鼠标、USB设备等。

子模板是一种通用型设备,在连接新设备时,需要相应的软件驱动程序来实现设备的支持。

在子模板与IO接口设备的软件驱动中,通常包括以下几个主要功能:1. 设备识别:软件驱动程序可以识别并标识连接的子模板和IO接口设备。

这样,操作系统就能够正确地识别设备并分配适当的资源。

2. 设备控制:软件驱动程序通过操作系统提供的接口来控制子模板和IO接口设备的各种功能。

这包括发送命令、接收数据、配置设备参数等。

3. 设备通信:软件驱动程序可以实现操作系统与设备之间的数据通信。

这样,用户就可以通过软件来操作和管理设备。

总的来说,子模板与IO接口设备的软件驱动是实现设备与操作系统之间交互的重要组成部分。

它能够帮助操作系统正确地识别、控制和通信子模板与IO接口设备,使设备能够正常工作并与计算机系统协同运行。

软件驱动是连接操作系统与硬件设备的一种软件程序,其作用是使操作系统能够正确识别、控制和与硬件设备进行通信。

在这里,我们将继续讨论子模板与IO接口设备的软件驱动的相关内容。

在现代计算机系统中,子模板与IO接口设备的软件驱动扮演着至关重要的角色。

随着计算机硬件不断发展和更新,越来越多的外部设备和接口不断涌现,软件驱动程序必须能够及时适配新的硬件设备,保证设备的兼容性和可靠性。

子模板是一种种通用的接口设备,可以连接各种各样的硬件设备。

软件驱动需要与特定的硬件设备相配合,以实现对设备的控制和数据传输。

因此,子模板与IO接口设备的软件驱动通常会涉及到硬件底层的控制和通信协议。

例如,对于USB设备,软件驱动需要处理USB协议的具体细节,包括数据传输、端点配置、插拔事件等。

usrp的基本结构和功能

USRP即Universal Software Radio Periphehal 的缩写,软件无线电外设。

其设计宗旨是使普通计算机能像高带宽的软件无线电外设一样工作。

从本质上讲,它充当一个无线通信系统的数字基带和中频部分。

USRP背后的设计理念是在主机CPU上完成所有波形相关方面的处理,比如调制和解调。

所有诸如数字上下变频、抽样和内插等高速通用操作都在USRP上的FPGA上完成。

USRP 由母版,覆盖不同带宽的子板以及相应的天线组成。

USRP有四路12位高速模数转换(ADCs)采样速率可达64MSsamples/sec,4路14位数模转换器(DACs),采样速率可达128 MSsamples/sec,转换器(DACs),采样速度可达128MSamples/sec。

这些4入4出通道同Altera 公司的Cyclone EP1 C12 FPGA相连。

FPGA相应地同Cypress公司的USB2接口芯片FX2相连,然后连接至计算机。

USRP同计算机通过高速的USB2接口相连,不能用于USB1.1接口。

因此,理论上,当采样信号时,系统具有4路输入4路输出。

但是,现实中csiji复合的(IQ)信号时,它只提供更多的灵活性(和带宽)。

因此把它们成对,便可形成两对复合输入两对复合输出。

基于USRP的成功经验,USRP2以更高速度和更高的精度(100MHz) 14位ADCs和400MHz 16位DACs ),允许使用更宽波段的信号,增加了信号的动态范围。

针对DSP应用优化了的大型现场可编程门阵列(FPGA)可以在高采样率下处理复杂波形。

千兆以太网络接口,使应用程序可以使用USRP2同时发送或接受50MHz的射频带宽。

在USRP2中,FPGA出现了诸如数字上变频器和下变频器等高速采样处理器。

较低采样率的操作可在主机电脑上,甚至可以在具有32位RISC微处理器和有很大用户设计自由空间的FPGA上。

USRP2的配置和固件被存储在一个SD闪存卡里,无需特别的硬件就可以轻松编程。

usrp介绍

看到一介绍USRP的好文,征得作者同意,现转载如下。

该文转载自:/blog/cns!4878164F2CBA0005!197.entryUSRP硬件平台介绍USRP:Universal Software Radio PeripheralUSRP由母板和子板组成。

一块USRP母板主要包括如下硬件器件[1]:1.4个高速AD转换器,每个AD采样率为64MS/s,12bit,85dB SFD R(无杂散动态范围)(AD9862);2.4个高速DA转换器,每个DA采样率为128MS/s,14bit,83dB SF DR (AD9862);3. 一片FPGA,型号为Altera Cyclone EP1C12Q240C8;4.一片高速USB2.0控制器(接口速率480Mbps),型号为Cypress EZ -USB FX2(注意,USRP不支持USB1.x);5.4个扩展插槽(2发2收),用于连接2-4块子板;6.每个子板上提供16个GPIO引脚,用于外部调试;7.一些胶合逻辑。

USRP2是USRP的增强版,于2008年9月推出,其母板所选用硬件的信号处理能力有很大提高[1]:üFPGA选择Xilinx Spartan 3-2000 FPGA;ü除USB2.0之外,还提供G比特以太网接口;ü两个100MS/s,14bit的AD转换器;ü两个400MS/s,16bit的DA转换器;üSD卡读卡器;ü等等…USRP的子板作为射频前端使用,其作用是将基带信号调制到一个较高的载频上输出,或将输入信号下变频到基带。

子板的类型有三种:接收板(Receiver)、发送板(Transmitter)、收发板(Transceiver)。

接收板只支持接收,并只有一个RX端口,接收板有以下几种[1][2]:üBasicRX,1-250MHz接收,BasicRX板只进行一个简单的接口转换,即将母板上扩展插槽引脚上的模拟信号转换为SMA射频线缆中的模拟信号。

龙尚U9300C 模块硬件接口手册_V1.2

U9300C 模块硬件接口手册_V1.2

共 53 页

第 1 页

重要声明 版权声明 版权所有:龙尚科技(上海)有限公司 本资料及其包含的所有内容为龙尚科技(上海)有限公司所有,受中国法律及适 用之国际公约中有关著作权法律的保护。未经龙尚科技(上海)有限公司书面授 权,任何人不得以任何形式复制、传播、散布、改动或以其它方式使用本资料的 部分或全部内容,违者将被依法追究责任。 不保证声明 龙尚科技 (上海) 有限公司不对此文档中的任何内容作任何明示或暗示的陈述或 保证, 而且不对特定目的的适销性及适用性或者任何间接、特殊或连带的损失承 担任何责任。 保密声明 本文档(包含任何附件)包含的信息是保密信息。接收人了解其获得的本文档是 保密的, 限用于规定的目的外不得用于任何目的,也不得将本文档泄露给任何第 三方。 免责声明 本公司不承担由于客户不正常操作造成的财产或者人身伤害责任。 请客户按照手 册中的技术规格和参考设计开发相应的产品。在未声明之前,本公司有权根据技 术发展的需要对本手册内容进行更改,且更改版本不另行通知。

U9300C 模块硬件接口手册_V1.2 共 53 页 第 3 页

U9300C 模块硬件接口手册_V1.2

共 53 页

第 2 页

目录

1. 引言............................................................................................................................................. 8 1.1. 文档目的...........................................................

精选Optix155622硬件设备

IU1:光接口板位,可以安插OI2S/OI2D/OI4/SB2等IU2,IU3:光/电接口板位,可以安插OI2S/OI2DD/OI4/SB2,SP1/SP2/SM1/HP2/PL3等IU3:环境监控,可以安插EMUIU4:电接口板位,可以安插PD2T/PM2/TDA/ET1/AIU等SCB:系统控制板位,可以安插X42、SCC、STG、OHP2A:防尘网,电源滤波板,可以安插POIB:风扇板位,FAN

STM-1

SPI:同步物理接口; MSP:复用段保护;RST:再生段终端; MSA:复用段适配; MST:复用段终端; HPT:高阶通道终端;再生段终端及复用段终端功能:先进的开销处理芯片完成所有开销字节的处理,包括B1、B2的计算,K1、K2字节的应用等,同时完成DCC通信和公务通信功能,此外还完成再生段、复用段和高阶通道的告警处理和维护功能

T-ALOS

155/622小盒子

2M故障环回法简单处理流程

通常交换通知某站不好,我们从网管上先对 小站上做环回操作,如果交换看不好,就放通,下一步仍从网管上对此站对应的北环机房的设备做环回操作,如仍不好,就从传输DDF架上环回,再则,就从交换的DDF架上环回,如不好,就是交换自己的事。

OI2板光模块指示

I:局内通信;S:短距离局间通信;L:表示长距离局间通信;横杠后的第一位表示STM的速率等级;第二个数字(小数点后的第一个数字)表示工作的波长窗口和所有光纤类型,1和没有表示工作的工作窗口为1310,2表示1550

OI4板

OI4板是STM-4速率等级的光接口板,目前此光板只有一种类型。OI4板除提供的线路速率高于OI2板外,其它基本相同。

结合原理了解支路板的功能

2048Kbit/s

其功能包括PDH物理接口(PPI)、低阶通道适配(LPA)、低阶通道终端(LPT)、高阶通道适配(HPA)

各类单板名称,功能介绍

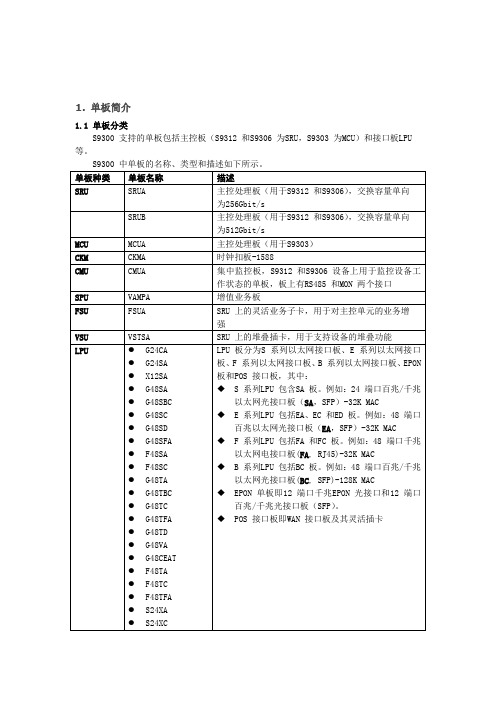

1. 单板简介1.1 单板分类S9300 支持的单板包括主控板(S9312 和S9306 为SRU,S9303 为MCU)和接口板LPU 等。

S9300 中单板的名称、类型和描述如下所示。

单板种类单板名称描述SRU SRUA主控处理板(用于S9312 和S9306),交换容量单向为256Gbit/sSRUB主控处理板(用于S9312 和S9306),交换容量单向为512Gbit/sMCU MCUA主控处理板(用于S9303)CKM CKMA 时钟扣板-1588CMU CMUA 集中监控板,S9312 和S9306 设备上用于监控设备工作状态的单板,板上有RS485 和MON 两个接口SPU VAMPA增值业务板FSU FSUA SRU 上的灵活业务子卡,用于对主控单元的业务增强VSU VSTSA SRU 上的堆叠插卡,用于支持设备的堆叠功能LPU●G24CA●G24SA●X12SA●G48SA●G48SBC●G48SC●G48SD●G48SFA●F48SA●F48SC●G48TA●G48TBC●G48TC●G48TFA●G48TD●G48VA●G48CEAT●F48TA●F48TC●F48TFA●S24XA●S24XC LPU 板分为S 系列以太网接口板、E 系列以太网接口板、F 系列以太网接口板、B 系列以太网接口板、EPON 板和POS 接口板,其中:◆S 系列LPU 包含SA 板。

例如:24 端口百兆/千兆以太网光接口板(SA,SFP)-32K MAC◆ E 系列LPU 包括EA、EC 和ED 板。

例如:48 端口百兆以太网光接口板(EA,SFP)-32K MAC◆ F 系列LPU 包括FA 和FC 板。

例如:48 端口千兆以太网电接口板(FA, RJ45)-32K MAC◆ B 系列LPU 包括BC 板。

例如:48 端口百兆/千兆以太网光接口板(BC, SFP)-128K MAC◆EPON 单板即12 端口千兆EPON 光接口和12 端口百兆/千兆光接口板(SFP)。

USRP1理论指导

如何对 tx_chain.v 写测试用例(test bench) ?.......................................................... 20 可以把自己的 Verilog 代码烧入去测试吗?..............................................................21 CORDIC 模块输出有效的数据需占有多少时钟, 为何 cordic 算法的构建要固定为 12层迭代呢?............................................................................................................. 21 内部 DLL 采样是否高于 64MSPS? 如果这样的话, DLL (采样)速度如何?它 可否被利用?................................................................................................................. 22 AD9862 的寄存器是如何被维护的?..........................................................................23 为了同时掌控两个 Basic_Tx 子板,现而易见两个 AD9862 相应其独立工作。该 对 AD9862 将时钟从 USRP 主板同时引入,是同一时钟吗?.............................. 23 能再唠叨一下 AD9862 的 PGA 的概念吗?............................................................ 23 更新 AD9862 的 AUX_DAC port, 很明显需通过 USB 控制器来来实现!这样理 解正确吗?必须牺牲 USB 的带宽来配置 AUX_DAC 吗?..................................... 23 控制 FPGA 寄存器问题...................................................................................................... 24 哪些 FPGA 的寄存器用于 SPI、I2C 控制?或者说它们只是标准寄存器?........24 诸如下面例程所示,使用 libusrp 读写 FPGA 寄存器。无关乎 FPGA 的那个寄存 器,返回“写”的过程都是“true” ,返回“读”的过程都是 0。这是何因?..... 25 Verilog 代码里并无用户定义的 FPGA 寄存器。需手动添加吗?需在 usrp_std.v 内完善这些吗?............................................................................................................. 25 可以使用 usrper 来读取 FPGA 的寄存器吗?......................................................... 25 数字下变频问题 ..................................................................................................................... 26 FPGA 接收链路中的复接器(Multiplexer)的目的如何?.......................................26 而半带抽取 FIR 滤波器在 FPGA 内以恒定值,抽取系数 2 来进行抽取滤波,这使 得系统的最低抽取系数为 8,使得通过 USRP 的 USB 的速率为 8 Msps 的。这样理 解正确吗?..................................................................................................................... 27 想要得到抽取系数为 64, 那么 DDC 的相应的 CIC 滤波器 (抽取系数 32) , HBF (抽 取系数 2)和级联后的 CIC + HBF(综合抽取系数为 64)的表现如何?.............. 27 FX2 支持多少 endpoints ?............................................................................................29 研究 tx_buffer 功能时发现该功能块交错地发送数据( 2 x I 通道、 2 x Q 通道) 。 这理解对吗?................................................................................................................. 29 FX 重构输入/出 FPGA 的 数据吗?......................................................................... 29 FIFO 的 wreq 触发器是由 (WR & ~ write_countr8) 触发的。这是否意味着在 WR 被移走之前仅 256 个 16 位的采样被写入 FIFO ?为何如此这般?该如何 准确确定何时已有必须要写入 FIFO 中的 I 或 Q 采样?.....................................30 当 FX2 诊断出 FPGA 上有 have_space(管脚有请求时) ,便传送 1 个完整的缓 存的 USB 数据包到 FPGA,然后有在询检管脚 have_space,这理解对吗?..... 30 苦于无法找到任何阐述 USRP 主板上的 EEPROM 的资料?............................... 30 USRP 上的 Cypress EZ-USB FX2 USB 控制器 的工作机制如何?....................... 31 USRP FX2 的工作原理?............................................................................................任公司

USRP平台结构和使用介绍

武汉中昊信科技有限公司

应用--无线电监测

对于传统的无线电监测任务可以有更灵活的解决方案

提供对新的智能认知无线电监测的能力。

武汉中昊信科技有限公司

应用--科学研究

认知无线电

新的调制解调方法

新的通信协议

武汉中昊信科技有限公司

应用--业余无线电台

可配置/可编程

多频段/多模式 可联网

武汉中昊信科技有限公司

体系结构-硬件

CIC & HB RX FIFO

射频子板

CORDIC

TX FIFO CIC Interp

武汉中昊信科技有限公司

PC端接口

体系结构-硬件

User-defined Code ETH FPGA ADC DAC

RF Front end

Spartan-3A DSP FPGA XC3D3400A UHD FPGA Firmware in flash, loaded in power-cycle Digital down converters (DDC) implemented with cascaded integrator-comb (CIC) filters, decimator and interpolator

武汉中昊信科技有限公司

理想的软件无线电体系结构

天线

基带(软件部分)

ADC DAC

GPU

武汉中昊信科技有限公司

软件无线电的优点-功能方面

可配置(Re-configurability)

增强可能的潜在应用 能最优化网络资源 便于演进到新的标准 多功能设备(Multifunctional devices) 可工作在多种模式(Multi-mode) 可工作在多个频段(Multi-band) 更短的市场投放时间(Shorter time-to-market) 更快的提供更有针对性得差异化产品 向后的兼容性

linux五大子系统

用户程序通过软件中断后,调用系统内核提供的功能,这个在用户空间和内核提供的服务之间的接口称为系统调用。

系统调用是Linux内核提供的,用户空间无法直接使用系统调用。

在用户进程使用系统调用必须跨越应用程序和内核的界限。

Linux内核向用户提供了统一的系统调用接口,但是在不同处理器上系统调用的方法各不相同。

Linux内核提供了大量的系统调用,现在从系统调用的基本原理出发探究Linux系统调用的方法。

这是在一个用户进程中通过GNU C库进行的系统调用示意图,系统调用通过同一个入口点传入内核。

以i386体系结构为例,约定使用EAX寄存器标记系统调用。

当加载了系统C库调用的索引和参数时,就会调用0x80软件中断,它将执行system_call 函数,这个函数按照EAX寄存器内容的标示处理所有的系统调用。

经过几个单元测试,会使用EAX寄存器的内容的索引查system_call_table表得到系统调用的入口,然后执行系统调用。

从系统调用返回后,最终执行system_exit,并调用resume_userspace函数返回用户空间。

linux内核系统调用的核心是系统多路分解表。

最终通过EAX寄存器的系统调用标识和索引值从对应的系统调用表中查出对应系统调用的入口地址,然后执行系统调用。

linux系统调用并不单层的调用关系,有的系统调用会由内核进行多次分解,例如socket 调用,所有socket相关的系统调用都与_NR_socketcall系统调用关联在一起,通过另外一个适当的参数获得适当的调用。

进程管理子系统当用户使用系统提供的库函数进行进程编程,用户可以动态地创建进程,进程之间还有等待,互斥等操作,这些操作都是由linux内核来实现的。

linux内核通过进程管理子系统实现了进程有关的操作,在linux系统上,所有的计算工作都是通过进程表现的,进程可以是短期的(执行一个命令),也可以是长期的(一种网络服务)。

Optix OSN2500PIU单板的功能和特性及工作原理doc

Optix OSN2500PIU单板的功能和特性及工作原理一.功能和特性

PIU是电源接口板,支持电源接入、防雷和滤波等功能和特性。

PIU单板的具体功能和特性如表1所示。

表1 PIU单板的功能和特性

功能和特

描述

性

防雷功能提供防雷功能,实现单板防雷失效告警信息上报。

滤波功能提供对电源端口的滤波,并对单板进行结构屏蔽,增强了系统的电磁兼容性。

供电接口提供1路外置单元(如:COA)供电接口,每路为50W。

FAN供电为FAN板提供–48V±20%电压。

告警监测提供单板在位告警信息的上报。

电源备份提供1+1热备份,任意1块PIU板可以满足单独为整个子架供电的需要。

二.工作原理和信号流

PIU单板由电源接入单元、滤波单元、防雷单元及失效检测构成。

PIU单板功能框图如图1所示。

图1 PIU单板功能框图

1.电源接入单元

为系统接入–48V或–60V的电源。

2.防雷单元

用于过流保护和防止雷击,并可以向CXL板上报防雷单元失效告警。

3.滤波单元

采用EMI(ElectroMagnetic Interference)滤波器,对电磁干扰信号进行滤波,以保证设备运行的稳定。

Linux驱动设计——内核模块(一)

Linux驱动设计——内核模块(⼀)Linux内核理论基础组成Linux内核的5个⼦系统:进程调度(SCHED)/内存管理(MM)/虚拟⽂件系统(VFS)/⽹络接⼝(NET)/进程间通信(IPC)。

进程调度(SCHED)在设备驱动编程中,当请求的资源不能得到满⾜时,驱动⼀般会调度其他进程执⾏,并使本进程进⼊睡眠状态,直到它请求的资源被释放,才会被唤醒⽽进⼊就绪态。

睡眠分成可被打断的睡眠和不可被打断的睡眠,两者的区别在于可被打断的睡眠在收到信号的时候会醒。

内存管理(MM)内存管理的主要作⽤是控制多个进程安全地共享主内存区域。

当CPU 提供内存管理单元(MMU)时,Linux 内存管理完成为每个进程进⾏虚拟内存到物理内存的转换。

虚拟⽂件系统(VFS)Linux 虚拟⽂件系统(VFS)隐藏各种了硬件的具体细节,为所有的设备提供了统⼀的接⼝。

它独⽴于各个具体的⽂件系统,是对各种⽂件系统的⼀个抽象,它使⽤超级块super block 存放⽂件系统相关信息,使⽤索引节点inode 存放⽂件的物理信息,使⽤⽬录项dentry 存放⽂件的逻辑信息。

⽹络接⼝(NET)⽹络接⼝提供了对各种⽹络标准的存取和各种⽹络硬件的⽀持。

在Linux 中⽹络接⼝可分为⽹络协议和⽹络驱动程序,⽹络协议部分负责实现每⼀种可能的⽹络传输协议,⽹络设备驱动程序负责与硬件设备通信,每⼀种可能的硬件设备都有相应的设备驱动程序。

进程间通信(IPC)进程通信⽀持提供进程之间的通信,Linux ⽀持进程间的多种通信机制,包含信号量、共享内存、管道等,这些机制可协助多个进程、多资源的互斥访问、进程间的同步和消息传递。

Linux 内核的5 个组成部分之间的依赖关系如下:1、进程调度与内存管理之间的关系:这两个⼦系统互相依赖。

在多道程序环境下,程序要运⾏必须为之创建进程,⽽创建进程的第⼀件事情,就是将程序和数据装⼊内存。

2、进程间通信与内存管理的关系:进程间通信⼦系统要依赖内存管理⽀持共享内存通信机制,这种机制允许两个进程除了拥有⾃⼰的私有空间,还可以存取共同的内存区域。

vpx总线标准背板

vpx总线标准背板VPX总线标准背板。

VPX是一种高性能计算机总线标准,用于军事和航空航天等领域的应用。

VPX 总线标准背板是VPX系统中的重要组成部分,它承担着连接各种模块和组件的重要作用。

本文将介绍VPX总线标准背板的基本概念、特点和应用。

VPX总线标准背板是一种高速、高密度的背板结构,通常采用3U或6U的尺寸。

它采用了高速差分信号传输技术,支持多种协议和接口标准,如PCI Express、Gigabit Ethernet、串行RapidIO等。

这使得VPX总线标准背板能够满足各种高性能计算和数据传输的需求。

与传统的背板相比,VPX总线标准背板具有更高的带宽和更低的延迟。

它采用了多层板设计,通过优化布局和信号完整性设计,能够实现更稳定和可靠的信号传输。

此外,VPX总线标准背板还支持热插拔和冗余设计,提高了系统的可靠性和可维护性。

在实际应用中,VPX总线标准背板被广泛应用于军事雷达、通信系统、航空航天控制系统等领域。

它能够满足复杂系统对于高带宽、低延迟、可靠性和可扩展性的要求。

同时,VPX总线标准背板还支持多种工业标准,如VITA 46、VITA 65等,为不同领域的应用提供了灵活的选择。

总的来说,VPX总线标准背板作为VPX系统的核心组成部分,具有高速、高密度、可靠性和可扩展性的特点,适用于各种高性能计算和数据传输的应用场景。

它的发展将进一步推动军事和航空航天领域的技术进步,为复杂系统的设计和应用提供了强大的支持。

在未来,随着技术的不断进步和应用领域的不断拓展,VPX总线标准背板将会继续发挥重要作用,为各种高性能计算和数据传输应用提供更加强大和灵活的解决方案。

我们期待着VPX总线标准背板在未来的发展和应用中取得更加辉煌的成就。

电子设计产品硬件概要设计(模板)V1.1

4 关键器件选型 ...................................................................................................................................... 10

4.1

单板 1 关键器件选型........................................................................................................... 10

2.2.3 单板 n 功能简介............................................................................................................. 7

2.3

硬件运行环境说明................................................................................................................. 7

3.4.1 单板 n 总体框图及功能说明....................................................................................... 10

3.4.2 单板 n 重用技术分析................................................................................................... 10

服务器三大体系SMPNUMAMPP研讨

服务器三大体系SMPNUMAMPP研讨服务器三大体系SMP、NUMA、MPP介绍摘要:从系统架构来看,目前的商用服务器大体能够分为三类,即对称多处理器结构、非一致存储访问结构与海量并行处理结构。

从系统架构来看,目前的商用服务器大体能够分为三类,即对称多处理器结构(SMP:Symmetric Multi-Processor),非一致存储访问结构(NUMA:Non-Uniform Memory Access),与海量并行处理结构(MPP:Massive Parallel Processing)。

它们的特征分别描述如下:SMP(Symmetric Multi-Processor)所谓对称多处理器结构,是指服务器中多个CPU对称工作,无主次或者从属关系。

各CPU共享相同的物理内存,每个CPU访问内存中的任何地址所需时间是相同的,因此SMP 也被称之一致存储器访问结构(UMA:Uniform Memory Access)。

对SMP服务器进行扩展的方式包含增加内存、使用更快的CPU、增加CPU、扩充I/O(槽口数与总线数)与添加更多的外部设备(通常是磁盘存储)。

SMP服务器的要紧特征是共享,系统中所有资源(CPU、内存、I/O等)都是共享的。

也正是由于这种特征,导致了SMP服务器的要紧问题,那就是它的扩展能力非常有限。

关于SMP服务器而言,每一个共享的环节都可能造成SMP服务器扩展时的瓶颈,而最受限制的则是内存。

由于每个CPU务必通过相同的内存总线访问相同的内存资源,因此随着CPU数量的增加,内存访问冲突将迅速增加,最终会造成CPU资源的浪费,使CPU性能的有效性大大降低。

实验证明,SMP服务器CPU利用率最好的情况是2至4个CPU。

NUMA(Non-Uniform Memory Access)由于SMP在扩展能力上的限制,人们开始探究如何进行有效地扩展从而构建大型系统的技术,NUMA就是这种努力下的结果之一。

基于OAI的LTE通信平台的研究与实现

基于OAI的LTE通信平台的研究与实现甘显豪张向裕(广东工业大学自动化学院,广东省物联网信息技术重点实验室,广东广州 510006)摘要:本文首先介绍基于SDR(Software Defined Radio,软件定义无线电)实现的LTE开源无线通信系统—OAI(OpenAirInterface的简称),重点分析OAI的软硬件平台以及OAI连接流程,通过OAI UE ↔ OAI eNB + OAI EPC/HSS实验调试与分析,采用FDD-LTE制式,实现了从EPS到eNodeB的S1接口的互连,再通过真实无线环境到UE的上下行通信。

相对于其它仿真实验,可为研究LTE和相关科研教学工作人员提供一个更加符合真实应用场景的实验平台。

关键字:OAI;LTE;SDR;无线通信Research and implementation of the LTE communication platform based on OAIGan Xianhao , Zhang Xiangyu(School of Automation, Guangdong University of Technology, and Guangdong Key Laboratory of IoT InformationProcessing,Guangzhou 510006, Guangdong)Abstract: At first,this paper introduces the OpenAirInterface,which implenments LTE wireless communication system of open-sourcing based on the SDR.It mainly analyzes the hardware and software platform of OAI,and the experiment about OAI UE ↔ OAI eNB + OAI EPC/HSS,which used the mode of FDD-LTE and successfully communicated with each other.It Differents from other kinds of simulation experiments and can be provide a more real wireless environment to the LTE researchers.Key words: OAI;LTE;SDR;Wireless communications1引言伴随着智能手机的普及,各种移动业务的应用,人们对移动数据流量的需求也在不断增长,LTE将在今后一段时间内成为移动网络的主力军。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主要销售的母板有:

RP1-PKG

USRP1是一个完整的RF收发系统,仅仅添加上天线,你就可以在许多知名频段实现双向、高带宽的通信。

该板有许多特性使之可以方便的集成到更复杂的系统中比如数字控制线,以及可分开发送和接收端口的选项等。

主要特征如下:∙30 MHz收发带宽全同步设计支持MIMO

∙所有功能可由软件或FPGA控制

∙接收机和发射机的独立本地振荡器LO

∙小于200微秒锁相环锁定时间,可用于跳频PLL(Phase Lock Loop,锁相环)∙内置收/发开关

∙发射机和接收机使用同一连接器或使用辅助接收机端口

∙16个数字I / O线来控制外部设备比如天线开关等

∙内置的模拟RSSI(Received Signal Strength Indication接收信号强度指示)测量

∙70分贝的AGC范围

∙可调发射功率

∙支持全双工功能(有某些限制)

RP E100

∙ADCs: 12-位 64 MS/s

∙DACs: 14-位 128 MS/s

∙720 MHz OMAP3 (ARM Cortex A8 处理器 & TI C64x+ DSP)

∙针对嵌入式应用的设计。

运行于 Linux 系统上。

∙512MB RAM

∙4GB microSD 插卡

∙100 M 以太网连接

∙可编程抽取率和下变频和可编程内插速率和上变频

∙Motherboard has one RTX daughterboard slot (1 RX + 1 TX connectors) ∙板上 FPGA 处理 - Onboard FPGA processing

∙TCXO 时钟参考

RP2-PKG

USRP2基于USRP的成功经验,以非常低的价格提供更高的性能和更大的灵活性。

更高速度和更高的精度ADC和DAC在允许使用更宽波段的信号,增加了信号的动态范围。

针对DSP应用优化了的大型现场可编程门阵列(FPGA )可以在高采样率下处理复杂波形。

千兆以太网接口,使应用程序可以使用USRP2同时发送或接受50 MHz的射频带宽。

在USRP2中,FPGA出现了诸如数字上变频器和下变频器等高采样率处理器。

较低采样率的操作可在主机电脑上,甚至可以在具有32位RISC微处理器和有很大用户设计自由空间的FPGA上做。

更大的FPGA使得USRP2可以在没有电脑主机的情况下作为一个独立的系统运行。

USRP2的配置和固件被存储在一个SD闪存卡里,无需特别的硬件就可以轻松编程。

多个USRP2系统可以连接在一起形成最多可达8天线MIMO的全相关多天线系统。

主振荡器可以被锁定到一个外部参考,并有一个每秒1个脉冲(1PPS )的输入用于对精确定时有需求的应用。

主要特性如下:

∙两个100 MS/s的14位模数转换器

∙两个400 MS/s的16位数模转换器

∙可编程控制抽样率的数字下变频器

∙可编程控制插值率的数字上变频器

∙千兆以太网接口

∙ 2 Gbps的高速串行接口用于扩展

∙能处理的信号带宽高达100 MHz

∙模块化的架构,可以支持更多的射频子板

∙附属的模拟和数字I/O支持复杂的无线电控制,例如RSSI和AGC

∙多达8天线的全相关多信道系统(支持MIMO)

∙1兆字节的板载高速SRAM

RP N200

∙ADC: 14-位 100 MS/s

∙DAC: 16-位 400 MS/s

∙采样的量化精度为 8 bit 情况下射频带宽(RF bandwidth)为 50 MHz

∙采样的量化精度为 16 bit 情况下射频带宽(RF bandwidth)为 25 MHz

∙千兆级以太网连接

∙MIMO capable - Requires two or more USRP N210 devices as motherboard has one daughterboard slot (1 RX + 1 TX connectors)

∙连接器类型为SMA

∙FPGA: Xilinx Spartan XC3SD1800A

∙参考时钟:能够锁定一个外部 5 或 10 MHz 的参考时钟

RP N210

∙主要特点:

∙ADC: 14-位 100 MS/s

∙DAC: 16-位 400 MS/s

∙采样的量化精度为 8 bit 情况下射频带宽(RF bandwidth)为 50 MHz

∙采样的量化精度为 16 bit 情况下射频带宽(RF bandwidth)为 25 MHz

∙千兆级以太网连接

∙MIMO capable - Requires two or more USRP N210 devices as motherboard has one daughterboard slot (1 RX + 1 TX connectors)

∙连接器类型为SMA

∙FPGA: Xilinx Spartan XC3SD3400A

∙参考时钟:能够锁定一个外部 5 或 10 MHz 的参考时钟

如下是海曼无限销售的发送或者接收的子板,即子板上只有发送或者是只有接收功能,不具有同时发送和接收功能:

1.BasicTX和BasicRX

1 MHz - 250 MHz发射机和接收机

BasicTX和BasicRX用做外部射频前端的中频(IF)接口。

ADC输入和DAC输出直接变压器耦合到SMA连接器(50欧姆阻抗)而不通过混频器、滤波器或者放大器。

SMA:Sub Miniature A 一种常见的天线接口。

BasicTX和BasicRX可以直接访问子板接口上的所有信号(包括16位告诉数字I/O,SPI和I2C总线以及低速ADC和DAC)。

2.LFTX和LFRX

直流-30 MHz发射机和接收机

LFTX和LFRX与BasicTX和BasicRX类似,主要有两个不同之处。

首先,由于LFTX和LFRX使用差分放大器而不是变压器,它们的频率响应可以达到直流。

其次,LFTX和LFRX有30 MHz低通滤波器用于抗锯齿化。

RX

50-860 MHz接收机

TVRX子板是个基于一个电视调谐器模块的完全的甚高频(VHF)和超高频(UHF)接收系统。

只需连接一个天线,你就可以在50-860 MHz范围内的任何地方接收到6 MHz宽的频谱范围。

所有的调谐和自动增益控制(AGC)功能可以通过软件控制。

这种板子不仅仅能用于接收电视,可以实现更多功能。

它的典型噪声系数为8dB。

注:TVRX是唯一不支持MIMO的子板

4.DBSRX

800 MHz- 2.4 GHz接收机

DBSRX是一个从800 MHz到2.4 GHz的完整接收系统,其噪声指数为3-5dB。

DBSRX有一个软件可控的信道滤波器,它可做成窄至1 MHz或宽至60 MHz。

DBSRX 频率范围涵盖了许多知名波段,包括所有GPS和伽利略波段、902-928 MHz ISM 波段、蜂窝和PCS、氢和羟基射电天文学波段、DECT(Digital Enhanced Cordless

Telecommunications, 数字增强型无绳电话通信)等更多波段。

DBSRX支持MIMO,并能通过同轴电缆为有源天线供电。

注:DBSRX不保证覆盖2.4-2.48 GHz 的ISM波段

如下是海曼无限销售的USRP的收发子板,即子板上同时包含了发送和接收功能:

1.WBX0510

频率范围:50 MHz-1 GHz

发射功率:100mW (20dBm)

WBX0510的频率范围覆盖许多知名波段,包括广播电视、公共安全、陆地移动通信、低功耗免许可设备、无线传感器网络、手机,以及五个业余无线电波段。

2.RFX900

频率范围:750-1050 MHz

发射功率:200mW (23dBm)

RFX900装配了一个902-928 MHz的ISM波段滤波器用于过滤强的带外信号(如寻呼机),这个滤波器可以很容易的绕过以便可在整个频率范围内与除了ISM 波段之外的蜂窝、寻呼、motes和双向无线电一起使用。

3.RFX1200

频率范围:1150-1450 MHz

发射功率:200mW(23dBm)

覆盖导航、卫星和业余波段

4.RFX1800

频率范围:1.5-2.1 GHz

发射功率:100mW(20dBm)

覆盖DECT、US-DECT和PCS频段(包括免许可波段)

5.RFX2400

频率范围:2.3-2.9 GHz

发射功率:50mW(17dBm)

RFX2400带有一个ISM波段(2400-2483 MHz)附近的带通滤波器。

该滤波器可被轻易绕过以便覆盖全部频率范围。

6.XCVR2450

频率范围:2.4-2.5 GHz和4.9-5.9 GHz

发射功率:100mW(20dBm)

XCVR2450覆盖2.4 GHzISM波段和整个4.9-5.9 GHz波段,包括公共安全、UNII (Unlicensed National Information Infrastructure,免许可国家信息基础设施)、ISM 和日本无线波段。