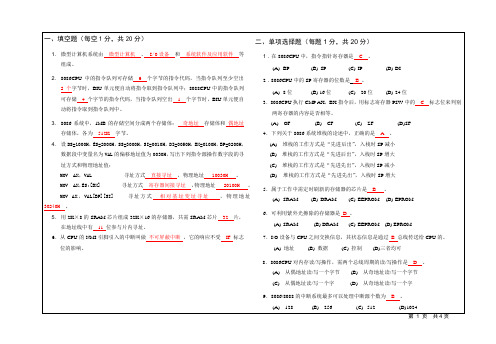

电子科技大学微机原理2012-2013期末A卷及答案

微机原理与应用期终考试卷A答案-201206

A. NMIB.单步中断C.除法错中断D. INTR

2.在数据传送指令中要注意:立即数只能作为(A)。

A.源操作数B.目的操作数

C.源操作数和目的操作数D.源操作数或目的操作数

四、简答题 (每小题5分,共25分)

1.在主存储器设计中,何为存储芯片的位扩展,何为存储芯片的字扩展?它们的作用分别是什么?

MOV AL,4

XLAT

4.编写完整的汇编源程序,实现下面函数的计算。(10分)

六、综合题(10分)

如图所示,设某8088系统用8255A控制步进电机的运行。其原理为:步进电机有A、B、C、D共4相,通过8255A,按A、AB、B、BC、C、CD、D、DA、A依次循环给脉冲,则步进电机按此旋向,依次一个一个步距角地旋转,进而使步进电机转动。

2.8086 CPU从NMI引脚产生的中断,其响应不受IF标志位的影响。

3.CPU与I/O接口间的信息一般包括状态信息、控制信息和数据信息三类

4.指令MOVAH,AL,对源操作数来说是_寄存器方式__寻址方式;指令MOV AX, [BX+60],对源操作数来说是_寄存器相对方式__寻址方式;指令MOV AX,ES:[1600H],对源操作数来说是_直接寻址方式___寻址方式。

(3)、它们不能与CPU直接相连

因为CPU通过总线要和多个外设打交道,而在同一个时刻CPU通常只和一个外设交换信息,就是说,一个外设不能长期和CPU相连,只有被CPU选中的外设,才接收数据总线上的数据或者将外部信息送到数据总线上。

除了上面这些原因外,外设的工作速度通常比CPU的速度低得多,而且各种外设的工作速度互不相同,这就要求接口电路对输入输出过程能起一个缓冲和联络的作用。

电子科技大学微机原理大题(含答案)

电子科技大学微机原理大题(含答案)目录第一章概述 (4)阐述摩尔定律,它有什么限制? (4)什么是Soc?什么是IP核?它有哪几种实现形式? (4)什么是嵌入式系统?它有哪些特点? (4)第二章计算机系统的结构组成与工作原理 (5)说明RISC架构与CISC架构之间的区别 (5)举例说明计算机体系结构、组成和实现之间的关系 (5)试说明现代计算机系统中常用的并行技术及其效果? (5)某时钟频率为1.25GHz、平均CPI为5的非流水线式处理器,其升级版本引入了6级流水线,但因存在诸如锁存延迟等流水线内部延迟,升级版处理器的时钟频率必须降到1GHz。

(5)简述冯.诺依曼体系结构的核心,并分析冯.诺依曼计算机存在的瓶颈? (6)简述冯.诺依曼计算机的实质 (6)第三章微处理器体系结构及关键技术 (6)试比较计算机各体系结构的优缺点 (6)常见的流水线冒险包括哪几种?如何解决? (7)试比较随机逻辑和微码体系结构的优缺点 (7)什么是微码体系结构?微指令的作用是什么? (7)第四章总线技术与总线标准 (7)比较串、并行通信的特点,为什么现代计算机中有总线串行化的趋势? (7)试比较同步、半同步、异步总线时序的优缺点 (8)RAM与CPU的连接有哪几类信号线?简述电路设计时需要考虑的几个问题? (8)计算机系统的总线仲裁有哪几种类型?请简述串行总线仲裁。

(8) 什么是总线?微机中三总线是指?微机系统采用总线的好处是?(8)第五章存储器系统 (9)简述Cache-主存层次与主存-辅存层次的不同点。

(9)什么是高速缓存技术和虚拟存储器技术?采用它们的目的是什么?(9)什么是虚拟地址?试简述虚拟存储器的基本工作原理。

(9)什么是存储器访问的局部性原理?它有哪几种含义? (9)试为某8位计算机系统设计一个具有8KB ROM和40KB RAM的存储器。

要求ROM用EPROM芯片2732组成,从0000H地址开始;RAM用SRAM 芯片6264组成,从4000H地址开始。

2012-2013-2《数字逻辑设计及应用》期末考试题-A参考解答

电子科技大学2012 -2013学年第二学期期末考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期:20 13 年07 月05 日考试时长:_120___分钟课程成绩构成:平时30 %,期中30 %,实验0 %,期末40 %本试卷试题由___七__部分构成,共__7___页。

I. Fill out your answers in the blanks (3’ X 10=30’)1. If a 74x138 binary decoder has 110 on its inputs CBA, the active LOW output Y5 should be ( 1 or high ).2. If the next state of the unused states are marked as “don’t-cares” when designing a finite state machine, this approach is called minimal ( cost ) approach.3.The RCO_L of 4-bit counter 74x169 is ( 0 or low ) when counting to 0000 in decreasing order.4. To design a "001010" serial sequence generator by shift registers, the shift register should need ( 4 ) bit at least.5. One state transition equation is Q*=JQ’+K’Q. If we use T flip-flop with enable to complete the equation,the enable input of T flip-flop should have the function EN=( JQ’+KQ ).6. A 4-bit Binary counter can have ( 16 ) normal states at most, 4-bit Johnson counter with no self-correction can have ( 8 ) normal states, 4-bit linear feedback shift-register (LFSR) counter with self-correction can have ( 16 ) normal states.7. If we use a ROM, whose capacity is 16 × 4 bits, to construct a 4-bit binary code to gray code converter, when the address inputs are 1001, ( 1101 ) will be the output.8. When the input is 10000000 of an 8 bit DAC, the corresponding output voltage is 2V. The output voltage is ( 3.98 ) V when the input is 11111111.II. Please select the only one correct answer in the following questions.(2’ X 5=10’)1. If a 74x85 magnitude comparator has ALTBIN=1, AGTBIN=0, AEQBIN=0, A3A2A1A0=1101, B3B2B1B0=0111 on its inputs, the outputs are ( D ).A) ALTBOUT=0, AEQBOUT=0, AGTBOUT=0 B) ALTBOUT=1, AEQBOUT=0, AGTBOUT=0C) ALTBOUT=1, AEQBOUT=0, AGTBOUT=1 D) ALTBOUT=0, AEQBOUT=0, AGTBOUT=12. As shown in Figure 1, what would the outputs of the 4-bit adder 74x283 be ( B ) when A3A2A1A0=0100, B3B2B1B0=1110 and S/A=1.A) C4=1, S3S2S1S0=0010 B) C4=0, S3S2S1S0=0110 C) C4=0, S3S2S1S0=1010D) C4=0, S3S2S1S0=1110Figure 13. Which of the following statements is INCORRECT? ( A )A) A D latch is edge triggered and it will follow the input as long as the control input C is activelow.B) A D flip flop is edge triggered and its output will not change until the edge of the controllingCLK signal.C) An S-R latch may go into metastable state if both S and R are changing from 11 to 00simultaneously.D) The pulse applying to any input of an S -R latch must meet the minimum pulse width requirement.4. The capacity of a memory that has 13 bits address bus and can store 8 bits at each address is ( B ).A) 8192 B) 65536 C) 104 D) 2565. Which state in Figure 2 is NOT ambiguous ( C ).A) A B) B C) C and D D) CABCD WX W+Y ZZ ’X ’+YYZ1X ’Z ’Figure 2III. Analyze the sequential-circuit as shown in Figure 3, D Flip-Flop with asynchronous presetand clear inputs. [15’]1.Write out the excitation equations, transition equations and output equation. [5’]2.Assume the initial state Q 2Q 1=00, complete the timing diagram for Q 2 ,Q 1 and Z. [10’]Figure 3参考答案:激励方程: D 1=Q 2/,D 2= Q 1转移方程:Q 1 *= D 1=Q 2/,Q 2 *=D 2= Q 1 输出方程:Z= (CLK+Q 2)/参考评分标准:1. 5个方程正确得5分;每错一个扣1分,扣完5分为止;2. Q 1、Q 2、Z 的波形边沿判断正确,得3分,错一个,扣1分,扣完3分为止;每个上升沿和下降沿各0.5分,错1处扣0.5分,扣完7分为止。

电子科技大学微机原理大题(含答案)

目录第一章概述 (4)阐述摩尔定律,它有什么限制? (4)什么是Soc?什么是IP核?它有哪几种实现形式? (4)什么是嵌入式系统?它有哪些特点? (4)第二章计算机系统的结构组成与工作原理 (5)说明RISC架构与CISC架构之间的区别 (5)举例说明计算机体系结构、组成和实现之间的关系 (5)试说明现代计算机系统中常用的并行技术及其效果? (5)某时钟频率为1.25GHz、平均CPI为5的非流水线式处理器,其升级版本引入了6级流水线,但因存在诸如锁存延迟等流水线内部延迟,升级版处理器的时钟频率必须降到1GHz。

(5)简述冯.诺依曼体系结构的核心,并分析冯.诺依曼计算机存在的瓶颈? (6)简述冯.诺依曼计算机的实质 (6)第三章微处理器体系结构及关键技术 (6)试比较计算机各体系结构的优缺点 (6)常见的流水线冒险包括哪几种?如何解决? (7)试比较随机逻辑和微码体系结构的优缺点 (7)什么是微码体系结构?微指令的作用是什么? (7)第四章总线技术与总线标准 (7)比较串、并行通信的特点,为什么现代计算机中有总线串行化的趋势? (7)试比较同步、半同步、异步总线时序的优缺点 (8)RAM与CPU的连接有哪几类信号线?简述电路设计时需要考虑的几个问题? (8)计算机系统的总线仲裁有哪几种类型?请简述串行总线仲裁。

(8)什么是总线?微机中三总线是指?微机系统采用总线的好处是? (8)第五章存储器系统 (9)简述Cache-主存层次与主存-辅存层次的不同点。

(9)什么是高速缓存技术和虚拟存储器技术?采用它们的目的是什么? (9)什么是虚拟地址?试简述虚拟存储器的基本工作原理。

(9)什么是存储器访问的局部性原理?它有哪几种含义? (9)试为某8位计算机系统设计一个具有8KB ROM和40KB RAM的存储器。

要求ROM用EPROM芯片2732组成,从0000H地址开始;RAM用SRAM芯片6264组成,从4000H地址开始。

2012年微型计算机原理与接口技术试题A卷-答案

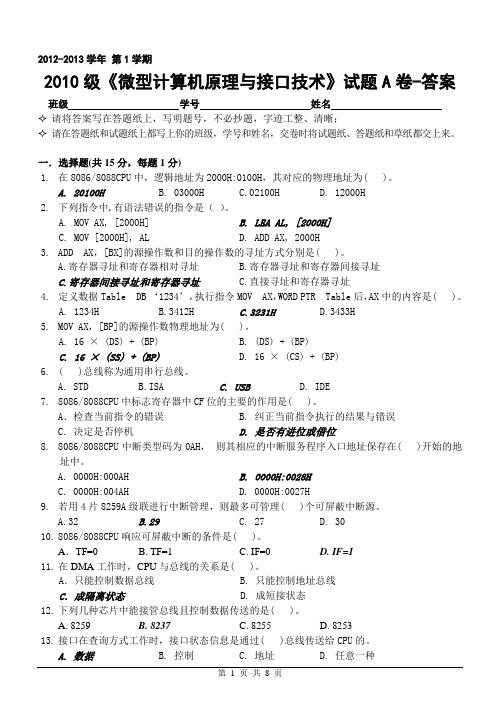

2012-2013学年第1学期2010级《微型计算机原理与接口技术》试题A卷-答案班级学号姓名✧请将答案写在答题纸上,写明题号,不必抄题,字迹工整、清晰;✧请在答题纸和试题纸上都写上你的班级,学号和姓名,交卷时将试题纸、答题纸和草纸都交上来。

一.选择题(共15分,每题1分)1.在8086/8088CPU中,逻辑地址为2000H:0100H,其对应的物理地址为( )。

A. 20100HB. 03000HC.02100HD. 12000H2.下列指令中,有语法错误的指令是()。

A. MOV AX, [2000H]B. LEA AL, [2000H]C. MOV [2000H], ALD. ADD AX, 2000H3.ADD AX,[BX]的源操作数和目的操作数的寻址方式分别是( )。

A.寄存器寻址和寄存器相对寻址B.寄存器寻址和寄存器间接寻址C.寄存器间接寻址和寄存器寻址 C.直接寻址和寄存器寻址4.定义数据Table DB ‘1234’,执行指令MOV AX,WORD PTR Table后,AX中的内容是( )。

A. 1234HB.3412HC.3231HD.3433H5.MOV AX,[BP]的源操作数物理地址为( )。

A. 16 × (DS) + (BP)B. (DS) + (BP)C. 16 × (SS) + (BP)D. 16 × (CS) + (BP)6.( )总线称为通用串行总线。

A. STDB.ISAC. USBD. IDE7.8086/8088CPU中标志寄存器中CF位的主要的作用是( )。

A.检查当前指令的错误 B. 纠正当前指令执行的结果与错误C. 决定是否停机D. 是否有进位或借位8.8086/8088CPU中断类型码为0AH,则其相应的中断服务程序入口地址保存在( )开始的地址中。

A. 0000H:000AHB. 0000H:0028HC. 0000H:004AHD. 0000H:0027H9.若用4片8259A级联进行中断管理,则最多可管理( )个可屏蔽中断源。

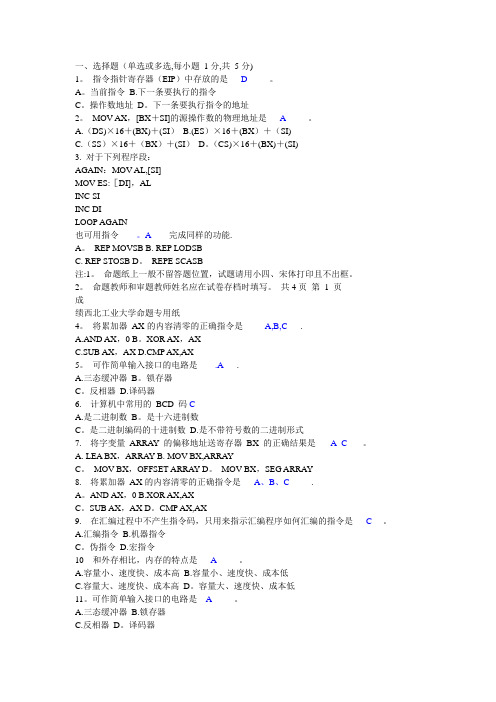

微机原理期末试题及答案

一、选择题(单选或多选,每小题1分,共5分)1。

指令指针寄存器(EIP)中存放的是___D_____。

A。

当前指令B.下一条要执行的指令C。

操作数地址D。

下一条要执行指令的地址2。

MOV AX,[BX+SI]的源操作数的物理地址是___A_____。

A.(DS)×16+(BX)+(SI)B.(ES)×16+(BX)+(SI)C.(SS)×16+(BX)+(SI)D。

(CS)×16+(BX)+(SI)3. 对于下列程序段:AGAIN:MOV AL,[SI]MOV ES:[DI],ALINC SIINC DILOOP AGAIN也可用指令____。

A____完成同样的功能.A。

REP MOVSB B. REP LODSBC. REP STOSB D。

REPE SCASB注:1。

命题纸上一般不留答题位置,试题请用小四、宋体打印且不出框。

2。

命题教师和审题教师姓名应在试卷存档时填写。

共4页第1 页成绩西北工业大学命题专用纸4。

将累加器AX的内容清零的正确指令是_____A,B,C___.A.AND AX,0 B。

XOR AX,AXC.SUB AX,AXD.CMP AX,AX5。

可作简单输入接口的电路是____.A___.A.三态缓冲器B。

锁存器C。

反相器D.译码器6. 计算机中常用的BCD 码CA.是二进制数B。

是十六进制数C。

是二进制编码的十进制数D.是不带符号数的二进制形式7. 将字变量ARRAY 的偏移地址送寄存器BX 的正确结果是___ A_C ___。

A. LEA BX,ARRAYB. MOV BX,ARRAYC。

MOV BX,OFFSET ARRAY D。

MOV BX,SEG ARRAY8. 将累加器AX的内容清零的正确指令是___A、B、C_____.A。

AND AX,0 B.XOR AX,AXC。

SUB AX,AX D。

CMP AX,AX9. 在汇编过程中不产生指令码,只用来指示汇编程序如何汇编的指令是___C __。

微机原理试卷(有答案)

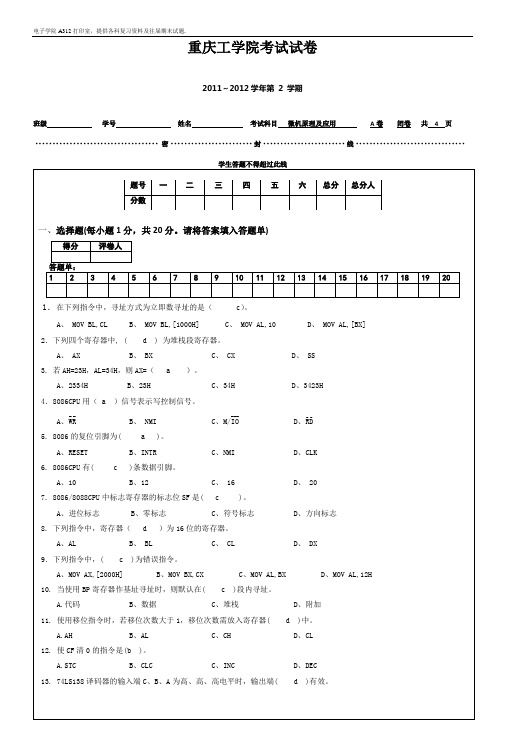

重庆工学院考试试卷2011~2012学年第2 学期班级学号姓名考试科目微机原理及应用A卷闭卷共 4 页····································密························封························线································学生答题不得超过此线A. Y2___B、Y3___C、Y4___D、Y7___重庆工学院考试试卷2011~2012学年第2 学期班级学号姓名考试科目微机原理与接口技术A卷闭卷共 4 页····································密························封························线································学生答题不得超过此线重庆工学院考试试卷2011~2012学年第2 学期班级学号姓名考试科目微机原理与接口技术A卷闭卷共 4 页····································密························封························线································学生答题不得超过此线MOV BL,80HADD AL,BLJC L1JMP L2...上述程序段运行后,AL=__ ,BL=__ ,程序转向处执行。

电子科技大学微机原理2012-2013期末A卷及答案

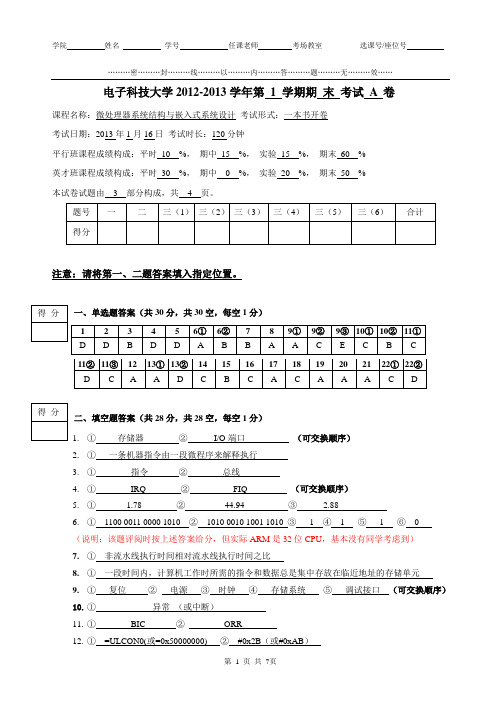

………密………封………线………以………内………答………题………无………效……电子科技大学2012-2013学年第 1 学期期 末 考试 A 卷课程名称:微处理器系统结构与嵌入式系统设计 考试形式:一本书开卷 考试日期:2013年1月16日 考试时长:120分钟平行班课程成绩构成:平时 10 %, 期中 15 %, 实验 15 %, 期末 60 % 英才班课程成绩构成:平时 30 %, 期中 0 %, 实验 20 %, 期末 50 % 本试卷试题由 3 部分构成,共 4 页。

注意:请将第一、二题答案填入指定位置。

一、单选题答案(共30分,共30空,每空1分)二、填空题答案(共28分,共28空,每空1分)1. ① 存储器 ② I/O 端口 (可交换顺序)2. ① 一条机器指令由一段微程序来解释执行3. ① 指令 ② 总线4. ① IRQ ② FIQ (可交换顺序)5. ① 1.78 ② 44.94 ③ 2.886. ① 1100 0011 0000 1010 ② 1010 0010 1001 1010 ③ 1 ④ 1 ⑤ 1 ⑥ 0 (说明:该题评阅时按上述答案给分,但实际ARM 是32位CPU ,基本没有同学考虑到)7. ① 非流水线执行时间相对流水线执行时间之比8. ① 一段时间内,计算机工作时所需的指令和数据总是集中存放在临近地址的存储单元 9. ① 复位 ② 电源 ③ 时钟 ④ 存储系统 ⑤ 调试接口 (可交换顺序) 10. ① 异常 (或中断) 11. ① BIC ② ORR12. ① =ULCON0(或=0x50000000) ② #0x2B (或#0xAB )………密………封………线………以………内………答………题………无………效……一、单选题(共30分,共30空,每空1分)1.以下常用总线标准中,不属于片内总线的是()。

A、Core ConnectB、AMBAC、AvalonD、SATA2.计算机系统中,以下不属于“异常”的是()。

微机原理-期末考试题库及答案(含3套试卷)

微机原理-期末考试题库及答案(含3套试卷)[BX]C. MOV AX, CXD. MOV AX, [CX]5.中断指令INT 17H的中断服务程序的入口地址放在中断向量表地址()开始的4个存贮单元内。

A. 00017HB. 00068HC. 0005CHD. 0005EH6.条件转移指令JNE的条件是()。

A. CF=0B. CF=1C. ZF=0D. ZF=17. 在8086/8088 CPU中,一个最基本的总线读写周期由( 1 )时钟周期(T状态)组成,在T1状态,CPU往总线上发( 2 )信息。

⑴ A. 1个 B. 2个 C. 4个 D. 6个⑵ A. 数据 B . 地址 C. 状态 D. 其它8. 8086有两种工作模式, 最小模式的特点是( 1 ),最大模式的特点是( 2 )。

⑴ A. CPU提供全部控制信号 B. 由编程进行模式设定C. 不需要8286收发器D. 需要总线控制器8288⑵ A. M/ 引脚可直接引用 B. 由编程进行模式设定C. 需要总线控制器8288D. 适用于单一处理机系统9.在8086微机系统的RAM 存储单元器0000H:002CH开始依次存放23H,0FFH,00H,和0F0H四个字节,该向量对应的中断号是( )。

A. 0AHB. 0BHC. 0CHD. 0DH10.真值超出机器数表示范围称为溢出,,此时标志寄存器中的( )位被置位A. OF B AF C PF D CF11.8086 系统中内存储器地址空间为1M,而在进行I/O读写是,有效的地址线是( )A . 高16位 B. 低16位 C. 高8位 D. 低8位12.8086 CPU中段寄存器用来存放( )A. 存储器的物理地址B. 存储器的逻辑地址C. 存储器的段基值D. 存储器的起始地址13.8259A可编程中断控制器的中断服务寄存器ISR用于( )A.记忆正在处理中的中断B. 存放从外设来的中断请求信号C.允许向CPU发中断请求D.禁止向CPU发中断请求14.8253 可编程定时/计数器的计数范围是( )A. 0-255B. 1-256C. 0-65535D. 1-6553615. 在8086中,(BX)=8282H,且题中指令已在队列中,则执行INC [BX]指令需要的总线周期数为( )A.0 B.1 C.2 D.316. 8086中,( ) 组寄存器都可以用来实现对存储器的寻址。

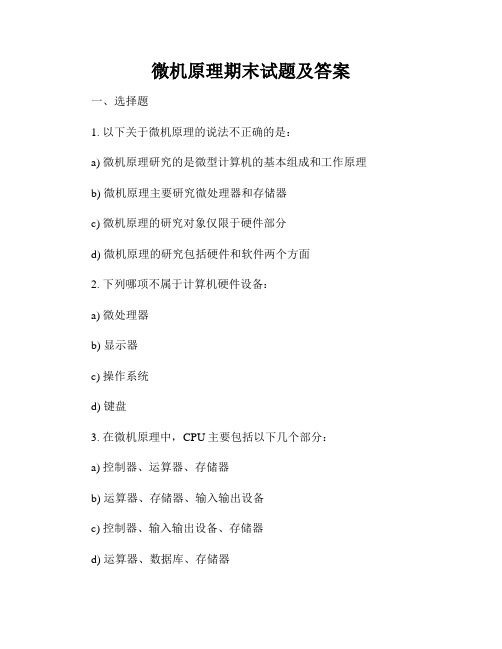

微机原理期末试题及答案

微机原理期末试题及答案一、选择题1. 以下关于微机原理的说法不正确的是:a) 微机原理研究的是微型计算机的基本组成和工作原理b) 微机原理主要研究微处理器和存储器c) 微机原理的研究对象仅限于硬件部分d) 微机原理的研究包括硬件和软件两个方面2. 下列哪项不属于计算机硬件设备:a) 微处理器b) 显示器c) 操作系统d) 键盘3. 在微机原理中,CPU主要包括以下几个部分:a) 控制器、运算器、存储器b) 运算器、存储器、输入输出设备c) 控制器、输入输出设备、存储器d) 运算器、数据库、存储器4. 下列哪个不是计算机的内存类型:a) RAMb) ROMc) HDDd) CACHE5. 在微机原理中,数据总线用于传输:a) 数据b) 控制信号c) 地址d) 所有的信号二、简答题(每题20分)1. 解释什么是指令周期、机器周期和时钟周期。

答:指令周期是执行一条机器指令所需要的时间,它包括取指令周期(fetch)、译码周期(decode)、执行周期(execute)和存取周期(memory)等。

机器周期是指执行一条基本操作所需要的时间,例如加法、乘法等。

时钟周期是指时钟发生一次跳变所需要的时间,它是微机系统运行的基本单位。

2. 什么是中断请求?答:中断请求是指外部设备通过向CPU提出请求,使CPU中断当前正在执行的程序,并转去执行相应的中断处理程序。

中断请求可以分为内部中断和外部中断两种。

3. 简述冯·诺依曼结构的原理。

答:冯·诺依曼结构是计算机系统的基本组织原理,主要包括存储器、运算器、控制器和输入输出设备四部分。

它的原理是将程序和数据存储在同一存储器中,由程序计数器指示当前指令的地址,按照指令的顺序执行程序。

运算器负责执行算术运算和逻辑运算,控制器负责解码指令并控制各个部件的工作。

输入输出设备负责与外部设备进行数据交互。

4. 什么是总线?答:总线是计算机中各个部件之间传输数据和控制信号的公共通道。

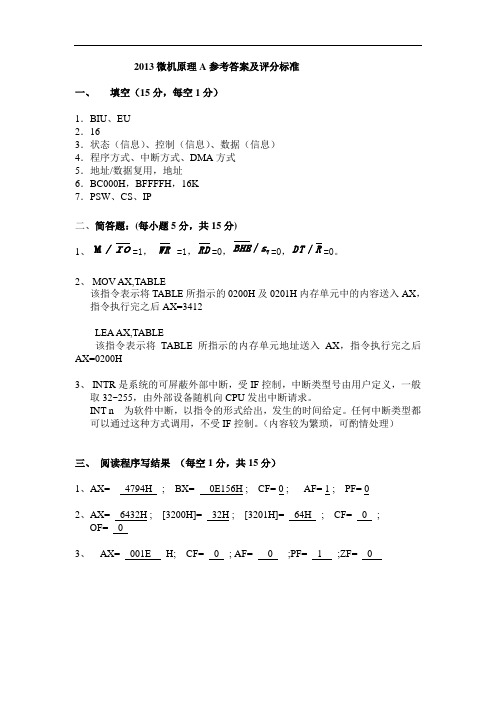

2013试题A答案

2013微机原理A 参考答案及评分标准一、 填空(15分,每空1分)1.BIU 、EU2.163.状态(信息)、控制(信息)、数据(信息)4.程序方式、中断方式、DMA 方式5.地址/数据复用,地址6.BC000H ,BFFFFH ,16K7.PSW 、CS 、IP二、简答题:(每小题5分,共15分)1、 IO /M =1, WR =1,RD =0,7/s BHE =0,R DT /=0。

2、 MOV AX,TABLE该指令表示将TABLE 所指示的0200H 及0201H 内存单元中的内容送入AX ,指令执行完之后AX=3412LEA AX,TABLE该指令表示将TABLE 所指示的内存单元地址送入AX ,指令执行完之后AX=0200H3、 INTR 是系统的可屏蔽外部中断,受IF 控制,中断类型号由用户定义,一般取32~255,由外部设备随机向CPU 发出中断请求。

INT n 为软件中断,以指令的形式给出,发生的时间给定。

任何中断类型都可以通过这种方式调用,不受IF 控制。

(内容较为繁琐,可酌情处理)三、 阅读程序写结果 (每空1分,共15分)1、AX= 4794H ; BX= 0E156H ; CF= 0 ; AF= 1 ; PF= 02、AX= 6432H ; [3200H]= 32H ; [3201H]= 64H ; CF= 0 ; OF= 03、 AX= 001E H; CF= 0 ; AF= 0 ;PF= 1 ;ZF= 0四、程序改错(每改对一处错误得2分)MOV BX, 2000HMOV AL, [BX]MOV CX, 99P1: INC BXCMP AL, [BX]JGE P2MOV AL, [BX]P2: LOOP P1MOV BX, 2100HMOV [BX], ALHLT五、程序设计1、编写程序,从16号端口输入1个数与预定值相比,将差的绝对值从18号端口输出。

参考答案DATA SEGMENTY DB 50H;设任意预定值DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATAGO:MOV AX,DATAMOV DS,AXMOV BL,YIN AL,10HCMP AL,BLJG L1XCHG AL,BLL1:SUB AL,BLOUT 12H,ALCODE ENDSEND GO评分细则程序结构2分,段定义2分,输入2分,输出2分,求绝对值2分2、编写子程序。

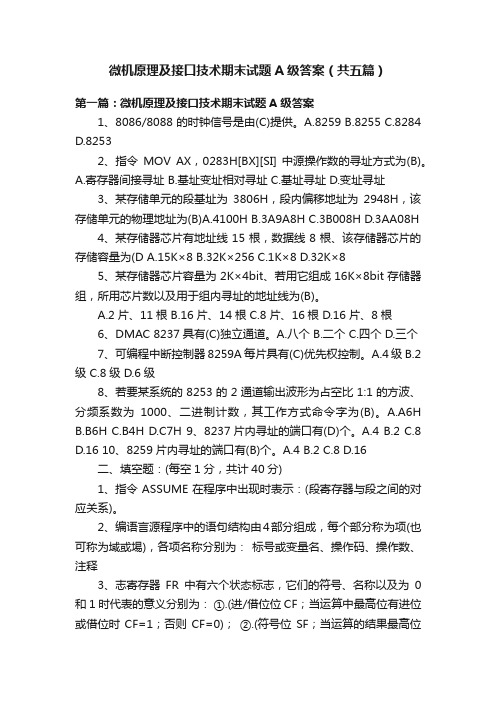

微机原理及接口技术期末试题A级答案(共五篇)

微机原理及接口技术期末试题A级答案(共五篇)第一篇:微机原理及接口技术期末试题A级答案1、8086/8088 的时钟信号是由(C)提供。

A.8259 B.8255 C.8284D.82532、指令MOV AX,0283H[BX][SI] 中源操作数的寻址方式为(B)。

A.寄存器间接寻址B.基址变址相对寻址C.基址寻址D.变址寻址3、某存储单元的段基址为3806H,段内偏移地址为2948H,该存储单元的物理地址为(B)A.4100H B.3A9A8H C.3B008H D.3AA08H4、某存储器芯片有地址线15根,数据线8根、该存储器芯片的存储容量为(D A.15K×8 B.32K×256 C.1K×8 D.32K×85、某存储器芯片容量为2K×4bit、若用它组成16K×8bit存储器组,所用芯片数以及用于组内寻址的地址线为(B)。

A.2片、11根B.16片、14根C.8片、16根D.16片、8根6、DMAC 8237具有(C)独立通道。

A.八个 B.二个 C.四个 D.三个7、可编程中断控制器8259A每片具有(C)优先权控制。

A.4级 B.2级 C.8级 D.6级8、若要某系统的8253的2通道输出波形为占空比1:1的方波、分频系数为1000、二进制计数,其工作方式命令字为(B)。

A.A6H B.B6H C.B4H D.C7H 9、8237片内寻址的端口有(D)个。

A.4 B.2 C.8D.16 10、8259片内寻址的端口有(B)个。

A.4 B.2 C.8 D.16二、填空题:(每空1分,共计40分)1、指令ASSUME在程序中出现时表示:(段寄存器与段之间的对应关系)。

2、编语言源程序中的语句结构由4部分组成,每个部分称为项(也可称为域或埸),各项名称分别为:标号或变量名、操作码、操作数、注释3、志寄存器FR中有六个状态标志,它们的符号、名称以及为0和1时代表的意义分别为:①.(进/借位位CF;当运算中最高位有进位或借位时CF=1;否则CF=0);②.(符号位SF;当运算的结果最高位为1即结果为负数时SF=1;否则SF=0)③.(奇偶位PF;当运算的结果中低8位中含1的个数为偶数时PF=1;否PF=0 ④.(全零位ZF;当运算的结果为零时ZF=1;否则ZF=0);⑤.(溢出位OF;当带符号数运算的结果有溢出时OF=1;否则OF=0);⑥.(半进/借位位AF;当运算的结果D3向D4有进位或借位时AF=1;否则AF=0);4、微机主机与输入/输出设备之间的数据传送方式有以下四种方式:(无条件传送)、(查询式传送)、(中断传送)、(DMA传送)、5、执行下面的程序段后,AX=(35)MOV CX,5 MOV AX,50 NEXT:SUB AX,CX LOOP NEXT HLT6、执行下面的程序段后,AL=(34H),BUF DW 2152H,3416H,5731H,4684HMOV BX,OFFSET BUF MOV AL,3 XLAT7、标志寄存器FR中有三个控制标志,它们的符号、名称以及为0和1时代表的意义分别为:①.(中断控制IF;允许即开中断时IF=1;否则IF=0);②.(方向控制DF;在串操作指令时需变址寄存器SI,DI按递减方式工作即-1/2时DF=1;否则DF=0);③.(单步操作控制TF;需单步工作时TF=1;否则TF=0);8、8086/8088 CPU具有两种外部中断,它们是(非屏蔽中断即NMI)和(可屏蔽中断即INTR)。

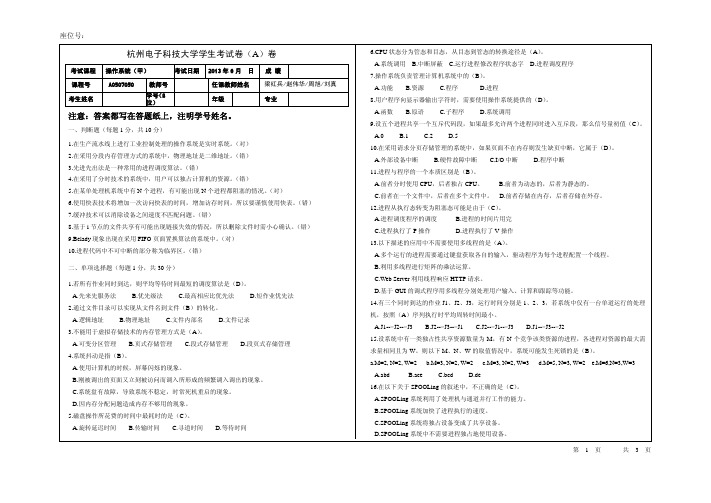

2012-2013-2 OS试卷A(带答案)

第2页

共3页

座位号:

P3 0020 P4 0642 b)P0->P2/P3->*,所以安全。 c)安全,可以分配。

2.(8 分)某磁盘大小为 1MB,磁盘上的磁盘块大小为 1KB,从 0 开始编号。某文件顺序存储在 4

个磁盘块上:20,500,10 和 900,且该文件的目录项位于 51 号块上,已知最后一次磁盘访问的是

23.下面关于 i 节点描述错误的是(A)。

A.i 节点和文件的目录项是一一对应的。

B.i 节点能描述文件占用的块数。

C.i 节点描述了文件大小和指向数据块的指针。

D.通过 i 节点实现文件的逻辑结构和物理结构的转换。 24.位示图法用于(D)。

A.文件目录的查找 B.主存空间的管理 C.文件的共享与保护

Maximum Need ABCD 0012 1750 2356 0652 0656

Available

ABCD 1520

a) What is the content of the matric "Need"?

b) Is the system in safe state? Prove it!

c) If a request from process P1 arrives for (0,4,2,0), can the request be immediately granted?

A.前者分时使用 CPU,后者独占 CPU。

B.前者为动态的,后者为静态的。

C.前者在一个文件中,后者在多个文件中。 D.前者存储在内存,后者存储在外存。

12.进程从执行态转变为阻塞态可能是由于(C)。

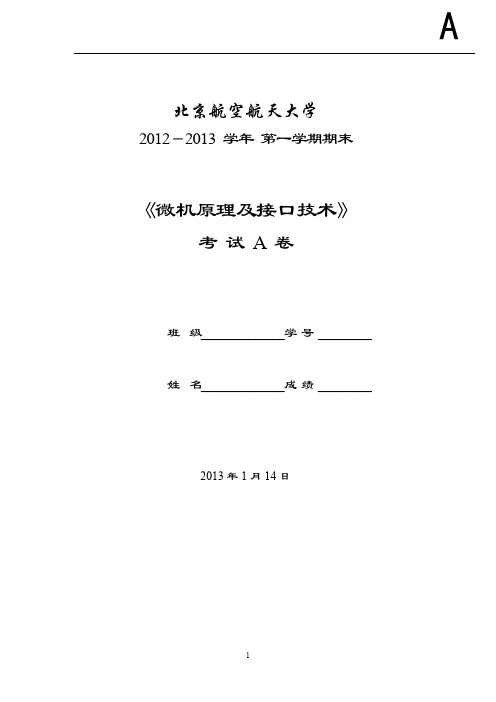

微原2012期末试题A

北京航空航天大学2012-2013 学年第一学期期末《微机原理及接口技术》考试A 卷班级______________学号_________姓名______________成绩_________2013年1月14日班号学号姓名成绩《微机原理及接口技术》期末考试卷注意事项:本试题共5题,7页,考试时间共120分钟。

一、填空题…………………………………………………………………( 30 分) 1.设AL=0C0H,BL=60H,若AL、BL中为有符号数,则对应的十进制数分别为和;执行ADD AL,BL后,目的操作数的内容为,标志寄存器中CF= ,OF= 。

2.设DS=2000H,SS=2100H,SI=11H,AL=50H,8086 CPU在执行指令ADD AL,[11H]时,引脚M/IO= ,BHE= ,RD= ,WR= 。

AD0在T1时钟周期为电平、在T2时钟周期为,地址锁存器8282输出的地址总线上信号为H,存储器中的数据通过数据总线的(高、低)八位传送到AL。

此指令中源操作数的寻址方式为。

指令的加法运算功能是由8086 CPU的部件完成的,源操作数物理地址的计算是由BIU中的实现的。

3.若在存储器2300H:100H地址中存放一条2字节的无条件短转移指令,机器码为EBH、CEH,则转移的目标逻辑地址为。

4.CPU 经过8255A与外设进行数据传送的方式可以有,和中断方式。

5.设8259A工作于完全嵌套方式,其中断服务寄存器ISR=01000010B,则引脚对应的中断服务被打断进入中断嵌套。

此时,产生了NMI、IR3、IR0中断请求,则8086首先响应的中断是,其次响应中断。

响应可屏蔽中断时需要8086输出个总线周期电平的中断响应信号,在第个总线周期从数据总线读取中断类型号。

6.RS-232-C采用全双工方式传送数据时,最少需要条信号线,其中引脚发送数据。

异步串行通讯以为单位传输,一帧数据格式必须包括,和停止位。

《微机原理》期末考试A卷(有答案)

1.试题可采用粘贴方式,请用B5纸打印,粘贴时不要超过边框。

2.本科课程的试题一般不留答题空间,答案写在专用答题纸上,专科课程试题一般要留答题空间,答案直接做在试卷上。

年级 专业班级姓名 学号 考试时间 年 月 日 午订装线2009 ——2010 学年 第 1 学期课程名称: 微机原理及应用 考试形式:( 闭 )考核方式:(考试)题号 一 二三四五总分得分评阅人签 名一、单项选择题(每题 1分,共 15 分)1.若用户数据位于存储区10000H ~1FFFFH ,则该数据的段地址为__C____。

(A) 0100H (B) 1FFFH (C) 1000H (D) 0FFFH 2.8086 CPU 在响应中断时顺序将_____C_____内容压入堆栈。

(A) CS.IP.PSW (B) IP.CS.PSW(C) PSW.CS.IP (D) PSW.IP.CS3.设(10FF0H)=10H ,(10FFlH)=20H ,(10FF2H)=30H ,则从物理地址10FF1H 中取出一个字的内容是 B 。

(A) 1020H (B) 3020H (C) 2030H (D) 2010H4.连续启动两次独立的存储器操作之间的最小间隔叫____D______。

(A) 存取时间 (B) 读周期 (C) 写周期 (D) 存取周期考场座号试卷类型 A 卷得 分命题教师签名: 汤定德 系主任签名: 徐根耀 日 期 2009.12.183.试编写由8位某型号数模转换器产生锯齿波模拟信号的一段程序,设地址51CH 为计算机中译码器的输出,且该输出信号使数模转换器的CS 为低电平。

(10分)CODE SEGMENTASSUME CS:CODE (2分) START:MOV CX,256 MOV AL,0MOV DX,51CH (2分)LOOP1:OUT DX,AL CALL DELAY INC AL LOOP LOOP1 JMP STARTCODE ENDS (5分) END START (1分)五、计算题(第1题5分、第2题10分,共15分)1.10010110 11010101(5分)解:根据“相异则或”的原则(2分),可得结果为01000011.(3分)2.00011001-00100000(要求有较详细的运算步骤)(10分)解:(5分) 而11111001即为-7的补码(2分),故差应为10000111(3分).得 分 订装线。

微机原理期末考试试卷(包含答案)

一、填空题(每空1分,共20分)1. 微型计算机系统由微型计算机、 I/O设备和系统软件及应用软件等组成。

2. 8086CPU中的指令队列可存储 6 个字节的指令代码,当指令队列至少空出2 个字节时,BIU单元便自动将指令取到指令队列中;8088CPU中的指令队列可存储 4 个字节的指令代码,当指令队列空出 1 个字节时,BIU单元便自动将指令取到指令队列中。

3. 8086系统中,1MB的存储空间分成两个存储体:奇地址存储体和偶地址存储体,各为512K 字节。

4. 设DS=1000H,ES=2000H,SS=3000H,SI=0010H,DI=0050H,BX=0100H,BP=0200H,数据段中变量名为VAL的偏移地址值为0030H,写出下列指令源操作数字段的寻址方式和物理地址值:MOV AX,VAL 寻址方式直接寻址,物理地址 10030H 。

MOV AX,ES:[BX] 寻址方式寄存器间接寻址,物理地址 20100H 。

MOV AX,VAL[BP][SI] 寻址方式相对基址变址寻址,物理地址30240H 。

5. 用2K×8的SRAM芯片组成32K×16的存储器,共需SRAM芯片32 片,在地址线中有11 位参与片内寻址。

6.从CPU的NMI引脚引入的中断叫做不可屏蔽中断,它的响应不受IF 标志位的影响。

二、单项选择题(每题1分,共20分)1.在8086CPU中,指令指针寄存器是 C 。

(A) BP (B) SP (C) IP (D) DI2.8086CPU中的SP寄存器的位数是 B 。

(A) 8位(B) 16位(C) 20位(D) 24位3.8086CPU执行CMP AX,BX指令后,用标志寄存器PSW中的 C 标志位来判别两寄存器的内容是否相等。

(A) OF (B) CF (C) ZF (D)SF4.下列关于8086系统堆栈的论述中,正确的是 A 。

(A) 堆栈的工作方式是“先进后出”,入栈时SP减小(B) 堆栈的工作方式是“先进后出”,入栈时SP增大(C) 堆栈的工作方式是“先进先出”,入栈时SP减小(D) 堆栈的工作方式是“先进先出”,入栈时SP增大5.属于工作中需定时刷新的存储器的芯片是 B 。

微机原理-期末考试题库及答案(含3套试卷)

微机原理-期末考试题库及答案(含3套试卷)微型计算机原理与接口技术综合测试题一一、单项选择题(下面题只有一个答案是正确的,选择正确答案填入空白处)1.8086CPU通过(1 )控制线来区分是存储器访问,还是I/O访问,当CPU执行IN AL,DX 指令时,该信号线为( 2 )电平。

(1) A. M/ B. C. ALE D. N/ (2) A. 高 B. 低 C. ECL D. CMOS2.n+1位有符号数x的补码表示范围为()。

A. -2n < x < 2nB. -2n ≤ x ≤ 2n -1C. -2n -1 ≤ x ≤ 2n-1D. -2n < x ≤ 2n3.若要使寄存器AL中的高4位不变,低4位为0,所用指令为()。

A. AND AL, 0FHB. AND AL, 0FOHC. OR AL, 0FHD. OR AL 0FOH4.下列MOV指令中,不正确的指令是()。

A. MOV AX, BXB. MOV AX,[BX]C. MOV AX, CXD. MOV AX, [CX]5.中断指令INT 17H的中断服务程序的入口地址放在中断向量表地址()开始的4个存贮单元内。

A. 00017HB. 00068HC. 0005CHD. 0005EH6.条件转移指令JNE的条件是()。

A. CF=0B. CF=1C. ZF=0D. ZF=17. 在8086/8088 CPU中,一个最基本的总线读写周期由( 1 )时钟周期(T状态)组成,在T1状态,CPU往总线上发( 2 )信息。

⑴ A. 1个 B. 2个 C. 4个 D. 6个⑵ A. 数据 B . 地址 C. 状态 D. 其它8. 8086有两种工作模式, 最小模式的特点是( 1 ),最大模式的特点是( 2 )。

⑴ A. CPU提供全部控制信号 B. 由编程进行模式设定C. 不需要8286收发器D. 需要总线控制器8288⑵ A. M/ 引脚可直接引用 B. 由编程进行模式设定C. 需要总线控制器8288D. 适用于单一处理机系统9.在8086微机系统的RAM 存储单元器0000H:002CH开始依次存放23H,0FFH,00H,和0F0H四个字节,该向量对应的中断号是( )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技大学2012-2013学年第 1 学期期 末 考试 A 卷课程名称:微处理器系统结构与嵌入式系统设计 考试形式:一本书开卷 考试日期:2013年1月16日 考试时长:120分钟平行班课程成绩构成:平时 10 %, 期中 15 %, 实验 15 %, 期末 60 % 英才班课程成绩构成:平时 30 %, 期中 0 %, 实验 20 %, 期末 50 % 本试卷试题由 3 部分构成,共 4 页。

注意:请将第一、二题答案填入指定位置。

一、单选题答案(共30分,共30空,每空1分)二、填空题答案(共28分,共28空,每空1分)1. ① 存储器 ② I/O 端口 (可交换顺序)2. ① 一条机器指令由一段微程序来解释执行3. ① 指令 ② 总线4. ① IRQ ② FIQ (可交换顺序)5. ① 1.78 ② 44.94 ③ 2.886. ① 1100 0011 0000 1010 ② 1010 0010 1001 1010 ③ 1 ④ 1 ⑤ 1 ⑥ 0 (说明:该题评阅时按上述答案给分,但实际ARM 是32位CPU ,基本没有同学考虑到)7. ① 非流水线执行时间相对流水线执行时间之比8. ① 一段时间内,计算机工作时所需的指令和数据总是集中存放在临近地址的存储单元 9. ① 复位 ② 电源 ③ 时钟 ④ 存储系统 ⑤ 调试接口 (可交换顺序) 10. ① 异常 (或中断) 11. ① BIC ② ORR12. ① =ULCON0(或=0x50000000) ② #0x2B (或#0xAB )一、单选题(共30分,共30空,每空1分)1.以下常用总线标准中,不属于片内总线的是()。

A、Core ConnectB、AMBAC、AvalonD、SATA2.计算机系统中,以下不属于“异常”的是()。

A、系统复位B、软件中断C、未定义指令陷阱D、函数调用3.一般地,微机接口电路一定是()。

A.可编程的B.可寻址的C.可中断的D.可定时的4.某减法定时/计数器的输入时钟周期为Ti,若计数初值为N,则定时时间为()。

A、1/(Ti*N)B、Ti/NC、N/TiD、N*Ti5.一般来说,CPU处于()状态时功耗最低。

A、正常工作B、暂停C、中断D、时钟停止6.遵循“程序存储与控制原理”的计算机属于(①)机。

按其思想,计算机将要执行的程序(包括代码和数据)应安排在计算机的(②)部件中。

①A、冯.诺依曼B、向量C、规约D、数据流②A、硬盘B、内存C、寄存器D、端口7.某微处理器的结构之所以称为超标量结构,是因为该微处理器()。

A、不仅能进行32位运算,也能进行64位运算B、内部含有多条指令流水线和多个执行部件C、数据传输速度很快,每个总线周期最高能传送4个64位数据D、芯片内部集成的晶体管数超过100万个,功耗很大8.总线上多个主设备同时发送信息导致的工作异常一般称为()。

A、总线冲突B、总线仲裁C、总线请求D、总线握手9.总线是一种(①),由系统中各部件所共享,在(②)的控制下完成与(③)的信息传送。

A、公共信号通道B、专用地信号连线C、主设备D、中断源E、从设备F、信号源10.在采用查询方式的输入输出接口中,状态寄存器一般用来存放(①),其中信息则通过系统(②)传送给CPU。

①A、CPU给外设的命令B、外设给CPU的命令C、外设的工作状态D、CPU的工作状态②A、控制总线B、数据总线C、地址总线D、专用总线11.下图所示半导体存储芯片的容量为(①)bits。

若用其构建容量为32K*16的存储体,共需(②)片,并应分成(③)组。

①A、2K*4 B、2K*8 C、8K*4 D、8K*8②A、2 B、4 C、8 D、16③A、1 B、2 C、4 D、812.SoC设计技术中,以版图形式提交、灵活性差、但可靠性高的IP核是()。

A、硬核B、固核C、软核D、以上都不对13.计算机系统中,一个外设的接口至少应具备一个(①)端口,最多可以有(②)个端口。

①A、数据B、状态C、控制D、其他②A、3 B、4 C、8 D、不定14.RISC执行程序的速度优于CISC的主要原因是( )。

A、程序在RISC上编译的目标程序较短B、RISC的指令数较少C、RISC的指令平均周期数较少D、RISC的指令编码不等长15.以下所列提高微机系统性能的技术,说法不正确的是()。

A、提高主机时钟频率后加快了指令执行速度。

B、采用流水线结构后每条指令的执行时间明显缩短。

C、增加Cache存储器后CPU与内存交换数据的速度得到提高。

D、引入虚拟存储技术后扩大了用户可用内存空间。

16.ARM处理器比较无符号数大小时是根据()标志位来判断的。

A、C和NB、C和VC、C和ZD、Z和V17.以下ARM指令中,()的源操作数采用了立即数寻址方式。

A、MOV R0,#2B、LDR R0,[R1]C、BL SUB1D、ADD R0,R1,R2,LSL #118.在CPU内部,通常()用于存放将要执行的指令代码。

A、PC寄存器B、SP寄存器 C. 指令寄存器 D. 指令译码器19.两个同符号补码数相加时,对产生“溢出”的正确叙述为()。

A、和的符号位与加数相反B、结果的符号位为1C、结果的最高位有进位D、结果的符号位为020.在计算机系统三总线结构中,用于产生存储器和外设片选信号的是()。

A、地址总线B、数据总线C、控制总线D、以上都不对21.存储器是计算机系统中的记忆设备,它主要用来存放()。

A、数据和程序B、程序C、数据D、微程序22.常用的输入/输出方式中,便于CPU处理随机事件和提高工作效率的I/O方式是(①),数据传输速率最快的是(②)。

A、无条件控制方式B、查询方式C、中断控制方式D、DMA方式二、填空题(共28分,共28空,每空1分)1.微处理器系统中,指令涉及的操作数可能位于寄存器、(①)或(②)中。

2.微程序控制器中,机器指令与微指令的关系是(①)。

3.处理器完成一条指令所需的时间通常称为(①)周期,而完成一次存储器读/写操作所用时间通常称为(②)周期。

4.ARM支持(①)和(②)两种中断异常。

5.一台主频为80MHz③)ms。

6.某ARM SUBS R0,R0,R1”执行后,R0的值为(①),R1的值为(②),状态标志位N为(③),V为(④),C为(⑤),Z为(⑥)。

(本题数字均采用二进制表示)7.流水线的加速比指(①)。

8.Cache技术的应用基于所谓“局部性原理”,该原理的含义是(①)。

9.嵌入式系统设计中,最小硬件系统通常包括处理器模块以及(①)、(②)、(③)、(④)和(⑤)等保障系统正常工作的基本硬件。

10.由于某突发事件引起CPU暂时终止正在运行的程序,而转去执行相应的服务程序,随后再返回被终止的程序的过程叫做(①)。

11.下列两行代码是用来打开和关闭中断的,请补充空白处的指令操作码。

MRS R0,CPSR(① )R0,R0, #0x80 ;使能中断MSR CPSR_c,R0MRS R1,CPSR(② )R1, R1, #0x80 ;禁止中断MSR CPSR_c,R112.在某个使用S3C2440处理器的系统中,如果要求设置串行通信接口UART0为普通操作模式,8位数据位,偶校验,1位停止位,请完成以下初始化程序段:(相关寄存器详细信息见试卷末页附录)ULCON0 EQU 0x50000000LDR R2, (① )MOV R3, (② )STRB R3, [R2]三、综合题(共42分)1.(7分)总线同步方式主要包括哪几种?下图所示时序属于哪种?这种同步方式有何优缺点?答:总线同步方式主要包括同步(半同步)和异步几种(2分)。

图示为异步并行总线的时序关系(1分)。

异步总线通过主、从控制信号之间应答信号的交替变化来保证总线上地址和数据信息的准确传输,速度适应能力极强(2分)。

缺点是握手控制电路复杂,且握手信号来回应答时间长,效率较低(2分)。

2.(7分)微机中为什么需要使用接口电路?简述接口电路的基本结构,并结合微机上一种具体的接口电路举例说明接口电路一般应具备哪些功能。

I/O接口一方面负责接收、转换、解释并执行CPU发来的命令,另一方面负责将外设的状态或请CPU,从而完成CPU与外设之间的数据传输。

(3分)接口电路的基本结构如下图所示(2分),通常应具有通信联络、设备选择、数据缓冲、信号格式转换、错误检测以及可编程等功能,举例说明略(2分)。

主设备从设备地址数据3. (7分)下图所示为某系统中传送一个字符时的信号波形,试根据波形回答问题。

① 该系统采用的是哪种串行通信方式?(2’)异步串行通信 ② 该系统采用的是奇校验还是偶校验?(1’) 奇校验 ③ 此次通信传送的字符值是多少? (2’) 01010010(0x52) ④ 若该系统每秒可传送960个字符,则其波特率应为多少?(2’) 96004. (7分)试说明中断处理与子程序调用的区别。

● 子程序的执行是程序员事先安排好的(由调用子程序的指令转入);而中断服务子程序的执行一般是由随机的中断事件引发的。

(2分)● 子程序的执行受到主程序或上层子程序的控制;而中断服务子程序一般与被中断的现行程序无关。

(2分) ● 不存在同时调用多个子程序的情况,因此子程序不需要进行优先级排队;而不同中断源则有同时向CPU 提出服务请求。

(2分)共同点:是都要进行程序跳转,都需要保护断点以确保正确返回(1分)。

5. (7分)简述CPU 以查询方式从外设读入数据的基本过程,并指出此种方式的优缺点。

3分):● 输入设备发出的选通信号,一方面将准备好的数据送到接口电路的数据锁存器中,另一方面使接口电路中的D 触发器置1并将该信号送到状态寄存器中等待CPU 查询;● CPU 读接口中的状态寄存器,并检查状态信息以确定外设数据是否准备好;● 若READY =1,说明外设已将数据送到接口中,CPU 读数据端口以获取输入数据,同时数据端口的读信号将接口中的D 触发器清零,即令READY =0,准备下一次数据传送。

查询式(条件式)程序控制方式是一种CPU 主动、外设被动的I/O 操作方式。

这种控制方式很好地解决了CPU 与外设之间的同步问题,不再像同步式(无条件式)程序控制方式那样对端口进行“盲读”、“盲写”,数据传送可靠性高,且硬件接口相对简单(2分);但它的缺点是CPU 工作效率较低,I/O 响应速度慢(2分)。

6. (7分)分析下图及ARM 汇编代码,定性地画出在执行该程序的过程中a 点的波形并做简单说明。

START LDR R0, = 0x3FF GOON MOV R1,# 0xFF STR R1, [R0] NOP MOV R1,# 0xFE STR R1, [R0] NOP NOP NOP B GOON答:从图中可知该锁存器输出端口的地址即3FFH ,程序不断地从Q0口依次输出高、低电平,且低电平持续时间与高电平a …… FFHFEHFFH FEH(参考评分标准:文字说明2分,波形图循环2分,高低电平比例正确3分)附录:S3C2440 UART0线路控制寄存器ULCON0(地址:0x50000000):一、单选题答案(共42分,共37题,单选每题1分,多选题选对一个选项1分)二、填空题答案(共28分,共14 题,每空1分)13.①运算器②控制器③存储器14.①时序逻辑控制/逻辑控制②地址和数据缓冲器(或内部总线)(次序可交换)15.①译码②执行16.①线选、②部分译码法③线选法17.①内总线18.操作码19.串行性20.①高速缓存②主存③辅助存储器④辅助存储器21.①中断控制② I/O处理机③DMA(三个可交换顺序)1 2 3 4 5 6 7 8 9 10 1112 13 14 15 16 17 18 1920D B C B D B A C B B A A D C B C D B C B21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37D B C D B C A D A B C A B A BDE AE BCE22.合理地控制和管理系统中主设备的总线请求,以避免总线冲突23.每种指令的平均周期数;24.①独立编址②统一编址③统一编址25.①2EH ②奇26.44 。