浮点数运算分析

浮点数的运算方法

浮点数的运算方法浮点数是计算机中一种表示实数的数据类型,其特点是可以表示带有小数部分的数字。

在进行浮点数的运算时,需要考虑到浮点数的精度问题、舍入误差以及运算顺序等因素。

浮点数的表示方法为:±m×be,其中m为尾数(即小数部分的数值),b为基数或底数,e为指数(表示位移的量)。

1.浮点数加法运算:-对两个浮点数的指数进行比较,将较小指数的浮点数的尾数左移指数之差的位数,使两个浮点数的小数点对齐。

-对齐后的尾数相加,得到一个和。

-对和进行规格化,即将结果的尾数进行处理,使其满足指定的位数限制。

-对规格化后的结果进行舍入运算,得到最终结果。

2.浮点数减法运算:-先将减数的指数调整与被减数的指数相等。

-对齐后的尾数相减,得到一个差。

-对差进行规格化和舍入运算,得到最终结果。

3.浮点数乘法运算:-将两个浮点数的指数相加,得到加法的和,并相应地调整两个浮点数的尾数。

-尾数相乘,得到一个乘积。

-对乘积进行规格化和舍入运算,得到最终结果。

4.浮点数除法运算:-将被除数的指数减去除数的指数,得到差,并相应地调整两个浮点数的尾数。

-尾数相除,得到一个商。

-对商进行规格化和舍入运算,得到最终结果。

在进行浮点数运算时需要注意一些问题:-浮点数的精度问题:由于浮点数的尾数有限位数,所以会存在精度丢失的问题。

这就意味着进行浮点数运算时,可能会出现舍入误差,导致结果有微小的偏差。

-运算顺序:浮点数的运算顺序可能会影响最终结果。

在连续进行多次浮点数运算时,可能会得到不同的结果。

这是因为浮点数的运算不满足交换律和结合律。

因此,在编程中需要谨慎选择运算顺序,以避免结果的不确定性。

-溢出和下溢问题:由于浮点数的范围限制,可能会出现溢出(结果超出浮点数的表示范围)或下溢(结果过小,无法表示)的情况。

针对这些情况,需要进行特殊处理,如返回特定的错误码或进行科学计数法表示。

在实际编程中,可以使用编程语言提供的浮点数运算库或内置函数来进行浮点数运算,以确保运算结果的准确性和可靠性。

浮点数表示方法与运算

在计算机系统的发展过程中,曾经提出过多种方法表达实数,典型的比如定点数。

在定点数表达方式中,小数点位置固定,而计算机字长有限,所以定点数无法表达很大和很小的实数。

最终,计算机科学发展出了表达范围更大的表达方式——浮点数,浮点数也是对实数的一种近似表达。

1.浮点数表达方式我们知道任何一个R 进制数N 均可用下面的形式表示:N R =±S ×R ±e其中,S—尾数,代表N 的有效数字;R—基值,通常取2、8、16;e—阶码,代表N 的小数点的实际位置(相当于数学中的指数)。

比如一个十进制数的浮点表达1.2345×102,其中1.2345为尾数,10为基数,2为阶码。

一个二进制数的浮点表达0.001001×25,0.001001为尾数,2为基数,5为阶码;同时0.001001×25也可以表示成0.100100×23,0.100100为尾数,2为基数,3为阶码。

浮点数就是利用阶码e 的变化达到浮动小数点的效果,从而灵活地表达更大范围的实数。

2.浮点数的规格化一个数用浮点表示时,存在两个问题:一是如何尽可能多得保留有效数字;二是如何保证浮点表示的唯一。

对于数0.001001×25,可以表示成0.100100×23、0.00001001×27等等,所以对于同一个数,浮点有多种表示(也就是不能唯一表示)。

另外,如果规定尾数的位数为6位,则0.00001001×27会丢掉有效数字,变成0.000010×27。

因此在计算机中,浮点数通常采用规格化表示方法。

当浮点数的基数R 为2,即采用二进制数时,规格化尾数的定义为:1/2<=|S|<1。

若尾数采用原码(1位符号位+n 位数值)表示,[S]原=S f S 1S 2S 3…S n (S f 为符号位的数符),则满足S 1=1的数称为规格化数。

深入理解C++浮点数(float、double)类型数据比较、相等操作判断

深⼊理解C++浮点数(float、double)类型数据⽐较、相等操作判断浮点数在内存中的存储机制喝整形数据不同,有舍⼊误差,在计算机中⽤近似表⽰任意某个实数。

具体来说,这个数由⼀个整数或定点数(即尾数)乘以某个基数(计算机中通常是2)的整数次幂得到。

这种表⽰⽅法类似于基数为10的科学计数法。

所以浮点数在运算过程中随着因为⽆法精确表⽰⽽进⾏的近似或舍⼊。

但是这种设计的好处是可以在固定的长度上存储更⼤范围的数。

1、将字符串转化为float、double过程存在精度损失,只是float、double各⾃损失的精度不相同⽽已std::string str="8.2";float cc=atof(str.c_str()); //cc的值为8.1999998std::string str="8.2";double cc=atof(str.c_str()); //cc的值为8.1999999999999993 2、将float、double转换为字符串的过程中可能存在精度损失,但是通过%.8lf可以规避 2.1 float⼩数点前后加起来有效数字只有6位,当给定的float有效数在6位以内转换为字符串时不会丢失精度,当有效位数⼤于6位就会存在精度丢失。

//精度没有丢失char buf[100]={'\0'};float aa=8000.25;sprintf(buf,"%f",aa); //8000.250000//精度没有丢失char buf[100]={'\0'};floataa=8.00025;sprintf(buf,"%f",aa); buf = 8.000250//精度丢失,存在误差charbuf[100]={'\0'};float aa=8000.251;sprintf(buf,"%f",aa); //8000.250977//精度丢失,存在误差此时使⽤.8lf也⽆效char buf[100]={'\0'};float aa=8000.251;sprintf(buf,"%.8lf",aa);//8000.25097656 2.2 double⼩数前后加起来的有效数字只有16位,当给定的double有效数在16位数以内转换为字符串时不会丢失精度,当有效位数⼤于16位就会出现精度丢失。

浮点数的运算方法

浮点数的运算方法浮点数是计算机中用于表示实数的一种数据类型,由于实数是无限的,而计算机只能存储有限的信息,所以必然存在精度误差。

浮点数的运算涉及到加法、减法、乘法和除法等基本运算,以及开方、幂函数等高级运算。

1.加法运算:浮点数相加时,先将较小的浮点数调整为与较大的浮点数相同的指数,然后进行尾数的相加,最后对结果进行规格化处理,即进行舍入操作,得到最终的结果。

2.减法运算:浮点数相减的原理与加法相同,只是在相减之前,需要将两个浮点数的指数调整为相等,然后进行尾数的相减操作,最后同样需要对结果进行规格化处理。

3.乘法运算:浮点数相乘时,将两个浮点数的指数相加,然后将尾数相乘得到结果的尾数部分,最后对结果进行规格化处理。

4.除法运算:浮点数除法的原理与乘法类似,先将两个浮点数的指数相减,然后将尾数相除得到结果的尾数部分,最后同样需要进行规格化处理。

5.开方运算:浮点数的开方运算是通过求解多项式的根来实现的,常用的方法有牛顿法、二分法和二次近似法等。

这些方法都是通过迭代的方式,逐步逼近平方根的值,直到达到所需的精度。

6.幂函数运算:浮点数的幂函数运算可以通过连乘或连乘的方式实现。

幂函数运算的精度取决于底数和指数的精度以及所需的结果精度。

在浮点数的运算过程中,需要注意以下几个常见问题:1.精度丢失:浮点数的表示是有限的,不可避免地存在精度误差,特别是在进行连续的浮点数运算时,会导致误差累积,可能导致结果的不准确。

2.舍入误差:浮点数的结果需要进行舍入操作以保持一定的精度。

舍入规则有多种,如四舍五入、向上取整、向下取整等,选择合适的舍入规则可以减小误差。

3.溢出和下溢:浮点数的范围是有限的,当计算结果超出范围时,会发生溢出;当结果接近零但无法表示时,会发生下溢。

这两种情况都需要进行特殊处理。

4. 特殊数值:浮点数中有几个特殊的数值,如无穷大(Infinity)、非数值(NaN)和零(0)。

这些特殊值的运算需要按照特定的规则进行处理,以免引起错误。

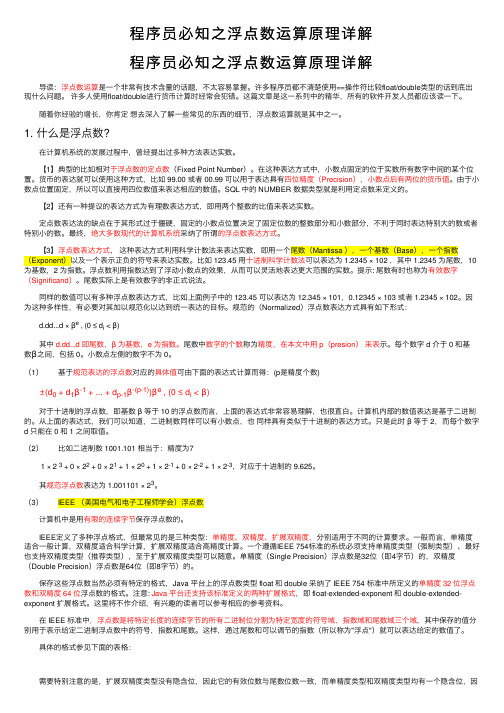

程序员必知之浮点数运算原理详解

程序员必知之浮点数运算原理详解程序员必知之浮点数运算原理详解 导读:浮点数运算是⼀个⾮常有技术含量的话题,不太容易掌握。

许多程序员都不清楚使⽤==操作符⽐较float/double类型的话到底出现什么问题。

许多⼈使⽤float/double进⾏货币计算时经常会犯错。

这篇⽂章是这⼀系列中的精华,所有的软件开发⼈员都应该读⼀下。

随着你经验的增长,你肯定想去深⼊了解⼀些常见的东西的细节,浮点数运算就是其中之⼀。

1. 什么是浮点数? 在计算机系统的发展过程中,曾经提出过多种⽅法表达实数。

【1】典型的⽐如相对于浮点数的定点数(Fixed Point Number)。

在这种表达⽅式中,⼩数点固定的位于实数所有数字中间的某个位置。

货币的表达就可以使⽤这种⽅式,⽐如 99.00 或者 00.99 可以⽤于表达具有四位精度(Precision),⼩数点后有两位的货币值。

由于⼩数点位置固定,所以可以直接⽤四位数值来表达相应的数值。

SQL 中的 NUMBER 数据类型就是利⽤定点数来定义的。

【2】还有⼀种提议的表达⽅式为有理数表达⽅式,即⽤两个整数的⽐值来表达实数。

定点数表达法的缺点在于其形式过于僵硬,固定的⼩数点位置决定了固定位数的整数部分和⼩数部分,不利于同时表达特别⼤的数或者特别⼩的数。

最终,绝⼤多数现代的计算机系统采纳了所谓的浮点数表达⽅式。

【3】浮点数表达⽅式,这种表达⽅式利⽤科学计数法来表达实数,即⽤⼀个尾数(Mantissa ),⼀个基数(Base),⼀个指数(Exponent)以及⼀个表⽰正负的符号来表达实数。

⽐如 123.45 ⽤⼗进制科学计数法可以表达为 1.2345 × 102 ,其中 1.2345 为尾数,10为基数,2 为指数。

浮点数利⽤指数达到了浮动⼩数点的效果,从⽽可以灵活地表达更⼤范围的实数。

提⽰: 尾数有时也称为有效数字(Significand)。

尾数实际上是有效数字的⾮正式说法。

计算机组成原理:浮点数表示及运算

0.1000101010

把不满足这一表示要求的尾数,变成满足这一要求的尾数 的操作过程,叫作浮点数的规格化处理,通过尾数移位和修改 阶码实现。

计算机组成原理 5

规格化目的: 为了提高数据的表示精度 为了数据表示的唯一性 尾数为R进制的规格化: 绝对值大于或等于1/R 二进制原码的规格化数的表现形式:

…

Em

M0

M1

M2

… …

…

Mn

阶符

计算机组成原理

阶值

尾符

尾数值

2

一个机器浮点数由阶码和尾数及其符号位组成: 尾数:用定点小数表示,给出有效数字的位数,决定了浮点数的表示精度 阶码:用定点整数形式表示,指明小数点在数据中的位置,决定了浮点数

的表示范围。

浮点数的表示范围

负上溢

负下溢

正下溢 正上溢

-

最 小 负 数

• 对阶原则 阶码小的数向阶码大的数对齐; 对阶过程小阶的尾数右移,每右移一位,其阶码加1(右规)。

210*(0.11000)+28*(0.00110) 大阶对小阶 210*(0.11000)--28*(11.000) 11.000+0.00110 ?????????

小阶对大阶 28*(0.00110)--210*(0.00001)

计算机组成原理

8

规格化浮点数的真值

31 30

32位浮点数格式:

23 22

0

S

E

M

一个规格化的32位浮点数x的真值为: x = (-1)s (1.M) 2E-127 e =E – 127 一个规格化的64位浮点数x的真值为: 这里e是真值,E是机器数 x = ( –1)s×(1.M)×2E-1023

浮点数的运算为什么更慢

浮点数的运算为什么更慢1. 浮点数的表⽰m 是尾数,为±d.dddddd 其中第⼀位必须⾮0b 是基数,下⾯,让我们回到⼀开始的问题:为什么0x00000009还原成浮点数,就成了0.000000?⾸先,将0x00000009拆分,得到第⼀位符号位s=0,后⾯8位的指数E=00000000,最后23位的有效数字M=000 0000 0000 0000 0000 1001。

由于指数E全为0,所以符合上⼀节的第⼆种情况。

因此,浮点数V就写成:V=(-1)^0×0.00000000000000000001001×2^(-126)=1.001×2^(-146)结论通⽤规则:整数和(和AND/ OR/ XOR)与乘积花费的时间相同,除法(和取模)的速度慢三倍。

浮点数的乘积⽐求和的乘积慢两倍,除法的乘积甚⾄更慢。

在相同数据⼤⼩下,浮点运算始终⽐整数运算慢。

越⼩越快。

64位整数精度确实很慢。

浮点数32位总和⽐64位快,但在乘积和除法上却不是。

80和128位精度仅在绝对必要时才应使⽤,它们⾮常慢。

特别案例:在x86-64 AVX上,浮点乘积在64位数据上⽐在32位上更快。

在POWER8 AltiVec上,浮点乘积以各种精度达到求和的速度。

对8位,16位,32位或64位整数以相同的速度执⾏整数运算。

在ARM1176上,按位整数运算符⽐加法运算要快。

⽰例代码:#include <stdio.h>#include <math.h>#include <stdlib.h>#include <cv/cv_tools.h>#include <picture/cv_picture.h>#include "libyuv.h"using namespace cv;using namespace std;using namespace oop;int main(){const int N= 10000;int sum = 0;float sumf = 0;float nf = 734.0f;int n = 734;timeInit;timeMark("int");for(int j=0;j!=100000;++j){sum = 0;for (int i = 0; i != N; ++i) {sum += n;}}timeMark("float");for (int j = 0; j != 100000; ++j){sumf = 0;for (int i = 0; i != N; ++i) {sumf += nf;}}timeMark(")");timePrint;printf("sum=%d\nsumf=%.2f\n",sum,sumf);getchar();}输出:( int,float ) : 2107 ms( float,) ) : 3951 mssum=7340000sumf=7340000.00Release:( int,float ) : 0 ms( float,) ) : 1814 mssum=7340000sumf=7340000.00实际上: Debug模式下,两者时间差不了多少,两倍的关系但是Release模式下, int ⼏乎很快就完成了!!说明int型被优化得很好了,float型运算不容易被编译器优化!!!我们在Release模式下,优化设置为O2, 连接器设置为-优化以便于调试查看int 乘法汇编指令:xmm0 表⽰128位的SSE寄存器,可见我们的代码都被优化为SSE指令了!!查看float 汇编代码:感觉⾥⾯也有xmm 等SSE指令集,⾄于为啥int型乘法⽐float乘法快很多,还是有点搞不明⽩,需要详细分析⾥⾯的汇编指令才能搞明⽩⽹上关于这⽅⾯的资料太少了,哎~~我们再看看float 和 int乘法对图像进⾏处理的例⼦:我们把BGR 3个通道分别乘以2 3 4 、 2.0f, 3.0f, 4.0f 然后输出,这⾥我们不考虑溢出的问题,仅仅对乘法的效率进⾏测试设置为Release模式,O2int main(){cv::Mat src = imread("D:/pic/nlm.jpg");//cvtColor(src,src,CV_BGR2GRAY);resize(src,src,Size(3840*2,2160*2));cv::Mat dst0(src.size(), src.type());cv::Mat dst1(src.size(), src.type());int w = src.cols;int h = src.rows;int of3=0;timeInit;timeMark("int");for (int j = 0; j != h; ++j) {for (int i = 0; i != w; ++i) {//int of3 = (j*w + i) * 3;dst0.data[of3 ] = src.data[of3] * 2;dst0.data[of3 + 1] = src.data[of3 + 1] * 3;dst0.data[of3 + 2] = src.data[of3 + 2] * 4;of3+=3;}}timeMark("float");of3=0;for (int j = 0; j != h; ++j) {for (int i = 0; i != w; ++i) {//int of3 = (j*w + i)*3;dst1.data[of3] = src.data[of3] * 2.0f;dst1.data[of3+1] = src.data[of3+1] * 3.0f;dst1.data[of3+2] = src.data[of3+2] * 4.0f;of3 += 3;}}timeMark("end");timePrint;myShow(dst0);myShow(dst1);waitKey(0);}输出:( int,float ) : 149 ms( float,end ) : 173 ms输出图像(分别为原图,dst0,dst1)(截取了⼀部分)可见,时间并差不了多少,但int还是要快⼀点!!这是我看到的另外⼀个帖⼦,⾥⾯讲的float乘法确实⽐较复杂,这可能是它⽐较慢的原因之⼀吧总结⼀下: float运算更慢的原因:1. float运算不容易被编译器优化2. float运算本⾝就慢(但并不⽐int型运算慢多少,⼤约1.3-2倍的样⼦)。

float 加减

float 加减在计算机编程中,float是一种数据类型,用来表示带有小数点的数字。

在编写程序时,经常需要进行浮点数的加减运算,本文将详细介绍float的加减运算及其注意事项。

在进行float的加减运算时,我们需要注意以下几点:1. 浮点数的表示方式浮点数的表示方式是通过科学计数法来表示的,即用一个尾数和一个指数来表示一个浮点数。

例如,3.14可以表示为3.14×10^0,而0.001可以表示为1×10^-3。

2. 浮点数的精度问题由于计算机内部表示浮点数时存在精度问题,因此在进行浮点数的加减运算时,可能会出现一定的误差。

这是由于浮点数的内部表示方式决定的,而不是编程语言本身的问题。

因此,在进行浮点数的加减运算时,需要注意精度问题,并且尽量避免进行多次浮点数的加减运算。

3. 浮点数的加法运算浮点数的加法运算是通过将两个浮点数的尾数相加,然后根据指数的差值来调整尾数的大小。

具体步骤如下:- 比较两个浮点数的指数大小,将指数较小的浮点数的尾数乘以10的差值次方,使两个浮点数的指数相等。

- 将两个浮点数的尾数相加,得到新的尾数。

- 对得到的尾数进行规格化,即将尾数的整数部分保留一个非零位,其余位数舍去或进位,得到最终的尾数。

4. 浮点数的减法运算浮点数的减法运算是通过将两个浮点数的尾数相减,然后根据指数的差值来调整尾数的大小。

具体步骤如下:- 比较两个浮点数的指数大小,将指数较小的浮点数的尾数乘以10的差值次方,使两个浮点数的指数相等。

- 将两个浮点数的尾数相减,得到新的尾数。

- 对得到的尾数进行规格化,即将尾数的整数部分保留一个非零位,其余位数舍去或进位,得到最终的尾数。

总结起来,float的加减运算需要注意浮点数的精度问题,并且需要进行指数的调整和尾数的规格化。

在实际编程中,可以使用编程语言提供的浮点数运算函数来进行浮点数的加减运算,这样可以避免一些精度问题。

以上是关于float加减的介绍,希望对大家有所帮助。

计算机组成原理第11-浮点数的运算1

x±y=(Mx2Ex-Ey±My)2Ey, Ex<=Ey

12/31/2023

信 息 科 学 与 工 程 学 院1

两数首先均为规格化数,进行规格化浮点数的加减运 算需经过5步完成: (1)对阶操作:低阶向高阶补齐,使阶码相等。 (2)尾数运算:阶码对齐后直接对尾数运算。 (3)结果规格化:对运算结果进行规格化处理(使补码尾 数的最高位和尾数符号相反)。如溢出则需右规;如不是 规格化时应左规。 (4)舍入操作:丢失位进行0舍1入或恒置1处理。 (5)判断溢出:判断阶码是否溢出,下溢则将运算结果置 0(机器0),上溢则中断。

14 12/31/2023

信 息 科 学 与 工 程 学 1院4

第二章 运算方法和运算器

2、乘、除法运算步骤 浮点数的乘除运算大体分为以下几个步骤:

1> 0 操作数检查。 2> 阶码加/减操作。 3> 尾数乘/除操作。 4> 结果规格化 5> 舍入处理。

15 12/31/2023

信 息 科 学 与 工 程 学 1院5

18 12/31/2023

信 息 科 学 与 工 程 学 1院8

第二章 运算方法和运算器

当尾数用原码表示时,舍入规则比较简单。最简便的方法,是只要尾数的最低位 为1,或移出的几位中有为1的数值位,就是最低位的值为1。 另一种是0舍1入法,即当丢失的最高位的值为1时,把这个1加到最低数值位上进 行修正,否则舍去丢失的的各位的值。 当尾数是用补码表示时,所用的舍入规则,应该与用原码表示时产生相同的处理 效果。 具体规则是:

(4) 右规

当 尾数溢出( >1)时,需 右规 即尾数出现 01. ×× …×或 10. ×× …×时

尾数 1,阶码加 1

12/31/2023

请简述浮点数加减运算的步骤。

请简述浮点数加减运算的步骤。

1.对齐小数点位置:首先,需要将参与运算的浮点数进行小数点的对齐,使其具有相同的小数位数,这样才能正确进行运算。

2.符号位处理:对于有符号的浮点数,需要首先对其符号位进行处理,即判断是否有正负号的变化,以便后续的运算。

3.阶码对齐:浮点数的运算涉及到对阶码的操作。

阶码表示了浮点数

的指数部分。

对于两个浮点数,它们的阶码可能不同,因此需要将它们的

阶码进行对齐。

对齐阶码后,还需要比较两个阶码的大小,确定哪个数应

进行放缩操作。

4.尾数运算:对齐阶码后,需要对尾数进行运算。

具体来说,如果两

个浮点数的阶码相同,那么它们的尾数直接相加或相减即可。

如果阶码不同,则需要将尾数按照较小的阶码进行放缩,以便进行运算。

5.规格化:运算完成后,还需要对结果进行规格化。

规格化的目的是

确保表示浮点数的规范形式。

具体来说,就是要保证尾数的最高有效位

(即尾数的最左边一位)为1,并且将阶码调整到正确的位置。

6.溢出判断:最后,需要对运算结果进行溢出判断。

如果运算结果超

出了浮点数所能表示的范围,即超出了尾数所能表示的有效位数,那么就

会发生溢出。

溢出的情况下,一般需要对结果进行舍入或截断处理。

总结起来,浮点数加减运算的步骤包括对齐小数点位置、符号位处理、阶码对齐、尾数运算、规格化和溢出判断等。

这些步骤保证了浮点数的加

减运算的正确性和精度。

浮点数的四则运算

主要内容:

• 浮点加减运算 • 浮点乘除运算

2.7.1 浮点加减运算

1、对阶 ■ 规则:小阶对大阶。

原因:舍去尾数低位,产生误差;若丢失尾数高位,必 然导致错误。

■ 方法:求阶差。

阶差=0,不需对阶; 阶差≠0,小阶码数的尾数右移,右移次数为阶差的绝 对值,其阶码加上阶差的绝对值。

❖X-Y的结果需要右规,将尾数右移1位,阶码加1,得:[X-Y]浮 =0011;00100010,阶码未超出+Emax,∴未溢出

6

4)舍入 ❖由于X+Y是左规,结果不需要舍入; ❖X-Y为右规,若采用末位恒置1法,则

[X-Y]浮=0011;00100011。 ❖若采用0舍1入法,则结果相同。

7

2.7.2 浮点乘除运算

解先将两浮点数表示为规格化的浮点数x浮000100110101y浮0010110101101对阶求阶差e0001补0010补1111补1exey按小阶对大阶原则x的尾数右移1位阶码加1尾数舍入采用末位恒置1法则x浮00100001101162尾数求和差000110111101011011110001即xy浮0010111100013结果规格化及判溢xy的结果是非规格化的数需左规

阶码一般用补码或者移码表示。

若阶码用移码表示,则根据移码的定义可知: [Ex]移 + [Ey]移 = 2n + Ex + 2n + Ey

= 2n + (2n + Ex + Ey) = 2n + [Ex + Ey]移 若直接用移码求阶码之和,结果比两数之和的移码多 了2n,即最高位上多加了一个1. 所以,要求两数和的移码,必须将两数移码之和的最 高位(符号位)取反。

c语言浮点数整除和浮点除

c语言浮点数整除和浮点除C语言是一种通用的高级编程语言,具有广泛的应用范围。

在C 语言中,浮点数的除法操作涉及两种运算:整除和浮点除法。

本文将逐步介绍这两种运算的概念、实现和应用。

首先,让我们来了解一下浮点数的基本概念。

在计算机中,浮点数是通过浮点数表示法来表示的。

浮点数表示法由两部分组成:尾数和指数。

尾数表示数值的有效位数,而指数表示尾数的小数点位置。

通过这种表示法,我们可以处理非常大或非常小的数值。

浮点数的除法是一种常见的运算,通常用于计算某个值除以另一个值的结果。

C语言提供了两种除法运算符:/ 和。

其中,/ 运算符执行浮点除法,而运算符执行整数除法并返回余数。

第一步,我们将讨论浮点数的整除操作。

整除是指将一个数值除以另一个数值,并返回其整数部分的结果。

例如,10除以3的整除结果为3。

在C语言中,我们可以使用类型转换操作符(int)来执行浮点数的整除操作。

下面是一个示例代码,用于演示浮点数的整除操作:include <stdio.h>int main() {float num1 = 10.0;float num2 = 3.0;int result = (int)(num1 / num2);printf("整除结果为:d\n", result);return 0;}运行上述代码,将输出整除结果为3。

在这个示例中,我们定义了两个浮点数变量num1和num2,然后使用类型转换操作符将它们的浮点除法结果转换为整数值,并将结果存储在result变量中。

最后,我们使用printf函数将result的值输出到控制台。

第二步,我们将讨论浮点数的浮点除法操作。

浮点除法是指将一个数值除以另一个数值,并返回精确到小数位的结果。

在C语言中,我们只需使用浮点数除法运算符(/)即可执行浮点除法操作。

下面是一个示例代码,用于演示浮点数的浮点除法操作:include <stdio.h>int main() {float num1 = 10.0;float num2 = 3.0;float result = num1 / num2;printf("浮点除法结果为:f\n", result);return 0;}运行上述代码,将输出浮点除法结果为3.333333。

单片机浮点数(二)

单片机浮点数(二)引言概述:本文旨在介绍单片机的浮点数运算(二)方面的知识。

浮点数运算在单片机应用中具有重要的地位,可以实现复杂的数值运算和精确的数据处理。

在本文中,我们将详细介绍单片机浮点数运算的相关概念、实现方法和应用场景。

读者通过本文的学习,将能够更好地理解和运用单片机的浮点数运算功能。

正文:一、浮点数的概念与表示方法1.1 浮点数的定义及特点1.2 浮点数的表示方法1.3 整数与浮点数的相互转换1.4 浮点数的正负表示与运算规则1.5 浮点数运算的精度问题二、浮点数的加减法运算2.1 浮点数的二进制加法运算2.2 浮点数的二进制减法运算2.3 超尾与规格化处理方法2.4 浮点数的加减法运算实例2.5 浮点数加减法运算的误差分析三、浮点数的乘法运算3.1 浮点数的二进制乘法运算3.2 小数部分的对齐与进位处理3.3 浮点数的乘法运算实例3.4 浮点数乘法运算的误差分析3.5 浮点数乘法运算的应用案例四、浮点数的除法运算4.1 浮点数的二进制除法运算4.2 小数部分的对齐与余数估算4.3 浮点数的除法运算实例4.4 浮点数除法运算的误差分析4.5 浮点数除法运算的应用场景五、浮点数运算的性能优化与应用案例5.1 浮点数运算的性能优化方法5.2 浮点数运算在机器人控制中的应用5.3 浮点数运算在图像处理中的应用5.4 浮点数运算在信号处理中的应用5.5 浮点数运算在科学计算中的应用总结:通过本文的介绍,我们了解了单片机浮点数运算的概念、表示方法和运算规则。

同时,我们学习了浮点数的加减法、乘法和除法运算,并掌握了相应的实例和误差分析方法。

最后,我们进一步讨论了浮点数运算的性能优化方法和应用案例。

希望本文对读者在单片机浮点数运算方面的学习和应用提供了一定的帮助。

浮点数的表达与运算

浮点数的表示与运算一、选择1、在规格化浮点数运算中,若浮点数为25X1.10101,其中尾数为补码表示,则该数需将尾数左移一位规格化2、浮点数格式如下:1位阶符,6位阶码,1位数符,8位尾数。

若阶码用移码,尾数用补码表示,则浮点数所能表示数的范围是-263 ~ (1-2-8)X 2633、某浮点机,采用规格化浮点数表示,阶码用移码表示(最高位代表符号位),尾数用原码表示。

下列哪个数的表示不是规格化浮点数?( B )阶码尾数A.,1.1000 ••• 00B.,1.0111 ••• 01C.,0.1111 •••01D.,0.1000 ••• 104、设浮点数阶的基数为8,尾数用模4补码表示。

试指出下列浮点数中哪个是规格化数?( C )A.11.B.00.C.11.D.11.5、按照IEEE654标准规定的32位浮点数(41A4c000)16对应的十进制数是(D )A.4.59375B.-20.59375C.-4.59375D.20.593756、如果某单精度浮点数、某原码、某补码、某移码的32位机器数为0xF。

这些数从大到小的顺序是移〉补>原>浮7、假定采用IEEE754标准中的单精度浮点数格式表示一个数为H,则该数的值是(+1.125)10X2118、设浮点数共12位。

其中阶码含1位阶符共4位,以2为底,补码表示:尾数含1位数符共8位,补码表示,规格化。

则该浮点数所能表示的最大正数是27-19、如果浮点数的尾数用补码表示,则下列(D )中的尾数是规格化数形式。

A. 1.11000B. 0.01110C. 0.01010D.1.0001010、设浮点数的基数为4,尾数用原码表示,则以下(C )是规格化的数。

A. 1.B.0.C.1.D.0.11、已知X=00.875X21, Y=0.625X22,设浮点数格式为阶符1位,阶码2位,数符1位,尾数3位,通过补码求出Z=X-Y 的二进制浮点数规格化结果是―0111 011—12、IEEE754标准中的舍入模式可以用于二进制数也可以用于十进制数,在采用舍入到最接近且可表示的值时,若要舍入两个有效数字形式,(12.5)D应该舍入为1213、下列关于舍入的说法,正确的是(E )A.不仅仅只有浮点数需要舍入,定点数在运算时也可能要舍入B.在浮点数舍入中,只有左规格化时可能要舍入C.在浮点数舍入中,只有右规格化时可能要舍入D.在浮点数舍入中,左、右规格化均可能要舍入E.舍入不一定产生误差二、综合应用题1、什么是浮点数的溢出?什么情况下发生上溢出?什么情况下发生下溢出?2、现有一计算机字长32位(D3rD0),数符位是第31位。

计算机浮点运算详解深入学习计算机组成原理

深入剖析浮点运算性能优化

04

策略

减少不必要的数据转换和传输延迟

数据重用

避免不必要的数据类型转换

尽量保持数据在运算过程中的类型一致,避免频繁 进行数据类型转换,以减少转换带来的性能开销。

通过缓存最近使用过的数据,减少从主存中 加载数据的次数,从而降低数据传输延迟。

优化数据布局

合理安排数据在内存中的布局,使得访问局 部性更好,减少缓存失效和页面换入换出的 次数。

性能问题

浮点运算通常比整数运算更复杂,需要更多的CPU周期和内存带宽。这可能导致性能瓶颈,特别是在需要大量浮点运 算的应用中。

兼容性问题

不同的计算机系统和编程语言可能采用不同的浮点表示方法和运算规则,这可能导致兼容性问题。例如, 一个系统上的计算结果可能在另一个系统上无法重现。

未来发展趋势预测及建议

• 精度提升:随着计算机硬件和算法的不断进步,未来浮点运算的精度将得到进 一步提升。例如,采用更高精度的浮点数表示方法和更精确的运算算法。

• 性能优化:为了提高浮点运算的性能,未来可能会采用更高效的硬件设计、并 行计算技术和优化算法。例如,利用GPU和TPU等专用硬件加速浮点运算, 以及采用分布式计算等技术提高大规模浮点运算的效率。

进行实验和编程实践

通过编写程序和使用相关工具 进行实验,加深对浮点数运算 的理解和掌握程度。

THANKS

感谢观看

数值积分与微分

利用浮点运算进行数值积分和微 分,可以求解函数的定积分、不 定积分、导数等。

图形图像处理领域应用

01

3D图形变换

02

03

图像滤波与处理

计算机视觉

在3D图形处理中,浮点运算用于 实现各种复杂的图形变换,如旋 转、缩放、平移等。

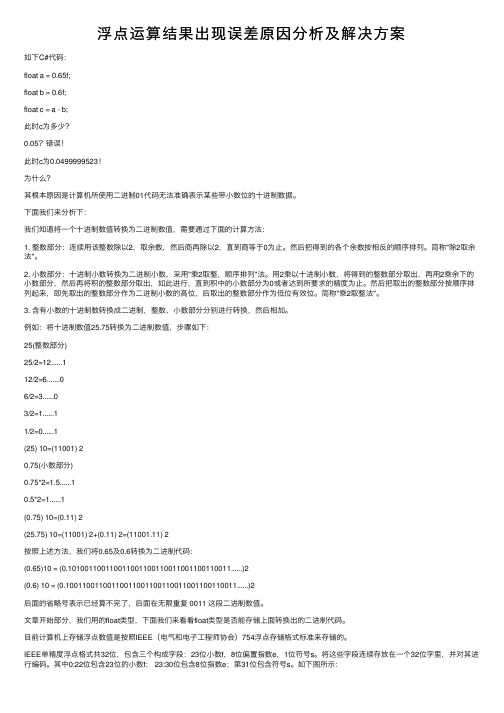

浮点运算结果出现误差原因分析及解决方案

浮点运算结果出现误差原因分析及解决⽅案如下C#代码:float a = 0.65f;float b = 0.6f;float c = a - b;此时c为多少?0.05?错误!此时c为0.0499999523!为什么?其根本原因是计算机所使⽤⼆进制01代码⽆法准确表⽰某些带⼩数位的⼗进制数据。

下⾯我们来分析下:我们知道将⼀个⼗进制数值转换为⼆进制数值,需要通过下⾯的计算⽅法:1. 整数部分:连续⽤该整数除以2,取余数,然后商再除以2,直到商等于0为⽌。

然后把得到的各个余数按相反的顺序排列。

简称"除2取余法"。

2. ⼩数部分:⼗进制⼩数转换为⼆进制⼩数,采⽤"乘2取整,顺序排列"法。

⽤2乘以⼗进制⼩数,将得到的整数部分取出,再⽤2乘余下的⼩数部分,然后再将积的整数部分取出,如此进⾏,直到积中的⼩数部分为0或者达到所要求的精度为⽌。

然后把取出的整数部分按顺序排列起来,即先取出的整数部分作为⼆进制⼩数的⾼位,后取出的整数部分作为低位有效位。

简称"乘2取整法"。

3. 含有⼩数的⼗进制数转换成⼆进制,整数、⼩数部分分别进⾏转换,然后相加。

例如:将⼗进制数值25.75转换为⼆进制数值,步骤如下:25(整数部分)25/2=12 (1)12/2=6 06/2=3 03/2=1 (1)1/2=0 (1)(25) 10=(11001) 20.75(⼩数部分)0.75*2=1.5 (1)0.5*2=1 (1)(0.75) 10=(0.11) 2(25.75) 10=(11001) 2+(0.11) 2=(11001.11) 2按照上述⽅法,我们将0.65及0.6转换为⼆进制代码:(0.65)10 = (0.101001100110011001100110011001100110011......)2(0.6) 10 = (0.10011001100110011001100110011001100110011......)2后⾯的省略号表⽰已经算不完了,后⾯在⽆限重复 0011 这段⼆进制数值。

理解浮点数运算的误差原理

理解浮点数运算的误差原理

浮点数运算的误差主要是由于计算机在表示浮点数时采用的是有限精度的二进制数,而不是精确的十进制数。

因此,在进行浮点数运算时可能会引入舍入误差,导致计算结果和真实结果之间存在微小的差距。

这种误差主要源自以下几个方面:

1. 精度限制:浮点数在计算机中的表示是有限的,因此无法精确地表示无限小的数或无限大的数。

这就意味着浮点数的表示精度是有限的,计算结果往往会被截断或者舍入,从而引入误差。

2. 运算顺序:浮点数的计算顺序可能会影响最终的结果。

由于浮点数的有限精度,不同的计算顺序可能会导致不同的结果,尤其在存在大数相加或相减的情况下。

3. 舍入误差:计算机在进行浮点数运算时,常常需要对结果进行舍入,使其符合浮点数的表示规范。

这个舍入过程往往会引入误差。

为了减小浮点数运算的误差,我们可以采取一些方法,例如使用更高精度的浮点数表示,尽量减小运算过程中的截断或者舍入,避免大数相加或相减等操作。

此外,也可以考虑使用数值稳定的算法或者对算法进行数值稳定性分析,以减小误差的影响。

浮点数误差原因

浮点数误差原因

浮点数误差的原因一般来说有以下几点:

1. 精度限制问题:浮点数只能表示特定范围内的数值,但是在这个范围内并不是所有的数都可以被准确表示。

这是由于浮点数精度的限制造成的。

在使用浮点数进行计算时,计算机会根据浮点数存储的精度对数值进行近似处理,这就会导致误差。

2. 舍入误差问题:在进行浮点数计算时,舍入误差也是不可避免的。

因为浮点数只能存储有限的精度,所以在计算时,可能会出现一些无法精确表示的小数部分。

这个小数部分会被计算机进行舍入处理,这就会导致一些误差的出现。

3. 运算顺序问题:浮点数计算时运算顺序也会导致误差。

因为浮点数计算是按照计算机内部的处理单元进行的,而这些处理单元的运算速度和精度是不一样的。

所以,在进行浮点数计算时,运算顺序可能会影响到误差的大小。

针对这些误差问题,我们可以采取以下方法来减少误差:

1. 使用更高精度的数据类型:使用double或者long double类型可

以提高浮点数的精度限制。

可以减少部分误差。

2. 尽量避免舍入误差:可以使用一些优化算法来减少舍入误差的出现,比如两个相近的数相减时,避免使用相反数的方法来避免出现大量的

小数部分。

3. 调整运算顺序:可以通过调整运算顺序来减少误差的出现。

比如在

进行浮点数累加时,可以采用两两相加的方式来避免误差的积累。

综上所述,浮点数误差是由于浮点数精度限制、舍入误差、运算顺序

等多种原因造成的。

通过使用更高精度的数据类型、避免舍入误差和

调整运算顺序等方式来减少这些误差的出现,可以提高浮点数计算的

精度。

float减法

float减法摘要:1.浮点数减法的基本概念2.浮点数减法的运算规则3.浮点数减法的精度问题4.浮点数减法的实际应用正文:一、浮点数减法的基本概念浮点数减法是指在计算机中进行的带有小数部分的数值相减运算。

这种运算涉及到数据的表示和处理,具有一定的复杂性。

由于计算机内部采用二进制表示法,浮点数减法实际上是通过一定的转换和计算来实现的。

二、浮点数减法的运算规则1.符号位规则:如果两个浮点数的符号位相同(均为0 或1),则它们可以进行正常的减法运算;如果符号位不同(一个为0,一个为1),则表示两个数不能进行减法运算,或者需要进行特殊处理。

2.阶码规则:在减法运算中,需要将两个数的阶码进行相应的调整,以保证计算结果的精度。

具体的调整方法取决于计算机系统的设计。

3.尾数规则:尾数是浮点数中表示小数部分的部分。

在减法运算中,需要将两个数的尾数进行对齐,然后按位相减。

如果相减结果的位数超过了尾数的表示范围,还需要进行溢出处理。

三、浮点数减法的精度问题由于计算机内部采用二进制表示法,浮点数减法可能会出现精度损失的问题。

例如,当两个数的尾数部分相差较大时,按位相减可能会导致结果的精度降低。

为了解决这个问题,可以采用一定的数值修约方法,如四舍五入、截断等。

四、浮点数减法的实际应用浮点数减法在实际应用中具有广泛的应用,例如在数值计算、图像处理、物理模拟等领域。

在这些应用中,浮点数减法往往需要高效、精确地进行,因此需要采用一定的算法和技巧来优化计算过程。

总之,浮点数减法是计算机中一种基本的数值运算,具有一定的复杂性和精度问题。

浮点数运算分析

浮点数运算分析浮点数的加减运算浮点数的加减运算一般由以下五个步骤完成:对阶↓尾数运算↓结果规格化↓舍入处理↓溢出判断设两浮点数X、Y进行加减运算,其中X=Mx·2Ex,Y=My·2Ey1. 对阶所谓对阶是指将两个进行运算的浮点数的阶码对齐的操作。

对阶的目的是为使两个浮点数的尾数能够进行加减运算。

因为,当进行Mx·2Ex与My·2Ey加减运算时,只有使两浮点数的指数值部分相同,才能将相同的指数值作为公因数提出来,然后进行尾数的加减运算。

对阶的具体方法是:首先求出两浮点数阶码的差,即⊿E=Ex-Ey,将小阶码加上⊿E,使之与大阶码相等,同时将小阶码对应的浮点数的尾数右移相应位数,以保证该浮点数的值不变。

几点注意:(1)对阶的原则是小阶对大阶,之所以这样做是因为若大阶对小阶,则尾数的数值部分的高位需移出,而小阶对大阶移出的是尾数的数值部分的低位,这样损失的精度更小。

(2)若⊿E=0,说明两浮点数的阶码已经相同,无需再做对阶操作了。

(3)采用补码表示的尾数右移时,符号位保持不变。

(4)由于尾数右移时是将最低位移出,会损失一定的精度,为减少误差,可先保留若干移出的位,供以后舍入处理用。

2. 尾数运算尾数运算就是进行完成对阶后的尾数相加减。

这里采用的就是我们前面讲过的纯小数的定点数加减运算。

3. 结果规格化在机器中,为保证浮点数表示的唯一性,浮点数在机器中都是以规格化形式存储的。

对于IEEE754标准的浮点数来说,就是尾数必须是1.M的形式。

由于在进行上述两个定点小数的尾数相加减运算后,尾数有可能是非规格化形式,为此必须进行规格化操作。

规格化操作包括左规和右规两种情况。

左规操作:将尾数左移,同时阶码减值,直至尾数成为1.M的形式。

例如,浮点数0.0011·25是非规格化的形式,需进行左规操作,将其尾数左移3位,同时阶码减3,就变成1.1100·22规格化形式了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

左规操作:将尾数左移,同时阶码减值,直至尾数成为1.M的形式。例如,浮点数0.0011·25是非规格化的形式,需进行左规操作,将其尾数左移3位,同时阶码减3,就变成1.1100·22规格化形式了。

右规操作:将尾数右移1位,同时阶码增1,便成为规格化的形式了。要注意的是,右规操作只需将尾数右移一位即可,这种情况出现在尾数的最高位(小数点前一位)运算时出现了进位,使尾数成为10.xxxx或11.xxxx的形式。例如,10.0011·25右规一位后便成为1.00011·26的规格化形式了。

=1.10111000100000000000000×25

结果的IEEE754标准存储格式为:0 10000100 10111000100000000000000

实现浮点运算的加法器逻辑电路原理框图如图2-11所示。

图2-11 浮点运算加法器

(4)朝0舍入(round toward 0)

即简单地截断舍去,而不管多余位是什么值。这种方法实现简单,但容易形成累积误差,且舍入处理后的值总是向下偏差。

5. 溢出判断

与定点数运算不同的是,浮点数的溢出是以其运算结果的阶码的值是否产生溢出来判断的。若阶码的值超过了阶码所能表示的最大正数,则为上溢,进一步,若此时浮点数为正数,则为正上溢,记为+∞,若浮点数为负数,则为负上溢,记为-∞;若阶码的值超过了阶码所能表示的最小负数,则为下溢,进一步,若此时浮点数为正数,则为正下溢,若浮点数为负数,则为负下溢。正下溢和负下溢都作为0处理。

图中,三个寄存器R0、R1和R2分别存放两个参加运算的浮点数和结果。第一步对阶,首先由⊿E加法器求出两个浮点数阶码的差值,然后由控制电路控制选择小阶码浮点数的尾数进入右移寄存器进行对阶时的右移,右移结果送入尾数加法器的一个输入端,大阶码浮点数的尾数则直接送入加法器的另一个输入端;第二步尾数相加减;第三步规格化,由尾数加法器产生的结果经规格化部件,一方面送移位寄存器进行尾数移位,另一方面控制选择大阶码进行阶码的增或减操作;第四步由舍入部件对规格化后的尾数进行舍入处理,并将结果送结果寄存器的尾数字段;第五步溢出处理,由溢出判别部件对规格化后的阶码进行溢出判别,若未溢出,则将结果送结果寄存器的阶码部分。

(1)对阶

⊿E=Ex-Ey=3-5=-2

x=1.01101100000000000000000×23=0.010110110000000000000000000×25

(2)尾数相加

x+y=0.010110110000000000000000000×25+1.01011101100000000000000×25

对于浮点数y:

符号位S=0

指数e=E-127=10000100-01111111=00000011=(5)10

尾数m=1.M=1.01011101100000000000000=1.010111011

于是有

y=(-1)s×m×2e =+1.01011101100000000000000×25

求X※Y

解:[X]浮: 0 1 010 1100110

[Y]浮: 0 0 110 1101101

第一步:阶码相加

[Ex+Ey]移=[Ex]移+[Ey]补=1 010+1 110=1 000

1 000为移码表示的0

第二步:原码尾数相乘的结果为:

0 10101101101110

(2)朝+∞舍入(round toward +∞) 对正数来说,只要多余位不为全0,则向尾数最低有效位进1;对负数来说,则是简单地舍去。

(3)朝-∞舍入(round toward -∞) 与朝+∞舍入方法正好相反,对正数来说,只是简单地舍去;对负数来说,只要多余位不为全0,则向尾数最低有效位进1。

(2)若⊿E=0,说明两浮点数的阶码已经相同,无需再做对阶操作了。

(3)采用补码表示的尾数右移时,符号位保持不变。

(4)由于尾数右移时是将最低位移出,会损失一定的精度,为减少误差,可先保留若干移出的位,供以后舍入处理用。

2. 尾数运算

尾数运算就是进行完成对阶后的尾数相加减。这里采用的就是我们前面讲过的纯小数的定点数加减运算。

对阶的具体方法是:首先求出两浮点数阶码的差,即⊿E=Ex-Ey,将小阶码加上⊿E,使之与大阶码相等,同时将小阶码对应的浮点数的尾数右移相应位数,以保证该浮点数的值不变。几点注意:

(1)对阶的原则是小阶对大阶,之所以这样做是因为若大阶对小阶,则尾数的数值部分的高位需移出,而小阶对大阶移出的是尾数的数值部分的低位,这样损失的精度更小。

2、浮点乘除法的运算步骤

①阶码运算:阶码求和(乘法)或阶码求差(除法)

即 [Ex+Ey]移= [Ex]移+ [Ey]补

[Ex-Ey]移= [Ex]移+ [-Ey]补

②浮点数的尾数处理:浮点数中尾数乘除法运算结果要进行舍入处理

例题:X=0 .0110011*211,Y=0.1101101*2-10

4. 舍入处理

浮点运算在对阶或右规时,尾数需要右移,被右移出去的位会被丢掉,从而造成运算结果精度的损失。为了减少这种精度损失,可以将一定位数的移出位先保留起来,称为保护位,在规格化后用于舍入处理。

IEEE754标准列出了四种可选的舍入处理方法:

ห้องสมุดไป่ตู้

(1)就近舍入(round to nearest) 这是标准列出的默认舍入方式,其含义相当于我们日常所说的“四舍五入”。例如,对于32位单精度浮点数来说,若超出可保存的23位的多余位大于等于100…01,则多余位的值超过了最低可表示位值的一半,这种情况下,舍入的方法是在尾数的最低有效位上加1;若多余位小于等于011…11,则直接舍去;若多余位为100…00,此时再判断尾数的最低有效位的值,若为0则直接舍去,若为1则再加1。

要注意的是,浮点数的表示范围和补码表示的定点数的表示范围是有所不同的,定点数的表示范围是连续的,而浮点数的表示范围可能是不连续的。如下图2-10示。

【例2.25】设两浮点数的IEEE754标准存储格式分别为

x=0 10000010 01101100000000000000000,y=0 10000100 01011101100000000000000,求x+y,并给出结果的IEEE754标准存储格式。

第三步:规格化处理:已满足规格化要求,不需左规,尾数不变,阶码不变。

第四步:舍入处理:按舍入规则,加1进行修正

所以 X※Y= 0.1010111※2+000

浮点数的加减运算

浮点数的加减运算一般由以下五个步骤完成:

对阶

↓

尾数运算

↓

结果规格化

↓

舍入处理

↓

溢出判断

设两浮点数X、Y进行加减运算,其中

X=Mx·2Ex,Y=My·2Ey

1. 对阶

所谓对阶是指将两个进行运算的浮点数的阶码对齐的操作。对阶的目的是为使两个浮点数的尾数能够进行加减运算。因为,当进行Mx·2Ex与My·2Ey加减运算时,只有使两浮点数的指数值部分相同,才能将相同的指数值作为公因数提出来,然后进行尾数的加减运算。

解:对于浮点数x:

符号位S=0

指数e=E-127=10000010-01111111=00000011=(3)10

尾数m=1.M=1.01101100000000000000000=1.011011

于是有

x=(-1)s×m×2e =+1.01101100000000000000000×23

3. 结果规格化

在机器中,为保证浮点数表示的唯一性,浮点数在机器中都是以规格化形式存储的。对于IEEE754标准的浮点数来说,就是尾数必须是1.M的形式。由于在进行上述两个定点小数的尾数相加减运算后,尾数有可能是非规格化形式,为此必须进行规格化操作。

规格化操作包括左规和右规两种情况。