阎石数电第四版课后习题答案详解第四章答案

数字电子技术基础(第四版)阎石第4章

CP S R Qn Qn1

0 t

0

0 1 1

X

X 0 0

X

X 0 0

0

1 0 1

0

1 0 1

RD

0 S 0 R 0 Q 0 t t

1

1 1 1 1 1

1

1 0 0 1 1

0

0 1 1 1 1

0

1 0 1 0 1

1

1 0 0 1* 1*

t

Q

0

t

在CLK

1期间,Q和Q可能随S、R潍坊学院 信息与控制工程学院 变化多次翻转

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

主从SR触发器的 表4.2.4 特性表如表4.2.4所示, CP S R 和电平触发的SR触发 × × × 器相同,只是CP作用 0 0 的时间不同

0 0 0 1 0 1 1 0 0 1 1

Q × 0 1 0 1 0 1 0 1

Q* Q 0 1 0 0 1 1 1* 1*

0

1 1 1 0 0 0* 0*

S D和R D同时为0 Q ,Q同为 1

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

4.2.2 同步RS触发器的电路结构与动作特点

在数字系统中,常常要求某些触发器在同一时刻动作,这 就要求有一个同步信号来控制,这个控制信号叫做时钟信号 (Clock pulse),简称时钟,用CP表示。这种受时钟控制的 触发器统称为时钟触发器。 一、电路结构与工作原理 图5.3.1所示为电平触发SR触发器(同步SR触发器)的基 本电路结构及图形符号。

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

2. 主从 JK触发器 为解除约束 即使出现 S R 1的情况下, Q n 1也是确定的

《数字电子技术基础》第四章习题答案

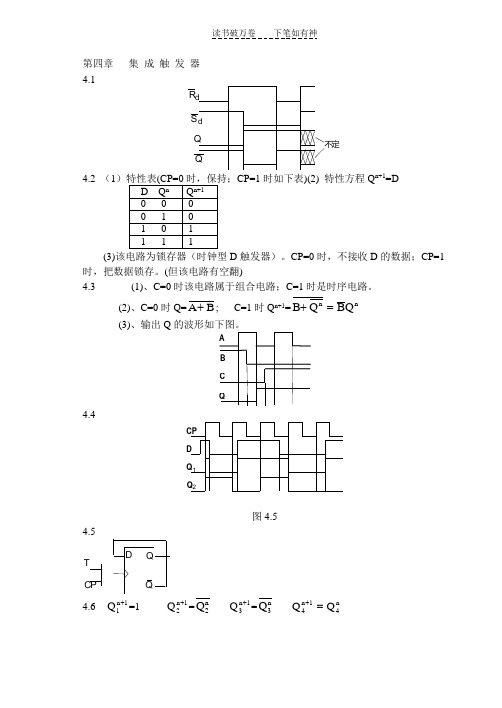

第四章 集 成 触 发 器 4.1R d S d Q Q不定4.2 (1CP=1时如下表)(2) 特性方程Q n+1=D(3)该电路为锁存器(时钟型D 触发器)。

CP=0时,不接收D 的数据;CP=1时,把数据锁存。

(但该电路有空翻)4.3 (1)、C=0时该电路属于组合电路;C=1时是时序电路。

(2)、C=0时Q=A B +; C=1时Q n+1=B Q BQ nn+= (3)、输出Q 的波形如下图。

A B C Q4.4CP D Q 1Q 2图4.54.5 DQ QCPT4.6 Q 1n 1+=1 Q 2n 1+=Q 2n Q n 13+=Q n 3 Q Q 4n 14n+=Q1CP Q2Q3Q44.7 1、CP 作用下的输出Q 1 Q 2和Z 的波形如下图; 2、Z 对CP 三分频。

DQ QCPQ1DQ QQ2ZRd CP Q1Q2Z14.8由Q D J Q KQ J Q KQ n 1n n n n +==+=⋅得D 触发器转换为J-K 触发器的逻辑图如下面的左图;而将J-K 触发器转换为D 触发器的逻辑图如下面的右图CPD Q QJKQ QDQ QJ KCP4.9CP B CA4.10CP X Q1Q2Z4.11 1、555定时器构成多谐振荡器 2、u c, u o 1, u o 2的波形u c u o 1u o 2t t t 1.67V3.33V3、u o 1的频率f 1=1074501316..H z ⨯⨯≈ u o 2的频率f 2=158H z4、如果在555定时器的第5脚接入4V 的电压源,则u o 1的频率变为1113001071501232....H z ⨯⨯+⨯⨯≈4.12 图(a)是由555定时器构成的单稳态触发电路。

1、工作原理(略);2、暂稳态维持时间t w =1.1RC=10ms(C 改为1μF);3、u c 和u o 的波形如下图:u ou ct t tu i (ms)(ms)(ms)5 10 25 30 45 503.33V4、若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路4.13由555定时器构成的施密特触发器如图(a)所示 1、电路的电压传输特性曲线如左下图; 2、u o 的波形如右下图;3、为使电路能识别出u i 中的第二个尖峰,应降低555定时器5脚的电压至3V 左右。

数字电子技术基础(第四版)-第4章-组合逻辑电路解析

1

Y (Y1Y2Y3) ' (( AB) '(BC) '( AC) ') '

2

Y AB BC AC

9

最简与或 表达式

3

真值表

4

电路的逻 辑功能

Y AB BC AC

3

ABC 000 001 010 011 100 101 110 111

Y

当输入A、B、

0

C中有2个或3

第四章 组合逻辑电路

学习要点

了解组合逻辑电路的特点和工作原理。 掌握组合逻辑电路的分析、设计方法。 了解组合逻辑电路中的竞争冒险现象。

1

4.1 概 述

2

数字电路

组合逻辑电路:t时刻输出仅与t时刻 输入有关,与t以前的 状态无关。

时序逻辑电路:t时刻输出不仅与t时刻 输入有关,还与电路过 去的状态有关。

编码器:把指令或状态等转换为与其对应 的二进制信息代码的电路。

普通编码器 优先编码器

22

23

一、二进制编码器

设:编码器有M个输入,在这M个输入中, 只有一个输入为有效电平,其余M-1个输入 均为无效电平。有N个输出。则二者之间满 足M≤2N的关系。

二进制编码器——将一般信号编为二进制代 码的电路。

Y F( A)

5

组合电路的特点: 1. 输出仅由输入决定,与电路之前状态无关; 2. 电路结构中无反馈环路(无记忆); 3. 能用基本门构成,即任何组合逻辑电路都能

用三种基本门实现。

6

4.2 组合逻辑电路的 分析和设计

7

4.2.1 组合逻辑电路的分析

8

逻辑图 例1:

1

逻辑表 达式

数字电子技术基础教材第四章答案

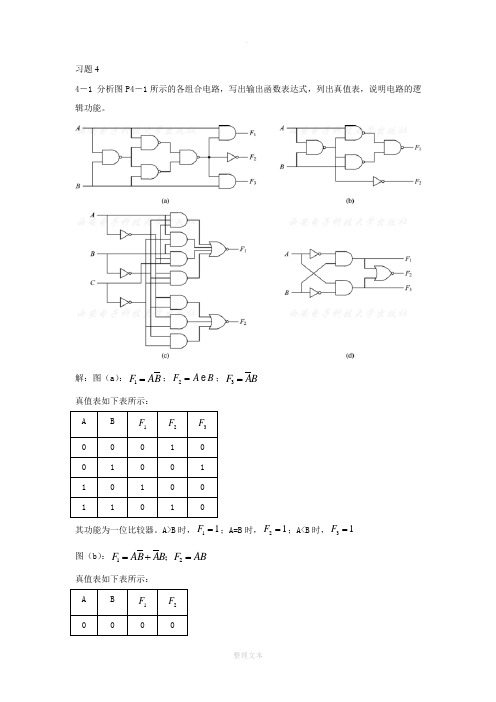

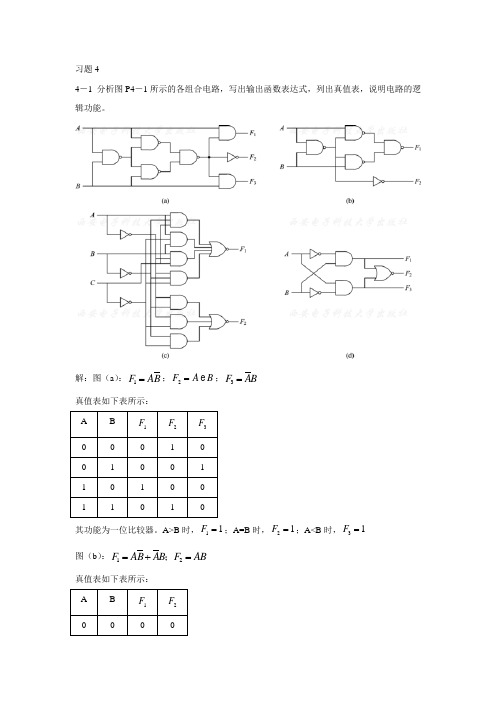

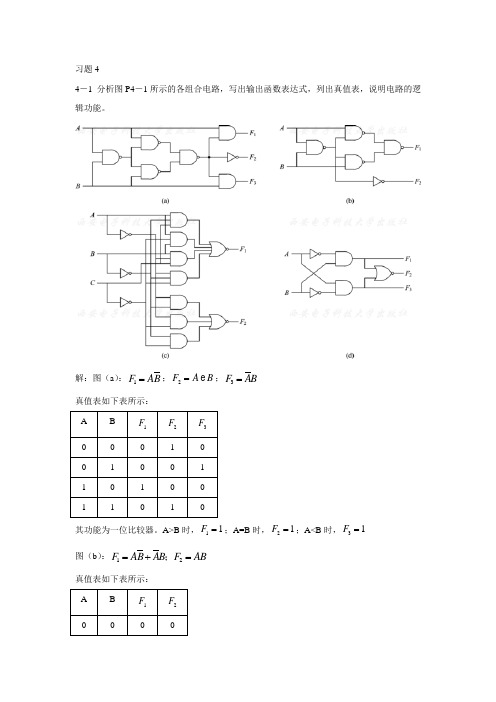

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

试列表说明电路在,,,得各种取值组合下F与A,B得逻辑关系。

解:,功能如下表所示,两个变量有四个最小项,最多可构造种不同得组合,因此该电路就是一个能产生十六种函数得多功能逻辑运算器电路。

4-5 已知某组合电路得输出波形如图P4-5所示,试用最少得或非门实现之。

解:电路图如下:4-6 用逻辑门设计一个受光,声与触摸控制得电灯开关逻辑电路,分别用A,B,C表示光,声与触摸信号,用F表示电灯。

灯亮得条件就是:无论有无光,声信号,只要有人触摸开关,灯就亮;当无人触摸开关时,只有当无关,有声音时灯才亮。

试列出真值表,写出输出函数表达式,并画出最简逻辑电路图。

解:根据题意,列出真值表如下:由真值表可以作出卡诺图,如下图:C AB 00 10 11 100 1由卡诺图得到它得逻辑表达式为: 由此得到逻辑电路为:4-7 用逻辑门设计一个多输出逻辑电路,输入为8421BCD 码,输出为3个检测信号。

阎石数电第四版课后习题答案详解数字信号处理指导书-修订版

实验一卷积运算1. 实验目的(1) MATLAB中序列的表示;(2) 序列的图形显示;(3) 序列的卷积计算。

2. 实验原理与方法(1) 信号在MATLAB中的表示方法MATLAB中用两个参数向量来表示有限长序列x(n),一个是x(n)中各点的样值向量,一个是各点的位置向量。

两个向量长度相等,假设位置向量的第m 个元素的值为k,则样值向量的第m个元素的值即为x(k)。

(2) 序列的图形显示MATLAB中可调用stem函数来显示序列,其具体形式为:stem(X,Y)stem(...,'fill')stem(...,LineSpec)(3) 序列的卷积运算卷积和是离散信号与系统分析的有效方法和工具,两个序列x(n)和h(n)的卷积和定义为:∑∞-∞=== =mmnhmxnhnxny)()()(*)()(利用MATLAB求离散序论卷积和的专用函数conv可以实现离散信号卷积和的计算。

其具体形式为:w = conv(u,v)3. 实验内容及步骤(1) 熟悉MATLAB造作环境,复习时域离散信号和系统的相关知识。

(2) 编写实验程序,产生以下序列并显示其图形:14234()()403()347()cos4()sin 8x n R n n n x n n n x n n x n n ππ=-≤≤⎧⎪=-≤≤⎨⎪⎩== (3) 编制程序,计算x 2(n)*x 1(n)、x 3(n)*x 1(n)、x 4(n)*x 1(n),并显示其计算结果。

(4) 手动计算上述卷积和,并与程序运行结果进行比较。

4.实验方式及要求每人一台安装有Matlab7.0的计算机,在计算机上编程仿真。

一人一组,独立完成。

5. 思考题脚本文件与函数文件编写上有什么区别?二者用法上有什么区别?6. 实验报告要求(1) 简述实验目的及实验原理。

(2) 按实验步骤附上实验过程中离散序列的时域波形,并对所得结果进行分析和解释。

(3) 总结实验中的主要结论。

数字电子技术基础(第四版)课后习题答案_第四章

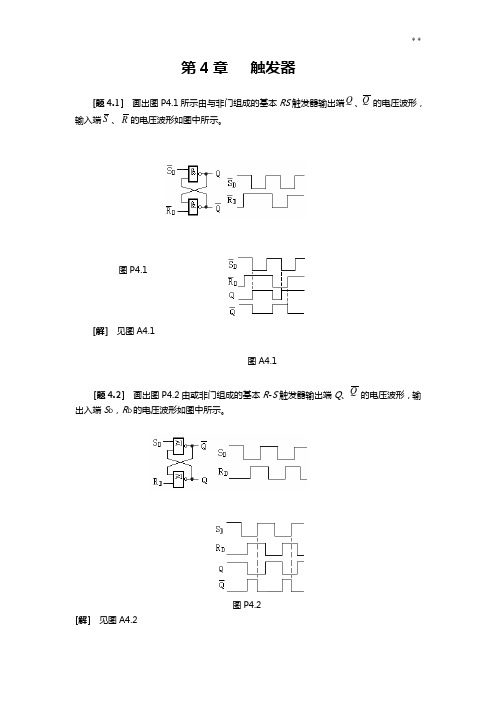

第4章触发器[题4.1]画出图P4.1所示由与非门组成的根本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的根本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3]试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3 [解]:图P4.3所示电路的真值表S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解] 见图A4.4图A4.4[题4.5] 在图P4.5电路中,假设CP 、S 、R 的电压波形如图中所示,试画出Q 和Q 端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图P4.5[解]见图A4.5图A4.5[题4.6]假设将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP 信号作用下Q和Q端的电压波形。

己知CP信号的宽度t w = 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]假设主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7[题4.8]假设主从结构RS触发器的CP、S、R、DR各输入端的电压波形如图P4.8所示,1DS。

数字电子技术基础教材第四章答案

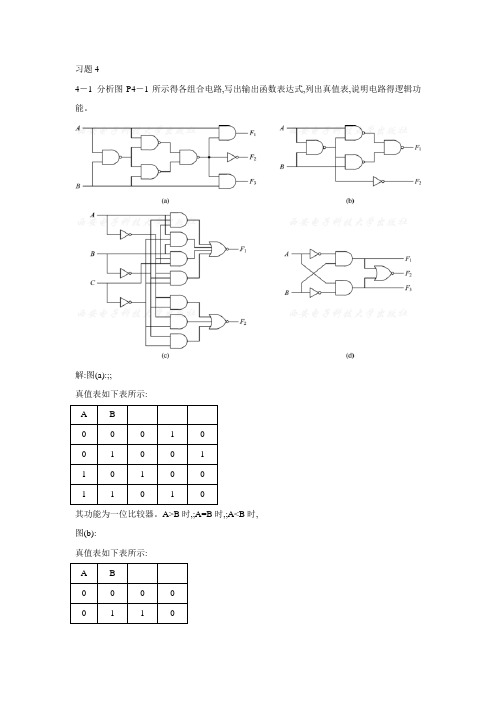

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F AB =;2F A B =e ;3F AB = 真值表如下表所示: A B 1F2F3F0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 111其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示: A B 1F2F功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,3,5,6)(1,2,4,7)F M m ==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F AB =;2F A B =e ;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:1A0AF0 0 0x 0 1 1x1 0 2x 1 13x4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下:3x2x1x0x3Y2Y1Y0YM=10 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 1 0 0 1 0 1 0 1 1 1 0 1 1 0 0 1 0 1 01 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 1 1 0 0 1 1 1 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 0 1 11111 0 1 1 0 0 1 1 1 1 0 1 0 1 1 111111由此可得:1M =当时,33232121010Y x Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

数字电子技术基础+阎石第四版课后习题答案详解

I

OL (max) 2I IL

=

16 2 ×1.6

=

5

N

高=

I

OH (max) 2I IH

=

0.4 2 × 0.04

=

5

∴ 最多能驱动5个相同的或非门

2.7 解:根据公式:

R L (max)

=

Vcc − VOH nI OH + mI IH

= 5 − 3.2 = 5K 3× 0.1 + 3× 0.02

= 0.08mA

(2)把 OC 门换成 TTL 门时, 若门输出为低电平时两者相同,无影响; 但输出高电平时两者截然不同,OC 门向内流进(漏电流), 而 TTL 的电流是向外流出,IB=IRB+IOH ,IOH 为 TTL 输出高电平时的输出电流。 由输出特性曲线知:当 VOH 下降到 0.7V 时,IOH 相当大,IC 也很大,会烧毁三极管。

(1)(17)10=(10001)2=(11)16

(3) (0.39)10 = (0.0110 0011 1101 0111 0000 1010)2 = (0.63 D70A )16

1.8 用公式化简逻辑函数

(2)(127)10=(1111111)2=(7F)16

(4) (25.7)10 = (11001.1011 0011)2 = (19.B3)16

输出为高电平时:Vo

=

⎜⎜⎝⎛

Vcc − Vo RL

+ iL ⎟⎟⎠⎞ × 0.01 = 0.05 + 0.01iL

2.13 解:

1)

对74系列:

5V

−VBE − Vo1 R1 + R

⋅

R

+ Vo1

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:A B0 0 0 1 00 1 0 0 11 0 1 0 01 1 0 1 0其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:A B0 0 0 00 1 1 0功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:0 00 11 01 14-3 图P4-3就是一个受M控制得代码转换电路,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:M=1 0 0 0 0 0 0 0 00 0 0 1 0 0 0 10 0 1 0 0 0 1 10 0 1 1 0 0 1 00 1 0 0 0 1 1 00 1 0 1 0 1 1 10 1 1 0 0 1 0 10 1 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 11 0 0 1 1 1 1 01 0 1 0 1 1 0 01 0 1 1 1 1 0 11 1 0 0 1 0 0 01 1 0 1 1 0 0 11 1 1 0 1 0 1 11 1 1 1 1 0 1 0由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

数字电路第四章答案

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

数字电子技术基础试题及答案1-阎石第四版

(4)逻辑功能为:全加器。 3. 1)据逻辑图写出电路的驱动方程:

T0 1

T1 Q0

T2 Q0Q1

2)求出状态方程:

Q n1 0

Q0

T3 Q0Q1 Q2

Qn1 1

Q0 Q1

Q0Q1

Qn1 2

Q0Q1 Q2

Q0Q1Q2

Qn1 3

Q0Q1Q2 Q3

Q0Q1Q2Q3

3)写出输出方程:C= Q0Q1Q2Q3

A

&

B

&

&

Y

C

&

2.试分析如图 3 所示的组合逻辑电路。 (15 分) 1). 写出输出逻辑表达式; 2). 化为最简与或式; 3). 列出真值表; 4). 说明逻辑功能。

3. 七、分析如下时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出 电路的状态转换图。(20)

图4

4.74161组成的电路如题37图所示,分析电路,并回答以下问题 (1)画出电路的状态转换图(Q3Q2Q1Q0); (2)说出电路的功能。(74161的功能见表)

B. 1011--0101--0010--0001--0000

C. 1011--1100--1101--1110--1111

D. 1011--1010--1001--1000--0111

5.已知 74LS138 译码器的输入三个使能端(E1=1, E2A = E2B=0)时,地址码 A2A1A0=011,

4)列出状态转换表或状态转换图或时序图:

5) 从以上看出,每经过 16 个时钟信号以后电路的状态循环变化一次;同时,每经过 16 个时钟脉冲作用后输出端 C 输出一个脉冲,所以,这是一个十六进制记数器,C 端的输 出就是进位。

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F A B =;2F A B =;3F AB =真值表如下表所示:其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示:功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,35,6)(124,7)F M m==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F A B =;2F A B =;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下:由此可得:1M =当时,3323212101Y x Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

0M =当时,332321321210321010Y x Y x x Y x x x Y x Y x x x x Y x =⎧⎪=⊕⎪⎨=⊕⊕=⊕⎪⎪=⊕⊕⊕=⊕⎩ 完成格雷码至二进制的转换。

数字电子技术基本(第四版)课后知识题目解析第四章

第4章触发器[题4.1]画出图P4.1所示由与非门组成的基本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的基本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3] 试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3[解]S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解]见图A4.4图A4.4[题4.5]在图P4.5电路中,若CP、S、R的电压波形如图中所示,试画出Q和Q端与之对应的电压波形。

假定触发器的初始状态为Q=0。

图P4.5[解]见图A4.5图A4.5[题4.6]若将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP 信号作用下Q和Q端的电压波形。

己知CP信号的宽度t w = 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]若主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q 端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7[题4.8]若主从结构RS触发器的CP、S、R、D R各输入端的电压波形如图P4.8所S。

试画出Q、Q端对应的电压波形。

示,1D图P4.8[解] 见图A4.8图A4.8[题4.9]已知主从结构JK触发器输入端J、K和CP的电压波形如图P4.9所示,试画出Q、Q端对应的电压波形。

(完整版)数字电子技术第四章答案

习题44-1 分析图P4-1所示的各组合电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

解:图(a ):1F AB =;2F A B =e ;3F AB = 真值表如下表所示: A B 1F2F3F0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 111其功能为一位比较器。

A>B 时,11F =;A=B 时,21F =;A<B 时,31F = 图(b ):12F AB AB F AB =+=; 真值表如下表所示: A B 1F2F功能:一位半加器,1F 为本位和,2F 为进位。

图(c ):1(0,3,5,6)(1,2,4,7)F M m ==∑∏2(0,1,2,4)(3,5,6,7)F M m ==∑∏真值表如下表所示:功能:一位全加器,1F 为本位和,2F 为本位向高位的进位。

图(d ):1F AB =;2F A B =e ;3F AB =功能:为一位比较器,A<B 时,1F =1;A=B 时,2F =1;A>B 时,3F =14-2 分析图P4-2所示的组合电路,写出输出函数表达式,列出真值表,指出该电路完成的逻辑功能。

解:该电路的输出逻辑函数表达式为:100101102103F A A x A A x A A x A A x =+++因此该电路是一个四选一数据选择器,其真值表如下表所示:1A0AF0 0 0x 0 1 1x 1 0 2x 1 13x4-3 图P4-3是一个受M 控制的代码转换电路,当M =1时,完成4为二进制码至格雷码的转换;当M =0时,完成4为格雷码至二进制的转换。

试分别写出0Y ,1Y ,2Y ,3Y 的逻辑函数的表达式,并列出真值表,说明该电路的工作原理。

解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下: 3x2x1x0x3Y2Y1Y0YM=10 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 1 0 0 1 0 1 0 1 1 1 0 1 1 0 0 1 0 1 01 1 0 0 1 0 0 M=0 1 0 0 0 1 1 1 1 1 0 0 1 1 1 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 0 1 1 1 0 0 1 0 0 0 1 1 0 1 1 0 0 1 1 1 1 0 1 0 1 1 111111由此可得:1M =当时,33232121010Y x Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

电路 第四版 答案(第四章)

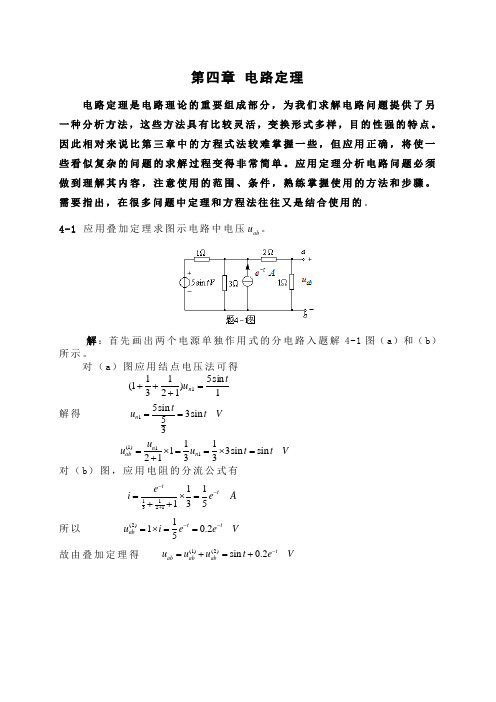

第四章 电路定理电路定理是电路理论的重要组成部分,为我们求解电路问题提供了另一种分析方法,这些方法具有比较灵活,变换形式多样,目的性强的特点。

因此相对来说比第三章中的方程式法较难掌握一些,但应用正确,将使一些看似复杂的问题的求解过程变得非常简单。

应用定理分析电路问题必须做到理解其内容,注意使用的范围、条件,熟练掌握使用的方法和步骤。

需要指出,在很多问题中定理和方程法往往又是结合使用的。

4-1 应用叠加定理求图示电路中电压ab u 。

解:首先画出两个电源单独作用式的分电路入题解4-1图(a )和(b )所示。

对(a )图应用结点电压法可得1sin 5)121311(1tu n =+++ 解得 15sin 3sin 53n tu t V == (1)111113sin sin 2133n ab n u u u t t V =⨯==⨯=+对(b )图,应用电阻的分流公式有1132111135tt e i e A --+=⨯=++所以 (2)110.25t t abu i e e V --=⨯== 故由叠加定理得 (1)(2)s i n 0.2ta b a b a b u u u t e V -=+=+4-2 应用叠加定理求图示电路中电压u 。

解:画出电源分别作用的分电路如题解(a )和(b )所示。

对(a )图应用结点电压法有105028136)101401281(1++=+++n u 解得 (1)113.650.10.0250.1n u u +==++18.624882.6670.2253V ===对(b )图,应用电阻串并联化简方法,可求得10402(8)32161040331040183(8)21040si u V ⨯⨯++=⨯=⨯=⨯+++ (2)16182323si u u V -==-⨯=- 所以,由叠加定理得原电路的u 为(1)(2)24888033u u u V =+=-= 4-3 应用叠加定理求图示电路中电压2u 。