第5章 状态机

第5章 VHDL 状态机

(reg_floor=curr_floor) (req_floor<curr_floor) (req_floor>curr_floor /direction:=idle /direction:=down /direction:=up (req_floor<curr_floor) (req_floor>curr_floor) /direction:=down /direction:=up 下降 空停 上升 (req_floor=curr_floor) (req_floor=curr_floor) /direction:=idle /direction:=idle (req_floor<curr_floor)/direction:=up (req_floor<curr_floor)/direction:=down 状态机描述 (b)

TYPE st1 IS ARRAY ( 0 TO 15 ) OF STD_LOGIC ; TYPE week IS (sun,mon,tue,wed,thu,fri,sat) ; , , , , , , TYPE m_state IS ( st0,st1,st2,st3,st4,st5 ) ; , , , , , : m_state ;

SIGNAL present_state,next_state ,

TYPE BOOLEAN IS (FALSE,TRUE) ; ,

5.1 状态机设计相关语句 5.1.1 类型定义语句 TYPE my_logic IS ( '1' ,'Z' ,'U' ,'0' ) ;

SIGNAL s1 : my_logic ; s1 <= 'Z' ; SUBTYPE 子类型名 IS 基本数据类型 RANGE 约束范围 约束范围; SUBTYPE digits IS INTEGER RANGE 0 to 9 ;

第五章 (10)LALR(1)分析方法

13

LaR• #

状态4和状态12 状态5和状态8 状态9和状态1113 状态10和状态13

注: 无冲突状态的LR(1)活前缀状态机合并同心状 态后得到的LALR(1)活前缀状态机可能存在冲突 状态:

可能产生归约—归约冲突,但是不可能产生移 入—归约冲突.

14

例如,假定Si、Sj是某一LR(1)状态机的两个状态,

RL• #

a

5 La•R # =

b R•L # =

L•aR # = L•b # =

RL

11 RL• # =

6

SL= • R #

R • L #

L•aR #

L•b

#

b

a

8 La•R # R•L # L•aR # L•b #

b

12 Lb• #

7 SL=R • #

R L

9

a RL• # L

R

13 LaR• #

3

LALR(1)方法

它具有SLR(1)的状态数少的优点和LR(1) 的适用范围广的优点.

LALR(1)方法的功能介于SLR(1)和LR(1) 之间.

LALR(1)状态机的状态个数和LR(0)状态 机的状态个数相同,而其展望符则即不 采用SLR(1)的Follow集方法,也不采用 LR(1)的完全精确法.

Si

A•

u1

B•

v1

C•a

t1

Sj

A•

u2

B•

v2

C•a

t2

其中,u1、u2、v1、v2、t1、t2分别为归约展望符集 , aVT.

在Si中有: u1v1=、u1{a}=、v1{a}=;

在Sj中有: u2v2=、u2{a}=、v2{a}=.

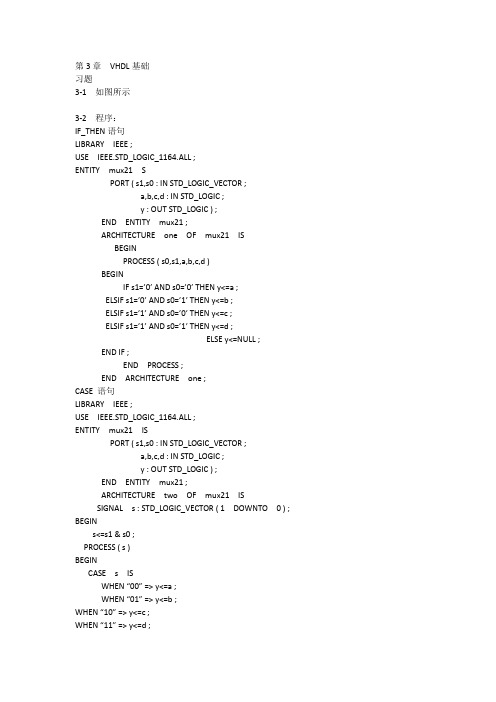

2023年大学_EDA技术与VHDL第二版(潘松著)课后习题答案下载

2023年EDA技术与VHDL第二版(潘松著)课后习题答案下载EDA技术与VHDL第二版(潘松著)课后答案下载第1章 EDA技术概述1.1 EDA技术及其发展1.1.1 EDA技术的发展1.1.2 EDA技术的涵义1.1.3 EDA技术的基本特征1.2 EDA技术的主要内容及主要的EDA厂商1.2.1 EDA技术的主要内容1.2.2 主要EDA厂商概述1.3 EDA技术实现目标1.3.1 超大规模可编程逻辑器件1.3.2 半定制或全定制ASIC1.3.3 混合ASIC1.4 EDA技术应用1.4.1 EDA技术应用形式1.4.2 EDA技术应用场合1.5 EDA技术的发展趋势1.5.1 可编程器件的发展趋势1.5.2 软件开发工具的发展趋势1.5.3 输入方式的发展趋势__小结思考题和习题第2章大规模可编程逻辑器件2.1 可编程逻辑器件概述2.1.1 PLD的'发展进程2.1.2 PLD的种类及分类方法2.2 简单可编程逻辑器件2.2.1 PLD电路的表示方法及有关符号 2.2.2 PROM基本结构2.2.3 PLA基本结构2.2.4 PAL基本结构2.2.5 GAL基本结构2.3 复杂可编程逻辑器件2.3.1 CPLD基本结构2.3.2 Altera公司器件2.4 现场可编程逻辑器件2.4.1 FPGA整体结构2.4.2 Xilinx公司FPGA器件2.5 在系统可编程逻辑器件2.5.1 ispLSl/pLSl的结构2.5.2 Lattice公司ispLSI系列器件 2.6 FPGA和CPLD的开发应用2.6.1 CPLD和FPGA的编程与配置2.6.2 FPGA和CPLD的性能比较2.6.3 FPGA和CPLD的应用选择__小结思考题和习题第3章 EDA设计流程与开发3.1 EDA设计流程3.1.1 设计输入3.1.2 综合3.1.3 适配3.1.4 时序仿真与功能仿真3.1.5 编程下载3.1.6 硬件测试3.2 ASIC及其设计流程3.2.1 ASIC设计方法3.2.2 一般的ASIC设计流程3.3 可编程逻辑器件的开发环境 3.4 硬件描述语言3.5 IP核__小结思考题和习题第4章硬件描述语言VHDL4.1 VHDL概述4.1.1 VHDL的发展历程4.1.2 VHDL的特点4.2 VHDL程序基本结构4.2.1 实体4.2.2 结构体4.2.3 库4.2.4 程序包4.2.5 配置4.3 VHDL基本要素4.3.1 文字规则4.3.2 数据对象4.3.3 数据类型4.3.4 运算操作符4.3.5 VHDL结构体描述方式 4.4 VHDL顺序语句4.4.1 赋值语句4.4.2 IF语句4.4.3 等待和断言语句4.4.4 cASE语句4.4.5 LOOP语句4.4.6 RETIARN语句4.4.7 过程调用语句4.4.8 REPORT语句4.5 VHDL并行语句4.5.1 进程语句4.5.2 块语句4.5.3 并行信号代人语句4.5.4 并行过程调用语句4.5.5 并行断言语句4.5.6 参数传递语句4.5.7 元件例化语句__小结思考题和习题第5章 QuartusⅡ软件及其应用5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件 5.1.2 创建工程5.1.3 编译前设计5.1.4 全程编译5.1.5 时序仿真5.1.6 应用RTL电路图观察器5.2 引脚设置和下载5.2.1 引脚锁定5.2.2 配置文件下载5.2.3 AS模式编程配置器件5.2.4 JTAG间接模式编程配置器件5.2.5 USBBlaster编程配置器件使用方法 __小结思考题和习题第6章 VHDL应用实例6.1 组合逻辑电路设计6.1.1 基本门电路设计6.1.2 译码器设计6.1.3 数据选择器设计6.1.4 三态门设计6.1.5 编码器设计6.1.6 数值比较器设计6.2 时序逻辑电路设计6.2.1 时钟信号和复位信号6.2.2 触发器设计6.2.3 寄存器和移位寄存器设计6.2.4 计数器设计6.2.5 存储器设计6.3 综合实例——数字秒表的设计__小结思考题和习题第7章状态机设计7.1 一般有限状态机7.1.1 数据类型定义语句7.1.2 为什么要使用状态机 7.1.3 一般有限状态机的设计 7.2 Moore型有限状态机设计 7.2.1 多进程有限状态机7.2.2 单进程有限状态机7.3 Mealy型有限状态机7.4 状态编码7.4.1 状态位直接输出型编码 7.4.2 顺序编码7.4.3 一位热码编码7.5 状态机处理__小结思考题和习题第8章 EDlA实验开发系统8.1 GW48型实验开发系统原理与应用8.1.1 系统性能及使用注意事项8.1.2 GW48系统主板结构与使用方法8.2 实验电路结构图8.2.1 实验电路信号资源符号图说明8.2.2 各实验电路结构图特点与适用范围简述8.3 GW48CK/GK/EK/PK2系统信号名与芯片引脚对照表 __小结思考题和习题第9章 EnA技术实验实验一:全加器的设计实验二:4位加减法器的设计实验三:基本D触发器的设计实验四:同步清零计数器的设计实验五:基本移位寄存器的设计串人/串出移位寄存器实验六:同步预置数串行输出移位寄存器的设计实验七:半整数分频器的设计实验八:音乐发生器的设计实验九:交通灯控制器的设计实验十:数字时钟的设计EDA技术与VHDL第二版(潘松著):内容简介《EDA技术与VHDL》主要内容有Altera公司可编程器件及器件的选用、QuartusⅡ开发工具的使用;VHDL硬件描述语言及丰富的数字电路和电子数字系统EDA设计实例。

状态机设计的一般步骤

状态机设计的一般步骤

设计状态机的一般步骤包括以下几个方面:

1. 确定需求,首先,需要明确状态机的设计目的和应用场景,包括需要处理的输入和产生的输出,以及系统所需的各种状态和状态转换条件。

2. 状态定义,根据需求,确定系统可能具有的各种状态,包括起始状态、中间状态和最终状态,对每个状态进行清晰准确的定义和描述。

3. 事件识别,识别触发状态转换的各种事件,包括外部输入、定时器到期、条件满足等,对每个事件进行详细的描述和分类。

4. 状态转换,确定状态之间的转换条件和转换规则,包括事件触发的条件、转换动作和目标状态,确保状态转换的合理性和完整性。

5. 状态机实现,根据上述设计,进行状态机的实现和编码,可以采用各种编程语言或专门的状态机工具,确保状态机的正确性和

可靠性。

6. 测试验证,对设计的状态机进行全面的测试和验证,包括正常输入、异常输入和边界条件的测试,确保状态机在各种情况下都能正确运行并产生预期的结果。

7. 优化改进,根据测试结果和实际应用情况,对状态机进行优化和改进,包括性能优化、功能扩展和错误修复,确保状态机能够持续稳定地运行。

总之,设计状态机的一般步骤包括需求确定、状态定义、事件识别、状态转换、状态机实现、测试验证和优化改进,通过严谨的设计和实现过程,确保状态机能够准确可靠地反映系统的运行逻辑和行为规则。

Stateflow入门教程

5. 添加注释:

如果需要在 Stateflow 的框图中使用 LaTex 字符集, 则需要按照下列步骤完成: (1) 在已经添加的文本上单击鼠标右键, 这时将显示快捷菜单; (2) 选择快捷菜单中 Text Format 子菜单中的 LaTex Instructions 复选项; (3) 用鼠标单击已经添加的文本注释, 重新进入文本编辑模式; (4) 添加 LaTex 字符, 例如键入 y ={\itAe}^{\alphax}sin(\beta\itt); (5) 在文本编辑区外单击鼠标完成注释的添加,此时的注释内 容将变为y = Aeax sin( bt) ,如图所示。

创建转移的具体步骤是: 形状。 (2) 按下鼠标左键并保持, 将引出的转移线拖放到目标状态的边缘即可,

给转移添加标签的方法:

(1) 左键单击选中相应的转移,此时转移将显示问号; (2) 左键单击出现的问号, 则进入文本编辑状态; (3) 在光标处插入文本; (4) 单击 Stateflow 编辑器中任意一处, 结束标签的插入。

如果用户设置事件的 Scope 属性为 Input from Simulink 或者 Output to Simulink,则添加事件的对话框会发生变化,

Trigger 属性:Trigger 属性总共有四个可能值, 分别为 Either、 Falling、 Rising 和 Function Call。在 Simulink 条件执行子系统中, 特别是 在使能或者触发子系统中, 触发子系统工作的 触发源就具有不同属性。 触发子系统的触发源 与这里的 Trigger 属性的意义完全一样, 分别 为双边沿触发、 下降沿触发、 上升沿触发。 Function Call(函数调用)是一类比较特殊的触发 属性

软件工程 第5章--UML

UML的定义

UML定义有两个主要组成部分:语义和表示法。 语义用自然语言描述,表示法定义了UML的可 视化标准表示符号,这决定了UML是一种可视 化的建模语言。 在语义上,模型是元模型的实例。UML定义给 出了语法结构的精确定义。 使用UML时,要从不同的角度观察系统,为此 定义了概念“视图(View)‖。视图是对系统的模 型在某方面的投影,注重于系统的某个方面。

独立于过程

系统建模语言,独立于开发过程。

9

容易掌握使用 概念明确,建模表示法简洁明了,图形结 构清晰,容易掌握使用。 着重学习三个方面的主要内容: (1) UML的基本模型元素 (2) 组织模型元素的规则 (3) UML语言的公共机制 与程序设计语言的关系 用Java,C++ 等编程语言可实现一个系统。 一些CASE工具可以根据 UML所建立的系 统模型来产生Java、C++ 等代码框架。

31

UML事物 — 注释事物

11) Note(注释)

依附于一个元素或一组元素之上,对其进

行约束或解释的简单符号。没有语义影响。

See policy8-5-96.doc for details about these algorithms.

CashAccount presentValue()

32

15

UML定义 9 种图,表达UML中的 5 种视图,各 视图在静态和动态方面表示系统模型。

结构 视图 静态 方面

动态 方面

行为 视图 同左

实现 视图 构件图

环境 视图 部署图

同左

用例 视图 用例图

同左

类图 对象图

顺序图 同左 顺序图 合作图 (注重 合作图 状态图 进程、 状态图 活动图 线程) 活动图

第5章 了解呼叫处理基本原理

• · 计费种类:定期或立即计费;家用计次表; 计费打印机等。 • · 出局类别:只允许本区内呼叫;允许市 内呼叫;允许国内长途呼叫;允许国际呼叫。 • · 优先级别及专用情况:是否热线电话; 是否优先;优先级别;能否作国际呼叫的被 叫。 • · 服务类别:呼叫转移;呼叫等待;三方 通话;叫醒服务;免打扰;恶意呼叫追踪等 服务性能。

• 5 、被叫应答和通话 • 被叫摘机,停振铃、回铃音; • 建立通话路由,开始通话; • 启动计费设备,开始计费; • 监视主、被叫用户状态;

• 6 、话终,主叫先挂机 • 路由复原 • 停计费 • 向被叫送忙音 • 7 、被叫先挂机 • 路由复原 • 停计费 • 向被叫送忙音

• 8、通话结束,释放资源

5.3 分析处理 • 对各种输入信息,可以来自用户线、中继 线、其他局、操作台等的各种信息进行分 析并处理,决定下一步该做什么,分析处 理由分析程序负责执行。

• 去话分析:发生在主叫局检测到用户摘机,对 主叫用户进行分析。 • 号码分析:主叫局分析本局用户所拨的号码, 或被叫局分析由局间信令送过来的主叫用户所 拨的号码。 来话分析:被叫局分析被叫用户。 状态分析:针对整个通话时间内的各种状态, 连同当时的输入信息一并进行分析处理。

掌握呼叫处理基本原理

目 录

呼叫处理过程 稳定状态和状态转换

输入处理 分析处理 任务执行和输出处理

• • • • • • • • • •

1. 呼叫处理过程 呼叫处理的基本过程: 1 、主叫用户A 摘机呼叫 检测到用户摘机 调查用户 A 的类别 检查用户呼叫限制情况 调查话机类别 2 、送拨号音,准备收号 找空闲收号器, 找 A 和信号音发生器间的 空闲路由或时隙; 向 A 送拨号音,提示A拨号; 监视A的用户线输入信号,准备收号

PLC5章状态转移图及编程方法

(2) 台车后退碰到限位开关SQ2后,台车电机M停转,台车停 车,停5 s,第二次前进,碰到限位开关SQ3,再次后退。

(3) 当后退再次碰到限位开关SQ2时,台车停止(或者 继续下一个循环)。

5.1 状态转移图及状态功能

PLC程序设计步骤

• 根据可编程序控制器系统硬件结构和生产工艺要求,在软件规格说 明书的基础上,用相应的编程语言指令,编制实际应用程序并形成 程序说明书的过程就是程序设计。

• PLC程序设计一般分为以下几个步骤: • 程序设计前的准备工作。 • 程序框图设计。 • 程序测试。 • 编写程序说明书。

1.程序设计前的准备工作

• 在熟悉被控对象的同时,还要认真借鉴前人在程 序设计中的经验和教训,总结各种问题的解决方 法——哪些是成功的,哪些是失败的,为什么。 总之,在程序设计之前,掌握东西越多,对问题 思考得越深入,程序设计就会越得应手。

• 3)充分利用手头的硬件和软件工具例如, 硬件工具有:编程器、GPC(图形编程器)、 FIT(工厂智能终端);编程软件有:LSS、 SSS、CPT、CX—ProgTammer、西门子STEP7 如果是利用计算机编程,可以大大提高编 程的效率和质量。

(3) 只要在不相邻的步进段内,则可重复使用同一编号的 计时器。这样,在一般的步进控制中只需使用2~3个计时器 就够了,可以节省很多计时器。

(4) 状态也可以作为一般中间继电器使用,其功能与M一 样,但作一般中间继电器使用时就不能再提供STL触点了。

5.2 单流程状态转移图的编程

第三步:设计步进梯形图

状态的转移条件可以是单一的,也可以是多个元件的串、 并联组合,如图所示。

第5章 VHDL 状态机.ppt

采用VHDL语言实现基于状态机的设计,就是 在时钟信号的触发下,完成两项任务:

(1)用case或if-else语句描述出状态的转移; (2)描述状态机的输出信号。

6.1 状态机设计相关语句

6.1 类型定义语句(自定义)

TYPE 数据类型名 IS 数据类型定义 OF 基本数据类型 ;或 TYPE 数据类型名 IS 数据类型定义 ;

号,决定何时进行何种数据处理。有限状态机分为两类:Moore

型和Mealy型

输入

状态 次态 状态 现态 输出

译码器

寄存器

逻辑

输出

状态机的基本操作有两种:

(1) 状态机内部状态转换。状态机经历一系列状态,下一状 态由状态译码器根据当前状态和输入条件决定。

(2) 产生输出信号序列。输出信号由输出译码器根据当前状 态和输入条件决定。

TYPE st1 IS ARRAY ( 0 TO 15 ) OF STD_LOGIC ; TYPE week IS (sun,mon,tue,wed,thu,fri,sat) ;

TYPE m_state IS ( st0,st1,st2,st3,st4,st5 ) ; SIGNAL present_state,next_state : m_state ;

...

5.1 状态机设计相关语句

6.1 状态机结构

2. 主控时序进程 :负责状态机运转和在时钟驱动下 负责状态转换的进程。

FSM: s_machine

clk reset

PROCESS REG

current_state next_state

PROCESS COM

comb_outputs

state_inputs

NEXT_STATE<=ST0; --在下一时钟后,进程REG的状态将维持为ST0

数字电子技术 第5章 时序逻辑电路的分析

40

5.8异步计数器

1.异步计数器的概念:异步计数器中的 触发器不会同时改变状态,因为它们没 有共同的时钟脉冲

41

2. 三位异步二进制计数器

42

波形图

Q0:2分频 Q1:4分频 Q2:8分频

Q0 Q1’ Q2

43

3.四位异步十进制计数器

1 CP 2 3 4 5 6 7 8 9 10

起译码 作用

电路分析: Di输入的数据,在cp 上升沿作用下,逐位 向左移动,经过4个 脉冲,将把输入的第 1个数传送到输出D0。

电压波形

34

5.5.MSI移位寄存器

M=0 M=1

串行输出

74LS95右移 移位寄存器

并 行 输 出

(1)电路形式:电路接成串行移位右移,并行输入,并行输出。 (2)工作原理:当方式控制M=1时,允许数据以并行方式输入,在cp2作用下,并 行存入J-K FF,并以并行方式输出Data.Q0~Q3。当M=0时,并行输入被禁止, 允许串行输入到J-K FF,在cp1作用下逐位右移。

1

1

1

1

4位异步二进制计数器(74LS93)

电路特点: 74LS93是一个MSI.模2×8进制计数器。从电路形式上看,第1 个FF为2进制,第2~4个FF是8进制计数器。采用两个时钟脉冲 CPA,CPB,有2个复位输入端,为方便灵活使用。

46

74LS93应用

用74LS93构成模16计数器。 将QA(第一级FF输出)作为CPB 使用,成为模16计数器。

(4)将驱动方程分别代入J-K FF的特性方程:

001 000 (2)时序电路的输出为Q3Q2Q1

(3)各FF的驱动方程: J1=Q3 K1=1 J2=1 K2=1 J3=Q2Q1 K3=1

数字设计:原理与实践第五版习题答案

数字设计:原理与实践第五版习题答案第一章:数字系统基础1. 哪些数学符号代表布尔逻辑运算?分别代表哪些逻辑操作?布尔逻辑运算包括与(AND)、或(OR)、非(NOT)、异或(XOR)等运算。

它们的对应数学符号表示如下:•与(AND):$\\cdot$ 或 $\\land$•或(OR):+或 $\\lor$•非(NOT):$\\overline{A}$ 或eee•异或(XOR):$\\oplus$2. 简述数字系统的信号表示和信号处理单元。

数字系统的信号表示使用离散量来表示连续或离散的信号,其中离散量指代具有离散数值的量。

信号处理单元是指对输入信号进行处理和操作的硬件模块,用于实现特定的功能或执行特定的任务。

3. 什么是布尔函数?它可以用哪些方法表示?布尔函数是指以布尔逻辑运算为基础,将一个或多个布尔变量映射为单一布尔值的函数。

布尔函数可以用真值表、逻辑表达式和逻辑图等方法表示。

4. 简述数字系统的设计方法。

数字系统的设计方法包括以下几个步骤:1.确定问题的需求和约束条件。

2.将问题抽象为逻辑功能的实现。

3.设计逻辑电路并进行仿真验证。

4.实现电路设计并进行实验验证。

5.优化电路设计并进行性能评估。

6.完成设计文档和报告。

第二章:组合逻辑电路设计1. 什么是组合逻辑电路?简述其基本特征。

组合逻辑电路是指将组合逻辑块进行组合形成的电路,其输出仅依赖于当前的输入。

它的基本特征包括:•输入输出之间无时序关系。

•只有组合逻辑块,没有存储元件。

•输出仅取决于当前输入。

2. 简述逻辑门的功能和特点。

逻辑门是实现布尔逻辑运算的基本构件,其功能和特点如下:•与门(AND):多个输入信号全部为高时,输出高;否则输出低。

•或门(OR):多个输入信号有一个为高时,输出高;否则输出低。

•非门(NOT):输入信号为高时,输出低;否则输出高。

•异或门(XOR):多个输入信号中奇数个为高时,输出高;否则输出低。

3. 什么是选择器和解码器?选择器是一种组合逻辑电路,根据选择信号将一组输入信号中的某一个作为输出。

状态机

用状态机原理进行软件设计池元武展讯通信(上海)有限公司,PLD,上海摘要:本文描述状态机基础理论,以及运用状态机原理进行软件设计和实现的方法。

关键词:有限状态机层次状态机面向对象分析行为继承参考文献[1] Miro Samek, Ph.D《Practical Statecharts in C/C++ Quantum Programming for Embedded Systems》[2] OpenFans/viewArticle.html?id=289缩略语名称描述StateMachineFSM FiniteHSM Hierarchical State MachineOOP Object Oriented ProgrammingUML Unified Modeling LanguageLSP Liskov Substitution PrinciplePoC push to talk over cellular目录第1章引言................................................................................................................................................1-1第2章 FSM概念......................................................................................................................................2-12.1 FSM定义.........................................................................................................................................2-12.2 FSM要素.........................................................................................................................................2-12.2.1 State(状态)......................................................................................................................2-12.2.2 Guard(条件)......................................................................................................................2-12.2.3 Event(事件)......................................................................................................................2-12.2.4 Action(动作)....................................................................................................................2-12.2.5 Transition(迁移).......................................................................................................2-22.3 FSM图示.........................................................................................................................................2-2 第3章 FSM设计方法..............................................................................................................................3-13.1 C Parser(注释分析程序)..................................................................................................................3-13.2 Calc(计算器)程序举例.....................................................................................................................3-2 第4章 HSM概念......................................................................................................................................4-14.1 programming-by-difference(按照差异编程)..............................................................................4-14.2 HSM图示.........................................................................................................................................4-14.3 HSM分析和OOP分析...................................................................................................................4-24.3.1 state inheritance and class inheritance(状态层次和类层次)..........4-24.3.2 Entry/Exit Actions and Construction/Destruction(进入/退出状态和构造/析构类).............................................................................................................................................4-34.3.3 programming-by-difference(按照差异编程)....................................................................4-34.3.4 abstraction(抽象)........................................................................................................4-4 第5章 HSM设计方法..............................................................................................................................5-15.1继续进行Calc设计......................................................................................................................5-15.2继承关系是否合理.........................................................................................................................5-35.2.1 Transition迁移执行顺序..............................................................................................5-4 第6章 HSM在实际工程的应用..............................................................................................................6-66.1 PoC Audio Player..............................................................................................................................6-66.2 PoC Call Control...............................................................................................................................6-7 第7章 FSM实现......................................................................................................................................7-17.1 nestted switch statement(嵌套switch)........................................................................................7-17.2 state table(状态表)................................................................................................................7-2-i-7.3 Function Address As State(用函数指针作为状态).....................................................7-37.4 QFSM frame(QFSM框架)..........................................................................................................7-5 第8章 HSM实现......................................................................................................................................8-1第9章附录 (1)-ii-图目录图2-1 Keyboard FSM in UML format 1...............................................................................................2-2 图2-2 Keyboard FSM in UML format 2...............................................................................................2-3 图3-1 C comment parser (CParser) FSM..............................................................................................3-2 图3-2 Basic Calc Example....................................................................................................................3-3 图3-3 Basic Calc FSM..........................................................................................................................3-4 图3-4 Basic Calc FSM add “Result” state............................................................................................3-5 图3-5 Basic Calc FSM add “Result” state and Cancel event................................................................3-6 图3-6 Simple Calc HSM.......................................................................................................................3-7 图 4-2 HSM conception.........................................................................................................................4-2 图5-1 substate of operandX..................................................................................................................5-1 图5-2 Full Calc HSM............................................................................................................................5-3 图5-3 State Tree of Calc.......................................................................................................................5-5 图 6-1 HSM of audio Player..................................................................................................................6-7 图6-2 HSM of Call Control..................................................................................................................6-8-i-第1章引言20多年以前,David Harel创造了状态机理论来描述复杂的交互系统。

2024年学习笔记信息系统项目管理师(第四版)第五章-信息系统工程

第五章-信息系统⼯程1-软件⼯程1.1-架构设计1.软件架构为软件系统提供了一个结构、行为和属性的高级抽象,由构件的描述,构件的相互作用(连接体)、指导构件集成的模式以及这些模式的约束组成。

2.软件架构主要研究内容涉及软件架构描述、软件架构风格。

软件架构评估和软件架构的形式化方法等。

3.研究软件架构的根本目的是解决好软件的复用、质量和维护问题。

4.软件架构设计的一个核心问题是能否达到架构级的软件复用,也就是说,能否在不同的系统中使用同一个架构软件。

软件架构风格是描述某一个特定应用领域找那个系统组织方式的惯用模式。

5.通用软件架构:数据流风格、调用/返回风格、独立构件风格、虚拟机风格和仓库风格。

6.数据流风格:包括批处理序列和管道/过滤器两种风格。

7.调用/返回风格包括主程序/子程序、数据抽象和面向对象,以及层次结构。

8.独立构件风格包括进程通信和事件驱动的系统9.虚拟机⻛格包括解释器和基于规则的系统。

10.仓库⻛格包括数据库系统、⿊板系统和超⽂本系统。

11.在架构评估过程中,评估⼈员所关注的是系统的质量属性。

1.2-需求分析1.虚拟机⻛格包括解释器和基于规则的系统。

需求是多层次的,包括业务需求、⽤户需求和系统需求,这三个不同层次从⽬标到具体,从整体到局部,从概念到细节。

2.业务需求:指反映企业或客户对系统⾼层次的⼀个⽬标追求,通常来⾃项⽬投资⼈、购买产品的客户、客户单位的管理⼈员、市场营销部⻔或产品策划部⻔等。

3.⽤户需求:描述的是⽤户的具体⽬标,或者⽤户要求系统能完成的任务,⽤户需求描述了⽤户能让系统来做什么。

4.系统需求:是指从系统的⻆度来说明软件的需求,包括功能需求,⾮功能需求和设计约束。

5.质量功能部署QFD是⼀种将⽤户要求转化成软件需求的技术,其⽬的是最⼤限度地提升软件⼯程过程中⽤户的满意度。

为了达到这个⽬标,QFD将需求分为三类,分别是常规需求、期望需求和意外需求。

6.需求过程主要包括需求获取、需求分析、需求规格说明书编制、需求验证与确认等。

EDA技术与VHDL课后答案(第3版)潘松 黄继业

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY 8f_suber IS

PORT ( x0,x1,x2,x3,x4,x5,x6,x7 : IN STD_LOGIC ;

y0,y1,y2,y3,y4,y5,y6,y7 : IN STD_LOGIC ;

sub_in : IN STD_LOGIC ;

ELSIF u2_y<= u2_b ;

ELSE u2_y<= NULL ;

END IF ;

END PROCESS p_ MUX21A_u2 ;

u1_s<= s0 ; u1_a<= a2 ; u1_b<= a3 ;

tmp<= u1_y ;

u2_s<=s1 ; u2_a<= a1 ; u2_b<= tmp;

diff=>diff2 ) ;

u3 : f_suber PORT MAP (x=>x3, y=>y3, sub_in=>c, sub_out=>d,

diff=>diff3 ) ;

u4 : f_suber PORT MAP (x=>x4, y=>y4, sub_in=>d, sub_out=>e,

diff=>diff4 ) ;

sub_in x y

sub_out

diffr

0

x

0

y

0

f_suber

sub_in x y

sub_out

diffr

1

x

1

y

1

f_suber

sub_in x y

sub_out

diffr

Verilog HDL数字设计教程(贺敬凯)第5章

第5章 同步有限状态机设计

其仿真结果如图5-11所示。 【例5-5】 对应于步骤四的Verilog HDL建模。 ///产生JK激励信号:D触发器的激励d---->JK触发器的激励J 和K

module D_JK(d,q,j,k);

input d,q; output reg j,k;

always @(d,q)

利用多余状态,卡诺图化简后的激励方程和输出方程为:

n n D1 Q0 A,D0 A, Y Q1 A

第六步:画出逻辑图并检查自启动能力。逻辑图如图57所示。

第5章 同步有限状态机设计

图5-7 例5-1的逻辑图

第5章 同步有限状态机设计

经检查,该电路具有自启动能力。 至此解题完毕。 以上六步,我们均可以采用Verilog HDL进行电路建模, 下面从后向前对各个步骤进行建模,见例5-2至例5-9。

第5章 同步有限状态机设计

程序说明:

(1) 例5-4的实现要求得出输出方程和激励方程,然后才

能对时序逻辑电路建模。这种建模方法同例5-2一样,需要 手工做大量复杂的工作,而不是由计算机来完成复杂的计算 工作。 (2) 该模块的综合结果如图5-12所示。

第5章 同步有限状态机设计

图5-12 例5-4的综合结果

第5章 同步有限状态机设计

【例5-3】 对例5-2的改进——消除毛刺。 module input clk,A; output reg Y; wire q0,q1; mydff_2 dff0(.D(A),.Q(q0),.clk(clk)), dff1(.D(A&q0), .Q(q1), .clk(clk)); always @(posedge clk) Y= q1 & (~A); endmodule 该模块的综合结果如图5-10所示。 fsm_1(clk,A,Y);

数字逻辑系统教案

课程介绍:先修课程:《数字电子技术》--学习了数字电路的基本设计方法。

本课程:《数字逻辑系统设计》--面向实际工程应用,紧跟技术发展,掌握数字系统新的设计方法。

主要学习可编程逻辑器件原理、VHDL硬件描述语言基础、QUARTUSII工具使用。

后续课程:1、《数字信号处理》--应用的一个方面,由FPGA代替DSP来实现算法,提高系统的速度。

2、《SOPC技术》--SOPC Builder 的NIOS嵌入式系统软硬件设计技术课程宗旨:1、更新数字电路的设计观念,建立用PLD器件取代传统TTL器件设计数字电路的思想2、更新数字系统设计手段,学会使用硬件描述语言(Hardware 2、Description Language)代替传统的数字电路设计方法来设计数字系统。

器件为什么能够编程?了解大规模可编程逻辑器件的结构及工作原理(第2章内容)怎样对器件编程?1、熟悉一种EDA软件的使用方法(工具)(以Altera公司的QUARTUSII为例)2、掌握一种硬件描述语言(方法),以设计软件的方式来设计硬件(重点)(以VHDL语言为例)教学安排:总学时数:78 学时理论课时:54 学时实验课时:24 学时分数:5 学分考核方式:1、成绩(20%):考勤、课堂纪律、回答问题、作业2、成绩(20%):实验操作、实验报告3、笔试(60%):闭卷考试选用教材:《EDA技术与VHDL(第2版)》潘松、黄继业编著,清华大学出版社参考教材:1、《VHDL程序设计教程(第3版)》,曾繁泰,清华大学出版社2、《VHDL硬件描述语言与数字逻辑电路设计》,侯伯亨、顾新,西安电子科技大学出版社3、《FPGA/VHDL快速工程实践入门与提高》,杨恒、卢飞成,北京航空航天大学出版社4、《集成电路/计算机硬件描述语言VHDL高级教程》,刘明业,清华大学出版社5、《用VHDL设计电子线路》,边计年、薛宏熙译,清华大学出版社本书重点:1、章 PLD硬件特性与编程技术2、第3章 VHDL基础3、第4章 Quartus II 使用方法4、第7章 VHDL语句5、第8章 VHDL结构本书难点:1、第2章 PLD硬件特性与编程技术2、第5章 VHDL状态机3、第6章 16位CISC CPU设计4、第9、10章 DSP Builder设计数字电子技术回顾布尔函数--数字系统数学基础(卡诺图)数字电路设计的基本方法:(提问)1、组合电路设计:问题逻辑关系真值表化简逻辑图2、时序电路设计:列出原始状态转移图和表状态优化状态分配触发器选型求解方程式逻辑图3、使用中、小规模器件设计电路(74、54系列)编码器(74LS148)、译码器(74LS154)、比较器(74LS85)计数器(74LS193)、移位寄存器(74LS194)………设计方法的局限(提问)1、卡诺图只适用于输入比较少的函数的化简。

EDA 第5章 5.3

5.4 状态编码

5.4.1 直接输出型编码

直接输出型编码:即将状态编码直接输出作为控 制信号。首先将不同状态下的各个控制信号的逻辑值 做为状态变量的编码,其次为使不同状态下的编码不 同,可采用原编码基础上增加标志信号位来区分不同 的状态。

5.4 状态编码

5.4.1 直接输出型编码

表5-1 控制信号状态编码表

st1; st2; st3; st4; st0;

END END END END END

IF; IF; IF; IF; IF;

(接下页)

5.3 Mealy状态机

END IF; END PROCESS COMREG ; COM1: PROCESS(STX,DATAIN,CLK) --输出控制信号的进程 VARIABLE Q2 : STD_LOGIC_VECTOR(4 DOWNTO 0); BEGIN CASE STX IS WHEN st0=> IF DATAIN='1' THEN Q2 :="10000"; ELSE Q2:="01010"; WHEN st1=> IF DATAIN='0' THEN Q2 :="10111"; ELSE Q2:="10100"; WHEN st2=> IF DATAIN='1' THEN Q2 :="10101"; ELSE Q2:="10011"; WHEN st3=> IF DATAIN='0' THEN Q2 :="11011"; ELSE Q2:="01001"; WHEN st4=> IF DATAIN='1' THEN Q2 :="11101"; ELSE Q2:="01101"; WHEN OTHERS => Q2:="00000" ; END CASE ; IF CLK'EVENT AND CLK = '1' THEN Q1<=Q2; END IF; END PROCESS COM1 ; Q <= Q1 ; END behav;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2、 有限状态机的几种描述方式

(1)用三个过程描述:即现态(CS)、次态(NS)、 输出逻辑(OL)各用一个always过程描述。 (2)双过程描述(CS+NS、OL双过程描述):使用两 个always过程来描述有限状态机,一个过程描述现态和次 态时序逻辑(CS+NS);另一个过程描述输出逻辑(OL)。 (3)双过程描述(CS、NS+OL双过程描述):一个过 程用来描述现态(CS);另一个过程描述次态和输出逻辑 (NS+OL)。 (4)单过程描述:在单过程描述方式中,将状态机的现 态、次态和输出逻辑(CS+NS+OL)放在一个always 过程中进行描述。

3、状 态 机 状 态 编 码

简单状态编码直接可采用前面的整数定义编码方式,但复 杂设计必须采用如下编码方式进行。

⑵复杂状态机状态编码方式

①二进制编码:是二进制数连续编码,这种方法在小型状 态机中常用,较其它方法好。 ②格雷编码(Gray code):码间只有一位不同的编码 方式。 ③独热编码(One-Hot code):每个编码只有一位是1, 其它都是0。 ④约翰逊编码(Johnson code):

1、FSM概念

有限状态机由输入和输出和具有记忆功能的寄存器 组成,寄存器用于寄存状态机内部状态,也称状态寄存 器。 状态机的下一个状态不仅与输入信号有关,还与该 寄存器的当前状态有关,因此有限状态机可看作是组合 逻辑与时序逻辑的一种组合。其中的时序逻辑功能是存 储有限状态机的内部状态;而组合逻辑又可分为次态产 生逻辑和输出逻辑两部分,次态产生逻辑的功能是确定 有限状态机的下一个状态,输出逻辑功能是确定有限状 态机的输出。 由于FSM的描述较为复杂,因此不能使用原理图方法 进行描述,而采用Verilog HDL语言进行行为级设计。

各种编码比较

如描述6个状态的编码: 二进制编码: 000,001,010,011,100,101

独热编码: 000001,000010,000100,001000, 010000,100000

格雷编码: 000,001,011,010,110,100

每个二进制位占有一个触发器,所以描述同样的状态数,二进制 编码和格雷编码所需触发器少,而独热编码相对较多。但从编译 角度来看,独热码相对其它两种简单。

… integer mealystate;//定义状态变量 parameter S0=0,S1=1,S2=2,S3=3; always(mealystate,din) case (mealystate) S0:…; S1:…; …; default:…; endcase endmodule

//定义状态编码

3、几种典型逻辑电路的状态机设计

⑴Moore型FSM的设计 Moore型状态机的输出只与有限状态机的当前状态有关, 与输入信号的当前输入无关,即可将Moore型有限状态机 的输出看成是当前状态的函数,次态=f(现状,输入), 输出=f(现状)。

Next state din current state

reset

S1

1/0

S2

下一状态 当前状态 din=0 s1,0 s1,0 s1,1 din=1 s0,0 s2,0 s0,0

s0=00 s1=01 s2=11

由输入信号检测010序列Verilong程序

module mealyfsm(clk,reset,din,dout, cs_state,ns_state); output dout; s1:begin output [1:0] cs_state,ns_state; dout=1'b0; input clk,reset,din; ns=(!din)?s1:s2; reg dout; end //用格雷码编码声明状态值 s2:begin parameter [1:0] s0=2'b00,s1=2'b10,s2=2'b11; reg [1:0]cs,ns; dout=(din)?1'b0:1'b1; assign cs_state=cs,ns_state=ns; ns=(din)?s0:s1; always@(posedge clk,posedge reset)begin end if(reset==1'b1) //异步复位,高电平有效 default:begin cs<=s0; dout=1'b0; else ns=s0; cs<=ns; end end //次态计算及输出信号产生, endcase always@(cs,din) endmodule case(cs) s0:begin dout=1'b0; if(din===1'bx)ns=s0; else ns=(din)?s0:s1;

0

仿真结果

可见dout输出由当前状态CS_state(或CS)决定,而次态 NS_state(或NS)由输入din和当前状态CS决定。这就是mooreFSM 状态机工作特点。

⑴Mealy型FSM的设计

Mealy型状态机的输出不仅与有限状态机的当前状态有关, 还与输入信号有关,即可将Mealy型有限状态机的输出看 成是当前状态和输入的函数,次态=f(现态,输入),输 出=f(现态,输入)。

第5章 Verilog有限状态机设计

本章内容

5.1、FSM概述 5.2、FSM设计方法

5.1 状态机概述

1、FSM概念

在数字系统中,有限状态机(FSM,Finite State Machine)是一类十分重要的时序电 路。微控制器的核心就是FSM。因此学习 FSM的原理及设计方法对于学习数字系统设 计和理解计算机原理都有重要意义。 本章首先概要介绍FSM的相关理论知识,通 过典型实例说明FSM的设计方法。

3、状 态 机 状 态 定 义 与 编 码

`define S0 2’b00; //定义状态编码 ③采用编译引导语句声 `define S1 2’b01; 明状态方式:就是采用 …; define语句定义状态。 module mealyFSM(clk,din,reset,dout); …; 语句格式: integer mealystate;//定义状态变量 `define <宏名><宏文本> always(mealystate,din) case (mealystate) 该语句在编译时用“宏文 S0:…; S1:…; 本”替代代码中的”宏 名”,这种方法可以提高 …; default:…; 程序的可读性,与上面的 endcase 参数定义类似。 endmodule

2、 有限状态机FSM组成

摩尔型(Moore)状态机

米里型(Mealy)状态机

单纯的Moore型或Mealy型比较少,常见是两种混合型设计。

例如: 状态机的一般控制形式

如图状态机的基本结构

状态机功能结构描述

7.1.1 状态机的基本结构 3. 主控组合过程

4. 辅助过程 接下页

状态机功能结构描述

0

S0 0

1

1

din clk dout

reset

S1 1

S2 1

1

0

1

S3 0 0

设计方式采用双过程描述 (CS、NS+OL双过程 描述):一个过程用来描 述现态(CS);另一个 过程描述次态和输出逻辑 (NS+OL)。

Moore型状态机Verilog描述程序

module mooreFSM(clk,reset,din,dout,CS_state,NS_state); input clk,reset,din; output dout;output [3:0] dout,CS_state,NS_state; reg dout; //one-hot code parameter S0=4'b0001,S1=4'b0010,S2=4'b0100,S3=4'b1000; reg [3:0] CS,NS;assign CS_state=CS,NS_state=NS; always @(posedge clk , posedge reset) begin if(reset==1'b1) CS<=S0; else CS<=NS; end 0 always @(CS or din or NS ) begin case(CS) S0 S0: begin dout<=1'b0; 1 0 0 if(din===1'bx)NS=S0; else NS=(!din)?S0:S2; end S1 1 S1: begin dout<=1'b1; S2 1 NS=(!din)?S0:S2; end 1 S2: begin dout<=1'b1; NS=(!din)?S2:S3; end 1 S3 S3: begin dout<=1'b0; 1 0 NS=(!din)?S3:S1; end default:begin dout=1'b0; 0 NS=S0; end endcase end endmodule

格雷编码

5.2 FSM状态机设计方法

1、采用Verilog HDL描述有限状态机设计原则

⑴根据系统要求确定状态数量、状态转移的条件和 各状态输出信号的赋值、并画出状态转移图。如下 图:

⑵按照状态转移图编写状态机的Verilog HDL代 码。 ⑶利用EDA工具对状态机的功能进行仿真验证。

各种编码比较

二进制编码、格雷码编码使用最少的触发器,消耗较多的 组合逻辑,而独热码编码反之。独热码编码的最大优势在于状 态比较时仅仅需要比较一个位,从而一定程度上简化了译码逻 辑,减少复杂性,提高系统的速度,即工作时钟频率可以做到 最高 。虽然在需要表示同样的状态数时,独热编码占用较多 的位,也就是消耗较多的触发器,但这些额外触发器占用的面 积可与译码电路省下来的面积相抵消。 在CPLD中,由于器件拥有较多的提供组合逻辑资源,所 以CPLD多使用二进制编码或格雷码,而FPGA更多地提供触 发器资源,所以在FPGA中多使用独热码编码。当然,这并不 是说在FPGA中就非得用独热编码,在CPLD中不能用独热编 码,一般的,对于小型设计(状态数小于4)使用二进制编码, 当状态数处于4-24之间时,宜采用独热码编码,而大型状态 机(状态数大于24)使用格雷码更高效。