基于DSPBuilder数字信号处理课程设计

基于DSP的数字信号处理系统设计与开发

基于DSP的数字信号处理系统设计与开发随着科学技术的不断进步和发展,数字信号处理技术的应用越来越广泛,对于数字信号处理系统的设计和开发也越来越重要。

在数字信号处理领域中,DSP(数字信号处理器)是一个非常重要的组成部分,它的高效性能和灵活性使得其在多个领域都有广泛的应用,如音频信号处理、图像处理、无线通信和控制等。

因此,基于DSP的数字信号处理系统设计与开发成为了当前的热点之一。

一、基本原理DSP的基本原理是将模拟信号转换为数字信号进行处理,再将处理后的数字信号转换为模拟信号输出。

在数字信号处理中,最基本的操作是数字信号的采样和量化,它们对于后续的处理过程具有决定性的影响。

采样率决定了数字信号中包含的信息量,而量化级数则决定了数字信号的精度。

在数字信号处理系统中,信号的处理过程主要涉及到数字滤波、谱分析、时频分析、信号的编码/解码和模拟数字转换等,其中最常见的操作是数字信号的滤波操作。

数字滤波技术可以通过数字域滤波和时域滤波来实现,其中数字域滤波包括数字滤波器设计和数字滤波器的应用两部分。

数字滤波器设计主要是通过滤波器特性的设计来满足特定的滤波要求,而数字滤波器的应用则是将设计出的数字滤波器应用到具体的信号处理中。

二、基于DSP的数字信号处理系统设计基于DSP的数字信号处理系统设计需要考虑多方面的因素,如硬件设计、软件设计、算法实现、系统性能和接口设计等。

硬件设计主要考虑DSP芯片的选择、外围电路设计和信号处理模块的构建,同时还需要注重系统的可扩展性和可维护性。

软件设计主要涉及到系统的编码和测试,软件的质量对于系统的性能和稳定性有着决定性的影响。

在DSP的开发中,算法的实现是非常关键的。

系统算法的效率和准确性直接影响到系统的性能和易用性。

在算法的实现中,需要注意算法的优化和算法的可移植性。

系统性能的评价一般包括系统的速度、功率、资源消耗和精度等指标。

在DSP的开发中,需要考虑这些指标以及如何进行优化,以满足系统要求。

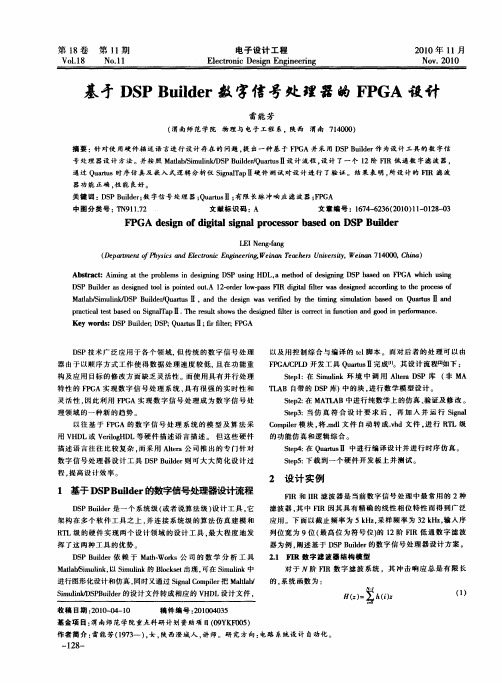

基于DSP Builder数字滤波器的FPGA设计

基于DSP Builder数字滤波器的FPGA设计摘要:现场可编程门阵列( FPGA) 器件广泛应用于数字信号处理领域,而使用VHDL 或VerilogHDL 语言进行设计比较复杂。

提出一种采用DSP Builder 实现IIR数字滤波器的设计方案,按照Matlab/Simulink/DSP Builder/QuartusⅡ的设计流程,设计了一个4阶IIR 低通数字滤波器,并通过QuartusⅡ软件中的嵌入式逻辑分析仪SignalTapⅡ对设计进行了硬件实时测试。

结果表明,所设计的IIR数字滤波器功能正确,性能良好。

Abstract: Field Programmable Gate Array (FPGA) devices is widely used in the field of digital signal processing, but it is complicated to design using VHDL or VerilogHDL. A method of designing IIR digital filter based on DSP Builder are pointed out. Then a 4-order low-pass IIR digital filter was designed according to the process ofMatlab/Simulink/DSP Builder/QuartusⅡ, and the practical test was finished based on Signa1TapⅡof QuartusⅡsoftware. The result shows the designed filter correct in function and good in performance.关键词: FPGA;无限长脉冲响应滤波器;DSP Builder;QuartusⅡKey words: FPGA;IIR filter;DSP Builder;QuartusⅡ中图分类号:TN911.72 文献标识码:A 文章编号:1006-4311(2011)07-0141-020 引言数字滤波器是现代数字信号处理系统的重要组成部分之一,具有模拟滤波器所无法替代的新特性,因此在通信、语音与图像处理、自动控制等领域有着广泛的应用,它对于降低噪声、提高信噪比及信号的频谱纯度等方面有着重要的意义。

基于DSP Builder的DDS数字系统设计与实现

MAT L A B的 S i mu l i n k系统级 工具 与 Qu a r t u s I I 设计 工具组合 在 一起 来设计 DDS数 字 系统 ,最终 实现

输 出频 率 可调 , 调频 范 围为 1 ~1 8 MHz 的 高精 度 DDS 数 字 系统 。

【 关键词 】  ̄ DD S ; D S P B u i l d e r ; MA T L A B; Q u a r t u s I I ;

用 于 建立 图形 模 块 并 能对其 进 行 仿 频率合成技术 , 是 一 种 新 型 的频 率 合 成 技 术 , 其 电路 的一 个 组成 部分 , 系 统 具有 较 高 的频 率分 辨 率 , 可 以实现 快 速 的频 率 切 真 。D S P B u i l d e r 作为 S i mu l i n k的一 个 控制 字 。每经 过 一 个

时钟 周 期 , 相位 累加 器 的值 递增 K。根 据 D D S基 本 结 构, 若f c 为 时钟 频 率 , f 0为输 出频率 , 则[ 3 卅:

f o= 半 / 2

D S P B u i l d e r 是 Ah e r a公 司 推 出 的一 种 基 于 F P —

换, 并 且 在 频 率 改 变 时 能 够 保 持 相位 的 连续 , 很 容 易 F P G A设 计 D S P系 统 完 全 可 以通 过 S i m u l i n k的 图 形

实现频 率 、 相位 和 幅度 的数 控 调制 。

界 面进 行 建模 、 系统 级 仿 真 , 设计 模 型还 可 以直 接 转

【 摘 要】 : 直接数 字合成器( D Ds ) 是采用数字技术的一种新型频 率合成技 术。针对这个问题提 出

基于DSP Builder的DDS设计

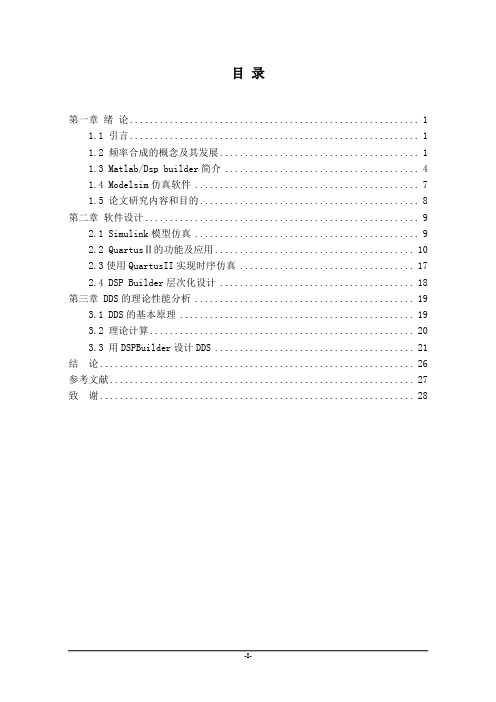

目录第一章绪论 (1)1.1 引言 (1)1.2 频率合成的概念及其发展 (1)1.3 Matlab/Dsp builder简介 (4)1.4 Modelsim仿真软件 (7)1.5 论文研究内容和目的 (8)第二章软件设计 (9)2.1 Simulink模型仿真 (9)2.2 QuartusⅡ的功能及应用 (10)2.3使用QuartusII实现时序仿真 (17)2.4 DSP Builder层次化设计 (18)第三章 DDS的理论性能分析 (19)3.1 DDS的基本原理 (19)3.2 理论计算 (20)3.3 用DSPBuilder设计DDS (21)结论 (26)参考文献 (27)致谢 (28)摘要直接数字频率合成技术(DDS)在数字通信系统中被广泛采用。

DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,本论文是在研究直接数字频率合成技术基本原理的基础上 ,利用 DSPBuilder对直接数字频率合成器进行算法级建模和硬件实现,而将QuartusⅡ作为底层设计工具置于后台,从而最大程度地发挥了这三种工具的优势。

本设计采用DSP Builder作为Simulink中的一个工具箱,使得用FPGA设计DSP系统完全可以通过Simulink的图形化界面进行,并给出了设计过程和仿真,直到把设计文件下载到FPGA中实现硬件。

关键词:直接数字频率合成DSPBuilder Simulink QuartusII FPGAABSTRACTDirect Digital Synthesis Technology (DDS) in digital communications systems that are widely used. DSP Builder is Altera has introduced a DSP-oriented development of system-level tools, in this paper is on Direct Digital Synthesis technology on the basis of basic principles, using DSPBuilder on Direct Digital Synthesis for algorithm-level modeling and hardware, And will Quartus Ⅱ design tools at the bottom as a background to maximize the advantages of these three tools. This design uses a DSP Builder Simulink in a tool box, making DSP with FPGA design system is entirely possible through the Simulink graphical interface, and gives the design process and simulation, until the design documents downloaded to the FPGA to achieve hardware.Key words: Direct Digital Synthesis DSPBuilder Simulink QuartusII FPGA第一章绪论1.1 引言1971年,美国学者J.Tierney等人撰写的“A Digital Frequency Synthesizer”-首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新合成原理。

基于DSPBuilder的数字调制解调器设计

数据输出得到相应的数据 , 这个数据用来作为取 样地址 , 来寻址正弦 ROM 查找表, 完成相位 幅 度的变换。输出经 D /A 转换后得到相对应的波 形 , 最后经低通平滑滤波器进行滤波处理后, 即可 得到模拟正弦输出。

从图 2 可以看出 , 解调时 , 接收端收到叠加的 e 2PSK ( t ) 信号 与噪声信号 n ( t ) 后, 通 过带通滤波 器将信号频带外的噪声过滤得到信号, 然后传送 至乘法器让其与本地载波 co s c t 相乘 , 本地载波

第 24 卷第 1期 2011 年 2 月

常州工学院学报

Journa l o f Chang zhou Institute o f T echno lo g y

V o.l 24 No. 1 Feb . 2011

基于 D SP Builder的数字调制解调器设计

赵泓扬 石岩 李姗姗 李俊生

( 常州工学院电子信息与电气工程学院 , 江苏 常州 213002)

[ 3 ] 林伟雄. LC 振荡电路的分析及仿真 [ J] . 漳州师 范学院学 报 : 自然科学版 , 2007 ( 2) : 54- 56. [ 4 ] 韩冰 , 李巨友 . 利用负电阻提高 LC 振荡 电路性能 [ J] . 河 北北 方学院学报 : 自然科学版 , 2008 ( 6) : 15 - 17 . [ 5 ] 叶树亮, 李东升 . 改进型高稳定度 LC 振 荡电路的研究 [ J] . 中 国计量学院学报 , 2003 ( 3) : 174 - 177 .

2 基于 D SP Builder的调制解调系 统设计

图 3 正弦信号发生器原理 示出其开发自动化的特点和优势。 2 1 载波信号发生器的设计 根据图 3 建立的 DD S 信号发生器 , 如图 4 所 示 , 使用 D SP B uilder 软件设计 , 所有基本组件都 已经存在, 只需要对每个组件设置参数后逐一连 接拼装即可。相位累加器的位数是 32 位 , 为了减 小 ROM 的容量 , 将其截断为 10 位。为了能够同 时调制和解调需要相干的正弦波 , 因此使用了 2 个正弦 ROM 查找表同时生成相干正弦波。

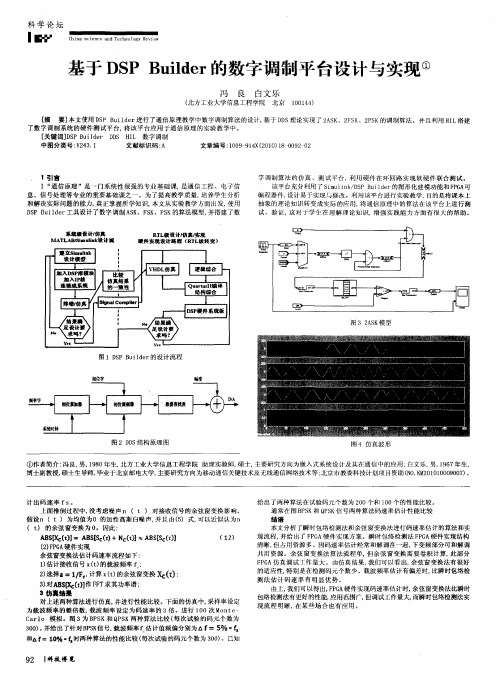

基于DSP Builder的数字调制平台设计与实现

计 出码速 率 fS 。 上 面推倒 过程 中, 没考 虑噪 声 n (t ) 对接 收信 号 的余弦 窗变换 影 响 。 假 设 n (t ) 为均值 为0 的加 性 高斯 白噪声 , 并且 由 () 式, 以近似 认 为n 5 可

( t 的余弦 窗 变换 为 0 因此 : ) 。

30 。 0) 并给 出了针对BS信号, PK 载波频率f估计值频偏分别为矗f S = % f |

字 调 制算 法 的仿 真 、测 试平 台 , 用硬 件在 环 回路 实现 软 硬件 联 合测 试 。 利 该平 台充分 利用 了 S m l n / S u l e i u i k D P B i d r的图形化 建模功 能和 F G 可 PA 编程 器件 , 设计易 于实 现与修 改 。利用 该平 台进行 实验 教学, 目的是将课 本上 抽 象 的理论 知识 转变 成实 际 的应 用 , 通信原 理 中的算 法在 该平 台上进 行 测 将 试 、 验证 , 对 于 学生 在理 解 理论 知 识, 强 实践 能 力方 面有 很 大的 帮助 。 这 增

科 学论 坛

I ■

Clccneoyv h iedcl J isnaTngew e hoR r a e

基于 D P B i e 的数字调制 平台设计与实现 ① S ul r d

冯 良 自文乐

北京 10 4) 0 14 ( 北方 工业 大学信 息工 程学 院 [ 摘 要] 文使 用 D P B i d r进 行 了通 信原 理教 学 中数字 调制算 法 的设计 , 本 S u l e 基于 D S理 沦实现 了 2 S 、2 S 、2 S D A K F K P K的调 制算法 。并且 利用 H L 建 I搭 了数字 调制 系统 的 硬件 测试 平 台, 该平 台应 用于 通信 原 理 的实验 教 学 中。 将 [ 关键 词]S u le D S H L 数字 调制 D PB idr D I 中图分 类号 :2 3 I V 4 . 文 献标识 码 : A 文章 编号 : 0 9 9 4 (0 0 1 0 2 0 10 1 X 2 1 ) 8 0 9 2

基于DSPBuilder数字信号处理课程设计

上海电力学院基于DSP Builder数字信号处理课程设计实验名称:AM调制FM调制及DDS信号专业:通信工程姓名:班级:学号:一、设计目的通过本次课程设计,巩固已学数字电路与逻辑设计的理论知识,掌握数字信号处理方法,引导学生从功能设计转向系统设计,掌握由现场可编程逻辑器件实现数字信号处理的方法,掌握现场可编程逻辑器件的应用设计,从而拓宽数字技术及处理的知识和设计能力,提高学生动手能力,培养学生分析问题与解决问题的能力。

二、设计内容本设计利用FPGA开发软件QuartusII,DSP BUILDER,MATLAB,设计实现各类波形信号的发生电路,如AM调制、FM调制、DDS控制等,进行引脚锁定、全编译通过后,完成FPGA器件Cyclone II的配置工作,并在Matlab Simulink中使用Scope显示仿真结果,在DE2开发板上下载并通过七段数码管,显示波形情况。

三、设计要求1.独立完成AM调制、FM调制、DDS控制电路的设计、译码显示电路的设计。

2.熟悉QuartusII,DSP BUILDER,MATLAB环境下系统开发设计流程。

3.在DE2上验证设计结果,并认真写出设计报告。

四、设计原理及步骤(一).AM 调制的设计AM 幅度调制函数信号可以用式)m 1(am dr ⋅+⋅=F F F 来表述,其中,dr F 、am F 、F 分别是被调制的载波信号,需要被调制的信号和调制后AM 的输出信号,它们都是有符号数,m 是调制度,10<<m 。

s (t )=m (t )*sin (t )其中m (t )是1或者是0,sin (t )是载波观察s (t )如果有波形输入的是1没波形是0。

基于DSP Builder 的数字的AM 系统如下图所示元器件的主要参数设定在这里省略介绍仿真如下图所示:通过matlab 转化成VHDL 语言通过Quartus2并下到板上验证,在这里需要添加几个模块一是分频器因为我们晶振频率较高反映在数码管上分辨不出所以叫频率降低,二是把8位的二进制传化成三位的十进制数,三是把十进制的数显示在数码管上;最后通过引脚分配输入端口有时钟clock 、使能端sw ,一个数字输入拨码开光,输出有四个数码管显示。

DSP Builder的调频信号发生器

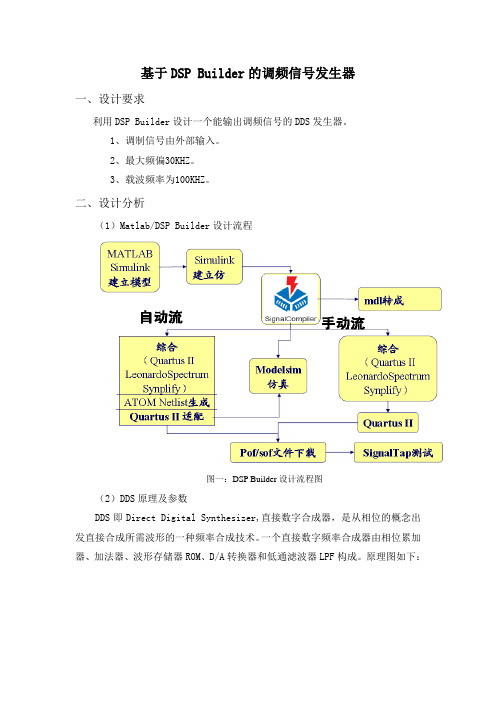

基于DSP Builder的调频信号发生器一、设计要求利用DSP Builder设计一个能输出调频信号的DDS发生器。

1、调制信号由外部输入。

2、最大频偏30KHZ。

3、载波频率为100KHZ。

二、设计分析(1)Matlab/DSP Builder设计流程图一:DSP Builder设计流程图(2)DDS原理及参数DDS即Direct Digital Synthesizer,直接数字合成器,是从相位的概念出发直接合成所需波形的一种频率合成技术。

一个直接数字频率合成器由相位累加器、加法器、波形存储器ROM、D/A转换器和低通滤波器LPF构成。

原理图如下:图二:DDS 原理框图其K 为频率控制字,P 为相位控制字、fc 为参考时钟频率,N 为相位累加器的字长,D 为ROM 数据位及D/A 转换器的字长。

相位累加器在时钟fc 的控制下以步长K 作累加,输出的N 位二进制码与相位控制字P 相加后作为波形ROM 的地址,对波形ROM 进行寻址,波形ROM 输出D 位的幅度码S (n )进D/A 转换器变成阶梯波S (t ),再经过低通滤波器平滑后就可以得到合成的信号波形。

相位寄存器每经过2N/M 个s f 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。

输出正弦波的频率计算: 0f =M 2s N f 先确定系统的分辨率f ∆,最高输出频率max f ,相位累加器位数N ,频率控制字M 。

(3)FM 调制原理设调制信号为t A t m m m ωcos )(=,载波信号为)cos()(t A t V c c ω=,则调频信号为]sin cos[)(t m t A t S m f c FM ωω+=。

三、电路设计四、Simulink仿真仿真结果如下:由上图可清楚得看到,输出信号的频率随着调制信号的变化而变化。

在调制信号的波峰处,输出信号频率达到最大值130KHZ;相应的,在调制信号的波谷处,输出信号频率为最小值70KHZ。

基于DSP的数字信号处理系统设计和实现

基于DSP的数字信号处理系统设计和实现基于DSP的数字信号处理系统设计和实现随着科技的发展和数字信号处理(DSP)技术的日益成熟,数字信号处理系统在众多领域都得到了广泛应用,例如通信、音频和视频处理、医疗影像等。

本文将探讨基于DSP的数字信号处理系统的设计和实现。

数字信号处理系统通常由硬件和软件两个主要部分组成。

硬件部分主要包括数字信号处理芯片(DSP芯片)、模数转换器(ADC)和数模转换器(DAC),以及与外部设备的连接接口。

而软件部分则是指通过编程语言(例如C语言或MATLAB)来编写算法和逻辑实现。

在设计数字信号处理系统时,首先需要明确系统的需求和目标。

比如,在通信领域中,可能需要实现信号的调制、解调、滤波和解码等功能。

而在音频处理领域,则可能需要实现声音的录制、降噪、混响和音频效果的增强等。

根据需求,我们可以选择适合的DSP芯片和外部设备。

选择合适的DSP芯片是系统设计的关键。

DSP芯片具有高性能的运算能力和强大的算法处理能力,能够高效地进行数字信号处理。

常见的DSP芯片有TI 公司的TMS320系列、ADI公司的Blackfin系列和FPGA芯片等。

不同的芯片有不同的特性和功能,因此在设计时需要根据需求选择适合的芯片。

另外,模数转换器和数模转换器也是设计中需要考虑的重要因素。

模数转换器可以将模拟信号转换为数字信号,而数模转换器可以将数字信号转换为模拟信号。

选择合适的转换器能够确保信号的质量和精度。

在硬件部分设计完成后,接下来是软件的设计和编码。

根据需求,我们可以选择合适的编程语言和开发环境。

例如,使用C语言和Code Composer Studio开发环境可以实现DSP芯片的编程,而使用MATLAB则可以方便地进行信号处理算法的开发和测试。

在软件开发中,需要利用编程语言来实现信号处理算法和逻辑。

例如,用C语言编写FIR滤波器,用MATLAB编写频谱分析算法。

同时还需要注意代码的优化和效率,以确保系统的性能和实时性。

基于DSPBuilder的DDS设计与实现.

基于DSPBuilder的DDS设计与实现DDS(DirectDigitalSynthesizer,直接数字合成器)是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术,具有易于程控,相位连续,输出频率稳定度高,频率转换速度快和分辨率高等优点。

在现代电子系统及设备的频率源设计中,DDS广泛用于接收机本振、信号发生器、仪器、跳频通信系统、雷达系统等,因此有多家器件公司先后推出了多种DDS专用电路芯片,如AD7008,AD9852,AD9955等,专用DDS芯片由于采用了特定工艺,其DDS(Direct Digital Synthesizer,直接数字合成器)是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术,具有易于程控,相位连续,输出频率稳定度高,频率转换速度快和分辨率高等优点。

在现代电子系统及设备的频率源设计中,DDS广泛用于接收机本振、信号发生器、仪器、跳频通信系统、雷达系统等,因此有多家器件公司先后推出了多种DDS专用电路芯片,如AD7008,AD9852,AD9955等,专用DDS芯片由于采用了特定工艺,其固定的控制方式使其在工作方式、频率控制等方面有时与实际系统的要求差距较大,并不能满足所有要求。

DDS中几乎所有部件都属于数字信号处理器件,所有可采用FPGA器件实现,利用FPGA可以较好地设计出符合用户系统需要的DDS系统,较好地解决了专用DDS灵活性差的问题。

本文应用模块化的设计方法,应用Altera公司的Cyclone器件和DSP Builder软件,设计出具有较高的频率分辨率和稳定性,能够实现频率及相位快速切换的DDS信号源。

在DDS的FPGA设计中,将Matlab仿真与FPGA设计相结合,使FPGA的波形仿真较为直观,大大缩短了DDS设计和调试时间。

1 DDS原理DDS结构见图1,由相位累加器、相位调制器、正弦ROM查找表、D/A构成。

相位累加器是整个DDS的核心,它由一个累加器和一个N位相位寄存器组成,每来一个时钟脉冲,相位寄存器以相位步长M增加,相位寄存器的输出与相位控制字相加,完成相位累加运算,其结果作为正弦查找表的地址,正弦ROM查找表内部存有一个完整周期正弦波的数字幅度信息,每个查找表地址对应正弦波中0°~360°范围的一个相位点,查找表把输入的地址信息映射成正弦波幅度信号,通过D/A输出,经低通滤波器后,即可得一纯净的正弦波。

第3章 DSP Builder设计 (2)

K 康芯科技 X

图3-12 Delay模块及其参数设置窗

7、放置乘法器Product模块

Altera DSP Build芯科技 X

图3-14 设置乘法单元

K 康芯科技 X

Altera DSP Builder--〉I0 & Bus库

9、放置输出端口OUTPUT

K 康芯科技 X

K 康芯科技 X

5. 设置LUT模块---正弦查找表

添加模块 Altera DSP Builder Gate & Control库

修改模块名称 参数设置

K 康芯科技 X

图9-10 LUT模块

6.放置Delay模块

Altera DSP Builder--〉Storage 库

K 康芯科技 X

图3-17 Scope模型

观察窗口

K 康芯科技 X

参数设置

K 康芯科技 X

图3-20 sinout全图

3.设置仿真激励

K 康芯科技 X

图3-22 simulink仿真Start

K 康芯科技 X

图3-23 simulink仿真设置

4、启动仿真

K 康芯科技 X

图3-24 有符号输出波形(系统级仿真 )

K 康芯科技 X

3.2 DSP Builder层次化设计

图3-49 修改子系统名

K 康芯科技 X

3.2 DSP Builder层次化设计

图3-50 修改SubSystem的端口

K 康芯科技 X

3.2 DSP Builder层次化设计

图3-51 顶层图的改变

K 康芯科技 X

3.2 DSP Builder层次化设计

图3-52 含subsystem的subsint模型

基于DSP Builder数字信号处理器的FPGA设计

器 由 于 以顺 序 方 式 工 作 使 得 数 据 处 理 速 度 较 低, 在 功 能 重 且

构 及 应用 目标 的 修 改 方 面缺 乏 灵 活 性 。而 使用 具 有 并 行 处 理 特 性 的 F G 实现 数 字 信 号 处 理 系 统 , 有 很 强 的 实 时性 和 PA 具 灵活性 , 因此 利 用 n A 实 现 数 字 信 号 处 理 成 为 数 字 信 号 处

号 处理 器设 计 方 法 。并按 照 Maa/i u n S u dr u r sI 计 流程 , 计 了一 个 l t bSm l  ̄D PB i e/ at 1设 l i l Q u 设 2阶 兀R低 通数 字滤 波 器 。 通过 Q au ur s时序 仿 真及 嵌 入 式逻 辑 分 析仪 Sga a I 件 测 试 对 设 计 进行 了验 证 。 结果 表 明 。 设 计 的 nR 滤 波 t i l pI硬 nT 所

FPGA e i n o i ia i a r c s o s d n DSP l r d sg fd g t lsg lp o e s r ba e o n Bui de

L INe g fn E n- g a

( eate tfPyi n lc oi E gnei , ia ec esU i ri, ia 10 0 C /a D p r n o hs sadEet n ni r gWennTahr nv sy Wenn7 40 , hn ) m c rc e n e t

pa t a s ae nSg aT pI T ers ls o sted sg e l ri c re t nfn t na dg o e oma c . rci lt tb sd o in la c e I. h eut h w ein d ft orc ci n o d i p r r n e h ie s i u o n f

基于DSP Builder数字滤波器的设计与实现毕业设计

摘要数字滤波器是现代数字信号处理系统的重要组成部分之一,具有模拟滤波器所无法替代的新特性,因此在通信、语音与图像处理、自动控制等领域有着广泛的应用,它对于降低噪声、提高信噪比及信号的频谱纯度等方面有着重要的意义。

数字滤波器根据单位脉冲响应的不同,可分为FIR(有限长脉冲响应)滤波器和IIR(无限长脉冲响应)滤波器,FIR的优点在于具有良好的相位特性,IIR的优点在于具有良好的幅频特性,可以根据不同的系统性能要求选择不同的滤波器。

目前滤波器的主要实现方法有三种,分别是:单片通用数字滤波器集成电路、采用DSP器件和FPGA(现场可编程门阵列)器件。

本文采用FPGA器件来实现滤波器的设计,在实现方法上先用MATLAB/Simulink工具箱建立滤波器模型,然后用SignalCompiler把Simulink的模型文件(后缀是.mdl)转化为硬件描述语言VHDL文件,最后利用QuartusII完成滤波器的仿真、配置、编译和下载。

本文最后用实例介绍了FIR数字滤波器和IIR数字滤波器的实现过程。

关键词:数字滤波器通信集成电路 DSP FPGAAbstractDigital filter is a digital signal processing system is one of the important component, analog filters cannot be replaced by the new characteristic, therefore in the communication, speech and image processing, automatic control and other fields have a wide range of applications, it can reduce noise, improve the signal to noise ratio and signal spectrum purity has important significance. Digital filter according to unit impulse response of different, can be divided into FIR ( finite impulse response filter ) and IIR ( infinite impulse response ) filter, FIR have the advantages of good phase characteristics, IIR have the advantages of good amplitude-frequency characteristics, according to different system performance requirements of different filter. The filter main realizing methods has three kinds, respectively is: the monolithic integrated circuit, digital filter with DSP device and FPGA ( field programmable gate array ) device. This paper uses FPGA to realize filter design, the realization method on the first MA TLAB / Simulink toolbox to establish filter model, then use SignalCompiler the Simulink model file ( the suffix is . MDL ) into the VHDL hardware description language file, finally using QuartusII complete filter simulation, configure, compile and download. Finally, examples of the FIR digital filter and IIR digital filter implementation process.Keywords: digital filter communication integrated circuit DSP FPGA目录1.绪论 (1)1.1研究背景 (1)1.2研究现状 (1)1.3本课题研究内容方法 (3)2.相关知识简介 (5)2.1 数字滤波器概述 (5)2.1.1 数字滤波器的定义 (5)2.1.2 数字滤波器的分类 (6)2.1.3 FIR和IIR数字滤波器的比较 (6)2.1.4 数字滤波器的设计要求和方法 (8)2.2 设计软件简介 (9)2.3 软件安装问题 (10)3.数字滤波器的总体设计方案 (12)3.1 FIR和IIR设计方法概述 (12)3.2 滤波器设计方法比较 (12)4. FIR设计实例 (16)4.1 FIR数字滤波器原理 (16)4.2 16阶FIR滤波器 (16)5. IIR设计实例 (27)5.1 IIR数字滤波器原理 (27)5.2 使用DSP B UILDER设计IIR滤波器 (30)5.2.1 4阶直接Ⅱ型IIR滤波器设计 (30)5.2.2 4阶级联型IIR滤波器设计 (32)6.总结 (38)参考文献 (40)致谢 (41)1.绪论1.1 研究背景当今,数字信号处理(DSP:Digtal Signal Processing)技术正飞速发展,它不但自成一门学科,更是以不同形式影响和渗透到其他学科:它与国民经济息息相关,与国防建设紧密相连;它影响或改变着我们的生产、生活方式,因此受到人们普遍的关注。

基于DSP Builder的数字调制器的设计

来 较为复 杂 , F G 而 P A不仅 具有灵 活性 和通 用 性 , 而 且使 用方便 、 件 测 试 和实 现 快 捷 。一 般来 说 , P 硬 F— G A的开发 流程为设 计 输 入 ( 用 V L 、 合 、 如 HD ) 综 仿

真 、 配 、 载 到器 件 。 由 于系 统 的 H L描 述需 要 适 下 D

究 方 向 : 电 子 技术 应 用 。 微

36 5

科

学

技

术

与

工

程

1 卷 1

式 ( ) 0 指 前 一 个 ck周 期 的 相 位 值 , 一 1 中,㈦ 1 B

2 0 N

K_l

13 1 Q . 6 AM 调 制 原 理

/ ,,△ 2 A /  ̄。只要 对 相位 的 量化 值 进 2rB 口 02 t

第 1卷 1

第2 期

21 年 1 01 月

科

学

技

术

与

工

程

⑥

Vo. 1 N . J n 2 1 11 o 2 a. 0 1

17 — 11 (0 1 20 5 —5 6 1 8 5 2 1 ) -35 0

S in e T c n lg n g n ei g ce c e h oo y a d En i e r n

真验 证 通 过 后 , 可 使 用 S nlC m ir MA — 即 i a o pl 把 g e T

L B S l k模 型设 计 文 件 ( md) 换 成 相 应 的 A /i i mu n . 1转 硬件描述 语 言 V D H L设 计 文 件 ( v d , .h ) 以及 用 于控

D S是一 种新 型 的频 率合 成 技 术 , 容 易实 现 D 很 频率 、 相位 和幅 度 的数 控调 制 。在 数 字 化 的调 制 解 调模块 中 , D D S取 代 了模 拟 的压 控 振 荡 器 , 大 量 被 使 用 。其典 型结 构如 图 1所示 。

基于DSP Builder的数字调制解调器设计

二进制相移键控是通过控制载波信号相 位的 变 化来传 递信 息 , 振 幅 和频 率 保持 不 变 。如 果 其

以载波 的不 同相 位直接 来表 示相应 的二进 制 数字 信 号 , 种 调 制 方 式 称 为 二 进 制 绝 对 相 移 键 控 这 ( P K) 2 S 。在 2 S 中 , 般 常用初 始相 位 0和 叮 PK 一 T 来 分别 表 示 二 进 制 数 字 基 带 信 号 的 “ ” “ ” 1和 0 。

性, 因此不能用来直接传输基带信号。一般需要 用 基带 信号对 载 波 进行 数 字 调 制 , 其 变 成适 合 使

于通信 传输 的信号形 式 。如果 利用数 字信号 取值 离 散 的特点 , 通过 开 关 键来 控 制 载 波 以实 现数 字

调 制 , 种方 法 称 为键 控 法 。本 文 所 利 用 的二 进 这

0 引言

在 数字通 信 系统 中 , 制解 调 器 是 一个 非 常 调 重 要 的器件 , 在数 字基带传 输 系统 中 , 以直 接传 可

应用。 1 数 字 调 制解 调 原 理

1 1 二 进制相 移键控 信号 的调制原 理的低 频分 量 , 多 数 的实 际信 道 具 有带 通 特 大

当数字基带信号为 “ ” 表示 已调信号与本地 1 时, 载波同相 ; 当基带信号为“ ” , 0 时 表示 已调信号与 本地 载波 反相 。二进制 相移键 控 已调信号 的时域 表达 式 为 :

制 相移键 控原 理 即对载 波 的相 位 进 行键 控 调 制 , 其 主要优 点是 抗衰减 性 、 噪声性 能较好 , 抗 频带 利 用率 较 高 , 中 、 在 高速 数据传 输系统 中得 到广泛 的

赵 泓扬 石岩 李姗姗 李俊 生

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

上海电力学院基于DSP Builder数字信号处理课程设计实验名称:AM调制FM调制及DDS信号专业:通信工程姓名:班级:学号:一、设计目的通过本次课程设计,巩固已学数字电路与逻辑设计的理论知识,掌握数字信号处理方法,引导学生从功能设计转向系统设计,掌握由现场可编程逻辑器件实现数字信号处理的方法,掌握现场可编程逻辑器件的应用设计,从而拓宽数字技术及处理的知识和设计能力,提高学生动手能力,培养学生分析问题与解决问题的能力。

二、设计内容本设计利用FPGA开发软件QuartusII,DSP BUILDER,MATLAB,设计实现各类波形信号的发生电路,如AM调制、FM调制、DDS控制等,进行引脚锁定、全编译通过后,完成FPGA器件Cyclone II的配置工作,并在Matlab Simulink中使用Scope显示仿真结果,在DE2开发板上下载并通过七段数码管,显示波形情况。

三、设计要求1.独立完成AM调制、FM调制、DDS控制电路的设计、译码显示电路的设计。

2.熟悉QuartusII,DSP BUILDER,MATLAB环境下系统开发设计流程。

3.在DE2上验证设计结果,并认真写出设计报告。

四、设计原理及步骤(一).AM 调制的设计AM 幅度调制函数信号可以用式)m 1(am dr ⋅+⋅=F F F 来表述,其中,dr F 、am F 、F 分别是被调制的载波信号,需要被调制的信号和调制后AM 的输出信号,它们都是有符号数,m 是调制度,10<<m 。

s (t )=m (t )*sin (t )其中m (t )是1或者是0,sin (t )是载波观察s (t )如果有波形输入的是1没波形是0。

基于DSP Builder 的数字的AM 系统如下图所示元器件的主要参数设定在这里省略介绍仿真如下图所示:通过matlab 转化成VHDL 语言通过Quartus2并下到板上验证,在这里需要添加几个模块一是分频器因为我们晶振频率较高反映在数码管上分辨不出所以叫频率降低,二是把8位的二进制传化成三位的十进制数,三是把十进制的数显示在数码管上;最后通过引脚分配输入端口有时钟clock 、使能端sw ,一个数字输入拨码开光,输出有四个数码管显示。

通过图形编辑法最终的实现电路为下图所示:Rom 中的mif 表格:分配引脚:波形仿真:下载到板上进行验证:可以看到的数码管的数字在以不同的值在跳动,调制前的数据没有变,调制后的数据和0交替跳动,因为输入的数字信号是1和1交替变化的,因此出现了这样的结果。

(二).DDS 控制电路的设计DDS ,即直接数字合成器,是采用数字技术的一种新型技术,他通过控制频率、相位增量的步长,产生各种不同频率的信号。

它的优点在于:有较高的频率;可以实现快速的频率切换;在频率改变时能够保持相位的连续;很容易实现频率、相位和幅度的数控调制等。

目前可采用专用或可编程逻辑芯片实现DDS ,专用的DDS 芯片产生的信号波形、功能和控制方式固定,常不能满足具体需要。

具有器件规模大、工作速度快及可编程的硬件特点,并且开发周期短,易于升级,因为非常适合用于实现DDS 。

DDS (直接数值合成器)信号发生器,通过不同的频率控制字产生各种不同频率的信号。

主要由16 位加法器、16位寄存器正弦波形数据查找表(LUT )、频率控制字组成,并且其输出计算波形为:)22cos()(c t f K t c Nπ=。

DDS 原理:DDS 的结构原理图如图所示,DDS 以数控的方式,产生频率、相位和幅度可控的正弦波。

电路包括了相位累加器、相位、正弦ROM 查找表、基准时钟源等组成。

其中前三者是DDS 结构中的数字部分,具有数字控制的功能。

图 基本DDS 结构框图如图所示,DDS 系统的核心是相位累加器,完成相位累加过程。

在基准时钟的控制下,频率控制字由累加器累加,以得到相应的相位数据,相位调制器接收相位累加器的相位输出,主要用于信号的相位调制,其输出的数据作为取样地址来寻址正弦ROM 查找表,完成相位-幅度变换,输出不同的幅度编码;再经过D/A 转换器得到相应的阶梯波;最后经低通对阶梯进行平滑处理,即可得到由频率控制字决定的连续变换输出的正弦波。

由以上原理可以得到DDS 的输出频率clk N out f B f ⋅=∆2θ,式中,θ∆B 是频率的控制字,它与系统时钟频率呈正比;clk f 是系统基准时钟的频率值;N 是相位累加器数据位宽,也是频率输入字的数据位宽。

DSP Builder 简介:DSP Builder 是美国Altera 公司推出的一个面向DSP 开发的系统级工具,他作为Matlab 的一个Simulink ,使得用FPGA 设计DSP 系统完全通过Simulink 的图形化界面进行建模、系统级仿真,设计模型可直接向硬件描述语言转换,并自动调用Quartus Ⅱ等EDA 设计软件,完成综合、网表生成以及器件适配乃至FPGA 的配置下载,使得系统描述与硬件实现有机的融合为一体,充分体现了现代技术自动化开发的特点与优势。

基于DSP Builder 的DDS 设计与仿真基于DSP Builder 的DDS 系统如图所示:图 DDS 直接频率合成器DSP Builder/Matlab Simulink 模型仿真图如下图:图 DDS 仿真图通过matlab转化成VHDL语言通过Quartus2并下到板上验证,在这里需要添加几个模块一是分频器因为我们晶振频率较高反映在数码管上分辨不出所以叫频率降低,二是把8位的二进制传化成三位的十进制数,三是把十进制的数显示在数码管上;最后通过引脚分配输入端口有时钟clock,输出由三个数码管显示。

通过图形编辑法最终的实现电路为下图所示:最后分配引脚下载到板上验证实验现象引脚分配如下图:通过matlab得到下载到DE2板子上的数据:下载到DE2板子上,观察实验现象可以看到数码管显示的是同scope里面出来的波形一直的数据,数据我通过matlab显示出来,对照可以看到其变化一致。

五. 设计结论本设计使用了DSP Builder,建立了基于DDS,AM调制系统模型,使用QuartusⅡ下到板上进行验证,结果表明该模型可以正确地产生AM调制信号、DDS信号。

本方案最大的特点是采用了DSP Builder,它作为一个算法级的设计工具,只需在Simulink中进行图形化设计,仿真通过后,即可使用Signal Compiler把MATLAB/Simulink模型文件(.mdl)转换成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的TCL脚本。

根据这些文件后续步骤可以由QuartusⅡ自己完成。

大大减少了编程的复杂度,使硬件描述更加的直观。

此外,本方案采用DDS技术,获得了较高的频率分辨率,同设计方法简单快捷,降低了实现的复杂度,而且便于修改和功能扩充。

通过该设计使我全面熟悉、掌握VHDL语言基本知识,掌握利用VHDL语言对信号发生器的编程和时序逻辑电路编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效方法,进一步提高动手能力,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

通过了本次实验使我对程序设计有了新的认识与体会,做实验不单单是在软件上运行出结果就表明对了,当其与硬件连接后能否对应现象也是非常重要的,我们不仅要学好软件,也要将硬件部分做好,多学习,多思考,在今后的运用中也将会更加的得心应手。

总之,这次课程设计我受益匪浅。

源程序:AM调制的分频器:library ieee;useentity clk_1_gen isport(clkin :in std_logic;clkout:out std_logic);end clk_1_gen;architecture behave_clk_1_gen of clk_1_gen issignal Counter:Integer RANGE 0 TO N;signal Clk: Std_Logic;beginprocess(clkin)beginif rising_edge(clkin) then --每计到4个(0~3)上升沿,输出信号翻转一次if Counter=N thenCounter<=0;Clk<=NOT Clk;elseCounter<= Counter+1;end if;end if;end process;clkout<= Clk;end behave_clk_1_gen;DDS调制的分频器:library ieee;useentity clk_1_gen isport(clkin :in std_logic;clkout:out std_logic);end clk_1_gen;architecture behave_clk_1_gen of clk_1_gen isconstant N: Integer:=390624;signal Counter:Integer RANGE 0 TO N;signal Clk: Std_Logic;beginprocess(clkin)beginif rising_edge(clkin) thenif Counter=N thenCounter<=0;Clk<=NOT Clk;elseCounter<= Counter+1;end if;end if;end process;clkout<= Clk;end behave_clk_1_gen;8选3选择器:library ieee;use eigth_to_3 isport(input :in std_logic_vector(7 downto 0); output: out std_logic_vector(3 downto 0); output1: out std_logic_vector(3 downto 0); output2: out std_logic_vector(3 downto 0) );end entity eigth_to_3;architecture three of eigth_to_3 issignal s :integer range 0 to 999;signal s1 :integer range 0 to 15;signal s2 :integer range 0 to 15;signal s3 :integer range 0 to 15;begins<=conv_integer(input);s1<=s/100;s2<=(s rem 100)/ 10;s3<=(s rem 10);output<=conv_std_logic_vector(s1,4); output1<=conv_std_logic_vector(s2,4); output2<=conv_std_logic_vector(s3,4); end;数码管显示:library ieee;useentity num_7seg isport(c:in std_logic_vector(3 downto 0);hex:out std_logic_vector(6 downto 0)); end num_7seg;architecture behave_num_7seg of num_7seg is beginwith c(3 downto 0) selecthex<= "1000000" when "0000" , --"0""1111001" when "0001" , --"1""0100100" when "0010" , --"2""0110000" when "0011" , --"3""0011001" when "0100" , --"4""0010010" when "0101" , --"5""0000010" when "0110" , --"6""1111000" when "0111" , --"7""0000000" when "1000" , --"8""0010000" when "1001" , --"9""1111111" when others; --" " end behave_num_7seg;。