Ti(德州仪器)-芯片手册-sn74ac86

SN74LS86N中文资料

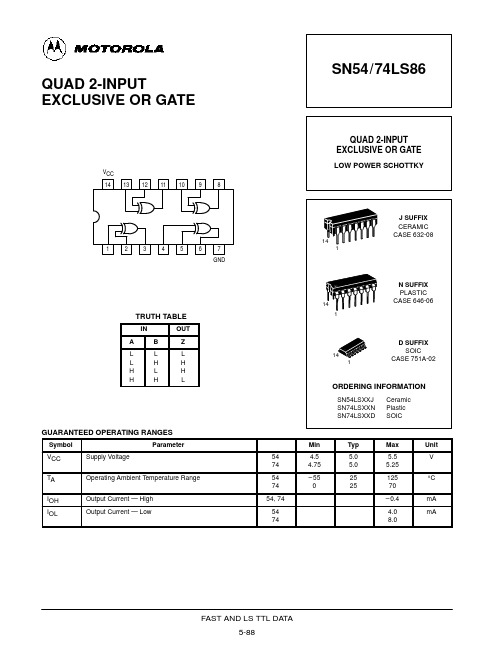

SN54/74LS86 QUAD 2-INPUT EXCLUSIVE OR GATE

QUAD 2-INPUT EXCLUSIVE OR GATE

LOW POWER SCHOTTKY

VCC 14 13 12 11 10 9 8

J SUFFIX CERAMIC CASE 632-08

GUARANTEED OPERATING RANGES

Symbol VCC TA IOH IOL Supply Voltage Operating Ambient Temperature Range Output Current — High Output Current — Low Parameter 54 74 54 74 54, 74 54 74 Min 4.5 4.75 – 55 0 Typ 5.0 5.0 25 25 Max 5.5 5.25 125 70 – 0.4 4.0 8.0 Unit V °C mA mA

FAST AND LS TTL DATA 5-89

14

1

2

3

4

6

7 GND

1

14

N SUFFIX PLASTIC CASE 646-06

1

TRUTH TABLE

IN A L L H H B L H L H OUT Z L H H L

14 1

D SUFFIX SOIC CASE 751A-02

ORDERING INFORMATION

SN54LSXXJ SN74LSXXN SN74LSXXD Ceramic Plastic SOIC

VCC = MAX, VIN = 2.7 V VCC = MAX, VIN = 7.0 V VCC = MAX, VIN = 0.4 V VCC = MAX VCC = MAX

ST M74HC86 数据手册

1/8July 2001sHIGH SPEED:t PD = 12ns (TYP .) at V CC = 6V sLOW POWER DISSIPATION:I CC = 1µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsWIDE OPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 86DESCRIPTIONThe M74HC86 is an high speed CMOS QUAD EXCLUSIVE OR GATE fabricated with silicon gate C 2MOS technology.Input and output buffer are installed, which enables high noise immunity and stable output.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC86QUAD EXCLUSIVE OR GATEPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & R DIP M74HC86B1R SOP M74HC86M1RM74HC86RM13TR TSSOPM74HC86TTRM74HC862/8INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSPIN No SYMBOL NAME AND FUNCTION 1, 4, 9, 121A to 4A Data Inputs 2, 5, 10, 131B to 4B Data Inputs 3, 6, 8, 111Y to 4Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageA B Y L L L L H H H L H HHLSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA I CC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature -55 to 125°C t r , t fInput Rise and Fall TimeV CC = 2.0V 0 to 1000ns V CC = 4.5V 0 to 500ns V CC = 6.0V0 to 400nsM74HC863/8DC SPECIFICATIONSAC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /4 (per gate)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V 4.53.15 3.15 3.156.04.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.81.8V OHHigh Level Output Voltage2.0I O =-20 µA 1.9 2.0 1.9 1.9V4.5I O =-20 µA 4.4 4.5 4.4 4.46.0I O =-20 µA5.96.0 5.9 5.94.5I O =-4.0 mA 4.18 4.31 4.13 4.106.0I O =-5.2 mA 5.685.8 5.635.60V OLLow Level Output Voltage2.0I O =20 µA 0.00.10.10.1V 4.5I O =20 µA 0.00.10.10.16.0I O =20 µA 0.00.10.10.14.5I O =4.0 mA 0.170.260.330.406.0I O =5.2 mA 0.180.260.330.40I I Input Leakage Current6.0V I = V CC or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current6.0V I = V CC or GND11020µA SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime 2.0307595110ns 4.581519226.07131619t PLH t PHL Propagation DelayTime2.0561********ns4.5142228336.012192428SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.05101010pF C PDPower Dissipation Capacitance (note 1)5.026pFM74HC864/8TEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)WAVEFORM : PROPAGATION DELAY TIME(f=1MHz; 50% duty cycle)M74HC86Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 8/8。

CD74AC86中文资料

0.05

3

0.05

4.5

12

3

24

4.5

75

5.5

(Note 6, 7)

50

5.5

(Note 6, 7)

25oC MIN MAX

-40oC TO 85oC

MIN MAX

-55oC TO 125oC

MIN MAX

UNITS

1.2

-

1.2

-

1.2

-

V

2.1

-

2.1

-

2.1

-

V

3.85

-

3.85

-

3.85

DC Electrical Specifications

PARAMETER AC TYPES High Level Input Voltage Low Level Input Voltage High Level Output Voltage

Low Level Output Voltage

TEST

CONDITIONS

• Speed of Bipolar FAST™/AS/S with Significantly Reduced Power Consumption

• Balanced Propagation Delays

• AC Types Feature 1.5V to 5.5V Operation and Balanced Noise Immunity at 30% of the Supply

CD54ACT86F3A CD74ACT86E

CD74ACT86M

-55 to 125

0 to 70oC, -40 to 85, -55 to 125

0 to 70oC, -40 to 85, -55 to 125

SN74LS86中文资料

LOW POWER SCHOTTKYDevice Package Shipping SN74LS86N 14 Pin DIP 2000 Units/Box SN74LS86D14 PinSOIC D SUFFIX CASE 751A2500/T ape & ReelPLASTIC N SUFFIX CASE 646141141ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others.SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. PUBLICATION ORDERING INFORMATIONASIA/PACIFIC: LDC for ON Semiconductor – Asia SupportPhone:303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time)Toll Free from Hong Kong 800–4422–3781Email: ONlit–asia@JAPAN: ON Semiconductor, Japan Customer Focus Center4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–8549Phone: 81–3–5487–8345Email: r14153@Fax Response Line:303–675–2167。

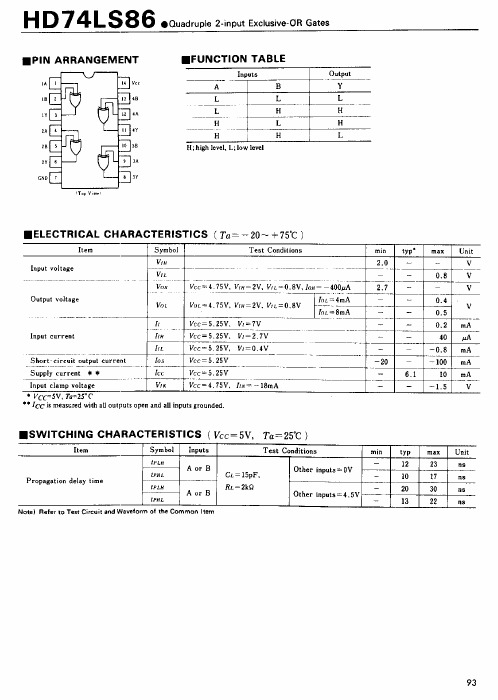

74ls86中文资料_数据手册_参数

Singapore 049318

Harbour City, Canton Road, Tsim Sha Tsui,

Tel: 535-2100

Kowloon, Hong Kong

Fax: 535-1533

Tel: <852> (2) 735 9218

Fax: <852> (2) 730 0281

Hitachi Asia Ltd.

Hitachi Europe GmbH Electronic components Group Dornacher Stra§e 3 D-85622 Feldkirchen, Munich Germany Tel: <49> (89) 9 9180-0 Fax: <49> (89) 9 29 30 00

DP-14 Conforms Conforms 0.97 g

10.06 10.5 Max

14

8

5.5

1

7

1.42 Max

0.10 ± 0.10

1.27

*0.42 ± 0.08 0.40 ± 0.06

0.15 0.12 M

*Dimension including the plating thickness Base material dimension

For further information write to:

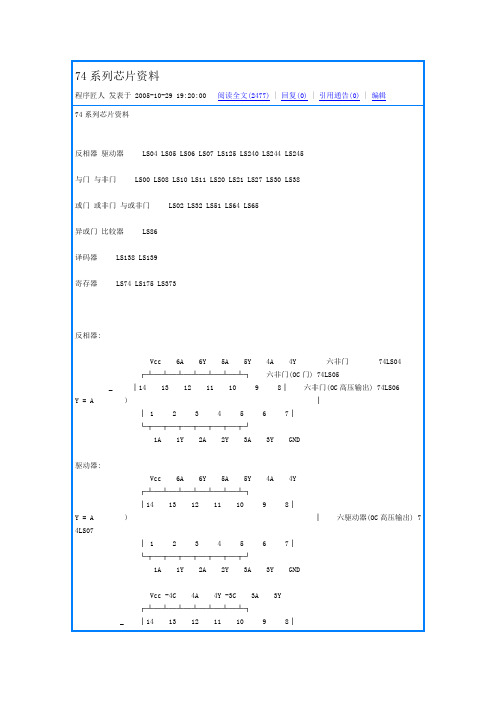

74系列芯片功能大全

74系列芯片功能大全同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx、74HCxx的使用说明可参阅74xx的使用说明。

有些型号里包含了几种型号,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的功能。

7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器常用74系列标准数字电路的中文名称资料器件代号器件名称 74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门 (OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√。

74系列各个芯片详细介绍

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门 74LS30│ 1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门 74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门 74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门 74S64 74S65(OC门) │14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器 74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(OC)TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

SN74HC86NSRE4中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)84046012A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC8404601CA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC8404601DA ACTIVE CFP W141TBD Call TI Level-NC-NC-NC JM38510/65202BCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SN54HC86J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCSN74HC86D ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86DE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86DRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86DT ACTIVE SOIC D14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86DTE4ACTIVE SOIC D14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74HC86NE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74HC86NSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86NSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86PW ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86PWE4ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HC86PWLE OBSOLETE TSSOP PW14TBD Call TI Call TISN74HC86PWR ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86PWRE4ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86PWT ACTIVE TSSOP PW14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HC86PWTE4ACTIVE TSSOP PW14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54HC86FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54HC86J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54HC86W ACTIVE CFP W141TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

TI SN74CBTLV3257-EP 低电压4位2选1 FET多路复用器 多路信号分离器说明书

PW PACKAGE Product Folder Order Now Technical Documents Tools &SoftwareSupport &CommunitySN74CBTLV3257-EPZHCSJO7A –MAY 2008–REVISED MAY 2019SN74CBTLV3257-EP 低电压4位2选1FET 多路复用器/多路信号分离器(1)组件资质符合JEDEC 和行业标准,确保在更宽泛的工作温度范围内可靠运行。

这包括但不限于高加速应力测试(HAST)或偏压85/85、温度循环、热压器或无偏压HAST 、电迁移、金属间键合寿命和模塑化合物寿命。

这些资质测试不能作为在超出额定性能和环境限制的条件下使用此组件的依据。

1特性•受控基线–一个组装地点–一个测试地点–一个制造地点•更宽泛的工作温度范围-55°C 至125°C •为制造资源减少(DMS)提供增强型支持•改进了产品变更通知•资质谱系(1)•两个端口间使用5Ω开关连接•支持在数据I/O 端口进行轨至轨开关•I off 支持局部断电模式运行•闩锁性能超过100mA ,符合JESD 78II 类规范•ESD 保护性能超过JESD 22规范要求–2000V 人体模型(A114-A)–200V 机器模型(A115-A)2应用•支持国防、航天和医疗应用3说明SN74CBTLV3257是一款4位2选1高速FET 多路复用器/多路信号分离器。

此开关具有低通态电阻,可以在最短传播延迟情况下建立连接。

选择(S)输入控制数据流。

当输出使能(OE)输入为高电平时,FET 多路复用器/多路解复用器被禁用。

该器件完全适用于I off 为了部分断电的应用。

I off 特性可确保在关断时防止损坏电流通过器件回流。

该器件可在关断时提供隔离。

为了确保加电或断电期间的高阻抗状态,OE 应通过一个上拉电阻器被连接至V CC ;该电阻器的最小值由驱动器的电流吸入能力来决定。

CD74HC86中文资料

-55 to 125 -55 to 125 -55 to 125

Wafer Wafer Die

• Adders and Subtractors

NOTE: When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

Pinout

CD74HC86, CD74HCT86 (PDIP, SOIC) TOP VIEW

1A 1 1B 2 1Y 3 2A 4 2B 5 2Y 6 GND 7

14 VCC 13 4B 12 4A 11 4Y 10 3B 9 3A 8 3Y

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

The Harris CD74HC86, CD74HCT86 contain four independent EXCLUSIVE OR gates in one package. They provide the system designer with a means for implementation of the EXCLUSIVE OR function. Logic gates utilize silicon gate CMOS technology to achieve operating speeds similar to LSTTL gates with the low power consumption of standard CMOS integrated circuits. All devices have the ability to drive 10 LSTTL loads. The 74HCT logic family is functionally pin compatible with the standard 74LS logic family.

TTL74系列芯片大全(中英文对照)

TTL74系列芯片大全(中英文对照)7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器SN74LSOO四2输入与非门SN74LSO2四2输入或非门SN74LS04六反相器SN74LS06六反相缓冲器/驱动器SN74LS08四2输入与非门SN74LS10三3输入与非门SN74LS12三3输入与非门SN74LS14六反相器.斯密特触发SN74LS16六反相缓冲器/驱动器SN74LS20双4输入与门SN74LS22双4输入与门SN74LS26四2输入与非门SN74LS28四输入端或非缓冲器SN74LS32四2输入或门SN74LS37四输入端与非缓冲器SN74LS40四输入端与非缓冲器SN74LS47BCD-七段译码驱动器SN74LS49BCD-七段译码驱动器SN74LS54四输入与或非门SN74LS63六电流读出接口门SN74LS74双D触发器SN74LS76双J-K触发器SN74LS83双J-K触发器SN74LS86四2输入异或门SN74LS904位十进制波动计数器SN74LS9212分频计数器SN74LS965位移位寄存器SN74LS109正沿触发双J-K触发器SN74LS113双J-K负沿触发器SN74LS121单稳态多谐振荡器SN74LS123双稳态多谐振荡器SN74LS125三态缓冲器SN74LS1313-8线译码器SN74LS13313输入与非门SN74LS137地址锁存3-8线译码器SN74LS139双2-4线译码-转换器SN74LS14710-4线优先编码器SN74LS153双4选1数据选择器SN74LS155双2-4线多路分配器SN74LS157四2选1数据选择器SN74LS160同步BDC十进制计数器SN74LS162同步BDC十进制计数器SN74LS1648位串入并出移位寄存SN74LS1668位移位寄存器SN74LS1694位可逆同步计数器SN74LS17216位多通道寄存器堆SN74LS1746D型触发器SN74LS176可预置十进制计数器SN74LS182超前进位发生器SN74LS18964位随机存储器SN74LS191二进制同步可逆计数器SN74LS193二进制可逆计数器SN74LS195并行存取移位寄存器SN74LS197可预置二进制计数器SN74LS2383-8线译码/多路转换器SN74LS241八缓冲/驱动/接收器SN74LS243四总线收发器SN74LS245八总线收发器SN74LS248BCD-七段译码驱动器SN74LS251三态8-1数据选择器SN74LS256双四位选址锁存器SN74LS258四2选1数据选择器SN74LS260双5输入或非门SN74LS266四2输入异或非门SN74LS275七位树型乘法器SN74LS279四R-S触发器SN74LS2834位二进制全加器SN74LS2934位二进制计数器SN74LS365六缓冲器带公用启动器SN74LS367六总线三态输出缓冲器SN74LS3738D锁存器SN74LS3754位双稳锁存器SN74LS386四2输入异或门SN74LS393双4位二进制计数器SN74LS5748位D型触发器SN74LS6848位数字比较器SN74LSO1四2输入与非门SN74LS03四2输入与非门SN74LS05六反相器SN74LS07六缓冲器/驱动器SN74LS09四2输入与非门SN74LS11三3输入与非门SN74LS13三3输入与非门SN74LS15三3输入与非门SN74LS17六反相缓冲器/驱动器SN74LS21双4输入与门SN74LS25双4输入与门SN74LS27三3输入与非门SN74LS30八输入端与非门SN74LS33四2输入或门SN74LS38双2输入与非缓冲器SN74LS42BCD-十进制译码器SN74LS48BCD-七段译码驱动器SN74LS51三3输入双与或非门SN74LS55四4输入与或非门SN74LS73双J-K触发器SN74LS754位双稳锁存器SN74LS78双J-K触发器SN74LS854位幅度比较器SN74LS884位全加器SN74LS918位移位寄存器SN74LS93二进制计数器SN74LS954位并入并出寄存器SN74LS107双J-K触发器SN74LS112双J-K负沿触发器SN74LS114双J-K负沿触发器SN74LS122单稳态多谐振荡器SN74LS124双压控振荡器SN74LS126四3态总线缓冲器SN74LS132二输入与非触发器SN74LS136四异或门SN74LS1383-8线译码/转换器SN74LS145BCD十进制译码/驱动器SN74LS1488-3线优先编码器SN74LS1518选1数据选择器SN74LS1544-16线多路分配器SN74LS156双2-4线多路分配器SN74LS158四2选1数据选择器SN74LS1614位二进制计数器SN74LS1634位二进制计数器SN74LS1658位移位寄存器SN74LS1684位可逆同步计数器SN74LS1704x4位寄存器堆SN74LS1734D型寄存器SN74LS1754D烯触发器SN74LS181运算器/函数发生器SN74LS183双进位保存全价器SN74LS190同步BCD十进制计数器SN74LS192BCD-同步可逆计数器SN74LS194双向通用移位寄存器SN74LS196可预置十进制计数器SN74LS221双单稳态多谐振荡器SN74LS240八缓冲/驱动/接收器SN74LS242四总线收发器SN74LS244八缓冲/驱动/接收器SN74LS247BCD-七段译码驱动器SN74LS249BCD-七段译码驱动SN74LS253双三态4-1数据选择器SN74LS257四3态2-1数据选择器SN74LS2598位可寻址锁存器SN74LS2612x4位二进制乘发器SN74LS273八进制D型触发器SN74LS276四J-K触发器SN74LS2809位奇偶数发生校检器SN74LS290十进制计数器SN74LS2954位双向通用移位寄存器SN74LS366六缓冲器带公用启动器SN74LS368六总线三态输出反相器SN74LS3748D触发器SN74LS3778位单输出D型触发器SN74LS390双十进制计数器SN74LS5738位三态输出D型锁存器SN74LS6708位数字比较器SN74HC00 四2输入与非门SN74HC02 四2输入或非门SN74HC03 四2输入或非门SN74HC04 六反相器SN74HC05 六反相器SN74HC08 四2输入与门SN74HC10 三3输入与非门SN74HC11 三3输入与门SN74HC14 六反相器/斯密特触发SN74HC20 双四输入与门SN74HC21 双四输入与非门SN74HC27 三3输入与非门SN74HC30 八输入端与非门SN74HC32 四2输入或门SN74HC42 BCD十进制译码器SN74HC73 双J-K触的器SN74HC76 双J-K触的器SN74HC86 四2输入异或门SN74HC107 双J-K触发器SN74HC113 双J-K负沿触发器SN74HC123 双稳态多谐振荡器SN74HC125 三态缓冲器SN74HC126 四三态总线缓冲器SN74HC132 二输入与非缓冲器SN74HC137 二输入与非缓冲器SN74HC138 3-8线译码/解调器SN74HC139 双2-4线译码/解调器SN74HC148 8选1数据选择器SN74HC151 双4选1数据选择器SN74HC154 4-16线多路分配器SN74HC157 四2选1数据选择器SN74HC161 4位二进制计数器SN74HC163 4位二进制计数器SN74HC164 8位串入并出移位寄存器SN74HC165 8位移位寄存器SN74HC173 4D型触发器SN74HC174 6D触发器SN74HC175 4D型触发器SN74HC191 二进制同步可逆计数器SN74HC221 双单稳态多谐振荡器SN74HC238 3-8线译码器SN74HC240 八缓冲器SN74HC244 八总线3态输出缓冲器SN74HC245 八总线收发器SN74HC251 三态8-1数据选择器SN74HC259 8位可寻址锁存器SN74HC266 四2输入异或非门SN74HC273 8D型触发器SN74HC367 六缓冲器/总线驱动器SN74HC368 六缓冲器/总线驱动器SN74HC373 8D锁存器SN74HC374 8D触发器SN74HC393 双4位二进制计数器SN74HC541 8位三态输出缓冲器SN74HC573 8位三态输出D 型锁存器SN74HC574 8D型触发器SN74HC595 8位移位寄存器/锁存器SN74HC4028 7级二进制串行加数器SN74HC4046 锁相环SN74HC4051 8选1模拟开关SN74HC4053 三2选1模拟开关SN74HC4060 14位计数/分频/振荡器SN74HC4066 四双相模拟开关SN74HC4078 3输入端三或门SN74HC4511 7段锁存/译码驱动器SN74HC4520 双二进制加法计数器74F00 高速四2输入与非门74F02 高速四2输入或非门74F04 高速六反相器74F08 高速四2输入与门74F10 高速三3输入与门74F14 高速六反相斯密特触发74F32 高速四2输入或门74F38 高速四2输入或门74F74 高速双D型触发器74F86 高速四2输入异或门74F139 高速双2-4线译码/驱动器74F151 高速双2-4线译码/驱动器74F153 高速双4选1数据选择器74F157 高速双4选1数据选择器74F161 高速6D型触发器74F174 高速6D型触发器74F175 高速4D型触发器74F244 高速八总线3态缓冲器74F245 高速八总线收发器74F373 高速8D锁存器SN74HCT04 六反相器。

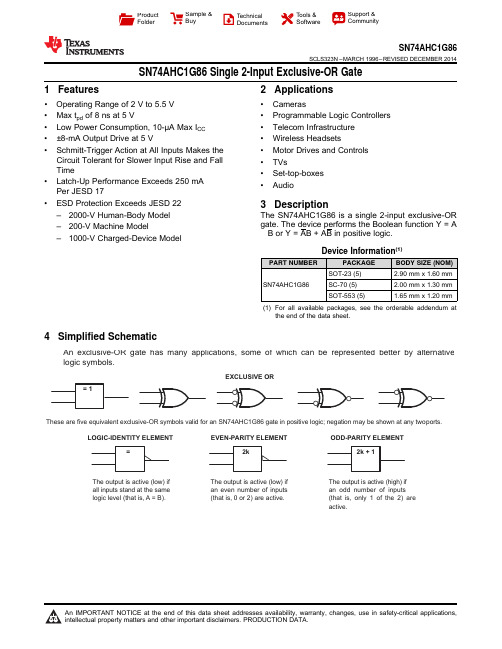

Ti(德州仪器)-芯片手册-sn74ahc1g86

An exclusive-OR gate has many applications,some of which can be represented better by alternative logic symbols.=1EXCLUSIVE ORThese are five equivalent exclusive-OR symbols valid for an SN74AHC1G86gate in positive logic;negation may be shown at any twoports.=2k2k +1LOGIC-IDENTITY ELEMENTEVEN-PARITY ELEMENTODD-PARITY ELEMENTThe output is active (low)if all inputs stand at the same logic level (that is,A = B).The output is active (low)if an even number of inputs (that is,0 or 2) are active.The output is active (high)if an odd number of inputs (that is,only 1of the2)areactive.Product FolderSample &BuyTechnical Documents Tools &SoftwareSupport &CommunitySN74AHC1G86SCLS323N –MARCH 1996–REVISED DECEMBER 2014SN74AHC1G86Single 2-Input Exclusive-OR Gate1Features2Applications•Operating Range of 2V to 5.5V •Cameras•Max t pd of 8ns at 5V•Programmable Logic Controllers •Low Power Consumption,10-µA Max I CC •Telecom Infrastructure •±8-mA Output Drive at 5V•Wireless Headsets•Schmitt-Trigger Action at All Inputs Makes the •Motor Drives and Controls Circuit Tolerant for Slower Input Rise and Fall •TVsTime•Set-top-boxes •Latch-Up Performance Exceeds 250mA •AudioPer JESD 17•ESD Protection Exceeds JESD 223Description–2000-V Human-Body Model The SN74AHC1G86is a single 2-input exclusive-OR gate.The device performs the Boolean function Y =A –200-V Machine Model×B or Y =+in positive logic.–1000-V Charged-Device ModelDevice Information (1)PART NUMBER PACKAGE BODY SIZE (NOM)SOT-23(5) 2.90mm x 1.60mm SN74AHC1G86SC-70(5) 2.00mm x 1.30mm SOT-553(5)1.65mm x 1.20mm(1)For all available packages,see the orderable addendum atthe end of the data sheet.4Simplified SchematicAn IMPORTANT NOTICE at the end of this data sheet addresses availability,warranty,changes,use in safety-critical applications,intellectual property matters and other important disclaimers.PRODUCTION DATA.SN74AHC1G86SCLS323N–MARCH1996–REVISED Table of Contents1Features..................................................................19Detailed Description. (8)9.1Overview (8)2Applications (1)9.2Functional Block Diagram (8)3Description (1)9.3Feature Description (8)4Simplified Schematic (1)9.4Device Functional Modes (8)5Revision History (2)10Application and Implementation (9)6Pin Configuration and Functions (3)10.1Application Information (9)7Specifications (4)10.2Typical Application (9)7.1Absolute Maximum Ratings (4)11Power Supply Recommendations (10)7.2ESD Ratings (4)12Layout (11)7.3Recommended Operating Conditions (4)12.1Layout Guidelines (11)7.4Thermal Information (5)12.2Layout Example (11)7.5Electrical Characteristics (5)13Device and Documentation Support (11)7.6Switching Characteristics,V CC=3.3V±0.3V (5)13.1Trademarks (11)7.7Switching Characteristics,V CC=5V±0.5V (5)13.2Electrostatic Discharge Caution (11)7.8Operating Characteristics (6)13.3Glossary (11)7.9Typical Characteristics (6)14Mechanical,Packaging,and Orderable 8Parameter Measurement Information (7)Information (11)5Revision HistoryChanges from Revision M(June2005)to Revision N Page •Added Applications,Device Information table,Pin Functions table,ESD Ratings table,Thermal Information table, Typical Characteristics,Feature Description section,Device Functional Modes,Application and Implementationsection,Power Supply Recommendations section,Layout section,Device and Documentation Support section,and Mechanical,Packaging,and Orderable Information section (1)•Deleted Ordering Information table (1)•Changed MAX operating temperature to125°C in Recommended Operating Conditions table (4)2Submit Documentation Feedback Copyright©1996–2014,Texas Instruments IncorporatedProduct Folder Links:SN74AHC1G86A V CCYBGNDDBV PACKAGE (TOP VIEW)DCK PACKAGE (TOPVIEW)A V CCYB GNDA V CC YB GNDDRL PACKAGE (TOP VIEW)See mechanical drawings for dimensions.SN74AHC1G86SCLS323N –MARCH 1996–REVISED DECEMBER 20146Pin Configuration and FunctionsPin FunctionsPINTYPE DESCRIPTION 1A I Input A 2B I Input B 3GND —Ground Pin 4Y O Output Y 5V CC—Power PinCopyright ©1996–2014,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Links:SN74AHC1G86SN74AHC1G86SCLS323N–MARCH1996–REVISED 7Specifications7.1Absolute Maximum Ratings(1)over operating free-air temperature range(unless otherwise noted)MIN MAX UNITV CC Supply voltage range–0.57VV I Input voltage range(2)–0.57VV O Output voltage range(2)–0.5V CC+0.5VI IK Input clamp current V I<0–20mAI OK Output clamp current V O<0or V O>V CC±20mAI O Continuous output current V O=0to V CC±25mAContinuous channel current through V CC or GND±50mAT stg Storage temperature range–65150°C (1)Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input and output voltage ratings may be exceeded if the input and output current ratings are observed.7.2ESD RatingsVALUE UNITHuman body model(HBM),per ANSI/ESDA/JEDEC JS-001,all pins(1)2000V(ESD)Electrostatic discharge VCharged device model(CDM),per JEDEC specification JESD22-C101,1000all pins(2)(1)JEDEC document JEP155states that500-V HBM allows safe manufacturing with a standard ESD control process.(2)JEDEC document JEP157states that250-V CDM allows safe manufacturing with a standard ESD control process.7.3Recommended Operating Conditionsover operating free-air temperature range(unless otherwise noted)(1)MIN MAX UNIT V CC Supply voltage2 5.5VV CC=2V 1.5V IH High-level input voltage V CC=3V 2.1VV CC=5.5V 3.85V CC=2V0.5V IL Low-level input voltage V CC=3V0.9VV CC=5.5V 1.65V I Input voltage0 5.5VV O Output voltage0V CC VV CC=2V–50µAI OH High-level output current V CC=3.3V±0.3V–4mAV CC=5V±0.5V–8V CC=2V50µAI OL Low-level output current V CC=3.3V±0.3V4mAV CC=5V±0.5V8V CC=3.3V±0.3V100∆t/∆v Input transition rise or fall rate ns/VV CC=5V±0.5V20T A Operating free-air temperature–40125°C (1)All unused inputs of the device must be held at V CC or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs(SCBA004).4Submit Documentation Feedback Copyright©1996–2014,Texas Instruments IncorporatedProduct Folder Links:SN74AHC1G86SN74AHC1G86 SCLS323N–MARCH1996–REVISED DECEMBER20147.4Thermal InformationSN74AHC1G86THERMAL METRIC(1)DBV DCK DRL UNIT5PINSRθJA Junction-to-ambient thermal resistance231.3287.6328.7RθJC(top)Junction-to-case(top)thermal resistance119.997.7105.1RθJB Junction-to-board thermal resistance60.665.150.3°C/WψJT Junction-to-top characterization parameter17.8 2.0 6.9ψJB Junction-to-board characterization parameter60.164.2148.4(1)For more information about traditional and new thermal metrics,see the IC Package Thermal Metrics application report(SPRA953).7.5Electrical Characteristicsover recommended operating free-air temperature range(unless otherwise noted)T A=25°C–40°C to85°C–40°C to125°C PARAMETER TEST CONDITIONS V CC UNITMIN TYP MAX MIN MAX MIN MAX2V 1.92 1.9 1.9I OH=–50µA3V 2.93 2.9 2.9V OH 4.5V 4.4 4.5 4.4 4.4VI OH=–4mA3V 2.58 2.48 2.48I OH=–8mA 4.5V 3.94 3.8 3.82V0.10.10.1I OL=50µA3V0.10.10.1V OL 4.5V0.10.10.1VI OL=4mA3V0.360.440.44I OL=8mA 4.5V0.360.440.440V toI I V I=5.5V or GND±0.1±1±1µA5.5VI CC V I=V CC or GND,I O=0 5.5V11010µAC i V I=V CC or GND5V4101010pF7.6Switching Characteristics,V CC=3.3V±0.3Vover recommended operating free-air temperature range(unless otherwise noted)(see Figure3)FROM TO T A=25°C–40°C to85°C–40°C to125°CLOADPARAMETER UNIT (INPUT)(OUTPUT)CAPACITANCE MIN TYP MAX MIN MAX MIN MAXt PLH711113114A orB YC L=15pF nst PHL711113114t PLH9.514.5116.5117.5A orB YC L=50pF nst PHL9.514.5116.5117.57.7Switching Characteristics,V CC=5V±0.5Vover recommended operating free-air temperature range(unless otherwise noted)(see Figure3)FROM TO T A=25°C–40°C to85°C–40°C to125°CLOADPARAMETER UNIT (INPUT)(OUTPUT)CAPACITANCE MIN TYP MAX MIN MAX MIN MAXt PLH 4.8 6.81818.6A orB YC L=15pF nst PHL 4.8 6.81818.6t PLH 6.38.8110111A orB YC L=50pF nst PHL 6.38.8110111Copyright©1996–2014,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Links:SN74AHC1G86SN74AHC1G86SCLS323N–MARCH1996–REVISED 7.8Operating CharacteristicsV CC=5V,T A=25°CPARAMETER TEST CONDITIONS TYP UNITC pd Power dissipation capacitance No load,f=1MHz18pF7.9Typical Characteristics6Submit Documentation Feedback Copyright©1996–2014,Texas Instruments IncorporatedProduct Folder Links:SN74AHC1G86V CCV CC0V0VVOLTAGE WAVEFORMSSETUP AND HOLD TIMESData InputInputOut-of-PhaseOutputIn-PhaseOutputTiming InputVOLTAGE WAVEFORMSPROPAGATION DELAY TIMESINVERTINGAND NONINVERTING OUTPUTSOutputControlOutputWaveform1S1at V CC(see NoteB)OutputWaveform2S1at GND(see Note B)V OLV OH≈V CC0V≈0VV CCVOLTAGE WAVEFORMSENABLE AND DISABLE TIMESLOW-AND HIGH-LEVEL ENABLINGt PLH/t PHLt PLZ/t PZLt PHZ/t PZHOpen DrainOpenV CCGNDV CCTEST S1V CC0VVOLTAGE WAVEFORMSPULSE DURATIONInputNOTES: A.C L includes probe and jig capacitance.B.Waveform1is for an output with internal conditions such that the output is low,except when disabled by the output control.Waveform2is for an output with internal conditions such that the output is high,except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics:PRR≤1MHz,Z O=50Ω, t r≤3ns,t f≤3ns.D.The outputs are measured one at a time,with one input transition per measurement.From OutputUnder Test(seeLOAD CIRCUIT FOR3-STATE AND OPEN-DRAIN OUTPUTSFrom OutputUnder Test(seeLOAD CIRCUIT FORTOTEM-POLE OUTPUTSOpenSN74AHC1G86 SCLS323N–MARCH1996–REVISED DECEMBER2014 8Parameter Measurement InformationFigure3.Load Circuit and Voltage WaveformsCopyright©1996–2014,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Links:SN74AHC1G86An exclusive-OR gate has many applications,some of which can be represented better by alternative logic symbols.=1EXCLUSIVE ORThese are five equivalent exclusive-OR symbols valid for an SN74AHC1G86gate in positive logic;negation may be shown at any twoports.=2k2k +1LOGIC-IDENTITY ELEMENTEVEN-PARITY ELEMENTODD-PARITY ELEMENTThe output is active (low)if all inputs stand at the same logic level (that is,A = B).The output is active (low)if an even number of inputs (that is,0 or 2) are active.The output is active (high)if an odd number of inputs (that is,only 1of the 2)are active.SN74AHC1G86SCLS323N –MARCH 1996–REVISED DECEMBER 20149Detailed Description9.1OverviewThe SN74AHC1G86is a single 2-input exclusive-OR gate.The device performs the Boolean function Y =A ×B or Y =AB +AB in positive logic.A common application is as a true or complementary element.If one of the inputs is low,the other input is reproduced in true form at the output.If one of the inputs is high,the signal on the other input is reproduced inverted at the output.9.2Functional Block DiagramFigure 4.Exclusive-OR Logic9.3Feature Description•Wide operating voltage range –Operates from 2V to 5.5V •Allows down-voltage translation –Inputs accept voltages to 5.5V•The low drive and slow edge rates will minimize overshoot and undershoot on the outputs9.4Device Functional ModesTable 1.Function TableINPUTS OUTPUTYA B L L L L H H H L H HHL8Submit Documentation FeedbackCopyright ©1996–2014,Texas Instruments IncorporatedProduct Folder Links:SN74AHC1G86SN74AHC1G86 SCLS323N–MARCH1996–REVISED DECEMBER201410Application and ImplementationNOTEInformation in the following applications sections is not part of the TI componentspecification,and TI does not warrant its accuracy or completeness.TI’s customers areresponsible for determining suitability of components for their purposes.Customers shouldvalidate and test their design implementation to confirm system functionality.10.1Application InformationSN74AHCT1G125is a low-drive CMOS device that can be used for a multitude of bus interface type applications where output ringing is a concern.The low drive and slow edge rates will minimize overshoot and undershoot on the outputs.The inputs can accept voltages to5.5V at any valid V CC making it Ideal for down translation.10.2Typical ApplicationFigure5.Typical Application Schematic10.2.1Design RequirementsThis device uses CMOS technology and has balanced output drive.Care should be taken to avoid bus contention because it can drive currents that would exceed maximum limits.The high drive will also create fast edges into light loads,so routing and load conditions should be considered to prevent ringing.10.2.2Detailed Design Procedure1.Recommended Input Conditions–For rise time and fall time specifications,seeΔt/ΔV in the Recommended Operating Conditions table.–For specified High and low levels,see V IH and V IL in the Recommended Operating Conditions table.–Inputs are overvoltage tolerant allowing them to go as high as5.5V at any valid V CC.2.Recommend Output Conditions–Load currents should not exceed25mA per output and50mA total for the part.–Outputs should not be pulled above V CC.Copyright©1996–2014,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Links:SN74AHC1G86SN74AHC1G86SCLS323N–MARCH1996–REVISED Typical Application(continued)10.2.3Application CurvesFigure6.Switching Characteristics Comparison11Power Supply RecommendationsThe power supply can be any voltage between the MIN and MAX supply voltage rating located in the Recommended Operating Conditions table.Each V CC pin should have a good bypass capacitor to prevent power disturbance.For devices with a single supply,0.1μF is recommended.If there are multiple V CC pins,0.01μF or0.022μF is recommended for each power pin.It is acceptable to parallel multiple bypass caps to reject different frequencies of noise.A0.1μF and 1μF are commonly used in parallel.The bypass capacitor should be installed as close to the power pin as possible for best results.10Submit Documentation Feedback Copyright©1996–2014,Texas Instruments IncorporatedProduct Folder Links:SN74AHC1G86V ccInputOutputInputOutputSN74AHC1G86 SCLS323N–MARCH1996–REVISED DECEMBER201412Layout12.1Layout GuidelinesWhen using multiple bit logic devices,inputs should not float.In many cases,functions or parts of functions of digital logic devices are unused.Some examples are when only two inputs of a triple-input AND gate are used, or when only3of the4-buffer gates are used.Such input pins should not be left unconnected because the undefined voltages at the outside connections result in undefined operational states.Specified in Figure7are rules that must be observed under all circumstances.All unused inputs of digital logic devices must be connected to a high or low bias to prevent them from floating.The logic level that should be applied to any particular unused input depends on the function of the device.Generally they will be tied to GND or V CC,whichever makes more sense or is more convenient.It is acceptable to float outputs unless the part is a transceiver.If the transceiver has an output enable pin,it will disable the outputs section of the part when asserted.This will not disable the input section of the I/Os so they also cannot float when disabled.12.2Layout Exampleyout Diagram13Device and Documentation Support13.1TrademarksAll trademarks are the property of their respective owners.13.2Electrostatic Discharge CautionThese devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.13.3GlossarySLYZ022—TI Glossary.This glossary lists and explains terms,acronyms,and definitions.14Mechanical,Packaging,and Orderable InformationThe following pages include mechanical,packaging,and orderable information.This information is the most current data available for the designated devices.This data is subject to change without notice and revision of this document.For browser-based versions of this data sheet,refer to the left-hand navigation.PACKAGING INFORMATION(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Addendum-Page 1(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN74AHC1G86 :•Automotive: SN74AHC1G86-Q1•Enhanced Product: SN74AHC1G86-EPNOTE: Qualified Version Definitions:•Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects•Enhanced Product - Supports Defense, Aerospace and Medical ApplicationsAddendum-Page 2TAPE AND REEL INFORMATION*All dimensions are nominal Device Package Type Package DrawingPinsSPQ Reel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74AHC1G86DBVR SOT-23DBV 53000180.08.4 3.23 3.17 1.37 4.08.0Q3SN74AHC1G86DBVR SOT-23DBV 53000178.09.2 3.3 3.23 1.55 4.08.0Q3SN74AHC1G86DBVR SOT-23DBV 53000178.09.0 3.3 3.2 1.4 4.08.0Q3SN74AHC1G86DBVRG4SOT-23DBV 53000178.09.0 3.23 3.17 1.37 4.08.0Q3SN74AHC1G86DBVT SOT-23DBV 5250178.09.2 3.3 3.23 1.55 4.08.0Q3SN74AHC1G86DBVT SOT-23DBV 5250180.08.4 3.23 3.17 1.37 4.08.0Q3SN74AHC1G86DBVT SOT-23DBV 5250178.09.0 3.23 3.17 1.37 4.08.0Q3SN74AHC1G86DCKR SC70DCK 53000178.09.2 2.4 2.4 1.22 4.08.0Q3SN74AHC1G86DCKR SC70DCK 53000178.09.0 2.4 2.5 1.2 4.08.0Q3SN74AHC1G86DCKT SC70DCK 5250178.09.0 2.4 2.5 1.2 4.08.0Q3SN74AHC1G86DCKT SC70DCK 5250178.09.2 2.4 2.4 1.22 4.08.0Q3SN74AHC1G86DRLR SOT-5X3DRL 54000180.08.4 1.98 1.780.69 4.08.0Q3*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN74AHC1G86DBVR SOT-23DBV53000202.0201.028.0 SN74AHC1G86DBVR SOT-23DBV53000180.0180.018.0 SN74AHC1G86DBVR SOT-23DBV53000180.0180.018.0SN74AHC1G86DBVRG4SOT-23DBV53000180.0180.018.0 SN74AHC1G86DBVT SOT-23DBV5250180.0180.018.0 SN74AHC1G86DBVT SOT-23DBV5250202.0201.028.0 SN74AHC1G86DBVT SOT-23DBV5250180.0180.018.0 SN74AHC1G86DCKR SC70DCK53000180.0180.018.0 SN74AHC1G86DCKR SC70DCK53000180.0180.018.0 SN74AHC1G86DCKT SC70DCK5250180.0180.018.0 SN74AHC1G86DCKT SC70DCK5250180.0180.018.0SN74AHC1G86DRLR SOT-5X3DRL54000202.0201.028.0IMPORTANT NOTICETexas Instruments Incorporated(TI)reserves the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46,latest issue,and to discontinue any product or service per JESD48,latest issue.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.TI’s published terms of sale for semiconductor products(/sc/docs/stdterms.htm)apply to the sale of packaged integrated circuit products that TI has qualified and released to market.Additional terms may apply to the use or sale of other types of TI products and services.Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such reproduced rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements. Buyers and others who are developing systems that incorporate TI products(collectively,“Designers”)understand and agree that Designers remain responsible for using their independent analysis,evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers'applications and compliance of their applications(and of all TI products used in or for Designers’applications)with all applicable regulations,laws and other applicable requirements.Designer represents that,with respect to their applications,Designer has all the necessary expertise to create and implement safeguards that(1)anticipate dangerous consequences of failures,(2)monitor failures and their consequences,and(3)lessen the likelihood of failures that might cause harm and take appropriate actions.Designer agrees that prior to using or distributing any applications that include TI products,Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.TI’s provision of technical,application or other design advice,quality characterization,reliability data or other services or information, including,but not limited to,reference designs and materials relating to evaluation modules,(collectively,“TI Resources”)are intended to assist designers who are developing applications that incorporate TI products;by downloading,accessing or using TI Resources in any way,Designer(individually or,if Designer is acting on behalf of a company,Designer’s company)agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.TI’s provision of TI Resources does not expand or otherwise alter TI’s applicable published warranties or warranty disclaimers for TI products,and no additional obligations or liabilities arise from TI providing such TI Resources.TI reserves the right to make corrections, enhancements,improvements and other changes to its TI Resources.TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.Designer is authorized to use,copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s)identified in such TI Resource.NO OTHER LICENSE,EXPRESS OR IMPLIED,BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT,AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN,including but not limited to any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI products or services are rmation regarding or referencing third-party products or services does not constitute a license to use such products or services,or a warranty or endorsement e of TI Resources may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.TI RESOURCES ARE PROVIDED“AS IS”AND WITH ALL FAULTS.TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS,EXPRESS OR IMPLIED,REGARDING RESOURCES OR USE THEREOF,INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS,TITLE,ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY,FITNESS FOR A PARTICULAR PURPOSE,AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE.IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT,SPECIAL,COLLATERAL,INDIRECT,PUNITIVE,INCIDENTAL,CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF,AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard(e.g.,ISO/TS16949 and ISO26262),TI is not responsible for any failure to meet such industry standard requirements.Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards,such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and ing products in an application does not by itself establish any safety features in the application.Designers must ensure compliance with safety-related requirements and standards applicable to their applications.Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death(e.g.,life support,pacemakers,defibrillators,heart pumps,neurostimulators,and implantables).Such equipment includes,without limitation,all medical devices identified by the U.S.Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.TI may expressly designate certain products as completing a particular qualification(e.g.,Q100,Military Grade,or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers’own risk.Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.Designer will fully indemnify TI and its representatives against any damages,costs,losses,and/or liabilities arising out of Designer’s non-compliance with the terms and provisions of this Notice.Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2017,Texas Instruments Incorporated。

0_74系列芯片功能略表

74系列芯片功能略表技术2008-12-17 10:47:39 阅读422 评论0 字号:大中小引自廖世迁的blog电子元件知识-74系列芯片功能略表74HC01 2输入四与非门(oc)74HC02 2输入四或非门74HC03 2输入四与非门(oc)74HC04 六倒相器74HC05 六倒相器(oc)74HC06 六高压输出反相缓冲器/驱动器(oc,30v)74HC07 六高压输出缓冲器/驱动器(oc,30v)74HC08 2输入四与门74HC09 2输入四与门(oc)74HC10 3输入三与非门74HC11 3输入三与门74HC12 3输入三与非门(oc)74HC13 4输入双与非门(斯密特触发)74HC14 六倒相器(斯密特触发)74HC15 3输入三与门(oc)74HC16 六高压输出反相缓冲器/驱动器(oc,15v)74HC17 六高压输出缓冲器/驱动器(oc,15v)74HC18 4输入双与非门(斯密特触发)74HC19 六倒相器(斯密特触发)74HC20 4输入双与非门74HC21 4输入双与门74HC22 4输入双与非门(oc)74HC23 双可扩展的输入或非门74HC24 2输入四与非门(斯密特触发)74HC25 4输入双或非门(有选通)74HC26 2输入四高电平接口与非缓冲器(oc,15v)74HC27 3输入三或非门74HC28 2输入四或非缓冲器74HC30 8输入与非门74HC31 延迟电路74HC32 2输入四或门74HC33 2输入四或非缓冲器(集电极开路输出)74HC34 六缓冲器74HC35 六缓冲器(oc)74HC36 2输入四或非门(有选通)74HC37 2输入四与非缓冲器74HC38 2输入四或非缓冲器(集电极开路输出)74HC39 2输入四或非缓冲器(集电极开路输出)74HC40 4输入双与非缓冲器74HC41 bcd-十进制计数器74HC42 4线-10线译码器(bcd输入)74HC43 4线-10线译码器(余3码输入)74HC44 4线-10线译码器(余3葛莱码输入)74HC45 bcd-十进制译码器/驱动器74HC46 bcd-七段译码器/驱动器74HC47 bcd-七段译码器/驱动器74HC48 bcd-七段译码器/驱动器74HC49 bcd-七段译码器/驱动器(oc)74HC50 双二路2-2输入与或非门(一门可扩展)74HC51 双二路2-2输入与或非门74HC51 二路3-3输入,二路2-2输入与或非门74HC52 四路2-3-2-2输入与或门(可扩展)74HC53 四路2-2-2-2输入与或非门(可扩展)74HC53 四路2-2-3-2输入与或非门(可扩展)74HC54 四路2-2-2-2输入与或非门74HC54 四路2-3-3-2输入与或非门74HC54 四路2-2-3-2输入与或非门74HC55 二路4-4输入与或非门(可扩展)74HC60 双四输入与扩展74HC61 三3输入与扩展74HC62 四路2-3-3-2输入与或扩展器74HC63 六电流读出接口门74HC64 四路4-2-3-2输入与或非门74HC65 四路4-2-3-2输入与或非门(oc)74HC70 与门输入上升沿jk触发器74HC71 与输入r-s主从触发器74HC72 与门输入主从jk触发器74HC73 双j-k触发器(带清除端)74HC74 正沿触发双d型触发器(带预置端和清除端)74HC75 4位双稳锁存器74HC76 双j-k触发器(带预置端和清除端)74HC77 4位双稳态锁存器74HC78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74HC80 门控全加器74HC81 16位随机存取存储器74HC82 2位二进制全加器(快速进位)74HC83 4位二进制全加器(快速进位)74HC84 16位随机存取存储器74HC85 4位数字比较器74HC86 2输入四异或门74HC87 四位二进制原码/反码/oi单元74HC89 64位读/写存储器74HC90 十进制计数器74HC91 八位移位寄存器74HC92 12分频计数器(2分频和6分频)74HC93 4位二进制计数器74HC94 4位移位寄存器(异步)74HC95 4位移位寄存器(并行io)74HC96 5位移位寄存器74HC97 六位同步二进制比率乘法器74HC100 八位双稳锁存器74HC103 负沿触发双j-k主从触发器(带清除端)74HC106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74HC107 双j-k主从触发器(带清除端)74HC108 双j-k主从触发器(带预置,清除,时钟)74HC109 双j-k触发器(带置位,清除,正触发)74HC110 与门输入j-k主从触发器(带锁定)74HC111 双j-k主从触发器(带数据锁定)74HC112 负沿触发双j-k触发器(带预置端和清除端)74HC113 负沿触发双j-k触发器(带预置端)74HC114 双j-k触发器(带预置端,共清除端和时钟端) 74HC116 双四位锁存器74HC120 双脉冲同步器/驱动器74HC121 单稳态触发器(施密特触发)74HC122 可再触发单稳态多谐振荡器(带清除端)74HC123 可再触发双单稳多谐振荡器74HC125 四总线缓冲门(三态输出)74HC126 四总线缓冲门(三态输出)74HC128 2输入四或非线驱动器74HC131 3-8译码器74HC132 2输入四与非门(斯密特触发)74HC133 13输入端与非门74HC134 12输入端与门(三态输出)74HC135 四异或/异或非门74HC136 2输入四异或门(oc)74HC137 八选1锁存译码器/多路转换器74HC138 3-8线译码器/多路转换器74HC139 双2-4线译码器/多路转换器74HC140 双4输入与非线驱动器74HC141 bcd-十进制译码器/驱动器74HC142 计数器/锁存器/译码器/驱动器74HC145 4-10译码器/驱动器74HC147 10线-4线优先编码器74HC148 8线-3线八进制优先编码器74HC150 16选1数据选择器(反补输出)74HC151 8选1数据选择器(互补输出)74HC152 8选1数据选择器多路开关74HC153 双4选1数据选择器/多路选择器74HC154 4线-16线译码器74HC155 双2-4译码器/分配器(图腾柱输出)74HC156 双2-4译码器/分配器(集电极开路输出)74HC157 四2选1数据选择器/多路选择器74HC158 四2选1数据选择器(反相输出)74HC160 可预置bcd计数器(异步清除)74HC161 可预置四位二进制计数器(并清除异步)74HC162 可预置bcd计数器(异步清除)74HC163 可预置四位二进制计数器(并清除异步)74HC164 8位并行输出串行移位寄存器74HC165 并行输入8位移位寄存器(补码输出)74HC166 8位移位寄存器74HC167 同步十进制比率乘法器74HC168 4位加/减同步计数器(十进制)74HC169 同步二进制可逆计数器74HC170 4*4寄存器堆74HC171 四d触发器(带清除端)74HC172 16位寄存器堆74HC173 4位d型寄存器(带清除端)74HC174 六d触发器74HC175 四d触发器74HC176 十进制可预置计数器74HC177 2-8-16进制可预置计数器74HC178 四位通用移位寄存器74HC179 四位通用移位寄存器74HC180 九位奇偶产生/校验器74HC181 算术逻辑单元/功能发生器74HC182 先行进位发生器74HC183 双保留进位全加器74HC184 bcd-二进制转换器74HC185 二进制-bcd转换器74HC190 同步可逆计数器(bcd,二进制)74HC191 同步可逆计数器(bcd,二进制)74HC192 同步可逆计数器(bcd,二进制)74HC193 同步可逆计数器(bcd,二进制)74HC199 八位移位寄存器74HC210 2-5-10进制计数器74HC213 2-n-10可变进制计数器74HC221 双单稳触发器74HC230 八3态总线驱动器74HC231 八3态总线反向驱动器74HC240 八缓冲器/线驱动器/线接收器(反码三态输出) 74HC241 八缓冲器/线驱动器/线接收器(原码三态输出) 74HC242 八缓冲器/线驱动器/线接收器74HC243 4同相三态总线收发器74HC244 八缓冲器/线驱动器/线接收器74HC245 八双向总线收发器74HC246 4线-七段译码/驱动器(30v)74HC247 4线-七段译码/驱动器(15v)74HC248 4线-七段译码/驱动器74HC249 4线-七段译码/驱动器74HC251 8选1数据选择器(三态输出)74HC253 双四选1数据选择器(三态输出)74HC256 双四位可寻址锁存器74HC257 四2选1数据选择器(三态输出)74HC258 四2选1数据选择器(反码三态输出)74HC259 8为可寻址锁存器74HC260 双5输入或非门74HC261 4*2并行二进制乘法器74HC265 四互补输出元件74HC266 2输入四异或非门(oc)74HC270 2048位rom (512位四字节,oc)74HC271 2048位rom (256位八字节,oc)74HC273 八d触发器74HC274 4*4并行二进制乘法器74HC275 七位片式华莱士树乘法器74HC276 四jk触发器74HC278 四位可级联优先寄存器74HC279 四s-r锁存器74HC280 9位奇数/偶数奇偶发生器/较验器74HC28174HC283 4位二进制全加器74HC290 十进制计数器74HC291 32位可编程模74HC293 4位二进制计数器74HC294 16位可编程模74HC295 四位双向通用移位寄存器74HC298 四-2输入多路转换器(带选通)74HC299 八位通用移位寄存器(三态输出)74HC348 8-3线优先编码器(三态输出)74HC352 双四选1数据选择器/多路转换器74HC353 双4-1线数据选择器(三态输出)74HC354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC365 6总线驱动器74HC366 六反向三态缓冲器/线驱动器74HC367 六同向三态缓冲器/线驱动器74HC368 六反向三态缓冲器/线驱动器74HC373 八d锁存器74HC374 八d触发器(三态同相)74HC375 4位双稳态锁存器74HC377 带使能的八d触发器74HC378 六d触发器74HC379 四d触发器74HC381 算术逻辑单元/函数发生器74HC382 算术逻辑单元/函数发生器74HC384 8位*1位补码乘法器74HC385 四串行加法器/乘法器74HC386 2输入四异或门74HC390 双十进制计数器74HC391 双四位二进制计数器74HC395 4位通用移位寄存器74HC396 八位存储寄存器74HC398 四2输入端多路开关(双路输出)74HC399 四-2输入多路转换器(带选通)74HC422 单稳态触发器74HC423 双单稳态触发器74HC440 四3方向总线收发器,集电极开路74HC441 四3方向总线收发器,集电极开路74HC442 四3方向总线收发器,三态输出74HC443 四3方向总线收发器,三态输出74HC444 四3方向总线收发器,三态输出74HC445 bcd-十进制译码器/驱动器,三态输出74HC446 有方向控制的双总线收发器74HC448 四3方向总线收发器,三态输出74HC449 有方向控制的双总线收发器74HC465 八三态线缓冲器74HC466 八三态线反向缓冲器74HC467 八三态线缓冲器74HC468 八三态线反向缓冲器74HC490 双十进制计数器74HC540 八位三态总线缓冲器(反向)74HC541 八位三态总线缓冲器74HC589 有输入锁存的并入串出移位寄存器74HC590 带输出寄存器的8位二进制计数器74HC591 带输出寄存器的8位二进制计数器74HC592 带输出寄存器的8位二进制计数器74HC593 带输出寄存器的8位二进制计数器74HC594 带输出锁存的8位串入并出移位寄存器74HC595 8位输出锁存移位寄存器74HC596 带输出锁存的8位串入并出移位寄存器74HC597 8位输出锁存移位寄存器74HC598 带输入锁存的并入串出移位寄存器74HC599 带输出锁存的8位串入并出移位寄存器74HC604 双8位锁存器74HC605 双8位锁存器74HC606 双8位锁存器74HC607 双8位锁存器74HC620 8位三态总线发送接收器(反相)74HC621 8位总线收发器74HC622 8位总线收发器74HC623 8位总线收发器74HC640 反相总线收发器(三态输出)74HC641 同相8总线收发器,集电极开路74HC642 同相8总线收发器,集电极开路74HC643 8位三态总线发送接收器74HC644 真值反相8总线收发器,集电极开路74HC645 三态同相8总线收发器74HC646 八位总线收发器,寄存器74HC647 八位总线收发器,寄存器74HC648 八位总线收发器,寄存器74HC649 八位总线收发器,寄存器74HC651 三态反相8总线收发器74HC652 三态反相8总线收发器74HC653 反相8总线收发器,集电极开路74HC654 同相8总线收发器,集电极开路74HC668 4位同步加/减十进制计数器74HC669 带先行进位的4位同步二进制可逆计数器74HC670 4*4寄存器堆(三态)74HC671 带输出寄存的四位并入并出移位寄存器74HC672 带输出寄存的四位并入并出移位寄存器74HC673 16位并行输出存储器,16位串入串出移位寄存器74HC674 16位并行输入串行输出移位寄存器74HC681 4位并行二进制累加器74HC682 8位数值比较器(图腾柱输出)74HC683 8位数值比较器(集电极开路)74HC684 8位数值比较器(图腾柱输出)74HC685 8位数值比较器(集电极开路)74HC686 8位数值比较器(图腾柱输出)74HC687 8位数值比较器(集电极开路)74HC688 8位数字比较器(oc输出)74HC689 8位数字比较器74HC690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)。

74系列引脚图

74系列芯片资料程序匠人发表于2005-10-29 19:20:00 阅读全文| 回复(0)| 引用通告| 编辑/user1/349/archives/2005/4810.html/user1/349/archives/2005/4810.html74系列芯片资料反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器74LS245│20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门74LS08│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门74LS00│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门74LS10│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门74LS30│1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门74LS32│14 13 12 11 10 9 8│)│ Y = A+B│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门74LS02│14 13 12 11 10 9 8│___)│Y = A+B│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门74S51│14 13 12 11 10 9 8│_____)│ 2Y = AB+DE│1 2 3 4 5 6 7│_______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门74S64 74S65(OC门)│14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C│16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B│16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B└┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器74LS74│14 13 12 11 10 9 8 │)││1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器74LS373│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器TI[DATA]SN7405六反相器(OC) TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器[DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

MC74ACT86DG,MC74AC86DR2G,MC74ACT86DR2G,MC74ACT86DR2G,MC74AC86DG,MC74AC86DTR2G, 规格书,Datasheet 资料