数字电子技术基础简明教程(第三版)答案第六章

数字电子技术基础简明教程(第三版)全

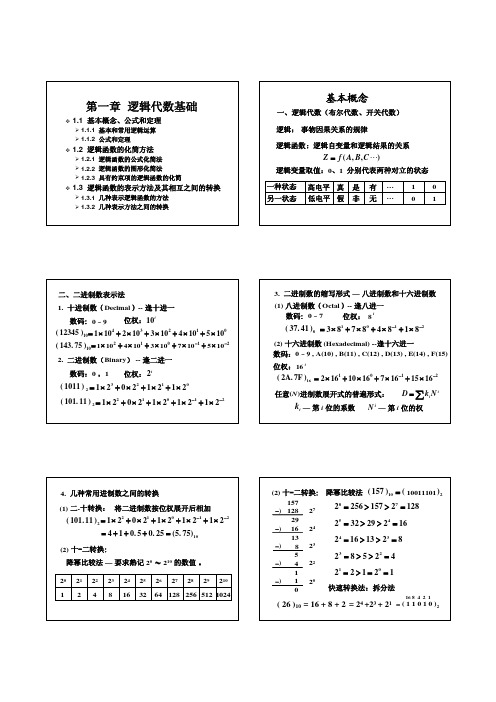

三、二进制代码 编码: 用二进制数表示文字、符号等信息的过程。 二进制代码: 编码后的二进制数。

二-十进制代码:用二进制代码表示十个数字符号 0 ~ 9,又称为 BCD 码(Binary Coded Decimal )。 8421码 2421码 5211码

几种常见的BCD代码: 余 3 码 余 3 循环码

Y2 1 0 1 0 11 0 0

& ≥1

Y3

(真值表略)

(4) 异或运算 A

=1

(Exclusive—OR) B

Y4 = A ⊕ B = AB + AB

(5) 同或运算 (异或非)

(Exclusive—NOR)

Y5 = A ⊕ B A =1 B

= AB + AB A=

= A⊙B B

Y4

A B Y4 00 0

10 1 11 1

(3)非运算:

真

A

Y

值

0

1

表

1

0

逻辑函数式 Y = A + B 逻辑符号

A B

≥1 Y 或门(OR gate)

逻辑函数式 逻辑符号

Y= A

A1

Y 非门(NOT gate)

二、逻辑变量与逻辑函数及常用复合逻辑运算

1. 逻辑变量与逻辑函数 逻辑变量:在逻辑代数中,用英文字母表示的变量称

¾ 1.3.1 几种表示逻辑函数的方法 ¾ 1.3.2 几种表示方法之间的转换

基本概念

一、逻辑代数(布尔代数、开关代数)

逻辑: 事物因果关系的规律

逻辑函数: 逻辑自变量和逻辑结果的关系 Z = f ( A, B, C L)

逻辑变量取值:0、1 分别代表两种对立的状态

数字电子技术基础简明教程第三版(6)

EXIT

6.2 555 定时器及其应用

主要要求:

了解 555 定时器的电路结构,掌握其符号和功能。 掌握用 555 定时器构成施密特触发器、单稳态 触发器和多谐振荡器的方法。

EXIT

一、555 定时器的工作原理和逻辑功能

555 定时器简介

555 定时器是一种结构简单、使用方便灵活、用途 广泛的多功能电路。它电源电压范围宽(双极型 555 定 时器为 5 ~ 16 V,CMOS 555 定时器为 3 ~ 18 V),可提 供与 TTL 及 CMOS 数字电路兼容的接口电平,还可输 出一定功率,驱动微电机、指示灯、扬声器等。

施密特触发器常用的非有矩施主形密要脉特用冲触以变发换将器成缓和陡慢单峭变稳化的态或矩触快形发速脉器变冲。化的

单稳态触发器

主要用以将宽度不符合要求的脉 冲变换成符合要求的矩形脉冲。

脉冲信号产生与 整形电路的实现

用门电路构成。 用专用的集成电路。 用 555 定时器构成。

是一种多用途集成电路,只要外接少量阻容 元件就可构成施密特触发器、单稳态触发器和多 谐振荡器等,使用方便、灵活,应用广泛。

0

2 3VCC 32VCC

1

0 导通

1

1 截止

1 不变 不变

EXIT

555 定时器的工作原理与逻辑功能

定时器 5G555 的功能表

输入

输出

TH TR RD OUT = Q V 状态

1

× ×0

0 导通

1

0 导通

1

2 3VCC

1

1 截止

32VCC

1 不变 不变

EXIT

Байду номын сангаас

简化功能表

使用要点

数字电子技术基础简明教程第三版4-6章(含答案)

第四章(选择、判断、填空共30题)一、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.在下列触发器中,有约束条件的是。

A.主从J K F/FB.主从D F/FC.同步R S F/FD.边沿D F/F3.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.3E.44.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T=。

A.0B.1C.QD.Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T=。

A.0B.1C.QD.Q7.对于D触发器,欲使Q n+1=Q n,应使输入D=。

A.0B.1C.QD.Q8.对于J K触发器,若J=K,则可完成触发器的逻辑功能。

A.R SB.DC.TD.Tˊ9.欲使J K触发器按Q n+1=Q n工作,可使J K触发器的输入端。

A.J=K=0B.J=Q,K=QC.J=Q,K=QD.J=Q,K=0E.J=0,K=Q10.欲使J K触发器按Q n+1=Q n工作,可使J K触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=QD.J=Q,K=1E.J=1,K=Q11.欲使J K触发器按Q n+1=0工作,可使J K触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=1D.J=0,K=1E.J=K=112.欲使J K触发器按Q n+1=1工作,可使J K触发器的输入端。

A.J=K=1B.J=1,K=0C.J=K=QD.J=K=0E.J=Q,K=013.欲使D触发器按Q n+1=Q n工作,应使输入D=。

A.0B.1C.QD.Q14.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从R S触发器C.同步R S触发器D.主从J K触发器15.下列触发器中,没有约束条件的是。

A.基本R S触发器B.主从R S触发器C.同步R S触发器D.边沿D触发器16.描述触发器的逻辑功能的方法有。

数字电子技术基础简明教程(第三版) 4-6章

抗干扰0 能1力极0 强;异步置0

只有置1

0

1、00 置不1用0

功能异不。步允置许1

3. T 型触发器

在CP作用下,当T = 0时保持状态不变,T =1 时状态 翻转的电路,叫T 型时钟触发器。

Q

Q

1T C1

T Q n+1 功能 Q n1 T Q n TQ n

0 Q n 保持

T Qn

1 Q n 翻转 CP 下降沿时刻有效

56 引出端 功能 14

VCC

98 7

地

特性表 SD D CP RD

3.C边P 沿D0 DR触1–D 发S–1D器Q主n0+1要特点同步注置0

4 2 3 1 10 12 11 13

–SD1 CP1 – S–D2 CP2 –

D1 RD1 D2 RD2

C1P

的11上升11 沿Q1(正n 边保沿同持)步(或置无下1效降) 沿(负边沿)触发;

2. CP = 1 时跟随。 (Qn1 D) 下降沿到来时锁存 (Qn1 Qn )

三、集成同步 D 触发器

1. TTL 74LS375

Q

G1 >1

R G3 &

Q

>1 G2

S & G4

R

1 S CP

G5 D

D1 CP1、2

D2

D3 CP3、4

D4

74LS375

1 4

1D0 1LE

7 1D1

9 12

换 (2)比较上述特性方程,得出给定触发器中输入

方

信号的接法。

法 (3)画出用给定触发器实现待求触发器的电路。

1. JK D

已有

因此,令J = K = D D

数字电子技术基础简明教程第三版课后练习题含答案

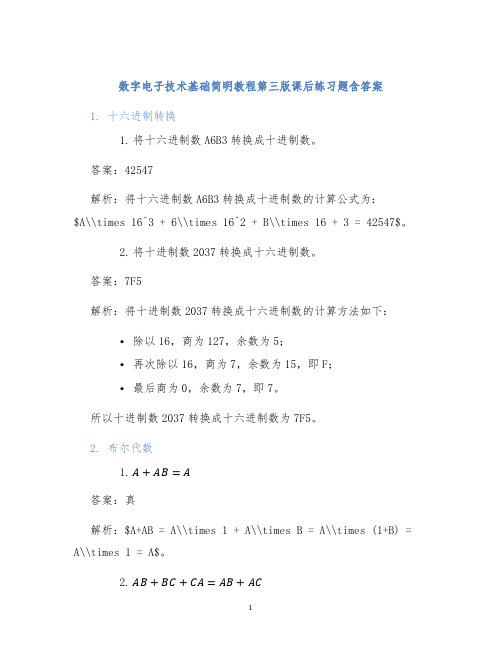

数字电子技术基础简明教程第三版课后练习题含答案1. 十六进制转换1.将十六进制数A6B3转换成十进制数。

答案:42547解析:将十六进制数A6B3转换成十进制数的计算公式为:$A\\times 16^3 + 6\\times 16^2 + B\\times 16 + 3 = 42547$。

2.将十进制数2037转换成十六进制数。

答案:7F5解析:将十进制数2037转换成十六进制数的计算方法如下:•除以16,商为127,余数为5;•再次除以16,商为7,余数为15,即F;•最后商为0,余数为7,即7。

所以十进制数2037转换成十六进制数为7F5。

2. 布尔代数1.A+AB=A答案:真解析:$A+AB = A\\times 1 + A\\times B = A\\times (1+B) = A\\times 1 = A$。

2.AB+BC+CA=AB+AC答案:真解析:AB+BC+CA=AB+AC的推导如下:AB+BC+CA=AB+AC+BC+CA−AC−BD−BD+BD=A(B+C)+B(C+D)−B(D+C)−C(A+D)=A(B+C)−C(A+D)+B(C−D)=AB+AC−BC+BD=AB+AC。

3. 数字逻辑门1.OR 门和 AND 门的输出关系是什么?答案:OR 门输出为真当且仅当其输入中至少有一位为真;AND 门输出为真当且仅当其输入中所有的位都为真。

2.NOT 门的输出关系是什么?答案:NOT 门的输出与输入相反,即若输入为真,则输出为假;若输入为假,则输出为真。

4. 状态分析1.下面是一个简单的计数器状态图,完成以下计数器输出的对应状态表。

计数器状态图计数器状态图答案:状态Q2 Q1 Q0 下一个状态0 0 0 0 11 0 0 1 22 0 1 0 33 0 1 1 44 1 0 0 55 1 0 1 66 1 1 0 77 1 1 1 02.已知一个状态机的状态表,如何画其状态图?答案:画出每个状态和它所连接的下一个状态之间的箭头,用圆圈表示状态,标出每个状态的名称。

数字电子技术(第三版) 第6章

图6–1 例1图

解 该电路为同步时序电路。 从电路图得到每一级的激励方程如下:

J1 Q3n J 2 Q1n J3 Q1nQ2n

K1 1 K2 Q1n K3 1

其次态方程为

Q n1 nQ2n

Q n1 3

Q1nQ2n Q3n

C Q3n

根据方程可得出状态迁移表, 如表 6-1 所示, 再由 表得状态迁移图, 如图 6-2 所示。 由此得出该计数器为 五进制递增计数器, 具有自校正能力(又称自启动能力)。

所谓自启动能力, 指当电源合上后, 无论处于何种状 态, 均能自动进入有效计数循环; 否则称其无自启动能力。

表 6 – 1 例 1 状态表

图 6 – 2 例 1 状态迁移图

该电路的波形图如图 6-3 所示。 图 6-3 例 1 波形图

例 2 时序电路如图 6 - 4 所示,分析其功能。 图6–4 例2图

解 该电路为同步时序电路。 电路图的激励方程为

D1 Q3n ; D2 Q1n ; D3 Q2n

表 6 – 3 例 3 状态真值表

Q1n

Q2n

Q3n

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Q1n1

1 0 1 0 1 0 1 0

Q2n1

0 0 0 0 1 1 1 1

Q n1 3

0 0 1 1 0 0 1 1

(3) 画出状态迁移图。 由状态真值表可得出相应的状态图, 如图 6-8 所 示。

万里学院-数字电子技术基础-第六章习题及参考答案

第六章习题一、选择题 1. PROM和 PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM 与阵列、或阵列均不可编程C.PAL 与阵列、或阵列均可编程D. PAL 的与阵列可编程 2. PAL是指。

A.可编程逻辑阵列B. 可编程阵列逻辑C. 通用阵列逻辑D. 只读存储器 3.当用异步 I/O 输出结构的 PAL 设计逻辑电路时,它们相当于。

A. 组合逻辑电路B. 时序逻辑电路C. 存储器D. 数模转换器 4. PLD器件的基本结构组成有。

A. 输出电路B. 或阵列C. 与阵列D. 输入缓冲电路5. PLD器件的主要优点有。

A. 集成密度高B. 可改写C. 可硬件加密D. 便于仿真测试 6. GAL的输出电路是。

A.OLMCB. 固定的C. 只可一次编程D. 可重复编程7. PLD开发系统需要有。

A. 计算机B. 操作系统C. 编程器D. 开发软件 8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD 9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD 10. ISP-PLD 器件开发系统的组成有。

A. 计算机B. 编程器C. 开发软件D. 编程电缆 11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8 的最多输入输出端个数为。

A.8 输入 8 输出B.10 输入 10 输出C.16 输入 8 输出D.16 输入 1 输出 13 一个容量为 1K×8 的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为 4K× 8 的 RAM,需要片容量为 256× 4 的 RAM。

A. 8B.4C. 2D.32 15.寻址容量为 16K× 8 的 RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有 8 位,行、列地址译码器输入端都为 4 个,则它们的字线加条。

数字电子技术基础简明教程第三版课后答案

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Coursewarening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021

Courseware template

On the evening of July 24, 2021