文献翻译原文-word形式

英文文献译文word版

资产重估或减值准备:了解占固定资产在Release 12布赖恩·刘易斯eprentise介绍显著的变化在财务报告的要求已经改变的固定资产核算框架公司。

国际财务报告准则(IFRS)要求的固定资产进行初步按成本入账,但有两种会计模式-成本模式计量的重估模式。

那么,有什么区别,当你应该考虑升值与减值?没有R12带给固定资产哪些重要变化?国际财务报告准则和美国公认会计准则报告的甲骨文®电子商务套件但很显然,美国证券交易委员会(SEC)将不会要求美国公司使用国际财务报告准则在不久的将来,大多数玩家在资本市场倾向于认为它是不可避免的,将国际财务报告准则最终成为美国的财务报告环境的更显著的部分。

这实际上是对发生的程度,超过400基于在美国以外的全球企业都被允许提交美国证券交易所(SEC)的财务报告(10K和10Q -通常被称为年度/季度财务报告)。

为海外谁也不在美国的证券交易委员会提交的公司,国际财务报告准则正在成为金融世界标准报告。

对于谁住在多个资本市场运作的公司,有可能实际上是一个双重报告要求国际财务报告准则和美国公认会计原则(公认会计原则)的财务报表。

与11i版,随后与12版时,Ora cle®电子商务套件(EBS)添加功能让用户生活在两个国际财务报告准则和美国公认会计准则的世界。

这两个报告之间的差异框架是广泛的,但对于本白皮书的目的,我们将专注于固定资产中核算EBS -特别是资产重估或减值。

根据美国公认会计准则,固定资产乃按历史成本,然后以折旧出售或剩余价值。

如果有某些迹象表明固定资产的变现价值造成负面改变,则该资产写下来,损失记录。

这被称为减值。

根据国际财务报告准则,财务报表发行人有权选择成本模式(这是大多数方面的选项类似美国公认会计原则机型)或重估模式(其中有没有下的并行报告美国公认会计原则)。

根据重估模式,固定资产可定期写入,以反映公平市场价值-这是专门美国公认会计原则和美国证券交易委员会的权威所禁止的东西。

(完整word版)英文文献及翻译:计算机程序

姓名:刘峻霖班级:通信143班学号:2014101108Computer Language and ProgrammingI. IntroductionProgramming languages, in computer science, are the artificial languages used to write a sequence of instructions (a computer program) that can be run by a computer. Simi lar to natural languages, such as English, programming languages have a vocabulary, grammar, and syntax. However, natural languages are not suited for programming computers because they are ambiguous, meaning that their vocabulary and grammatical structure may be interpreted in multiple ways. The languages used to program computers must have simple logical structures, and the rules for their grammar, spelling, and punctuation must be precise.Programming languages vary greatly in their sophistication and in their degree of versatility. Some programming languages are written to address a particular kind of computing problem or for use on a particular model of computer system. For instance, programming languages such as FORTRAN and COBOL were written to solve certain general types of programming problems—FORTRAN for scientific applications, and COBOL for business applications. Although these languages were designed to address specific categories of computer problems, they are highly portable, meaning that the y may be used to program many types of computers. Other languages, such as machine languages, are designed to be used by one specific model of computer system, or even by one specific computer in certain research applications. The most commonly used progra mming languages are highly portable and can be used to effectively solve diverse types of computing problems. Languages like C, PASCAL and BASIC fall into this category.II. Language TypesProgramming languages can be classified as either low-level languages or high-level languages. Low-level programming languages, or machine languages, are the most basic type of programming languages and can be understood directly by a computer. Machine languages differ depending on the manufacturer and model of computer. High-level languages are programming languages that must first be translated into a machine language before they can be understood and processed by a computer. Examples of high-levellanguages are C, C++, PASCAL, and FORTRAN. Assembly languages are intermediate languages that are very close to machine languages and do not have the level of linguistic sophistication exhibited by other high-level languages, but must still be translated into machine language.1. Machine LanguagesIn machine languages, instructions are written as sequences of 1s and 0s, called bits, that a computer can understand directly. An instruction in machine language generally tells the computer four things: (1) where to find one or two numbers or simple pieces of data in the main computer memory (Random Access Memory, or RAM), (2) a simple operation to perform, such as adding the two numbers together, (3) where in the main memory to put the result of this simple operation, and (4) where to find the next instruction to perform. While all executable programs are eventually read by the computer in machine language, they are not all programmed in machine language. It is extremely difficult to program directly in machine language because the instructions are sequences of 1s and 0s. A typical instruction in a machine language might read 10010 1100 1011 and mean add the contents of storage register A to the contents of storage register B.2. High-Level LanguagesHigh-level languages are relatively sophisticated sets of statements utilizing word s and syntax from human language. They are more similar to normal human languages than assembly or machine languages and are therefore easier to use for writing complicated programs. These programming languages allow larger and more complicated programs to be developed faster. However, high-level languages must be translated into machine language by another program called a compiler before a computer can understand them. For this reason, programs written in a high-level language may take longer to execute and use up more memory than programs written in an assembly language.3. Assembly LanguagesComputer programmers use assembly languages to make machine-language programs easier to write. In an assembly language, each statement corresponds roughly to one machine language instruction. An assembly language statement is composed with the aid of easy to remember commands. The command to add the contents of the storage register A to the contents of storage register B might be written ADD B, A in a typical assembl ylanguage statement. Assembly languages share certain features with machine languages. For instance, it is possible to manipulate specific bits in both assembly and machine languages. Programmers use assemblylanguages when it is important to minimize the time it takes to run a program, because the translation from assembly language to machine language is relatively simple. Assembly languages are also used when some part of the computer has to be controlled directly, such as individual dots on a monitor or the flow of individual characters to a printer.III. Classification of High-Level LanguagesHigh-level languages are commonly classified as procedure-oriented, functional, object-oriented, or logic languages. The most common high-level languages today are procedure-oriented languages. In these languages, one or more related blocks of statements that perform some complete function are grouped together into a program module, or procedure, and given a name such as “procedure A.” If the same sequence of oper ations is needed elsewhere in the program, a simple statement can be used to refer back to the procedure. In essence, a procedure is just amini- program. A large program can be constructed by grouping together procedures that perform different tasks. Procedural languages allow programs to be shorter and easier for the computer to read, but they require the programmer to design each procedure to be general enough to be usedin different situations. Functional languages treat procedures like mathematical functions and allow them to be processed like any other data in a program. This allows a much higher and more rigorous level of program construction. Functional languages also allow variables—symbols for data that can be specified and changed by the user as the program is running—to be given values only once. This simplifies programming by reducing the need to be concerned with the exact order of statement execution, since a variable does not have to be redeclared , or restated, each time it is used in a program statement. Many of the ideas from functional languages have become key parts of many modern procedural languages. Object-oriented languages are outgrowths of functional languages. In object-oriented languages, the code used to write the program and the data processed by the program are grouped together into units called objects. Objects are further grouped into classes, which define the attributes objects must have. A simpleexample of a class is the class Book. Objects within this class might be No vel and Short Story. Objects also have certain functions associated with them, called methods. The computer accesses an object through the use of one of the object’s methods. The method performs some action to the data in the object and returns this value to the computer. Classes of objects can also be further grouped into hierarchies, in which objects of one class can inherit methods from another class. The structure provided in object-oriented languages makes them very useful for complicated programming tasks. Logic languages use logic as their mathematical base. A logic program consists of sets of facts and if-then rules, which specify how one set of facts may be deduced from others, for example: If the statement X is true, then the statement Y is false. In the execution of such a program, an input statement can be logically deduced from other statements in the program. Many artificial intelligence programs are written in such languages.IV. Language Structure and ComponentsProgramming languages use specific types of statements, or instructions, to provide functional structure to the program. A statement in a program is a basic sentence that expresses a simple idea—its purpose is to give the computer a basic instruction. Statements define the types of data allowed, how data are to be manipulated, and the ways that procedures and functions work. Programmers use statements to manipulate common components of programming languages, such as variables and macros (mini-programs within a program). Statements known as data declarations give names and properties to elements of a program called variables. Variables can be assigned different values within the program. The properties variables can have are called types, and they include such things as what possible values might be saved in the variables, how much numerical accuracy is to be used in the values, and how one variable may represent a collection of simpler values in an organized fashion, such as a table or array. In many programming languages, a key data type is a pointer. Variables that are pointers do not themselves have values; instead, they have information that the computer can use to locate some other variable—that is, they point to another variable. An expression is a piece of a statement that describe s a series of computations to be performed on some of the program’s variables, such as X+Y/Z, in which the variables are X, Y, and Z and the computations are addition and division. An assignment statement assigns a variable a value derived fromsome expression, while conditional statements specify expressions to be tested and then used to select which other statements should be executed next.Procedure and function statements define certain blocks of code as procedures or functions that can then be returned to later in the program. These statements also define the kinds of variables and parameters the programmer can choose and the type of value that the code will return when an expression accesses the procedure or function. Many programming languages also permit mini translation programs called macros. Macros translate segments of code that have been written in a language structure defined by the programmer into statements that the programming language understands.V. HistoryProgramming languages date back almost to the invention of the digital computer in the 1940s. The first assembly languages emerged in the late 1950s with the introduction of commercial computers. The first procedural languages were developed in the late 1950s to early 1960s: FORTRAN, created by John Backus, and then COBOL, created by Grace Hopper The first functional language was LISP, written by John McCarthy4 in the late 1950s. Although heavily updated, all three languages are still widely used today. In the late 1960s, the first object-oriented languages, such as SIMULA, emerged. Logic languages became well known in the mid 1970swith the introduction of PROLOG6, a language used to program artificial intelligence software. During the 1970s, procedural languages continued to develop with ALGOL, BASIC, PASCAL, C, and A d a SMALLTALK was a highly influential object-oriented language that led to the merging ofobject- oriented and procedural languages in C++ and more recently in JAVA10. Although pure logic languages have declined in popularity, variations have become vitally important in the form of relational languages for modern databases, such as SQL.计算机程序一、引言计算机程序是指导计算机执行某个功能或功能组合的一套指令。

(完整word版)光学外文文献及翻译

学号2013211033 昆明理工大学专业英语专业光学姓名辜苏导师李重光教授分数导师签字日期2015年5月6日研究生部专业英语考核In digital holography, the recording CCD is placed on the ξ-ηplane in order to register the hologramx ',y 'when the object lies inthe x-y plane. Forthe reconstruction ofthe information ofthe object wave,phase-shifting digital holography includes two steps:(1) getting objectwave on hologram plane, and (2) reconstructing original object wave.2.1 Getting information of object wave on hologram plateDoing phase shifting N-1 times and capturing N holograms. Supposing the interferogram after k- 1 times phase-shifting is]),(cos[),(),(),,(k k b a I δηξφηξηξδηξ-⋅+= (1) Phase detection can apply two kinds of algorithms:synchronous phase detection algorithms [9]and the least squares iterative algorithm [10]. The four-step algorithm in synchronous phase detection algorithm is in common use. The calculation equation is)2/3,,(),,()]2/,,()0,,([2/1),(πηξπηξπηξηξηξiI I iI I E --+=2.2 Reconstructing original object wave by reverse-transform algorithmObject wave from the original object spreads front.The processing has exact and clear description and expression in physics and mathematics. By phase-shifting technique, we have obtained information of the object wave spreading to a certain distance from the original object. Therefore, in order to get the information of the object wave at its initial spreading position, what we need to do is a reverse work.Fig.1 Geometric coordinate of digital holographyexact registering distance.The focusing functions normally applied can be divided into four types: gray and gradient function, frequency-domain function, informatics function and statistics function. Gray evaluation function is easy to calculate and also robust. It can satisfy the demand of common focusing precision. We apply the intensity sum of reconstruction image as the evaluation function:min ),(11==∑∑==M k Nl l k SThe calculation is described in Fig.2. The position occurring the turning point correspondes to the best registration distanced, also equals to the reconstructing distance d '.It should be indicated that if we only need to reconstruct the phase map of the object wave, the registration distance substituted into the calculation equation is permitted having a departure from its true value.4 Spatial resolution of digital holography4.1 Affecting factors of the spatial resolution of digital holographyIt should be considered in three respects: (1) sizes of the object and the registering material, and the direction of the reference beam, (2) resolution of the registering material, and (3) diffraction limitation.For pointx2on the object shown in Fig.3, the limits of spatial frequency are λξθλθθ⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫ ⎝⎛-'-=-=-0211maxmax tan sin sin sin sin z x f R R Fig.2 Determining reconstructing distanceλξθλθθ⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫⎝⎛-'-=-=-211minmintansinsinsinsin zxfRRFrequency range isλξξ⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫⎝⎛-'-⎥⎦⎤⎢⎣⎡⎪⎪⎭⎫⎝⎛-=∆--211211tansintansinzxzxfso the range is unrelated to the reference beam.Considering the resolution of registering material in order to satisfy the sampling theory, phase difference between adjacent points on the recording plate should be less than π, namely resolution of the registration material.cfff=∆η21)(minmaxπ4.2 Expanding the spatial resolution of reconstruction imageExpanding the spatial resolution can be realized at least in three ways: (1) Reducing the registration distance z0 can improve the reconstruction resolution, but it goes with reduction of the reconstruction area at the same ratio.Therefore, this method has its limitation. (2) Increasing the resolution and the imaging size of CCD with expensive price. (3) Applying image-synthesizing technique[11]CCD captures a few of images between which there is small displacement (usually a fraction of the pixel size) vertical to the CCD plane, shown in Fig.4(Schematic of vertical moving is the same).This method has two disadvantages. First, it is unsuitable for dynamic testing and can only be applied in the static image reconstruction. Second, because the pixel size is small (usually 5μm to 10μm) and the displacement should a fraction of this size (for example 2μm), it needs a moving table with high resolution and precision. Also it needs high stability in whole testing.In general, improvement of the spatial resolution of digital reconstruction is Fig.3 Relationship between object and CCDstill a big problem for the application of digital holography.5 Testing resultsFig.5 is the photo of the testing system. The paper does testing on two coins. The pixel size of the CCD is 4.65μm and there are 1 392×1 040 pixels. The firstis one Yuan coin of RMB (525 mm) used for image reconstruction by phase-shifting digital holography. The second is one Jiao coin of RMB (520 mm) for the testing of deformation measurement also by phase-shifting digital holography.5.1 Result of image reconstructionThe dimension of the one Yuancoin is 25 mm. The registrationdistance measured by ruler isabout 385mm. We capture ourphase-shifting holograms andreconstruct the image byphase-shifting digital holography.Fig.6 is the reconstructed image.Fig.7 is the curve of the auto-focusFig.4 Image capturing by moving CCD along horizontal directionFig.5 Photo of the testing systemfunction, from which we determine the real registration distance 370 mm. We can also change the controlling precision, for example 5mm, 0.1 mm,etc., to get more course or precision reconstruction position.5.2 Deformation measurementIn digital holography, the method of measuring deformation measurement differs from the traditional holography. It gets object wave before and after deformation and then subtract their phases to obtain the deformation. The study tested effect of heating deformation on the coin of one Jiao. The results are shown in Fig.8, Where (a) is the interferential signal of the object waves before and after deformation, and (b) is the wrapped phase difference.5.3 Improving the spatial resolutionFor the tested coin, we applied four sub-low-resolution holograms to reconstruct the high-resolution by the image-synthesizing technique. Fig.9 (a) is the reconstructed image by one low-resolution hologram, and (b) is the high-resolution image reconstructed from four low-resolution holograms.Fig.6 Reconstructed image Fig.7 Auto-focus functionFig.8 Heating deformation resultsFig.9 Comparing between the low and high resolution reconstructed image6 SummaryDigital holography can obtain phase and amplitude of the object wave at the same time. Compared to other techniques is a big advantage. Phase-shifting digital holography can realize image reconstruction and deformation with less noise. But it is unsuitable for dynamic testing. Applying the intensity sum of the reconstruction image as the auto-focusing function to evaluate the registering distance is easy, and computation is fast. Its precision is also sufficient. The image-synthesizing technique can improve spatial resolution of digital holography, but its static characteristic reduces its practicability. The limited dimension and too big pixel size are still the main obstacles for widely application of digital holography.外文文献译文:标题:图像重建中的相移数字全息摘要:相移数字全息术被用来研究研究艺术品的内部缺陷。

【2018最新】英文文献快速中文翻译-优秀word范文 (10页)

本文部分内容来自网络整理,本司不为其真实性负责,如有异议或侵权请及时联系,本司将立即删除!== 本文为word格式,下载后可方便编辑和修改! ==英文文献快速中文翻译篇一:英文文献小短文(原文加汉语翻译)A fern that hyperaccumulates arsenic(这是题目,百度一下就能找到原文好,原文还有表格,我没有翻译)A hardy, versatile, fast-growing plant helps to remove arsenic from contaminated soilsContamination of soils with arsenic,which is both toxic and carcinogenic, is widespread1. We have discovered that the fern Pteris vittata (brake fern) is extremely efficient in extracting arsenicfrom soils and translocating it into its above-ground biomass. This plant —which, to our knowledge, is the first known arsenic hyperaccumulator as well as the first fern found to function as a hyperaccumulator— has many attributes that recommend it for use in the remediation of arsenic-contaminated soils.We found brake fern growing on a site in Central Florida contaminated with chromated copper arsenate (Fig. 1a). We analysed the fronds of plants growing at the site for total arsenic by graphite furnace atomic absorption spectroscopy. Of 14 plant species studied, only brake fern contained large amounts of arsenic (As;3,280–4,980p.p.m.). We collected additional samples of the plant and soil from the contaminated site (18.8–1,603 p.p.m. As) and from an uncontaminated site (0.47–7.56 p.p.m. As). Brake fern extracted arsenic efficiently from these soils into its fronds: plants growingin the contaminated site contained 1,442–7,526p.p.m. Arsenic and those from the uncontaminated site contained11.8–64.0 p.p.m. These values are much higher than those typical for plants growing in normal soil, which contain less than 3.6 p.p.m. of arsenic3.As well as being tolerant of soils containing as much as 1,500 p.p.m. arsenic, brake fern can take up large amounts of arsenic into its fronds in a short time (Table 1). Arsenic concentration in fernfronds growing in soil spiked with 1,500 p.p.m. Arsenic increasedfrom 29.4 to 15,861 p.p.m. in two weeks. Furthermore, in the same period, ferns growing in soil containing just 6 p.p.m. arsenic accumulated 755 p.p.m. Of arsenic in their fronds, a 126-fold eichment. Arsenic concentrations in brake fern roots were less than 303 p.p.m., whereas those in the fronds reached 7,234 p.p.m.Addition of 100 p.p.m. Arsenic significantly stimulated fern growth, resulting in a 40% increase in biomass compared with the control (data not shown).After 20 weeks of growth, the plant was extracted using a solution of 1:1 methanol:water to speciate arsenic with high-performance liquid chromatography–inductively coupled plasma mass spectrometry. Almostall arsenic was present as relatively toxic inorganic forms, withlittle detectable organoarsenic species4. The concentration of As(III) was greater in the fronds (47–80%) than in the roots (8.3%), indicating that As(V) was converted to As(III) during translocation from roots to fronds.As well as removing arsenic from soils containing different concentrations of arsenic (Table 1), brake fern also removed arsenic from soils containing different arsenic species (Fig. 1c). Again, upto 93% of the arsenic was concentrated in the fronds. Although both FeAsO4 and AlAsO4 are relatively insoluble in soils1, brake fern hyperaccumulated arsenic derived from these compounds into its fronds (136–315 p.p.m.) at levels 3–6 times greater than soil arsenic.Brake fern is mesophytic and is widely cultivated and naturalized in many areas with a mild climate. In the United States, it grows in the southeast and in southern California5. The fern is versatile and hardy, and prefers sunny (unusual for a fern) and alkaline environments (where arsenic is more available). It has considerable biomass, and is fast growing, easy to propagate,and perennial.We believe this is the first report of significant arsenic hyperaccumulationby an unmanipulated plant. Brake fern has great potential toremediate arsenic-contaminated soils cheaply and could also aid studies of arsenic uptake, translocation, speciation, distributionand detoxification in plants. *Soil and Water Science Department, University ofFlorida, Gainesville, Florida 32611-0290, USAe-mail: lqma@?Cooperative Extension Service, University ofGeorgia, Terrell County, PO Box 271, Dawson,Georgia 31742, USA?Department of Chemistry & SoutheastEnvironmental Research Center, FloridaInternational University, Miami, Florida 33199,1. Nriagu, J. O. (ed.) Arsenic in the Environment Part 1: Cycling and Characterization (Wiley, New York, 1994).2. Brooks, R. R. (ed.) Plants that Hyperaccumulate Heavy Metals (Cambridge Univ. Press, 1998).3. Kabata-Pendias, A. & Pendias, H. in Trace Elements in Soils and Plants 203–209 (CRC, Boca Raton, 1991).4. Koch, I., Wang, L., Ollson, C. A., Cullen, W. R. & Reimer, K. J. Envir. Sci. Technol. 34, 22–26 (201X).5. Jones, D. L. Encyclopaedia of Ferns (Lothian, Melbourne, 1987).积累砷的蕨类植物耐寒,多功能,生长快速的植物,有助于从污染土壤去除砷有毒和致癌的土壤砷污染是非常广泛的。

中英文外文文献翻译中小企业财务风险管理研究

本科毕业设计(论文)中英文对照翻译(此文档为word格式,下载后您可任意修改编辑!)作者:Bernard G期刊:International Journal of Information Business and Management 第5卷,第3期,pp:41-51.原文The research of financial Risk Management in SMESBernard GINTRUDUCTIONSmall and medium sized enterprises (SME) differ from large corporations among other aspects first of all in their size. Theirimportance in the economy however is large . SME sector of India is considered as the backbone of economy contributing to 45% of the industrial output, 40% of India’s exports, employing 60 million people, create 1.3 million jobs every year and produce more than 8000 quality products for the Indian and international markets. With approximately 30 million SMEs in India, 12 million people expected to join the workforce in next 3 years and the sector growing at a rate of 8% per year, Government of India is taking different measures so as to increase their competitiveness in the international market. There are several factors that have contributed towards the growth of Indian SMEs. Few of these include; funding of SMEs by local and foreign investors, the new technology that is used in the market is assisting SMEs add considerable value to their business, various trade directories and trade portals help facilitate trade between buyer and supplier and thus reducing the barrier to trade With this huge potential, backed up by strong government support; Indian SMEs continue to post their growth stories. Despite of this strong growth, there is huge potential amongst Indian SMEs that still remains untapped. Once this untapped potential becomes the source for growth of these units, there would be no stopping to India posting a GDP higher than that of US and China and becoming the world’s economic powerhouse. RESEARCH QUESTIONRisk and economic activity are inseparable. Every business decisionand entrepreneurial act is connected with risk. This applies also to business of small and medium sized enterprises as they are also facing several and often the same risks as bigger companies. In a real business environment with market imperfections they need to manage those risks in order to secure their business continuity and add additional value by avoiding or reducing transaction costs and cost of financial distress or bankruptcy. However, risk management is a challenge for most SME. In contrast to larger companies they often lack the necessary resources, with regard to manpower, databases and specialty of knowledge to perform a standardized and structured risk management. The result is that many smaller companies do not perform sufficient analysis to identify their risk. This aspect is exacerbated due to a lack in literature about methods for risk management in SME, as stated by Henschel: The two challenging aspects with regard to risk management in SME are therefore: 1. SME differ from large corporations in many characteristics 2. The existing research lacks a focus on risk management in SME The following research question will be central to this work: 1.how can SME manage their internal financial risk? 2.Which aspects, based on their characteristics, have to be taken into account for this? 3.Which mean fulfils the requirements and can be applied to SME? LITERA TURE REVIEWIn contrast to larger corporations, in SME one of the owners is oftenpart of the management team. His intuition and experience are important for managing the company. Therefore, in small companies, the (owner-) manager is often responsible for many different tasks and important decisions. Most SME do not have the necessary resources to employ specialists on every position in the company. They focus on their core business and have generalists for the administrative functions. Behr and Guttler find that SME on average have equity ratios lower than 20%. The different characteristics of management, position on procurement and capital markets and the legal framework need to be taken into account when applying management instruments like risk management. Therefore the risk management techniques of larger corporations cannot easily be applied to SME. In practice it can therefore be observed that although SME are not facing less risks and uncertainties than large companies, their risk management differs from the practices in larger companies. The latter have the resources to employ a risk manager and a professional, structured and standardized risk management system. In contrast to that, risk management in SME differs in the degree of implementation and the techniques applied. Jonen & Simgen-Weber With regard to firm size and the use of risk management. Beyer, Hachmeister & Lampenius observe in a study from 2010 that increasing firm size among SME enhances the use of risk management. This observation matches with the opinion of nearly 10% of SME, which are of the opinion, that risk management is onlyreasonable in larger corporations. Beyer, Hachmeister & Lampenius find that most of the surveyed SME identify risks with help of statistics, checklists, creativity and scenario analyses. reveals similar findings and state that most companies rely on key figure systems for identifying and evaluating the urgency of business risks. That small firms face higher costs of hedging than larger corporations. This fact is reducing the benefits from hedging and therefore he advises to evaluate the usage of hedging for each firm individually. The lacking expertise to decide about hedges in SME is also identified by Eckbo, According to his findings, smaller companies often lack the understanding and management capacities needed to use those instruments. METHODOLOGY USE OF FINANCIAL ANAL YSIS IN SME RISK MANAGEMENT How financial analysis can be used in SME risk management? Development of financial risk overview for SME The following sections show the development of the financial risk overview. After presenting the framework, the different ratios will be discussed to finally present a selection of suitable ratios and choose appropriate comparison data. Framework for financial risk overviewThe idea is to use a set of ratios in an overview as the basis for the financial risk management.This provides even more information than the analysis of historicaldata and allows reacting fast on critical developments and managing the identified risks. However not only the internal data can be used for the risk management. In addition to that also the information available in the papers can be used. Some of them state average values for the defaulted or bankrupt companies one year prior bankruptcy -and few papers also for a longer time horizon. Those values can be used as a comparison value to evaluate the risk situation of the company. For this an appropriate set of ratios has to be chosen. The ratios, which will be included in the overview and analysis sheet, should fulfill two main requirements. First of all they should match the main financial risks of the company in order to deliver significant information and not miss an important risk factor. Secondly the ratios need to be relevant in two different ways. On the one hand they should be applicable independently of other ratios. This means that they also deliver useful information when not used in a regression, as it is applied in many of the papers. On the other hand to be appropriate to use them, the ratios need to show a different development for healthy companies than for those under financial distress. The difference between the values of the two groups should be large enough to see into which the observed company belongs. Evaluation of ratios for financial risk overview When choosing ratios from the different categories, it needs to be evaluated which ones are the most appropriate ones. For this some comparison values are needed inorder to see whether the ratios show different values and developments for the two groups of companies. The most convenient source for the comparison values are the research papers as their values are based on large samples of annual reports and by providing average values outweigh outliers in the data. Altman shows a table with the values for 8 different ratios for the five years prior bankruptcy of which he uses 5, while Porporato & Sandin use 13 ratios in their model and Ohlson bases his evaluation on 9 figures and ratios [10]. Khong, Ong & Y ap and Cerovac & Ivicic also show the difference in ratios between the two groups, however only directly before bankruptcy and not as a development over time [9]. Therefore this information is not as valuable as the others ([4][15]).In summary, the main internal financial risks in a SME should be covered by financial structure, liquidity and profitability ratios, which are the main categories of ratios applied in the research papers.Financial structureA ratio used in many of the papers is the total debt to total assets ratio, analyzing the financial structure of the company. Next to the papers of Altman, Ohlson and Porporato & Sandin also Khong, Ong & Y ap and Cerovac & Ivicic show comparison values for this ratio. Those demonstrate a huge difference in size between the bankrupt andnon-bankrupt groups.Therefore the information of total debt/total assets is more reliable and should rather be used for the overview. The other ratios analyzing the financial structure are only used in one of the papers and except for one the reference data only covers the last year before bankruptcy. Therefore a time trend cannot be detected and their relevance cannot be approved.译文中小企业财务风险管理研究博纳德引言除了其他方面,中小型企业(SME)与大型企业的不同之处首先在于他们的规模不同,但是,他们在国民经济中同样具有重要的作用。

论文翻译 Word 文档

pH对CuO吸附和解析SeO32-和SeO42-的影响。

如图1所示为pH与CuO对SeO32-的吸附于解析的函数变化。

pH=9.5时,CuO粉末对SeO32-在其水溶液中的吸收率韦100%。

随着pH的增加,CuO粉末对SeO32-的吸收率下降,当pH=12.5时SeO32-大部分存在在其溶液中,即吸附量很少。

增加的氧化物阴离子的吸附随pH 值降低是阴离子的吸附过程的一个典型特征。

在图1中表明CuO对SeO32-吸收是一个可逆过程。

这个结论同样可以运用于针铁矿(a-FeOOH)对的吸收随pH变化的函数关系中。

如图1所示为pH与CuO对SeO42-的吸附于解析的函数变化。

结果表明在pH=6.0是CuO对SeO42完全吸收。

随着pH的增加,CuO粉末对SeO42-的吸收率下降,当pH=11.0时,几乎不吸收。

表明CuO对SeO42-吸收也是一个可逆过程。

本杰明对无定型氢氧化铁对SeO42-的吸收随pH变化函数的研究表明,在pH=4.5时,只有85%被吸收。

他也表明,溶液中的二价阳离子,如Cu2+对Fe2O3.H2O对SeO42-的吸收有积极影响。

Balistrieri和Chao表明pH=6时,体系中存在300mg/L(a-FeOOH)时对的吸收很少量(<20%)。

然而,这个研究表明,当PH=6.0时,较少含量的CuO能将从其水溶液中将近100%吸收。

一中可能性是,CuO比(a-FeOOH)需要较高的pH(9.5),(a-FeOOH)需要较低的pH,在6-7之间。

吸收和解析的结果表明,与SeO32-相比,CuO粒子对SeO42-的吸收更容易。

例如,在pH=11.0时,只有50%SeO32-被吸收在CuO表面(图1),而SeO42-是100%(图2)。

一种可能是SeO32-结构较复杂,形成较强的内力,SeO42-内力较弱。

图3和图4表明CuO粒子的浓度对SeO42-和SeO32-的吸收的影响与pH的变化函数关系。

水轮机和水力发电文献翻译(Word最新版)

水轮机和水力发电文献翻译通过整理的水轮机和水力发电文献翻译相关文档,渴望对大家有所扶植,感谢观看!中文3840字外文文献:hydraulicturbines and hydro-electric power Abstract Power may be developed from water by three fundamental processes : by action of its weight, of its pressure, or of its velocity, or by a combination of any or all three. In modern practice the Pelton or impulse wheel is the only type which obtains power by a single process the action of one or more high-velocity jets. This type of wheel is usually found in high-head developments. Faraday had shown that when a coil is rotated in a magnetic field electricity is generated. Thus, in order to produce electrical energy, it is necessary that we should produce mechanical energy, which can be used to rotate the ‘coil’. The mechanical energy is produced by running a prime mover (known as turbine ) by the energy of fuels or flowing water. This mechanical power is converted into electrical power by electric generator which is directly coupled to the shaft of turbine and is thus run by turbine. The electrical power, which is consequently obtained at the terminals of the generator, is then transited to the area where it is to be used for doing work.he plant ormachinery which is required to produce electricity (i.e. prime mover +electric generator) is collectively known as power plant. The building, in which the entire machinery along with other auxiliary units is installed, is known as power house. Keywords hydraulic turbines hydro-electric power classification of hydel plants head scheme There has been practically no increase in the efficiency of hydraulic turbines since about 1925, when maximum efficiencies reached 93% or more. As far as maximum efficiency is concerned, the hydraulic turbine has about reached the practicable limit of development. Nevertheless, in recent years, there has been a rapid and marked increase in the physical size and horsepower capacity of individual units. In addition, there has been considerable research into the cause and prevention of cavitation, which allows the advantages of higher specific speeds to be obtained at higher heads than formerly were considered advisable. The net effect of this progress with larger units, higher specific speed, and simplification and improvements in design has been to retain for the hydraulic turbine the important place which it has long held at one of the most important prime movers. 1. types of hydraulic turbines Hydraulic turbines may be grouped in two general classes: the impulse type which utilizes the kinetic energy of a high-velocity jet which acts upon only a small partof the circumference at any instant, and the reaction type which develops power from the combined action of pressure and velocity of the water that completely fills the runner and water passages. The reaction group is divided into two general types: the Francis, sometimes called the reaction type, and the propeller type. The propeller class is also further subdivided into the fixed-blade propeller type, and the adjustable-blade type of which the Kaplan is representative. 1.1 impulse wheels With the impulse wheel the potential energy of the water in the penstock is transformed into kinetic energy in a jet issuing from the orifice of a nozzle. This jet discharge freely into the atmosphere inside the wheel housing and strikes against the bowl-shaped buckets of the runner. At each revolution the bucket enters, passes through, and passes out of the jet, during which time it receives the full impact force of the jet. This produces a rapid hammer blow upon the bucket. At the same time the bucket is subjected to the centrifugal force tending to separate the bucket from its disk. On account of the stresses so produced and also the scouring effects of the water flowing over the working surface of the bowl, material of high quality of resistance against hydraulic wear and fatigue is required. Only for very low heads can cast iron be employed. Bronze and annealed cast steel are normallyused. 1.2 Francis runners With the Francis type the water enters from a casing or flume with a relatively low velocity, passes through guide vanes or gates located around the circumstance, and flows through the runner, from which it discharges into a draft tube sealed below the tail-water level. All the runner passages are completely filled with water, which acts upon the whole circumference of the runner. Only a portion of the power is derived from the dynamic action due to the velocity of the water, a large part of the power being obtained from the difference in pressure acting on the front and back of the runner buckets. The draft tube allows maximum utilization of the available head, both because of the suction created below the runner by the vertical column of water and because the outlet of he draft tube is larger than the throat just below the runner, thus utilizing a part of the kinetic energy of the water leaving the runner blades. 1.3 propeller runners nherently suitable for low-head developments, the propeller-type unit has effected marked economics within the range of head to which it is adapted. The higher speed of this type of turbine results in a lower-cost generator and somewhat smaller powerhouse substructure and superstructure. Propeller-type runners for low heads and small outputs are sometimes constructed of cast iron. For heads above 20 ft, they are made of cast steel, a much morereliable material. Large-diameter propellers may have individual blades fastened to the hub. 1.4 adjustable-blade runners The adjustable-blade propeller type is a development from the fixed-blade propeller wheel. One of the best-known units of this type is the Kaplan unit, in which the blades may be rotated to the most efficient angle by a hydraulic servomotor. A cam on the governor is used to cause the blade angle to change with the gate position so that high efficiency is always obtained at almost any percentage of full load. By reason of its high efficiency at all gate openings, the adjustable-blade propeller-type unit is particularly applicable to low-head developments where conditions are such that the units must be operated at varying load and varying head. Capital cost and maintenance for such units are necessarily higher than for fixed-blade propeller-type units operated at the point of maximum efficiency. 2. thermal and hydropower As stated earlier, the turbine blades can be made to run by the energy of fuels or flowing water. When fuel is used to produce steam for running the steam turbine, then the power generated is known as thermal power. The fuel which is to be used for generating steam may either be an ordinary fuel such as coal, fuel oil, etc., or atomic fuel or nuclear fuel. Coal is simply burnt to produce steam from water and is the simplest and oldesttype of fuel. Diesel oil, etc. may also be used as fuels for producing steam. Atomic fuels such as uranium or thorium may also be used to produce steam. When conventional type of fuels such s coal, oil, etc. (called fossils ) is used to produce steam for running the turbines, the power house is generally called an Ordinary thermal power station or Thermal power station. But when atomic fuel is used to produce steam, the power station, which is essentially a thermal power station, is called an atomic power station or nuclear power station. In an ordinary thermal power station, steam is produced in a water boiler, while in the atomic power station; the boiler is replaced y a nuclear reactor and steam generator for raising steam. The electric power generated in both these cases is known as thermal power and the scheme is called thermal power scheme. But, when the energy of the flowing water is used to run the turbines, then the electricity generated is called hydroelectric power. This scheme is known as hydro scheme, and the power house is known as hydel power station or hydroelectric power station. In a hydro scheme, a certain quantity of water at a certain potential head is essentially made to flow through the turbines. The head causing flow runs the turbine blades, and thus producing electricity from the generator coupled to turbine. In this chapter, we are concerned with hydel scheme only.3.classification of hydel plants Hydro-plants may be classified on the basis of hydraulic characteristics as follow: ① run-off river plants .②storage plants.③pumped storage plants.④tidal plants. th ey are described below. (1) Run-off river plants. These plants are those which utilize the minimum flow in a river having no appreciable pondage on its upstream side. A weir or a barrage is sometimes constructed across a river simply to raise and maintain the water level at a pre-determined level within narrow limits of fluctuations, either solely for the power plants or for some other purpose where the power plant may be incidental. Such a scheme is essentially a low head scheme and may be suitable only on a perennial river having sufficient dry weather flow of such a magnitude as to make the development worthwhile. Run-off river plants generally have a very limited storage capacity, and can use water only when it comes. This small storage capacity is provided for meeting the hourly fluctuations of load. When the available discharge at site is more than the demand (during off-peak hours ) the excess water is temporarily stored in the pond on the upstream side of the barrage, which is then utilized during the peak hours. he various examples of run-off the river pant are: Ganguwal and Kolta power houses located on Nangal Hydel Channel, Mohammad Pur and Pathri power houses on GangaCanal and Sarda power house on Sarda Canal. The various stations constructed on irrigation channels at the sites of falls, also fall under this category of plants. (2) Storage plants A storage plant is essentially having an upstream storage reservoir of sufficient size so as to permit, sufficient carryover storage from the monsoon season to the dry summer season, and thus to develop a firm flow substantially more than minimum natural flow. In this scheme, a dam is constructed across the river and the power house may be located at the foot of the dam such as in Bhakra, Hirakud, Rihand projects etc. the power house may sometimes be located much away from the dam (on the downstream side). In such a case, the power house is located at the end of tunnels which carry water from the reservoir. The tunnels are connected to the power house machines by means of pressure pen-stocks which may either be underground (as in Mainthon and Koyna projects) or may be kept exposed (as in Kundah project). When the power house is located near the dam, as is generally done in the low head installations ; it is known as concentrated fall hydroelectric development. But when the water is carried to the power house at a considerable distance from the dam through a canal, tunnel, or pen-stock; it is known as a divided fall development. (3) Pumped storage plants. A pumped storage plantgenerates power during peak hours, but during the off-peak hours, water is pumped back from the tail water pool to the headwater pool for future use. The pumps are run by some secondary power from some other plant in the system. The plant is thus primarily meant for assisting an existing thermal plant or some other hydel plant. During peak hours, the water flows from the reservoir to the turbine and electricity is generated. During off-peak hours, the excess power is available from some other plant, and is utilized for pumping water from the tail pool to the head pool, this minor plant thus supplements the power of another major plant. In such a scheme, the same water is utilized again and again and no water is wasted. For heads varying between 15m to 90m, reservoir pump turbines have been devised, which can function both as a turbine as well as a pump. Such reversible turbines can work at relatively high efficiencies and can help in reducing the cost of such a plant. Similarly, the same electrical machine can be used both as a generator as well as a motor by reversing the poles. The provision of such a scheme helps considerably in improving the load factor of the power system. (4) Tidal plants Tidal plants for generation of electric power are the recent and modern advancements, and essentially work on the principle that there is a rise in seawater during high tide period and afall during the low ebb period. The water rises and falls twice a day; each fall cycle occupying about 12 hours and 25 minutes. The advantage of this rise and fall of water is taken in a tidal plant. In other words, the tidal range, i.e. the difference between high and low tide levels is utilized to generate power. This is accomplished by constructing a basin separated from the ocean by a partition wall and installing turbines in opening through this wall. Water passes from the ocean to the basin during high tides, and thus running the turbines and generating electric power. During low tide,the water from the basin runs back to ocean, which can also be utilized to generate electric power, provided special turbines which can generate power for either direction of flow are installed. Such plants are useful at places where tidal range is high. Rance power station in France is an example of this type of power station. The tidal range at this place is of the order of 11 meters. This power house contains 9 units of 38,000 kW. 4.Hydro-plants or hydroelectric schemes may be classified on the basis of operating head on turbines as f ollows: ① low head scheme (head<15m),②medium head scheme (head varies between 15m to 60 m) ,③high head scheme (head>60m). They are described below: (1) Low head scheme. A low head scheme is one which uses water head of less than 15 meters or so. A run offriver plant is essentially a low head scheme, a weir or a barrage is constructed to raise the water level, and the power house is constructed either in continuation with the barrage or at some distance downstream of the barrage, where water is taken to the power house through an intake canal. (2) Medium head scheme A medium head scheme is one which used water head varying between 15 to 60 meters or so. This scheme is thus essentially a dam reservoir scheme, although the dam height is mediocre. This scheme is having features somewhere between low had scheme and high head scheme.(3) High head scheme. A high head scheme is one which uses water head of more than 60m or so. A dam of sufficient height is, therefore, required to be constructed, so as to store water on the upstream side and to utilize this water throughout the year. High head schemes up to heights of 1,800 meters have been developed. The common examples of such a scheme are: Bhakra dam in (Punjab), Rihand dam in (U.P.), and Hoover dam in (U.S.A), etc. The naturally available high falls can also be developed for generating electric power. The common examples of such power developments are: Jog Falls in India, and Niagara Falls in U.S.A. 水轮机和水力发电摘要水的能量可以通过三种基本方法来获得:利用水的重力作用、水的压力作用或水的流速作用,或者其中随意两种或全部三种作用的组合。

SCI文献翻译DOC

The locust genome provides insight into swarmformation and long-distance flight蝗虫的基因组对集群和长途飞行提供了见解Locusts are one of the world’s most destructive agricultur al pests and represent a useful model system in entomology. Here we present a draft 6.5 Gb genome sequence of Locusta migratoria, which is the largest animal genome sequenced so far. Our findings indicate that the large genome size of L. migratoriais likely to be because of transposable element proliferation combined with slow rates of loss for these elements. Methylome and transcriptome analyses reveal complex regulatory mechanisms involved in microtubule dynamic-mediated synapse plasticity during phase change. We find significant expansion of gene families associated with energy consumption and detoxification, consistent with long-distance flight capacity and phytophagy. We report hundreds of potential insecticide target genes, including cys-loop ligand-gated ion channels, G-protein-coupled receptors and lethal genes. The L. migratoria genome sequence offers new insights into the biology and sustainable management of this pest species, and will promote its wide use as a model system.蝗虫是一个世界上最具破坏性的农业害虫,并且在昆虫学中代表一个有用的模式系统。

英文文献全文翻译

英文文献全文翻译全文共四篇示例,供读者参考第一篇示例:LeGuin, Ursula K. (December 18, 2002). "Dancing at the Edge of the World: Thoughts on Words, Women, Places".《世界边缘的舞蹈:关于语言、女性和地方的思考》Introduction:In "Dancing at the Edge of the World," Ursula K. LeGuin explores the intersection of language, women, and places. She writes about the power of words, the role of women in society, and the importance of our connection to the places we inhabit. Through a series of essays, LeGuin invites readers to think critically about these topics and consider how they shape our understanding of the world.Chapter 1: LanguageConclusion:第二篇示例:IntroductionEnglish literature translation is an important field in the study of language and culture. The translation of English literature involves not only the linguistic translation of words or sentences but also the transfer of cultural meaning and emotional resonance. This article will discuss the challenges and techniques of translating English literature, as well as the importance of preserving the original author's voice and style in the translated text.Challenges in translating English literature第三篇示例:Title: The Importance of Translation of Full English TextsTranslation plays a crucial role in bringing different languages and cultures together. More specifically, translating full English texts into different languages allows for access to valuable information and insights that may otherwise be inaccessible to those who do not speak English. In this article, we will explore the importance of translating full English texts and the benefits it brings.第四篇示例:Abstract: This article discusses the importance of translating English literature and the challenges translators face when putting together a full-text translation. It highlights the skills and knowledge needed to accurately convey the meaning and tone of the original text while preserving its cultural and literary nuances. Through a detailed analysis of the translation process, this article emphasizes the crucial role translators play in bridging the gap between languages and making English literature accessible to a global audience.IntroductionEnglish literature is a rich and diverse field encompassing a wide range of genres, styles, and themes. From classic works by Shakespeare and Dickens to contemporary novels by authors like J.K. Rowling and Philip Pullman, English literature offers something for everyone. However, for non-English speakers, accessing and understanding these works can be a challenge. This is where translation comes in.Translation is the process of rendering a text from one language into another, while striving to preserve the original meaning, tone, and style of the original work. Translating afull-length English text requires a deep understanding of both languages, as well as a keen awareness of the cultural andhistorical context in which the work was written. Additionally, translators must possess strong writing skills in order to convey the beauty and complexity of the original text in a new language.Challenges of Full-text TranslationTranslating a full-length English text poses several challenges for translators. One of the most significant challenges is capturing the nuances and subtleties of the original work. English literature is known for its rich and layered language, with intricate wordplay, metaphors, and symbolism that can be difficult to convey in another language. Translators must carefully consider each word and phrase in order to accurately convey the author's intended meaning.Another challenge of full-text translation is maintaining the author's unique voice and style. Each writer has a distinct way of expressing themselves, and a good translator must be able to replicate this voice in the translated text. This requires a deep understanding of the author's writing style, as well as the ability to adapt it to the conventions of the target language.Additionally, translators must be mindful of the cultural and historical context of the original work. English literature is deeply rooted in the history and traditions of the English-speaking world, and translators must be aware of these influences in orderto accurately convey the author's intended message. This requires thorough research and a nuanced understanding of the social, political, and economic factors that shaped the work.Skills and Knowledge RequiredTo successfully translate a full-length English text, translators must possess a wide range of skills and knowledge. First and foremost, translators must be fluent in both the source language (English) and the target language. This includes a strong grasp of grammar, syntax, and vocabulary in both languages, as well as an understanding of the cultural and historical context of the works being translated.Translators must also have a keen eye for detail and a meticulous approach to their work. Every word, sentence, and paragraph must be carefully considered and translated with precision in order to accurately convey the meaning of the original text. This requires strong analytical skills and a deep understanding of the nuances and complexities of language.Furthermore, translators must possess strong writing skills in order to craft a compelling and engaging translation. Translating a full-length English text is not simply a matter of substituting one word for another; it requires creativity, imagination, and a deep appreciation for the beauty of language. Translators mustbe able to capture the rhythm, cadence, and tone of the original work in their translation, while also adapting it to the conventions of the target language.ConclusionIn conclusion, translating a full-length English text is a complex and challenging task that requires a high level of skill, knowledge, and creativity. Translators must possess a deep understanding of both the source and target languages, as well as the cultural and historical context of the work being translated. Through their careful and meticulous work, translators play a crucial role in making English literature accessible to a global audience, bridging the gap between languages and cultures. By preserving the beauty and complexity of the original text in their translations, translators enrich our understanding of literature and bring the works of English authors to readers around the world.。

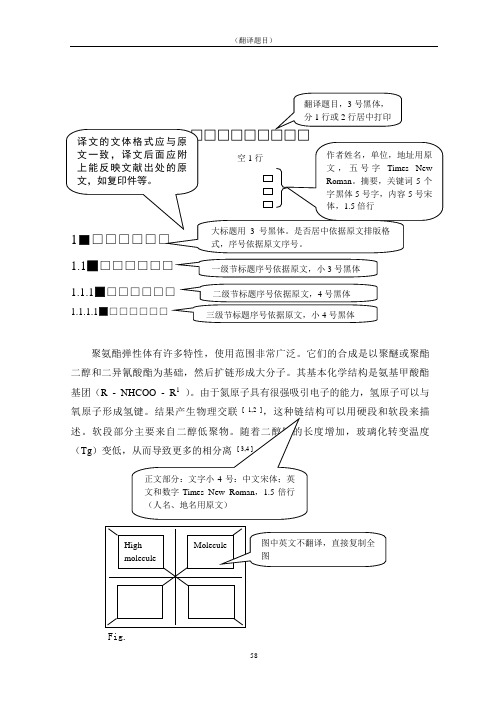

4文献翻译模板

(2-7)

(如果有的话)

表6-1■2000—2010年世界聚氨酯产量

CASE

3484940

4792195

5877100

476000

592370

669700

3672125

4944500

5942000

2290215

3423500

4418800

9923280

13752565

16907600

■■数据来源:2008年(企业快报[J].聚氨酯)

(正文部分字数应在3000字以上,具体应按各系(部)的具体要求执行)

空1行

参考文献

空1行

[1] Miller JA, Lin SB, Huang KKS, Cooper SL. Macromolecules ,1985;18:32.

[2] Boyarchuk YM, Rapport LY, Apukhtine NP. Polym Sci, USSR ,1965;7:859.

□□□□□□□□□

空1行

1■□□□□□□

1.1■□□□□□□

1.1.1■□□□□□□

1.1.1.1■□□□□□□

聚氨酯弹性体有许多特性,使用范围非常广泛。它们的合成是以聚醚或聚酯二醇和二异氰酸酯为基础,然后扩链形成大分子。其基本化学结构是氨基甲酸酯基团(R - NHCOO - R1)。由于氮原子具有很强吸引电子的能力,氢原子可以与氧原子形成氢键。结果产生物理交联[ 1,2 ],这种链结构可以用硬段和软段来描述。软段部分主要来自二醇低聚物。随着二醇链的长度增加,玻璃化转变温度(Tg)变低,从而导致更多的相分离[ 3,4 ]。

[3] Petrovic ZS, Simendic B. Rubber Chem and Technol ,1985; Rubber Chem and Technol,1985;58:701.

英语文献翻译文档