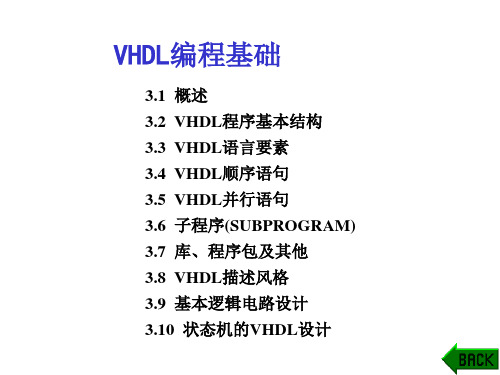

《VHDL的基本语法》

VHDL基本语句

例

ARCHITECTURE example OF mux4 IS BEGIN PROCESS (sel) 注 BEGIN ●CASE中的选择值必须在表达式的取值范围内; CASE sel IS WHEN 0=> q <= d0 ; ●CASE语句是无序的,所有表达式值都是并行 WHEN 1=> q <= d1 ; 处理;而IF语句是有序的,最起始、最优先 WHEN 2=> q<= d3 ; WHEN 3=> q<= d4 ; 的先处理; WHEN others => NULL; ●可以有很多分支,但OTHERS分支只能有一个, END CASE; 且只能位于最后;用来使所有选择值能涵盖表 END PROCESS; END example; 达式的所有取值,以免插入不必要的锁存器

3、用于多选控制的IF语句:

格式 IF 条件1 THEN

<顺序处理语句1>;

ELSIF 条件2 THEN <顺序处理语句2>; : ELSIF 条件n-1 THEN <顺序处理语句n-1>; ELSE <顺序处理语句n>; END IF;

P1: PROCESS (clk) BEGIN

IF (clk‘ event and clk=‗1‘ ) THEN

顺序语句

赋值语句

VHDL设计实体内的数据传递以及对端口界面外部数据的读写 都必须通过赋值语句的运行来实现。 功能是将一个值或表达式的运算结果传递给某一数据对象。 赋值语句有两种: 信号赋值语句和变量赋值语句 区别

《VHDL语法基础》PPT课件

(5) 在结构体ART3中,COMPONENT→END COMPONENT 语句结构对所要调用的或门和半加器两元件作了声明 (COMPONENT DECLARATION),并由SIGNAL语句定义了三 个信号D、E和F,作为中间信号转存点,以利于几个器件间的信 号连接。接下去的“PORT MAP( )”语句称为元件例化语句 (COMPONENT INSTANTIATION)。所谓例化,在电路板上, 相当于往上装配元器件;在逻辑原理图上,相当于从元件库中取 了一个元件符号放在电路原理图上,并对此符号的各引脚进行连 线。例化也可理解为元件映射或元件连接,MAP是映射的意思。 例如,语句“U2:H_ADDER PORT MAP(A=>E,B=>CIN, CO=>F,SO=>SUM)”表示将实体H_ADDER描述的元件U2的引 脚信号A、B、CO和SO分别连向外部信号E、CIN、F和SUM。

(2) VHDL具有丰富的仿真语句和库函数,使得在任何大系 统的设计早期,就能查验设计系统的功能可行性,随时可对系 统进行仿真模拟,使设计者对整个工程的结构和功能可行性做 出判断。

(3) VHDL语句的行为描述能力和程序结构,决定了它具 有支持大规模设计的分解和已有设计的再利用功能。符合市场 需求的大规模系统高效、高速的完成必须有多人甚至多个开发 组共同并行工作才能实现,VHDL中设计实体的概念、程序包 的概念、设计库的概念为设计的分解和并行工作提供了有利的 支持。

END ENTITY OR2; --实体OR2的结构体ART1的说明

ARCHITECTURE ART1 OF OR2 IS

BEGIN C<=A OR B; END ARCHITECTURE ART1;

2) 半加器的逻辑描述 -- IEEE库的使用说明

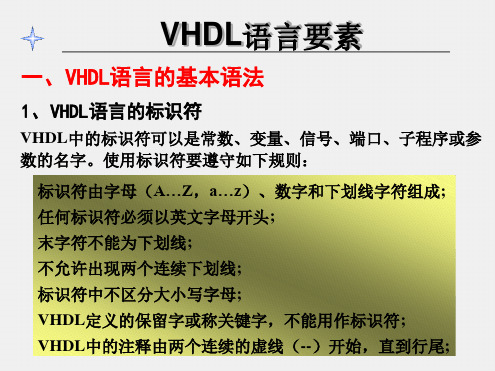

VHDL语言的基本语法解析

2、变量( Variable )

变量是一个局部变量,它只能在进程语句、函数语句和过程 语句结构中使用,用作局部数据存储。变量常用在实现某种算 法的赋值语句中。

一般格式:

VARIABLE 变量名:数据类型 约束条件:= 表达式;

例: VARIABLE x, y: INTEGER;

--定义x,y为整数变量

SIGNAL Y ,Z :BIT;

Y<=A(M) ;

--M是不可计算型下标表示

Z<=B(3) ;

--3是可计算型下标表示

C (0 TO 3)<=A (4 TO 7) ; -以段的方式进行赋值

C (4 TO 7)<=A (0 TO 3) ; -以段的方式进行赋值

二、VHDL语言的数据对象

1、常数( Constant )

常量的使用范围取决于它被定义的位置 :

(1)程序包中定义的常量具有最大的全局化特性,可以用在调 用此程序包的所有设计实体中;

(2)设计实体中定义的常量,其有效范围为这个实体定义的所 有的结构体;

(3)设计实体中某一结构体中定义的常量只能用于此结构体;

(4)结构体中某一单元定义的常量,如一个进程中,这个常量 只能用在这一进程中。

5,678,0,156E2(=15600) , 45_234_287(=45234287)

(2) 实数文字: 实数文字也都是十进制的数,但必 须带有小数点,如: 188.993, 88_670_551.453_909(=88670551.453909) ,

1.0,44.99E-2(=0.4499) ,1.335,0.0

?16#F.01#E+2ቤተ መጻሕፍቲ ባይዱ--( 十六进制数表示,等于 3841.00)

VHDL基本语法

变量不是真正的物理量 , 因此不能 出现在敏感信号表中. 出现在敏感信号表中. 在 process 语句中只作为输出存在的 信号 ( 出现在信号赋值符 " < =" 的左 边 ) 不能作为敏感信 号. 既出现在信号赋值符 "<=" 的左边 , 又出现在信号赋值符 "<=" 右边的信 号 , 可以出现在敏感信号表中 , 这是因 为这些信号既作为这块电路的输出 , 又 是电路内部的反馈信号. 是电路内部的反馈信号.

例7 2 与非门. 与非门. 参见程序' (参见程序'例7') ) 说明: 说明: 本例中 , 首先将与非门输入信号 a 和 b 并置 , 生成一个 2 位的 std_logic_vector 信号 sel .信号 C 是与非门的输出. 是与非门的输出.第一个 when 中的 "|" 代表或者 , 即 3 个条件中的任何一 语句. 个满足 , 执行 C <='1' 语句.

格式 : IF 条件 1 THEN 若干顺序执行语句 1 ELSIF 条件 2 THEN 若干顺序执行语句 2 … ELSIF 条件 n-1 THEN 若干顺序执行语句 n-1 ELSE 若干顺序执行语句 n END IF;

(5) 进程语句 进程语句(PROCESS)

进程语句是一个十分重要的语句 进程语句是一个十分重要的语句 , 本质上它描述了一个功能独立的电路 本质上它描述了一个功能独立的电路 块.

CASE语句与 语句一样也是个顺序执 语句与IF语句一样也是个顺序执 语句与 行语句,但使用上有区别. 行语句,但使用上有区别. CASE语句执行时是无序的,所有表达 语句执行时是无序的, 语句执行时是无序的 式是并行处理; 语句是有序的, 式是并行处理;而IF语句是有序的, 语句是有序的 先处理最优先的条件, 先处理最优先的条件,后处理次优先 条件. 条件. 在某种情况下,两种语句都可以使用, 在某种情况下,两种语句都可以使用, 语句比IF语句描述更简捷 但 CASE语句比 语句描述更简捷, 语句比 语句描述更简捷, 更清晰.故应优先选用CASE语句. 语句. 更清晰.故应优先选用 语句

VHDL语法入门

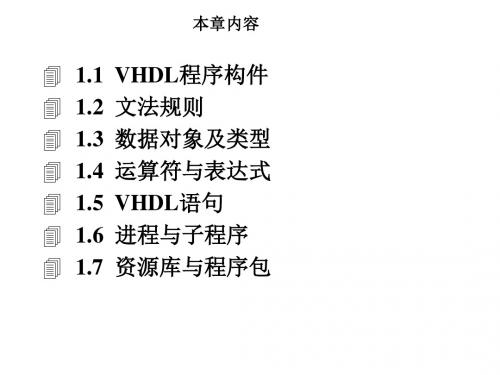

1.1 VHDL程序构件

配置说明

将具体的构造体分配给实体说明 示例

configuration conf1 of xor_gate is for data_flow end for; end conf1;

configuration conf2 of xor_gate is for structure end for; end conf1;

字符串

被双引号括起来的ASCII字符,如,“Hello”;

位串

被双引号括起来的数字序列,其前冠以基数说明符;如, B“0110_1111”,O“117”,X“FFE0”;

1.2 文法规则

文法格式

关键字、标识符:不区分大小写; 注释:‘--’,且只在该文本行有效; 分隔:‘;’为行分隔,VHDL的语句行可写在不同文本行

[端口说明;]

end [设计实体名] ;

1.1 VHDL程序构件

1.1 VHDL程序构件 IN

从外部输入至实体; 单向端口;

entity

1.1 VHDL程序构件 OUT

从实体输出至外部; 单向端口;

entity

1.1 VHDL程序构件 INOUT

可以从外部输入至实体; 也可以从实体输出至外部; 双向端口;

变量:

用于进程、子程序等模块的内部; 局部性数据对象;

1.3 数据对象及类型

例子:信号与变量

p2: process(a) variable tmp: integer:=1; begin tmp:=tmp*2; c2<=a+tmp; end process; end;

entity exmp1 is port(a: in Integer; b: out Integer); end; architecture behv of exmp1 is signal c1,c2: Integer; begin b<=c1+c2; p1: process(a) variable tmp: integer:=0; begin tmp:=tmp+1; c1<=a+tmp; end process;

VHDL基本语句用法 ppt课件

15

10.2.1 并行信号赋值语句

1. 简单信号赋值语句

格式:赋值目标 = 表达式

例: ARCHITECTURE curt OF bc1 IS SIGNAL s1, e, f, g, h : STD_LOGIC ; BEGIN output1 <= a AND b ; output2 <= c + d ; g <= e OR f ; h <= e XOR f ; s1 <= g ;

10.2.4 元件例化语句

1)格式:

COMPONENT 元件名 IS GENERIC (类属表); -- 元件定义(说明)语句

PORT (端口名表);

END COMPONENT 文件名;

例化名 :元件名 PORT MAP( [端口名 =>] 连接端口名,...) ;

2)说明:

- - - - 元件例化(调用)语句。

c;

END;

例1的逻辑电路图见 图1

2021/3/26

VHDL基本语句用法 ppt课件

18

3. 选择信号赋值语句

1)格式:

WITH 选择表达式 SELECT

赋值目标信号 <=表达式1 WHEN 选择值1 表达式2 WHEN 选择值2 ... 表达式n WHEN 选择值n;

2)举例:[例2]

[例3]

4)CASE 语句举例

2021/3/26

VHDL基本语句用法 ppt课件

4

例【 10.1】

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT (s4,s3, s2,s1 : IN STD_LOGIC;

VHDL语法简单总结

VHDL语法(yǔfǎ)简单总结VHDL语法简单(jiǎndān)总结VHDL语法(yǔfǎ)简单总结一个(yī ɡè)VHDL程序代码包含实体(shítǐ)(entity)、结构(jiégòu)体(architecture)、配置(pèizhì)(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型(lèixíng)上加一些约束条件,可以定义(dìngyì)该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用(shǐyòng)SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起(yīqǐ)形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型(lèixíng)语法结构SIGNAL signal_name: type_name [:=initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数(xìshù)类型定义SIGNAL delay_regs: delay_lines; –信号延迟(yánchí)寄存器声明CONSTANT coef: coeffs := ( ); –常量(chángliàng)系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以(suǒyǐ)必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

第3章VHDL语法基础

--设初始值

FOR I IN 1 DOWNTO 0 LOOP

IF (A(I)=‘1’ AND B(I)=‘0’) THEN

A_LESS _B<=FALSE;

EXIT;

ELSIF (A(I)=‘0’ AND B(I)=‘1’) THEN

A_LESS _B<=TRUE;

--A<B

EXIT;

ELSE NULL;

PROCESS(A) IS

BEGIN TMP <=‘0’;

FOR N IN 0 TO 7 LOOP

TMP <=TMP XOR A(N);

END LOOP; Y<= TMP;

结果:

END PROCESS;

Y=‘0’— A含偶数个‘1’,

END ARCHITECTURE ART;

Y=‘1’— A含奇数个‘1’。

BEGIN

PROCESS(A,B,C) IS

VARIABLE N: BOOLEAN;

BEGIN

C

IF A THEN N:=B;

ELSE N:=C; END IF; OUTPUT <=N; END PROCESS;

A

OUTPUT

B

对应的硬件电路

END ARCHITECTURE ART;

例3: 由两个2选1多路选择器构成的电路逻辑描述如图所示, 其中,当P1和P2为高电平时下端的通道接通。

A

S2 S1

D C

Z B A

ARCHITECTURE ART OF MUX41 IS

SIGNA S :STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

S<=S1 & S2;

VHDL基本语句用法

10.2.4 元件例化语句

COMPONENT 元件名 IS 1)格式: GENERIC (类属表); -- 元件定义(说明)语句 PORT (端口名表); END COMPONENT 文件名;

例化名 :元件名 PORT MAP( [端口名 =>] 连接端口名,...) ; - - - - 元件例化(调用)语句。 (1) 元件声明语句用于调用已生成的元件,这些元件可能在库中, 也可能是预先编写的元件实体描述.; (2) 元件语句可以在ARCHITECTURE,PACKAGE和BLOCK的说明部分.

--输入初始值 ----当sel=0时选中 当sel为1或3时选中 当sel为2、4、5、6或7时选中 当sel为8~15中任一值时选中

CASE 语句病句举例

【例10.2】

10.1.4 LOOP语句

1 、单个LOOP语句 格式: [ LOOP标号:] LOOP 顺序语句 END LOOP [ LOOP标号 ]; 2、FOR_LOOP语句 格式:

第10章

VHDL基本语句

一:主要内容:VHDL基本语句讲解 ① 顺序语句 ② 并行语句 二:重点掌握:常用VHDL基本语句及应用

10.1 顺序语句

10.1.1 赋值语句

信号赋值语句

变量赋值语句 • 变量赋值语句:

•信号代入语句:

格式: 目的信号变量<=信号变量表达式 例: a<=b;

格式: 目的变量:=表达式 例: c:=a+d

IF 条件 THEN … END IF; 10.1.3 CASE语句

1) CASE语句的结构:

CASE 表达式 IS When 选择值 => 顺序语句; When 选择值 => 顺序语句; ... 【WHEN OTHERS =>】; END CASE ;

VHDL基本语法

一、数据类型A. 标准数据类型1)整数类型(INTEGER)VARIBLE A:INTEGER RANGE -128 TO 128范围-(231-1)~ +(231-1)2#11111111# --binary,=255D8#377#16#FF#2)实数类型和浮点类型(REAL & FLOATING)实数范围-1.0E+38 ~ +1.0E+38大多数EDA工具不支持浮点类型16#0F#E+016#FF.FF#E-13)位类型(BIT)TYPE BITIS(‘0',‘1')4)位矢量类型(BIT_VECTOR)位矢量(bit_vector)类型实际上就是位(bit)的一位数组,它的表示方法是用双引号将一组位数据括起来。

例如:"11010111"。

不难看出,采用位矢量可以很方便地表示电路描述中的总线状态,这在VHDL程序中经常用到。

B"1111-1100" --长度为8X"FBC" --长度为12,=B"1111-1011-1100"O"371" --长度为9,=B"011-111-001"5)布尔类型(BOOLEAN)6)字符类型(CHARACTER)‘A',‘a',‘B',大小写不敏感。

7)字符串类型(TRING)"VHDL","MULTI_SCREEN"8)物理类型(physical)--时间类型--The physics unit time is a predefined typeTYPE time IS RANGE -1E18 TO 1E18UNITSfs; -- Femto-secondps = 1000 fs;ns = 1000 ps;us = 1000 ns;ms = 1000 us;sec = 1000ms;min = 60 sec;END UNITS--another--DISTANCE TYPETYPE distance IS RANGE 0 TO 1E16UNITSA;nm = 10A;um = 1000nm;mm = 1000um;cm = 10mm;m = 1000 mm;km = 1000m;END UNITS;9)错误类型(NOTE,WARNING,ERROR,FAILURE)10)自然数、正整数类型(NATURAL & POSITIVE)ENTITY_compare ISPORT(a,b:INTEGER RANGE 0 to 9:=0;c:out Boolean);END compare;B. 自定义数据类型1)枚举类型(ENUMERATED)TYPE PCI_BUSstate IS(Idle,busbusy,write,read,Back off); --PCI总线状态机变量TYPEstd_ulogic IS('U',‘X',‘1',‘0',‘Z',‘W',‘L',‘H',‘-‘);TYPE boolean IS(false,true);TYPE BITIS(‘0',‘1');2)整数类型(INTEGER)TYPE digit IS INTEGER RANGE -128 TO 1283)实数类型和浮点类型(REAL & FLOATING)4)数组类型(ARRAY)TYPE MYARRAY IS ARRAY(INTEGER 0 TO 9)OFstd_LOGIC5)存取类型(ACCESS)TYPE line IS ACCESS string; --Line是指向字符串的指针6)文件类型(FILES)TYPE text IS FILE OF string;TYPE input-type IS FILE OF character;7)记录类型(RECODE)--RECORD适于描写总线,通讯协议TYPE PCI_BUS IS RECORDADDR:std_LOCIG_VECTOR(31 DOWNTO 0);DATA:std_LOGIC_VECTOR(31 DOWNTO 0);END RECORD;SEGINAL DECODE1,DECODE2:PCI_BUS;PCI_DEVICE1 <= DECODE1.ADDR;PCI_DEVICE1RAM <= DECODE1.DATA;8)时间类型(TIME)9)VHDLstd_logic在VHDL中,设计人员经常使用的数据类型是枚举类型std_ulogic和它的子类型std_logic,它们都是一个九值逻辑系统。

vhdl基本语法

Testbench文件的编写

时间标度指令`timescale 用于说明程序中 的时间单位和仿真精度。

`timescale module reg test; set; 10ns/1ns

编译指令

程序示例

仿真和延迟时间值度量单位参数 时间单位精度参数

parameter d = 1.55; initial begin

编译指令

是被包含进当前源文件的其他文件名

条件编译指令包括`ifdef,`else,`endif

这些指令用来控制源代码程序是否参与编译:

`define a; ……… `Ifdef a: 程序段1 `else 程序段2 `endif

版板所有 © 广州周立功单片机发展有限公司 2007

//`define a; ……… `Ifdef a: 程序段1 `else 程序段2 `endif

版板所有 © 广州周立功单片机发展有限公司 2007

广州周立功单片机发展有限公司

版板所有 © 广州周立功单片机发展有限公司 2007

系统任务和编译预处理语句 仿真控制任务

系统任务

主要用在测试文件的initial模块内,配合时间延时控制仿真时间 $finish $stop

$finish: 退出仿真器,返回操作系统

$stop: 把EDA工具置成暂停模式,可以通过相应的命令使仿真继续;

$stop和$finish可以带参数,如$finish(0),根据参数的不同,

编译预处理

编译指令

同C语言的编译预处理指令一样,Verilog HDL也提供了大量的 编译语句。通过编译语句,EDA工具开发商使得用他们的工具解释 Verilog HDL 模型变得相当容易。

第三章VHDL语法

例:TYPE week IS (sun,mon,tue,wed,thu,fri,sat);

2、数组类型

格式: TYPE 数据类型名 IS ARRAY 范围 OF 原数据类型

例:TYPE word IS ARRAY (0 TO 7) OF STD_LOGIC;

用户定义的数据类型

3、记录Record Types

相同或不同类型的元素组成,类似C中的结构 描述总线或功能块

Type iocell is record Enable :bit; Data :bit_vector(7 downto 0);

end record; singal bus : iocell; bus.Enable <= ‘1’; bus.Data <= “00110110”;

-- a、b、c的数据类型同属4位长的位矢量

d<=e OR f OR g ; h<=(i NAND j)NAND k ;

-- 两个操作符OR相同,不需括号 -- NAND必须加括号

l<=(m XOR n)AND(o XOR p); -- 操作符不同,必须加括号

h<=i AND j AND k ;

-- 两个操作符都是AND,不必加括号

Signal data : std_logic_vector(0 to 3);

VHDL语法基础

VHDL基础语法

§1 VHDL 概述

一、什么是VHDL?

VHDL: VHSIC (Very High Speed Integrated Circuit) Hardware Description Language

二、VHDL的历史

80年代初由美国国防部在实施超高速集成电 路(VHSIC)项目时开发的。 1987年由 IEEE 协会批准为 IEEE 工业标准,

元件例化语句

实体与结构体的关系:

一个设计实体可有多个结构体,代表实体 的多种实现方式。各个结构体的地位相同。 结构体1 结构体2 设计实体 结构体3

。

。 。

结构体n

结构体的语法:

architecture 结构体名称 of 实体名称 [说明语句] begin [功能描述语句]; end [architecture] 结构体名称; is

五、VHDL语言的一些基本特点:

VHDL语言由保留关键字组成。每条VHDL语句由一个分号 (;)结束; 语句结构描述中方括号‚[ ]”内的内容为可选内容。 对于VHDL的编译器和综合器来说,程序文字的大小写是 不加区分的。本书一般使用大写。 例外:‘ ’、‚ ‛所括的字符、字符串大小写意义有 别。 程序中的注释使用双横线‚--”。在VHDL程序的任何一行 中,双横线‚--”后的文字都不参加编译和综合。 为了便于程序的阅读与调试,书写和输入程序时,使用 层次缩进格式,同一层次的对齐,低层次比较高层次缩 进两个字符。 EDA软件要求源程序文件的名字与实体名必须一致,因此 为了使同一个VHDL源程序文件能适应各个EDA开发软件上 的使用要求,建议各个源程序文件的命名均与其实体名 一致。

端口名是设计者为实体的每一个对外通道所取的 名字;端口模式是指这些通道上的数据流动方 式,如输入或输出等; 其中,端口模式: in: 输入型,此端口为只读型。 out: 输出型,只能在实体内部对其赋值。 inout:输入输出型,既可读也可赋值。 buffer: 缓冲型,与 out 相似,但可读。

VHDL语法入门

§1. VHDL语法 入门

1.3 数据对象及类型

枚举: type Bit is (’0’,’1’); type Boolean is (false, true); 物理: type Time is range –2147483647 to +2147483647 units fs; ps=1000 fs; ns=1000 ps; us=1000 ns; ms=1000 us; sec=1000 ms; min=60 sec; hr= 60 min; end units;

§1. VHDL语法 入门

1.1 VHDL程序构件

配置说明

将具体的构造体分配给实体说明 示例

configuration conf1 of xor_gate is for data_flow end for; end conf1;

configuration conf2 of xor_gate is for structure end for; end conf1;

1.3 数据对象及类型

数据对象 数据类型

§1. VHDL语法 入门

1.3 数据对象及类型

数据对象

VHDL语言中用于进行赋值等操作的客体 信号(Signal)

信号赋值: sig <= a + b; 信号说明:

端口信号 port (端口信号名:端口模式 数据类型名 [:=初始 值];…); 内部信号 signal 信号名:数据类型名 [:=初始值]; 例:signal sel: bit := ’0’;

VHDL语言的基本语法

--位矢量赋值,a的数据类型是位矢量 位矢量赋值, 的数据类型是位矢量 位矢量赋值 --段赋值 段赋值 a(3 TO 6):=(‘1’,’1’,’0’,’1’); a(0 TO 5):=b(2 TO 7); a(7):=’0’; --位赋值 位赋值

3、信号(Signal) 信号(Signal)

信号是描述硬件系统的基本数据对象,它类似于连接线。 信号是描述硬件系统的基本数据对象,它类似于连接线。它 除了没有数据流动方向说明以外,其他性质与实体的端口( 除了没有数据流动方向说明以外,其他性质与实体的端口(Port) ) 概念一致。 概念一致。 信号说明格式为: 信号说明格式为: SIGNAL 信号名:数据类型 约束条件:= 初始值; 信号名: 约束条件: 初始值; 信号初始值的设置不是必需的,而且初始值仅在VHDL的行 信号初始值的设置不是必需的,而且初始值仅在VHDL的行 为仿真中有效。 为仿真中有效。 例:SIGNAL temp: STD_LOGIC:=‘0’; ; SIGNAL flaga, flagb: BIT; SIGNAL date: STD_LOGIC_VECTOR (15 DOWNTO 0);

3、字符串型文字 字符是用单引号引起来的ASCII字符,可 字符是用单引号引起来的 字符, 单引号引起来的 字符 以是数值,也可以是符号或字母, 以是数值,也可以是符号或字母,如:‘R’, , ‘A’,‘*’,‘Z’。 , , 。 而字符串则是一维的字符数组,须放在双 而字符串则是一维的字符数组,须放在双 引号中 中有两种类型的字符串: 引号中。VHDL中有两种类型的字符串:文字 中有两种类型的字符串 字符串和数位字符串。 字符串和数位字符串。

常量的使用范围取决于它被定义的位置: 常量的使用范围取决于它被定义的位置

vhdl基本语法(简略共34页)

vhdl基本语法(简略共34页)vhdl基本语法(简略共34页)VHDL硬件描述语言1.1 VHDL概述1.1.1 VHDL的特点VHDL语言作为一种标准的硬件描述语言,具有结构严谨、描述能力强的特点,由于VHDL语言来源于C、Fortran等计算机高级语言,在VHDL语言中保留了部分高级语言的原语句,如if语句、子程序和函数等,便于阅读和应用。

具体特点如下:1. 支持从系统级到门级电路的描述,既支持自底向上(bottom-up)的设计也支持从顶向下(top-down)的设计,同时也支持结构、行为和数据流三种形式的混合描述。

2. VHDL的设计单元的基本组成部分是实体(entity)和结构体(architecture),实体包含设计系统单元的输入和输出端口信息,结构体描述设计单元的组成和行为,便于各模块之间数据传送。

利用单元(componet)、块(block)、过程(procure)和函数(function)等语句,用结构化层次化的描述方法,使复杂电路的设计更加简便。

采用包的概念,便于标准设计文档资料的保存和广泛使用。

3. VHDL语言有常数、信号和变量三种数据对象,每一个数据对象都要指定数据类型,VHDL的数据类型丰富,有数值数据类型和逻辑数据类型,有位型和位向量型。

既支持预定义的数据类型,又支持自定义的数据类型,其定义的数据类型具有明确的物理意义,VHDL是强类型语言。

4. 数字系统有组合电路和时序电路,时序电路又分为同步和异步,电路的动作行为有并行和串行动作,VHDL语言常用语句分为并行语句和顺序语句,完全能够描述复杂的电路结构和行为状态。

1.1.2 VHDL语言的基本结构VHDL语言是数字电路的硬件描述语言,在语句结构上吸取了Fortran和C等计算机高级语言的语句,如IF语句、循环语句、函数和子程序等,只要具备高级语言的编程技能和数字逻辑电路的设计基础,就可以在较短的时间内学会VHDL语言。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

整理课件

6

VHDL在电子系统设计中的应用

•电子系统的设计模块

整理课件

7

VHDL在电子系统设计中的应用

• 电子系统设计的描述等级 1、行为级 2、RTL级(Register transfer level) 3、逻辑门级 4、版图级 • 用VHDL可以描述以上四个等级

格式: Arcthitecture 构造体名 of 实体名 is

[定义语句] 内部信号、常数、元件、数据类型、函数等的定义

begin [并行处理语句和block、process、function、procedure] end 构造体名;

整理课件

18

VHDL结构要点

• 例子(HalfAdd)

整理课件

VHDL培训教程

欢迎参加VHDL培训

整理课件

1

VHDL培训教程

第一讲、VHDL简介及其结构 第二讲、VHDL中的对象、操作符、数据类型 第三讲、VHDL中的控制语句及模块 第四讲、状态机的设计

整理课件

2

第一讲、VHDL简介及其结构

• 通过本课的学习您可以了解以下几点 1、VHDL 的基本概念 2、VHDL的基本结构 3、VHDL的设计初步

signal databuffer: STD_LOGIC_VECTOR (3 downto 0);

begin

dataout<=databuffer;

process(clock,reset)

begin

if (reset='1') then databuffer<="0000";

elsif (clock'event and clock='1') then

整理课件

8

VHDL在电子系统设计中的应用

•系统设计的描述等级-制版级

整理课件

9

VHDL在电子系统设计中的应用

•系统设计的描述等级-逻辑门级

整理课件

10

VHDL在电子系统设计中的应用

•系统设计的描述等级-RTL级

整理课件

11

VHDL在电子系统设计中的应用

•系统设计的描述等级-行为级

整理课件

12

整理课件

3

什么是VHDL

• VHDLVHSIC Hardware Decription Language

其中VHSICVery High Speed Integrated Circuit

电子设计自动化的关键技术之一是要求用形式化 方法来描述硬件系统。VHDL适应了这种要求。

整理课件

4

VHDL和Verilog HDL

19

VHDL结构要点

• 例子 (FullAdd) (学习如何调用现有模块)

整理课件

20

VHDL结构要点

• 实例(FullAdd)-entity

整理课件

21

VHDL结构要点

• 实例(FullAdd)-architecture

整理课件

22

ห้องสมุดไป่ตู้ 整理课件

23

VHDL中的设计单元

除了entity(实体)和architecture(构造体)外还有 另外三个可以独立进行编译的设计单元

其中端口说明格式为: PORT(端口名1,端口名N:方向:类型) 其中方向有: IN , O整U理T课,件INOUT, BUFFER, LINKAGE15

VHDL结构要点

• 注意

In 信号只能被引用,不能被赋值 out 信号只能被赋值,不能被引用 buffer 信号可以被引用,也可以被赋值

• 简单地说

In 不可以出现在<= 或 : = 的左边

out不可以出现在<= 或 : = 的右边

buffer可以出现整理在课件<= 或 : = 的两边

16

VHDL结构要点

• 例子 (HalfAdd)

其内部结构将整由理课A件rchitecture来描述

17

VHDL结构要点

2、Arcthitecture(构造体)

Library 库的概念

• 用户自己的库

如何使用VHDL描述硬件实体

Entity(实体)

Architecture 1(构造体)

Architecture N

process(进程结构) subprograms(子程序) block(块结构)

procedure(过程)

整理课件

function(函数)

13

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity count is

port ( clock,reset: in STD_LOGIC;

dataout: out STD_LOGIC_VECTOR (3 downto 0) );

end count;

architecture behaviorl of count is

• Verilog HDL:

另一种硬件描述语言,由Verilog 公司开 发,1995年成为IEEE标准。

优点:简单、易学易用

缺点:功能不如VHDL强大,仿真工具少 • VHDL :

1987年成为IEEE标准

优点:功能强大、通用性强。

缺点:难学整理课件

5

VHDL的发展历史

• 起源于八十年代,由美国国防部开发 • 两个标准:

if databuffer="1000" then

databuffer<="0000"; else databuffer<=databuffer+'1';

end if;

end if;

end process;

end behavioral; 整理课件

14

VHDL结构要点

1、ENTITY(实体)

格式: Entity 实体名 IS [类属参数说明] [端口说明] End Entity;

• VHDL中的设计单元(可以独立编译)

整理课件

25

Library 库的概念

库: 数据的集合。内含各类包定义、实体、构造体等

• STD库 --VHDL的标准库 • IEEE库 -- VHDL的标准库的扩展 • 面向ASIC的库 --不同的工艺 • 不同公司自定义的库 • 普通用户自己的库

整理课件

26

• Package(包集合)属于库结构的一个层次,存放信 号定义、常数定义、数据类型、元件语句、函数定 义和过程定义。

• Package Body 具有独立对端口(port)的package

• configuration(配置)描述层与层之间的连接关系以 及实体与构造体之间关系。

整理课件

24

VHDL中的设计单元