数字移相信号发生器设计说明书

第4章-数字式移相信号发生器的设计

第4章

2. DDS DDS技术将输出波形的一个完整周期的幅度值都顺 序地存放在波形存储器中, 通过控制相位增量产生频 率、相位可控制的波形。DDS电路一般包括基准时钟、 相位增量寄存器、相位累加器、波形存储器、D/A转换 器和低通滤波器(LPF)等模块, 如图4.4所示。

第4章

相位 增量

相位

地址

K

m

ax

128 359 45

1021.55

则相位控制字K的位数取10 bit就能满足设计任务关于

移相的要求(分辨率为1°, 移相范围是0~359°)。

若“相位加法器”采用24 bit加法器实现, 则上述10 bit的相位控制字应扩展成24 bit, 具体扩展方法是在上述 10 bit相位控制字后面(右边)添加14个逻辑0就可以了。

基于DDS技术的数字式移相信号发生器的主 要模块框图如图4.5所示。

第4章

频率 控制 字 寄 存 器

相位 控制 字 寄 存 器

相位 累加 器

相位 加法 器

寄 存

Address1

器

寄 存

Address2

器

图4.5 基于DDS技术的数字式移相信号发生器主要模块框图

第4章

3. 1)确定系统时钟频率fcp 不妨设输出信号最高频率为fmax 、最高频率 fmax下的最少采样点数为Smin , 则有

第4章

4.3 系统硬件设计

4.3.1 DDS 1. DDS 1971年, 美国学者J.Tierncy、C.M.Rader和B.Gold提出了以全数

字技术从相位概念出发直接合成所需波形的一种新的频率合成原理。 随着电子技术的发展和水平的提高, 一种新的频率合成技术——直接数 字频率合成(DDS, Direct Digital Synthesis)技术得到了飞速发展。 DDS技术是一种把一系列数字形式的信号通过D/A转换而成模拟形式的 信号合成技术, 目前使用最广泛的一种DDS方式是利用高速存储器作查 找表, 然后通过高速D/A转换输出已经用数字形式存入存储器的正弦波。

基于FPGA的高精度数字式移相正弦波信号发生器设计

摘要: 文章介绍了基于FPGA和数字频率合成技术,利用VHDL 编制程序并下载至Xilinx公司的SpartanⅡ系列XC2S100E-6PQ208 FPAG芯片上,加以简单的外围电路,构成了高精度数字式移相正弦波信号发生器。

该装置能够产生频率、相位、幅度均可数字式预置并可调节的两路正弦波信号,相位差范围为0~359°,步进为1°。

关键词:数字移相;FPGA;VHDL;直接数字频率合成1.引言在一些试验、研究中,有时需要存在相位差的两同频信号。

通常采用移相网络来实现,如阻容移相,变压器移相等。

采用这些方法有许多不足之处,比如:输出波形受输入波形的影响,移相操作不方便,移相角度随信号频率和所接负载等因素的影响等。

若采用直接数字频率合成及数字移相技术,能得到频率及相位差高度稳定精确的信号且实现方便。

2.波形及移相波形发生器的系统组成原理如图1所示为波形及移相波形发生器的系统组成方框图。

500)this.style.width=500;" border=0>图1 波形及移相波形发生器的系统组成原理框图标准时钟(由晶振电路产生)加于进制可编程的n进制计数器,其溢出脉冲加于可预置初值的地址计数器,生成波形存储器所需的地址信号,地址信号的产生频率正比于时钟频率,且周而复始地变化,从而使波形数据存储器输出周期的正弦序列,D/A转换器则输出连续的模拟正弦电压(或电流)波形,如图2所示。

500)this.style.width=500;" border=0>为移相方便,设一周期的正弦波共采样360个点,即波形数据存储器共存储360个正弦波形的数据。

由于移相波形的地址计数器的第一次运行初值为m,故两正弦波存在相位差为m°。

相邻采样点有n 个标准时钟脉冲间隔,即500)this.style.width=500;" border=0> 。

图1中波形数据存储器的全部数据被读出一次的频率为:500)this.style.width=500;" border=0> 。

低频数字式移相信号发生器的设计

!K#

软件工具

为了便于携带, 上位机一般采用笔记本电脑。检测仪提供

多种 软 件 工 具 方 便 操 作 者 使 用, 如下装程序和参数设置给 测量单点图像、 连续检测管道内表面图像等。这些工具 "$:、 都是在 BLMN=OI42, 具有良好的界面。呈现给 4) 平台上运行, 用户的可以是被测目标点相对于检测仪的角度和距离、 管道内 表面图像, 也可以是内表面实测图像与原始图像的比较以确定 管道变形程度等。

5!) 768B 5%&, <$5 5%/ 565 5%& <$5 5%/ 565 5%& <$5 5%/ 565 5%& <$5 5%/ 565 5%& 5!A 3"" 5%/, 5C7: <==> 即可得到平滑的波形。即用放大器 " - 3 输出后经放大器, 实现了平滑滤波的作用。经实验发现其效果很好。 按键操作: 键盘由设置键、 确定键、 上下键和左右键 0 个键 组成。可以实现频率和相位的参数设置。

!""# 年 第(期

仪 表 技 术 与 传 感 器 QD<HGM-.DH @.PODEWM. 0DR 9.D<JG

!""# ^J2(

低频数字式移相信号发生器的设计

任旭虎& , 梁 锴& , 宋玉章! (& ’ 石油大学, 山东 东营 !%(")&; 山东 东营 ! ’ 石油大学科技园, !%(")&)

(上接第 (% 页) 流电机的驱动。以太通信模块完成 "$: 和上位 机间的通信, 除了下装程序和数据外, 主要任务是将 "$: 处理 好的管道内表面的图像数据传给上位机。

数字信号发生器F120使用说明

F05/F10/F20/F40/F80 /F120数字合成函数/任意波信号发生器/计数器南京盛普仪器科技有限公司NANJING SAMPLE INSTRUMENT TECHNOLOGY CO.,LTD.使用说明书目录第一章概述 (1)第二章主要特征 (1)第三章技术参数 (2)一、函数信号发生器 (2)二、计数器 (4)三、其它 (5)第四章面板说明 (6)一、显示说明 (6)二、前面板说明 (7)三、后面板说明 (11)第五章使用说明 (12)一、测量、试验的准备工作 (12)二、函数信号输出使用说明 (12)三、计数使用说明 (31)第六章遥控操作使用说明 (32)第七章注意事项与检修 (47)第八章仪器整套设备及附件 (49)本仪器是一台精密的测试仪器,具有输出函数信号、调频、调幅、FSK 、PSK 、猝发、频率扫描等信号的功能。

此外,本仪器还具有测频和计数的功能。

本仪器是电子工程师、电子实验室、生产线及教学、科研的理想测试设备。

1、采用直接数字合成技术(DDS )。

2、主波形输出频率为100μHz ~ 120MHz (F120)。

3、小信号输出幅度可达0.1mV 。

4、脉冲波占空比分辨率高达千分之一。

5、数字调频分辨率高、准确。

6、猝发模式具有相位连续调节功能。

7、频率扫描输出可任意设臵起点、终点频率。

8、相位调节分辨率达0.1度。

9、调幅调制度1% ~ 120% 可任意设臵。

10、输出波形达30余种。

11、具有频率测量和计数的功能。

12、机箱造型美观大方,按键操作舒适灵活。

概述 12主要特征一、函数发生器1、波形特性主波形:正弦波,方波, TTL 波(频率大于40MHz 仅有正弦波) 波形幅度分辨率:12 bits采样速率:200Msa/s (F120 为300 Msa/s) 正弦波谐波失真:-50dBc (频率≤ 5MHz ) -45dBc (频率≤ 10MHz ) -40dBc (频率≤ 20MHz )-35dBc (频率> 20MHz )正弦波失真度: ≤0.1%(f :20Hz ~ 100kHz ) 方波升降时间: ≤25ns (F05型、F10型)≤15ns (F20型、F40型、F80型、F120型)注:正弦波谐波失真、正弦波失真度、方波升降时间测试条件:输出幅度2Vp-p (高阻),环境温度25℃〒5℃储存波形:正弦波,方波,脉冲波,三角波,锯齿波,阶梯波等27种波形 波形长度:4096点波形幅度分辨率:10 bits脉冲波占空系数:0.1% ~ 99.9%(频率≤10kHz ),1% ~ 99%(10kHz ~ 100kHz )脉冲波升降时间: ≤100ns直流输出误差:≤〒5%+10mV (输出电压值范围10mV~10V )2、频率特性频率范围:主波形:1μHz ~ 5MHz (F05型) 1μHz ~ 10MHz (F10型) 1μHz ~ 20MHz (F20型) 1μHz ~ 40MHz(F40型)3技术指标1μHz ~ 80MHz (F80型)1μHz ~ 120MHz (F120型)储存波形:1μHz ~ 100kHz分辨率:1μHz频率误差:≤〒5×10-6 频率稳定度:优于〒1×10-63、幅度特性幅度范围(频率≤40MHz):2mV ~ 20Vp-p(高阻),1mV ~ 10Vp-p(50Ω)幅度范围(频率>40MHz):2mV ~ 4Vp-p(高阻),1mV ~ 2Vp-p(50Ω)F120:幅度范围(频率≤40MHz):0.2mV ~ 20Vp-p(高阻),0.1mV ~ 10Vp-p(50Ω)幅度范围(频率>40MHz):-76dBm ~ +13.5 dBm(50Ω)或100цV ~ 3Vp-p(50Ω)最高分辨率:2μVp-p (高阻),1μVp-p(50Ω)幅度误差:≤〒1%+0.2mV (频率1KHz正弦波)幅度稳定度:〒0.5 % /3小时平坦度:幅度≤2Vp-p:〒3%(频率≤5MHz), 〒10%(频率≤40MHz)幅度>2Vp-p:〒5%(频率≤5MHz), 〒10%(频率≤20MHz)〒20%(频率>20MHz)F120:〒1dBm(频率>40MHz)输出阻抗:50Ω幅度单位:Vp-p,mVp-p,Vrms,mVrms,dBm4、偏移特性直流偏移(高阻,频率≤40MHz):〒(10V-Vpk ac),(偏移绝对值≤2〓幅度峰峰值)直流偏移(高阻,频率>40MHz):〒(2V-Vpk ac),(偏移绝对值≤2〓幅度峰峰值)最高分辨率:2μV(高阻),1μV(50Ω)偏移误差:≤〒(1% +10mV)信号幅度≤2Vp-p (高阻)≤〒(1% +20mV)信号幅度>2Vp-p (高阻)5、调幅特性载波信号:波形为正弦波或方波,频率范围同主波形调制方式:内或外调制信号:内部5种波形(正弦、方波、三角、升锯齿、降锯齿)或外输入信号调制信号频率:100μHz ~ 20kHz失真度:≤2%调制深度:1% ~ 120%1%~ 80% (频率>40MHz,载波幅度>2Vp-p(高阻)时) 相对调制误差:≤〒(5% +0.2)(100μHz ~ 10KHz);≤〒(10% +0.5)(10KHz ~ 20KHz)外输入信号幅度:3Vp-p(-1.5V~ +1.5V)6、调频特性载波信号:波形为正弦波或方波,频率范围同主波形调制方式:内或外调制信号:内部5种波形(正弦、方波、三角、升锯齿、降锯齿)调制信号频率:100μHz ~ 10kHz频偏:内调频最大频偏为载波频率的50%;外调频最大频偏为载波频率的10%,输入信号电压3Vp-p(-1.5V~+1.5V)外调频:载波频率精确度≤ 10-2 ,频偏误差≤〒20%FSK:频率1和频率2任意设定控制方式:内或外(外控:TTL电平,低电平F1;高电平F2)交替速率:0.1ms ~ 800s7、调相特性基本信号:波形为正弦波或方波,频率范围同主波形PSK:相位1(P1)和相位2(P2)范围:0.1 ~ 360.0°分辨率:0.1°交替时间间隔:0.1ms ~ 800s控制方式:内或外(外控TTL电平,低电平P2,高电平P1)8、猝发基本信号:波形为正弦波或方波,频率范围同主波形猝发计数:1 ~ 10000个周期猝发信号交替时间间隔:0.1ms ~ 800s控制方式:内(自动)/外(单次手动按键触发、外输入TTL脉冲上升沿触发)9、频率扫描特性信号波形:正弦波和方波扫描范围:扫描起始点频率(100цHz ≤ F ≤ 40MHz)。

ADS数字信号发生器说明书

Photo 39395Brief descriptionADS is provided with two independently programmable synthesis channels.Thanks to its simple channel synchroniza-tion facility and precise phase setting, the ADS is ideal for generating complex sig-nals.ARB generators are essential tools for •digital modulation,•communications,•navigation,•automatic test equipment,•component testing,•audio and acoustics measurements,•material testing,•ultrasound measurements,•filter design,•video applications, control engineer-ing,•sensors and•automotive engineering.Complex modulation signalsThe ADS is a high-precision signal source for driving I/Q modulators to produce dig-ital modulation; it is particularly suitable for driving the I/Q modulator of Signal Generator SMIQ (page 133).Main features•Convenient editor functions for creating user-programmable waveforms, ARB sequences and ARB sweeps •12-bit amplitude resolution•64-Kpoints waveform memory per channel•Sine synthesis with high spectral purity (0.1 Hz to 5 MHz)•Generation of triangular waves with high linearity (0.1 Hz to 100 kHz)•User-programmable frequency sweep •ARB sequence mode for generating sig-nals with extremely long periods •Nonvolatile memory for storing 20 instrument setups as well as up to 99 ARB signals, ARB sequences and ARB sweeps•Memory card for waveform librariesSpectral purityThe low distortion (typ. −70 dB) and a fre-quency response of typ. 0.1 dB allow pre-cise audio measurements. The high spec-tral purity close to the carrier throughout the entire sinewave frequency range ena-bles testing of fast, high-resolution A/D converters.Trigger functionsA variety of trigger functions (SINGLE, GATE, RESET, HOLD and HOLD/RESET in ARB mode, SINGLE and STEP in sequence mode) is provided for control of signal generation. In the sine mode, the modula-tion modes FSK (frequency shift keying), PSK (phase shift keying) and PM (pulse modulation) can be selected in addition to the trigger functions HOLD and HOLD/RESET. Triggering can be carried out withDual Arbitrary Waveform Generator ADSSignal source of virtually unlim-ited flexibility, see also Applica-tion Software AWD-K1, IQSIM-K, DAB-K1Overview of options and softwareSee catalog "Test and Measurement Products"Designation, functionsTypeClock Generator: resolution improved by a factor of 4000 to further enhance the accuracy of setting the period of ARB signals ADS-B1Software: for generating complex waveformsAWD-K1Software: for generating I/Q signals for any digital modulation modes IQSIM-K Software: for generating COFDM signalsDAB-K1the internal trigger generator, through an external source or manually.OperationWaveform editorThis is a highly convenient tool for synthe-sis and modification of any waveform or application-specific sweep. The complete waveform library stored by the user in theinternal memory can be accessed and isavailable for editing.Sequence modeIn this mode, ARB signals can be joinedup to a continuous programmedsequence. By assigning a repetition rateto any element in the sequence, it is pos-sible to create sequences that use a frac-tion of the memory capacity required forconventional ARB synthesis. Each ele-ment in the sequence can be assigned anindividual read clock frequency; in thisway, expanded ARB signals can beincluded in the sequence. The SEQ editorwhich is similar to the ARB editor is usedfor programming and modifying ARBsequences.Specifications in briefSpecifications apply to both synthesis channels of ADS Signal outputOutput voltage (AC), EMF0 to 20 V pp, Imax = ±100 mA,0 to10 V into 50 ΩDC offset setting range−5 to +5 V into 50 ΩSine0.1 Hz to 5 MHzTriangle0.1 Hz to 100 kHzPhase setting range CH1/CH2 −180° to +180°Trigger modesFrequency shift keying (FSK)phase-continuousPhase shift keying (PSK)setting range −180 ° to +180 °Pulse modulation (PM)Reset (RESET)triggered phase reset to 0°Hold triggered stopHold/Reset (HD/RS)triggered stop and resetSweep modeDigital, user-programmable frequency and phase sweeps,triggered internally, externally or manuallyUser-programmable waveformsLength2 to 65536 points, composite ARBsequencesAmplitude resolution12 bitsClock source (CLK)internal400Hz to 25 MHzwith ADS-B1200Hz to 33 MHzexternal DC to 33 MHzFilters(DC) 400 Hz to 33.33 MHz3rd-order Bessel filters, modified10 kHz, 100 kHz, 1 MHz, 2.5 MHz7th-order Chebychev filters, modified500 kHz, 5 MHzARB sequencesSequence length 2 to 8192 ARB curvesRepetition rate for single curves 1 to 65535, programmable Expansion factor(1 to 65535) x clock period, programma-ble for each ARB curveOperating modesContinuous mode CONTTrigger modes SINGLE, STEPTrigger mode trigger source internal, external,manual Internal triggering HCT/TTL-compatible, 50 ΩTrigger period 1 µs to 2000 sOn/off ratio adjustable, 1:6500 to 6500:1 Resolution, ON/OFF time min. 500 nsExternal triggeringInput impedance50 Ω/600 Ω, selectableTrigger threshold0.2 V/2.0 V, selectableTrigger edge up/down selectableTrigger state active LOW/HIGH selectable Frequency DC to 25 MHzMemory320 Kbyte, nonvolatileMemory card128 KbyteClock generator (option ADS-B1)Read frequency200 points/s to 33.33 Mpoints/s Resolution0.01%, min. 10 psReference frequencyInput/output frequency 5 or 10 MHz, selectableRemote control IEC bus (IEEE 488.2), in line with SCPI General dataPower supply100/230 V −10/+15%,120/220 V −15/+10%,47 to 420 Hz, 150 VADimensions (W x H x D)435 mm x192 mm x350 mmWeight14 kg for fully equipped unit Ordering informationDual Arbitrary Waveform Generator ADS1012.4002.02 OptionClock Generator ADS-B11013.5748.02 ExtrasMemory Card CMS-Z20841.1509.02 Software for ARB Signals AWD-K11026.4500.03 for I/Q Signals IQSIM-K1013.1642.02for COFDM Signals DAB-K11013.4649.02 Service Kit ADS-Z21013.1494.02。

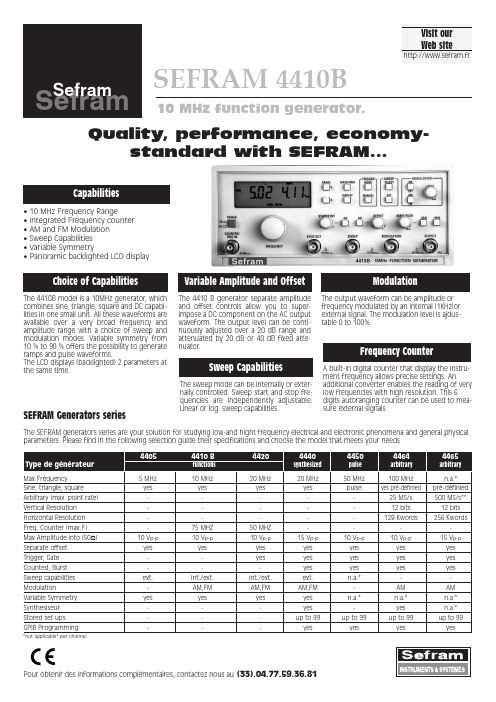

SEFRAM 4410B 数字信号发生器使用说明书

Pour obtenir des informations complémentaires, contactez nous au(33).04.77.59.36.81Visit our Web sitehttp://www.sefram.frSEFRAM 4410BQuality, performance, economy-standard with SEFRAM...Sefram• 10 MHz Frequency Range • Integrated Frequency counter • AM and FM Modulation • Sweep Capabilities • Variable Symmetry• Panoramic backlighted LCD displayThe 4410B model is a 10MHz generator, which combines sine, triangle, square and DC capabi-lities in one small unit. All these waveforms are available over a very broad frequency and amplitude range with a choice of sweep and modulation modes. Variable symmetry from 10 % to 90 % offers the possibility to generate ramps and pulse waveforms.The LCD displays (backlighted) 2 parameters at the same time.The 4410 B generator separate amplitude and offset controls allow you to super-impose a DC component on the AC output waveform. The output level can be conti-nuously adjusted over a 20 dB range and attenuated by 20 dB or 40 dB fixed atte-nuator.The sweep mode can be internally or exter-nally controlled. Sweep start and stop fre-quencies are independently adjustable.Linear or log. sweep capabilities.SEFRAM Generators seriesThe SEFRAM generators series are your solution for studying low-and hight frequency electrical and electronic phenomena and general physical parameters. Please find in the following selection guide their specifications and choose the model that meets your needsModulationThe output waveform can be amplitude or frequency modulated by an internal (1KHz)or external signal. The modulation level is ajdus-table 0 to 100%.Frequency CounterA built-in digital counter that display the instru-ment frequency allows precise settings. Anadditional converter enables the reading of very low frequencies with high resolution. This 6digits autoranging counter can be used to mea-sure external signals.10 MHz function generator.44054410 B 44204440445044644465Type de générateurfunctionssynthesizedpulsearbitraryarbitraryMax Fréquency .5 MHz 10 MHz 20 MHz 20 MHz 50 MHz 100 MHz n.a.*Sine, triangle, square yes yesyesyespulseyes pré-définied pré-définied Arbitrary (max. point rate)-----25 MS/s 500 MS/s**Vertical Resolution -----12 bits 12 bits Horizontal Resolution -----128 Kwords256 KwordsFreq. Counter (max.F .)-75 MHZ 50 MHZ ----Max Amplitude into (50Ω)10 V p-p 10 V p-p 10 V p-p 15 V p-p 10 V p-p 10 V p-p 15 V p-p Separate offset yes yes yes yes yes yes yes Trigger, Gate --yes yes yes yes yes Counted, Burst ---yes yes yes yes Sweep capabilities ext.int./ext.int./ext.ext.n.a.*--Modulation -AM,FM AM,FM AM,FM -AM AM Variable Symmetry yes yes yes yes n.a.*n.a.*n.a.*Synthesiseur ---yes -yes n.a.*Stored set ups ---up to 99up to 99up to 99up to 99GPIB Programming---yesyesyesyes*not applicable* per channelW AVEFORMSSine, square, triangle and DC.O PERATINGMODESSymmetry : 10% to 90%, up to 1 MHzSweep : The output waveform can be linear internally swept over 100 : 1 range. The sweep start and stop freq. can be independently adjusted and the sweep rate can be set from 20 ms to 10s.Modulation : The output can be AM and FM modulated by an internal or external signal. The internal modulation is a 1 KHz sinewave.F REQUENCYCHARACTERISTICSRange : 0.01 Hz to 10 MHz in 8 overlapping ranges. Each range capable of over 100 : 1 frequency change.Control :The range is selected by up and down keys; frequency within the range is set with a multiturn control.Display :Up to 4 digits (1100 counts) with backlight LCD, range units (MHz, KHz, Hz, and mHz) and decimal point.Display accuracy is 0.01 % of reading ±1 LSB from 100 Hz to 10 MHz and 3%from 0,01 Hz to 99 Hz .O UTPUTCHARACTERISTICSAmplitude Range :Up to 10 V p-p into 50Ω (20 v p-p into open circuit).Amplitude Controle : >20 dB continously variable.Amplitude Attenuator : 2 independant attenuators with a±2 %accuracyAmplitude Flatness : ±0,5 dB to 1 MHz±2 dB to 10 MHzOffset range : Variable up to ±10 V. Absolute peak amplitude plus offset limited to 10 V (±5 V into 50 Ω).Output impedance : 50ΩOutput protection : The generator main output is non-destructively pro-tected against short circuit to ground or to any voltage practically available in electronic laboratories.W AVEFORMCHARASTERISTICSine Distorsion : < 1 %THD, 10 Hz to 100 KHz.< 25 dBc above 100 KHzTriangle Linearity : > 98 % to 100 KHz.Square Transition Times : < 22 ns 10 % à 90 % at full output amplitude terminated into 50 Ω.Square Abberations : < 5 % of p-p amplitude ±50 mVI NPUTSAND OUTPUTS• Sync, Out : TTL levels square wave with a 50 Ω impedance . Can drive a minimum of 20 TTL loads.• Sweep In-Out : 0-5 V input for a up to 100 : 1 frequency change. In the sweep mode, the sweep voltage is available at this output.Output impedance : 600 ΩInput impedence : 10 Ω• Mode In-Out : The internal 1 KHz sine-wave is available for external synchronisation. The signal amplitude is 2 Vp-p and 600 Ω output impe-dance.In EXT modulation mode, a signal applied to this input will modulate the output signal. A 2 Vp-p signal is required for a 100 % AM modulation. The input impedance is 10 Ω• Trigger in : TTL compatible external signal width is 50 ns minimum with MAX. rate of 10 MHzC OUNTERCHARACTERISTICRange : 5 Hz to 75 MHzResolution : Autoranging, up to 6 digits. Accuracy : ±1digit ±20 ppm.Sensitivity : 30 mV RMS .G ENERALSafety : IEC 1010, Cat. IPower Requirements : 93-128 VAC, 185-256 VAC sweetch selectable,48-66 Hz, 25 VA Max.Dimensions : 89 x 220 x 200 mm Weight : 2 kgOperating temperature : 0°C to 50°C.Storage temperature : -20°C to 60°C.Warranty : 3 years.S UPPLIEDWITHAll generators are supplied with a power cord and user’s manual.O PTIONALACCESSORIES• BNC/BNC cable (1m, black, IEC 1010) - SO 410• BNC m/2 x BNC f. adaptator- SO 401• Isolated BNC m/2 x ban. f adaptator - SO 402• 50 Ω, 2 w load - SO 405To discover the complete range of accessories, contactus and ask for the ELDITEST catalogSeframSEFRAM 4410B10 MHz function generator.32, rue Edouard Martel • 42100 - St Etienne Lignes commerciales directes :+33 (0).4.77.59.36.80 ou +33 (0).4.77.59.36.81Fax. +33 (0).4.77.57.23.23Web:www.sefram.fr•e-mail:***************Specifications subject to change without notice - FT 4410B A 00For assistance and ordering。

数字式移相信号发生器-课程设计报告(个人版)

《数字式移相信号发生器》课程设计报告系别:专业班级:学生姓名:学生学号:指导教师:(课程设计时间:2011年1月4日——2011年1月22日)前言EDA技术是一门涉及多学科的综合性技术,是以大规模逻辑器件为设计载体,以硬件描述语言为系统逻辑表达的主要方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具通过有关的开发软件,自动完成用软件方式设计的电子系统到硬件系统的逻辑编译、化简、分割、综合、优化、布局布线及仿真,直至对特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专业集成芯片的一门新技术。

本次课程设计中我们基于EDA技术,运用VHDL编制程序,完成数字式移相频率计的程序编辑,最终下载到ACEX1K系列EPF1K50LC208-3芯片上,加以简单的外围电路,构成数字移相信号发生器。

该装置能测出频率在20HZ-2000KHZ 之间的正弦波信号频率,并给出指定相位差的两路同频信号。

目录1.课程设计目的 (1)2.题目描述及要求 (2)3.课程设计报告内容 (2)3.1系统框图 (2)3.2系统各组成部分介绍 (3)3.2.1数字移相及信号产生模块 (3)3.2.2数字频率计模块 (7)3.2.3显示模块 (13)3.3系统完整介绍 (15)3.4 引脚分配 (16)4.总结 (17)参考文献 (19)1. 课程设计目的(1)进一步加深对EDA 技术的基本知识的理解,提高VHDL 编程仿真程序的运用能力。

(2)培养根据课题需要查找参考书籍和文献资料,并学习运用的的能力,从而更好的培养了自学能力和独立思考问题和解决问题的能力。

(3)培养硬件设计、软件设计及系统软、硬件调试的基本思路、方法和技巧,并能熟练使用当前较流行的一些有关电路设计与分析方面的软件和硬件。

(4)培养严肃认真的工作作风和科学态度,逐步建立正确的生产观念、工程观念和全局观点。

2. 题目描述及要求设计题目:数字式移相信号发生器设计要求:(1)被测正弦信号频率范围:20HZ —2000KHZ ;(2)正弦信号频率皆采用BCD 码计数方式;具有正弦信号频率测量及数字显示功能;(3)能够输出给定相位差的两路同频,相位测量绝对误差≤2º。

基于FPGA数字移相信号发生器设计

基于FPGA 数字移相信号发生器设计付莉,潘明(桂林电子科技大学 计算机与控制学院 广西 桂林 541004)摘 要:根据直接数字合成器的基本原理,给出了基于FPGA 的直接数字合成器的设计与实现,利用FPGA 有效地扩展了输出波形的频率范围,实现了数字移相信号发生器。

该信号发生器主要采用了直接数字合成器、直接存储器存取、数字移相和数字调幅等技术,对传统的模拟移相不能实现任意波形的移相的缺点方便进行了改进和优化。

关键词:直接数字合成器;FPGA;频率范围;移相信号发生器中图分类号:TP332.3 文献标识码:BDesign of Digital Phase Shift Signal Generator Based on FPGAFu Li ,Pan Ming(School of Computer Science and Control, Guilin University of Electronic Technology, Guilin 541004 , China )Abstract: According to the basic principles of Direct Digital Synthesizer, this article put forward Design and Implementation of the Direct Digital Synthesizer based on FPGA, and extend the output waveform of the frequency range with FPGA effectively. The signal generator used mainly technologies of direct digital synthesizer, a direct memory access, digital phase-shifting and digital AM. It improve and optimise the traditional analog phase-shifting arbitrary waveforms which can not be realized the shortcomings of the phase-shifting facilitate.Key word :Direct Digital Synthesizer; Frequency range; Digital Phase Shift Signal Generator0 引言DDS 即Direct Digital Synthesizer ,中文名称是直接数字合成器,是一种新型的频率合成技术,具有较高的频率分辨率,可以实现快速的频率切换,并且在改变时能够保持相位连续,很容易实现频率、相位和幅度的数控调制。

数字移相信号发生器设计

分类号编号XXXXXX本科毕业论文(设计)基于DDS的数字移相信号发生器设计Design of digital phase shifted signal generator based on DDSXXX指导教师姓名单位名称及地址专业名称论文提交日期论文答辩日期答辩委员会主席论文评阅人XX年XX 月XX 日XXXX大学本科毕业设计(论文)任务申请书承担指导任务单位XXXX 导师姓名XXX导师职称X带教学生人数 1 专业X 年级X级论文题目基于DDS的数字移相信号发生器设计题目分类1.应用与非应用类:〇工程〇科研○√教学建设〇理论分析〇模拟2.软件与软硬结合类:〇软件〇硬件○√软硬结合〇非软硬件(1、2类中必须各选一项适合自己题目的类型在〇内打√)主要内容1.掌握数字移相信号发生器的工作原理和设计方法;2.基于DDS设计实现一个频率、相位可控的数字信号发生器。

主要技术指标1.输出两路正弦信号,由两路10位D/A实现波形输出;2.频率范围:1Hz~4kHz,频率步进为1Hz,输出频率可预置。

实施要求1.具备EDA技术的基础知识;2.具备数字电路和编程基础。

主要参考文献:1.潘松黄继业,EDA技术使用教程科学出版社2005. 2.COMS集成电路国防工业出版社1985.3.阎石,数字电子技术基础,高等教育出版社2000. 4.白居宪,直接数字频率合成,西安交通大学出版社2007.开题时间XXXX年X月完成时间XXXX年X月系所(单位)审定意见:系所(单位)主官签字:年月日教学指导委员会审定意见:教学指导委员主任委员签字:年月日摘要随着现代电子技术的发展,数字式信号发生器的应用越来越广泛。

本文介绍了一种以DDS为基本单元的数字移相信号发生器的设计方法。

设计采用直接数字频率合成(DDS)技术,利用FPGA芯片及D/A转换器,实现了一个频率、相位可控的正弦信号发生器。

直接数字频率合成(DDS)技术是一种新型频率合成技术,所产生的信号具有频率分辨率高、频率切换速度快、频率切换时相位连续、输出相位噪声低和可以产生任意波形等诸多优点。

EDA课程设计任务书-基于DDS的数字移相信号发生器

基于DDS的数字移相信号发生器一、课程设计目的1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、信号发生器的原始数据存储在外部存储器里,由FPGA进行读取,经过D/A转换输出,由示波器观察最终结果。

6、完成两路相位相差90度的频率幅度可调的移相信号发生器。

结果通过嵌入式分析仪观察两路正交信号。

(包括正弦波、方波、三角波)注意:以上前5点为基本要求,第6点为提高要求。

三、基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图1 直接数字频率合成器原理图其中K为频率控制字,f c为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。

相位累加器在时钟f c的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM 输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= f c K/2n,f0为输出频率,f c为时钟频率。

信号发生器使用说明书

信号发生器使用说明书一、产品简介信号发生器是一种用于产生不同频率、波形和幅度的电信号的仪器设备。

它广泛应用于电子测试、通信、音频、视频等领域。

本说明书将详细介绍信号发生器的主要功能和使用方法,帮助用户正确使用该设备。

二、产品特点1. 多功能:信号发生器支持产生多种不同波形的信号,包括正弦波、方波、三角波等,满足不同测试需求。

2. 宽频范围:信号发生器具有宽广的频率范围,可根据需要调节频率大小,适应不同的应用场景。

3. 高精度:信号发生器能够提供高精度的信号输出,保证测量结果的准确性。

4. 便携式设计:信号发生器采用便携式设计,方便用户携带和操作。

三、使用方法1. 连接电源:将信号发生器插头插入供电插座,确保电源稳定。

2. 连接信号输出:使用适当的连接线将信号发生器的输出端与被测试设备的输入端连接。

3. 设置参数:根据实际需要,通过仪器面板上的菜单和按钮设置所需的频率、波形和幅度。

4. 信号发生器启动:按下仪器面板上的启动按钮,信号发生器开始工作,并输出指定参数的信号。

5. 测试结果:通过被测试设备接收到的信号,观察和记录测试结果。

四、操作注意事项1. 信号发生器只能在干燥的室内环境中使用,避免与水和潮湿环境接触。

2. 使用前请确保信号发生器和被测试设备的电源都已关闭,避免操作中的电子干扰。

3. 在调节参数或更换连接线时,请先关闭信号发生器,以避免误操作造成损坏。

4. 在使用过程中,应注意信号发生器的工作状态,及时调整参数以满足测试需求。

5. 使用完毕后,请及时关闭信号发生器和被测试设备的电源。

五、故障排除以下是一些常见故障及可能的解决方法:1. 无信号输出:请检查是否正确连接了信号输出和被测试设备,确保所有线缆连接紧密。

2. 信号不稳定:请检查输入电源是否稳定,排除电源波动的可能性。

3. 参数调节不准确:请检查是否正确操作仪器面板上的按钮和菜单,确保参数设置正确。

六、维护保养1. 定期检查仪器面板和连接线是否有损坏,如发现问题请及时更换。

基于FPGA的高精度数字移相信号发生器的设计

基于FPGA的高精度数字移相信号发生器的设计黄俊;余水宝;黄相平【摘要】以FPGA为核心,采用锁相技术、直接数字频率合成(DDS)技术产生两路频率相同而相位不同的移相信号。

同时通过STC12LE5A60S2单片机控制,可任意设置两路信号的频率、相位差。

输入和输出的波形参数可通过液晶12864显示。

实验结果表明,系统输出的波形相移精度高、稳定性好,具有良好的实用性。

%The system as the core of FPGA,using phase-locked,DDS can produce two the same frequency but different phase shifting phase signal.At the same time with the use of the STC12LE5A60S2 MCU, the system can arbitrarily set the frequency and phase of the two signals.Waveform parameters of the input and output can be displayed through the LCD 12864. The experimental results show that it has high-precision phase-shift,excellent stability,which has good practicability.【期刊名称】《微型机与应用》【年(卷),期】2012(031)018【总页数】3页(P79-81)【关键词】FPGA;锁相;直接数字频率合成;信号发生器;DAC902【作者】黄俊;余水宝;黄相平【作者单位】浙江师范大学数理与信息工程学院,浙江金华321004;浙江师范大学数理与信息工程学院,浙江金华321004;浙江师范大学数理与信息工程学院,浙江金华321004【正文语种】中文【中图分类】TM935移相信号在电子、通信等科学研究领域有着广泛的应用,两个同频的移相信号又是电子行业继电保护领域中模拟、分析事故的一个重要手段,因此移相信号发生器是实验室和科研单位经常使用到的一个重要仪器设备。

移相正弦信号发生器设计课件

移相正弦信号发生器设计

9

设CLK=1MHZ,ROM地址线位10条(000-3FFH,1024个),

[9..0]

ADD

[7..0] FW

10位 [9..0] 10位

加法器

寄存器

正弦波 ROM2

FOUT

启始地址ADD=000H

CLK

当FW=01H=1D 下一个CLK,ADD=001H=1D 扫描一次ROM需要的CLK

移相正弦信号发生器设计

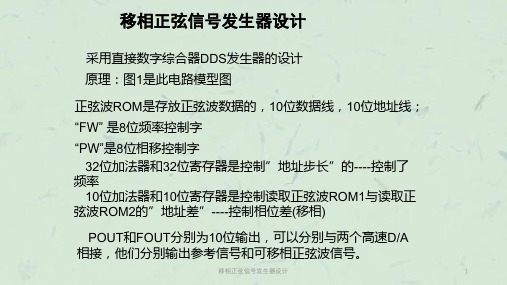

采用直接数字综合器DDS发生器的设计 原理:图1是此电路模型图

正弦波ROM是存放正弦波数据的,10位数据线,10位地址线;

“FW” 是8位频率控制字

“PW”是8位相移控制字 32位加法器和32位寄存器是控制”地址步长”的----控制了

频率 10位加法器和10位寄存器是控制读取正弦波ROM1与读取正

--10位地址10位数据正弦信号数据ROM

PORT

( address

: IN STD_LOGIC_VECTOR(9 DOWNTO 0);

inclock : IN STD_LOGIC ;

q

: OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END COMPONENT;

移相正弦信号发生器设计

DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0); DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); END REG32B; ARCHITECTURE behav OF REG32B IS BEGIN PROCESS(CLK, DIN) BEGIN IF CLK'EVENT AND Load = '1' THEN DOUT <= DIN; END IF; END PROCESS; END behav;

FPGA基于DDS的移相调频调幅信号发生器..

《EDA》课程设计报告实验题目:基于DDS的数字移相信号发生器基于DDS的数字移相信号发生器一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、信号发生器的原始数据存储在外部存储器里,由FPGA进行读取,经过D/A转换输出,由示波器观察最终结果。

三、基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图 1 直接数字频率合成器原理图其中K为频率控制字, fc为时钟频率,N为相位累加器的字长,D为ROM数据位及D/A 转换器的字长。

相位累加器在时钟 fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= fc K/2n,f0为输出频率,fc 为时钟频率。

当K=1时,DDS输出最低频率(也既频率分辩率)为fc /2nDDS的最大输出频率由 Nyguist 采样定理决定,即fc /2,也就是说K的最大值为2n-1.因此,只要N足够大,DDS可以得到很细的频率间隔。

根据DDS的数字移相信号发生器

EDA课程设计课题名称_ 基于DDS的数字移相信号发生器专业_ 电子信息工程____ _ _ 班级_____ _________ __ __ 学号_姓名_ __ __ 成绩_____ ____________ _指导教师___ _ ___ ___2014年5 月7日一、课程设计目的 (3)二、设计任务 (3)三、工作原理及模块分析 (3)1、频率预置与调节电路 (4)2、累加器 (4)3、波形存储器 (5)4、D/A转换器 (5)四、相关程序 (5)1、加法器 (5)(1)ADD10 (5)(2)ADD32 (7)2、寄存器 (9)(1)REG10B (9)(2)REG32B (11)3、ROM (13)4、主程序 (16)五、仿真结果: (20)六、引脚配置和下载 (20)七、实验心得 (22)一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM_ADD_SUB、LPM ROM、LPM_FF 的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计二、设计任务完成10位输出数据宽度的频率可调的移相正弦信号发生器,通过按键调节频率和初始相位,实现相位和频率可调的正弦信号发生器三、工作原理及模块分析直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:fc图1直接数字频率合成器原理图其中K为频率控制字,fc为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。

相位累加器在时钟fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

SFF05A型数字信号发生器使用说明书

目录第一章概述1第二章主要特征1第三章技术指标2一、函数信号发生器2二、计数器5三、其它6第四章面板说明7一、显示说明7二、前面板说明8三、后面板说明13第五章使用说明14一、测试前的准备工作14二、函数信号输出使用说明14三、计数器使用说明32第六章遥控操作使用说明34第七章B路信号说明52第八章功率放大模块说明57第九章注意事项与检修58第十章附录USB接口驱动安装59第十一章仪器整套设备及附件63南京盛普仪器科技有限公司 1南京盛普仪器科技有限公司 2本仪器是一台精密的测试仪器,具有输出函数信号、调频、调幅、FSK 、PSK 、猝发、频率扫描等信号的功能。

此外,本仪器还具有测频和计数的功能。

本仪器是电子工程师、电子实验室、生产线及教学、科研的理想测试设备。

1、 采用直接数字合成技术(DDS )。

2、 主波形输出频率为1μHz ~ 20MHz 。

3、 小信号输出幅度可达1mV 。

4、 脉冲波占空比分辨率高达千分之一。

5、 数字调频、调幅分辨率高、准确。

6、 猝发模式具有相位连续调节功能。

7、 频率扫描输出可任意设置起点、终点频率。

8、 相位调节分辨率达0.1度。

9、调幅调制度1% ~ 100% 可任意设置。

10、输出波形达30余种。

11、具有频率测量和计数的功能。

12、机箱造型美观大方,按键操作舒适灵活。

13、具有第二路输出,可控制和第一路信号的相位差。

概述 12主要特征南京盛普仪器科技有限公司 3一、函数发生器1、波形特性主波形:正弦波、方波波形幅度分辨率:12 bits采样速率:200Msa/s正弦波谐波失真:-50dBc (频率≤ 5MHz )-45dBc (频率≤ 10MHz )-40dBc (频率>10MHz )正弦波失真度: ≤0.2%(频率:20Hz ~ 100kHz )方波升降时间: ≤ 25ns (SPF05A ≤ 28ns )注:正弦波谐波失真、正弦波失真度、方波升降时间测试条件:输出幅度2Vp-p (高阻),环境温度25℃±5℃储存波形:正弦波,方波,脉冲波,三角波,锯齿波,阶梯波等26种波形,TTL 波形(仅F20A ,输出频率同主波形)波形长度:4096点波形幅度分辨率:12 bits脉冲波占空系数:1.0% ~ 99.0%(频率≤10kHz ),10% ~ 90%(频率10kHz ~ 100kHz )脉冲波升降时间: ≤1uS直流输出误差:≤±10%+10mV (输出电压值范围10mV~10V )TTL 波形输出:(F05A 、F10A )输出频率:同主波形输出幅度:低电平 < 0.5 V 高电平 > 2.5 V输出阻抗:600 Ω2、频率特性3技术指标频率范围:主波形:1μHz ~ 5MHz (SPF05A型)1μHz ~ 10MHz (SPF10A型)1μHz ~ 20MHz (SPF20A型)储存波形:1μHz ~ 100kHz分辨率:1μHz频率误差:≤±5×10-4 频率稳定度:优于±5×10-53、幅度特性幅度范围:1mV ~ 20Vp-p(高阻),0.5mV ~ 10Vp-p(50Ω)最高分辨率:2μVp-p (高阻),1μVp-p(50Ω)幅度误差:≤±2%+1mV (频率1KHz正弦波)幅度稳定度:±1 % /3小时平坦度:±5%(频率≤5MHz正弦波), ±10% (频率>5MHz 正弦波)±5%(频率≤50 kHz其它波形), ±20% (频率>50 kHz 其它波形)输出阻抗:50Ω幅度单位:Vp-p,mVp-p,Vrms,mVrms,dBm4、偏移特性直流偏移(高阻):±(10V-Vpk ac),(偏移绝对值≤2×幅度峰峰值)最高分辨率:2μV(高阻),1μV(50Ω)偏移误差:≤±10% +20mV (高阻)5、调幅特性载波信号:波形为正弦波,频率范围同主波形调制方式:内或外调制信号:内部5种波形(正弦、方波、三角、升锯齿、降锯齿)或外输入信号调制信号频率:1Hz ~ 20kHz(内部)100Hz ~ 10kHz(外部)失真度:≤1% (调制信号频率1KHz正弦波)南京盛普仪器科技有限公司 4调制深度:1% ~ 100%相对调制误差:≤±5% +0.5 (调制信号频率1KHz正弦波)外输入信号幅度:3Vp-p(-1.5V~ +1.5V)6、调频特性载波信号:波形为正弦波,频率范围同主波形调制方式:内或外(外为选件)调制信号:内部5种波形(正弦、方波、三角、升锯齿、降锯齿))或外输入信号调制信号频率:1Hz ~ 10kHz(内部)100Hz ~ 10kHz(外部)频偏:内调频最大频偏为载波频率的50%,同时满足频偏加上载波频率不大于最高工作频率+100 kHz 失真度:≤1% (调制信号频率1KHz正弦波)相对调制误差:≤±5%设置值±50Hz (调制信号频率1KHz正弦波)外输入信号幅度:3Vp-p(-1.5V~ +1.5V)FSK:频率1和频率2任意设定控制方式:内或外(外控:TTL电平,低电平F1;高电平F2)交替速率:0.1ms ~ 800s7、调相特性基本信号:波形为正弦波,频率范围同主波形PSK:相位1(P1)和相位2(P2)范围:0.1 ~ 360.0°分辨率:0.1°交替时间间隔:0.1ms ~ 800s控制方式:内或外(外控TTL电平,低电平P2,高电平P1)8、猝发基本信号:波形为正弦,频率范围同主波形猝发计数:1 ~ 30000个周期猝发信号交替时间间隔:0.1ms ~ 800s南京盛普仪器科技有限公司 5控制方式:内(自动)/外(单次手动按键触发、外输入TTL脉冲上升沿触发)9、频率扫描特性信号波形:正弦波扫描频率范围:扫描起始点频率:主波形频率范围扫描终止点频率主波形频率范围。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书(指导教师填写)课程设计名称现代电子系统课程设计学生姓名专业班级设计题目数字移相信号发生器设计一、课程设计目的掌握数字移相信号发生器的工作原理和设计方法;掌握DDS技术的工作原理;掌握GW48_SOPC实验箱的使用方法;了解基于FPGA的电子系统的设计方法。

二、设计内容、技术条件和要求基于DDS技术利用VHDL设计并制作一个数字式移相信号发生器。

(1)基本要求:a.频率范围:1Hz~4kHz,频率步进为1Hz,输出频率可预置。

b.A、B两路正弦信号输出,10位输出数据宽度c.相位差范围为0~359°,步进为1.4°,相位差值可预置。

d.数字显示预置的频率(10进制)、相位差值。

(2)发挥部分a.修改设计,增加幅度控制电路(如可以用一乘法器控制输出幅度)。

b.输出幅度峰峰值0.1~3.0V,步距0.1Vc.其它。

三、时间进度安排布置课题和讲解:1天查阅资料、设计:4天实验:3天撰写报告:2天四、主要参考文献何小艇《电子系统设计》浙江大学出版社2008.1潘松黄继业《EDA技术实用教程》科学出版社2006.10王勇《EDA》实验指导书电工电子实验教学中心2006.8指导教师签字:2009年12月14日摘要在现代的信号分析和处理领域,高精度的频率和相位测量非常重要,它是理论和工程分析的重要工具。

使用模拟或数字示波器测量频率,是我们最常用的方法,同时也是不是很精确的方法;同时如果要测量两路信号的相位差,使用示波器又不是很方便。

而且示波器的价格最低需要几千元,对于普通人来讲不是最佳选择。

在本文中,我们设计了一个数字移相信号发生器设计。

主要分为如下几个部分:●键盘和显示模块:用键盘输入,数码管显示频率控制字和相位控制字。

采用按键复用的方法。

●数字DDS模块:分为频率合成模块和相位合成模块。

具体的方案论证将在下面进行。

●时钟模块:由于系统需要时钟频率和实验箱上的不匹配,需要频率变换,具体的方案论证将在下面进行。

●高速DA模块:输出两个频率和幅度相同相位不同的正弦波,且同时频率和相位差可调。

关键词:频率、移相、VHDL、FPGA、DDS目录一.任务解析 (5)1 任务与要求 (5)2 系统原理框图 (5)二.系统方案论证 (5)2.1 总体方案与比较论证 (5)2.2系统原理与结构 (6)2.2.1主要芯片选型 (7)2.2.2系统结构 (7)三. 数字DDS(DDFS)模块设计 (8)3.1 DDFS原理 (8)3.2频率合成模块 (9)3.3相位合成模块 (10)3.4数字DDS实现方式 (11)四.时钟模块设计 (13)4.1设计方案论证 (13)4.2方案的实现 (14)五. 键盘和显示模块设计 (14)5.1 硬件设计 (14)5.2 软件设计及仿真 (15)六. 高速DA模块 (16)七.程序整体设计 (16)7.1模块整合 (16)7.2整体仿真 (18)八. 总结 (18)8.1测试性能概览 (18)8.2 系统误差原因分析 (19)8.2.1噪声的混入: (19)8.2.2数字式移相信号发生器的误差 (19)8.3心得体会 (19)一.任务解析1 任务与要求基于DDS技术利用VHDL设计并制作一个数字式移相信号发生器。

a.频率范围:1Hz~4kHz,频率步进为1Hz,输出频率可预置。

b.A、B两路正弦信号输出,10位输出数据宽度c.相位差范围为0~359°,步进为1.4°,相位差值可预置。

d.数字显示预置的频率(1-4000)(10进制)、相位差值(00-FF)。

2 系统原理框图图1-1 DDS数字移相调频原理框图二.系统方案论证2.1 总体方案与比较论证方案一:采用函数发生器(如ICL8038)产生频率可变的正弦波周期性波形。

此方案实现电路复杂,难于调试,且要保证技术要求的指标困难,故方案不理想。

方案二:采用单片机控制合波形波形频率控制由单片机编程实现。

此方案产生的频率范围,步进值取决于所采用的每个周期的输出点数及单片机执行指令的时间。

此方案的优点是硬件电路简单,所用器件少,且实现各种波形相对容易,在低频区基本能实现要求的功能;缺点是精度不易满足,产生波形频率范围小,特别难以生成高频波形。

方案三:采用DDS技术,将所需生成的波形写入ROM中,按照相位累加原理合成任意波形。

此方案得到的波形稳定,精度高,产生波形频率范围大,容易产生高频。

方案四:锁相频率合成技术方案,优点:有稳定的频率、稳定的边沿,具有易预置、易调节的优点,控制和调节电路都是数字电路,工作稳定可靠。

缺点:锁相环的锁相特性,环路滤波器既要保证有很好的滤波特性,又要求它能够使锁相环有很快的捕捉时间,电路的复杂程度中等。

比较以上四种方案的优缺点,方案三简洁、灵活、可扩展性好,能完全达到设计要求,故采用第三种方案。

2.2系统原理与结构2.2.1主要芯片选型EP1C0Q240C8(Cyclone系列FPGA):Cyclone(飓风):Altera中等规模FPGA,2003年推出,0.13um工艺,1.5v 内核供电,与Stratix结构类似,是一种低成本FPGA系列,是目前主流产品,其配置芯片也改用全新的产品。

DA5651:10位超高速DAC(转换速率最高150MHz)。

2.2.2系统结构系统从硬件上看主要由显示模块、FPGA模块(时钟)、DA转换模块、按键输入模块。

硬件和软件设计更方便,利于以后的扩展;FPGA模块实现波形数据的存储与输出;DA转换模块作用将波形数据转换为模拟量。

显示器用于显示频率、相位等。

硬件系统框图见图2.2.1。

键盘数模转换FPGA显示图2.2.1 硬件系统框图系统从功能上看可分为:键盘和显示模块,数字DDS模块(分为频率合成模块和相位合成模块),时钟模块、高速DA模块。

功能系统框图见图2.2.2。

键盘和显示频率合成模块相位合成模块高速DA模块时钟模块DDS图2.2.2 功能系统框图三.数字DDS(DDFS)模块设计3.1 DDFS原理DDFS 以数控的方式产生频率、相位和幅度可以控制的正弦波,DDFS 的基本结构主要由相位累加器、相位调制器、正弦ROM 查找表和D/A 构成,相位累加器是整个DDFS 核心,完成相位累加运算。

相位累加器、相位调制器、正弦ROM 查找表是DDFS 结构中的数字部分,由于具有数控频率合成的功能,又合称为NCO(Numerically Controlled Oscillators)。

直接数字频率合成(DDFS)移相原理是:先将正弦波信号数字化,并形成一张数据表存入两片ROM芯片中,此后可通过两片D/A转换芯片在计数器的控制下连续地循环输出该数据表,就可获得两路正弦波信号。

当两片D/A转换芯片所获得的数据序列完全相同时,则转换所得到的两路正弦波信号无相位差称为同相。

当两片D/A转换芯片所获得的数据序列不同时,则转换所得到的两路正弦波信号就存在着相位差。

相位差的值与数据表中数据的总个数及数据地址的偏移量有关。

这种处理方式的实质是将数据地址的偏移量映射为信号间的相位值。

数据的偏差可以通过外部微处理器来获得相应的数字量输入,这个数值对应着正弦信号的移相角度。

数字移相信号发生器的核心是 DDFS ,相位累加器输出与相位增量相加,相加后的结果形成正弦查询表地址,取出表中与该相位对应的单元中的幅度量化正弦函数值,经高速 D/A 转换器输出模拟信号。

两路信号的相位差用相位字来控制,只要相位字不同,就可得到两路不同相位的移相信号。

一张数据表格由 1024 个数据点组成,存储了一个周期的正弦波,相位差的分辨率为:0.0061359222210===ππD P ,具有很高的相位分辨率。

3.2频率合成模块设计要求频率范围:1Hz ~4kHz ,频率步进为1Hz ,因此频率控制字需要N 应该满足40002≥N ,N ≥12,本设计取N=12,频率控制字为12位,累加器的位数应不小于(12+10)=22,才能满足波形精度不受输入频率的影响,本设计采用32位(低10位不用)。

模块连接图如图3.2.1所示。

如图3.2.1 频率合成模块连接图3.3相位合成模块设计要求相位差范围为0~359°,步进为1.4°,因此需要8位的相位控制字,加法器和寄存器采用sin_rom和相位控制字的最大值10位,模块连接图如图3.3.1所示如图3.3.1 相位合成模块连接图3.4数字DDS实现方式图3.4.1 DDS模块RTL图图3.4.2 DDS模块仿真波形四.时钟模块设计4.1设计方案论证根据频率范围和累加器位数,以及其连接的情况可以计算出,DDFS模块所需要的系统时钟频率为MHz2104+,因实验箱上没有4MHz的时钟频率,22=所以需要频率变换,具体有如下方案:方案一:数字锁相环,利用Altera公司的FPGA开发MegaWizard Plug-In Manager定制数字锁相环。

优点:不用编写代码,调试方便,容易修改,频率稳定。

缺点:主要针对高频的时钟变换,4MHz的频率不属于高频,不能直接定制。

方案二:分频方式,优点:代码简单,容易编写,对输入频率没有特别的要求,只要满足4MHz的整数倍就行。

缺点:如果输入频率信号质量不太好,可能会影响输入频率。

本设计采用方案二分频方式。

4.2方案的实现采用12MHz的时钟进行3分频,模块符号文件和仿真波形如图4.2.1和图4.2.2所示。

图4.2.1 时钟模块符号文件图4.2.1 时钟模块仿真波形五.键盘和显示模块设计5.1 硬件设计本模块采用按键复用方式,显示采用数码管,电路原理图如图5.1.1所示,按键S1(对应实验箱上按键8)控制输入控制字是频率控制字还是相位控制字,当S1为低电平时输入频率控制字,否则,是相位控制字。

如图5.1.1 键盘和显示模块电路原理图5.2 软件设计及仿真由于设计要求采用十进制显示,然而实验箱上用的是十六进制计数器,所以把十六进制当做十进制看待,当输入的控制字有一位大于9时,控制字无效,仿真波形图如图5.2.2所示。

图5.2.2 键盘和显示模块仿真波形六.高速DA 模块GW_ADDA 板含两片10位超高速DAC (转换速率最高150MHz ),D/A 全部处于使能状态,除了数据线外,任一器件的控制信号线只有时钟线,这有利于高速控制和直接利用MATLAB/DSP Builder 工具的设计。

GW_ADDA 板上工作时钟必须由FPGA 的I/O 口提供,优点是时钟频率容易变化,且可通过Cyclone 中的PLL 的到几乎任何时钟频率。

由此即可测试DAC 的最高转换频率。

两个电位器可分别调协两个D/A 输出的幅度(输出幅度峰峰值不可大于5V ,否则波形失真);模拟信号从接插口的2针“AIN ”输入,J1和J2分别是模拟信号输出的PA 、PB 口,也可在两挂钩处输出,分别是两个10位DA5651输出口。