PCB4层叠层

PCB叠层设计层的排布原则和常用层叠结构

PCB叠层设计层的排布原则和常用层叠结构叠层设计层的排布原则和常用层叠结构在设计多层PCB板之前,设计者需要首先按照电路的规模、电路板的尺寸和电磁兼容()的要求来确定所采纳的电路板结构,也就是打算采纳4层,6层,还是更多层数的电路板。

确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。

这就是多层PCB层叠结构的挑选问题。

层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。

本文介绍多层PCB板层叠结构的相关内容。

对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题;层的排布普通原则:1、确定多层PCB板的层叠结构需要考虑较多的因素。

从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增强。

对于生产厂家来说,层叠结构对称与否是PCB板创造时需要关注的焦点,所以层数的挑选需要考虑各方面的需求,以达到最佳的平衡。

对于有阅历的设计人员来说,在完成元器件的预布局后,会对PCB的布线瓶颈处举行重点分析。

结合其他工具分析电路板的布线密度;再综合有特别布线要求的信号线如差分线、敏感信号线等的数量和种类来确定信号层的层数;然后按照电源的种类、隔离和抗干扰的要求来确定内电层的数目。

这样,囫囵电路板的板层数目就基本确定了。

2、元件面下面(其次层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;敏感信号层应当与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为信号层提供屏蔽。

电路中的高速信号传输层应当是信号中间层,并且夹在两个内电层之间。

这样两个内电层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。

3、全部信号层尽可能与地平面相邻;4、尽量避开两信号层挺直相邻;相邻的信号层之间简单引入串扰,从而导致电路功能失效。

在两信号层之间加入地平面可以有效地避开串扰。

pcb叠层参考

名词定义:SIG:信号层;GND:地层;PWR:电源层;电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到十层板的叠层:2.1 单面板和双面板的叠层;对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:1 在同一层的电源走线以辐射状走线,并最小化线的长度总和;2 走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于线路板的厚度乘以信号线的长度。

2.2 四层板的叠层;推荐叠层方式:2.2.1 SIG-GND(PWR)-PWR (GND)-SIG;2.2.2 GND-SIG(PWR)-SIG(PWR)-GND;对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

4层PCB制作过程,图解创意DIY

4层PCB制作过程,图解创意DIY我们来看一下印刷电路板是如何制作的,以四层为例。

四层PCB板制作过程:1.化学清洗—【Chemical Clean】为得到良好质量的蚀刻图形,就要确保抗蚀层与基板表面牢固的结合,要求基板表面无氧化层、油污、灰尘、指印以及其他的污物。

因此在涂布抗蚀层前首先要对板进行表面清洗并使铜箔表面达到一定的粗化层度。

内层板材:开始做四层板,内层(第二层和第三层)是必须先做的。

内层板材是由玻璃纤维和环氧树脂基复合在上下表面的铜薄板。

2.裁板压膜—【Cut Sheet Dry Film Lamination】涂光刻胶:为了在内层板材作出我们需要的形状,我们首先在内层板材上贴上干膜(光刻胶,光致抗蚀剂)。

干膜是由聚酯簿膜,光致抗蚀膜及聚乙烯保护膜三部分组成的。

贴膜时,先从干膜上剥下聚乙烯保护膜,然后在加热加压的条件下将干膜粘贴在铜面上。

3.曝光和显影-【Image Expose】【Image Develop】曝光:在紫外光的照射下,光引发剂吸收了光能分解成游离基,游离基再引发光聚合单体产生聚合交联反应,反应后形成不溶于稀碱溶液的高分子结构。

聚合反应还要持续一段时间,为保证工艺的稳定性,曝光后不要立即撕去聚酯膜,应停留15分钟以上,以时聚合反应继续进行,显影前撕去聚酯膜。

显影:感光膜中未曝光部分的活性基团与稀碱溶液反应生产可溶性物质而溶解下来,留下已感光交联固化的图形部分。

4.蚀刻-【Copper Etch】在挠性印制板或印制板的生产过程中,以化学反应方法将不要部分的铜箔予以去除,使之形成所需的回路图形,光刻胶下方的铜是被保留下来不受蚀刻的影响的。

5.去膜,蚀后冲孔,AOI检查,氧化Strip Resist】【Post Etch Punch】【AOI Inspection】【Oxide】去膜的目的是清除蚀刻后板面留存的抗蚀层使下面的铜箔暴露出来。

“膜渣”过滤以及废液回收则须妥善处理。

PCB叠层结构参考即多层板叠层建议

PCB叠层结构参考即多层板叠层建议电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷, 将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到十层板的叠层:一、单面PCB板和双面PCB板的叠层对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHZ的低频模拟设计中:1在同一层的电源走线以辐射状走线,并最小化线的长度总和;2走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于线路板的厚度乘以信号线的长度。

、四层板的叠层;推荐叠层方式:1. SIG —GND(PWR) —PWR (GND) —SIG ;2. GND -SIG(PWR) —SIG(PWR) —GND ;对于以上两种叠层设计,潜在的问题是对于传统的 1.6mm (62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

PCB分层技巧

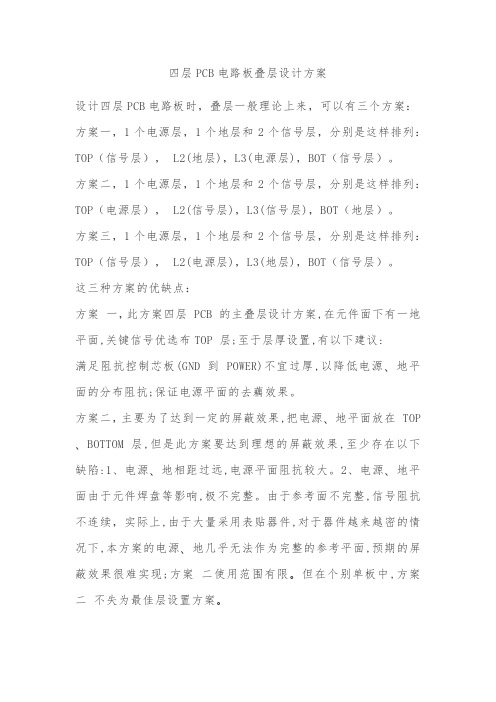

PCB分层技巧①二层板,此板仅能用于低速设计。

EMC比较差。

②四层板。

由以下几种叠层顺序。

下面分别把各种不同的叠层优劣作说明.表一注:S1 信号布线一层,S2 信号布线二层;GND 地层 POWER 电源层第一种情况,应当是四层板中最好的一种情况.因为外层是地层,对EMI有屏蔽作用,同时电源层同地层也可靠得很近,使得电源内阻较小,取得最佳郊果。

但第一种情况不能用于当本板密度比较大的情况.因为这样一来,就不能保证第一层地的完整性,这样第二层信号会变得更差。

另外,此种结构也不能用于全板功耗比较大的情况.表中的第二种情况,是我们平时最常用的一种方式。

从板的结构上,也不适用于高速数字电路设计。

因为在这种结构中,不易保持低电源阻抗.以一个板2毫米为例:要求Z0=50ohm。

以线宽为8mil。

铜箔厚为35цm。

这样信号一层与地层中间是0.14mm。

而地层与电源层为1。

58mm。

这样就大大的增加了电源的内阻.在此种结构中,由于辐射是向空间的,需加屏蔽板,才能减少EMI。

表中第三种情况,S1层上信号线质量最好。

S2次之。

对EMI有屏蔽作用.但电源阻抗较大。

此板能用于全板功耗大而该板是干扰源或者说紧临着干扰源的情况下。

③六层板表二A种情况,是常见的方式之一,S1是比较好的布线层.S2次之。

但电源平面阻抗较差。

布线时应注意S2对S3层的影响。

B种情况,S2层为好的布线层,S3层次之.电源平面阻抗较好。

C种情况,这种情况是六层板中最好的情况,S1,S2,S3都是好的布线层.电源平面阻抗较好。

美中不足的是布线层同前两种情况少了一层。

D种情况,在六层板中,性能虽优于前三种,但布线层少于前两种。

此种情况多在背板中使用.④八层板表三八层板,如果要有6个信号层,以A种情况为最好。

但此种排列不宜用于高速数字电路设计。

如果是5个信号层,以C种情况为最好。

在这种情况中,S1,S2,S3都是比较好的布线层。

同时电源平面阻抗也比较低.如果是4个信号层,以表三中B种情况为最好。

PCB电路板如何快速掌握PCB四层板

PCB电路板如何快速掌握PCB四层板四层电路板布线方法一般而言,四层电路板可分为顶层、底层和两个中间层。

顶层和底层走信号线,中间层首先通过命令DESIGN/LAYERSTACKMANAGER用ADDPLANE添加INTERNALPLANE1和INTERNALPLANE2分别作为用的最多的电源层如VCC和地层如GND(即连接上相应的网络标号。

注意不要用ADDLAYER,这会增加MIDPLAYER,后者主要用作多层信号线放置),这样PLNNE1和PLANE2就是两层连接电源VCC和地GND的铜皮。

如果有多个电源如VCC2等或者地层如GND2等,先在PLANE1或者PLANE2中用较粗导线或者填充FILL(此时该导线或FILL对应的铜皮不存在,对着光线可以明显看见该导线或者填充)划定该电源或者地的大致区域(主要是为了后面PLACE/SPLITPLANE命令的方便),然后用PLACE/SPLITPLANE在INTERNALPLANE1和INTERNALPLANE2相应区域中划定该区域(即VCC2铜皮和GND2铜片,在同一PLANE中此区域不存在VCC 了)的范围(注意同一个PLANE中不同网络表层尽量不要重叠。

设SPLIT1和SPLIT2是在同一PLANE中重叠两块,且SPLIT2在SPLIT1内部,制版时会根据SPLIT2的边框自动将两块分开(SPLIT1分布在SPLIT的外围)。

只要注意在重叠时与SPLIT1同一网络表的焊盘或者过孔不要在SPLIT2的区域中试图与SPLIT1相连就不会出问题)。

这时该区域上的过孔自动与该层对应的铜皮相连,DIP封装器件及接插件等穿过上下板的器件引脚会自动与该区域的PLANE让开。

点击DESIGN/SPLITPLANES可查看各SPLITPLANES。

protel99的图层设置与内电层分割PROTEL99的电性图层分为两种,打开一个PCB设计文档按,快捷键L,出现图层设置窗口。

四层PCB电路板叠层设计方案

四层PCB电路板叠层设计方案

设计四层PCB电路板时,叠层一般理论上来,可以有三个方案:方案一,1个电源层,1个地层和2个信号层,分别是这样排列:TOP(信号层), L2(地层),L3(电源层),BOT(信号层)。

方案二,1个电源层,1个地层和2个信号层,分别是这样排列:TOP(电源层), L2(信号层),L3(信号层),BOT(地层)。

方案三,1个电源层,1个地层和2个信号层,分别是这样排列:TOP(信号层), L2(电源层),L3(地层),BOT(信号层)。

这三种方案的优缺点:

方案一,此方案四层 PCB 的主叠层设计方案,在元件面下有一地平面,关键信号优选布TOP 层;至于层厚设置,有以下建议:

满足阻抗控制芯板(GND 到 POWER)不宜过厚,以降低电源、地平面的分布阻抗;保证电源平面的去藕效果。

方案二,主要为了达到一定的屏蔽效果,把电源、地平面放在 TOP 、BOTTOM 层,但是此方案要达到理想的屏蔽效果,至少存在以下缺陷:1、电源、地相距过远,电源平面阻抗较大。

2、电源、地平面由于元件焊盘等影响,极不完整。

由于参考面不完整,信号阻抗不连续,实际上,由于大量采用表贴器件,对于器件越来越密的情况下,本方案的电源、地几乎无法作为完整的参考平面,预期的屏蔽效果很难实现;方案二使用范围有限。但在个别单板中,方案二不失为最佳层设置方案。

方案三:此方案同方案 1 类似,适用于主要器件在 BOTTOM 布局或关键信号底层布线的情况;。

PCB叠层设计

多层线路板设计-适合于初学者多层PCB层叠结构在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。

确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。

这就是多层PCB层叠结构的选择问题。

层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。

本节将介绍多层PCB板层叠结构的相关内容。

11.1.1 层数的选择和叠加原则确定多层PCB板的层叠结构需要考虑较多的因素。

从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。

对于生产厂家来说,层叠结构对称与否是PCB板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到最佳的平衡。

对于有经验的设计人员来说,在完成元器件的预布局后,会对PCB的布线瓶颈处进行重点分析。

结合其他EDA工具分析电路板的布线密度;再综合有特殊布线要求的信号线如差分线、敏感信号线等的数量和种类来确定信号层的层数;然后根据电源的种类、隔离和抗干扰的要求来确定内电层的数目。

这样,整个电路板的板层数目就基本确定了。

确定了电路板的层数后,接下来的工作便是合理地排列各层电路的放置顺序。

在这一步骤中,需要考虑的因素主要有以下两点。

(1)特殊信号层的分布。

(2)电源层和地层的分布。

如果电路板的层数越多,特殊信号层、地层和电源层的排列组合的种类也就越多,如何来确定哪种组合方式最优也越困难,但总的原则有以下几条。

(1)信号层应该与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为信号层提供屏蔽。

(2)内部电源层和地层之间应该紧密耦合,也就是说,内部电源层和地层之间的介质厚度应该取较小的值,以提高电源层和地层之间的电容,增大谐振频率。

内部电源层和地层之间的介质厚度可以在Protel的Layer Stack Manager(层堆栈管理器)中进行设置。

PCB4-16层叠层

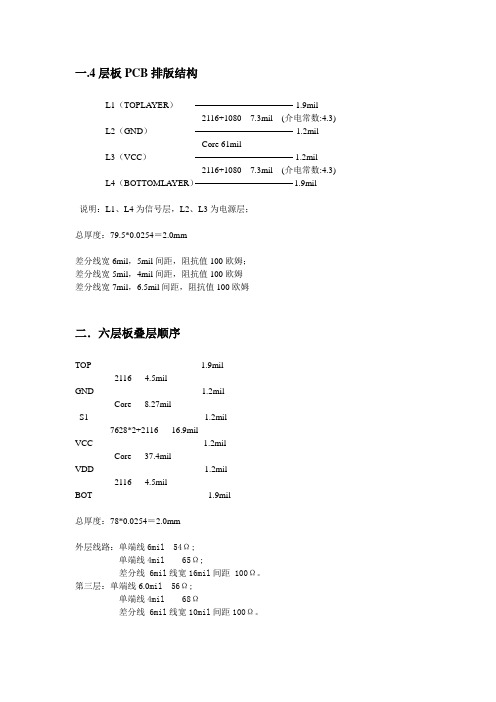

一.4层板PCB排版结构L1(TOPLAYER) 1.9mil2116+1080 7.3mil (介电常数:4.3) L2(GND) 1.2milCore 61milL3(VCC) 1.2mil2116+1080 7.3mil (介电常数:4.3) L4(BOTTOMLAYER) 1.9mil说明:L1、L4为信号层,L2、L3为电源层;总厚度:79.5*0.0254=2.0mm差分线宽6mil,5mil间距,阻抗值100欧姆;差分线宽5mil,4mil间距,阻抗值100欧姆差分线宽7mil,6.5mil间距,阻抗值100欧姆二.六层板叠层顺序TOP ------------------------------- 1.9mil2116 4.5milGND------------------------------- 1.2milCore 8.27milS1 --------------------------------- 1.2mil7628*2+2116 16.9milVCC-------------------------------- 1.2milCore 37.4milVDD-------------------------------- 1.2mil2116 4.5milBOT---------------------------------- 1.9mil总厚度:78*0.0254=2.0mm外层线路:单端线6mil 54Ω;单端线4mil 65Ω;差分线 6mil线宽16mil间距 100Ω。

第三层:单端线6.0mil 56Ω;单端线4mil 68Ω差分线 6mil线宽10mil间距100Ω。

③. 八层板叠层顺序TOP ------------------------------- 1.9mil1080*2 7.3milGND------------------------------- 1.2milCore 20.08milS1 --------------------------------- 1.2mil7628*2+2116 16.9milVCC-------------------------------- 1.2milCore 20.08milVDD-------------------------------- 1.2mil7628*2+2116 16.9milS2 ---------------------------------- 1.2milCore 20.08milGND--------------------------------- 1.2mil1080*2 7.3milBOT---------------------------------- 1.9mil总厚度:117*0.0254=3.0mm外层线路:单端线12mil 50Ω;单端线6.5mil 68Ω;单端线5mil 75Ω差分线 4mil线宽19mil间距 150Ω。

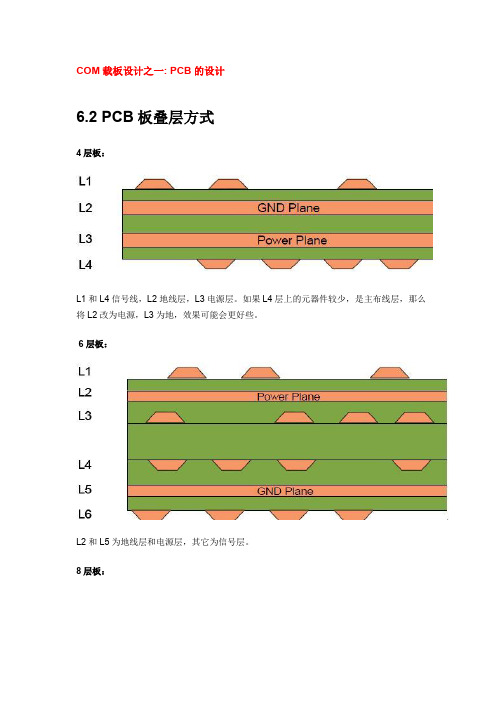

COM载板设计之一PCB的设计

IDE 布线规则

参数

布线

传输速率@ATA100MHz

100MB/sec

载板上允许的最大信号线长度

7 英寸

单端阻抗

55 欧姆+/-15%

线宽

5mil

信号线间的间隙

7mil

选通和数据信号线的长度差异

最大 450mil

数据信号之间_IOR 与 IDE_IOW 之间的长度差异 最大 100mil

差分对与低速非周期信号之间相距

最小 100mil

差分对两个线的长度相差

最大 5mil

RX 和 TX 差分对之间的长度相差

最大 30mil

数字地平面和模拟地平面(变压器和 RJ45)之间的间隙

最小 60mil

距离层平面的边缘的空隙

最小 40mil

过孔的使用

TX:最多 2 个过孔;RX 最多 4 个过孔

载板上允许的信号线长度

6.75 英寸

差分阻抗

100 欧姆+/-20%

单端阻抗

55 欧姆+/-15%

线宽

4mil

两个差分线间的间距(差分对内)(S)

7mil

对与对之间的间隙(S)

最小 20mil

差分对与高速周期信号之间相距

最小 20mil

差分对与低速非周期信号之间相距

最小 20mil

差分对之间的长度相差

差

RX 和 TX 通道,不要因为满足长度问题而去蜿蜒曲折。

距离层平面的边缘的空隙 过孔的使用 AC 耦合电容

最小 40mil 总是要极力使过孔最少 TX 和 RX 线上的 AC 耦合电容在 COM 板上

LVDS 布线指南:

参数

布线

PCB四层板典型叠层方法与板厚控制

PCB四层板典型叠层方法与板厚控制四层板是一种常见的印制电路板(PCB)类型,其内部有四层铜箔,分别是两层信号层、一层地平面层和一层电源层。

这种叠层结构能够提供更好的电磁兼容性(EMC)和信号完整性,适用于较复杂的电路设计。

在设计四层板时,需要考虑叠层方法和板厚控制,以确保电路板的性能和可靠性。

一、四层板典型叠层方法1.信号层-地平面层-电源层-信号层叠层方法:这是最常见的四层板叠层方法。

信号层分布在两个对称层,地平面层用于提供地平面,电源层用于提供电源。

这种叠层方法可以减少信号层之间的干扰,并提供良好的电源和地平面。

2.信号层-电源层-地平面层-信号层叠层方法:这种叠层方法与第一种方法相似,只是地平面层和电源层的顺序颠倒。

这种叠层方法较少使用,但在一些特殊情况下可能会有特定要求。

3.隔层地平面层的叠层方法:在一些高频应用中,需要在信号层之间插入地平面层,以提供更好的环境屏蔽和电磁兼容性。

这种叠层方法可以减少信号层之间的互相干扰,并提供更好的信号完整性。

二、板厚控制在四层板设计中,板厚控制至关重要,常见的四层板标准厚度为1.6mm。

以下是一些常见的板厚控制要求:1.信号层和电源层铜箔厚度:通常,信号层和电源层的铜箔厚度相同,常用的铜箔厚度有1oz(约35um)和2oz(约70um)。

选择合适的铜箔厚度可以满足电流要求,并提供足够的导电性。

2.地平面层铜箔厚度:地平面层的铜箔厚度通常要比信号层和电源层的铜箔厚度大,以提供更好的导电性和地平面。

3.内层铜箔厚度:内层铜箔厚度一般与信号层和电源层的铜箔厚度相同,用于提供信号层之间的连接。

4.外层厚度:除了铜箔层之外,四层板还包括外层的基材。

通常,外层基材的厚度为0.1mm至0.2mm,可以根据需要进行选择。

5.高频应用板厚控制:对于高频应用,板厚控制更为严格。

通常要求板厚公差小于±5%。

在设计和制造过程中需要更加注意,以避免高频信号的传输损耗。

四层线路板层定义-概述说明以及解释

四层线路板层定义-概述说明以及解释1.引言1.1 概述概述部分的内容可以根据四层线路板(Four-Layer PCB)的定义和特点进行介绍。

以下是一个示例:四层线路板(Four-Layer PCB)是一种常见的印制电路板(Printed Circuit Board,简称PCB)结构,它由四层互相交织的电路层组成。

这种线路板的设计和制造具有许多优势,主要体现在以下几个方面:首先,四层线路板允许更复杂的电路设计。

相比于双层线路板或单层线路板,四层线路板提供了更多的电路层,这意味着设计师可以在更小的面积上实现更多的功能。

这对于那些需要高度集成的电路应用来说尤为重要,因为它们通常需要更多的元器件和连接。

其次,四层线路板能够减少电磁干扰(Electromagnetic Interference,简称EMI)的问题。

由于四层线路板具有内部的地层和电源层,它们可以有效地吸收和隔离来自不同电路之间的干扰信号。

这有助于提高电路的稳定性和可靠性,并减少信号跳变和串音等问题。

此外,四层线路板还可以提供更好的散热性能。

通过为电路设计添加附加的散热层,四层线路板可以将热量从关键元器件和电路区域有效地传导和分散,从而降低温度并延长电子设备的使用寿命。

最后,四层线路板在布线和布板中提供了更多的灵活性。

由于存在更多的电路层,设计师可以更好地规划和组织信号和电源的走线路径,从而减少电路布线的混乱和交叉。

这样可以提高布局的整洁性和电路的可读性,同时也有助于减少电路的延迟和串扰干扰。

总之,四层线路板作为一种常用的PCB结构,由于其复杂电路设计、抗干扰能力、散热性能和布线灵活性等优势,被广泛应用于各种电子设备和应用领域。

在不断发展和改进的电子技术环境中,四层线路板的重要性和应用前景将愈发突出。

1.2文章结构1.2 文章结构本文将从四层线路板的定义、结构组成、特点等方面进行介绍和探讨。

主要内容如下:第一部分为引言部分,通过概述四层线路板的定义和应用领域,介绍四层线路板的重要性和研究的目的。

电路板叠层的设计原则及设计方式

电路板叠层的设计原则及设计方式电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1、每个走线层都必须有一个邻近的参考层(电源或地层);2、邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到十层板的叠层:2.1 单面板和双面板的叠层;对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:在同一层的电源走线以辐射状走线,并最小化线的长度总和;走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于线路板的厚度乘以信号线的长度。

2.2 四层板的叠层;推荐叠层方式:2.2.1 SIG-GND(PWR)-PWR (GND)-SIG;2.2.2 GND-SIG(PWR)-SIG(PWR)-GND;对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

pcb叠层参考

pcb叠层参考名词定义:SIG:信号层;GND:地层;PWR:电源层;电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到十层板的叠层:2.1 单面板和双面板的叠层;对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:1 在同一层的电源走线以辐射状走线,并最小化线的长度总和;2 走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于线路板的厚度乘以信号线的长度。

2.2 四层板的叠层;推荐叠层方式:2.2.1 SIG-GND(PWR)-PWR (GND)-SIG;2.2.2 GND-SIG(PWR)-SIG(PWR)-GND;对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

(完整word版)四层板层叠方案

(一)常用四层板层叠方案如图:(二)不同层叠方案分析方案1此方案为业界现行四层PCB主选层设置方案,在元件面下有一地平面,关键信号优选布TOP层;为了达到一定屏蔽效果,有人试图把电源、地平面放在TOP、BOTTOM层,即采用方案2:此方案为了达到想要屏蔽效果,至少存在以下缺陷:A、电源、地相距过远,电源平面阻抗较大B、电源、地平面由于元件焊盘等影响,极不完整C、由于参考面不完整,信号阻抗不连续在当前大量采用表贴器件,且器件越来越密情况下,本方案电源、地几乎无法作为完整参考平面,预期屏蔽效果很难实现;方案2使用范围有限。

但在个别单板中,方案2不失为最佳层设置方案。

以下为方案2在XX产品接口滤波板中使用案例;案例:在以太网交换机接口滤波板中,出现了以下情况:A,整板无电源平面;B,整板走线简单,但作为接口滤波板,布线辐射必须关注;C,该板贴片元件较少,多数为插件。

分析:1,由于该板无电源平面,电源地耦合无须考虑;2,由于贴片元件少,若表层做平面层,内层走线,参考平面完整性基本能得到保证,而且第二层可铺铜保证少量顶层走线参考平面;3,作为接口滤波板,PCB布线辐射必须关注,若内层走线,表层为GND,走线得到很好屏蔽,传输线辐射得到控制;鉴于以上原因,在本板层排布时,我们决定采用方案2,即:GND、S1、S2、GND,由于表层仍有少量短走线,而底层则为完整地平面,我们在S1布线层铺铜,保证了表层走线参考平面;列举以上特例,就是要告诉大家,要领会层排布原则,而非机械照搬。

方案3:此方案同方案1类似,适用于主要器件在BOTTOM布局或关键信号底层布线情况;一般情况下,限制使用此方案;(三)总结结论:优选方案1,可用方案3。