基于EDA技术的数字时钟设计

用EDA技术设计多功能数字钟

用EDA技术设计多功能数字钟摘要近年来,随着电子技术和通信技术的飞速发展,要求设计研究方面运用电子设计自动化(Electronic Design Automation,简称EDA)工具进行开发。

在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可靠性,减轻了设计者的劳动强度。

本设计为通过EDA仿真软件MAX+PLUSII设计一个多功能数字钟,并下载到硬件中实现。

本系统的设计电路由计时电路、动态显示电路、闹钟电路、控制电路、显示电路等部分组成。

本系统采用动态显示的原理在数码管上显示12小时计时的时刻,具有清零、保持、校时、报时的功能,并在此基础上增加了闹铃、秒表、12小时制计时、A/P显示等功能。

在设计过程中,将各部分均模块化,各模块间相互独立,又相互联系。

本实验吸收了硬件软件化的思想,大部分功能通过软件来实现,使电路简单明了,系统稳定性大大提高。

本系统不仅成功的实现了要求的基本功能,发挥部分也得到完全的实现,而且有一定的创新功能。

关键词数字钟、计数器、多功能、动态显示、原理图、仿真、模块化AbstractRecently, with the rapid development of electronic and communication technology, it is required to use Electronic Design Automation (EDA) as a tool in designing systems. EDA derives from the concepts of Computer Aided Design, Computer Aided Manufacture, Computer Aided Test and Computer Aided Engineering in the 1990s. Designers use Hardware Describe Language to accomplish designing files on the platform of software. Then, computer will finish the work of logical compiling, simplification, division, synthesis, optimizing, layout, tracking and simulating automatically, and it can also accomplish the work of proper compiling, logical projecting and downloading of the target chip. As a result, it evidently improves the efficiency and reliability of the circuit design, and it also lighten designer’s workload.This experiment has designed a multifunctional digital clock via using the MAX+PLUSII, and the basic and extended performances and functions are successfully realized in the hardware. This system includes time circuit, alarm circuit, dynamic display circuit, control circuit, display circuit. In the system, the segment display can display time in the 24-hour format, it includes such functions as clear, hold, check the time and so on. We can also add alarm, stopwatch, 12-hour format display and other functions on that basic. In the designing process, many parts are modularized, they are not only independent but also related. Many functions are finished by the software. So it simples the circuit and enhances the stability of the system. Not only all the basic and extended performances and functions are successfully realized, but also accomplish some innovation functions.KeywordsDigital clock, arithmometer, multifunctional, dynamic display,schematic diagram, simulate, modularization目录摘要 1ABSTRACT 11、前言62、EDA技术的介绍及发展 73、总体方案设计 93.1 设计内容 93.2 方案比较 (9)3.3 方案论证 (10)3.4 方案选择 104、多功能数字中的设计 124.1 课题要求 124.2 课题分析 12 4.3 功能实现 134.3.1 秒计时模块 144.3.2 分计时模块 164.3.3 小时计时模块 17 4.3.4 校时校分模块 194.3.5 整点报时模块 194.3.6 时段控制模块 204.3.7 连接各模块 214.4 下载过程 234.5 总结报告 265、设计总结 285.1 设计小结 28 5.2 设计收获 285.3 设计改进 286、致谢 287、参考文献 301、前言本课题研究的背景和目的:二十一世纪是信息化高速发展的世纪,产业的信息化离不开硬件芯片的支持。

基于EDA的数字电子钟设计

摘要数字时钟,就是以数字显示取代模拟表盘的钟表,在显示上它用数字反应此时的时间,它还能同时显示时,分,秒,且能够对时,分,秒准确进行校时。

数字时钟是一种用数字电路技术实现时、分、秒计时的装置。

与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,已得到广泛的使用。

数字钟从原理上讲是一种典型的数字电路,一般是由振荡器、分频器、计数器、显示器等几部分组成。

其中包括了组合逻辑电路和时序电路。

数字钟的设计方法有许多种,例如:可用中小规模集成电路组成电子钟;也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟;还可以利用单片机来实现电子钟等等。

本设计采用EDA技术,以硬件描述语言Verilog HDL为系统逻辑描述手段设计文件,在QUARTUS II工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的数字钟。

数字时钟以其体积小、重量轻、抗干扰能力强、对环境要求高、高精确性、容易开发等特性,在工业控制系统、智能化器仪表、办公自动化等诸多领域取得了极为广泛的应用,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、自动启闭路灯、定时开关烘箱、通断动力设备、甚至各种定时电气的自动启用等。

关键词:EDA、QuartusII、Verilog HDL、FPGA芯片、数字时钟等AbstractDigital clock is with digital display to replace analog dial watch, in the show it with digital reaction at this time, it can display at the same time, minutes and seconds, and can pair, minutes and seconds precise timing.Digital clock is a digital circuit technology to achieve time, minutes and seconds of the device. Compared with the mechanical clock has higher accuracy and intuitive, and no mechanical device, has a longer life, has been widely used. Digital clock from the principle of speaking is a typical digital circuit, generally by the oscillator, frequency divider, counter, display and other parts of the composition. The combination logic circuit and the sequential circuit are included in the circuit. Digital clock design, there are many methods. For example: available small scale integrated circuit composition electronic clock; can also use special chip electronic clock with to display circuit and its peripheral circuit composed of electronic clock; can also be used to achieve single-chip electronic clock and so on.This design using EDA technology, the Hardware Description Language Verilog HDL logic system description method of design documents, in the Quartus II software environment by top-down design method, by all the basic modules work together to build a based on FPGA digital clock.Digital clock with the volume small, light weight, strong anti-interference ability, on the environment requirements high, high precision, ease of development, and so on, in the fields of industrial control system, intelligent of instrumentation, office automation, made extremely widely used, such as timing automatic alarm, timely automatic bell, a time program automatic control, regular radio, automatic opening and closing lights, oven timer switch, on-off power equipment, and even a variety of timing electric automatically enabled.Keywords: EDA, QuartusII, Verilog HDL,FPGA chip, Digital clock, etc.摘要 (1)第一章绪论 (4)1.1选题意义与研究现状 (4)1.2国内外研究及趋势 (4)第二章EDA技术 (6)2.1 EDA技术简介 (6)2.2 EDA技术特点 (6)2.3 EDA技术的发展历程 (6)第三章 QuartusⅡ,FPGA的简介 (9)3.1 Quartus II简介 (9)3.2 FPGA简介 (9)3.3 FPGA系统设计流程 (11)3.4本设计所用黑金开发板AX301简介 (12)第四章数字时钟总体设计方案 (14)4.2 数字钟的工作原理 (14)第五章数字时钟的具体设计 (15)5.1 本设计的顶层图 (15)5.2 时钟控制模块 (15)5.2.1信号定义 (15)5.2.2分频模块 (16)5.2.3走时模块 (16)5.3显示模块 (20)第六章程序的验证与修改 (25)6.1程序导入 (25)6.2开发板演示 (25)第七章总结与展望 (27)7.1论文总结 (27)7.2后续展望 (27)致谢 ................................................................................................................... 错误!未定义书签。

(2023)EDA课程数字钟设计报告(一)

(2023)EDA课程数字钟设计报告(一)EDA课程数字钟设计报告设计目的本次设计的目的是通过使用EDA software,设计一个能够正常运行的数字钟,使其能够满足一定的时间显示功能。

设计思路本设计主要使用Verilog HDL编程语言,利用EDA software提供的仿真功能,模拟数字钟的运行过程。

具体实现过程如下:1.首先,设置时钟频率,并利用counter计数器进行计数,产生时间基准信号。

2.利用BCD编码对时间进行编码,分别将时、分、秒的数据传至显示器。

3.设计逻辑电路计算秒钟、分针、时钟转动角度。

4.在EDA software上进行仿真,观察数字钟是否正常工作。

设计图样以下为数字钟方案的部分设计图样。

image textimage text实现结果通过复杂的编程训练和模拟,数字钟设计的功能已经被确认。

数字钟电路能够准确地显示当前时间。

同时,数字钟的设计也具有较高的可靠性、稳定性和精度。

并且,数字钟的主板设计紧凑、易于集成。

这些优点使得本次设计非常适合应用于智能仪器、家庭用品和其他数字显示电子设备中。

总结数字钟设计是一项有挑战性的工程,需要设计人员具有充分的编程功底和深入的EDA工具熟练度。

本设计的成功,体现了设计团队的技术实力和团队协作能力,为未来的科技产品发展提供了有力的技术支撑。

改进方案虽然本设计实现了数字钟正常工作的功能,但是我们仍然可以从以下几个方面进行改进:1.在原有电路基础上增加闹钟功能,方便用户定时提醒。

2.增加显示背光,使数字钟更方便在夜间环境下使用。

3.将数字钟设计进行微小的改动使其更小巧便携,方便携带和使用。

参考文献1.微机原理与接口技术(第四版) 教材2.EDA Software (Xilinx ISE) 许可证书致谢在本次数字钟的设计过程中,我们向来自各地的优秀工程师团队表示感谢,感谢他们在繁忙的工作中,准确地指导我们的设计工作。

同时也感谢电子设计自动化(EDA) company提供的软件支持,使得我们能够顺利完成该设计。

EDA技术--数字电子钟的设计

电子信息工程专业项目化课程《EDA技术》项目二总结报告数字电子钟的设计班级姓名指导老师完成时间2010 年10 月 4 日项目二数字电子钟的设计一、概述设计一个具有校时、校分功能的能进行正常时、分、秒计时,分别有六个数码管显示时、分、秒的数字电子钟电路。

并具有整点报时功能。

二、项目要求1.实现60 进制分、秒和24进制时的计时功能。

2.由六个数码管动态显示时、分、秒。

3.通过按键实现校时、校分功能。

4.能利用蜂鸣器实现整点报时,59分50秒开始报时,整点结束。

5.用层次化(模块化)设计方法设计总电路,用VHDL语言编写各个功能模块。

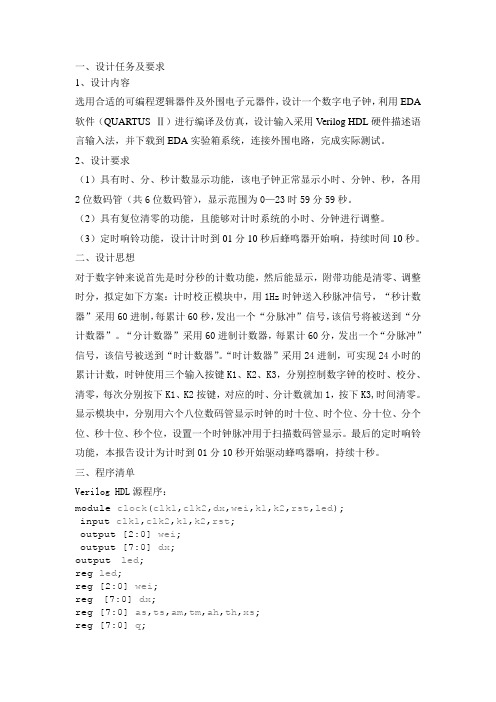

6.用EDA实训系统下载验证三、数字时钟总电路设计11223344DDCCBBAATitleNumberRevisionSize A4Date:2010-11-16Sheet of File:C:\My Documents\..\SHEET1.SCHDOC Drawn By:S1S2S3S4Speaker LS10KRes2R110K R210K R310K R42N3904Q210KR71KR8D1D2D3D4VCCVCC CLK1IN 2DEV_CLR 3DATA75DATA66DATA57DATA48DATA39DATA210DATA111DATA012DCLK 13n C E14TDI 15I/O 16I/O 17I/O 18I/O 19I/O 21I/O 22I/O 23I/O 24I /O25I /O 27I /O 28I /O 29I /O 30MSEL031MSEL132nCONFIG 34I /O 35I /O 36I /O 37I /O38I /O 39CLK 43IN 44I /O 47I /O 48I /O 49I /O 50I /O 51I /O 52I /O53I /O 54nSTATUS 55TRST 56TMS 57I /O 58I /O 59I /O 60I /O61I /O 62I /O 64I /O 65I /O 66I /O 67INIT_DONE 69RDYnBUSY 70I /O 71I /O 72CLKUSR 73TDO 74n C E O 75CONF_DONE 76TCK 77nCS 78CS 79nWS 80nRS 81DEV_OE83IN 84V C C I N T4V C C I N T 20G N D I N T26V C C I N T 33V C C I N T 40G N D I N T 41V C C I N T 45G N D I N T 46V C C I N T 63G N D I N T 68G N D I N T 82IN 42EPF10K10LC84-3U0OED1Q1D2Q2D3Q3D4Q4D5Q5D6Q6D7Q7D8Q8VCCGND 74LS244U1VCC A 1B 2C 3OE2A 4OE2B5OE16Y77GND8Y69Y510Y411Y312Y213Y114Y015VCC 16SN74LS138DU4Y0Y1Y2Y5Y3Y4VCCW0W1W2W 1W 2W 0QA QB QC QD QE QF QG VCC VCCA0A1A2A3A4A5A6A7A 0A 1A 2A 3A 4A 5A 6A 7QD 7QE 5QF 4QG 6QH 14QI 13QJ 15QL 1QM 2QN 3/CKO 10CKO9CLR12CKI11CD4060BU3V C C 1N C 2C O U N T 3G N D4U2VCC1024HZ 1024HZ 9123456781KPR1T M S T D I T D 0T CKNetLabel2y 0Y 1Q A Q B Q C Q D Q E Q F Q GY 2Y 3Y 5Y 4Q A Q C Q B Q D Q E Q GQ F A B C D E F G D P C 1C 2DS2Dpy Red-CAA B C D E F G D 1D 2D 3D 4D P DS1Dpy Red-CB12Header 2JP112Header 2JP21234567891110D Connector 9J1680R4D110KR5VCCl9nCONFIG VCCDLCK DAT nSTATUS CONF_DONE k1100pFCap C1nCONFIG nSTATUS DCLK CONF DONE四、VHDL语言编程设计4.1、60进制设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jinzhi60 isport (ctp,nreset,clk1s:in std_logic;co:out std_logic;qhh:out std_logic_vector(3 downto 0);qll:out std_logic_vector(3 downto 0));end jinzhi60;architecture behave of jinzhi60 issignal ql,qh:std_logic_vector(3 downto 0);beginco<='1' when (qh="0101" and ql="1001" and ctp='1') else'0'; process(clk1s,nreset,ctp)beginif(nreset='0')thenqh<="0000";ql<="0000";elsif(clk1s' event and clk1s='1')thenif(ctp='1')thenif (qh="0101" and ql="1001")thenqh<="0000";ql<="0000";elsif(ql<9)thenql<=ql+1;elseql<="0000";end if;end if;end if;qhh<=qh; qll<=ql;end process;end behave;4.2、24进制设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jinzhi24 isport (ctp,nreset,clk1s:in std_logic;co:out std_logic;qhh:out std_logic_vector(3 downto 0);qll:out std_logic_vector(3 downto 0));end jinzhi24;architecture behave of jinzhi24 issignal ql,qh:std_logic_vector(3 downto 0);beginco<='1' when (qh="0101" and ql="1001" and ctp='1') else'0'; process(clk1s,nreset,ctp)beginif(nreset='0')thenqh<="0000";ql<="0000";elsif(clk1s' event and clk1s='1')thenif(ctp='1')thenif (qh="0101" and ql="1001")thenql<="0000";elsif(ql<9)thenql<=ql+1;elseql<="0000";qh<=qh+1;end if;end if;end if;qhh<=qh; qll<=ql;end process;end behave;4.3、动态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity datm isport(clk:in bit;a,b,c,d,e,f:in std_logic_vector(3 downto 0);w:out std_logic_vector(2 downto 0);q:out std_logic_vector(6 downto 0));end datm;architecture wei of datm issignal qq:std_logic_vector(3 downto 0);signal cntt:std_logic_vector(2 downto 0);beginprocess(clk)variable cnt:std_logic_vector(2 downto 0);beginif clk'event and clk='1' thenif cnt<5 then cnt:=cnt+1;else cnt:="000";end if;cntt <=cnt;case cnt iswhen "000"=>qq<=a;when "001"=>qq<=b;when "010"=>qq<=c;when "011"=>qq<=d;when "100"=>qq<=e;when "101"=>qq<=f;when others=>null;end case;end if;end process;process(qq)beginw<=cntt;case qq iswhen "0000"=>q<="1111110";when "0001"=>q<="0110000";when "0010"=>q<="1101101";when "0011"=>q<="1111001";when "0100"=>q<="0110011";when "0101"=>q<="1011011";when "0110"=>q<="1011111";when "0111"=>q<="1011111";when "1000"=>q<="1110000";when "1001"=>q<="1111111";when "1010"=>q<="1111011";when "1011"=>q<="1110111";when "1100"=>q<="0011111";when "1101"=>q<="1001110";when "1110"=>q<="1001111";when "1111"=>q<="1000111";when others=>q<="0000000"; end case;end process;end wei;4.5、1000分频设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity datm1000 isport(clk:in std_logic;co:out std_logic);end datm1000;architecture behave of datm1000 is beginprocess(clk)variable cn:integer:=0;beginif (clk'event and clk='1') thenif (cn<999) thencn:=cn+1;co<='0';elsecn:=0;co<='1';End if;end if;End process;end behave;4.6、校时、校分电路library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity xuanz isport (b,n,m:in std_logic;qo:out std_logic);end xuanz;architecture beha of xuanz is beginprocess(b,n,m)beginif (m='1') thenqo<=b;elseqo<=n;end if;end process;end beha;4.7、报时电路library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity baoshi isport (m1,m0,s1,s0: in std_logic_vector(3 downto 0);clk:in std_logic;q: out std_logic);end baoshi;architecture rtl of baoshi isbeginprocess(clk)variable c0 :std_logic_vector(2 downto 0);beginif clk'event and clk='1' thenif m1="0101"and m0="1010" and s1="0101" thenc0:=c0+1;if s0="0000"or s0="0010"or s0="0100" or s0="0110" or s0="1000"then q<='0';elseq<='1';end if;elseq<='1';end if;end if;end process;end rtl;五、总电路框图5.1 引脚设置首先使用软件选择对应的实验箱芯片:Assign>>Device 选择FLEX10K>>EPF10K10LC84-3,然后OK。

基于EDA技术的数字电子时钟设计修改

EDA技术实现的数字电子钟设计摘要电子设计自动化 Electronic Design Automation (以下简称EDA)技术已经代替传统的集成电路设计方法,逐渐成为电子系统设计者的主要设计手段。

MAXplusⅡ是EDA仿真软件之一。

具有功能强大、界面友好和使用方便等特点,是目前教育与工业界流行的集成电路辅助设计软件。

MAXplusⅡ是一种在电子技术工程与电子技术教学中广泛应用的优秀计算机仿真软件,被誉为“计算机里的电子实验室”。

本文介绍了一种基于MAXplusⅡ软件设计数字电子钟的方法。

关键词EDA MAXplusⅡ软件数字电子钟目录引言 (1)第一章 EDA概论 (2)1.1EDA技术概述 (2)1.2 EDA在数字电路课程设计中的必要性 (2)1.3 MAXplusⅡ概述 (3)1.4 设计电子钟的可行性分析 (3)第二章设计依据 (4)2.1设计总体方案 (4)2.2设计原理 (4)2.3 设计目标和方法 (4)第三章 EDA电子钟系统设计 (5)3.1电子钟的功能分析、总体规划 (5)3.1.1电子钟功能分析 (5)3.1.2总体规划 (5)3.2使用MAXplusⅡ作为数字电子钟设计平台 (5)3.2.1 MAXplusⅡ软件仿真特点 (5)3.2.2 MAXplusⅡ介绍 (6)3.3 单元电路设计与分析 (6)3.3.1石英晶体振荡器 (6)3.3.2分频电路 (7)3.3.3秒、分计数电路 (8)3.3.4时计数电路 (9)3.3.5校时电路 (10)3.3.6整点报时电路 (10)3.3.7定时闹钟 (12)第四章MAXplusⅡ电子钟仿真结果 (15)4.1MAXplusⅡ电子钟基本功能仿真结果 (15)4.2 MAXplusⅡ电子钟扩展功能仿真结果 (15)4.3 MAXplusⅡ电子钟整体仿真结果 (15)结束语 (17)参考文献 (18)引言随着计算机在国内的逐渐普及,计算机已经深入到每一个行业,计算机与每个工作领域紧密地联系在了一起。

毕业设计21基于EDA技术的数字电子时钟设计

单片机应用系统开发过程

1.2

应用系统硬件设计方法

通常,硬件设计应遵循以下原则: 1) 尽可能选择标准化、模块化的典型电路,提高设计

的成功率和结构的灵活性;

2) 系统扩展和配置应充分满足系统功能要求,并留有

余地,以便进行二次开发; 3)系统中相关的元器件应尽可能做到性能匹配; 4) 要考虑系统的抗干扰能力,硬件、软件要作抗干扰 设计,以使系统能可靠、正常的运行。

1.1.1 应用系统设计要求

其中,适用、可靠、经济最为重要。对于一个应用系 统的设计要求,应根据具体任务和实际情况进行分析后提 出。

单片机应用系统开发过程

1.1.2 应用系统设计步骤

单片机应用系统类型很多,用途和功能各异,因而构

成系统硬件和软件也不相同;但就系统的设计方法和步骤 来说,却是基本相同的。如图1-1所示。

单片机应用系统开发过程

1.1.2 应用系统设计步骤

(4)硬件和软件的功能划分

系统的硬件配置和软件设计是紧密联系的,硬件和软 件有一定的互换性。有些硬件的功能可以由软件完成,有 些软件功能也可以由硬件完成。用硬件可以提高工作速度, 但成本增加;软件可以降低硬件成本,但编程复杂,且占 用CPU时间。因此,在总体设计时,对系统的硬件、软件都 应有全面的了解,综合考虑以上因素,合理搭配软 /硬件的 比重。

1.1.2 应用系统设计步骤

(1)系统构成方案选择 由单片机构成的应用系统,通常有两种方式可供选择。

1) 专用系统。系统的扩展和配置电路完全按照应用系 统功能要求设计,系统的硬件、软件资源获得充分利用。 这种系统有最佳配置,体积小,结构紧凑,性价比较高, 因而系统设计常采用这种方式。

单片机应用系统开发过程

单片机应用系统开发过程

EDA数字钟毕业设计

EDA数字钟毕业设计第一篇:EDA数字钟毕业设计[ 标签:数字钟, eda ]1、设计一个能显示1/10秒、秒、分、时的12小时数字钟。

2、时钟源使用频率为0.1Hz的连续脉冲。

3、设置两个按钮,一个供“开始”及“停止”用,一个供系统“复位”用。

4、时钟显示使用数码管显示。

基于VHDL的多功能数字钟的设计EDA课程设计资料类别课程(专业)EDA 适用年级大学文件格式word+DLS 文件大小1725K 上传时间2008-10-10 20:57:00 预览文件无(只能预览文件中的部分内容)下载次数0内容简介:EDA课程设计基于VHDL的多功能数字钟的设计,共11页,6086字,附源程序。

摘要:介绍了利用VHDL硬件描述语言设计的多功能数字钟的思路和技巧。

在MAX+PLUSII开发环境中编译和仿真了所设计的程序,并在可编程逻辑器件上下栽验证。

仿真和验证结果表明,该设计方法切实可行。

EDA-时钟设计-基于Altera数字钟的实现:EDA课程设计基于VHDL的多功能数字钟的设计:EDA数字钟设计报告:资料包括:论文(12页2036字)图纸说明:中文摘要:数字钟学习的目的是掌握各类计数器及它们相连的设计方法;掌握多个数码管显示的原理与方法;掌握FPGA技术的层次化设计方法;掌握用VHDL语言的设计思想以及整个数字系统的设计。

此数字钟设计具有时,分,秒计数显示功能,以24小时为计数循环;能实现清零,调节小时,分钟以及整点报时的功能。

第二篇:eda数字钟程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY clock IS PORT(EN :IN STD_LOGIC;数码管使能CLK:IN STD_LOGIC;时钟信号RST:IN STD_LOGIC;复位信号SEC_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);秒高位SEC_01 :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);秒低位MIN_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);分高位MIN_01 :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);分低位HOU_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);时高位HOU_01 :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);时低位BEE:OUT STD_LOGIC);END clock;ARCHITECTURE behovior OF clock IS SIGNAL SEC_HIGH:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL SEC_LOW:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL MIN_HIGH:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL MIN_LOW:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL HOU_HIGH:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL HOU_LOW:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL CY_MIN:STD_LOGIC;分进位SIGNAL CY_HOU:STD_LOGIC;时进位SIGNAL LOGO_1:STD_LOGIC;标志SIGNAL LOGO_2:STD_LOGIC;SIGNAL LOGO_3:STD_LOGIC;BEGIN MIAOLOW:PROCESS(CLK,RST,EN)BEGINIF(RST = '0')THENSEC_LOW <= “1000”;附给秒低位为8ELSIF(CLK'EVENT AND CLK = '1' AND EN = '1')THEN 检测时钟上升沿及数码管使能端IF(SEC_LOW = “1001”)THENSEC_LOW <= “0000”;ELSESEC_LOW <= SEC_LOW + “0001”;加一END IF;END IF;END PROCESS MIAOLOW;LOGO_1 <= SEC_LOW(3)AND SEC_LOW(0);SEC_01<= SEC_LOW;秒个位放8MIAOHIGH:PROCESS(CLK,RST)BEGINIF(RST = '0')THENSEC_HIGH <= “0101”;ELSIF(CLK'EVENT AND CLK = '1')THEN检测时钟上升沿IF(LOGO_1 = '1')THENIF(SEC_HIGH = “0101”)THENSEC_HIGH <= “0000”;CY_MIN <= '1';ELSESEC_HIGH <= SEC_HIGH + “0001”;加一CY_MIN <= '0';END IF;END IF;END IF;END PROCESS MIAOHIGH;SEC_1 <= SEC_HIGH;秒十位放5FENLOW:PROCESS(CY_MIN,RST,EN)BEGINIF(RST = '0')THEN 若复位位为0MIN_LOW <= “1000”;则分个位为8ELSIF(CY_MIN'EVENT AND CY_MIN = '1' AND EN = '1')THEN 检测时钟上升沿及数码管使能端IF(MIN_LOW = “1001”)THENMIN_LOW <= “0000”;ELSEMIN_LO W <= MIN_LOW + “0001”;加一END IF;END IF;END PROCESS FENLOW;LOGO_2 <= MIN_LOW(3)AND MIN_LOW(0);MIN_01 <= MIN_LOW;分个位放8FENHIGH:PROCESS(CY_MIN,RST)BEGINIF(RST = '0')THENMIN_HIGH <= “0101”;ELSIF(CY_MIN'EVENT AND CY_MIN = '1')THEN检测分进位上升沿IF(LOGO_2 = '1')THENIF(MIN_HIGH = “0101”)THEN若分十位为5MIN_HIGH <= “0000”;CY_HOU <= '1';时进位为1ELSEMIN_HIGH <= MIN_HIGH + “0001”;加一CY_HOU <= '0';END IF;END IF;END IF;END PROCESS FENHIGH;MIN_1 <= MIN_HIGH;分十位放5SHILOW:PROCESS(CY_HOU,RST,EN)BEGINIF(RST = '0')THENHOU_LOW <= “1001”;ELSIF(CY_HOU'EVENT AND CY_HOU = '1'AND EN = '1')THEN检测时进位上升沿及数码管使能端IF(HOU_LOW = “1001”)THEN若时低位为9HOU_LOW <= “0000”;ELSIF(HOU_HIGH = “0010” AND HOU_LOW = “0011”)THEN若时十位为2,个位为3HOU_LOW <= “0000”;ELSEHOU_LOW <= HOU_LOW + “0001”;加一END IF;END IF;END PROCESS SHILOW;LOGO_3 <= HOU_LOW(3)AND HOU_LOW(0);HOU_01 <= HOU_LOW;时个位放3SHIHIGH:PROCESS(CY_HOU,RST)BEGINIF(RST = '0')THENHOU_HIGH <= “0001”;ELSIF(CY_HOU'EVENT AND CY_HOU = '1')THEN检测时进位上升沿IF(HOU_HIGH = “0010” AND HOU_LOW = “0011”)THEN 若时十位为2,时个位为3HOU_HIGH <= “0000”;ELSIF(LOGO_3 = '1')THENHOU_HIGH <= HOU_HIGH + “0001”;加一END IF;END IF;END PROCESS SHIHIGH;BEE_CLOCK:PROCESS(CLK)BEGINIF(CLK'EVENT AND CLK = '1')THEN检测时钟上升沿IF(SEC_HIGH = “0101” AND SEC_LOW = “1001”AND MIN_HIGH = “0101” AND MIN_LOW = “1001”)THENBEE <= '1';ELSEBEE <= '0';END IF;END IF;END PROCESS BEE_CLOCK;HOU_1 <= HOU_HIGH;时十位放2END behovior;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY clock1 IS PORT(EN :IN STD_LOGIC;CLK:IN STD_LOGIC;RST:IN STD_LOGIC;SEC_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);SEC_01 :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);MIN_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);MIN_01 :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);HOU_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);HOU_01 :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);BEE:OUT STD_LOGIC);END clock1;ARCHITECTURE behovior OF clock1 IS SIGNAL SEC_HIGH:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL SEC_LOW:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL MIN_HIGH:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL MIN_LOW:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL HOU_HIGH:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL HOU_LOW:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL CY_MIN:STD_LOGIC;SIGNAL CY_HOU:STD_LOGIC;SIGNAL LOGO_1:STD_LOGIC;SIGNAL LOGO_2:STD_LOGIC;SIGNAL LOGO_3:STD_LOGIC;BEGIN MIAOLOW:PROCESS(CLK,RST,EN)BEGINIF(RST = '0')THENSEC_LOW <= “1000”;ELSIF(CLK'EVENT AND CLK = '1' AND EN = '1')THEN IF(SEC_LOW = “1001”)THENSEC_LOW <= “0000”;ELSESEC_LOW <= SEC_LOW + “0001”;END IF;END IF;END PROCESS MIAOLOW;LOGO_1 <= SEC_LOW(3)AND SEC_LOW(0);SEC_01<= SEC_LOW;MIAOHIGH:PROCESS(CLK,RST)BEGINIF(RST = '0')THENSEC_HIGH <= “0101”;ELSIF(CLK'EVENT AND CLK = '1')THENIF(LOGO_1 = '1')THENIF(SEC_HIGH = “0101”)THENSEC_HIGH <= “0000”;CY_MIN <= '1';ELSESEC_HIGH <= SEC_HIGH + “0001”;CY_MIN <= '0';END IF;END IF;END IF;END PROCESS MIAOHIGH;SEC_1 <= SEC_HIGH;FENLOW:PROCESS(CY_MIN,RST,EN) BEGINIF(RST = '0')THENMIN_LOW <= “1000”;ELSIF(CY_MIN'EVENT AND CY_MIN = '1' AND EN = '1')THEN IF(MIN_LOW = “1001”)THENMIN_LOW <= “0000”;ELSEMIN_LOW <= MIN_LOW + “0001”;END IF;END IF;END PROCESS FENLOW;LOGO_2 <= MIN_LOW(3)AND MIN_LOW(0);MIN_01 <= MIN_LOW;FENHIGH:PROCESS(CY_MIN,RST)BEGINIF(RST = '0')THENMIN_HIGH <= “0101”;ELSIF(Cy_MIN'EVENT AND CY_MIN = '1')THENIF(LOGO_2 = '1')THENIF(MIN_HIGH = “0101”)THENMIN_HIGH <= “0000”;CY_HOU <= '1';ELSEMIN_HIGH <= MIN_HIGH + “0001”;CY_HOU <= '0';END IF;END IF;END IF;END PROCESS FENHIGH;MIN_1 <= MIN_HIGH;SHILOW:PROCESS(CY_HOU,RST,EN)BEGINIF(RST = '0')THENHOU_LOW <= “1001”;ELSIF(CY_HOU'EVENT AND CY_HOU = '1' AND EN = '1')THEN IF(HOU_LOW = “1001”)THENHOU_LOW <= “0000”;ELSIF(HOU_HIGH = “0010” AND HOU_LOW = “0011”)THENHOU_LOW <= “0000”;ELSEHOU_LOW <= HOU_LOW + “0001”;END IF;END IF;END PROCESS SHILOW;LOGO_3 <= HOU_LOW(3)AND HOU_LOW(0);HOU_01 <= HOU_LOW;SHIHIGH:PROCESS(Cy_HOU,RST)BEGINIF(RST = '0')THENHOU_HIGH <= “0001”;ELSIF(CY_HOU'EVENT AND CY_HOU = '1')THENIF(HOU_HIGH = “0010” AND HOU_LOW = “0011”)THEN HOU_HIGH <= “0000”;ELSIF(LOGO_3 = '1')THENHOU_HIGH <= HOU_HIGH + “0001”;END IF;END IF;END PROCESS SHIHIGH;BEE_CLOCK:PROCESS(CLK)BEGINIF(CLK'EVENT AND CLK = '1')THENIF(SEC_HIGH = “0101” AND SEC_LOW = “1001”AND MIN_HIGH = “0101” AND MIN_LOW = “1001”)THENBEE <= '1';ELSEBEE <= '0';END IF;END IF;END PROCESS BEE_CLOCK;HOU_1 <= HOU_HIGH;END behovior;第三篇:EDA数字钟课程设计课程设计报告设计题目:用VHDL语言实现数字钟的设计班级:电子1002班学号:20102625 姓名:于晓指导教师:李世平、李宁设计时间:2012年12月摘要数字钟是一种用数字电路技术实现时、分、秒计时的钟表。

基于eda的数字钟程序设计

基于e d a的数字钟程序设计文件编码(GHTU-UITID-GGBKT-POIU-WUUI-8968)一、课题要求:(1)技术要求:1、掌握多功能数字钟的工作原理。

2、应用EDA技术,VHDL语言编写程序。

3、层次化设计,设计原理框图。

4,、硬件设计及排版。

(2)功能要求:1、基本功能:能进行正常的时、分、秒计时功能,分别由6个数码管显示24小时、60分钟、60秒的计数器显示。

2、扩展功能:(1)能够利用按键实现“校时”“校分”“清零”功能。

(2)能利用扬声器做整点报时,整点前五秒短声,整点长声。

(3)本人工作:负责软件部分,,编写各部分模块的VHDL程序,并且锁定引脚,将程序下载到芯片中。

二、设计方案:原理框图:数字钟原理框图一共有11个小模块:分频,片选,按键,小时,分,秒,显示模块,七段显示译码器,报时,扬声,36译码器。

左边第一个是时钟信号输入端,50Mhz到分频模块。

第二个为清零按键,第三个为校分按键,第四个为校时按键。

右边第一个为七段显示译码器输出端,第二个为扬声器输出端,第三个为6个数码管输出端。

中间模块为数字钟的核心,有计时,报时,校时功能。

三、单元模块设计1、分频模块2、秒模块仿真图为秒的数值,在计时到59时进位1到co端。

当按下s3时,秒清零。

3.、分模块仿真图该模块也为60进制计数器,计时输出为分的数值。

在EN信号有效且时钟来时,计数器加1、在s2按下时,EN使能端有效,实现校分功能。

4、时模块仿真图该模块为24进制计数器,计时输出为小时的数值,在EN信号到来时,计数器加1,在S1按下时,EN信号有效,实现校时功能。

5、片选模块仿真图该模块提供数码管片选信号。

6、按键模块仿真图该模块是有几个门电路组成,把它编写成一个模块,到时写程序方便。

该模块连接几个按键,由按键控制。

7、报时模块仿真图该模块为整点报时提供控制信号,当59分时,秒为50,52,54,56,58时,Q500输出“1”;秒为00时,Q1000输出“1”。

EDA数字时钟设计报告

EDA课程设计报告设计题目:数字时钟班级:姓名:学号:日期:一、系统设计要求设计一个具有整点报时功能的数字时钟,要求;1.具有时、分、秒的计数显示功能,24小时循环显示。

2.具有清零、预置初值功能,实现LED动态显示,整点报时采用声音报时。

3.采用元件例化方式实现各模块间的连接。

二、系统设计方案要设计的数字时钟具有基本的计时功能,采用二十四小时计时,显示时分秒,其中分钟和秒模块采用60进制计数器实现,小时模块则需要一24进制计数器实现。

要实现时钟预置初值功能分别设计一个分钟允许置数端和小时允许置数端。

要实现LED动态显示,单独设计一个显示模块。

整点报时采用隔秒响一声实六十进制计数器模块二十四进制计数器模块显示模块元器件例化模块三、主要VHDL源程序六十进制计数器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY liushijinzhi ISPORT(clk,clr,en,a: IN STD_LOGIC;load_1,load_10: IN STD_LOGIC_VECTOR(3 DOWNTO 0); co: OUT STD_LOGIC;q_10,q_1: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END liushijinzhi;ARCHITECTURE behav OF liushijinzhi ISSIGNAL q1:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL q10:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL c:STD_LOGIC;BEGINPROCESS(clk,clr,a,en,load_1)BEGINIF(clr='1') THENq1<="0000";ELSIF(a='1') THENq1<=load_1;ELSIF(clk'event AND clk='1') THENIF(en='1')thenIF(q1="1001") THENq1<="0000";c<='0';ELSIF(q1="1000") THENq1<=q1+'1';c<='1';ELSEq1<=q1+'1';c<='0';END IF;END IF;END IF;END PROCESS;PROCESS(c,clk,clr,a,load_10)BEGINIF(clr='1') THENq10<="0000";ELSIF(a='1') THENq10<=load_10;ELSIF (clk'event AND clk='1') THENIF(c='1') THENIF(q10="0101") THENq10<="0000";co<='1';ELSEq10<=q10+'1';co<='0';END IF;END IF;END IF;END PROCESS;PROCESS(q1)BEGINCASE q1 ISWHEN"0000"=>q_1<="1111110";WHEN"0001"=>q_1<="0110000";WHEN"0010"=>q_1<="1101101";WHEN"0011"=>q_1<="1111001";WHEN"0100"=>q_1<="0110011";WHEN"0101"=>q_1<="1011011";WHEN"0110"=>q_1<="0011111";WHEN"0111"=>q_1<="1110000";WHEN"1000"=>q_1<="1111111";WHEN"1001"=>q_1<="1110011";WHEN OTHERS=>q_1<="ZZZZZZZ";END CASE;END PROCESS;PROCESS(q10)BEGINCASE q10 ISWHEN"0000"=>q_10<="1111110";WHEN"0001"=>q_10<="0110000";WHEN"0010"=>q_10<="1101101";WHEN"0011"=>q_10<="1111001";WHEN"0100"=>q_10<="0110011";WHEN"0101"=>q_10<="1011011";WHEN OTHERS=>q_10<="ZZZZZZZ";END CASE;END PROCESS;END behav;二十四进制计数器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ershisijinzhi ISPORT(clk,clr,en,a:IN STD_LOGIC;load_1,load_10:IN STD_LOGIC_VECTOR(3 DOWNTO 0); q_1,q_10:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END ershisijinzhi;ARCHITECTURE behav OF ershisijinzhi ISSIGNAL c:STD_LOGIC;SIGNAL q1:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL q10:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk,clr,en,a,load_1)BEGINIF(clr='1') THENq1<="0000";ELSIF (a='1') THENq1<=load_1;ELSIF(clk'event AND clk='1') THENIF(q1="0011" AND q10="0010") THENq1<="0000";ELSIF (en='1') THENIF(q1="1001") THENq1<="0000";c<='0';ELSIF(q1="1000") THENq1<=q1+'1';c<='1';ELSEq1<=q1+'1';c<='0';END IF;END IF;END IF;END PROCESS;PROCESS(clk,clr,c,a,q1,load_10)BEGINIF(clr='1') THENq10<="0000";ELSIF (a='1') THENq10<=load_10;ELSIF(clk'event AND clk='1') THENIF(q1="0011" AND q10="0010") THEN q10<="0000";ELSIF (c='1') THENIF(q10="0010") THENq10<="0000";ELSEq10<=q10+'1';END IF;END IF;END IF;END PROCESS;PROCESS(q1)BEGINCASE q1 ISWHEN"0000"=>q_1<="1111110"; WHEN"0001"=>q_1<="0110000"; WHEN"0010"=>q_1<="1101101"; WHEN"0011"=>q_1<="1111001";WHEN"0100"=>q_1<="0110011";WHEN"0101"=>q_1<="1011011";WHEN"0110"=>q_1<="0011111";WHEN"0111"=>q_1<="1110000";WHEN"1000"=>q_1<="1111111";WHEN"1001"=>q_1<="1110011";WHEN OTHERS=>q_1<="ZZZZZZZ";END CASE;END PROCESS;PROCESS(q10)BEGINCASE q10 ISWHEN"0000"=>q_10<="1111110";WHEN"0001"=>q_10<="0110000";WHEN"0010"=>q_10<="1101101";WHEN OTHERS=>q_10<="ZZZZZZZ";END CASE;END PROCESS;END behav;显示模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY qdmkz ISPORT(clk,clr:IN STD_LOGIC;din1,din2,din3,din4,din5,din6:IN STD_LOGIC_VECTOR(6 DOWNTO 0); sel:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);num:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END qdmkz;ARCHITECTURE behav OF qdmkz ISSIGNAL q :STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINsel<=q;PROCESS(clk,clr)BEGINIF(clr='1') THENq<="101";ELSIF(clk'event AND clk='1') THENIF(q="000") THENq<="101";ELSEq<=q-'1';END IF;END IF;END PROCESS;PROCESS(q,din1,din2,din3,din4,din5,din6)BEGINCASE q ISWHEN "101"=>num<=din1;WHEN "100"=>num<=din2;WHEN "011"=>num<=din3;WHEN "010"=>num<=din4;WHEN "001"=>num<=din5;WHEN "000"=>num<=din6;WHEN OTHERS=>num<="ZZZZZZZ";END CASE;END PROCESS;END behav;元器件例化模块含报时LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY shuzishizhong ISPORT(clk1,clk2,clrh,clrm,clrs,clr,ah,am,as,en:IN STD_LOGIC;load_1,load_10:IN STD_LOGIC_VECTOR(3 DOWNTO 0);sel:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);num:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);alm:OUT STD_LOGIC);END shuzishizhong;ARCHITECTURE one OF shuzishizhong ISCOMPONENT liushijinzhi ISPORT(clk,clr,en,a: IN STD_LOGIC;load_1,load_10: IN STD_LOGIC_VECTOR(3 DOWNTO 0);co: OUT STD_LOGIC;q_10,q_1: OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;COMPONENT ershisijinzhi ISPORT(clk,clr,en,a:IN STD_LOGIC;load_1,load_10:IN STD_LOGIC_VECTOR(3 DOWNTO 0);q_1,q_10:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;COMPONENT qdmkz ISPORT(clk,clr:IN STD_LOGIC;din1,din2,din3,din4,din5,din6:IN STD_LOGIC_VECTOR(6 DOWNTO 0);sel:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);num:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;SIGNAL co1,co2:STD_LOGIC;SIGNAL sq_1,sq_10,mq_1,mq_10,hq_1,hq_10:STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINu1:liushijinzhi PORT MAP (clk1,clrs,en,as,load_1,load_10,co1,sq_10,sq_1);u2:liushijinzhi PORT MAP (co1,clrm,en,am,load_1,load_10,co2,mq_10,mq_1);u3:ershisijinzhi PORT MAP (co2,clrh,en,ah,load_1,load_10,hq_1,hq_10);u4:qdmkz PORT MAP(clk2,clr,hq_10,hq_1,mq_10,mq_1,sq_10,sq_1,sel,num);PROCESS(sq_10,sq_1,mq_10,mq_1,hq_10,hq_1)BEGINIF(((hq_10="1111110" AND hq_1="1111110")OR(hq_10="0110000" AND hq_1="1101101")) AND mq_1="1111110"AND mq_10="1111110" AND ((sq_10="1111110"AND(sq_1="1111110"OR sq_1="1101101"OR sq_1="0110011"OR sq_1="0011111"OR sq_1="1111111"))OR(sq_10="0110000"AND(sq_1="1111110"OR sq_1="1101101"OR sq_1="0110011"OR sq_1="0011111"OR sq_1="1111111")) OR(sq_10="1101101"AND(sq_1="1111110"OR sq_1="1101101")))) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="0110000") OR (hq_10="0110000" AND hq_1="1111001")) AND mq_1="1111110"ANDmq_10="1111110" AND sq_10="1111110"AND sq_1="1111110") THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="1101101") OR (hq_10="0110000" AND hq_1="0110011")) AND mq_1="1111110"ANDmq_10="1111110" AND sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101")) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="1111001") OR (hq_10="0110000" AND hq_1="1011011")) AND mq_1="1111110"ANDmq_10="1111110" AND sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011")) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="0110011") OR (hq_10="0110000" AND hq_1="0011111")) AND mq_1="1111110"ANDmq_10="1111110" AND sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111")) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="1011011") OR (hq_10="0110000" AND hq_1="1110000")) AND mq_1="1111110"AND mq_10="1111110"AND sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111"OR sq_1="1111111")) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="0011111") OR (hq_10="0110000" AND hq_1="1111111")) AND mq_1="1111110"AND mq_10="1111110"AND ((sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111"OR sq_1="1111111"))OR(sq_10="0110000"AND sq_1="1111110"))) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="1110000") OR (hq_10="0110000" AND hq_1="1110011")) AND mq_1="1111110"AND mq_10="1111110"AND ((sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111"OR sq_1="1111111"))OR(sq_10="0110000"AND (sq_1="1111110"OR sq_1="1101101")))) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="1111111") OR (hq_10="1101101" AND hq_1="1111110")) AND mq_1="1111110"AND mq_10="1111110"AND ((sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111"OR sq_1="1111111"))OR(sq_10="0110000"AND (sq_1="1111110"OR sq_1="1101101" OR sq_1="0110011")))) THENalm<='1';ELSIF(((hq_10="1111110" AND hq_1="1110011") OR (hq_10="1101101" AND hq_1="0110000")) AND mq_1="1111110"AND mq_10="1111110"AND ((sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111"OR sq_1="1111111"))OR(sq_10="0110000"AND (sq_1="1111110"OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111")))) THENalm<='1';ELSIF(((hq_10="0110000" AND hq_1="1111110") OR (hq_10="1101101" AND hq_1="1101101")) AND mq_1="1111110"AND mq_10="1111110"AND ((sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111"OR sq_1="1111111"))OR(sq_10="0110000"AND (sq_1="1111110"OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111" OR sq_1="1111111")))) THENalm<='1';ELSIF(((hq_10="0110000" AND hq_1="0110000") OR (hq_10="1101101" AND hq_1="1111001")) AND mq_1="1111110"AND mq_10="1111110"AND ((sq_10="1111110"AND (sq_1="1111110" OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111"OR sq_1="1111111"))OR(sq_10="0110000"AND (sq_1="1111110"OR sq_1="1101101" OR sq_1="0110011" OR sq_1="0011111" OR sq_1="1111111"))OR(sq_10="1101101"AND sq_1="1111110"))) THENalm<='1';ELSEalm<='0';END IF;END PROCESS;END;四、系统仿真/硬件验证五、设计中遇到的问题与体会在置数方面,第一次写时,在时钟沿内,同步置数,下载在试验箱上很难实现,于是把置数改成异步置数。

基于EDA的数字式时钟毕业设计

摘要本设计为一个数字时钟万年历,具有年、月、日、时、分、秒计数显示功能,以24小时循环计数,具有校对功能。

本设计采用EDA技术,以硬件描述语言VHDL为系统逻辑描述手段设计文件,在Quartu sⅡ工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的万年历。

EDA是电子设计自动化(Electronic Design Automation)的缩写,EDA技术是现代电子工程领域的一门新技术,它提供了基于计数机和信息技术的电路系统设计方法。

随着EDA技术的发展,硬件电子电路的设计几乎全部可以依靠计算机来完成,这样就大大缩短了硬件电子电路设计的周期,从而使制造商可以快速开发出品种多,批量小的产品,以满足市场的众多需求。

系统主芯片采用EP2C35F484C8,由时钟模块、控制模块、计时模块、数据译码模块、显示模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,本系统能够完成年、月、日和时、分、秒的分别显示,由按键输入进行数字钟的校时、清零、启停功能。

关键词数字时钟万年历;VHDL;FPGAAbstractThe design for a multi-functional digital clock calendar, with a year, month, day, hours, minutes and seconds count display to a 24-hour cycle count; have proof functions.The use of EDA design technology, hardware-description language VHDL description logic means for the system design documents, in Quartu s Ⅱtools environment, a top-down design, by the various modules together build a FPGA-based digital clock.Electronic design automation EDA (Electronic Design Automation) acronym, EDA technology of modern electrical engineering is a field of new technology, which provides information technology based on counting machine and the circuit design. With the development of EDA technology, hardware design of electronic circuits can rely on almost all computers to be completed, thus greatly reducing the hardware electronic circuit design cycle, enabling manufacturers to quickly develop varieties, small batch of products to meet the the many needs of the market.The main system chips used EP2C35F484C8,make up of the clock module, control module, time module, data decoding module, display and broadcast module. After compiling the design and simulation procedures, the programmable logic device to download verification, the system can complete the year, month, day and the hours, minutes and seconds respectively, using keys to modify, cleared , start and stop the digital clock.Keywords digital clock calendar; VHDL; FPGA目录摘要 (I)1 绪论 (1)1.1 选题背景 (1)1.1.1 课题相关技术的发展 (2)1.1.2 课题研究的必要性 (2)1.2 课题研究的内容 (3)2 FPGA简介 (4)2.1 FPGA概述 (4)2.2 FPGA基本结构 (4)2.3 FPGA系统设计流程 (7)2.4 FPGA开发编程原理 (9)3数字钟总体设计方案 (10)3.1 数字钟的构成 (10)3.2 数字钟的工作原理 (11)4 单元电路设计 (13)4.1 分频模块电路设计与实现 (13)4.2 校时控制模块电路设计与实现 (14)4.2.1 键盘接口电路原理 (14)4.2.2 键盘接口的VHDL描述 (15)4.3 计数模块设计与实现 (23)4.3.1 秒计数模块 (23)4.3.2 日计数模块 (26)4.3.3 月计数和年计数模块 (29)4.4 动态扫描及显示电路设计与实现 (31)4.4.1 动态扫描模块 (31)4.4.2 显示模块 (32)5 实验结论 (33)致谢 (34)参考文献 (36)附录1程序 (36)附录2英文资料及中文翻译 (35)附录3万年历整体框图 (35)1绪论现代社会的标志之一就是信息产品的广泛使用,而且是产品的性能越来越强,复杂程度越来越高,更新步伐越来越快。

基于EDA的数字时钟课程设计报告

EDA课程设计报告目录一、设计内容简介 (2)二、设计要求 (2)基本要求 (2)提高部分要求 (3)三、方案论证(整体电路设计原理) (3)四、各个模块设计原理 (4)4.1 分频电路模块设计 (5)4.2 秒计时器模块设计 (7)4.3 分计时器模块设计 (9)4.4 小时计时器模块设计 (11)4.5 报时模块设计 (13)五、实验中遇到问题及解决方法 (20)六、结论 (20)七、实验心得 (21)八、参考文献 (22)一、设计内容简介设计一个数字钟,可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、清零、快速校时、快速校分、整点报时等功能。

我设计的电路在具有基本功能的基础上,增加了下列功能:改变分频比、不同整点不同报时等;二、设计要求基本要求1、能进行正常的时、分、秒计时功能;2、分别由六个数码管显示时分秒的计时;3、K1是系统的使能开关(K1=0正常工作,K1=1时钟保持不变);4、K2是系统的校分开关;5、K3是系统的校时开关;提高部分要求1、使时钟具有整点报时功能(当时钟计到59’50”时开始报时,四个不同整点发出不同声音);2、分频比可变;三、方案论证(整体电路设计原理)本实验在实现实验基本功能的基础上,加入了整点报时等功能;图1为实验功能方框图:图1 实验方框图数字计时器基本功能是计时,因此首先需要获得具有精确振荡时间的脉振信号,以此作为计时电路的时序基础,实验中可以使用的振荡频率源为4KHZ,通过分频获得所需脉冲频率(1Hz,1KHz,500Hz)。

为产生秒位,设计一个模60计数器,对1HZ的脉冲进行秒计数,产生秒位;为产生分位,通过秒位的进位产生分计数脉冲,分位也由模60计数器构成;为产生时位,用一个模24计数器对分位的进位脉冲进行计数。

整个数字计时器的计数部分共包括六位:时十位、时个位、分十位、分个位、秒十位和秒个位。

显示功能是通过数选器、译码器、码转换器和7段显示管实现的。

基于EDA数字电子钟设计

基于EDA数字电子钟设计[摘要]:随着基于PLD的EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。

本文详细介绍EDA课程设计任务——数字钟的设计的详细设计过程及结果,并总结出心得体会。

[关键字]:EDA技术;VHDL语言;数字钟EDA技术作为现代电子设计技术的核心,它依赖强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、逻辑简化、逻辑分割、逻辑综合,以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

[1]笔者详细介绍在QUARTUS II软件环境下开发基于VHDL语言数字钟的设计。

1.设计任务及要求1、设计内容选用合适的可编程逻辑器件及外围电子元器件,设计一个数字电子钟,利用EDA 软件(QUARTUS Ⅱ)进行编译及仿真,设计输入可采用VHDL硬件描述语言输入法和原理图输入法,并下载到EDA实验开发系统,连接外围电路,完成实际测试。

2、设计要求(1)具有时、分、秒计数显示功能。

(2)具有清零的功能,且能够对计时系统的小时、分钟进行调整。

(3)小时为十二小时制。

2.方案选择与论证数字系统的设计采用自顶向下、由粗到细, 逐步分解的设计方法, 最顶层电路是指系统的整体要求, 最下层是具体的逻辑电路的实现。

自顶向下的设计方法将一个复杂的系统逐渐分解成若干功能模块, 从而进行设计描述, 并且应用EDA 软件平台自动完成各功能模块的逻辑综合与优化, 门级电路的布局, 再下载到硬件中实现设计[1]。

因此对于数字钟来说首先是时分秒的计数功能,然后能显示,附带功能是清零、调整时分。

通过参考EDA课程设计指导书,有以下方案:1.作为顶层文件有输入端口:时钟信号,清零按键,调时按键,调分按键;输出端口有:用于接数码管的八段码输出口,扫描用于显示的六个数码管的输出口。

2.底层文件分为:○1时间计数模块。

EDA课程设计报告数字电子钟

数字钟一、【课题要求】1.设计一个能显示1/10秒、秒、分、时的12小时数字钟。

2.熟练掌握各种计数器的使用。

3.能用计数器构成十进制、六十进制、十二进制等所需进制的计数器。

4.能用低位的进位输出构成高位的计数脉冲。

<注意>1、时钟源使用频率为0.1HZ的连续脉冲。

2、设置两个按钮,一个供“开始”及“停止”使用,一个供系统“复位”用。

3、时钟显示使用数码管显示。

4、“时显示”部分注意12点后显示1点。

5、注意各部分的关系,由低位到高位逐级设计、调试。

二、【分析与设计】数字钟是计数器的综合应用,数字钟由十分之一秒、秒钟、分钟、时钟组成,十分之一秒由十进制计数器74160组成,秒钟由六十进制计数器构成,分钟由六十进制计数器,时钟由十二进制计数器构成。

该数字钟程序的底层文件主要有六进制计数器模块、六十进制计数器模块和十二进制模块,对各模块进行封装,供顶层文件调用,各模块有VHDL文本设计及原理图设计。

输入端clk是连续脉冲,clrn是高电平系统复位,en是高电平使能端,输出端是十分之一秒位、秒钟个位、秒钟十位、分钟个位、分钟十位、时钟个位、时钟十位,最后由7个数码管显示各位的值。

该数字钟程序的底层文件主要有六进制计数器模块、六十进制计数器模块和十二进制模块,对各模块进行封装,供顶层文件调用,各模块有VHDL 文本设计及原理图设计。

程序框图:十分之一秒 秒钟 分钟 小时三、【程序代码及原理图】 1、六进制计数器VHDL 代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY cout6 ISPORT(clk,en,clrn,load:IN STD_LOGIC;date:IN STD_LOGIC_VECTOR(2 DOWNTO 0); cnt:OUT STD_LOGIC_VECTOR(2 DOWNTO 0); co:OUT STD_LOGIC ); END cout6;ARCHITECTURE behave OF cout6 ISSIGNAL q:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINco<='1' WHEN((q="101")AND(en='1'))ELSE'0'; PROCESS(en,clk) BEGINIF clrn='0' THEN q<="000";ELSIF(clk'event and clk='1') THENIF load='0' THEN q<=date;ELSIF en='1' THEN q<=q+1;IF(q="101")THEN q<="000";END IF;END IF;END IF;END PROCESS;cnt<=q;END behave;波形仿真:2、六十进制计数器原理图:波形仿真:3、十二进制计数器VHDL代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cout12 ISPORT(clk,clrn,ldn,en:IN STD_LOGIC;ha:IN STD_LOGIC_VECTOR(3 DOWNTO 0); hb:IN STD_LOGIC;qa:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); qb:out STD_LOGIC);END cout12;ARCHITECTURE behav OF cout12 ISSIGNAL q:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL b:STD_LOGIC;SIGNAL a:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(en,clk)BEGINIF clrn='0' THENq<="0000";ELSIF(clk'event and clk='1') THEN IF ldn='0' THENb<=hb;a<=ha;ELSIF en='1' THENq<=q+1;IF(q="1011")THENq<="0000"; END IF;END IF;END IF;CASE q ISWHEN"0000"=>b<='1';a<="0010"; WHEN"0001"=>b<='0';a<="0001"; WHEN"0010"=>b<='0';a<="0010"; WHEN"0011"=>b<='0';a<="0011"; WHEN"0100"=>b<='0';a<="0100"; WHEN"0101"=>b<='0';a<="0101"; WHEN"0110"=>b<='0';a<="0110"; WHEN"0111"=>b<='0';a<="0111"; WHEN"1000"=>b<='0';a<="1000"; WHEN"1001"=>b<='0';a<="1001"; WHEN"1010"=>b<='1';a<="0000"; WHEN"1011"=>b<='1';a<="0001"; WHEN OTHERS =>NULL;END CASE;END PROCESS;qa<=a;qb<=b;END ARCHITECTURE behav;波形仿真:4、数字钟原理图:波形仿真:四、【结果与测试】根据六进制的波形图判断出六进制的设计正确,实现了0~5的计数,并且在5处产生进位,将六进制进行封装与十进制74160根据原理图设计成六十进制计数器,然后将它进行封装,根据六十进的波仿真图可以看出实现了0~59的计数,并且在59处产生进位,然后将它进行封装。

EDA设计(II)实验报告数字电子钟

EDA设计(II)实验报告-数字电子钟实验报告:数字电子钟一、实验目的本实验旨在通过使用EDA设计软件,设计并实现一个具有时、分、秒功能的数字电子钟。

通过学习使用EDA工具,掌握数字电路设计的基本步骤和技巧,培养实践能力和创新思维。

二、实验原理数字电子钟是一种以数字形式显示时间的装置,它利用了时、分、秒的计时原理。

核心部分包括一个时钟发生器,用于产生标准时间信号,以及一个计数器,用于对时间进行计数并显示。

此外,还需要一些控制逻辑来控制时、分、秒的进位和显示。

三、实验步骤1.设计准备:在开始设计之前,首先明确设计要求和功能。

考虑到实验的复杂性和可实现性,我们采用最简单的电路结构,即基于计数器和译码器的数字电子钟。

2.绘制电路图:使用EDA设计软件(如Quartus II)绘制电路图。

首先创建新项目,然后添加必要的元件(如74LS192计数器、74LS248译码器等),并根据设计要求连接元件。

3.编写程序:使用硬件描述语言(如VHDL或Verilog)编写计数器和译码器的程序。

确保程序能够实现所需的功能,并进行仿真测试。

4.编译和下载:将程序编译成可下载的配置文件,然后下载到FPGA开发板上。

5.硬件测试:连接开发板到PC,启动程序,观察数字电子钟的显示情况。

检查时间是否准确,各部分功能是否正常。

6.性能评估:对数字电子钟的性能进行评估,包括计时精度、稳定性等指标。

根据评估结果对设计进行优化。

四、实验结果与分析1.设计结果:经过上述步骤,我们成功地设计并实现了一个基于FPGA的数字电子钟。

通过EDA软件和硬件描述语言,我们实现了计数器和译码器的功能,并完成了程序的编写和下载。

2.性能分析:经过测试,我们的数字电子钟具有较高的计时精度和稳定性。

时间显示准确,各部分功能正常。

这表明我们的设计是成功的。

3.优化方向:虽然我们的数字电子钟已经具有较好的性能,但仍有一些方面可以优化。

例如,可以考虑添加更多的功能,如闹钟、温度显示等;也可以进一步优化电路结构,降低成本和提高性能。

eda多功能数字钟实验报告

eda多功能数字钟实验报告EDA多功能数字钟实验报告一、引言数字钟是现代生活中常见的一种时间显示工具,其准确性和便携性使其成为人们生活中不可或缺的一部分。

本实验旨在设计并制作一款多功能数字钟,通过EDA(电子设计自动化)软件进行模拟和仿真,验证其功能和性能。

二、设计原理1. 时钟电路:采用CMOS(互补金属氧化物半导体)技术设计时钟电路,包括时钟发生器、计数器和显示器。

时钟发生器产生稳定的方波信号,计数器根据方波信号进行计数,显示器将计数结果以数字形式显示出来。

2. 功能模块:多功能数字钟除了显示时间外,还应具备日期显示、闹钟设置、温度检测等功能。

为实现这些功能,需要添加相应的模块,如时钟芯片、温度传感器、闹钟电路等。

三、电路设计1. 时钟电路设计:根据设计原理,使用EDA软件进行电路设计,选择合适的元器件和连接方式。

通过仿真验证电路的工作稳定性和准确性。

2. 功能模块设计:根据需求,添加相应的功能模块。

时钟芯片用于精确计时和日期显示,温度传感器用于检测环境温度并显示,闹钟电路用于设置闹钟时间并触发报警。

四、电路实现1. 元器件选取:根据电路设计需求,选择合适的元器件。

时钟芯片应具备高精度和稳定性,温度传感器应具备高灵敏度和准确度,闹钟电路应具备可调节和触发功能。

2. 电路布局:将选取的元器件按照电路设计进行布局,注意元器件之间的连接和布线,避免干扰和短路。

3. 电路连接:根据电路设计进行元器件之间的连接,注意连接的正确性和稳定性。

五、仿真与测试1. 仿真验证:使用EDA软件进行电路仿真,检查电路的稳定性和准确性。

通过仿真结果对电路进行调整和优化,确保其正常工作。

2. 功能测试:对多功能数字钟进行功能测试,包括时间显示、日期显示、温度检测和闹钟设置等。

通过测试结果对电路进行调整和改进,确保其功能的完善和可靠性。

六、实验结果与分析经过仿真和测试,多功能数字钟实现了准确的时间显示、日期显示、温度检测和闹钟设置等功能。

EDA课程数字钟设计报告(1)

EDA课程数字钟设计报告(1)EDA课程数字钟设计报告一、设计目标:本次设计要求设计一款数字钟,要求具有如下功能:1.计时功能:能够以时、分、秒的形式显示时间,每经过一秒钟就自动更新时间。

2.报时功能:能够在每个整点或半个小时时报时,并具有报时器关闭功能。

3.闹钟功能:设定闹钟时间后,在设定时间到达时自动响铃。

4.指示功能:能够以数字形式指示时间,并能在背景板上对时间进行显示。

二、方案设计:1.硬件设计:本次设计所需器材包括Cyclone IV E FPGA,七段数码管以及电路底板。

Cyclone IV E是英特尔公司推出的第四代Cyclone系列FPGA器件,具有可编程的逻辑元件、存储器单元和DSP功能单元等特点,足以满足本项目所需的复杂性。

七段数码管是一种显示器件,可以用来显示数字和一些字母。

本设计采用了常见的共阳极七段数码管。

电路底板是一个电路板,用于连接各种测试设备并测试控制电路。

2.软件设计:本设计的软件应该被分为以下几个部分来实现:1.时钟模块:该模块负责自动更新钟表,更新范围应该包括时、分、秒的更新。

2.闹钟模块:该模块负责实现闹钟功能,比较当前时间和设定时间,如果相同,则自动响铃。

3.报时模块:该模块负责在每个整点或半个小时时报时,并可自动关闭报时器。

4.数字显示模块:该模块主要用于以数字形式指示时间,并能在背景板上显示时间。

5.用户交互模块:该模块负责接受用户输入,开关闹钟、报时器,并显示设置的时间和状态信息。

三、实现:1. 外部电路该设计采用七段数码管显示时间,其中每个数码管都有8个引脚,分别对应7条段和一个共阳极。

在数字显示时,需要依次将每个数码管复位,并发送相应的数据信号,以显示所需的数字。

数字与LED的亮度控制采用PWM宽度调制技术,可实现手动调节亮暗。

2. 操作流程本设计操作流程为:用户首先输入设定的闹钟时间、关闭报时器的时间间隔及报时器、闹钟等的开启与关闭状态。

系统开始计时并根据所设定的时间执行相应操作。

EDA课程设计数字电子钟

一、设计任务及要求1、设计内容选用合适的可编程逻辑器件及外围电子元器件,设计一个数字电子钟,利用EDA 软件(QUARTUS Ⅱ)进行编译及仿真,设计输入采用Verilog HDL硬件描述语言输入法,并下载到EDA实验箱系统,连接外围电路,完成实际测试。

2、设计要求(1)具有时、分、秒计数显示功能,该电子钟正常显示小时、分钟、秒,各用2位数码管(共6位数码管),显示范围为0—23时59分59秒。

(2)具有复位清零的功能,且能够对计时系统的小时、分钟进行调整。

(3)定时响铃功能,设计计时到01分10秒后蜂鸣器开始响,持续时间10秒。

二、设计思想对于数字钟来说首先是时分秒的计数功能,然后能显示,附带功能是清零、调整时分,拟定如下方案:计时校正模块中,用1Hz时钟送入秒脉冲信号,“秒计数器”采用60进制,每累计60秒,发出一个“分脉冲”信号,该信号将被送到“分计数器”。

“分计数器”采用60进制计数器,每累计60分,发出一个“分脉冲”信号,该信号被送到“时计数器”。

“时计数器”采用24进制,可实现24小时的累计计数,时钟使用三个输入按键K1、K2、K3,分别控制数字钟的校时、校分、清零,每次分别按下K1、K2按键,对应的时、分计数就加1,按下K3,时间清零。

显示模块中,分别用六个八位数码管显示时钟的时十位、时个位、分十位、分个位、秒十位、秒个位,设置一个时钟脉冲用于扫描数码管显示。

最后的定时响铃功能,本报告设计为计时到01分10秒开始驱动蜂鸣器响,持续十秒。

三、程序清单Verilog HDL源程序:module clock(clk1,clk2,dx,wei,k1,k2,rst,led);input clk1,clk2,k1,k2,rst;output [2:0] wei;output [7:0] dx;output led;reg led;reg [2:0] wei;reg [7:0] dx;reg [7:0] as,ts,am,tm,ah,th,xs;reg [7:0] q;always @(posedge clk1 or posedge rst)beginif(rst){as,ts,xs,am,tm,xs,ah,th}<=8'b00000000; else if(k1)beginif(ah==8'b00001001)beginah=8'b00000000;th=th+8'b00000001;endelse if(ah==8'b00000011&&th==8'b00000010) beginth=8'b00000000;ah=8'b00000000;endelse ah=ah+8'b00000001;endelse if(k2)beginif(am==8'b00001001)beginam=8'b00000000;if(tm==8'b00000101)tm=8'b00000000;else tm=tm+8'b00000001;endelse am=am+8'b00000001;endelse if(as==8'b00001001)beginas=8'b00000000;if (ts==8'b00000101) begints=8'b00000000;if(am==8'b00001001)beginam=8'b00000000;if(tm==8'b00000101)begintm=8'b00000000;if(ah==8'b00001001)beginah=8'b00000000;th=th+8'b00000001;endelseif(ah==8'b00000011&&th==8'b00000010)beginth=8'b00000000;ah=8'b00000000;endelse ah=ah+8'b00000001;endelse tm=tm+8'b00000001;endelse am=am+8'b00000001;end else ts=ts+8'b00000001; endelse as=as+8'b00000001;endalways @(posedge clk2)beginif(wei==3'b111)wei<=3'b000;else wei<=wei+3'b001;endalways @(q or wei or k1)beginif(wei==3'b000)q<=as;else if(wei==3'b001)q<=ts;else if(wei==3'b010)q<=8'b11111111;else if(wei==3'b011)q<=am;else if(wei==3'b100)q<=tm;else if(wei==3'b101)q<=8'b11111111;else if(wei==3'b110)q<=ah;else if(wei==3'b111)q<=th;case(q)0:dx<=8'b11111100;1:dx<=8'b01100000;2:dx<=8'b11011010;3:dx<=8'b11110010;4:dx<=8'b01100110;5:dx<=8'b10110110;6:dx<=8'b10111110;7:dx<=8'b11100000;8:dx<=8'b11111110;9:dx<=8'b11110110;default dx<=8'b00000010;endcaseendalways @(posedge clk1)beginled=1;if(ts==8'b00000001&&am==8'b00000001&&tm==8'b00000000&&ah= =8'b00000000&&th==8'b00000000)led=~led;elseif(as==8'b00000000&&ts==8'b00000010&&am==8'b00000001&&tm= =8'b00000000&&ah==8'b00000000&&th==8'b00000000) led=0;endendmodule四、调试及总结1.仿真波形图2.总结通过此次课程设计,让我对EDA这门技术有了更深的体会,并更好的学会了使用QuartusⅡ软件进行硬件设计。

基于eda数字时钟设计课程设计论文本科论文

西安建筑科技大学课程设计(论文)任务书专业班级:学生姓名:指导教师(签名):一、课程设计(论文)题目数字时钟设计二、本次课程设计(论文)应达到的目的培养自己逻辑设计能力和采用EDA方法进行设计的思想。

三、本次课程设计(论文)任务的主要内容和要求(包括原始数据、技术参数、设计要求等)1.设计一个具有时,分,秒,计数显示功能并以24小时循环计时和清零,调节小时、分钟功能及整点报时功能,整点报时的同时LED灯花样显示的数字时钟。

2. 完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、时序仿真、下载验证等。

四、应收集的资料及主要参考文献[1]潘松.EDA技术与VHDL(第4版).北京:清华大学出版社,2013.80~86.[2]阎石.数字电子技术基础. 北京:高等教育出版社,1998.46~54.[3]谭会生.EDA技术及应用.西安:西安电子科技大学出版社,2001.187~196.[4]潘松,王国栋.基于EDA技术CPLD/FPGA应用前景.北京:清华大学出版社,1993.35~74.[5]邢建平,曾繁泰.VHDL程序设计教程.北京:清华大学出版社,2005.38~47.五、审核批准意见教研室主任(签字)摘要日常生活中数字时钟非常常见,而数字时钟设计的实现方法有很多种,比如可以用单片机实现,也可以通过画电路控制原理图实现。

但是本次课程设计利用EAD技术实现,利用QuartusII软件设计一个数字时钟,进行电路设计和仿真调试,实现了计时,校时,清零,显示和整点报时等多种基本功能,并下载到实验仪器进行调试和验证。

在本次课程设计的过程中,根据设计要求和所要达到的目的,利用QuartusⅡ软件成功仿真出了数字时钟的各个信号状态的波形,并且在得到仿真波形的同时给出了分析结果。

关键词:数字时钟,VHDL,QuartusⅡ,仿真波形AbstractDigital clock in daily life is very common, and the realization of digital clock design method has many kinds, such as can be achieved with a single chip, can also be achieved by drawing circuit control schematic. But the curriculum design using ead technology design, using Quartus II software to design a digital clock, and debug the circuit design and simulation, has realized the time, school, school, clear, keep and the whole point timekeeping and other basic functions, and download to experiment instrument testing and verification. In the curriculum design process, according to the design requirements and to achieve the purpose of, using Quartus II software simulation waveforms of the digital clock of each state of the signal lamp, and get waveform simulation and analysis result is given.Keywords:Digital clock, VHDL, Quartus II, simulation waveforms目录一.绪论 (1)二.数字时钟设计原理 (2)2.1 QuartusⅡ软件介绍 (2)2.2 数字时钟设计原理 (2)三.设计要求和目的 (3)3.1 设计要求 (3)3.2 设计目的 (3)四.电路设计方案分析 (4)4.1 数字时钟总体设计状态图 (4)4.2 数字时钟总设计电路图 (5)4.3 方案论证分析 (5)4.4 子模块电路设计原理 (5)4.4.1 时、分、秒计数显示电路原理 (6)4.4.2 数码管扫描片选驱动模块 (11)4.4.3 整点报时驱动电路 (14)4.4.4 按键抖动消除电路模块 (16)五. 综合仿真测试过程及结果 (18)5.1 全程综合与编译 (18)5.2 仿真测试 (18)5.3 仿真波形图 (19)六. 总结 (22)参考文献 (23)一.绪论人类社会已进入到高度发达的信息化社会。

基于EDA技术的数字钟设计与实现

基于EDA技术的数字钟设计与实现摘要:为使数字钟从电路设计、性能分析到设计出PCB版(即印制电路版)图的整个过程能够在计算机上自动处理完成,从而缩短设计周期、提高设计效率、战小设计风险。

本系统基于EDA技术的设计方法,提出一种采用P-MOS大规模集成电路LM8560作为计数译码的石英数字钟的设计方案,在Prote199SE软件平台下创建原理图和绘制印制电路版,实现了基本计时显示和设置、调整时间和闹钟等功能,最后组装出一个完整的数字钟。

关键词:EDA技术;数字钟;LM8560;Prote199SE;印制电路版数字钟是一种用数字电路技术实现时、分、秒计时的装置,传统数字钟的设计过程要经过设计方案提出、方案验证和修改3个阶段。

一般采用搭接实验电路的方法进行,往往需要实验和修改的反复过程,直到设计出正确的结论为止,例如参考文献中的多功能数字钟的电路设计。

而利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程在计算机上自动处理完成。

电子产品从系统设计、电路设计到芯片设计、PCB设计都可以用EDA工具完成,其中仿真分析、规则检查、自动布局和自动布线是计算机取代人工的最有效部分。

利用EDA工具,可大大缩短设计周期,提高设计效率,减小设计风险。

Protel99SE是一个32位印制板辅助设计软件包,具有强大的设计功能,可以完成原理图、印制板设计和可编程逻辑器件设计。

1 数字钟工作原理数字计时器一般由振荡器、分频器、计数器、译码器、显示器等几部分组成。

这些都是数字电路中应用最广的电路,其组成框图如图1所示。

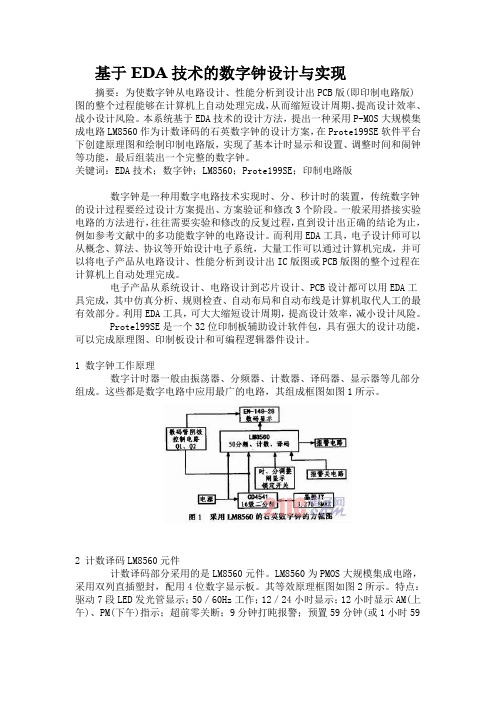

2 计数译码LM8560元件计数译码部分采用的是LM8560元件。

LM8560为PMOS大规模集成电路,采用双列直插塑封,配用4位数字显示板。

其等效原理框图如图2所示。

特点:驱动7段LED发光管显示;50/60Hz工作;12/24小时显示;12小时显示AM(上午)、PM(下午)指示;超前零关断;9分钟打盹报警;预置59分钟(或1小时59分钟)睡眠定时;预置24小时内的报警;使用触摸递增器设置控制;电源失效指示;备用RC振荡器;900 Hz乐音输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子系统课程设计任务书设计题目:基于EDA技术的数字时钟设计设计目的:课程设计是一种复杂的学习实践过程。

设计过程采用系统设计的方法,先分析任务,得到系统设计的要求,然后进行总体设计,划分子系统模块,然后进行详细设计,编写各个功能子系统VHDL代码并进行功能仿真,最后进行整个系统总装并仿真。

设计内容:设计一个采用0.5英寸LED数码管显示的数字时钟系统,工作电源5V,它采用24小时制,具有“时”、“分”、“秒”显示,并且可以校正时间显示。

设计要求:1.由石英晶体多谐振荡器20MHz和分频器产生1Hz标准秒脉冲;(说明:EDA试验箱中晶振频率20MHz,经试验箱内一系列二分频可将频率降低,但无法直接产生1Hz信号,需要大家根据实际情况编制分频器得到1Hz信号);2.秒电路、分电路均为60进制计数,时电路为24进制计数;3.数码管采用动态扫描方式;4.能动手校时,校时模块功能可以自由发挥。

比如可用两个按钮实现校时,A按钮控制调整项目,B按钮调整数字,B按钮还可以根据按下时间长短实现慢调、快调功能。

也可以用三个按钮实现增减两个方向的手动校时。

校时用按钮开关不能超过4个;5.扩展内容:1)进入校时状态后,被调整数字以2Hz闪烁;2)24/12小时可调,处于12小时制时,要有AM/PM显示;3)所有开关加入防抖设计;4)加入检测外部环境亮度功能,夜间自动降低数码管显示亮度;5)加入整点报时电路;6)增加秒表功能;7)增加报闹功能。

6.以上电路功能除外部环境亮度检测电路外均由VHDL代码实现层次式设计,顶层电路可以采用EDA电路图。

设计成果:1.课程设计说明书,要求内容完整,图表完备,条理清楚,字迹工整,程序完整有相应的注解,仿真波形设计合理有必要的分析,引用资料要注明出处。

2.顶层电路原理图,各层电路VHDL代码及仿真波形。

设计说明书目录一、前言二、任务分析和方案设计三、外部输入输出要求四、内部各功能模块1)分频模块2) 秒计数模块SECOND3) 分计数模块MINUTE4)时计数模块HOUR5)整点报时功能模块ALERT6)扫描模块SELTIME7)译码显示功能模块DISPLAY8)按键防抖模块KEY五、系统顶层设计图六、各模块块程序七、心得体会参考文献基于EDA技术的数字时钟设计一.前言EDA简介EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA 软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

二.任务分析和方案设计根据设计内容与要求知,本系统由分频模块(20MHz变为1Hz)、秒计数模块(六十进制)、分计数模块(六十进制)、时计数模块(二十四进制)、时间数据扫描分时选择模块和8421BCD 到7段码的译码模块,再加上一个整点报时模块和按键防抖模块作为发挥部分。

设计框图三、外部输入输出要求1.输入接口代表清零,调时,调分信号RESET、SETHOUR、SETMIN 的引脚分别接高电平、KEY1、KEY2;代表计数时钟信号CLK和扫描时钟信号CLKDSP的引脚分别同1HZ时钟源和200HZ(或更高)时钟源相连。

2.输出接口代表扫描显示驱动信号SEL[2..0]连到SEL2、SEL1、SEL0端,段码信号输出abcdefg连接到7段数码管的段码插口abcdefg端,小数点DP输出端同7段数码管的段码插口DP 相连;代表扬声器驱动信号的引脚SPEAKER同扬声器驱动接口SPEAKER相连;代表花样LED灯显示的信号引脚LAMP[2..0]同3个LED灯相连。

四、内部各功能模块:1)FREQ分频模块:整点报时用的200Hz与时钟用的1Hz的脉冲信号,这里的输入信号是20MHz信号,所以要设计两个分频器,将20MHz变为1Hz、200Hz。

程序见后面。

例图为1000分频,输入为5MHz,输出为5KHz.2)秒计数模块SECOND:60进制,带有进位和清零功能的,输入为1Hz脉冲和高电平有效的清零信号RESET。

程序见后面。

3)分计数模块MINUTE60进制,带有进位和置数功能的,输入为1Hz脉冲和高电平有效的使能信号EN。

程序见后面。

4)时计数模块HOUR:24进制,输入为1Hz脉冲和高电平有效的使能信号EN。

程序见后面。

5)整点报时功能模块ALERT:输入为分/秒信号,输出为SPEAK信号。

程序见后面。

6)扫描模块SELTIME:输入为秒、分、时、扫描时钟CLK1,输出为DP和显示控制信号SEL。

程序见后面。

7)译码显示功能模块DISPLAY:输入为NUM,输出为LED。

程序见后面。

8)按键防抖模块KEY输入为按键信号和20MHz的时钟信号,输出为CK信号。

程序见后面。

五、系统顶层设计图六、各模块程序1.分频器a(20MHZ分成1HZ)程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity freq1 isport(clk:in std_logic;freout:out std_logic);end freq1;architecture behave of freq1 issignal full:std_logic;beginp1:process(clk)variable cqi:std_logic_vector(23 downto 0);beginif clk'event and clk='1' thenif cqi<9999999 thencqi:=cqi+1;else cqi:=(others=>'0');end if;end if;if cqi=9999999 then full<='1';else full<='0';end if;end process;p2:process(full)variable cnt1:std_logic;beginif full'event and full='1' thencnt1:=not cnt1;if cnt1='1' thenfreout<='1';elsefreout<='0';end if;end if;end process;end behave;2.分频器b(20MHz分为200Hz)程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity freq2 isport(clk:in std_logic;freout:out std_logic);end freq2;architecture fun of freq2 isbeginp1:process(clk)variable cq:std_logic_vector(17 downto 0);beginif clk'event and clk='1' thenif cq<99999 thencq:=cq+1;else cq:=(others=>'0');end if;end if;if cq=99999 then freout<='1';else freout<='0';end if;end process;end fun;由上面程序原理可得1000分频的波形图3.秒计数器LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY second ISPORT(clk,reset,setmin:IN STD_LOGIC;enmin:OUT STD_LOGIC;daout:out std_logic_vector(6 downto 0));END entity second;ARCHITECTURE fun OF second ISSIGNAL count:STD_LOGIC_VECTOR(6 downto 0);SIGNAL enmin_1,enmin_2:STD_LOGIC; \\enmin-1为59秒时进位信号BEGIN \\enmin-2:由clk调制后的手动调分脉冲信号串daout<=count;enmin_2<=(setmin and clk); \\setmin为手动分控制信号、高电平有效enmin<=(enmin_1 or enmin_2); \\enmin为向分进位信号PROCESS(clk,reset,setmin)beginif (reset='0') then count<="0000000"; \\若reset为0,则异步清零(即直接复0)elsif (clk'event and clk='1') then \\否则,若clk上升沿到if (count(3 downto 0)="1001") then \\若个位计数值恰好到“1001”if(count<16#60#) then \\ 又若count小于16#60#(即X“60” ;即60H,为十六进制数写法)if (count="1011001") then \\又若count已到59Denmin_1<='1';count<="0000000";\\则置进位为1及count复0else \\若count未到59Dcount<=count+7; \\则加7,而+7=+1+6,即作“加6校正”,使前面16#60#的end if; \\个位转变为8421BCD的容量,即个位的最大值只能是1001了(注)else \\若count不小于16#60#,(即count等于或大于16#60#)count<="0000000"; \\则count复0(有此句,则对无效状态电路可自启动)end if; \\ end if(count<16#60#)elsif (count<16#60#) then \\若个位计数未达到“1001”则转到此句再判:否则若count<16#60#count<=count+1; \\则count加1enmin_1<='0' after 100 ns; \\没有进位发生else \\否则,若count不小于16#60#(即count等于或大于16#60#)count<="0000000"; \\则count复0(有此句,则对无效状态电路可自启动)end if; \\end if(count(3 downto 0)=”1001”)end if; \\end if(reset=’0’)end process;END fun;仿真波形图如下:4.分计数器LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY minute ISPORT(clk,clk1,reset,sethour:IN STD_LOGIC;enhour: OUT STD_LOGIC;daout:out std_logic_vector(6 downto 0));END entity minute;ARCHITECTURE fun OF minute ISSIGNAL count:STD_LOGIC_VECTOR(6 downto 0);SIGNAL enhour_1,enhour_2:STD_LOGIC;BEGINdaout<=count;enhour_2<=(sethour and clk1);enhour<=(enhour_1 or enhour_2);process(clk,reset,sethour)beginif(reset='0')thencount<="0000000";elsif(clk'event and clk='1')thenif(count(3 downto 0)="1001")thenif(count<16#60#)thenif(count="1011001")thenenhour_1<='1';count<="0000000";ELSEcount<=count+7;end if;elsecount<="0000000";end if;elsif(count<16#60#)thencount<=count+1;enhour_1<='0' after 100 ns;elsecount<="0000000";end if;end if;end process;END fun;仿真波形如下图;5.小时文本LIBRARY ieee;use ieee .std_logic_1164.all;use ieee .std_logic_unsigned.all;ENTITY hour ISPORT(clk,reset:IN STD_LOGIC;daout:out std_logic_vector(5 downto 0));END entity hour;ARCHITECTURE fun OF hour ISSIGNAL count:STD_LOGIC_VECTOR(5 downto 0); BEGINdaout<=count;process(clk,reset)beginif(reset='0')thencount<="000000";elsif(clk'event and clk='1')thenif(count(3 downto 0)="1001")thenif(count<16#23#)thencount<=count+7;elsecount<="000000";end if;elsif(count<16#23#)thencount<=count+1;elsecount<="000000";end if;end if;end process;END fun;仿真波形如下图:6.报警文本LIBRARY ieee;use ieee .std_logic_1164.all;use ieee .std_logic_unsigned.all;ENTITY alert ISPORT(clk:IN STD_LOGIC;dain:IN STD_LOGIC_VECTOR(6 DOWNTO 0);speak:OUT STD_LOGIC;lamp:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END alert;ARCHITECTURE fun OF alert ISsignal count:std_logic_vector(1 downto 0);signal count1:std_logic_vector(1 downto 0);BEGINspeaker:process(clk)beginspeak<=count(1);if(clk'event and clk='1')thenif(dain="0000000")thenif(count1>="10")thencount1<="00"; \\-count1为三进制加法计数器elsecount1<=count1+1;end if;end if;end if;end process speaker;lamper:process(clk)beginif(rising_edge(clk))thenif(count<="10")thenif(count="00")thenlamp<="001"; \\循环点亮3只LED灯elsif(count="01")thenlamp<="010";elsif(count="10")thenlamp<="100";end if;count<=count+1;elsecount<="00";end if;end if;end process lamper;END fun;7.时间数据扫描分时选择模块文本LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;ENTITY seltime ISPORT(clk1,reset:IN STD_LOGIC;sec,min: IN STD_LOGIC_VECTOR(6 downto 0);hour:in std_logic_vector(5 downto 0);daout:OUT STD_LOGIC_vector(3 downto 0);dp:OUT STD_LOGIC;sel:out std_logic_vector(2 downto 0));END seltime;ARCHITECTURE fun OF seltime ISSIGNAL count:STD_LOGIC_vector(2 downto 0);BEGINsel<=count;process(clk1,reset)beginif(reset='0')thencount<="000";elsif(clk1'event and clk1='1')thenif(count>="101")thencount<="000";elsecount<=count+1;end if;end if;case count iswhen"000"=>daout<=sec(3 downto 0);dp<='0'; \\送出秒个位,秒个位的dp 不点亮when"001"=>daout(3)<='0';daout(2 downto 0)<=sec(6 downto 4); \\送出秒十位dp<='0'; \\秒十位的dp不点亮when"010"=>daout<=min(3 downto 0);dp<='1'; \\送出分个位,分个位的dp 点亮when"011"=>daout(3)<='0';daout(2 downto 0)<=min(6 downto 4); \\送出分十位dp<='0'; \\分十位的dp不点亮when"100"=>daout<=hour(3 downto 0);dp<='1'; \\送出小时个位,小时个位的dp点亮when others=>daout(3 downto 2)<="00"; \\送出小时十位daout(1 downto 0)<=hour(5 downto 4);dp<='0'; \\小时十位的dp不点亮end case;end processend fun;8.译码器文本LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY deled ISPORT(num: IN std_logic_vector(3 downto 0);led: OUT std_logic_vector(6 downto 0));END deled;ARCHITECTURE fun OF deled ISBEGIN--abcdefgled<="1111110" when num="0000" else \\7段管显示0,led[6..0]=7EH "0110000" when num="0001" else \\7段管显示1,led[6..0]=30H"1101101" when num="0010" else \\7段管显示2,led[6..0]=6DH"1111001" when num="0011" else \\ 7段管显示3,led[6..0]=79H"0110011" when num="0100" else \\7段管显示4,led[6..0]=33H"1011011" when num="0101" else \\ 7段管显示5,led[6..0]=5BH "1011111" when num="0110" else \\7段管显示6,led[6..0]=5FH"1110000" when num="0111" else \\ 7段管显示7,led[6..0]=70H"1111111" when num="1000" else \\ 7段管显示8,led[6..0]=7FH"1111011" when num="1001" else \\7段管显示9,led[6..0]=7BH"1110111" when num="1010" else \\ 7段管显示A,led[6..0]=77H "0011111" when num="1011" else \\ 7段管显示b,led[6..0]=1FH"1001110" when num="1100" else \\ 7段管显示C,led[6..0]=4EH "0111101" when num="1101" else \\ 7段管显示d,led[6..0]=3DH "1001111" when num="1110" else \\ 7段管显示E,led[6..0]=4FH "1000111" when num="1111" ; \\ 7段管显示F,led[6..0]=47H END fun;9.按键A、B防抖程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity key isport(clk1,key1: in std_logic;ck1:out std_logic);end entity key;architecture fun of key issignal tmp1:std_logic_vector(9 downto 0);beginprocess(clk1)beginif rising_edge(clk1) thentmp1(0)<=key1;tmp1(9 downto 1)<=tmp1(8 downto 0);if tmp1="1111111111" then ck1<='1';else ck1<='0';end if ;end if;end process;end fun;仿真波形为:七、心得体会论文的撰写过程是对所学的电子技术基本理论知识的综合运用,对三年专业知识的一次综合应用、扩充和深化,也是对我们理论运用于实际设计的一次锻炼。