命令行下面烧写FPGA程序

FPGA烧写的方式和具体过程分析

FPGA烧写的方式和具体过程分析做了三年四个项目最近才第一次需要深入的搞一下FPGA 烧写。

在这里简单总结一下FPGA烧写的具体过程和玩的花样大家常用的办法对于大部分人来说,至少入门时会用到的烧写方式就两种:① 通过JTAG直接将bitsteam 烧录到FPGA。

断电后信息丢失。

这种方式多用于发开调试阶段,板子一直连着电脑。

通过ISE 或者 Vivado (2020年开始估计还有Vitis)使用JTAG接口烧录。

② 在设计release以后,到产品上一般都是把配置文件通过IDE工具保存存在Nor Flash里。

上电后自动编程FPGA。

较为进阶的一种方法通常情况下这两种方式也就可以满足大部分需求了。

开发调试直接JTAG。

产品出货前,配置文件通过JTAG接口,用VIVADO或者SDK等工具烧进Flash。

之后把接口封起来。

产品需要更新的时候,派技术支持去,重新打开接口,插上JTAG,把新的配置文件烧入Flash。

但是这次项目是个小型手持测量设备,JTAG接口只有在设备拆散状态下通过扩展板才能使用。

组装好后FPGA只能通过Flash来编程。

由于是个精密仪器,每次拆开再组装,整个设备都需要重新校准,非常费事费力。

组装后更新Flash里面的配置文件只能用别的办法了。

这种情况下常用的方法是通过一个和外界有通信能力的微控制器将image发送给FPGA,再由FPGA写入Flash。

这种remote update Xilinx提供了一种解决方案,相对应的ApplicaTIon Note 是:QuickBoot Method for FPGA DesignRemote Update (文档号码XAPP1081)采用这种方案的前提是理解FPGA通过Flash配置的细节,所以以7系FPGA为例先需要看一下这个文档:7 Series FPGAsConfiguraTIon (UG470)主要是看第五章:Chapter 5 ConfiguraTIon DetailsXilinx 远程烧录FPGA方法远程烧录一般是为了设备出厂以后还需对FPGA进行更新或者升级。

FPGA在线烧程序方法(用MCU直接配置FPGA)

用CPU配置Altera公司的FPGA一. 概述目前很多产品都广泛用了FPGA,虽然品种不同,但编程方式几乎都一样:利用专用的EPROM对FPGA进行配置。

专用的EPROM价格不便宜,且大不跟上都是一次性OPT方式编程。

一旦更改FPGA设计,代价不小。

为了进一步降低产品的成本和升级成本,可以考虑利用板上现有CPU子系统中空闲的ROM空间存放FPGA的配置数据,并由CPU 模拟专用EPROM对FPGA进行配置。

本文将以PowerPC860和EP1K30为例,讲解如何利用CPU来配置FPGA。

CPU配置FPGA的优点与Configuration EPROM方式相比本设计有如下优点:1.降低硬件成本——省去了FPGA专用EPROM的成本,而几乎不增加其他成本。

以A LTERA的10K系列为例,板上至少要配一片以上的EPC1,每片EPC1的价格要几十元,容量1M位。

提供1Mb的存储空间,对于大部分单板来说(如860系统的单板),是不需要增加硬件的。

即使增加1Mb存储空间,通用存储器也会比FPGA专用EPROM便宜。

2.可多次编程——FPGA专用EPROM几乎都是OTP,一旦更换FPGA版本,旧版本的并不便宜的EPROM只能丢弃。

如果使用本设计对FPGA配置,选用可擦除的通用存储器保存FPGA的编程数据,更换FPGA版本,无须付出任何硬件代价。

这也是降低硬件成本的一个方面。

3.实现真正"现场可编程"--FPGA的特点就是"现场可编程",只有使用CPU对FPGA 编程才能体现这一特点。

如果设计周全的话,单板上的FPGA可以做到在线升级。

4.减少生产工序--省去了对"FPGA专用EPROM"烧结的工序,对提高生产率,降低生产成本等均有好处。

对于双面再流焊的单板,更可省去手工补焊DIP器件的工序。

当然,与Configuration EPROM方式相比也有一些需要注意的的地方:1.需要CPU提供5根I/O线--一般来说,这并不困难。

FPGA烧录步骤(Quartus II)

下载SOF文件程序到FPGA

Step1

安装相应的驱动,点击Programmer按钮,点击Hardware Setup按钮,选择下载口。

Step2

在Programmer界面点击Auto Detect按钮,选择配置芯片。

双击none文件,选择要烧录的sof文件。

勾选Program/Configure选项,点击Start按钮,下载SOF文件到FPGA。

固化程序

Step1

点击Flie,选择Convert Programming File选项,在Programming file type选项中选择jic文件格式。

Step2

在Configuration Device选项中选择配置芯片。

Step3

在File name选项中更改生成的jic文件名称以及存放的位置。

Step4

在Input files to convert栏中,点击选择Flash Loader,点击Add Device按钮,选择Flash Loader 的芯片,点击SOF Data,选择相应的SOF文件。

点击Generate按钮,生成jic文件。

Step5

回到Programmer界面,点击Add File按钮,选择相应的jic文件。

Step6

删除sof格式的文件(通常情况下在第一行),在名称含有jic的文件选项中,勾选以下几个选项:Program/configure,Verify,Blank-Check。

勾选Program/configure时其他文件的该选项也会自动勾选。

Step7

点击Start按钮,进行程序固化。

By Shawn。

FPGA应用程序烧写

FPGA掉电配置及应用程序引导Xilinx公司的spartan3e开发板上面有丰富的外围器件,就存储器来说有一个16M并行flash,一个4Mbits串行flash,还又一个64M的DDR,在嵌入式开发中,一般我们可能会在FPGA中嵌入cpu软核,让C语言程序在里面运行。

这就涉及到FPGA配置文件的引导,如果C语言程序太大,需要在DDR里面运行的话也涉及到应用程序的引导的问题。

我刚接触到xinlinx的spartan3e开发板时,只会将FPGA配置文件(.bit)直接通过JTAG口下载到芯片里。

后来编写的程序大了,如果将程序直接放到内部的RAM里面就装不下了,这时就只有将程序放到DDR里面运行,如果仅仅是调试应用程序不需要重启开发板后程序也可以运行,那么可以直接用EDK里面的XDM工具通过dow命令直接下载到DDR里面,然后就可以执行了。

但是我们的应用程序和硬件配置调试通过,达到了我们的要求以后我们就想到可不可以将让程序在板子上电时就可以自动运行呢。

因为FPGA是掉电要丢失的,重新上电就必须重新配置。

我们通过查找相关资料,找到了解决烧写问题的解决办法。

首先是配置文件的烧写。

spartan3e提供了3个掉电不丢失的外部存储器,就是上面提到的并行flash,串行flash和Flash PROM。

配置文件都可以烧写到其中任何一个储存器里面。

但是,在我看来,一般的配置问件都是烧写到Flash PROM里面。

烧写方法有很多,可以用Xilinx公司的专门的烧写.mcs文件的工程烧写,也可以用iMPACT烧写。

一般用iMPACT工具烧写,烧写过程如下:打开iMPACT,弹出新建工程时选择Cancle,然后双击窗口左边的PROM File Formater 如下图:弹出的窗口中选择Xilinx PROM文件格式选择mcs,PROM File name为:test.mcs,选择好保存路径点击下一步如下图:上步中点击Next,Select a PROM(bits)选择xcf->xcf04s,点击Add,然后点下一步如下图:上图中点击Next后出现窗口中点击filinsh,弹出消息框点OK,会有一个选择bit问件的窗口,选择一个已经编写好的EDK或者ISE工程生成的.bit文件,OK后提示是否加入其他器件,选择NO,然后双击窗口右边的Generate File,生成.mcs文件如下图所示:然后,双击Boundary Scan,在中间空白处,点击鼠标右键,选择Initialize chain,弹出的第一个窗口中选择Bypass,第二个选择刚才生成的.mcs文件,第三个也选择Bypass,然后选中中间那个模块,点击窗口左下角的program如下图:弹出窗口中选中OK就可以了,烧写完后会看到,Program Successful提示。

FPGA创建工程及烧录程序简单教程

FPGA创建工程及烧录程序简单教程(适用于IntelCycloneII EP2C35F672C8N)1.双击应用程序2.创建一个新工程(文件夹、工程名、文件名及文件路径中都不要带中文)最后finish,工程就建好了3.创建文件点击file~>new~>Design Files~>VHDL File或Verilog HDL File,然后请开始你的表演!(编写程序)(VHDL文件名应与工程名一致4.引脚编辑引脚如何编辑在FPGA自带的光盘中有提及,请在其中寻找并编辑。

(在光盘文件中也有流水灯的引脚文件waterled.qsf,找到并替换工程文件夹下的qsf文件即可实现引脚编辑)这时打开Quartus II 的Pin Planner可以看见引脚分配5.调试程序程序调试成功后会产生waterled.sof与waterled.qof文件6.烧录程序到软件中在烧录程序时应将电源线与USB-blaster如图示插入并打开电源。

打开Programmer后,应如下图所示6.(1)如果未自动弹出hardware,点开Hardware Setup,双击USB-Blaster,然后Close即可。

6.(2)如果没有USB-Blaster,可能是因为没有安装驱动程序右键安装或更新驱动程序文件路径不尽相同,Quartus II 安装在哪个盘就去哪个盘里面找在解决了驱动的问题后我们继续烧录程序Add Device:双击下图箭头位置添加文件(之前调试产生的waterled.sof文件):箭头位置的Program Configure一定要选上!!!然后点击Start,烧录程序烧录成功!!!!!。

Flash烧写步骤

Flash程序烧写步骤1、protect off allerase all(如果要同时烧录fpga0、fpga1、vmlinux内核才使用此命令,擦除所有all。

如果只需要更换其中的部分,可单独擦除,如下。

)2、printenv(查看网络连接情况)3、setenv serverip 192.168.11.60(设置电脑地址)4、setenv ipaddr 192.168.11.201(设置UC IP地址)5、saveenv(保存设置)6、setenv ethact octeth1(erase 18080000 180fffff - 如果单独烧写fpga0则使用该命令擦除flash中原fpga0的内容,如果执行了命令“erase all”,则不用执行该命令)7、tftp 20000000 fp0_v200c_0802.app(使用tftp将fpga0从电脑传到UC内存的20000000地址)tftp 20000000 fp0_v200d_20101108.app(软交换)8、cp.b 20000000 0x18080000 0x39998(【1】将刚传到UC内存地址20000000的fpga0拷贝到UC的flash的18080000地址中;【2】注意文件大小正确,此例的大小是0x39998)(erase 19f40000 19ffffff - 如果单独烧写fpga1则使用该命令擦除flash中原fpga1的内容,如果执行了命令“erase all”,则不用执行该命令)9、tftp 20000000 fp1_v2005_0802.app(使用tftp将fpga1从电脑传到UC内存的20000000地址)tftp 20000000 fp1_v2007_20101207.app(软交换)10、cp.b 20000000 0x19f40000 0x39998(【1】将刚传到UC内存地址20000000的fpga1拷贝到UC的flash的18080000地址中;【2】注意文件大小正确,此例的大小是0x39998)(erase 0x18100000 0x186fffff - 如果单独烧写Linux则使用该命令擦除flash中原Linux的内容,如果执行了命令“erase all”,则不用执行该命令)tftp 20000000 vmlinux.64.2011_01_05.gztftp 20000000 vmlinux.64.2011_01_18.gz(1-18最新内核)11、tftp 20000000 vmlinux.64.2011_01_20.gzcp.b 0x20000000 0x18100000 0x598a41(【1】将刚传到UC内存地址20000000的vmlinux.64.gz拷贝到UC的flash的18080000地址中;【2】注意文件大小正确,此例的大小是0x4fcff0)cp.b 0x20000000 0x18100000 0x598a7e(新版本的大小)在其修改了,还是在终端出现错误12、cp.b 0x20000000 0x18100000 0x5cd32113、askenv boot(设置boot参数)Please enter 'boot':gunzip 0x18100000 0x598a41 0x20000000 0xb00000(1-5号的版本)Please enter 'boot':gunzip 0x18100000 0x598a7e 0x20000000 0xb00000(1-18号的版本)14、Please enter 'boot':gunzip 0x18100000 0x5cd321 0x20000000 0xb00000 (1-20号的版本)15、askenv bootcmd(设置boot参数)16、Please enter 'bootcmd':run boot;Init8201;bootoctlinux17、saveenv(保存设置)18、run bootcmd19、在shell终端执行命令:20、~ # ifconfig eth1 up<激活UC网口eth1>21、~ # ifconfig eth1 192.168.11.1 <为UC的eth1网口配置IP地址>------------------------------------------------------------------------------------------------------------------------------------------------- <<smba挂载>>将保存到tftp里的tables.dat文件导入:zlj<共享文件名称>,192.168.11.30<PC的IP地址> ————————————————————————————————————————~ # mount -t cifs -o username=ZhangLiJun,passwd='zhanglijun' //192.168.11.30/today /mnt~ # cd /mnt/mnt # lsPromptTone.tar rc.local tables.datdis.tar.gz simple.script uscmacippbx.tar.gz system.conf wm.tar.gz/mnt # cp tables.dat /disk/ (copy tables.dat) ----cp * /disk(copy all file)/mnt # lsPromptTone.tar rc.local tables.datdis.tar.gz simple.script uscmacippbx.tar.gz system.conf wm.tar.gz/mnt # cd /disk//disk # lsPromptTone.tar rc.local tables.datdis.tar.gz simple.script uscmacippbx.tar.gz system.conf wm.tar.gz/disk # chmod 777 */disk # lsPromptTone.tar rc.local tables.datdis.tar.gz simple.script uscmacippbx.tar.gz system.conf wm.tar.gz ————————————————————————————————————————HTTP工具wget 网址-------------------------------------------------------------------------------------------------------------------------------------------------22、~ # cd /disk/<打开UC中的目标目录文件夹>23、/disk # tftp -g -r ippbx.tar.gz 192.168.11.60<-g:代表的文件传输方向是从源PC(192.168.11.60)到目的UC(192.168.11.1)> <加载ippbx.tar.gz>24、/disk # tftp -g -r rc.local 192.168.11.60 <加载rc.local >25、/disk # tftp -g -r system.conf 192.168.11.60 <加载rc. system.conf >26、tftp -g -r dis.tar.gz 192.168.11.6027、tftp -g -r PromptTone.tar 192.168.11.6028、tftp -g -r simple.script 192.168.11.6029、tftp -g -r uscmac 192.168.11.6030、tftp -g -r wm.tar.gz 192.168.11.6031、chmod a+rwx *32、chmod 777 * (注意一定要更改权限:UC软件包中的文件都下载完后,重启系统,使下载的文件生效)33、/disk # reboot <软重启>直接掉电重启AX配置说明对AX的配置,只需要根据具体需求,更改AX的IP地址。

FPGA程序烧写流程

F P

G A程序下载方法

(1)设备上电;

(2)双击IMPACT,打开下载软件,界面如图1.1所示。

图1.1IMPACT界面

(3)选择“Loadmostresentproject”,单击“Browse”,选择解压目录里的“FPGA.ipf”,

如图1.2所示。

图1.2路径选择界面

单击“打开”,在弹出的窗口中双击左边的PROMFileFormater,如图1.3所示。

图1.3IMPACT选择窗口界面

在弹出的窗口选择XilinxPROM文件格式选择mcs,PROMFilename为:test.mcs.选择好保存路径进行下一步,如图1.4所示。

图1.4文件选择窗口

点击下一步,选择PROM(bits),选择XC3S1000,点击Add,Finish,会有一个选择bit文件的窗口,选择一个已经编好的EDK或者ISE工程生成的.bit文件,OK后提示是否加入其它器件,选择NO,然后双击窗口右边的GenerateFile,生成.mcs文件,如图1.5所示。

图1.5PROMFileFormater窗口

双击BoundaryScan,在空白处,点击鼠标右键,选择Initializechain,弹出的第一个窗口选择Bypass,第二个选择刚才生成的.mcs文件,第三个也选择Bypass,然后选中间那个模块,点击窗口左下角的program,如图1.6所示。

弹出窗口选中OK就可以了,烧写完后会看到,ProgramSuccessful提示,程序下载完成。

图1.6BoundaryScan选择窗口。

FPGA烧写问题

altera cyclone器件告别AS下载模式,直接用JTAG配置器件进行编程看CYCLONE II的器件手册时,看到一段关于配置器件的描述:可以通过JTAG接口对串行配置器件进行编程,可是里面没有详细的使用方法,在altera的网站上找到了一些关于这个的资料先介绍一下SFL:Serial Flash Loader,它是通过JTAG接口在系统编程(isp)串行配置器件。

这种方法主要是通过FPGA作为一个JTAG与串行配置器件之间的桥梁,优点是能通过一个JTAG接口对器件进行配置,缺点是慢,因为在编程前要对FPGA进行配置。

废话少说,首先编译生成SOF文件,也就是JTAG方式下的下载文件,然后1 在“文件”里选择“Convert Programming Files”,出现对话框后2 在programming file type里选.jic3 在configuration device里选择相应的串行配置器件4 file name选择转换文件5 选sof data,单击add file选择sof文件6 flash loader单击add device选择FPGA器件然后OK生成JIC文件,后面的事情跟JTAG下下载一样,只是将文件类型选为JIC文件,可惜我转换的时候选EPCS1时,老提示容量不够,选EPCS4就没有问题了,大家可以试试。

cyclone器件, jtag和as下载模式JTAG是直接烧到FPGA里面的,由于是SRAM,所以断电后要重烧;AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里;pof文件可以通过as方式下载(保证byteblasterII/usb blaster连接正确);sof文件或者转换的jic可以通过jtag方式下载;这两种下载模式使用的接口外形是完全一样的,要注意区分!使用Flash Loader(JTAG模式)下载EPCS器件一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。

fpga程序烧录流程

fpga程序烧录流程FPGA程序烧录流程一、概述FPGA(Field Programmable Gate Array)是一种可编程逻辑设备,通过烧录程序来实现不同的功能。

FPGA程序烧录是将设计好的逻辑电路程序加载到FPGA芯片中的过程,本文将详细介绍FPGA程序烧录的流程。

二、准备工作在进行FPGA程序烧录之前,我们需要进行一些准备工作:1. 确定烧录的目标FPGA芯片型号:不同的芯片可能有不同的烧录方式和工具。

2. 获取烧录工具:根据芯片型号和厂商提供的信息,下载并安装相应的烧录工具。

3. 编写FPGA程序:使用HDL(硬件描述语言)或者图形化编程软件,编写FPGA的逻辑电路程序。

三、连接硬件在进行烧录之前,需要将目标FPGA芯片与烧录设备连接起来:1. 将FPGA芯片插入烧录设备的插槽中,确保芯片插入正确并稳固。

2. 连接烧录设备与主机:使用USB或者其他接口将烧录设备与主机连接起来。

四、软件设置在进行烧录之前,需要进行一些软件设置:1. 打开烧录工具:根据厂商提供的信息,打开相应的烧录工具软件。

2. 选择目标FPGA芯片:在烧录工具中,选择目标FPGA芯片型号,确保与实际芯片型号匹配。

3. 导入FPGA程序:在烧录工具中,选择要烧录的FPGA程序文件,并导入到烧录工具中。

五、烧录操作进行软件设置后,即可进行烧录操作:1. 连接到目标FPGA芯片:在烧录工具中,选择连接方式,将烧录设备与目标FPGA芯片建立连接。

2. 擦除目标FPGA芯片:在烧录工具中,选择擦除操作,将目标FPGA芯片中原有的程序擦除。

3. 烧录FPGA程序:在烧录工具中,选择烧录操作,将导入的FPGA程序烧录到目标FPGA芯片中。

4. 烧录验证:在烧录完成后,烧录工具会进行烧录验证,确保程序正确烧录到目标FPGA芯片中。

5. 断开连接:烧录完成后,可以选择断开烧录设备与目标FPGA芯片的连接。

六、烧录结果验证在烧录完成后,我们需要对烧录结果进行验证:1. 功能验证:使用适当的测试方法,验证烧录到FPGA芯片中的程序是否能够实现预期的功能。

FPGA在线烧程序方法(用MCU直接配置FPGA)

用CPU配置Altera公司的FPGA一. 概述目前很多产品都广泛用了FPGA,虽然品种不同,但编程方式几乎都一样:利用专用的EPROM对FPGA进行配置。

专用的EPROM价格不便宜,且大不跟上都是一次性OPT方式编程。

一旦更改FPGA设计,代价不小。

为了进一步降低产品的成本和升级成本,可以考虑利用板上现有CPU子系统中空闲的ROM空间存放FPGA的配置数据,并由CPU 模拟专用EPROM对FPGA进行配置。

本文将以PowerPC860和EP1K30为例,讲解如何利用CPU来配置FPGA。

CPU配置FPGA的优点与Configuration EPROM方式相比本设计有如下优点:1.降低硬件成本——省去了FPGA专用EPROM的成本,而几乎不增加其他成本。

以A LTERA的10K系列为例,板上至少要配一片以上的EPC1,每片EPC1的价格要几十元,容量1M位。

提供1Mb的存储空间,对于大部分单板来说(如860系统的单板),是不需要增加硬件的。

即使增加1Mb存储空间,通用存储器也会比FPGA专用EPROM便宜。

2.可多次编程——FPGA专用EPROM几乎都是OTP,一旦更换FPGA版本,旧版本的并不便宜的EPROM只能丢弃。

如果使用本设计对FPGA配置,选用可擦除的通用存储器保存FPGA的编程数据,更换FPGA版本,无须付出任何硬件代价。

这也是降低硬件成本的一个方面。

3.实现真正"现场可编程"--FPGA的特点就是"现场可编程",只有使用CPU对FPGA 编程才能体现这一特点。

如果设计周全的话,单板上的FPGA可以做到在线升级。

4.减少生产工序--省去了对"FPGA专用EPROM"烧结的工序,对提高生产率,降低生产成本等均有好处。

对于双面再流焊的单板,更可省去手工补焊DIP器件的工序。

当然,与Configuration EPROM方式相比也有一些需要注意的的地方:1.需要CPU提供5根I/O线--一般来说,这并不困难。

FPGA程序烧写手册

FPGA程序烧写手册李贵鹏,2012.2.4一、程序的安装注意事项先安装80_quartus_windows,再安装80_nios2eds_windows。

安装需要注意:安装路径和工程路径都不能有空格和中文路径。

破解:打开Crack_QII8.0文件夹。

Step 1:Patch sys_cpt.dll执行QuartusII80_patch.exe,按下[应用补丁]。

若程式出现乱码別在意,此为简体中文,在繁体Windows下会有乱码属正常,若你在乎乱码,请下载微软的AppLocale解決。

Step 2:开启sys_cpt.dllsys_cpt.dll预设会放在C:\altera\80\quartus\bin\下储存license.DAT將license.DAT储存到c:\altera\80\下Step 4:修改license.DAT的HOSTID用记事本开启c:\altera\80\license.DAT,將HOSTID=xxxxxxxxxxxx,改成你的网络卡的physical address,注意不含dash(-),仅含数字和英文字母,修改后存档。

如何得知网络卡的physical address?开始->所有程序->附件->命令提示符输入ipconfig/all,出下以下讯息,红色部分即为physical address(每台电脑不同)。

#把license.dat里的XXXXXXXXXXXX 用您老的网卡号替换(在Quartus II 8.0的Tools菜单下选择License Setup,下面就有NIC ID)检查Quartus II 8.0是否破解成功执行Quartus II,如出現以下画面,表示尚未设定license,选Specify valid license file。

若沒出现此画面,进入Quartus II后,请自行选择Tool->License Setup指定你的License File(license.DAT)位置,必須出现下方紅色圆圈的內容才表示设定成功。

Vivado安装、生成bit文件及烧录FPGA的简要流程

Vivado安装、⽣成bit⽂件及烧录FPGA的简要流程使⽤Vivado制作FPGA的简要流程⼀、在Windows下安装Xilinx Vivado Design Suite:1.1.Xilinx Vivado Design Suite安装⽂件,解压后得到安装⽬录:1.2.运⾏xsetup.exe⽂件,进⼊安装程序。

如果提⽰要更新就直接点continue关掉。

1.3.选⼀些根本看都不会看的I agree.1.4.选第⼆个或者第三个应该都可以。

我感觉第三个看起来更加⾼⼤上⼀点,我就选了第三个:1.5.直接点next:1.6.选择路径,稍等⽚刻就能安装完成:1.7.安装完成后,在开始菜单找到Xilinx Design Tools\Vivado2014.3⽂件夹,打开Manage Xilinx Licenses:1.8.打开后选择左边的load license选项卡:1.9.点击copy license,选中刚才安装⽬录中的crack⽂件夹中的license.lic:1.10.⾄此Windows下的Xilinx Vivado Design Suite已经全部安装完成。

⼆、在服务器中使⽤Vivado⽣成bit⽂件:2.0.由于综合和布局布线需要较好的硬件资源,所以本次流程中综合和布局布线在linux环境的服务器中完成。

在linux环境中运⾏vivado请确保正确安装JVM,在Windows环境下图形界⾯流程完全⼀致。

2.1.在服务器上正确安装JVM后执⾏以下指令:2.2.执⾏“Vivado&”打开Vivado。

注意Vivado会在你执⾏这条命令的⽬录下⽣成⼀些log 信息,所以最好新建⼀个⽬录再打开Vivado:2.3.点击Create New Project建⽴新的项⽬,在弹出的对话框中点Next:2.4.输⼊项⽬名称,然后再点击Next:2.5.选择项⽬类型,因为我们要从RTL代码开始综合,因此选择RTL Project。

fpga烧写步骤

FPGA烧写步骤简介FPGA(现场可编程门阵列)是一种可编程逻辑设备,通常用于实现各种数字电路和系统。

在FPGA烧写过程中,需要按照一定的步骤进行操作。

下面是一份FPGA 烧写的步骤:1.准备开发板和FPGA芯片首先需要准备一个开发板和一块FPGA芯片。

开发板通常包括FPGA芯片、电源电路、晶振、复位电路等,而FPGA芯片则需要根据具体的设计需求选择合适的型号。

2.安装开发环境在烧写FPGA之前,需要安装相应的开发环境,例如Quartus或Vivado等。

这些开发环境通常包括编译器、仿真器、调试器等工具,可以帮助用户完成FPGA设计、编译、仿真和调试等任务。

3.设计FPGA电路使用硬件描述语言(如Verilog或VHDL)设计FPGA电路。

在设计过程中,需要考虑电路的功能、性能和可扩展性等因素。

4.编译设计文件将设计文件编译成二进制文件,以便烧写到FPGA芯片中。

在编译过程中,需要对设计文件进行优化,以提高FPGA的性能和可扩展性。

5.烧写二进制文件到FPGA芯片使用烧写器将编译后的二进制文件烧写到FPGA芯片中。

在烧写过程中,需要注意FPGA芯片的配置方式和烧写速度等因素。

6.验证FPGA电路功能通过仿真器或调试器验证FPGA电路的功能是否正确。

如果发现问题,需要及时进行修改和调试。

7.上板测试将烧写好的FPGA芯片安装到开发板上进行测试。

测试时需要注意电源、信号质量等因素,以确保FPGA芯片能够正常工作。

以上是FPGA烧写的步骤,具体操作可能会因不同的开发环境和FPGA芯片型号而有所不同。

在进行FPGA烧写时,需要注意安全操作,避免因操作不当导致设备损坏或数据丢失等问题。

FPGA烧写程序

FPGA烧写程序⽐如说Altera FPGA,对于⼤部分芯⽚都可以同时采⽤2种编程⽅法,即AS+配置芯⽚⽅式以及JTAG⽅式,下载电缆都可以通⽤,⽐如ByteBlasterII;⽤AS+配置芯⽚⽅式,就是可以将程序下载到配置芯⽚中,配置芯⽚(如EPCS系列)就是⼀块EPROM,它可以在每次系统上电的时候,都⾃动将程序烧写到FPGA中,这样⼀来FPGA就⽤不着每次上电都重新烧写了,跟使⽤CPLD时是⼀样的。

这种⽅式下采⽤的下载⽂件时POF⽂件。

⽤JTAG⽅式的话,就是直接将程序下载到FPGA中,由于FPGA中是基于SRAM结构的,所以每次断电之后程序就没有了,所以必须每次上电都重新下载。

⽤JTAG⽅式的好处在于便于调试,⽐如我们可以⽤QuartusII中的SignalTapII嵌⼊式逻辑分析仪进⾏FPGA I/0引脚上信号的实时观测,⾮常的⽅便。

这种⽅式下采⽤的下载⽂件时SOF⽂件。

另外,如果使⽤了某些没有License的IP Core资源的话,那么必须在JTAG⽅式下,把下载线连在FPGA上才能使⽤,⽽且通常有时间限制,超过时限之后,就需要重新编译程序,产⽣新的SOF下载⽂件。

----------------------------------------------------------AS模式:FPGA器件每次上电时,作为控制器从配置器件EPCS主动发出读取数据信号,从⽽把EPCS的数据读⼊FPGA中,实现对FPGA的编程。

PS模式:EPCS作为控制器件,把FPGA当做存储器,把数据写⼈到FPGA中,实现对FPGA的编程。

该模式可以实现对FPGA在线可编程。

在下载配置的时候对于cycloneII的器件,如ep2c8,在JTAG下载⽅式对应.sof,AS下载⽅式对应 .pof.JTAG是直接烧到FPGA⾥⾯的由于是SRAM 断电后要重烧,AS是烧到FPGA的配置芯⽚⾥保存的每次上电就写到FPGA⾥。

FPGA烧写方法FPGA,CPLD,烧写,烧录,测试

FPGA烧写步骤

一、前期准备:

1、要烧写的fpga程序

2、电脑以及相关软件以及下载器驱动(默认自动安装)。

3、下载工具以及连接线

二、连线方式:通过连接线连接下载器和J2接口,连接的时候注意1口对1口连接,连接错误将导致无法下载。

左图中三角号对应的是1脚,连接图示下载器1脚,另一端连接J2的1脚,下载线另一端连接到笔记本的usb接口上。

注意事项图

连接后效果如下:

连接示意图

三、下载方法

连好线后,打开altera工具软件,默认在开始-所有程序菜单里,如下图

Altera打开路径图

打开工具后点击programmer选择

接着会看到如下图窗口:

下面点击图示按钮选择下载设备:

选择我们的下载设备usb-0,然后close

下一步选择Addfile添加须要烧写的jic文件

勾选图示选项后点击start开始烧写

一直等待右上角提示success就表示烧写成功,拔下线重启计算机即完成烧录。

FPGA程序烧写流程

FPGA程序下载方法

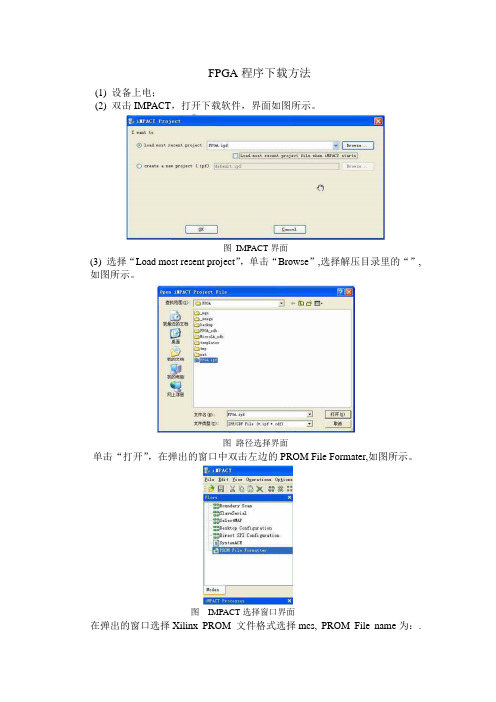

(1) 设备上电;

(2) 双击IMPACT,打开下载软件,界面如图所示。

图IMPACT界面

(3) 选择“Load most resent project”,单击“Browse”,选择解压目录里的“”,如图所示。

图路径选择界面

单击“打开”,在弹出的窗口中双击左边的PROM File Formater,如图所示。

图IMPACT选择窗口界面

在弹出的窗口选择Xilinx PROM 文件格式选择mcs, PROM File name为:.

选择好保存路径进行下一步,如图所示。

图文件选择窗口

点击下一步,选择PROM(bits),选择XC3S1000,点击Add,Finish,会有一个选择bit文件的窗口,选择一个已经编好的EDK或者ISE工程生成的.bit文件,OK后提示是否加入其它器件,选择NO,然后双击窗口右边的Generate File,生成.mcs文件,如图所示。

图PROM File Formater窗口

双击Boundary Scan,在空白处,点击鼠标右键,选择Initialize chain,弹出的第一个窗口选择Bypass,第二个选择刚才生成的.mcs文件,第三个也选择Bypass,然后选中间那个模块,点击窗口左下角的program,如图所示。

弹出窗口选中OK就可以了,烧写完后会看到,Program Successful提示,程序下载完成。

图Boundary Scan选择窗口。

Xilinx FPGA下载烧写教程(超详细)

Step by step 学习下载配置Xilinx之FPGA配合Mars-EDA的Spartan2核心板,用图文方式向大家详细讲述如何下载配置Xilinx 的FPGA。

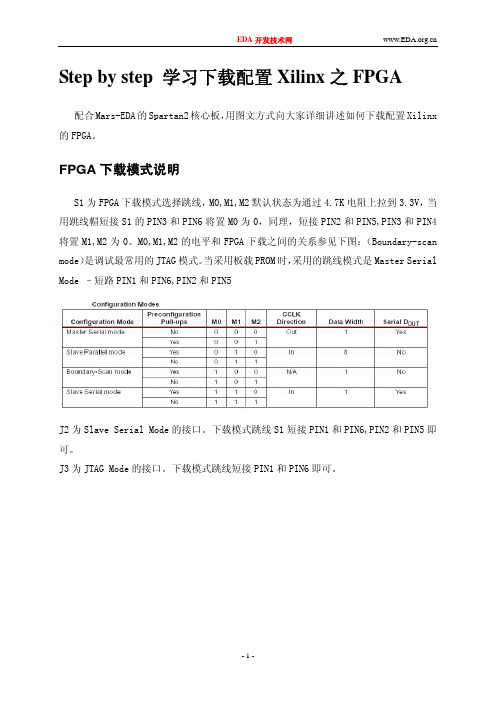

FPGA下载模式说明S1为FPGA下载模式选择跳线,M0,M1,M2默认状态为通过4.7K电阻上拉到3.3V,当用跳线帽短接S1的PIN3和PIN6将置M0为0,同理,短接PIN2和PIN5,PIN3和PIN4将置M1,M2为0。

M0,M1,M2的电平和FPGA下载之间的关系参见下图:(Boundary-scan mode)是调试最常用的JTAG模式。

当采用板载PROM时,采用的跳线模式是Master Serial Mode –短路PIN1和PIN6,PIN2和PIN5J2为Slave Serial Mode的接口。

下载模式跳线S1短接PIN1和PIN6,PIN2和PIN5即可。

J3为JTAG Mode的接口。

下载模式跳线短接PIN1和PIN6即可。

S2跳线说明1.通过JTAG方式烧录FPGA:短接PIN1和PIN3。

2.通过JTAG方式烧录PROM:短接PIN3和PIN5,PIN2和PIN4.3.通过菊花链下载FPGA和烧录PROM:短接PIN3和PIN5,PIN4和PIN6.下面我们利用Spartan2核心板介绍一下通过JTAG菊花链方式下载FPGA和烧录PROM. 硬件跳线选择:1. 跳线S1: 此时要求M0 M1 M2 = 100, 设置FPGA的下载方式为Boundary-scan mode,此时将M1和M2的跳线安上。

跳线S2 : 通过菊花链下载FPGA和烧录PROM:短接PIN3和PIN5,PIN4和PIN6.2. 将Xilinx下载线和核心板上JTAG mode接口J3相连,连接到计算机并口。

核心板上电。

软件操作一、产生PROM配置文件在烧写PROM之前,需要将ISE生成的*.bit文件转换成prom格式的文件才能下载Xilinx 专用的配置PROM中。