Quartus II介绍用Verilog设计

verilog 实验实验一具体步骤

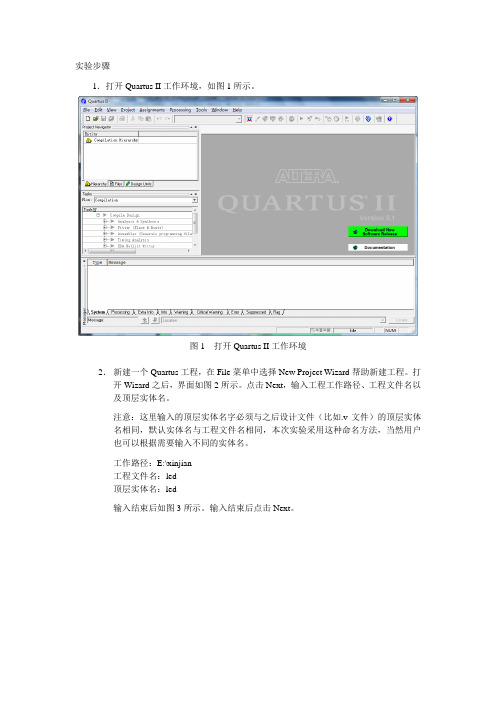

实验步骤1.打开Quartus II工作环境,如图1所示。

图1 打开Quartus II工作环境2.新建一个Quartus工程,在File菜单中选择New Project Wizard帮助新建工程。

打开Wizard之后,界面如图2所示。

点击Next,输入工程工作路径、工程文件名以及顶层实体名。

注意:这里输入的顶层实体名字必须与之后设计文件(比如.v文件)的顶层实体名相同,默认实体名与工程文件名相同,本次实验采用这种命名方法,当然用户也可以根据需要输入不同的实体名。

工作路径:E:\xinjian工程文件名:led顶层实体名:led输入结束后如图3所示。

输入结束后点击Next。

图2 New Project Wizard界面图3 输入设计工程信息3.添加设计文件,界面如图4所示。

如果用户之前已经有设计文件(比如.v文件),那么再次添加相应文件,如果没有完成的设计文件,点击Next,之后添加并且编辑设计文件。

图4 添加设计文件4.选择设计所用器件。

由于本次实验使用Altera公司提供的DE2开发板,用户必须选择与DE2开发板相对应的FPGA器件型号。

在Family菜单中选择CycloneII在Target device选项框中选择Specific device selected in ‘A vailable devices’ list 在A vailable device列表中选择EP2C35F672C6这个型号的器件。

完成后如图5所示,点击Next。

图5 选择相应器件5.设置EDA工具。

设计中可能会用到的EDA工具有综合工具、仿真工具以及时序分析工具。

在本次实验中不使用这些工具,因此点击Next直接跳过设置。

图6 设置EDA工具6.查看新建工程总结。

在基本设计完成后,Quartus II会自动生成一个总结让用户核对之前的设计(如图7所示),确认后点击Finish完成新建。

图7 新建工程总结在完成新建后,Quartus II界面中Project Navigator的Hierarchy标签栏中会出现用户正在设计的工程名以及所选用的器件型号,如图8所示。

QuartusII实验过程示范

QuartusII实验过程⽰范实验⼆⼗进制计数器实验该实验将使⽤Verilog 硬件描述语⾔在DE2-70 开发平台上设计⼀个基本时序逻辑电路——1 位⼗进制计数器。

通过这个实验,读者可以了解使⽤Quartus ⼯具设计硬件的基本流程以及使⽤Quartus II 内置的⼯具进⾏仿真的基本⽅法和使⽤SignalTap II 实际观察电路运⾏输出情况。

SignalTap II 是Quartus ⼯具的⼀个组件,是⼀个⽚上的逻辑分析仪,可以通过JTAG 电缆将电路运⾏的实际输出传回Quartus 进⾏观察,从⽽省去了外界逻辑分析仪时的很多⿇烦。

实验步骤3.1建⽴⼯程并完成硬件描述设计1. 打开Quartus II ⼯作环境,如图3-1 所⽰。

图3-1 Quartus II⼯作环境界⾯2. 点击菜单项File->New Project Wizard 帮助新建⼯程。

参看图3-2。

图3-2 选择New Project Wizard打开Wizard 之后,界⾯如图3-3 所⽰。

点击Next,如图3-3。

第23 页共208 页图3-3 New Project Wizard界⾯3. 输⼊⼯程⼯作路径、⼯程⽂件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和⼯程名的关系,记住⽬前指定的⼯程名与顶层实体名都是Counter10,输⼊结束后,如图3-4 所⽰。

点击Next。

图3-4输⼊设计⼯程信息4. 添加设计⽂件。

界⾯如图3-5 所⽰。

如果⽤户之前已经有设计⽂件(⽐如.v ⽂件)。

那么再次添加相应⽂件,如果没有完成的设计⽂件,点击Next 之后添加并且编辑设计⽂件。

图3-5添加设计⽂件5. 选择设计所⽤器件。

由于本次实验使⽤Altera 公司提供的DE2-70 开发板,⽤户必须选择与DE2-70 开发板相对应的FPGA 器件型号。

在Family 菜单中选择Cyclone II,Package 选FBGA,Pin Count 选896,Speed grade 选6,确认Available devices 中选中EP2C70F896C6,如图3-6。

图形和Verilog的电路设计

实验六图形和Verilog HDL语言混合输入的电路设计一、 实验目的1、学习在QUARTUSII软件中模块符号文件的生成与调用。

2、掌握模块符号与模块符号之间的连线规则与方法。

3、掌握从设计文件到模块符号的创建过程。

二、 实验原理在层次化的设计文件中,经常需要将已经设计好的工程文件生成一个模块符号文件作为自己的功能模块符号在顶层调用,该符号就像图形设计文件中的任何其它宏功能符号一样可被高层设计重复调用。

本实验的实验原理就是用Verilog HDL语言分别实现50M信号源的分频、十进制、六进制模块,然后通过QUARTUSII软件合并成一个设计文件。

实现60进制的功能。

三、 实验内容在实验中,时钟信号为50MHZ,经过分频电路分频后得到一个较低的频率(1HZ)做为计数器的时钟频率进行计数器的加法运算。

得到的值在发光二级管上显示出来。

实验箱中的数字时钟模块、按键开关LED与FPGA的接口电路,以及与FPGA的管脚连接在前面的实验中都做了详细说明,这里不在赘述。

四、 实验步骤1、打开QUARTUSII软件,新建一个工程。

2、选择File>new命令,新建一个Verilog文件。

点击OK按钮确认,然后点击保存按钮,弹出一对话框,重命名为fenpin.v,保存。

在打开的文本编辑器中写分频程序代码。

3、选择File>new命令,新建一个Verilog文件。

点击OK按钮确认,然后点击保存按钮,弹出一对话框,重命名为counter10.v,保存。

在打开的文本编辑器中写十进制程序代码。

4、选择File>new命令,新建一个Verilog文件。

点击OK按钮确认,然后点击保存按钮,弹出一对话框,重命名为counter6.v,保存。

在打开的文本编辑器中写十进制程序代码。

5、在File菜单中选择Create/Update项,进而选择Create Symbol for Current File,点击确定按钮,即可创建一个代表刚才打开的设计文件功能的符号(.bsf),如图6-2所示。

实验三基于QuartusII的流水灯设计仿真

实验收获与体会

理论与实践相结合

通过本次实验,我们将数字电路设计与FPGA应用开发的理论知识与实践相结合,加深了对理论知识的理解,提高了 实际操作能力。

团队合作的重要性

在实验过程中,我们小组成员之间进行了充分的讨论和交流,共同解决问题。这使我们深刻体会到团队合作在解决问 题中的重要性。

不断探索与创新

03 通过设计实现流水灯,培养数字电路设计能力。

实验背景

FPGA(现场可编程门阵列)是一种可编artus II是Altera公司推出的一款FPGA开发软件,提供了完整的FPGA设计流程, 包括设计输入、综合、布局布线、仿真和下载等。

Verilog是一种硬件描述语言,用于描述数字电路的行为和结构,广泛应用于FPGA 设计和ASIC设计领域。

高度集成

Quartus II软件集成了设计、编译、仿真和编程等所有必要 的工具,方便用户进行FPGA开发。

高效编译

Quartus II软件采用了高效的编译算法,能够快速将设计转 换为FPGA可执行的配置文件。

灵活设计

Quartus II软件支持多种硬件描述语言,如VHDL和Verilog, 以及多种设计约束格式,方便用户进行灵活的设计。

03 流水灯设计原理

流水灯简介

01

流水灯是一种常见的LED显示设 备,通过控制LED灯的亮灭顺序 和时间间隔,实现动态的视觉效 果。

02

流水灯通常由多个LED灯珠组成 ,按照一定的顺序排列在一条线 上,通过控制每个LED灯的亮灭 状态,形成连续的视觉效果。

流水灯工作原理

流水灯的工作原理主要是通过控 制每个LED灯的亮灭状态和时间 间隔,实现动态的视觉效果。

控制每个LED灯的亮灭状态通常 是通过微控制器或数字逻辑电路 实现的,时间间隔则通过程序控

实验1 应用QuartusII完成基本组合电路设计

实验1 应用QuartusII完成基本组合电路设计一、实验目的:熟悉QuartusⅡ的Verilog文本设计流程全过程,学习简单组合电路的设计、仿真和硬件测试。

二、实验内容1:首先利用QuartusⅡ完成2选1多路选择器(课本例3-3)的文本编辑输入(mux21a.v)和仿真测试等步骤,给出图1所示的仿真波形。

最后在实验系统上进行硬件测试,验证本项设计的功能。

图1 mux21a功能时序波形module mux21a(a,b,s,y);a,b,s;inputy;outputassign y=(s? a:b);endmodule2、将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图2(或书93页图3-29),并将此文件放在同一目录中。

图2 含2选1多路选择器的模块module muxk(a1,a2,a3,s0,s1,outy);a1,a2,a3;inputs0,s1;inputouty;outputtmp;wireu1(.a(a2),.b(a3),.s(s0),.y(tmp));mux21au2(.a(a1),.b(tmp),.s(s1),.y(outy));mux21aendmodule按步骤对上例分别进行编译、综合、仿真。

并对其仿真波形作出分析说明。

3、引脚锁定以及硬件下载测试:选择目标器件是EP1C6,建议选实验电路模式5(附录文件:GW48 EDA-SOPC 主系统使用说明中图7)。

用键1(PIO0,引脚号为1)控制s0;用键2(PIO1,引脚号为2)控制s1;a3、a2和a1分别接clock5(引脚号为16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。

通过短路帽选择clock0接256Hz信号,clock5接1024Hz,clock2接8Hz信号。

最后进行编译、下载和硬件测试实验(通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调)。

QuartusII里面的verilog文件模板

QuartusII⾥⾯的verilog⽂件模板l 单⼝RAM// Quartus II Verilog Template// Single port RAM with single read/write addressmodule single_port_ram(input [(DATA_WIDTH-1):0] data,input [(ADDR_WIDTH-1):0] addr,input we, clk,output reg [(DATA_WIDTH-1):0] q);parameter DATA_WIDTH = 8;parameter ADDR_WIDTH = 6;// Declare the RAM variablereg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];always @ (posedge clk)begin// Writeif (we)ram[addr] = data;// Read returns NEW data at addr if we == 1'b1. This is the// natural behavior of TriMatrix memory blocks in Single Port// modeq <= ram[addr];endendmodulel 简单双⼝RAM单时钟// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and// single read/write clockmodule simple_dual_port_ram_single_clock(input [(DATA_WIDTH-1):0] data,input [(ADDR_WIDTH-1):0] read_addr, write_addr,input we, clk,output reg [(DATA_WIDTH-1):0] q);parameter DATA_WIDTH = 8;parameter ADDR_WIDTH = 6;// Declare the RAM variablereg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];always @ (posedge clk)begin// Writeif (we)ram[write_addr] <= data;// Read (if read_addr == write_addr, return OLD data). To return// NEW data, use = (blocking write) rather than <= (non-blocking write) // in the write assignment. NOTE: NEW data may require extra bypass // logic around the RAM.q <= ram[read_addr];endendmodulel 简单双⼝RAM(双时钟)// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and// separate read/write clocksmodule simple_dual_port_ram_dual_clock(input [(DATA_WIDTH-1):0] data,input [(ADDR_WIDTH-1):0] read_addr, write_addr,input we, read_clock, write_clock,output reg [(DATA_WIDTH-1):0] q);parameter DATA_WIDTH = 8;parameter ADDR_WIDTH = 6;// Declare the RAM variablereg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];always @ (posedge write_clock)begin// Writeif (we)ram[write_addr] <= data;endalways @ (posedge read_clock)begin// Readq <= ram[read_addr];endendmodulel 完整的双⼝RAM(单时钟)// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and // separate read/write clocksmodule simple_dual_port_ram_dual_clock(input [(DATA_WIDTH-1):0] data,input [(ADDR_WIDTH-1):0] read_addr, write_addr,input we, read_clock, write_clock,output reg [(DATA_WIDTH-1):0] q);parameter DATA_WIDTH = 8;parameter ADDR_WIDTH = 6;// Declare the RAM variablereg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];always @ (posedge write_clock)begin// Writeif (we)ram[write_addr] <= data;endalways @ (posedge read_clock)begin// Readq <= ram[read_addr];endendmodulel 完整的双⼝RAM(双时钟)// Quartus II Verilog Template// True Dual Port RAM with dual clocksmodule true_dual_port_ram_dual_clock(input [(DATA_WIDTH-1):0] data_a, data_b,input [(ADDR_WIDTH-1):0] addr_a, addr_b,input we_a, we_b, clk_a, clk_b,output reg [(DATA_WIDTH-1):0] q_a, q_b);parameter DATA_WIDTH = 8;parameter ADDR_WIDTH = 6;// Declare the RAM variablereg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0];always @ (posedge clk_a)begin// Port Aif (we_a)beginram[addr_a] <= data_a;q_a <= data_a;endelsebeginq_a <= ram[addr_a];endendalways @ (posedge clk_b)begin// Port Bif (we_b)beginram[addr_b] <= data_b;q_b <= data_b;endelsebeginq_b <= ram[addr_b];endendendmodulel 单⼝ROM// Quartus II Verilog Template// Single Port ROMmodule single_port_rom(input [(ADDR_WIDTH-1):0] addr,input clk,output reg [(DATA_WIDTH-1):0] q);parameter DATA_WIDTH = 8;parameter ADDR_WIDTH = 6;// Declare the ROM variablereg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];// Initialize the ROM with $readmemb. Put the memory contents // in the file single_port_rom_init.txt. Without this file,// this design will not compile.// See Verilog LRM 1364-2001 Section 17.2.8 for details on the // format of this file.initialbegin$readmemb("single_port_rom_init.txt", rom);endalways @ (posedge clk)beginq <= rom[addr];endendmodulel 双⼝ROM// Quartus II Verilog Template// Dual Port ROMmodule dual_port_rom(input [(ADDR_WIDTH-1):0] addr_a, addr_b,input clk,output reg [(DATA_WIDTH-1):0] q_a, q_bparameter DATA_WIDTH = 8;parameter ADDR_WIDTH = 6;// Declare the ROM variablereg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];// Initialize the ROM with $readmemb. Put the memory contents // in the file dual_port_rom_init.txt. Without this file,// this design will not compile.// See Verilog LRM 1364-2001 Section 17.2.8 for details on the // format of this file.initialbegin$readmemb("dual_port_rom_init.txt", rom);endalways @ (posedge clk)beginq_a <= rom[addr_a];q_b <= rom[addr_b];endendmodulel ⽆符号加法器// Quartus II Verilog Template// Unsigned Addermodule unsigned_adder(input [WIDTH-1:0] dataa,input [WIDTH-1:0] datab,input cin,output [WIDTH:0] result);parameter WIDTH = 16;assign result = dataa + datab + cin;endmodulel 有符号加法器// Quartus II Verilog Template// Signed addermodule signed_adder(input signed [WIDTH-1:0] dataa, input signed [WIDTH-1:0] datab, input cin,output [WIDTH:0] result);parameter WIDTH = 16;assign result = dataa + datab + cin;endmodulel ⽆符号乘法器// Quartus II Verilog Template// Unsigned multiplymodule unsigned_multiply(input [WIDTH-1:0] dataa,input [WIDTH-1:0] datab,output [2*WIDTH-1:0] dataout );parameter WIDTH = 8;assign dataout = dataa * datab;endmodulel 有符号乘法器// Quartus II Verilog Template// Signed multiplymodule signed_multiply(input signed [WIDTH-1:0] dataa,input signed [WIDTH-1:0] datab,output [2*WIDTH-1:0] dataout);parameter WIDTH = 8;assign dataout = dataa * datab;endmodulel 带输⼊输出寄存器的⽆符号乘法器// Quartus II Verilog Template// Unsigned multiply with input and output registersmodule unsigned_multiply_with_input_and_output_registers (input clk,input [WIDTH-1:0] dataa,input [WIDTH-1:0] datab,output reg [2*WIDTH-1:0] dataout);parameter WIDTH = 8;// Declare input and output registersreg [WIDTH-1:0] dataa_reg;reg [WIDTH-1:0] datab_reg;wire [2*WIDTH-1:0] mult_out;// Store the result of the multiplyassign mult_out = dataa_reg * datab_reg;// Update dataalways @ (posedge clk)begindataa_reg <= dataa;datab_reg <= datab;dataout <= mult_out;endendmodulel 带输⼊输出的有符号乘法器// Quartus II Verilog Template// Signed multiply with input and output registersmodule signed_multiply_with_input_and_output_registers (input clk,input signed [WIDTH-1:0] dataa,input signed [WIDTH-1:0] datab,output reg signed [2*WIDTH-1:0] dataout);parameter WIDTH = 8;// Declare input and output registersreg signed [WIDTH-1:0] dataa_reg;reg signed [WIDTH-1:0] datab_reg;wire signed [2*WIDTH-1:0] mult_out;// Store the result of the multiplyassign mult_out = dataa_reg * datab_reg;// Update dataalways @ (posedge clk)begindataa_reg <= dataa;datab_reg <= datab;dataout <= mult_out;endendmodulel ⽆符号乘加器// Quartus II Verilog Template// Unsigned multiply-accumulatemodule unsigned_multiply_accumulate(input clk, aclr, clken, sload,input [WIDTH-1:0] dataa,input [WIDTH-1:0] datab,output reg [4*WIDTH-1:0] adder_out);parameter WIDTH = 8;// Declare registers and wiresreg [4*WIDTH-1:0] old_result;wire [2*WIDTH-1:0] multa;// Store the results of the operations on the current data assign multa = dataa * datab;// Store the value of the accumulation (or clear it)always @ (adder_out, sload)beginif (sload)old_result <= 0;// Clear or update data, as appropriatealways @ (posedge clk or posedge aclr)beginif (aclr)beginadder_out <= 0;endelse if (clken)beginadder_out <= old_result + multa;endendendmodulel 有符号乘加器(略)l 基本移位寄存器// Quartus II Verilog Template// One-bit wide, N-bit long shift registermodule basic_shift_register(input clk, enable,input sr_in,output sr_out);parameter N = 64;// Declare the shift registerreg [N-1:0] sr;// Shift everything over, load the incoming bit always @ (posedge clk)sr[N-1:1] <= sr[N-2:0];sr[0] <= sr_in;endend// Catch the outgoing bitassign sr_out = sr[N-1];endmodulel Mealy状态机// Quartus II Verilog Template// 4-State Mealy state machine// A Mealy machine has outputs that depend on both the state and // the inputs. When the inputs change, the outputs are updated // immediately, without waiting for a clock edge. The outputs// can be written more than once per state or per clock cycle.module four_state_mealy_state_machine(input clk, in, reset,output reg [1:0] out);// Declare state registerreg [1:0]state;// Declare statesparameter S0 = 0, S1 = 1, S2 = 2, S3 = 3;// Determine the next state synchronously, based on the// current state and the inputalways @ (posedge clk or posedge reset) beginif (reset)S0:if (in)beginstate <= S1; endelsebeginstate <= S1; endS1:if (in)beginstate <= S2; endelsebeginstate <= S1; endS2:if (in)beginstate <= S3; endelsebeginstate <= S1; endS3:if (in)beginstate <= S2; endelsebeginstate <= S3; end// Determine the output based only on the current state // and the input (do not wait for a clock edge).always @ (state or in)begincase (state)S0:if (in)beginout = 2'b00;endelsebeginout = 2'b10;endS1:if (in)beginout = 2'b01;endelsebeginout = 2'b00;endS2:if (in)beginout = 2'b10;endelsebeginout = 2'b01;endS3:if (in)beginout = 2'b11;out = 2'b00;endendcaseendendmodulel Moor状态机// Quartus II Verilog Template// 4-State Moore state machine// A Moore machine's outputs are dependent only on the current state. // The output is written only when the state changes. (State// transitions are synchronous.)module four_state_moore_state_machine(input clk, in, reset,output reg [1:0] out);// Declare state registerreg [1:0]state;// Declare statesparameter S0 = 0, S1 = 1, S2 = 2, S3 = 3;// Output depends only on the statealways @ (state) begincase (state)S0:out = 2'b01;S1:out = 2'b10;S2:out = 2'b11;out = 2'b00;endcaseend// Determine the next statealways @ (posedge clk or posedge reset) begin if (reset)state <= S0;elsecase (state)S0:state <= S1;S1:if (in)state <= S2;elsestate <= S1;S2:if (in)state <= S3;elsestate <= S1;S3:if (in)state <= S2;elsestate <= S3;endcaseendendmodulel 流⽔线加法树// Quartus II Verilog Template// Pipelined binary adder treeinput clk,output [WIDTH-1:0] out);parameter WIDTH = 16;wire [WIDTH-1:0] sum1, sum2, sum3, sum4;reg [WIDTH-1:0] sumreg1, sumreg2, sumreg3, sumreg4;always @ (posedge clk)beginsumreg1 <= sum1;sumreg2 <= sum2;sumreg3 <= sum3;sumreg4 <= sum4;end// 2-bit additionsassign sum1 = A + B;assign sum2 = C + D;assign sum3 = sumreg1 + sumreg2;assign sum4 = sumreg3 + E;assign out = sumreg4;endmodulel 三态缓冲器(完成双向⼝的输⼊输出)// When tri-state buffers are output enabled, they output a value.// Otherwise their "output" is set to high-impedence.inout <bidir_variable>;assign <bidir_variable> = (<output_enable> ? <data> : 1'bZ);l 三态寄存器// Tri-state registers are registers on inout ports. As with any// registers, their output can be updated synchronously or asynchronously.if (!<asynch_output_enable>)begin<bidir_variable> <= 1'bZ;endelsebegin<bidir_variable> <= (<output_enable>) ? <data> : 1'bZ;endendl 双向I/Omodule bidirectional_io (input <output_enable>, input [WIDTH-1:0] <data>, inout [WIDTH-1:0] <bidir_variable>, output [WIDTH-1:0] <read_buffer>);parameter WIDTH = 4;// If we are using the bidir as an output, assign it an output value,// otherwise assign it high-impedenceassign <bidir_variable> = (<output_enable> ? <data> : {WIDTH{1'bz}});// Read in the current value of the bidir port, which comes either// from the input or from the previous assignment.assign <read_buffer> = <bidir_variable>;endmodulel 综合属性1. 保持属性// Prevents Quartus II from minimizing or removing a particular// signal net during combinational logic optimization. Apply// the attribute to a net or variable declaration.(* keep *) wire <net_name>;(* keep *) reg <variable_name>;2. 保护属性// a register.(* preserve *) <variable_declaration>;(* preserve *) module <module_name>(...);l ALTERA原语1. 缓冲器u LCELL LCELL <instance_name> (.in(<data_in>), .out(<data_out>)); ;。

Quartus-Ⅱ8.1入门教程(一个Verilog程序的编译和功能仿真)

Quartus-Ⅱ8.1入门教程(一个Verilog程序的编译和功能仿真)Quartus Ⅱ8.1入门教程(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

快捷工具●快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

●菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

注意以下命名要一致。

第二步:新建工程(file>new Project Wizard)所建工程的1 工程名称:2第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序以实现一个与门和或门为例,Verilog描述源文件如下:module test(a,b,out1,out2);input a,b;Output out1,out2;assign out1=a&b; assign out2=a | b; endmodule然后保存源文件;第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis ))点击确定完成语法检查第六步:(锁定引脚,点击工具栏的(pin planner ))(注:如果不下载到开发板上进行测试,引脚可以不用分配)双击location 为您的输入输出配置引脚。

第七步:整体编译(工具栏的按钮(startComplilation))各个端口顶层某块的第八步:功能仿真(直接利用quratus 进行功能仿真)1 将仿真类型设置为功能仿真(Assignments>setting>Simulator Settings>下拉>Function )2 建立一个波形文件:(new>Vector Waveform File )然后导入引脚(双击Name 下面空白区域>Node Finder>list>点击):接下来设置激励信号(单击>选择>Timing>Multiplied by1)设置b 信号源的时候类同设置a 信号源,最后一步改为然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist )设置输入接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):观察波形,刚好符合我们的逻辑。

设计工具Quartus II简介

设计工具Quartus II简介二十世纪后半期,随着集成电路和计算机技术的飞速发展,数字系统也得到了飞速发展。

在可编程集成电路的开发过程中,以计算机为工作平台,融合了电子应用技术,计算机技术,智能化技术最新成果的电子设计自动化(Electronic Design Automation)技术能辅助各种规模的设计工作。

Quartus II是Altera 提供的FPGA/CPLD开发集成环境,Altera是世界最大可编程逻辑器件供应商之一。

Quartus II在21世纪初推出,是Altera前一代FPGA/CPLD集成开发环境MAX+plus II 的更新换代产品,其界面友好,使用便捷。

在Quartus II上可以完成设计输入、HDL综合、布线布局(适配)、仿真和下载和硬件测试等流程,它提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程。

Altera的Quartus II 提供了完整的多平台设计环境,能满足各种特定设计的需要,也是单芯片可编程系统(SOPC) 设计的综合性环境和SOPC 开发的基本设计工具,并为Altera DSP 开发包进行系统模型设计提供了集成综合环境。

Quartus II设计工具完全支持VHDL、Verylog 的设计流程,其内部嵌有VHDL、Verilog 逻辑综合器。

Quartus II也可以利用第三方的综合工具,如Leonardo Spectrum Synplify Pro FPGA Complier II并能直接调用这些工具。

同样,Quartus II具备仿真功能,同时也支持第三方的仿真工具,如ModelSim。

此外,Quartus II与MATLAB和DSP Builder结合,可以进行基于FPGA的DSP系统开发,是DSP硬件系统实现的关键EDA工具。

Quartus II包括模块化的编译器。

编译器包括的功能模块有分析综合器(Analysis &Synthesis)、适配器(Filter)、装配器( Assembler)、时序分析器(Timing Analyzer)、设计辅助模块(Design Assistant)、EDA网表文件生成器(EDA Netlist Writer) 和编辑数据接口(Complier Database Interface 等。

quartus II建立工程 verilog

参考资料:FPGA设计技巧与案例开发详解(第2版)

《FPGA设计技巧与案例开发详解(第2版)》是2015年12月电子工业出版社出版的图书,作者是 韩彬、于潇宇、张雷鸣。

内ห้องสมุดไป่ตู้介绍

FPGA初学者学习quartus II建立工程,使用verilog HDL。本例使用win7系统下安装的quartus II 13.0版本演示。

参考资料:实例讲解基于Quartus II的FPGA/CPLD数字系统设计快速入门

《实例讲解基于Quartus II的FPGA/CPLD数字系统设计快速入门》是2017年电子工业出版社出版 的图书,作者是赵艳华,温利,佟春明。

参考资料:基于Quartus II的FPGA/CPLD设计

《基于QuartusII的FPGA/CPLD设计》是2006年电子工业出版社出版的图书,作者是李洪伟。

参考资料:基于Verilog的FPGA设计基础

《基于Verilog的FPGA设计基础》是2006年西安电子科技大学出版社出版的图书,作者是杜慧敏、 李宥谋、赵全良。

参考资料:基于Verilog HDL的数字系统设计快速入门

《基于Verilog HDL的数字系统设计快速入门》是2016年电子工业出版社出版的图书,作者是高 敬鹏、武超群。

方法/步骤

进入工程,新建verilog文件,点击 “File”-->“New”-->"Verilog HDL File"-->"OK"

方法/步骤

在新建verilog HDL中输入设计文件 (硬件描述功能情况),完毕后,点 击保存(或ctrl+s),文件名为 “test.v”保存到自己需要的路径里, 选择“保存(S)”默认路径即可;

quartusii编程语法

quartusii编程语法(最新版)目录1.Quartus II 简介2.Quartus II 编程基础3.Quartus II 编程语法特点4.Quartus II 编程实践与应用正文【Quartus II 简介】Quartus II 是一款由 Altera 公司开发的 FPGA 设计软件,它提供了丰富的功能和强大的工具,帮助工程师们快速实现数字逻辑电路设计。

Quartus II 集成了硬件描述语言(HDL)编译器、调试器和仿真器,支持多种 HDL 语言,如 VHDL 和 Verilog。

【Quartus II 编程基础】Quartus II 编程主要包括以下几个步骤:1.创建工程:新建一个工程,导入所需的库文件和 HDL 源文件。

2.编写代码:使用 VHDL 或 Verilog 语言编写数字逻辑电路的描述。

3.编译:将编写的代码编译为二进制文件,以便下载到 FPGA 芯片。

4.下载:将编译好的二进制文件下载到 FPGA 芯片,进行实际运行。

5.调试:使用 Quartus II 的调试器和仿真器对运行的电路进行调试和验证。

【Quartus II 编程语法特点】Quartus II 支持多种 HDL 语言,下面以 Verilog 为例,介绍其编程语法特点:1.模块声明:使用`module`关键字定义一个模块,声明模块所需的输入输出端口和参数。

2.变量声明:使用`wire`、`reg`或`integer`等关键字声明变量,定义其数据类型和作用域。

3.逻辑描述:使用`and`、`or`、`not`等逻辑门实现数字逻辑电路。

4.循环结构:使用`always`关键字定义循环结构,实现时序逻辑电路。

5.条件语句:使用`if`、`else`和`while`等关键字实现条件判断和循环控制。

6.函数和任务:使用`function`和`task`关键字定义函数和任务,实现模块的复用和层次化设计。

【Quartus II 编程实践与应用】以一个简单的半加器电路为例,介绍 Quartus II 编程实践:1.创建工程,导入 VHDL 库文件。

QuartusII软件使用及设计流程

时序优化

时序分析

在Quartus II中进行时序分析,确保设计满足时序要求,找出关键 路径并优化。

延迟调整

通过调整逻辑单元的时序参数,减小关键路径的延迟,提高时钟频 率。

布局优化

合理安排逻辑单元的位置,减小信号传输延迟,提高时序性能。

面积优化

优化算法

采用高效的算法和优化策略,减小设计规模, 降低面积成本。

低功耗硬件选择

选择低功耗硬件器件和IP核,从硬件层面降低功 耗。

06

Quartus II实际应用案 例

数字钟设计案例

总结词

数字钟设实现数字钟的原理图 设计和编程。

详细描述

首先,在Quartus II软件中创建一个新的工程,选择合适的FPGA芯片型号。然后,使 用原理图输入方式设计数字钟电路,包括分频器、计数器、译码器等模块。接着,进行 仿真测试以确保设计正确。最后,将设计文件下载到FPGA芯片中,完成数字钟的硬件

保存配置

完成配置后,保存配置文件以便以后使用。

许可证激活与验证

获取许可证文件

从Altera官网或授权合作伙伴处获取Quartus II软件 的许可证文件。

激活许可证

运行许可证激活程序,输入许可证文件中的激活码进 行激活。

验证许可证

启动Quartus II软件,验证许可证是否有效,确保软 件正常使用。

完成串口通信的硬件实现。

THANKS FOR WATCHING

感谢您的观看

Quartus II软件中提供了大量的IP核,用户可以直接调用这些IP核进行设计, 避免了重复造轮子,提高了设计效率。

IP核定制

对于一些特殊需求,用户可以通过定制IP核的方式实现。Quartus II软件提供了 IP核定制工具,用户可以根据需求对IP核进行修改和定制,以满足特定设计要求。

基于QuartusII13.0的优先编码器设计与仿真

基于QuartusII 13.0的优先编码器设计与仿真发布时间:2021-12-06T06:37:59.811Z 来源:《现代电信科技》2021年第14期作者:滕艳菲黄春梅[导读] 基于QuartusII13.0版本用verilog语言设计的优先编码器,如果用其自带仿真器仿真,在建立vwf文件时,将输入X值在仿真工具栏中设置为时,输出结果不正确,本文主要针对这一问题,提出解决方法。

(广东科技学院)摘要:基于QuartusII13.0版本用verilog语言设计的优先编码器,如果用其自带仿真器仿真,在建立vwf文件时,将输入X值在仿真工具栏中设置为时,输出结果不正确,本文主要针对这一问题,提出解决方法。

关键词:QuartusII 13.0;优先编码器;仿真;X仿真设置一引言优先编码器是FPGA初学者经常练习的组合逻辑电路,一般在QuartusII软件里以verilog编码,以QuartusII自带仿真器仿真。

下面介绍基于QuartusII13.0版本的优先编码器的设计及仿真。

二优先编码器的设计优先编码器的真值表如图1所示,采用QuartusII13.0,依据真值表设计的verilog文本如图2所示:四结束语本文介绍了基于QuartusII13.0版本的优先编码器的设计及仿真过程,并对仿真遇到的问题提出了一种解决方法,仿真结果符合预期。

值得一提的是R信号只产生了高低电平,并没有X和Z,尚不完全是真正意义的随机信号,更好的仿真方法值得继续探索。

参考文献:[1]王静霞. FPGA/CPLD应用技术(Verilog语言版)第2版[M],北京:电子工业出版社,2014[2]范舒颜.基于 Quartus Ⅱ的数字逻辑电路功能设计[J],经验交流,2019.06[3]曹志成. 基于 LabVIEW 的 3 位优先编码器的实现[J],信息通信,2015年第11期。

基于Quartus2的Verilog实例详解

基于Quartus2的Verilog 实例详解说明:该例程分两部分:第一部分主要是通过一个半加器的实验来演示Quartus2软件的基本用法,从而使入门者很快上手。

第二部分主要是VerilogHDL 的实例,其中每个程序都是已经调试通过的,尤其是后边的数字钟、频率计等都有已经建好的工程,若将其下到实验箱就可以直接观察效果。

由于水平有限,纰漏之处还请指正!第一部分半加器的实现1、打开Quartus2软件如下图所示:图1—1Quartus II 软件图形用户界面我们首先简单了解一下各部分的作用:菜单栏工程栏资源管理窗编译状态显示窗信息显示窗标题栏:显示当前工程的路径和程序的名称。

菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、资源分配(Assignments)、操作(Processing)、工具(Tools)、窗口(Window)、和帮助(Help)、9个下拉菜单组成。

工具栏:包含常用命令的快捷图标。

资源管理窗:显示当前工程中所有相关的文件。

工程工作区:对不同的工程文件进行各种操作。

编译状态显示窗:显示模块综合、布局布线过程和时间。

信息显示窗:显示软件综合、布局布线过程中的信息。

下面我们通过一个半加器的实验来进一步学习:我们首先要新建一个工程,按下图进行操作单击后会出现下列的窗口,按照下图继续进行……鼠标单击,下一步保存文件路径工程名称鼠标单击,下一步鼠标单击,下一步元件系列选择具体元件选择(我们采用实验箱上的Cyclone系列的EP1C3T144C8)最后单击下一步工程建好后新建一个图形文件,File New(如下图所示)用鼠标选中,单击OK 确定后弹出如下图所示的窗口最后,单击“Finish ”图形文件编辑区双击图形文件编辑区会弹出如下图所示的对话框。

在原理图中调入与门(and2)、异或门(xor)、输入端口(input)、输出端口(output)等元件,可在“Name”的文本框中直接输入元件的名字,也可以在元件库中直接寻找,调入元件。

QuartusII软件使用及设计流程

(2)选择元件。在原理图编辑窗中的任何一个位置上双

击鼠标的左键将跳出一个元件选择窗。

参数可设置的强函数元件库 MAX+plus库

基本逻辑元件库

基本逻辑元件库中的元件 由此输入所需要的元件名

(3)连接各元器件并命名。

在图1-39中,将光标移到input右侧,待变成十字形光标 时,按下鼠标左键(或选中工具栏中的 工具,光标自动 会变成十字形的连线状态),再将光标移动到异或门的左 侧,待连接点上出现蓝色的小方块后释放鼠标左键,即可 看到input和异或门之间有一条连线生成。

(3)编辑输入信号并保存文件。在图1-22中单击 “Name”下方的“A”,即选中该行的波形。在本 例中将输入信号“A”设置为时钟信号,单击工具 栏中的 按钮,弹出“Clock”对话框,此时可以

修改信号的周期、相位和占空比。设置完后单击 “OK”按钮,输入信号“A”设置完毕。同理设置 其他输入信号“B”,最后单击保存文件按钮 , 根据提示完成保存工作,如图1-23所示。同时,

使用New Project Wizard 可以为工程指定工作目录、分配 工程名称以及指定最高层设计实体的名称,还可以指定要 在工程中使用的设计文件、其他源文件、用户库和EDA 工具,以及目标器件系列和具体器件等。在此要利用 “New Preject Wizard”工具选项创建此设计工程,并设定 此工程的一些相关的信息,如工程名、目标器件、综合器、 仿真器等。

(4)第三方工 具选择。 如图1-7所示, 用户可以选择所 用到的第三方工 具,比如 ModleSim、 Synplify等。在 本例中并没有调 用第三方工具, 可以都不选.

(5)确认信息对话框。 图1-8所示。建立的工程的名称、选择的器件和 选择的第三方工具等信息,如果无误的话就可 以单击“Finish”按钮,弹出如图1-9所示的窗口, 在资源管理窗口可以看到新建的工程名称 half_add。

VERILOG & QUARTUS II

VERILOG 範例二 - REGISTER (BEHAVORAL MODELING)

module Register( D, clock, enable, Q );

// 需和 input , output 相符 output input reg Q; // 宣告 output 埠 D, clock, enable; // 宣告 input 埠 Q; // 表示 out 除了是輸出, 也是可暫存值的變數(註)

Rbar Qbar

module SR_latch(Q, Qbar, Sbar, Rbar); SR_latch 為 自訂模組名稱, 括號內的為input或output接腳名稱(和順序位置)

當別的module需要使用到這個module時,就需使用 module名稱來描述與該module的連接方式 nand n1(Q,Sbar,Qbar); (nand為QuartusII內建的module) 表示module名稱為nand,n1則是自訂的別名 同一個module可宣告多次 (即同架構module,不同實體) 所以別名間不能相同,以方便區別階同的module實體 建議是取有意義的名稱,方便設計者辨視

VERILOG 範例一 - SR LATCH (GATE-LEVEL MODELING)

module SR_latch(Q, Qbar, Sbar, Rbar);

// 需和 input , output 相符 output input Q, Qbar; Sbar, Rbar; // 宣告 output 埠 // 宣告 input 埠

reset 1 0 0 0 enable x 0 1 1 c/ld x x 1 0 Q 0 Q Q+1 D

QuartusII使用入门及FPGA设计流程

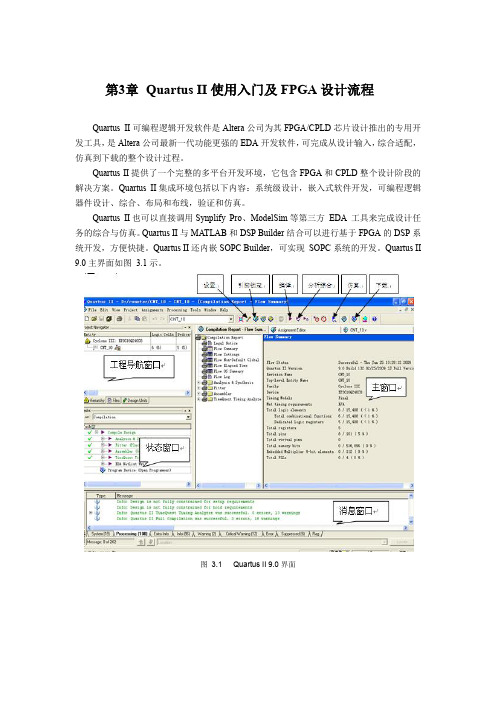

第3章Quartus II使用入门及FPGA设计流程Quartus II可编程逻辑开发软件是Altera公司为其FPGA/CPLD芯片设计推出的专用开发工具,是Altera公司最新一代功能更强的EDA开发软件,可完成从设计输入,综合适配,仿真到下载的整个设计过程。

Quartus II提供了一个完整的多平台开发环境,它包含FPGA和CPLD整个设计阶段的解决方案。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件设计、综合、布局和布线,验证和仿真。

Quartus II也可以直接调用Synplify Pro、ModelSim等第三方EDA 工具来完成设计任务的综合与仿真。

Quartus II与MATLAB和DSP Builder结合可以进行基于FPGA的DSP系统开发,方便快捷。

Quartus II还内嵌SOPC Builder,可实现SOPC系统的开发。

Quartus II 9.0主界面如图3.1示。

图 3.1 Quartus II 9.0界面3.1 Quartus II 基本设计流程Quartus II 设计的主要流程包括创建工程、设计输入、分析综合、编译、仿真验证、编程下载等,其一般流程如图 3.2所示。

下面以硬件描述语言输入法设计计数器为例,说明Quartus II 的设计流程。

3.1.1 创建工程使用Quartus II 设计电路被称作工程。

Quartus II 每次只进行一个工程,并将该工程的全部信息保存在同一个文件夹中。

开始一项新的电路设计,首先要创建一个文件夹,用以保存该工程的所有文件。

之后便可通过Quartus II 的文本编辑器编辑Verilog 源文件并存盘。

3.1.2 设计输入Quartus II 中包含原理图输入和硬件描述语言输入两种方法。

(1)原理图输入原理图输入的优点是,设计者不必具有诸如编译技术、硬件描述语言等新知识就能迅速入门,完成较大规模的电路系统的设计,且具有直观,易于理解的特点,适合于初学者使用。

FPGA设计及QUARTUS_II教程

FPGA设计及QUARTUS_II教程FPGA(Field Programmable Gate Array)设计是指通过对FPGA芯片的编程来实现特定电路的功能。

FPGA芯片是一种可编程的逻辑芯片,它由一系列可配置的逻辑单元和可编程的互连网络组成,可以被编程为实现任意的数字电路。

QUARTUS II是美国Altera公司开发的一款FPGA设计软件,被广泛应用于FPGA设计领域。

QUARTUS II提供了直观的图形化界面,支持多种编程语言(如VHDL和Verilog),并具有强大的仿真和调试功能。

下面介绍FPGA设计的基本流程以及QUARTUSII的使用方法。

1.确定设计需求:首先,需要明确设计的功能以及性能要求。

对于复杂的设计,可以将其分解为多个模块,每个模块实现一个特定的功能。

2. 编写设计代码:使用VHDL或Verilog等编程语言,根据设计需求编写代码。

设计代码描述了电路的逻辑功能和数据流动。

3.进行功能仿真:在QUARTUSII中创建一个新的项目,导入设计代码,并进行仿真。

仿真可以验证设计的正确性以及性能是否达到要求。

4.进行综合和布局布线:在QUARTUSII中选择综合和布局布线选项,将设计代码综合为FPGA可以理解的底层逻辑,并进行布局布线,将逻辑单元和互连网络进行物理连接。

6.进行硬件调试:通过FPGA芯片提供的调试接口,可以对设计进行硬件调试。

QUARTUSII提供了丰富的调试工具,如信号波形查看器和时序分析器,可以帮助快速定位和修复问题。

通过学习FPGA设计及QUARTUSII的教程,可以了解FPGA的基本原理和设计流程,掌握QUARTUSII软件的使用方法,从而能够独立完成FPGA 设计项目。

同时,还需要不断实践和积累经验,才能逐渐成为一名优秀的FPGA工程师。

Quartus II介绍用Verilog设计

Quartus II介绍用Verilog设计第一章介绍本教程介绍了Quartus II®CAD系统介绍。

它是利用FPGA器件实现电路的设计给出了一个典型的CAD流程的一般概述,并说明这种流动是在Quartus II 软件实现。

通过使用Quartus II软件在Altera公司的FPGA器件实现一个非常简单的电路提供一步一步的指示,说明了设计过程。

Quartus II系统包括所有流行的进入一个描述所需的电路转换为CAD系统的方法充分的支持。

本教程使用Verilog设计输入方法,在用户指定的Verilog 硬件描述语言所需的电路。

本教程的其他两个版本也可以;一个用VHDL硬件描述语言,另一种是基于在一个示意图的形式定义所需的电路。

在设计过程中的最后一步是在实际的FPGA器件的配置设计的电路。

显示如何做到这一点,它是假定用户接入到Altera DE系列发展和教育局连接到电脑,Quartus II软件安装。

一个读者没有访问DE系列板仍然会发现有用的教程学习如何编程和配置FPGA执行任务。

屏幕捕捉在教程中使用Quartus II 11版得到;如果使用其他版本的软件,有些图片可能略有不同。

内容:•典型的CAD流•开始•开始一个新项目•Verilog设计输入•编制设计•引脚分配•模拟电路设计•编程和配置FPGA器件•测试电路设计第二章背景计算机辅助设计(CAD)软件可以很容易地通过使用可编程逻辑器件实现所需的逻辑电路,如现场可编程门阵列(FPGA)芯片。

一个典型的FPGA CAD流程如图1所示。

图1 典型的CAD流该CAD流程包括以下步骤:●设计输入–所需的电路是指定的示意图,或使用硬件描述语言,如Verilog或VHDL●合成–输入设计合成了一个电路构成的逻辑元素(LES)在FPGA芯片提供●功能仿真–合成电路进行测试,验证其功能的正确性;这种模拟不考虑任何时机的问题●拟合的CAD–钳工工具确定LES的定义在表到LES在实际的FPGA芯片的位置;它也选择路由的导线在芯片制造所需的之间的连接特定的LES●时序分析–传播延迟在安装电路的各种路径的分析,提供了电路的预期性能的指示●时序仿真–拟合电路进行测试,验证其功能的正确性和时间●编程和配置–所设计的电路是通过编程配置交换机配置的LES和建立所需的布线连接的FPGA芯片实现的一个物理本教程介绍了Quartus II软件的基本特征。

Quartus II 使用方法——数字电路课程设计实验

Quartus II 使用方法实例:设计一个3线-8线译码器,真值表如表1所示:(1)设置使能控制端,低电平有效。

(2)输出高电平有效。

(3)采用Verilog语言的文本输入方式。

(4) 进行功能仿真与验证。

程序://Gate-level description of a 3-to-8line decoder (Figure 1)module _3to8decode(A1,A2,A3,E,Y);input A1,A2,A3,E; //定义输入信号output[7:0] Y; //定义输出信号wire A1not,A2not,A3not,Enot; //定义电路内部节点信号not n1(A1not,A1), //非门调用n2(A2not,A2),n3(A3not,A3),n4(Enot,E);and n5(Y[0],A3not,A2not,A1not,Enot), //与门调用n6(Y[1],A3not,A2not,A1,Enot),n7(Y[2],A3not,A2,A1not,Enot),n8(Y[3],A3not,A2,A1,Enot), //与门调用n9(Y[4],A3,A2not,A1not,Enot),n10(Y[5],A3,A2not,A1,Enot),n11(Y[6],A3,A2,A1not,Enot),n12(Y[7],A3,A2,A1,Enot);endmodule一.打开Quartus II二.创建一个工程1.执行菜单命令“File > New Project Wizard”,打开Introduction对话框。

单击“Next”。

2.选择所建立工程的工作目录,输入工程名称、顶层实体名工程名称可以是任何名字,建议使用和顶层实体名相同的名字。

顶层实体名称必须和顶层文件名字相同!单击“Next”。

3.若事先没有写好verilog程序,则直接点next3.注意红色圈出的部分,其他的默认,点next4.默认,next5.确认红色圈出部分一致,点finish工程创建完成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Quartus II介绍用Verilog设计第一章介绍本教程介绍了Quartus II®CAD系统介绍。

它是利用FPGA器件实现电路的设计给出了一个典型的CAD流程的一般概述,并说明这种流动是在Quartus II 软件实现。

通过使用Quartus II软件在Altera公司的FPGA器件实现一个非常简单的电路提供一步一步的指示,说明了设计过程。

Quartus II系统包括所有流行的进入一个描述所需的电路转换为CAD系统的方法充分的支持。

本教程使用Verilog设计输入方法,在用户指定的Verilog 硬件描述语言所需的电路。

本教程的其他两个版本也可以;一个用VHDL硬件描述语言,另一种是基于在一个示意图的形式定义所需的电路。

在设计过程中的最后一步是在实际的FPGA器件的配置设计的电路。

显示如何做到这一点,它是假定用户接入到Altera DE系列发展和教育局连接到电脑,Quartus II软件安装。

一个读者没有访问DE系列板仍然会发现有用的教程学习如何编程和配置FPGA执行任务。

屏幕捕捉在教程中使用Quartus II 11版得到;如果使用其他版本的软件,有些图片可能略有不同。

内容:•典型的CAD流•开始•开始一个新项目•Verilog设计输入•编制设计•引脚分配•模拟电路设计•编程和配置FPGA器件•测试电路设计第二章背景计算机辅助设计(CAD)软件可以很容易地通过使用可编程逻辑器件实现所需的逻辑电路,如现场可编程门阵列(FPGA)芯片。

一个典型的FPGA CAD流程如图1所示。

图1 典型的CAD流该CAD流程包括以下步骤:●设计输入–所需的电路是指定的示意图,或使用硬件描述语言,如Verilog或VHDL●合成–输入设计合成了一个电路构成的逻辑元素(LES)在FPGA芯片提供●功能仿真–合成电路进行测试,验证其功能的正确性;这种模拟不考虑任何时机的问题●拟合的CAD–钳工工具确定LES的定义在表到LES在实际的FPGA芯片的位置;它也选择路由的导线在芯片制造所需的之间的连接特定的LES●时序分析–传播延迟在安装电路的各种路径的分析,提供了电路的预期性能的指示●时序仿真–拟合电路进行测试,验证其功能的正确性和时间●编程和配置–所设计的电路是通过编程配置交换机配置的LES和建立所需的布线连接的FPGA芯片实现的一个物理本教程介绍了Quartus II软件的基本特征。

它显示了如何使用该软件可以实现电路采用Verilog硬件描述语言指定的设计。

它使得使用的图形用户接口来调用Quartus II的命令。

在本教程中,读者将了解:●创建一个项目●设计入门使用Verilog代码●合成电路的Verilog代码●拟合成电路到Altera公司的FPGA●分配电路的输入和输出,在FPGA●模拟电路设计●编程和配置在Altera公司的FPGA芯片特定DE系列板引脚第三章开始每个逻辑电路,或子电路,采用Quartus II软件被称为一个项目。

该软件可以在一个项目上,让所有的信息在一个单一的目录(文件夹)项目中的文件系统。

开始一个新的逻辑电路设计,第一步是创建一个目录来保存文件。

在本教程将设计文件,我们将使用一个目录introtutorial。

本教程的实例是双向光的一个简单的控制电路。

开始Quartus II软件。

你应该看到一个显示类似于图2中的一个。

这显示由几个Windows提供的Quartus II软件的特点,其中用户选择的计算机鼠标。

大多数通过Quartus II软件提供的指令可以通过使用一组菜单位于标题栏访问。

例如,在图2中点击菜单“文件打开如图3所示的菜单,鼠标左键。

点击鼠标左键在出入境退出Quartus II软件。

在一般情况下,只要用鼠标选择点,左边的按钮是用来。

因此,我们通常不会指定按哪个按钮。

在少数情况下,当需要使用鼠标右键,它将被明确指定。

图2 主要的Quartus II显示图3 文件菜单的例子一些命令需要访问序列中的两个或两个以上的菜单。

我们使用公约>Menu1 menu2>项目表明,选择所需的命令,用户应首先点击Menu1鼠标左键,然后在菜单中点击menu2,然后在menu2点击项目。

例如,文件>退出使用鼠标退出系统。

许多命令都可以通过点击一个工具栏的显示一个图标调用。

看到一个图标关联的命令,位置在图标和鼠标会出现工具提示显示命令名称。

3.1 Quartus II的在线帮助Quartus II软件提供全面的在线文档,回答了许多使用该软件时可能出现的问题。

从帮助菜单访问该文件,提供一定的思路,让读者通过浏览帮助菜单获得有价值的信息。

如果没有指定Web浏览器,Quartus将错误消息的报错。

指定Web浏览器,点击工具>选项…>一般>互联网连接。

指定要在Web浏览器领域的Web浏览器的路径。

用户可以通过快速搜索帮助主题选择帮助>搜索,将打开一个对话框,关键词可以进入。

另一种方法,上下文敏感的帮助,提供快速查找特定主题的文档。

在使用大多数应用程序中,按下键盘上的F1键打开帮助显示应用程序可用的命令。

第四章开始一个新项目开始一个新的设计,我们首先需要定义一个新的设计方案。

Quartus II软件设计者的任务容易通过向导的形式提供支持。

创建一个新的项目如下:1.选择文件>新项目向导图4到窗口,这要求项目名称和目录。

图4 一个新的项目创建2.将工作目录设置为introtutorial;当然,如果你喜欢你可以选择使用一些其他的目录名称。

项目必须有一个名字,通常包括相同的顶层实体和项目。

选择light为项目和顶层实体的名称,如图4所示。

按“下一步”。

由于我们还没有创建的目录introtutorial,Quartus II软件显示的弹出框图5询问是否要创建所需的目录。

单击“是”,从而导致在图6窗口。

图5 Quartus II软件可以为项目创建一个新目录图6 该向导可以包括用户指定的设计文件3.该向导可以很容易地指定的现有文件(如果有)应包括在项目。

假设我们没有任何现有的文件,请单击“下一步”,从而导致在图7窗口。

图7 选择设备的家庭和一个特定的设备4.我们必须指定的装置的设计的电路将执行类型。

选择你的DE系列板cycloneseries设备的家庭。

我们可以让Quartus II软件选择家庭中的一个特定的设备,或者我们可以选择装置明确。

我们将采取后一种方法。

从可用设备列表,选择你的德系列板适当的设备名称。

一系列的设备在德系列主板的名字可以在表1中找到。

按“下一步”按钮,打开如图8所示的窗口。

板设备名称DE0 Cyclone III EP3C16F484C6DE1 Cyclone II EP2C20F484C7DE2 Cyclone II EP2C35F672C6DE2-70 Cyclone II EP2C70F896C6DE2-115 Cyclone IVE EP4CE115F29C7表1 DE系列FPGA器件名称图8 其它EDA工具可以指定5.用户可以指定任何第三方工具应使用的。

一种常用的电子电路CAD软件项的EDA工具,其中的缩写代表电子设计自动化。

这个词是在Quartus II 中使用的信息,参阅第三方工具,它的开发和销售以外的Altera公司的工具。

因为我们将仅仅依靠QuartusⅡ工具,我们不会选择其他工具。

按“下一步”。

6.所选择的设置,总结出现在图9所示的屏幕。

按“完成”,并返回到主Quartus II窗口,但指定为新的项目,显示在标题栏,如图10所示。

图9 设置一个DE2板工程实例总结图10 用于创建项目在DE2板Quartus II显示第五章设计输入采用Verilog代码作为一个设计实例,我们将使用双向光控制器电路如图11所示。

该电路可以用来控制两个光开关,X1和X2,在一个封闭开关对应的逻辑值1。

也是电路真值表中给出的图。

请注意,这只是输入X1和X2异或功能,但我们将指定使用显示的大门。

图11 该光源控制器电路要求的电路由图12中的Verilog代码描述。

请注意,Verilog模块称为光在图4中给出的名称匹配,这是创建项目时指定。

此代码可以键入文件使用任何文本编辑器存储ASCII文件,或通过使用Quartus II文本编辑设施。

当文件可以是任何名称,它是一种常见的设计实践中使用相同的名称作为顶级Verilog 模块的名称。

文件名必须包含扩展.V,这表明Verilog文件。

因此,我们将命名light.v。

光源模块(x1, x2, f);输入 x1, x2;输出 f;分配 f = (x1 & »x2) j (»x1 & x2);结束模块图12 Verilog代码为在图11电路5.1使用Quartus II文本编辑器本节说明如何使用Quartus II文本编辑器。

如果你们愿意的话可以使用一些其他的文本编辑器来创建的Verilog源代码文件跳过这一节,我们将命名light.V。

选择文件>新图13中得到的窗口,选择Verilog HDL语言文件,然后单击“确定”。

这将打开文本编辑器窗口。

第一步是为要创建的文件指定一个名字。

选择文件>保存打开的弹出框,如图14所示。

在保存类型选择框的Verilog HDL 文件。

在箱标记文件名light。

把标记在箱文件添加到当前项目。

单击“保存”,将文件放入目录introtutorial导致文本编辑器窗口如图15所示。

输入的Verilog代码在图12中的文本编辑器,输入文件>保存该文件,或键入快捷ctrl-s。

大多数文本编辑器中可用的命令是不言自明的。

文本是显示在插入点,这是由一个薄的垂直线表示。

插入点可以通过使用键盘上的方向键或用鼠标移动。

文本编辑器的两个特点是特别方便打字的Verilog代码。

首先,编辑器可以显示不同类型的不同颜色的Verilog语句,这是默认的选择。

第二,编辑器会自动缩进的文本在新的一行,它匹配一行。

这些选项可以通过工具>选项>文本编辑器设置控制。

图13 准备一个Verilog文件图14 命名文件图15 文本编辑器窗口。

Verilog代码的语法有时是困难的设计师要记住。

为了解决这个问题,文本编辑器提供了一个收集的Verilog模板。

该模板提供各种类型的Verilog语句的例子,例如一个模块的声明,一个总是块,和赋值语句。

这是值得浏览模板选择编辑>插入模板>Verilog HDL熟悉这个资源。

5.2添加到项目设计文件我们表明,当讨论图6,你可以告诉Quartus II软件设计文件应作为当前项目的一部分。

看到已包括在light项目文件列表,选择作业>设置,从而导致在图16窗口。